TC74AC112P/F/FN

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74AC112P,TC74AC112F,TC74AC112FN

Dual J-K Flip Flop with Preset and Clear

The TC74AC112 is an advanced high speed CMOS DUAL J-K

FLIP FLOP fabricated with silicon gate and double-layer metal

wiring C

Bipolar Schottky TTL while maintaining the CMOS low power

dissipation.

device changes state on negative going transition of the clock

pulse.

accomplished by a low logic level on the corresponding input.

discharge or transient excess voltage.

2

MOS technology.

It achieves the high speed operation similar to equivalent

In accordance with the logic level given J and K input this

CLEAR

All inputs are equipped with protection circuits against static

and

PRESET

are independent of the clock and

Features

Note: xxxFN (JEDEC SOP) is not available in

Japan.

TC74AC112P

TC74AC112F

• High speed: f

• Low power dissipation: I

• High noise immunity: V

• Symmetrical output impedance: |IOH| = IOL = 24 mA (min)

Capability of driving 50 Ω

transmission lines.

• Balanced propagation delays: t

• Wide operating voltage range: V

• Pin and function compatible with 74F112

= 170 MHz (typ.) at VCC = 5 V

max

= 4 μA (max) at Ta = 25°C

CC

NIH

= V

= 28% VCC (min)

NIL

∼

t

−

pLH

pHL

(opr) = 2 to 5.5 V

CC

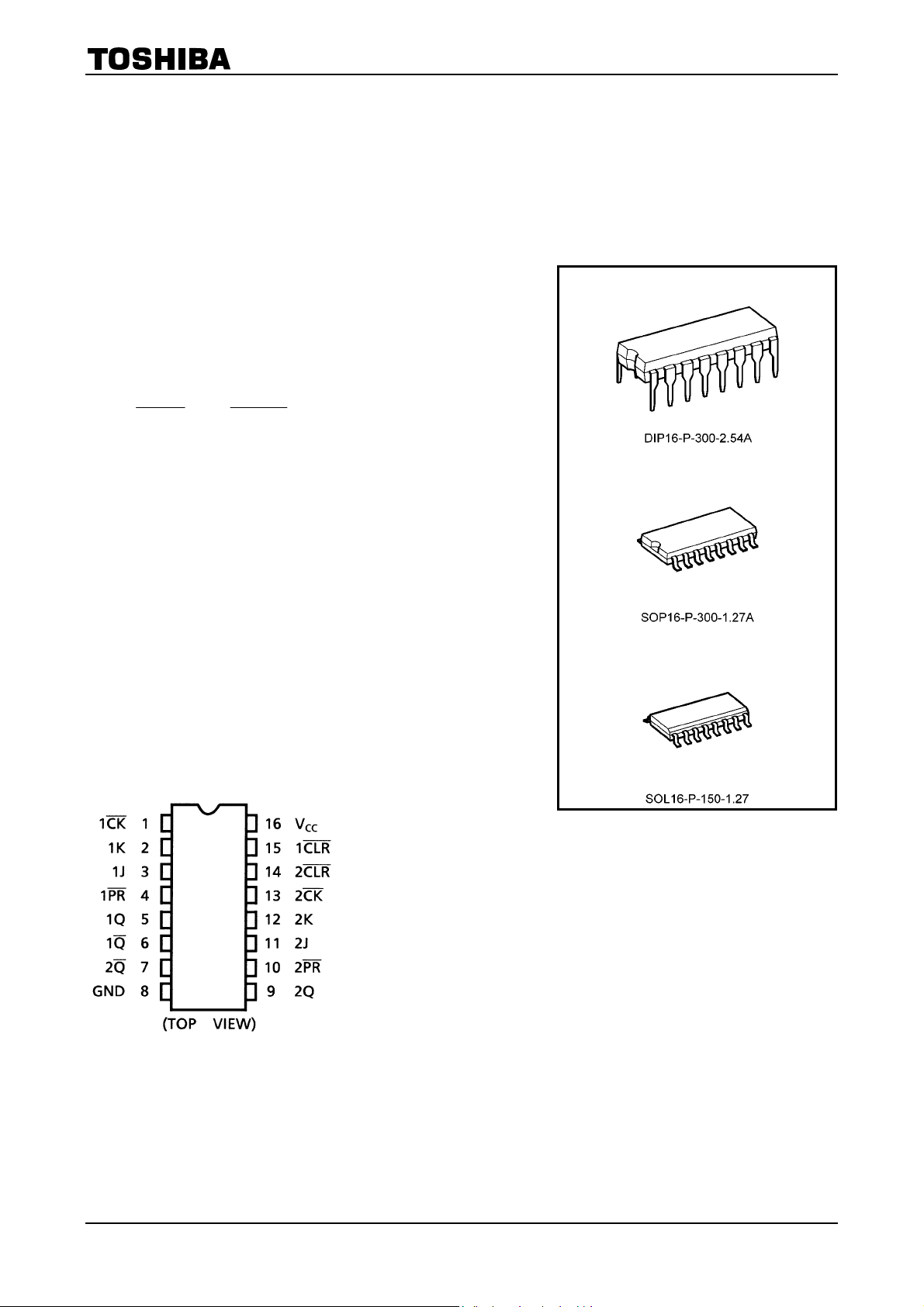

Pin Assignment

TC74AC112FN

Weight

DIP16-P-300-2.54A : 1.00 g (typ.)

SOP16-P-300-1.27A : 0.18 g (typ.)

SOL16-P-150-1.27 : 0.13 g (typ.)

1

2007-10-01

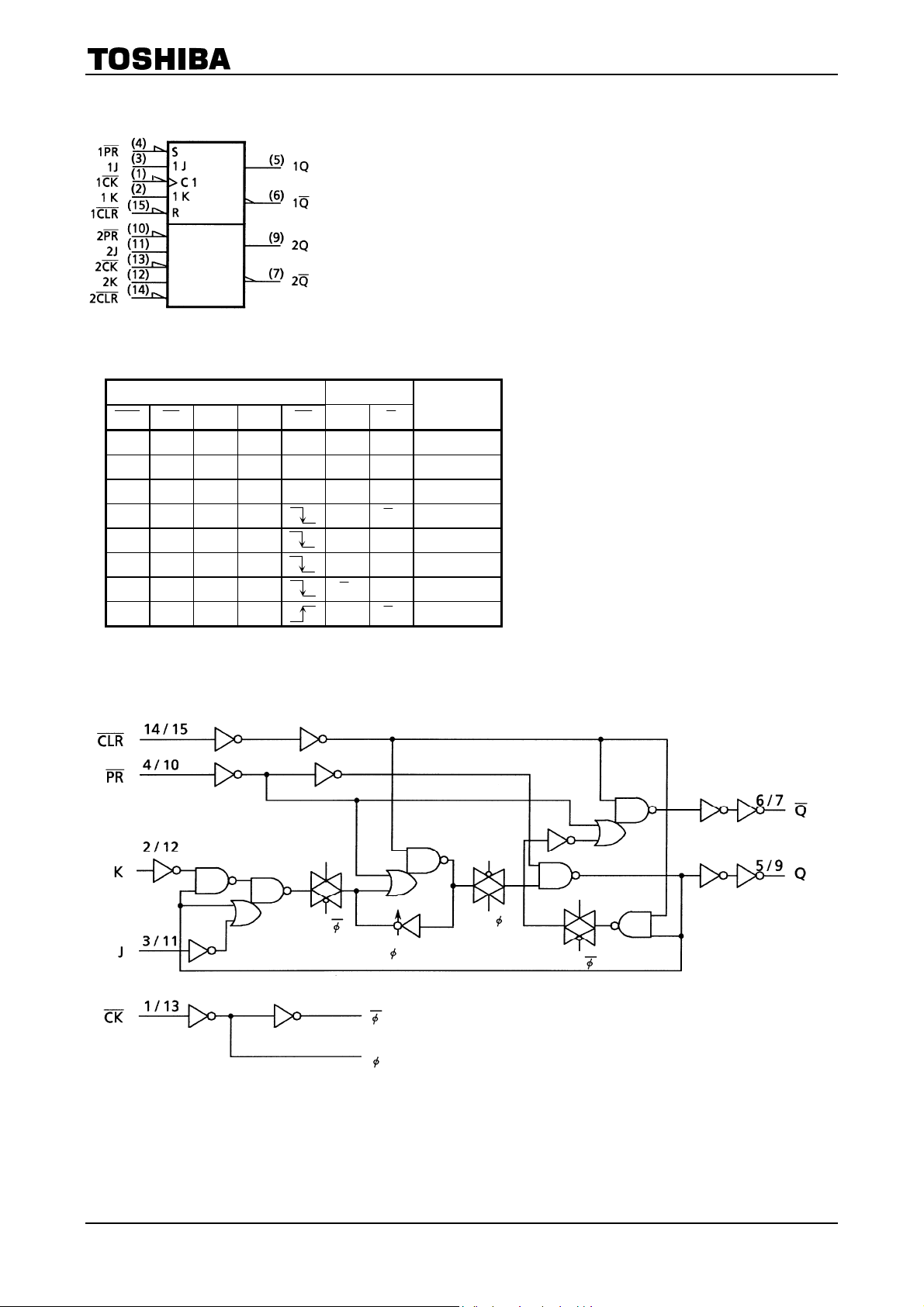

IEC Logic Symbol

Truth Table

TC74AC112P/F/FN

Inputs Outputs

CLR PR J K CK Q Q

L H X X X L H Clear

H L X X X H L Preset

L L X X X H H

H H L L Qn

H H L H L H

H H H L H L

H H H H

H H X X Qn

QnToggle

Q

n

Q

Q

n

n

No Change

No Change

X: Don’t care

System Diagram

Function

2

2007-10-01

TC74AC112P/F/FN

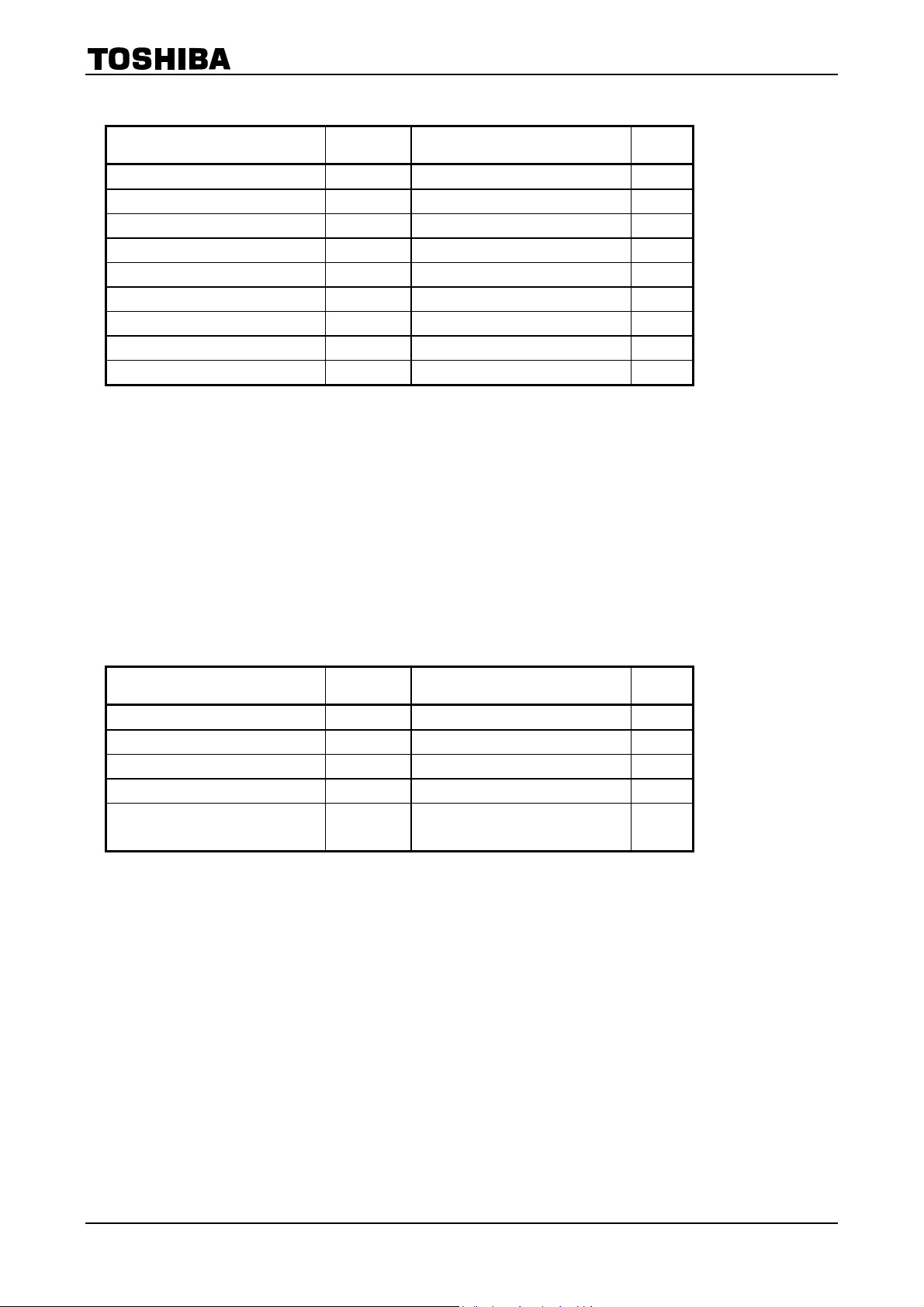

Absolute Maximum Ratings (Note 1)

Characteristics Symbol Rating Unit

Supply voltage range VCC −0.5 to 7.0 V

DC input voltage VIN −0.5 to VCC + 0.5 V

DC output voltage V

Input diode current IIK ±20 mA

Output diode current IOK ±50 mA

DC output current I

DC VCC/ground current ICC ±100 mA

Power dissipation PD 500 (DIP) (Note 2)/180 (SOP) mW

Storage temperature T

Note 1: Exceeding any of the absolute maximum ratings, even briefly, lead to deterioration in IC performance or

even destruction.

Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the

significant change in temperature, etc.) may cause this product to decrease in the reliability significantly

even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute

maximum ratings and the operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook

(“Handling Precautions”/Derating Concept and Methods) and individual reliability data (i.e. reliability test

report and estimated failure rate, etc).

−0.5 to VCC + 0.5 V

OUT

±50 mA

OUT

−65 to 150 °C

stg

Note 2: 500 mW in the range of Ta = −40 to 65°C. From Ta = 65 to 85°C a derating factor of −10 mW/°C should be

applied up to 300 mW.

Operating Ranges (Note)

Characteristics Symbol Rating Unit

Supply voltage VCC 2.0 to 5.5 V

Input voltage VIN 0 to V

Output voltage V

Operating temperature T

Input rise and fall time dt/dV

0 to V

OUT

opr

0 to 100 (V

0 to 20 (V

CC

CC

−40 to 85 °C

= 3.3 ± 0.3 V)

CC

= 5 ± 0.5 V)

CC

Note: The operating ranges must be maintained to ensure the normal operation of the device.

Unused inputs must be tied to either VCC or GND.

V

V

ns/V

3

2007-10-01

Loading...

Loading...