TOSHIBA Field Effect Transistor Silicon N Channel MOS Type

SSM3K7002FU

High Speed Switching Applications

SSM3K7002FU

Analog Switch Applications

• Small package

• Low ON resistance : R

: R

: Ron = 3.0 Ω (max) (@VGS = 10 V)

Absolute Maximum Ratings

Characteristics Symbol Rating Unit

Drain-Source voltage V

Gate-Source voltage V

Drain current

Drain power dissipation (Ta = 25°C) PD (Note 1) 150 mW

Channel temperature Tch 150 °C

Storage temperature range T

Note: Using continuously under heavy loads (e.g. the application of

high temperature/current/voltage and the significant change in

temperature, etc.) may cause this product to decrease in the

reliability significantly even if the operating conditions (i.e.

operating temperature/current/voltage, etc.) are within the

absolute maximum ratings.

Please design the appropriate reliability upon reviewing the

Toshiba Semiconductor Reliability Handbook (“Handling

Precautions”/“Derating Concept and Methods”) and individual

reliability data (i.e. reliability test report and estimated failure

rate, etc).

Note 1: mounted on FR4 board

(25.4 mm × 25.4 mm × 1.6 t, Cu Pad: 0.6mm

= 3.3 Ω (max) (@VGS = 4.5 V)

on

= 3.2 Ω (max) (@VGS = 5 V)

on

(Ta = 25°C)

DS

± 20 V

GSS

DC ID 200

Pulse I

800

DP

−55~150 °C

stg

60 V

mA

2

× 3)

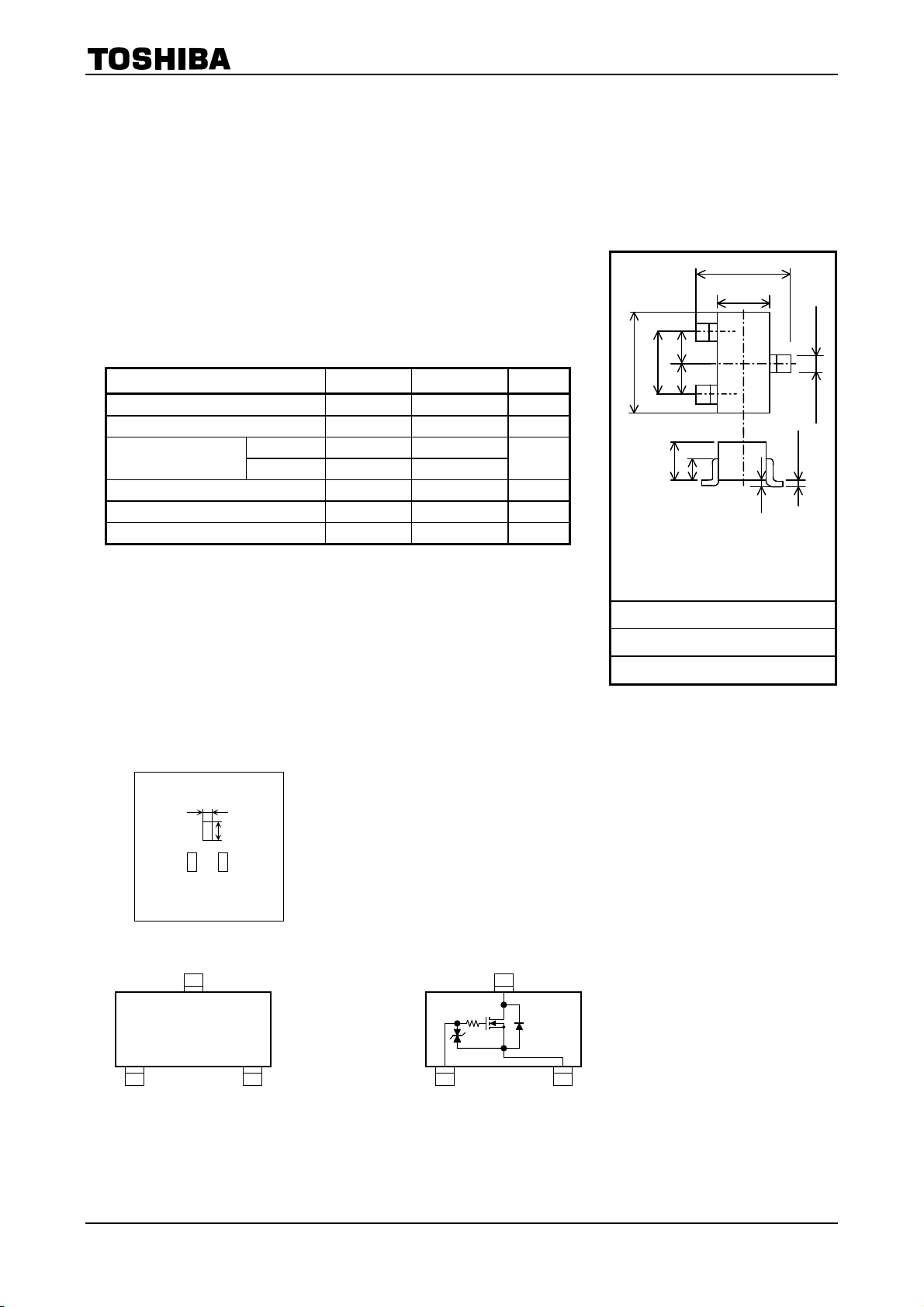

Unit: mm

2.1± 0.1

1.25 ± 0.1

+0.1

1

0.65

2.0 ± 0.2

1.3 ± 0.1

USM

JEDEC ⎯

JEITA SC-70

TOSHIBA 2-2E1E

2

0.65

0.7

0.9 ± 0.1

0~0.1

1. GATE

2. SOURCE

3. DRAIN

0.3 - 0

3

+0.1

0.15 -0.05

0.6 mm

1.0 mm

Marking Equivalent Circuit

3

1 2

NC

12

3

(top view)

Handling Precaution

When handling individual devices (which are not yet mounting on a circuit board), be sure that the environment is

protected against electrostatic electricity. Operators should wear anti-static clothing, and containers and other objects

that come into direct contact with devices should be made of anti-static materials.

1

2007-11-01

SSM3K7002FU

<

)

Electrical Characteristics

Characteristics Symbol Test Condition Min Typ Max Unit

Gate leakage current I

Drain-Source breakdown voltage V

Drain cut-off current I

Gate threshold voltage Vth VDS = 10 V, ID = 0.25 mA 1.0 ⎯ 2.5 V

Forward transfer admittance ⎪Yfs⎪ V

Drain-Source ON resistance R

Input capacitance C

Reverse transfer capacitance C

Output capacitance C

Switching time

Turn-on delay time td

Turn-off delay time td

(Ta = 25°C)

VGS = ± 20 V, VDS = 0 ⎯ ⎯ ± 10 μA

GSS

(BR) DSSID

DSS

DS (ON)

⎯ 17 ⎯ pF

iss

⎯ 1.4 ⎯ pF

rss

oss

(on)

(off)

= 0.1 mA, VGS = 0 60 ⎯ ⎯ V

VDS = 60 V, VGS = 0 ⎯ ⎯ 1 μA

= 10 V, ID = 200 mA 170 ⎯ ⎯ mS

DS

ID = 500 mA, VGS = 10 V ⎯ 2.0 3.0

ID = 100 mA, VGS = 5 V ⎯ 2.1 3.2

= 100 mA, VGS = 4.5 V ⎯ 2.2 3.3

I

D

V

= 25 V, VGS = 0, f = 1 MHz

DS

⎯ 2.4 4.0

= 30V, ID = 200 mA,

V

DD

= 0 ~ 10V

V

GS

⎯ 5.8 ⎯ pF

⎯ 26 40

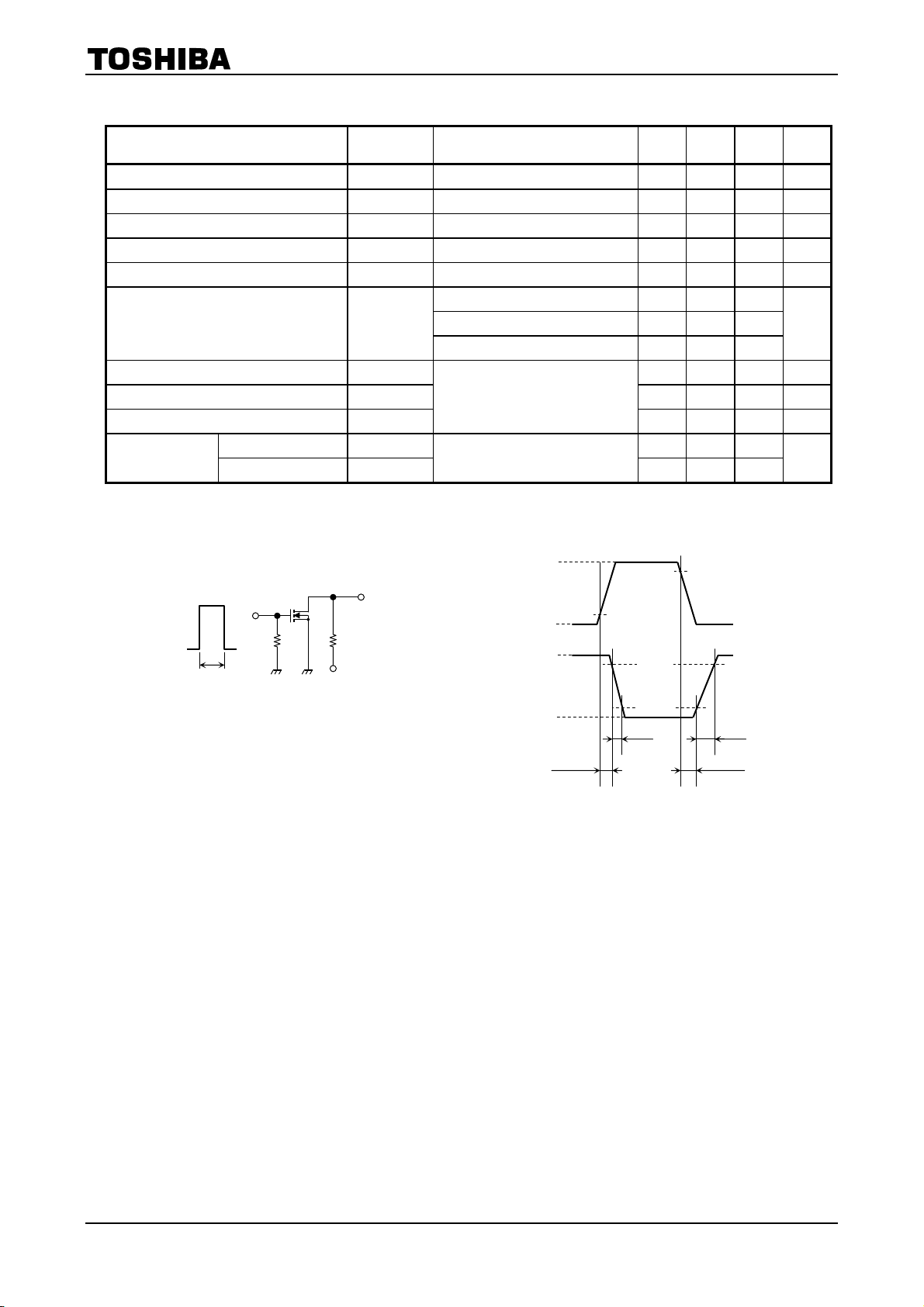

Switching Time Test Circuit

(a) Test circuit

10V

IN

0

10 μs

VDD = 30 V

1%

Duty

=

: tr, tf < 2 ns

V

IN

(Z

= 50 Ω)

out

Common Source

Ta = 25°C

(b) V

OUT

IN

50 Ω

RL

V

DD

(c) V

OUT

V

V

DS (ON

10 V

0 V

DD

90%

10%

td

(on)

t

r

10%

90%

t

f

td

(off)

Precaution

Ω

ns

Vth can be expressed as voltage between gate and source when low operating current value is ID = 250 μA for this

product. For normal switching operation, V

than V

. (Relationship can be established as follows: V

th

requires higher voltage than Vth and V

GS (on)

< Vth < V

GS (off)

GS (on)

requires lower voltage

GS (off)

)

Please take this into consideration for using the device.

2

2007-11-01

Loading...

Loading...