Page 1

SERVICE MANUAL

DVD VIDEO PLAYER

SD-1300A

FILE NO. 810-200105

SD-1300H

SD-1300T

SD-1300Y

PRINTED IN JAPAN, Jun., 2001

S

Page 2

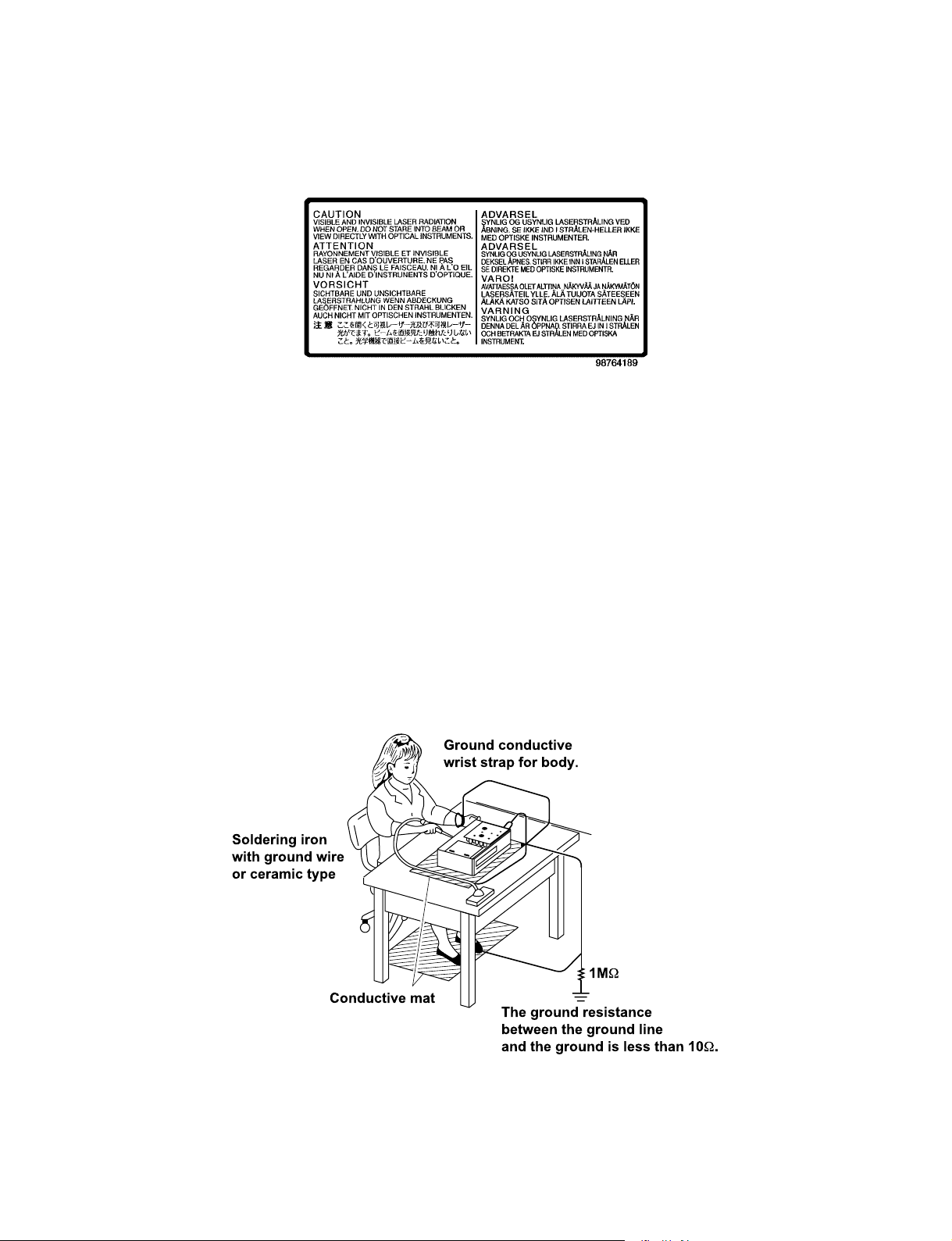

LASER BEAM CAUTION LABEL

When the power supply is being turned on, you may not remove this laser cautions label. If it removes, radiation of a laser

may be recceived.

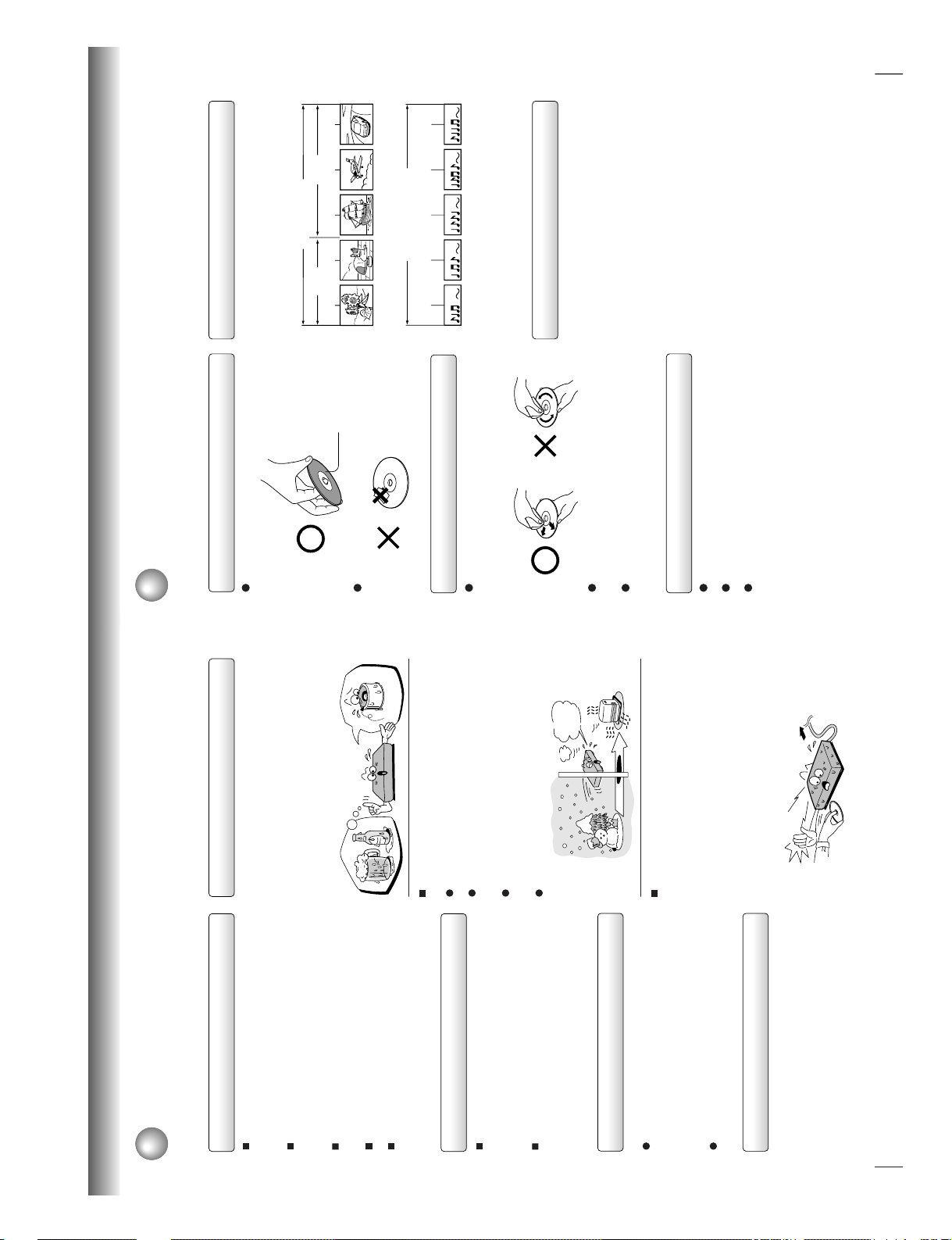

PREPARATION OF SERVICING

Pickup Head consists of a laser diode that is very susceptible to external static electricity.

Although it operates properly after replacement, if it was subject to electrostatic discharge during replacement,

its life might be shortened. When replacing, use a conductive mat, soldering iron with ground wire, etc. to

protect the laser diode from damage by static electricity.

And also, the LSI and IC are same as above.

Ground conductive

wrist strap for body.

Soldering iron

with ground wire

or ceramic type

1M

W

Conductive mat

The ground resistance

between the ground line

and the ground is less than 10W.

Page 3

CONTENTS

GENERAL DESCRIPTIONS

1. OPERATING INSTRUCTIONS................................................ 1- 1

2. LOCATION OF MAIN PARTS AND

MECHANISM PARTS ............................................................. 1-24

2-1. Location of Main Parts ..................................................... 1-24

2-2. Location of Mechanism Parts .......................................... 1-25

SECTION 1

3. TROUBLESHOOTING ............................................................ 1-29

3-1. Main Circuit....................................................................... 1-29

3-1-1. Servo System.................................................................. 1-29

3-1-2. Location Diagram of Servo Test Point........................ 1-36

PART REPLACEMENT AND ADJUSTMENT PROCEDURES

1. REPLACEMENT OF MECHANICAL PARTS ...................... 2-1

1-1. Cabinet Replacement .......................................................... 2-1

1-1-1. Top Cover ........................................................................ 2-1

1-1-2. Clamper Stay ................................................................... 2-1

1-1-3. Tray Panel ....................................................................... 2-2

1-1-4. Front Panel and Tray ..................................................... 2-3

1-1-5. Rear Panel........................................................................ 2-3

1-2. PC Board Replacement....................................................... 2-4

1-2-1. Main PC Board ............................................................... 2-4

1-2-2. Power PC board .............................................................. 2-4

1-2-3. Front PC Board............................................................... 2-5

SERVICING DIAGRAMS

1. STANDING PC BOARDS FOR SERVICING .........................3-1

2. CIRCUIT SYMBOLS AND

SUPPLEMENTARY EXPLANATION..................................... 3- 2

2-1. Precautions for Part Replacement..................................... 3-2

2-2. Solid Resistor Indication..................................................... 3-2

2-3. Capacitance Indication ....................................................... 3-2

2-4. Inductor Indication ............................................................. 3-3

2-5. Waveform and Voltage Measurement .............................. 3-3

2-6. Others ...................................................................................3-3

3. PRINTED WIRING BOARD AND

SCHEMATIC DIAGRAM.......................................................... 3-4

4. BLOCK DIAGRAMS.................................................................. 3-5

4-1. Overall Block Diagram ....................................................... 3-5

4-2. Power Supply Block Diagram ............................................ 3-7

4-3. Front Display, Power Switch Block Diagram................... 3-8

4-4. Main Block Diagrams ....................................................... 3-11

SECTION 2

1-3. Mechanism Parts ................................................................. 2-5

1-3-1. Mechanism Chassis Assembly........................................ 2-5

1-3-2. Loading Belt .................................................................... 2-6

1-3-3. Loading Motor ................................................................ 2-6

1-3-4. Sub Chassis (with a pickup mechanism) ....................... 2-7

1-3-5. Pickup Mechanism Assembly......................................... 2-7

1-3-6. Gear A Assembly, Gear B and

Rack Gear Assembly....................................................... 2-8

1-3-7. Feed Motor ...................................................................... 2-9

SECTION 3

5. CIRCUIT DIAGRAMS............................................................. 3-15

5-1. Power Supply Circuit Diagram........................................ 3-15

5-2. Front Display, Power Switch Circuit Diagram .............. 3-18

5-3. Main Circuit Diagram ...................................................... 3-21

5-4. Motor System Circuit Diagrams ...................................... 3-34

6. PC BOARDS .............................................................................. 3-35

6-1. Power Supply PC Board ................................................... 3-35

6-2. Power Switch PC Board ................................................... 3-36

6-3. Front Display PC Board ................................................... 3-37

6-4. Main PC Board.................................................................. 3-39

SAFETY PRECAUTION ................................................................. 4 -1

NOTICE ............................................................................................. 4-1

ABBREVIATIONS ........................................................................... 4-1

1. Integrated Circuit (IC) ............................................................ 4-1

2. Capacitor (Cap) ....................................................................... 4-1

3. Resistor (Res) ........................................................................... 4-1

SECTION 4

PARTS LIST

4. EXPLODED VIEWS................................................................... 4-2

4-1. Packing Assembly................................................................ 4-2

4-2. Chassis Assembly ................................................................ 4-3

4-3. Mechanism Assembly.......................................................... 4-4

5. PARTS LIST ................................................................................ 4-6

Page 4

This page is not printed.

Page 5

2

Introduction

WARNING: TO REDUCE THE RISK OF FIRE OR ELECTRIC SHOCK, DO NOT EXPOSE THIS APPLIANCE

TO RAIN OR MOISTURE. DANGEROUS HIGH VOLTAGES ARE PRESENT INSIDE THE

ENCLOSURE. DO NOT OPEN THE CABINET . REFER SERVICING TO QUALIFIED PERSONNEL

ONLY.

CAUTION: This Digital Video Disc Plzayer employs a Laser System.

To ensure proper use of this product, please read this owner’s manual carefully and retain for

future reference. Should the unit require maintenance, contact an authorized service location -

see service procedure.

Use of controls or adjustments or performance of procedures other than those specified herein

may result in hazardous radiation exposure.

To prevent direct exposure to laser beam, do not try to open the enclosure.

Visible and invisible laser radiation when open and interlocks defeated.

DO NOT STARE INTO BEAM.

In the spaces provided below, record the Model and Serial No. located on the rear panel of your DVD video

player.

Model No. Serial No.

Retain this information for future reference.

The lightning flash with arrowhead symbol, within an equilat-

eral triangle, is intended to alert the user to the presence of

uninsulated “dangerous voltage” within the product’s enclo-

sure that may be of sufficient magnitude to constitute a risk

of electric shock to persons.

The exclamation point within an equilateral triangle is in-

tended to alert the user to the presence of important operat-

ing and maintenance (servicing) instructions in the literature

accompanying the appliance.

WARNING

RISK OF ELECTRIC SHOCK

DO NOT OPEN

AVIS

RISQUE DE CHOC ELECTRIQUE NE

PAS OUVRIR

WARNING : TO REDUCE THE RISK OF

ELECTRIC SHOCK, DO NOT REMOVE

COVER (OR BACK). NO USERSERVICEABLE

PARTS INSIDE. REFER SERVICING TO

QUALIFIED SERVICE PERSONNEL.

SAFETY PRECAUTIONS

CLASS1 LASER PRODUCT

3

Introduction

Location of the required label

WARNING

TO REDUCE THE RISK OF

ELECTRIC SHOCK.

DO NOT REMOVE COVER.

REFER SERVICING TO QUALIFIED

SERVICE PERSONNEL.

TOS

H

IBA

CORPORATION

SECTION 1

GENERAL DESCRIPTIONS

GENERAL DESCRIPTIONS

1. OPERATING INSTRUCTIONS (SD-1300A/H)

SECTION 1

1-1

Page 6

4

Introduction

IMPORTANT SAFETY INSTRUCTIONS

CAUTION: PLEASE READ AND OBSERVE ALL WARNINGS AND INSTRUCTIONS GIVEN IN THIS

OWNER’S MANUAL AND THOSE MARKED ON THE UNIT. RETAIN THIS BOOKLET FOR

FUTURE REFERENCE.

This set has been designed and manufactured to assure personal safety. Improper use can result in electric

shock or fire hazard. The safeguards incorporated in this unit will protect you if you observe the following

procedures for installation, use and servicing. This unit is fully transistorized and does not contain any parts that

can be repaired by the user.

DO NOT REMOVE THE CABINET COVER, OR YOU MA Y BE EXPOSED TO DANGEROUS VOL T AGE.

REFER SERVICING TO QUALIFIED SERVICE PERSONNEL ONLY .

1. Read these instructions.

2. Keep these instructions.

3. Heed all warnings.

4. Follow all instructions.

5. Do not use this apparatus near water.

6. Clean only with dry cloth.

5

Introduction

7. Do not block any ventilation openings. Install in accordance with the

manufacturer’s instructions.

8. Do not install near any heat sources such as radiators, heat registers, stoves,

or other apparatus (including amplifiers) that produce heat.

9. Protect the power cord from being walked on or pinched particularly at plugs,

convenience receptacles, and the point where they exit from the apparatus.

10. Only use attachments/accessories specified by the manufacturer.

S3125A

11.Use only with the car t, stand, tripod, bracket, or table specified by the

manufacturer, or sold with the apparatus. When a cart is used, use caution

when moving the cart/apparatus combination to avoid injury from tip-over.

1-2

Page 7

6

Introduction

IMPORTANT SAFETY INSTRUCTIONS

12.Unplug this apparatus during lightning storms or when unused for long periods

of time.

13.Refer all servicing to qualified service personnel. Servicing is required when

the apparatus has been damaged in any way, such as power-supply cord or

plug is damaged, liquid has been spilled or objects have fallen into the

apparatus, the apparatus has been exposed to rain or moisture, does not

operate normally, or has been dropped.

14.When you use headphones, keep the volume at a moderate level. If you use

the headphones continuously with high volume sound, it may cause hearing

damage.

15.Do not overload wall outlets; extension cords, or integral convenience

receptacles as this can result in a risk of fire or electric shock.

16.Nev er insert objects of any kind into this apparatus through openings as they

may touch dangerous voltage points or short-out parts that could result in a

fire or electric shock. Never spill liquid of any kind on the apparatus.

7

Introduction

17. Keep your fingers well clear of the disc tray as it is closing. Neglecting to do

so may cause serious personal injury.

18.Do not place a heavy object on or step on the apparatus. The object may f all,

causing serious personal injury and serious damage to the apparatus.

19. Do not use a cracked, deformed, or repaired disc. These discs are easily

broken and may cause serious personal injury and apparatus malfunction.

1-3

Page 8

8

Introduction

Precautions

Notes on handling

When shipping the DVD video player, the original

shipping carton and packing materials come in handy.

For maximum protection, repack the unit as it was

originally packed at the factory.

Do not use volatile liquids, such as insect spray, near

the DVD video player. Do not leave rubber or plastic

products in contact with the DVD video player for a

long time. They will leave marks on the finish.

The top and rear panels of the DVD video player may

become warm after a long period of use. This is not a

malfunction.

When the DVD video player is not in use, be sure to

remove the disc and turn off the power.

If you do not use the DVD video player for a long

period, the unit may not function properly in the

future. Turn on and use the DVD video player

occasionally.

Notes on locating

Place the DVD video player on a level surface. Do not

use it on a shaky or unstable surface such as a

wobbling table or inclined stand. The loaded disc may

come off the proper position and cause damage to

the DVD video player.

When you place this DVD video player near a TV,

radio, or VTR, the playback picture may become poor

and the sound may be distorted. In this case, place

the DVD video player away from the TV, radio, or

VTR.

Notes on cleaning

Use a soft, dry cloth for cleaning.

For stubborn dirt, soak the cloth in a weak detergent

solution, wring well and wipe. Use a dry cloth to wipe

it dry.

Do not use any type of solvent, such as thinner and

benzine, as they may damage the surface of the DVD

video player.

If you use a chemical saturated cloth to clean the unit,

follow that product’s instructions.

To obtain a clear picture

The DVD video player is a high technology, precision

device. If the optical pick-up lens and disc drive parts

are dirty or worn down, the picture quality becomes

poor. To obtain a clear picture, we recommend regular

inspection and maintenance (cleaning or parts

replacement) every 1,000 hours of use depending on

the operating environment. For details, contact your

nearest dealer.

Notes on moisture condensation

Moisture condensation damages the DVD video

player. Please read the following carefully.

Moisture condensation occurs, for example, when you

pour a cold drink into a glass on a warm day. Drops of

water form on the outside of the glass. In the same way,

moisture may condense on the optical pick-up lens

inside this unit, one of the most crucial internal parts of

the DVD video player.

Moisture condensation occurs during the

following cases.

When you bring the DVD video player directly from a

cold place to a warm place.

When you use the DVD video player in a room where

you just turned on the heater, or a place where the

cold wind from the air conditioner directly hits the unit.

In summer, when you use the DVD video player in a

hot and humid place just after you move the unit from

an air conditioned room.

When you use the DVD video player in a humid place.

Do not use the DVD video player when moisture

condensation may occur.

If you use the DVD video player in such a situation, it

may damage discs and internal parts. Remove the

disc, connect the power cord of the DVD video player

to the wall outlet, turn on the DVD video player, and

leave it for two or three hours. After two or three

hours, the DVD video player will have warmed up and

evaporated any moisture. Keep the DVD video player

connected to the wall outlet and moisture

condensation will seldom occur.

E

x

a

m

p

l

e

o

f

m

o

i

s

t

u

r

e

c

o

n

d

e

n

s

a

t

i

o

n

!

Optical pick-up

lens

It’s too

warm!

Wait!

Wall outlet

9

Introduction

Notes on Discs

On handling discs

Do not touch the playback side of the disc.

Do not attach paper or tape to discs.

On cleaning discs

Fingerprints and dust on the disc cause picture and

sound deterioration. Wipe the disc from the center

outwards with a soft cloth. Always keep the disc

clean.

If you cannot wipe off the dust with a soft cloth, wipe

the disc lightly with a slightly moistened soft cloth and

finish with a dry cloth.

Do not use any type of solvent such as thinner,

benzine, commercially available cleaners or antistatic

spray for vinyl LPs. It may damage the disc.

On storing discs

Do not store discs in a place subject to direct sunlight

or near heat sources.

Do not store discs in places subject to moisture and

dust such as a bathroom or near a humidifier.

Store discs vertically in a case. Stacking or placing

objects on discs outside of their case may cause

warping.

Playback side

DVD video disc

Title 1

Title 2

Chapter 1 Chapter 2 Chapter 1 Chapter 2 Chapter 3

Track 1 Track 2 Track 3 Track 4 Track 5

Structure of disc contents

Normally, DVD video discs are divided into titles, and

the titles are sub-divided into chapters. VIDEO CDs/

audio CDs are divided into tracks.

DVD video disc

VIDEO CD/audio CD

Each title, chapter or track is assigned a number, which

is called “title number”, “chapter number” or “track

number” respectively.

There may be discs that do not have these numbers.

Notes on copyright

It is forbidden by law to copy, broadcast, show,

broadcast on cable, play in public, and rent copyrighted

material without permission.

DVD video discs are copy protected, and any recordings

made from these discs will be distorted.

This product incorporates copyright protection

technology that is protected by method claims of certain

U.S. patents and other intellectual property rights owned

by Macrovision Corporation and other rights owners.

Use of this copyright protection technology must be

authorized by Macrovision Corporation, and is intended

for home and other limited viewing uses only unless

otherwise authorized by Macrovision Corporation.

Reverse engineering or disassembly is prohibited.

VIDEO CD/audio CD

1-4

Page 9

10

Introduction

DIGITAL VIDEO

About this owner’s manual

This owner’s manual explains the basic instructions of

this DVD video player. Some DVD video discs are

produced in a manner that allows specific or limited

operation during playback. As such, the DVD video

player may not respond to all operating commands. This

is not a defect in the DVD video player. Refer to

instruction notes of discs.

“

” may appear on the TV screen during operation.

A “

” means that the operation is not permitted by the

DVD video player or the disc.

Notes on region numbers

The DVD video player is allotted one of region numbers,

which stand for their playable area. If the numbers are

printed on your DVD video disc, and are different from

that of the DVD video player, disc playback will not be

allowed by the player. (In this case, the DVD video player

displays the message.)

The region number of this DVD video player is printed

on the rear panel of the main unit and on the carton.

On VIDEO CDs

This DVD video player supports VIDEO CDs equipped

with the PBC (Version 2.0) function. (PBC is the

abbreviation of Playback Control.) You can enjoy two

playback variations depending on types of discs.

• VIDEO CD not equipped with PBC function

(Version 1.1)

Sound and movie can be played on this DVD video

player in the same way as an audio CD.

• VIDEO CD equipped with PBC function

(Version 2.0)

In addition to operation of a VIDEO CD not equipped

with the PBC function, you can enjoy playback of

interactive software with search function by using the

menu displayed on the TV screen (Menu Playback).

Some of the functions described in this owner’s

manual may not work with some discs.

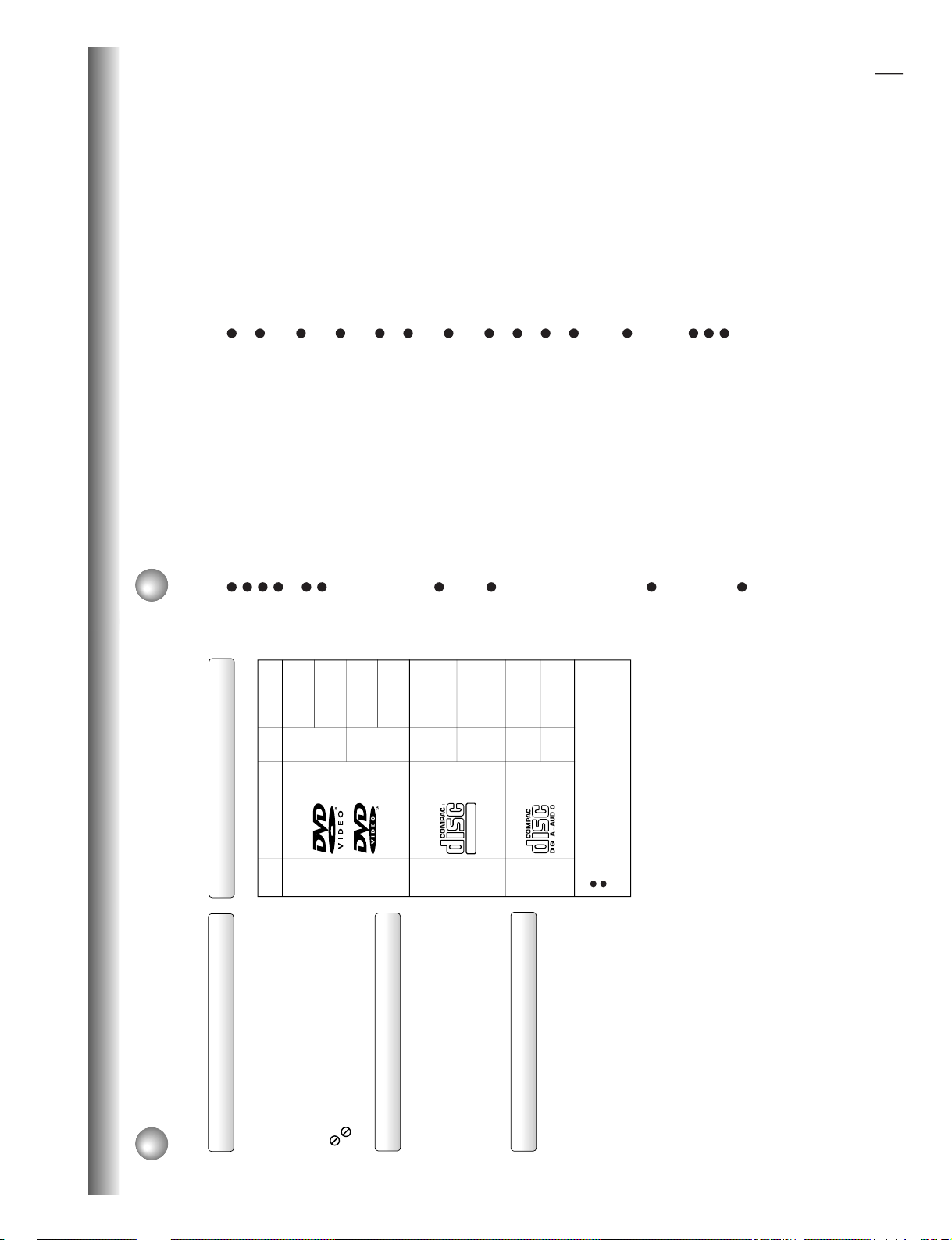

Playable discs

This DVD video player can play the following discs.

• You cannot play discs other than those listed above.

• You cannot play discs of DVD-RAM, DVD-RW, etc.,

even if they may be labeled marks listed above.

• This DVD video player uses the NTSC/PAL color

system, and cannot play DVD video discs recorded in

any other color system (SECAM, etc.).

Notes on Discs (continued)

DVD

video

discs

Disc Mark

Contents

Disc

Size

Maximum

playback time

VIDEO

CDs

Approx. 4 hours

(single sided disc)

Approx. 8 hours

(double sided disc)

Approx. 80 minutes

(single sided disc)

Approx. 160 minutes

(double sided disc)

Approx. 74 minutes

Approx. 20 minutes

8 cm

12 cm

8 cm

12 cm

Audio

+

video

(moving

pictures)

Audio

+

video

(moving

pictures)

Audio

CDs

Approx. 74 minutes

Approx. 20 minutes

8 cm

(CD

single)

12 cm

Audio

The following discs are also available.

CD-R

CD-RW

CD-R/RW discs recorded by CD-DA method can be

played. Some CD-R/RW discs may be incompatible.

11

Introduction

Table of Contents

Introduction

SAFETY PRECAUTIONS .......................... 2

IMPORTANT SAFETY INSTRUCTIONS ...4

Precautions ............................................... 8

Notes on Discs..........................................9

Notes on region numbers ............................... 10

Table of Contents....................................11

Identification of Controls .......................12

Front panel ..................................................... 12

Rear panel...................................................... 12

DVD display....................................................13

Remote control ............................................... 14

Loading batteries............................................ 15

Operating with the remote control .................. 15

Connections

Connecting to a TV .................................16

Connecting to a TV.........................................16

Connecting to an audio system and TV

equipped with component video inputs ........ 17

Connecting to Optional Equipment ......18

Connecting to an amplifier equipped with a

Dolby Digital decoder ................................... 18

Connecting to an amplifier equipped with

Dolby Pro Logic Surround ............................ 18

Connecting to an amplifier equipped with a

DTS decoder ................................................ 18

Connecting to an amplifier equipped with an

MPEG2 audio decoder................................. 19

Connecting to an amplifier equipped with a

digital audio input ......................................... 19

Basic playback

Playing a Disc .........................................20

Basic playback ............................................... 20

Playing in fast reverse or fast forward

directions...................................................... 22

Playing frame by frame................................... 22

Playing in slow-motion....................................23

Resuming playback from the same location...23

Locating a Specific Title, Chapter, or

Track ........................................................24

Locating a title using the top menu.................24

Locating a title by entering the title number....24

Locating a specific chapter or track directly ... 25

Locating a specific chapter or track................ 25

Advanced playback

Accessing a Specific Location Directly ...

26

Entering the time of the desired location ........ 26

Playing Repeatedly.................................27

Repeating a title, chapter, or track.................. 27

Repeating a specific segment ........................ 27

Playing in a Favorite Order ....................28

Setting titles, chapters, or tracks in a favorite

order............................................................. 28

Playing in Random Order.......................29

Playing titles, chapters or tracks in random

order............................................................. 29

Zooming a Picture ..................................30

Zooming a picture...........................................30

Selecting the Picture Enhancement

(E.P.M.) .....................................................31

Selecting the picture enhancement ................ 31

Selecting the Sound Enhancement

(E.A.M.) ....................................................32

Selecting the sound enhancement ................. 32

Selecting the Camera Angle .................. 33

Changing the camera angle ........................... 33

Selecting Subtitles .................................34

Selecting a subtitle language ......................... 34

Selecting a Language.............................35

Selecting a playback audio setting ................. 35

Operating in the On-screen Display Mode....

36

Operating in the on-screen display mode.......36

Function setup

Customizing the Function Settings ......38

Setting procedure ........................................... 38

Setting details................................................. 40

Others

Table of Languages................................46

Before Calling Service Personnel ......... 47

Specifications .........................................48

1-5

Page 10

12

Introduction

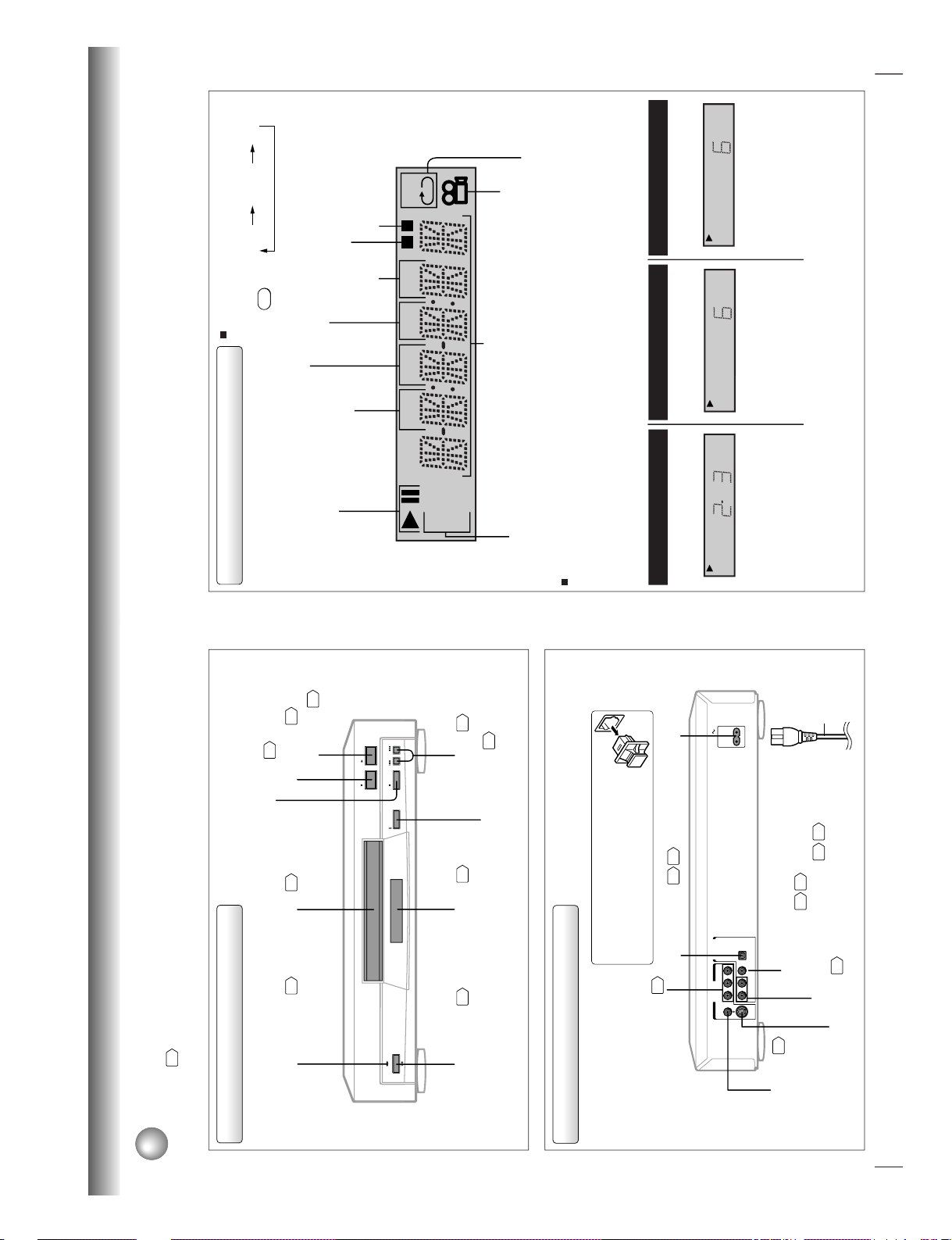

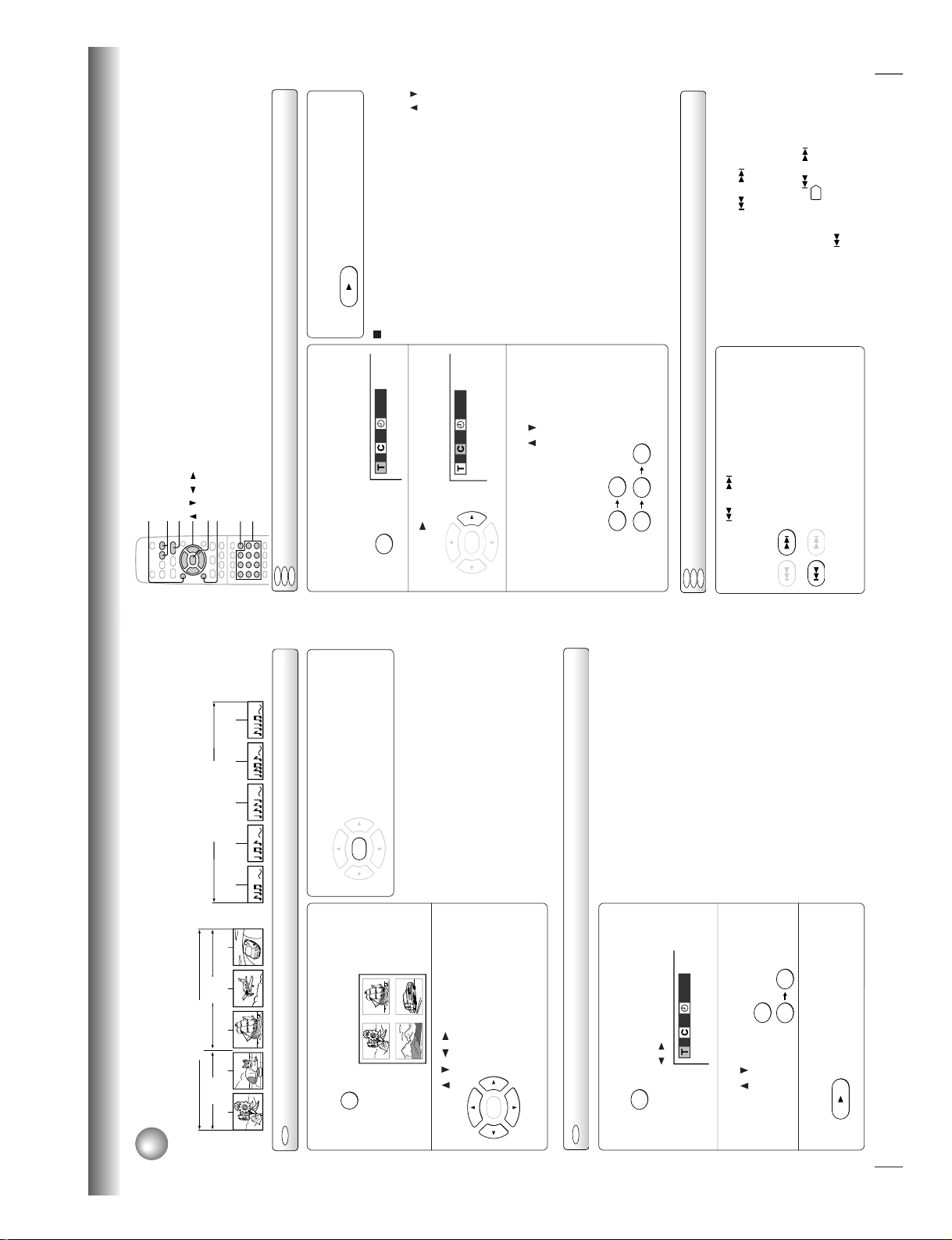

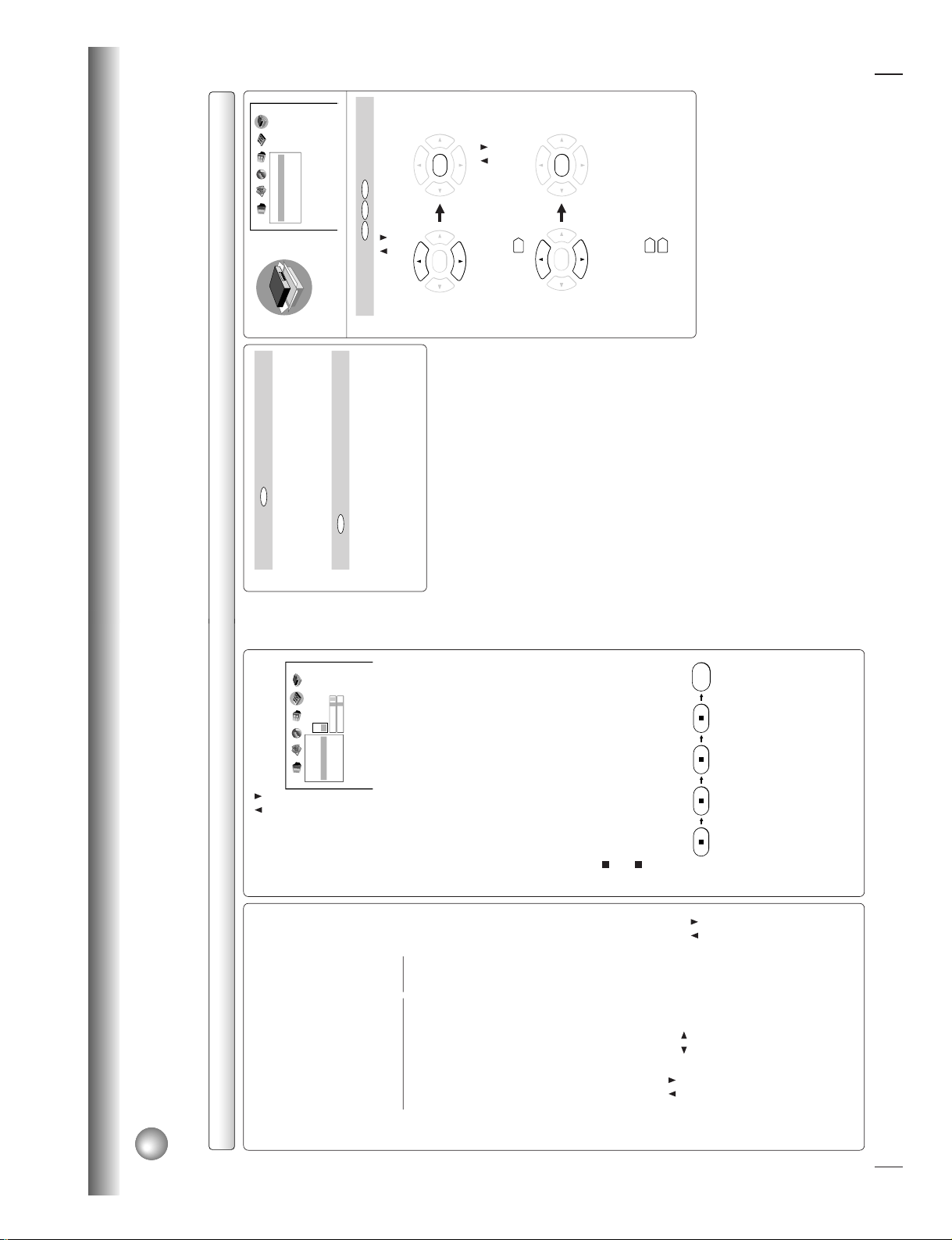

Identification of Controls

See the page in

for details.

Front panel

Rear panel

PAUSE

SKIP

OPEN/CLOSE

ON/STANDBY

PLAYSTOP

ON/STANDBY button

20

DVD display

13

OPEN/CLOSE button

20

SKIP buttons

25

STOP button

21

PLAY button

20

PAUSE button

21

ON/STANDBY indicator

20

Disc tray

20

BITSTREAM/PCM

AC IN

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B PR

S

AUDIO OUT

VIDEO OUT

AC inlet

Power cord

VIDEO OUT (Y/P

B

/P

R

)

(Component video) jacks

ANALOG AUDIO OUT (L/R) jacks

16

18

19

18 19

16

S VIDEO OUT jack

VIDEO OUT jack

17

BITSTREAM/PCM COAXIAL

AUDIO OUT jack

BITSTREAM/PCM OPTICAL

AUDIO OUT jack

16 17

When connecting the optical digital cable, remove

the cap and fit the connector into the jack firmly.

When not using the jack, keep the cap inserted

to protect it from dust intrusion.

13

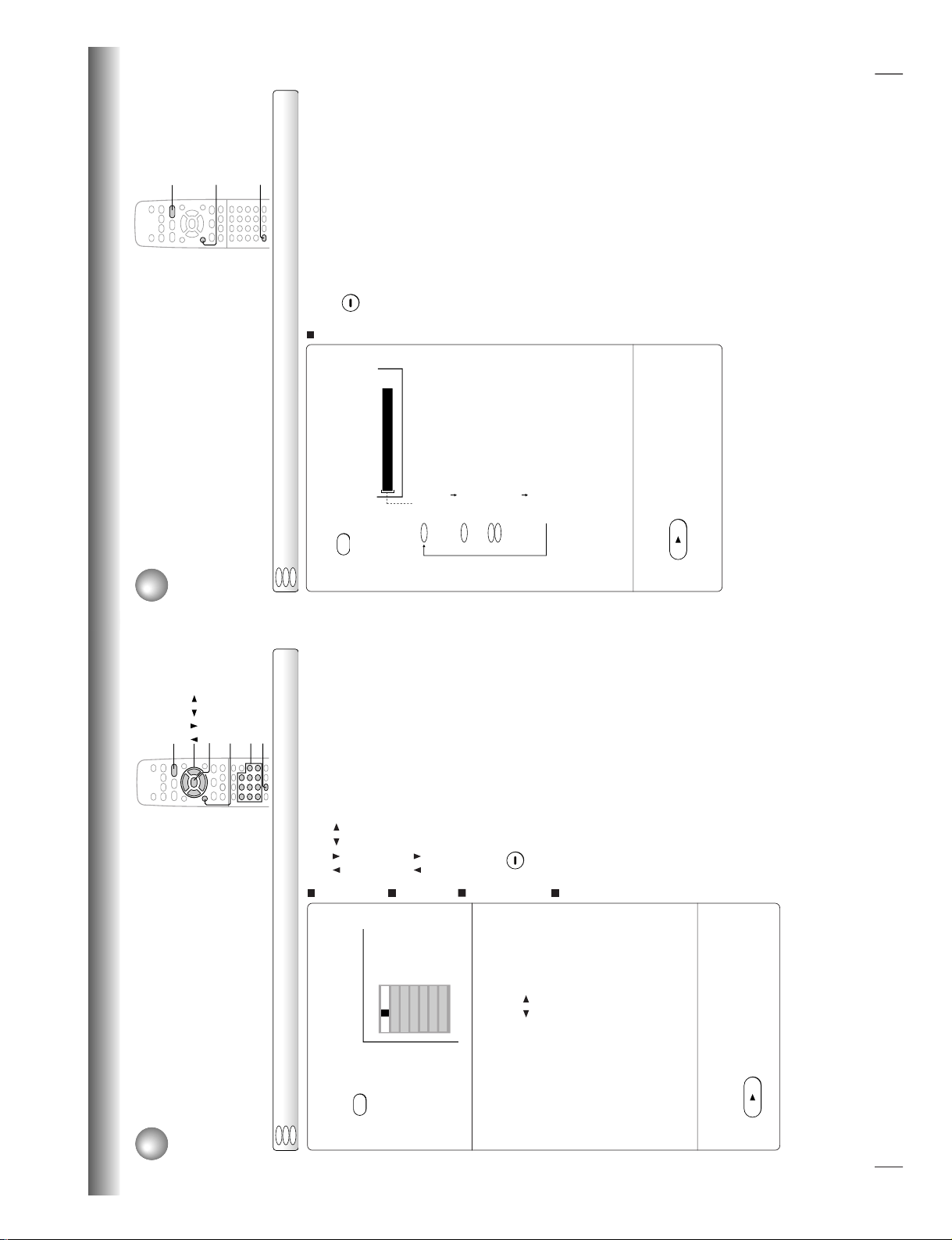

Introduction

DVD

VCD

TITLE TOTAL

CHP TRK

M A

-

BR

DVD display

Pressing of the FL DIM button on the remote

control changes the brightness of the display.

Repeat playback indicator

Angle icon indicator

Total playing time indicator

Memory playback indicator

Chapter number indicator

Title number indicator

Play mode indicator

Multifunctional indicator (indicates operating status or

messages, etc.)

Normal

Off

FL DIM

Dimmed

The indicators vary depending on the kinds of discs you play.

DVD video disc

Audio CD

Some discs may not display chapter

numbers or elapsed time.

• During playback:

Playing chapter 3 of title 2

Example

• During playback:

Example

Playing track 6

VIDEO CD

• During playback:

Example

Playing track 6

Some discs may not display track

numbers or elapsed time.

DVD

TITLE

CHP

VCD

TRK

CD

TRK

Track number

indicator

Random playback indicator

When you start playback, the elapsed time indicators appear. Pressing the FL SELECT button switches

them to the title/chapter/track number indicators. Some discs may not permit this operation.

DVD/VIDEO CD/CD indicator

1-6

Page 11

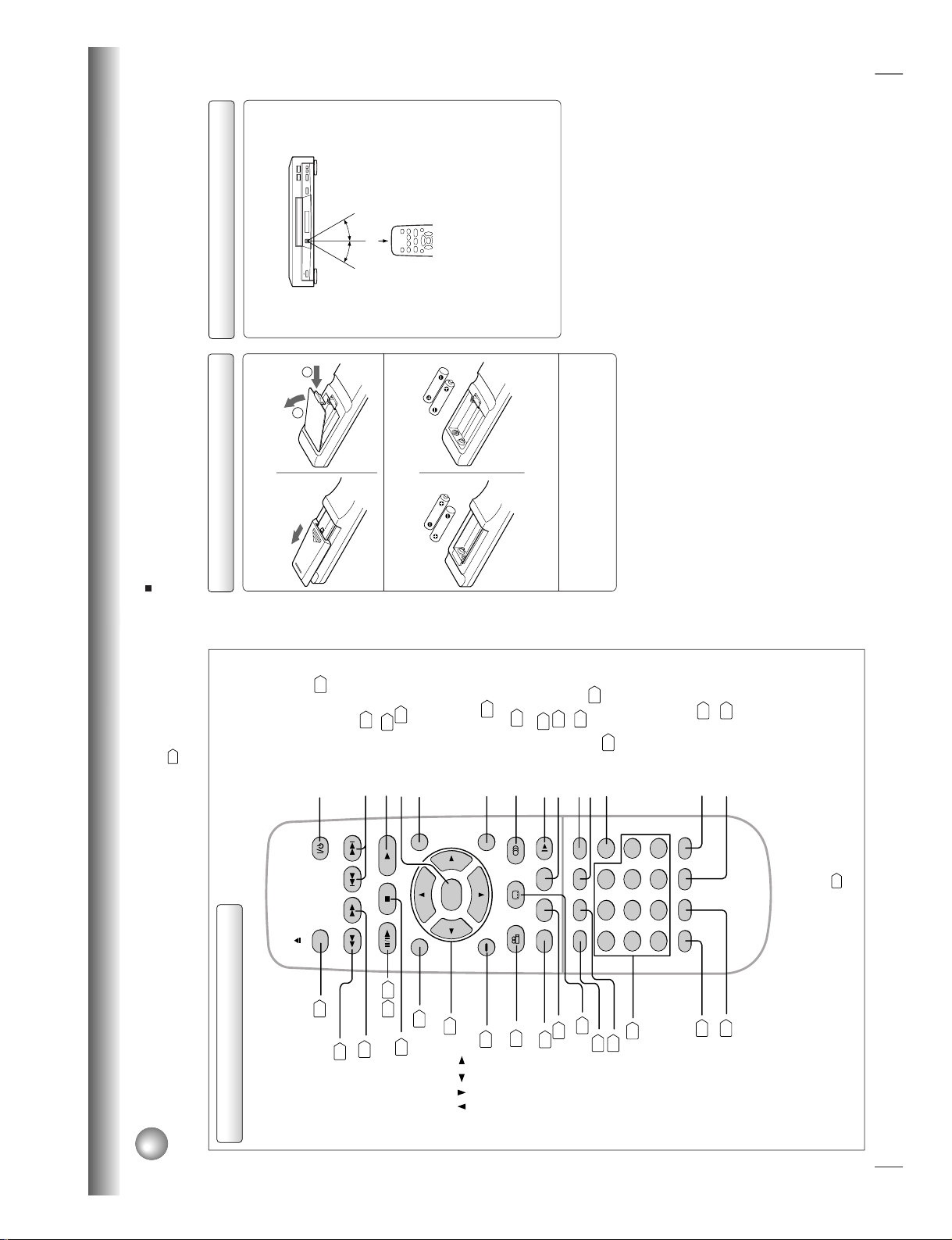

14

Introduction

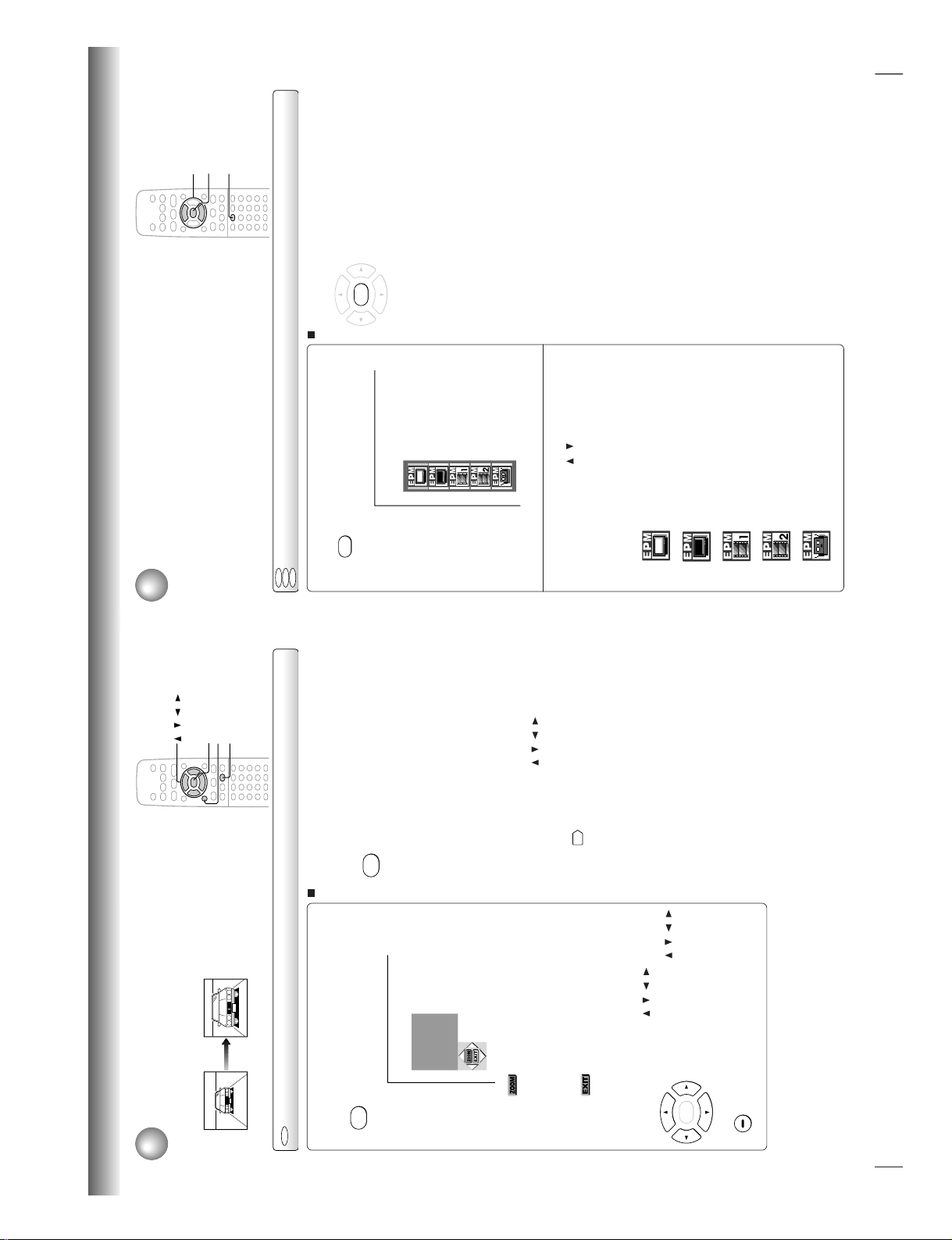

Identification of Controls (continued)

The instructions in this manual describe the functions on the remote control. See the page in

for details.

Remote control

* MENU button

Use the MENU button to display the menu included on

many DVD video discs. To operate a menu, follow the

instructions in “Locating a title using the top menu.”

24

TOP MENU

MENU

ENTER

RETURN

CLEAR

21

456

78

3

90

+10

T

RANDOM

REPEAT

A-B RPT

ANGLE SUBTITLE AUDIO

SETUP SLOWZOOMDISPLAY

MEMORY

SEARCH

SKIPREV

STOP PLAY

PAUSE/STEP

FWD

OPEN/CLOSE

FL SELECT

E.A.M. E.P.M.

FL DIM

OPEN/CLOSE button20PAUSE/STEP button

21 22

SETUP button

38

ANGLE button

33

34

SUBTITLE button

TOP MENU button

24

CLEAR button

25

REV button22FWD button

22

21

E.A.M. button

32

E.P.M. button

31

STOP button

RANDOM button

29

MEMORY button

28

MENU button*

RETURN button

38

ENTER button

38

FL DIM button

PLAY button

20

SKIP buttons

25

A-B RPT button

REPEAT button

ON/STANDBY button

20

SLOW button

23

ZOOM button

30

AUDIO button

35

Direction buttons

( / / / )

38

Number buttons

24

DISPLAY button

36

T button

24

27

27

13

FL SELECT button

13

15

Introduction

Operating with the remote control

Point the remote control at the remote

sensor and press the buttons.

Distance: About 7 m from the front of the remote

sensor

Angle: About 30° in each direction of the front of

the remote sensor

* Do not expose the remote sensor of the DVD video

player to a strong light source such as direct

sunlight or other illumination. If you do so, you may

not be able to operate the DVD video player via the

remote control.

Notes on the remote control

• Direct the remote control at the remote sensor of the DVD

video player.

• Do not drop or give the remote control a shock.

• Do not leave the remote control near an extremely hot or

humid place.

• Do not spill water or put anything wet on the remote

control.

• Do not open the remote control.

Within about 7 m

30°

30°

Open the cover.

Insert batteries (R6 size).

Make sure to match the + and – on the batteries

to the marks inside the battery compartment.

Close the cover.

Notes on batteries

Improper use of batteries may cause battery leakage and

corrosion. To operate the remote control correctly, follow the

instructions below.

• Do not insert batteries into the remote control in the wrong

direction.

• Do not charge, heat, open, or short-circuit the batteries.

Do not throw batteries into a fire.

• Do not leave dead or exhausted batteries in the remote

control.

• Do not use different types of batteries together, or mix old

and new batteries.

• If you do not use the remote control for a long period of

time, remove the batteries to avoid possible damage from

battery corrosion.

• If the remote control does not function correctly or if the

operating range becomes reduced, replace all batteries

with new ones.

• If battery leakage occurs, wipe the battery liquid from the

battery compartment, then insert new batteries.

1

2

3

Loading batteries

1

2

About the illustrations of the battery compartment

There are two types of battery compartment in the

supplied remote controls. (This does not mean a

difference in performance between the two.)

Refer to either illustration depending on the actual

remote control.

1-7

Page 12

16

Connections

BITSTREAM/PCM

AC IN

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B

P

R

S

AUDIO OUT

VIDEO OUT

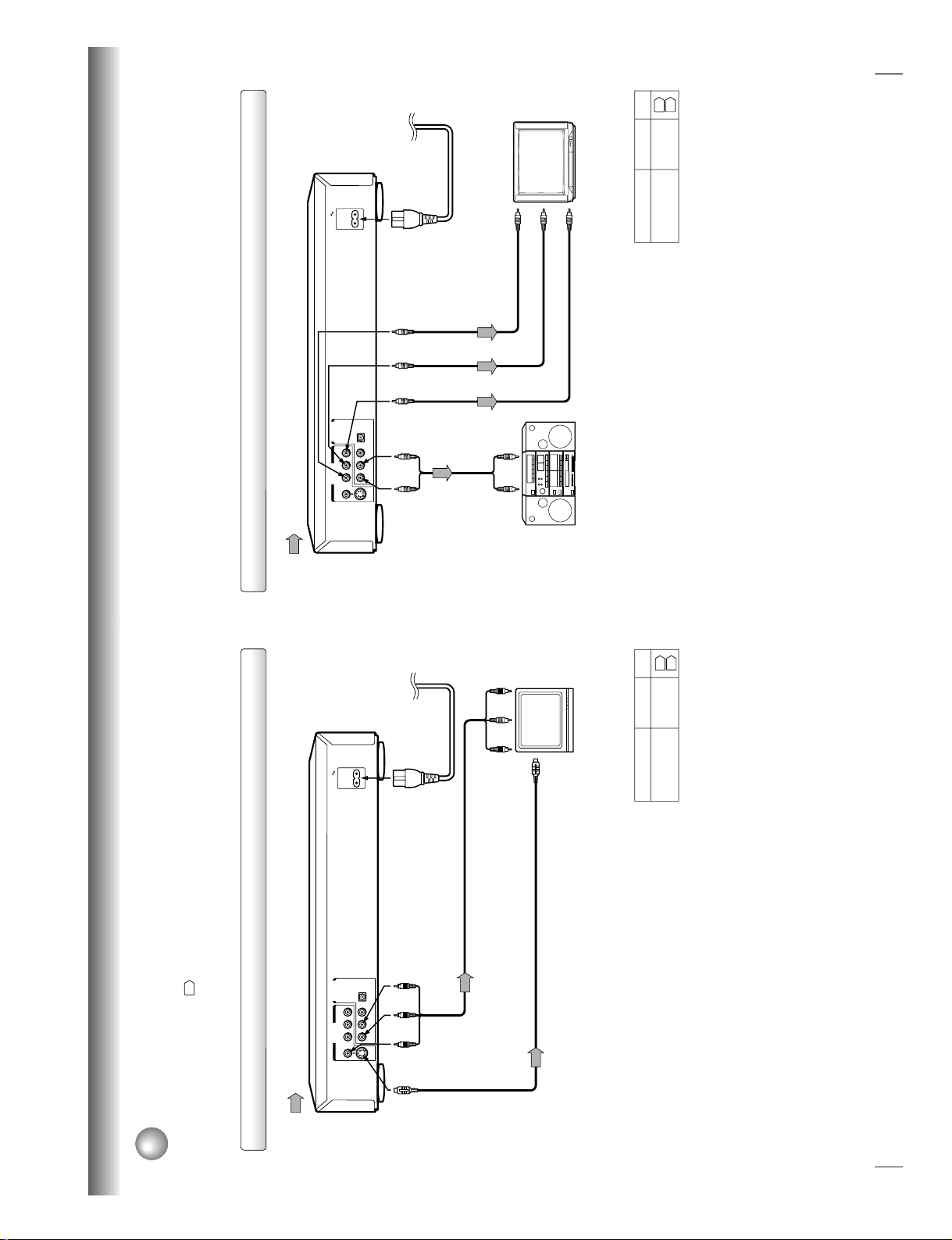

Connecting to a TV

Connect the DVD video player to your TV.

For details of output sound, see

35

.

Connecting to a TV

T o VIDEO

OUT

To ANALOG AUDIO OUT

(red) (white)

(yellow)

Signal flow

To wall outlet

To video input

(yellow)

(red)

(white)

To S video input

Audio/video cable (supplied)

S video cable (not supplied)

To audio inputs

If the TV has an S video input, connect the

DVD video player with an S video cable.

When using an S video cable, do not

connect the yellow video cable.

Notes

• Refer to the owner’s manual of the connected TV as well.

• When you connect the DVD video player to your TV, be sure to turn off the power and unplug both units from the wall outlet

before making any connections.

• If your television set has one audio input, connect the DVD video player to a Y cable adapter (not supplied) and then connect

to your TV.

• Connect the DVD video player directly to your TV. If you connect the DVD video player to a VTR, TV/VTR combination or

video selector, the playback picture may be distorted as DVD video discs are copy protected.

• Make the following setting.

On-screen display

Select:

Page

“Analog 2ch”

“Audio Out Select”

TV or monitor with

audio/video inputs

38

40

To S VIDEO

OUT

17

Connections

BITSTREAM/PCM

AC IN

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B

P

R

S

AUDIO OUT

VIDEO OUT

To PRVIDEO

OUT

Notes

• Refer to the owner’s manual of the connected equipment as well.

• When you connect the DVD video player to other equipment, be sure to turn off the power and unplug all of the equipment

from the wall outlet before making any connections.

• If you place the DVD video player near a tuner or radio, the radio broadcast sound might be distorted. In this case, place the

DVD video player away from the tuner and radio.

• The output sound of the DVD video player has a wide dynamic range. Be sure to adjust the receiver’s volume to a moderate

listening level. Otherwise, the speakers may be damaged by a sudden high volume sound.

• Turn off the amplifier before you connect or disconnect the DVD video player’s power cord. If you leave the amplifier power

on, the speakers may be damaged.

Connecting to an audio system and TV equipped with component video inputs

Signal flow

To wall outlet

To audio inputs of

the amplifier

(red)

(white)

(red) (white)

To Y

VIDEO

OUT

To P

B

VIDEO

OUT

To Y video input

To P

B

video input

To P

R

video input

TV or monitor with

component video inputs

Audio system

Component video outputs/inputs

Some TVs or monitors are equipped with component video inputs. Connecting to

these inputs allows you to enjoy higher quality picture playback.

Actual labels for component video inputs may vary depending on the TV

manufacturer. (ex. “Y, R-Y, B-Y” or “Y, C

B

, C

R

”)

In some TVs or monitors, the color levels of the playback picture may be reduced

slightly or the tint may change. In such a case, adjust the TV or monitor for

optimum performance.

• Make the following setting.

On-screen display

Select:

Page

“Analog 2ch”

“Audio Out Select”

To ANALOG AUDIO OUT

38

40

1-8

Page 13

18

Connections

BITSTREAM/PCM

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B

P

R

S

AUDIO OUT

VIDEO OUT

BITSTREAM/PCM

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B

P

R

S

AUDIO OUT

VIDEO OUT

BITSTREAM/PCM

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B PR

S

AUDIO OUT

VIDEO OUT

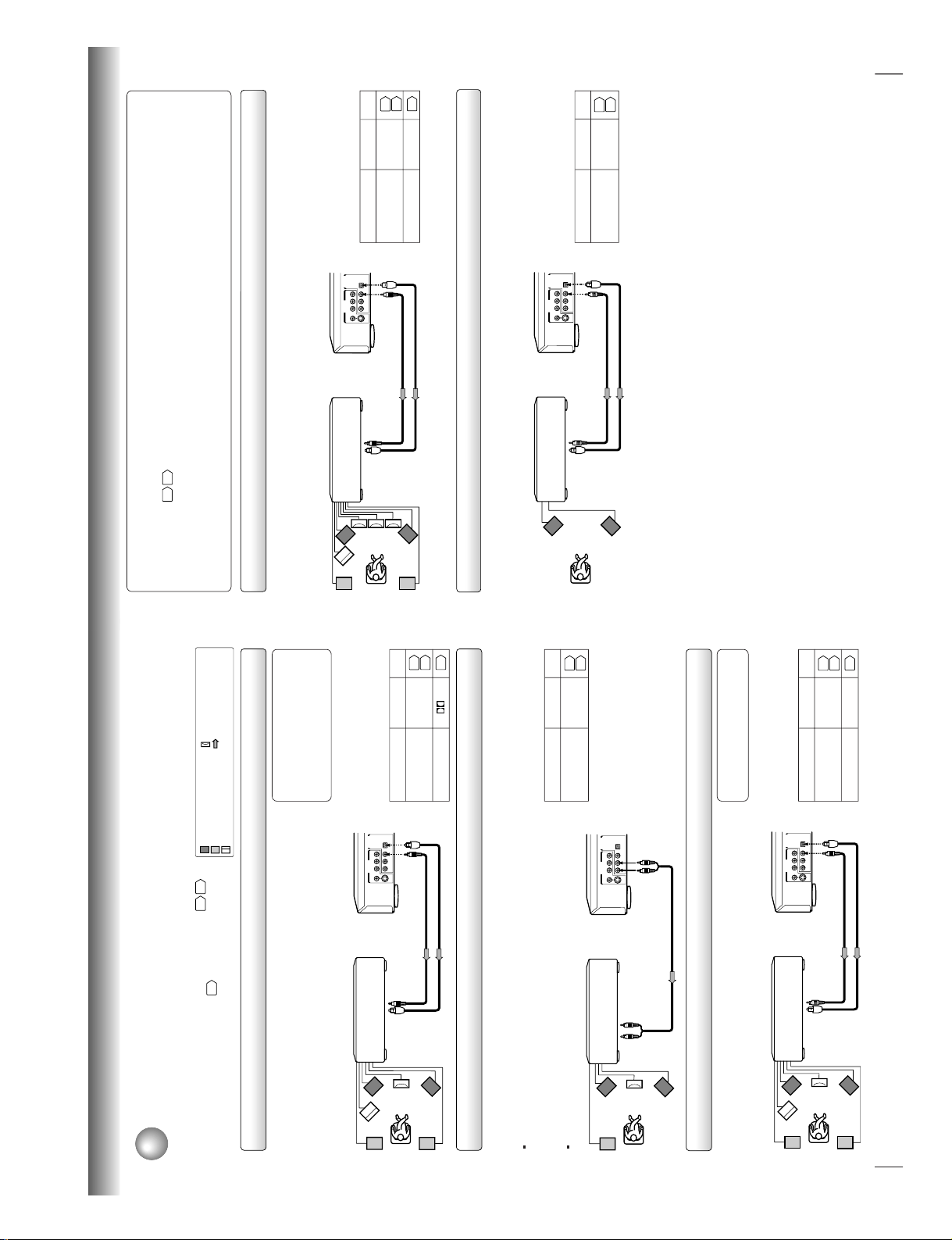

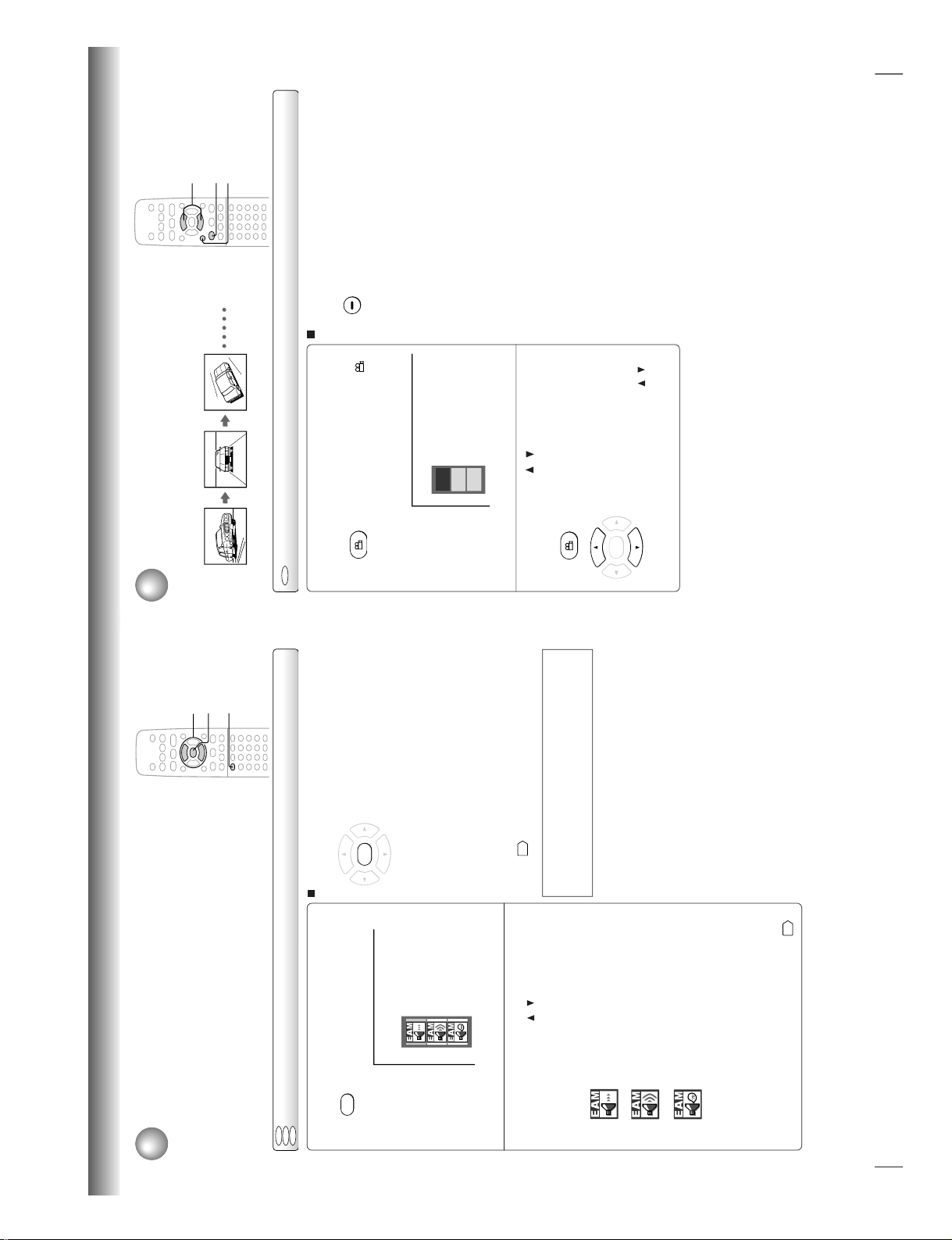

Connecting to Optional Equipment

You can enjoy high quality dynamic sounds by connecting the DVD video player

to optional audio equipment.

For connection to your TV, see “Connecting to a TV”

16

17

.

For details of output sound, see

35

.

: Front speaker

: Rear speaker

: Sub woofer

: Center speaker

: Signal flow

Connecting to an amplifier equipped with a Dolby Digital decoder

Connecting to an amplifier equipped with Dolby Pro Logic Surround

Dolby Pro Logic Surround

You can enjoy the dynamic realistic sound of Dolby Pro Logic Surround by connecting an amplifier and speaker system (right and left

front speakers, a center speaker, and one or two rear speakers).

Connecting to an amplifier equipped with a DTS decoder

Digital Theater Systems (DTS)

DTS is a high quality surround technology used in theaters and now available for home use,

on DVD video discs or audio CDs.

If you have a DTS decoder or processor, you can obtain the full benefit of 5.1 channel DTS

encoded sound tracks on DVD video discs or audio CDs.

Manufactured under license from Dolby

Laboratories. “Dolby”, “Pro Logic”, and

the double-D symbol are trademarks of

Dolby Laboratories. Confidential

unpublished works. ©1992-1997 Dolby

Laboratories. All rights reserved.

• Use DVD video discs encoded via

the Dolby Digital recording

system.

• Make the following setting.

• Use DVD video discs or audio

CDs encoded via the DTS

recording system.

• Make the following setting.

Be sure to set “Audio Out Select”

to “Analog 2ch” when you enjoy

sounds of Dolby Pro Logic

Surround using this connection.

* Connect one or two rear speakers.

The output sound from the rear speakers will be

monaural even if you connect two rear speakers.

• Make the following setting.

“DTS” and “DTS Digital Surround” are

trademarks of Digital Theater Systems,

Inc.

On-screen display Select:

Page

“Bitstream”“Audio Out Select”

Recording system

On-screen display

Select:

Page

“Bitstream”

“Audio Out Select”

Recording system DTS

On-screen display

Select:

Page

“Analog 2ch”

“Audio Out Select”

With an amplifier equipped with Dolby Digital

Connect the equipment the same way as described in “Connecting to an amplifier

equipped with a Dolby Digital decoder.” Refer to that amplifier’s owner’s manual and set

the amplifier so you can enjoy Dolby Pro Logic Surround sound.

With an amplifier not equipped with Dolby Digital

Connect the equipment as follows.

Dolby Digital

Dolby Digital is the surround sound technology used in theaters showing the latest movies,

and is now available to reproduce this realistic effect in the home. You can enjoy motion

picture and live concert DVD video discs with this dynamic realistic sound by connecting the

DVD video player to a 6 channel amplifier equipped with a Dolby Digital decoder or Dolby

Digital processor. If you have a Dolby Pro Logic Surround decoder, you will obtain the full

benefit of Pro Logic from the same DVD movies that provide full 5.1-channel Dolby Digital

soundtracks, as well as from titles with the Dolby Surround mark.

38

403538

40

38

40

35

D

Amplifier equipped with a

Dolby Digital decoder

75 Ω coaxial cable

To OPTICAL

type digital

audio input

Amplifier equipped with

Dolby Pro Logic Surround

To audio input

Audio cable

*

To ANALOG AUDIO OUT

Amplifier equipped with

a DTS decoder

Connect either.

To COAXIAL type

digital audio input

Optical digital cable

75 Ω coaxial cable

To OPTICAL

type digital

audio input

Connect either.

To COAXIAL type

digital audio input

Optical digital cable

19

Connections

BITSTREAM/PCM

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B PR

S

AUDIO OUT

VIDEO OUT

BITSTREAM/PCM

L

COAXIAL OPTICAL

ANALOG

R

VIDEO Y P

B

PR

S

AUDIO OUT

VIDEO OUT

Warning

• When you are connecting (via the BITSTREAM/PCM AUDIO OUT jack) an AV decoder that does not have the Dolby

Digital, Digital Theater Systems (DTS) or MPEG2 decoding function, be sure to set “Audio Out Select” to “PCM” from the

on-screen displays

38

40

. Otherwise, high volume sound may damage your hearing as well as the speakers.

• When playing DTS-encoded discs (DVD video discs and audio CDs), excessive noise may be output from the analog

stereo jacks. To avoid possible damage to the audio system, you should take proper precautions when the ANALOG

AUDIO OUT (L/R) jacks of the DVD video player are connected to an amplification system. To enjoy DTS Digital

Surround™ playback, an external 5.1 channel DTS Digital Surround™ decoder system must be connected to the

BITSTREAM/PCM AUDIO OUT jack of the DVD video player.

Connecting to an amplifier equipped with an MPEG2 audio decoder

MPEG2 sound

You can enjoy motion picture and live concert DVD video discs with dynamic realistic sound

by connecting an amplifier equipped with an MPEG2 audio decoder or MPEG2 audio

processor.

Connecting to an amplifier equipped with a digital audio input

2 channel digital stereo

You can enjoy the dynamic sound of 2 channel digital stereo by connecting an amplifier

equipped with a digital audio input and speaker system (right and left front speakers).

Notes

• DO NOT connect the BITSTREAM/PCM AUDIO OUT jack of the DVD video player to the AC-3 RF input of a Dolby Digital

Receiver. This input on your A/V Receiver is reserved for Laserdisc use only and is incompatible with the BITSTREAM/PCM

AUDIO OUT jack of the DVD video player.

• Connect the BITSTREAM/PCM AUDIO OUT jack of the DVD video player to the “OPTICAL” or “COAXIAL” input of a Receiver

or Processor.

• Refer to the owner’s manual of the connected equipment as well.

• When you connect the DVD video player to other equipment, be sure to turn off the power and unplug all of the equipment

from the wall outlet before making any connections.

• The output sound of the DVD video player has a wide dynamic range. Be sure to adjust the receiver’s volume to a moderate

listening level. Otherwise, the speakers may be damaged by a sudden high volume sound.

• Turn off the amplifier before you connect or disconnect the DVD video player’s power cord. If you leave the amplifier power

on, the speakers may be damaged.

• Use DVD video discs encoded via

the MPEG2 recording system.

• Make the following setting.

On-screen display

Select:

Page

“Bitstream”

“Audio Out Select”

Recording system

MPEG

• Make the following setting.

On-screen display

Select:

Page

“PCM”

“Audio Out Select”

38

403538

40

Amplifier equipped with an

MPEG2 audio decoder

Amplifier equipped with

a digital audio input

75 Ω coaxial cable

To OPTICAL

type digital

audio input

Connect either.

To COAXIAL type

digital audio input

Optical digital cable

75 Ω coaxial cable

To OPTICAL

type digital

audio input

Connect either.

To COAXIAL type

digital audio input

Optical digital cable

1-9

Page 14

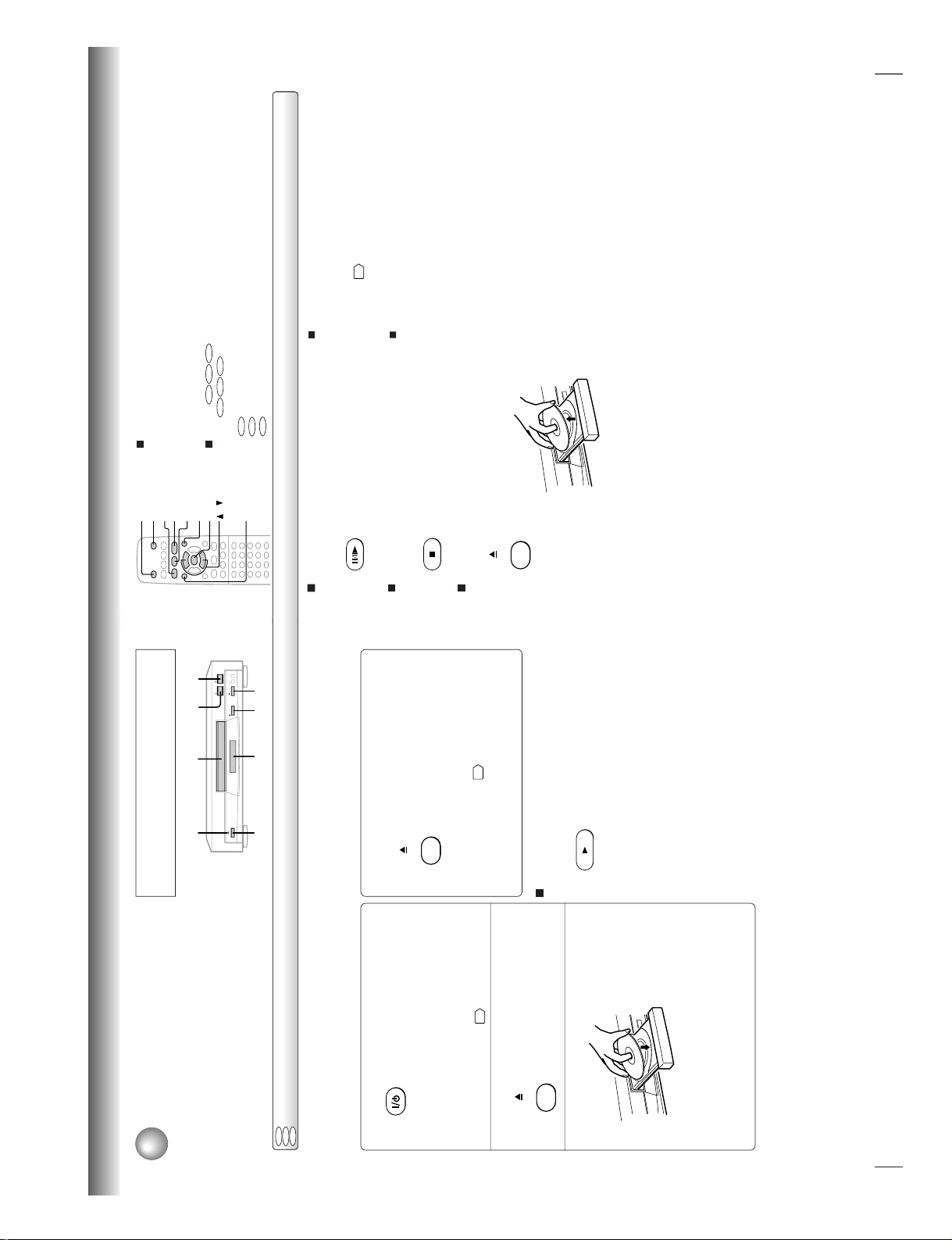

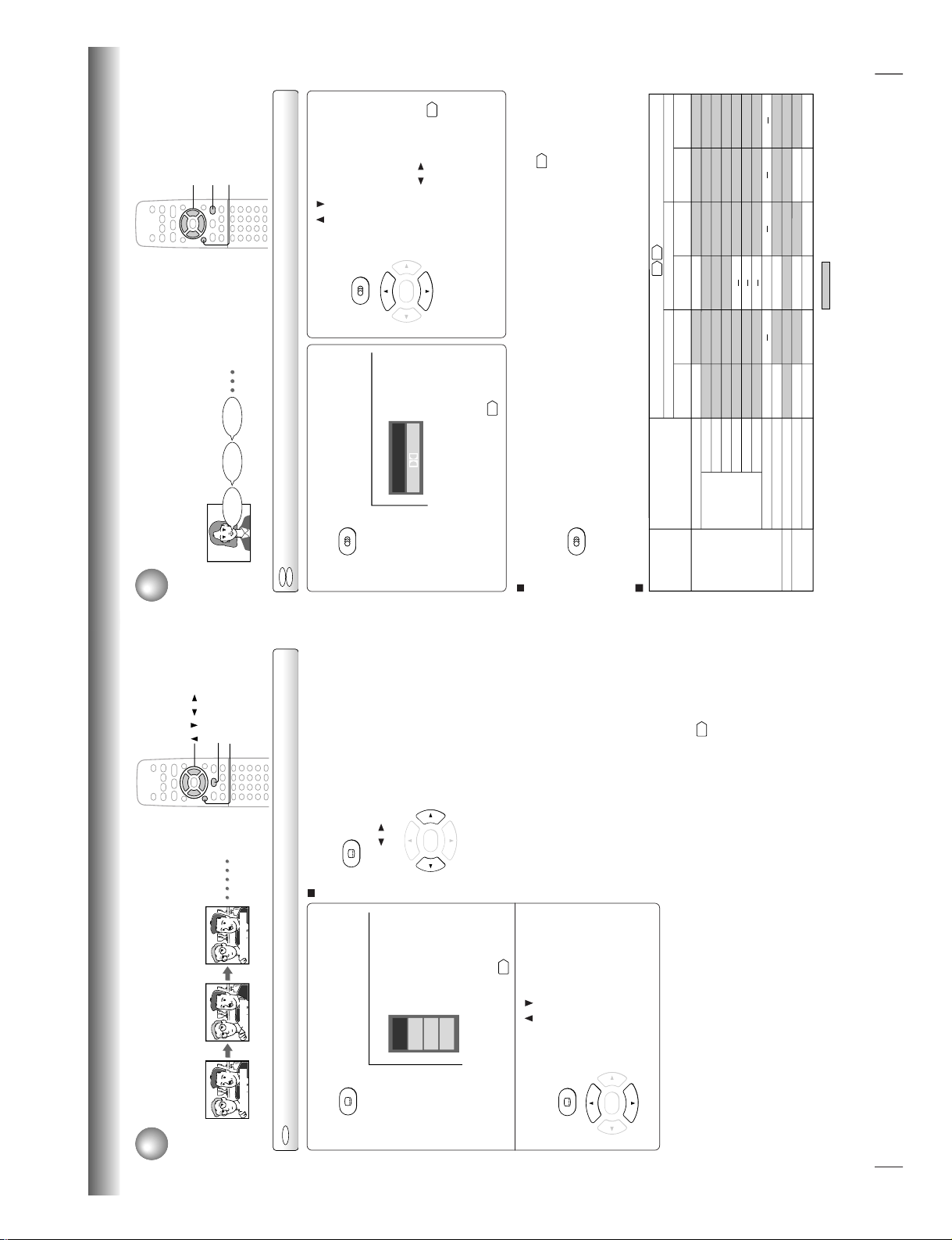

20

Basic playback

Playing a Disc

This section shows you the basics on how to play a disc.

CAUTION

Keep your fingers well clear of the disc tray as it is closing.

Neglecting to do so may cause serious personal injury.

Basic playback

Preparations

• When you want to view a disc, turn on the TV and select the video input connected to the DVD video player.

• When you want to enjoy the sound of discs from the audio system, turn on the audio system and select the input connected

to the DVD video player.

1

2

OPEN/CLOSE

3

4

To start playback in the stop mode

Press PLAY.

PAUSE

PAUSE SKIP

OPEN/CLOSE

ON/STANDBY

PLAYSTOP

1

2

,

4

PLAY

3

STOP

ON/STANDBY indicator

DVD display

Press ON/STANDBY.

The DVD video player turns on and

the color of the ON/STANDBY

indicator changes from red (standby)

to green (on).

When the DVD video player is turned on for

the first time, a message appears. Press

ENTER, and make the proper settings before

proceeding to step 2.

45

Press OPEN/CLOSE.

The disc tray opens.

Place the disc on the disc tray.

With the playback

side down

• There are two different disc sizes. Place the disc in

the correct guide on the disc tray. If the disc is out of

the guide, it may damage the disc and cause the

DVD video player to malfunction.

• Do not place a disc which is unplayable in this DVD

video player.

OPEN/CLOSE

Press OPEN/CLOSE to close the disc

tray.

Playback starts.

If you insert a DVD video disc that contains a top

menu, a menu may appear. See “Locating a title

using the top menu.”

24

• You may need to press the TOP MENU or MENU

button to display disc menu (depending on the actual

DVD video disc.)

DVD

VCD

CD

PLAY

21

Basic playback

To pause playback (still mode)

Press PAUSE/STEP during playbac k.

To resume normal playback, press

the PLAY button.

• Sound is muted during still mode.

To stop playback

Press STOP.

To remove the disc

Press OPEN/CLOSE.

Remove the disc after the disc tray

opens completely.

Be sure to press the OPEN/CLOSE button to close

the disc tray after you remove the disc.

PAUSE/STEP

STOP

OPEN/CLOSE

About the screen saver

If you pause a picture of a DVD video disc and leave it

still for a long while, the screen saver of the DVD video

player automatically appears (when “Screen Saver” is

set to “On”

43

). To turn off the screen saver, press the

PLAY button.

Automatic Power Off function

If the DVD video player is stopped, or the screen saver

is engaged for approximately 20 minutes, the DVD

video player will automatically turn itself off.

PAUSE/STEP

ENTER

MENU

STOP

TOP MENU

PLAY

2, 4

1

/

Notes

• Do not move the DVD video player during playback. Doing so may damage the disc.

• Use the OPEN/CLOSE button to open and close the disc tray. Do not push the disc tray while it is moving. Doing so may

cause the DVD video player to malfunction.

• Do not push up on the disc tray or put any objects other than discs on the disc tray. Doing so may cause the DVD video

player to malfunction.

• In many instances, a menu screen will appear after playback of a movie is completed. Prolonged display of an on-screen

menu may damage your television set, permanently etching that image onto its screen. To avoid this, be sure to press the

STOP button on your remote control once the movie is completed.

To obtain a higher quality picture

Occasionally, some picture noise not usually visible during a normal broadcast

may appear on the TV screen while playing a DVD video disc because the high

resolution pictures on these discs include a lot of information. While the amount of

noise depends on the TV you use with this DVD video player, you should generally

reduce the sharpness adjustment on your TV when viewing DVD video discs.

About

DVD VCD

CD

The

DVD

VCD CD

icons on the heading bar show the playable discs for the

function described under that heading.

DVD

: You can use this function with DVD video discs.

VCD

: You can use this function with VIDEO CDs.CD : You can use this function with audio CDs.

1-10

Page 15

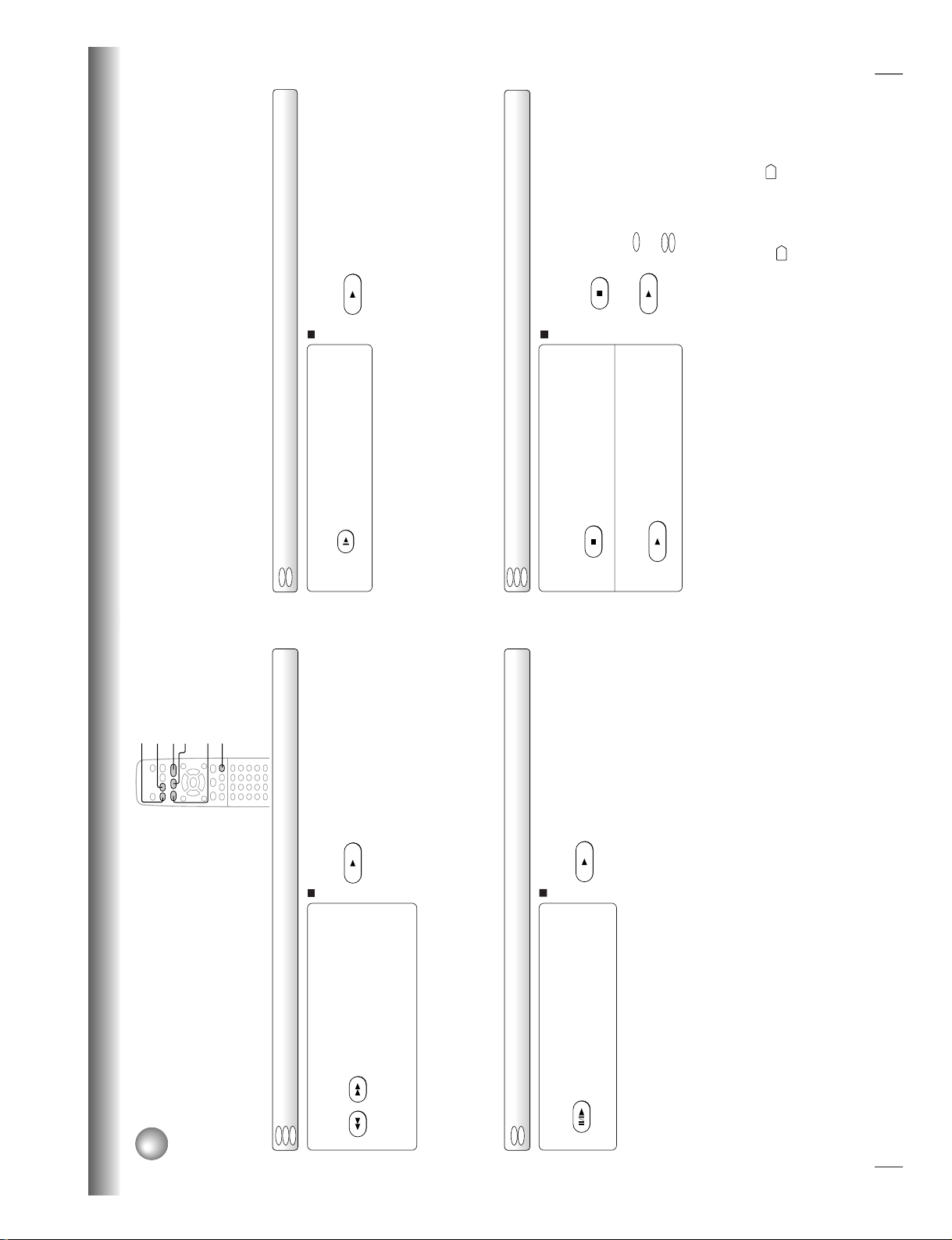

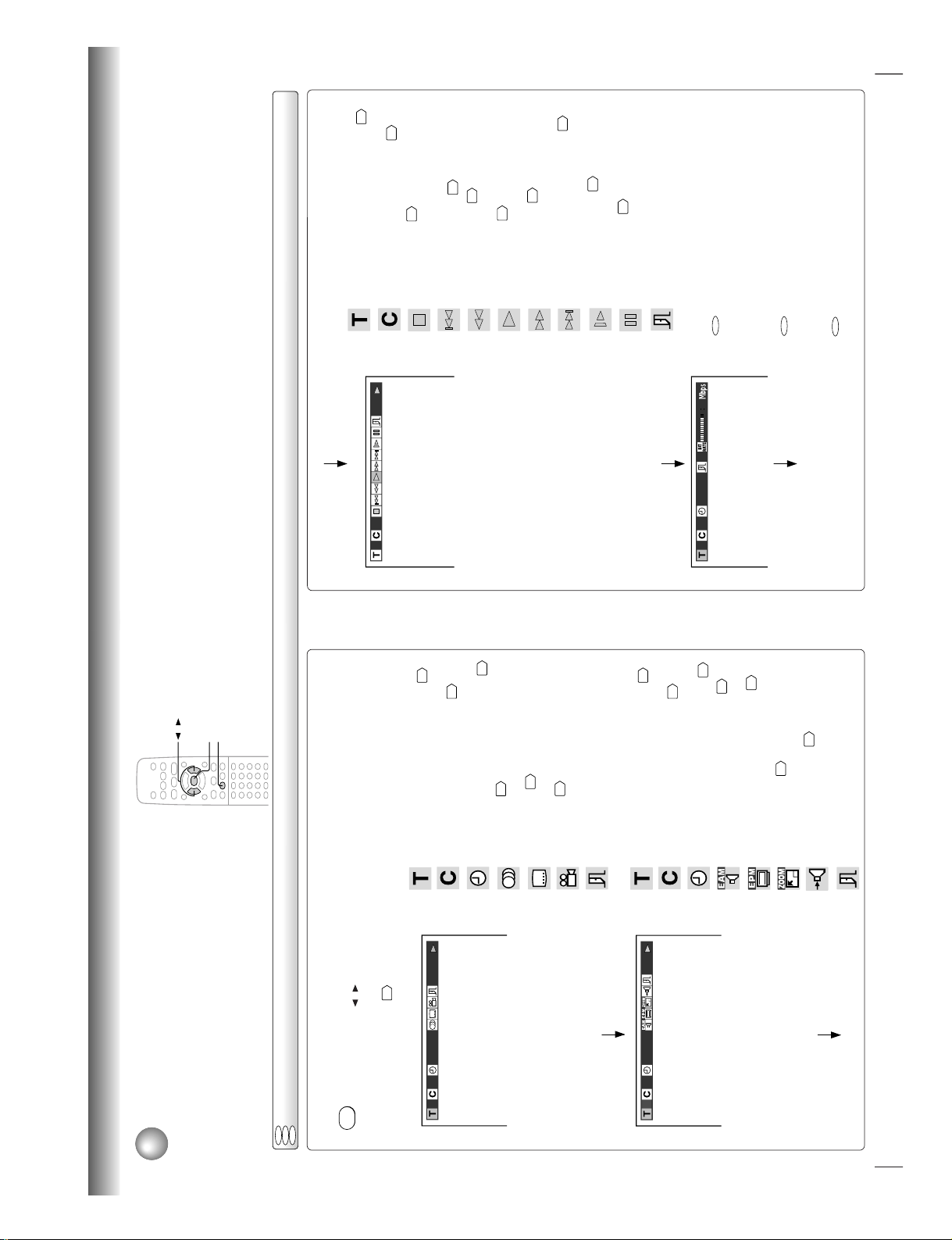

22

Basic playback

Playing a Disc (continued)

You can play discs at various speeds, and resume playback from the location

where you stopped playback.

Playing in fast reverse or fast forward directions

Press REV or FWD during playback.

REV: Fast reverse playback

FWD: Fast forward playback

Each time you press the REV or

FWD button, the playback speed

changes.

To resume normal playback

Press PLAY.

Notes

• The DVD video player mutes sound and omits subtitles

during reverse and forward scan of DVD video discs.

However, the DVD video player plays sound during fast

forward or fast reverse play of audio CDs.

• The playback speed may differ depending on the disc.

Playing frame by frame

Press PAUSE/STEP during still playback.

Each time you press the PAUSE/

STEP button, the picture advances

one frame.

To resume normal playback

Press PLAY.

Note

The sound is muted during frame by frame playback.

FWD

REV

PAUSE/STEP

PLAY

SLOW

STOP

DVD

VCD

REV

FWD

PLAY

PAUSE/STEP

PLAY

DVD

VCD

CD

23

Basic playback

Press STOP at the location where you

want to interrupt playback.

The DVD video player memorizes

the location where playback is

stopped.

Press PLAY.

The DVD video player resumes

playback from the location where

you stopped playback.

Playing in slow-motion

Press SLOW during playback.

Each time you press the SLOW

button, the slow-motion speed

changes.

To resume normal playback

Press PLAY.

Notes

• The sound is muted during slow-motion playback.

• The playback speed may differ depending on the disc.

Resuming playback from the same location

1

2

To start playback from the beginning regardless

of the location where you stopped playback

1 Press STOP twice.

The DVD video player’s memory is

cleared.

2 Press PLAY.

Playback starts from the

beginning of the current title.

Playback starts from the

beginning of the disc.

• If you want to return to the beginning of a DVD video

disc, open and close the disc tray once with the

OPEN/CLOSE button before pressing the PLAY

button.

Notes

• The DVD video player’s memory is also cleared when:

–you change the parental lock setting

43

or select a disc

menu language

41

.

–you open the disc tray.

• There may be a difference in the location where playback

resumes depending on the disc.

• Settings you changed using the on-screen displays while the

DVD video player keeps a location in the memory may

function only after the memory is cleared.

DVD

VCD

DVD

VCDCDDVD

SLOW

PLAY

STOP

PLAY

STOP

PLAY

VCD

CD

1-11

Page 16

24

Basic playback

Locating a Specific Title, Chapter, or Track

Normally, DVD video discs are divided into titles, and the titles are sub-divided into chapters. VIDEO CDs and audio CDs

are divided into tracks. You can quickly locate any specific title, chapter, or track.

Locating a title using the top menu

Press TOP MENU.

The top menu appears on the TV

screen.

e.g.

Press

/ / / to select the title you

want.

If the titles in the top menu are

assigned a number, you can directly

locate a specific title by pressing its

designated number with the number

buttons.

Press ENTER.

Playback starts from chapter 1 of the

selected title.

1

2

DVD video disc

Title 1

Title 2

Chapter 1 Chapter 2 Chapter 1 Chapter 2 Chapter 3

Track 1

Track 2 Track 3 Track 4 Track 5

VIDEO CD/audio CD

3

Notes

• The instructions above describe basic procedures which

may vary depending on the contents of the DVD video disc.

If different instructions appear on the TV screen, follow those

instructions.

• If you display the top menu during playback and press the

TOP MENU button again without selecting any title, the DVD

video player may resume playback from the point where you

first pressed the TOP MENU button (depending on the actual

DVD video disc.)

• This method of locating a title is available only on a disc that

contains a top menu.

• Instruction notes of discs may refer to the button that

displays the top menu as TITLE button.

Locating a title by entering the title number

Press T .

Make sure that the space of “T (Title)”

is highlighted.

(You can shift the highlight using the

/

buttons.)

Enter the number for the title you want,

using

/ or the number buttons.

e.g. To select title 2

To select title 12

Press PLAY.

Playback starts from chapter 1 of the

selected title.

1

3

Notes

• Pressing the CLEAR button resets the title and chapter

numbers. To clear the “T (Title)” and “C (Chapter)” display,

press the T button several times.

• This method of locating a title is available only on a disc that

contains title numbers.

DVD

TOP MENU

TITLE 1

TITLE 3

TITLE 2

TITLE 4

ENTER

ENTER

DVD

T

SEARCH

2

2

21

PLAY

1

–

:

––

:

––

1

e.g.

25

Basic playback

Locating a specific chapter or track directly

Press T .

If you are using a VIDEO CD/audio CD, skip steps 1

and 2, then at steps 3, enter the number for the track

you want using the number buttons.

Press to highlight the space of “C

(Chapter).”

Enter the number for the chapter or

track you want, using

/ or the

number buttons.

When you use the number buttons, you can use

the +10 button to select numbers from 10 through

99.

e.g. To select chapter or track 25

or

1

2

Press PLAY.

Playback starts from the selected

chapter or track.

3

4

To select a title and chapter number at the same

time

Perform step 1, and enter a title number you want in the

space of “T (Title)” using the number buttons or the

/

buttons then perform steps 2 to 4.

Note

Pressing the CLEAR button resets the title and chapter

numbers. To clear the “T (Title)” and “C (Chapter)” display,

press the T button several times.

Locating a specific chapter or track

Press SKIP

or repeatedly to display

the chapter or track number you want.

Playback starts from the selected chapter or track.

To locate succeeding chapters or tracks

Playback starts from the beginning of

the current chapter or track.

When you press twice, playback starts

from the beginning of the preceding

chapter or track.

Notes

• Some titles may not display chapter numbers.

• If you press and hold the SKIP

or button on the front

panel during playback, the DVD video player performs fast

reverse or fast forward playback. You can vary the speed by

pressing the button repeatedly.

To locate chapters or tracks during fast reverse or fast

forward playback, first press the PLAY button to resume

normal playback, then use the SKIP

or button.

• When you set “Title Stop” to “Off”

45

, you can access

chapters in another title. If you go back to the preceding title

by pressing the SKIP

button, the DVD video player

locates the first chapter of the title. When “Title Stop” is set

to “On,” you can access chapters only within the current title.

T

SEARCH

ENTER

PLAY

DVD

VCD

CD

SKIP

SKIP

/ / /

CLEAR

PLAY

ENTER

TOP MENU

T

Number buttons

SKIP

5

+10 +10

DVD

VCD

CD

52

1

–

:

––

:

––

1

1

–

:

––

:

––

1

e.g.

e.g.

1-12

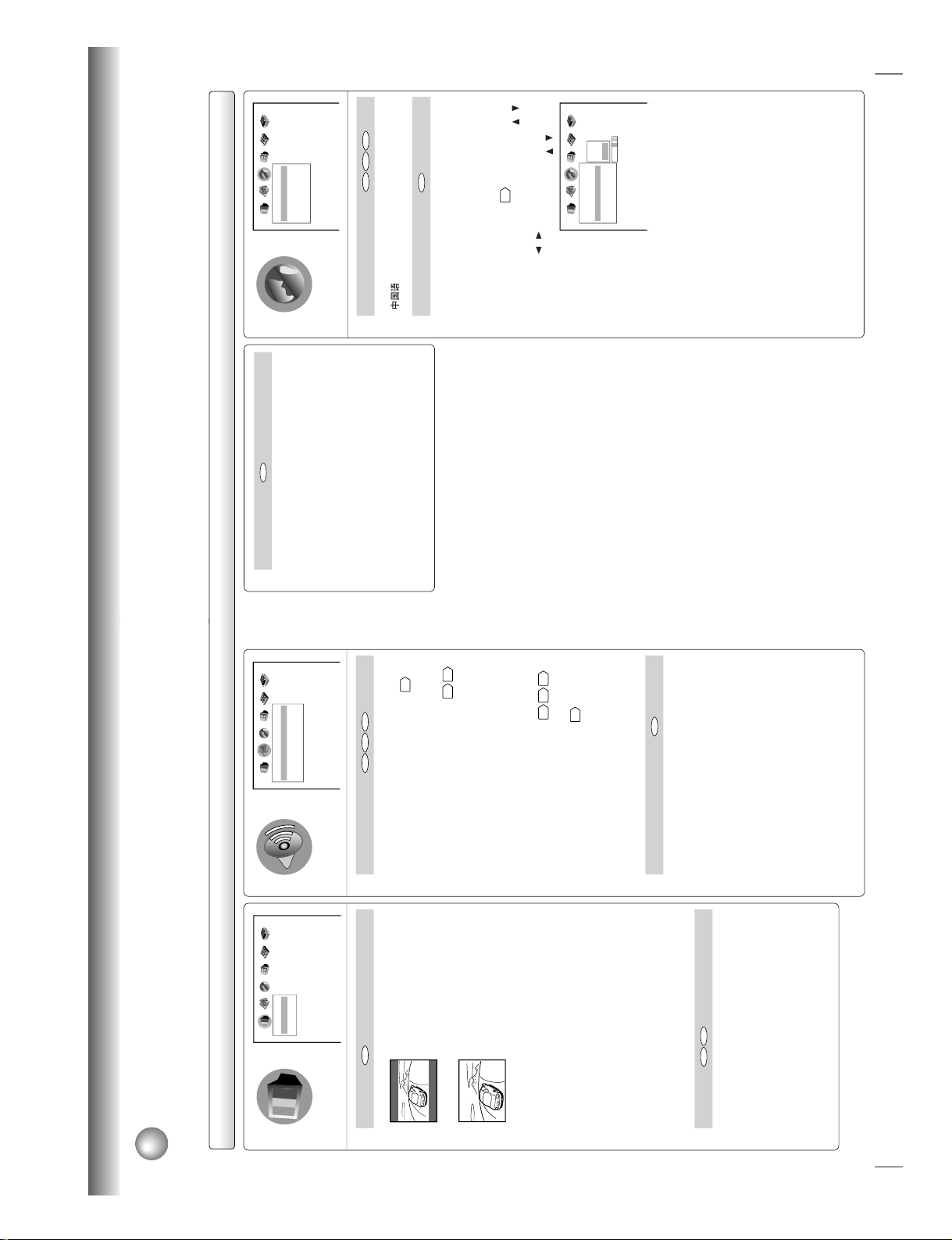

Page 17

26

Advanced playback

Press T three times.

You may have to press further

depending on the disc. Press the

button repeatedly until the clock icon

is highlighted.

Press the number buttons to enter the

time.

Press PLAY.

Playback starts from the desired

location.

Accessing a Specific Location Directly

You can access a specific location by entering its corresponding time (hours,

minutes, seconds).

Entering the time of the desired location

2

1

Notes

• Some discs may not respond to this process.

• Some scenes may not be located precisely as you specified.

• This method for accessing specific locations is available

only within the current title of the DVD video disc or within

the current track of the VIDEO CD/audio CD.

2

1

3

T

SEARCH

e.g.

3

PLAY

DVD

VCD

CD

1 2

5 3 0

1

–

:

––

:

––

1

1

1

:

25

:

30

1

e.g.

27

Advanced playback

Playing Repeatedly

You can play a specific title, chapter, track, or segment repeatedly.

(Title repeat, chapter/track repeat, A-B repeat)

Repeating a title, chapter, or track

Press REPEAT.

Each time you press the REPEAT

button, the repeat mode changes as

follows.

1

To resume normal playback

Press CLEAR.

Note

Some discs may not permit repeat operation.

Repeating a specific segment

Press A-B RPT at the beginning of the

segment (point A) you want to play

repeatedly.

Press A-B RPT again at the end of the

segment (point B).

The DVD video player automatically

returns to point A and starts repeat

playback of the selected segment

(A-B).

2

1

To resume normal playback

Press CLEAR.

Notes

• Some discs may not permit A-B repeat operation.

• You cannot set the A-B repeat function for a segment that

includes multiple camera angles

33

.

• You can specify a segment only within the current title or

track (VIDEO CD).

• There may be a slight difference between point A and the

location where playback actually resumes depending on the

disc.

A-B RPT

REPEAT

CLEAR

PLAY

A-B RPT

A-B RPT

REPEAT

CLEAR

CLEAR

Press PLAY.

The DVD video player starts repeat

playback.

Press the PLAY button within about

5 seconds after you press the

REPEAT button.

2

PLAY

DVD

VCD

CD

DVD

VCD

CD

DVD

DVD

DVD

VCD

CD

VCD

CD

Chapter Repeat

Title Repeat

Track Repeat

All Repeat

Repeat Off

Repeats the current

chapter.

Repeats the current

title.

Repeats the current

track.

Repeats the entire

disc.

Resumes normal

playback.

Chapter Repeat

A–

A–B

1-13

Page 18

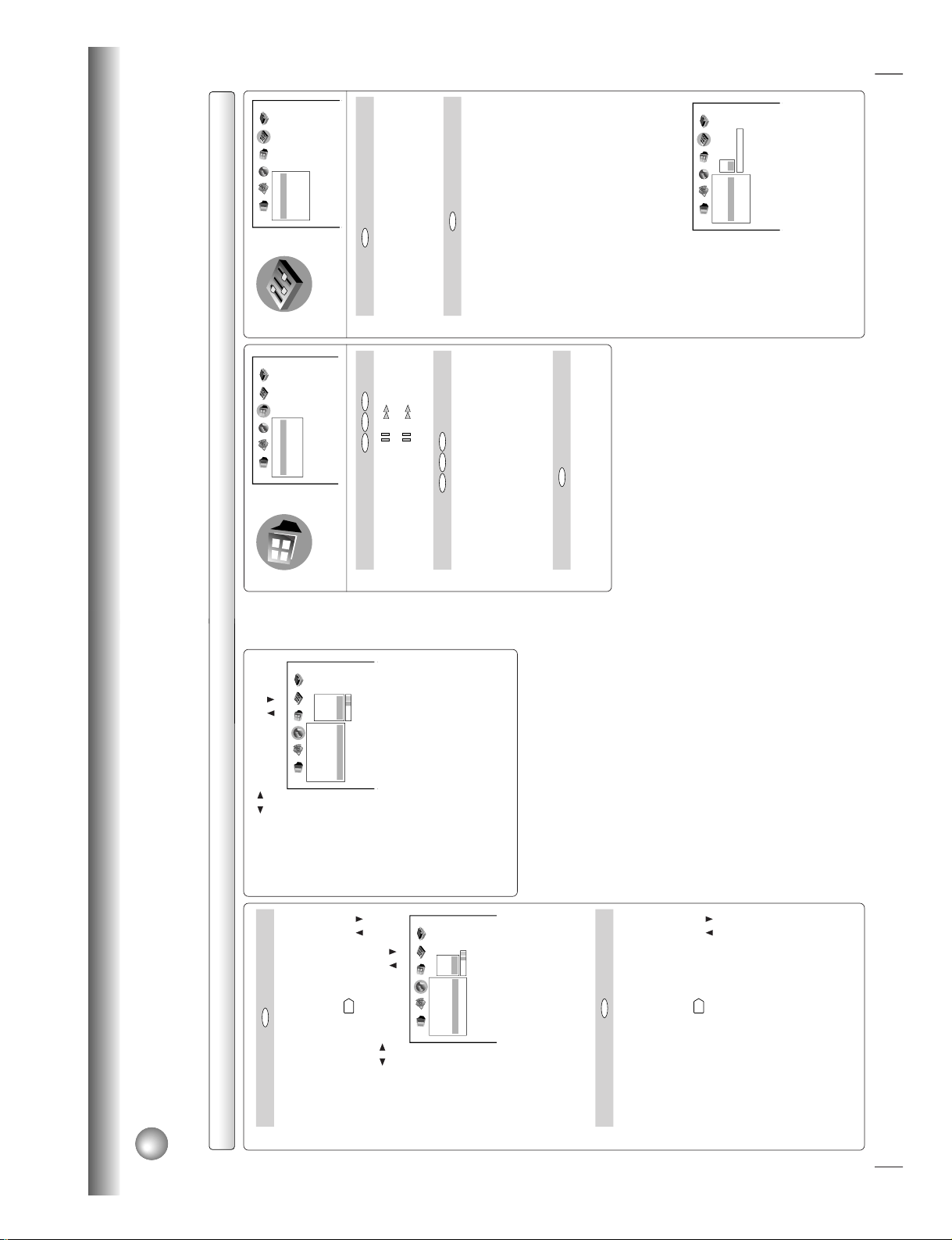

28

Advanced playback

Playing in a Favorite Order

You can combine your favorite titles, chapters, or tracks and play them in the

order you determine. You can program up to 30 selections into the memory.

(Memory playback)

Setting titles, chapters, or tracks in a favorite order

Insert a disc and press MEMORY during

stop.

The following display appears.

Select the items in the order you want

by pressing the number buttons, then

ENTER for each item.

Each time you press the

/ button, the space

of “T” and “CT” is highlighted in turn. Highlight

where you want to enter, then press the

corresponding number buttons.

To select another chapter in the same title, you do

not need to select the title number.

To select tracks from a VIDEO CD/audio CD in

order, press the number buttons for the track,

then press the ENTER button for each selection

you want.

Note

The space of “T (Title)” may be sho wing a number.

Neglect this number when using a VIDEO CD/audio

CD.

Press PLAY while the display appears

on the TV screen.

The DVD video player starts

memory playback.

1

2

3

To change the programmed selections

1 While the display appears on the TV screen, press

/ / / to move the highlighted bar to the item

you want to change.

2 Change the selection following the instructions in

step 2.

To cancel the programmed selections

1 While the display appears on the TV screen, press

/ to move the highlighted bar to the item you

want to cancel.

2 Press CLEAR.

To resume normal playback from memory

playback

Press CLEAR.

The memory playback indicator

disappears.

To program during playback

If you press the MEMORY button during playback, a

programming display appears.

Follow steps 2 and 3.

Notes

• Some discs may not permit memory playback operation.

• If you press the REPEAT button during memory playback,

the DVD video player repeats the current memory playback.

• If you press the MEMORY or RETURN button while the

display appears on the TV screen, the display disappears.

• The programmed selections will be cleared when you turn

off the DVD video player.

T: Title number

CT: Chapter number

or track number

MEMORY

PLAY

CLEAR

DVD

VCD

CD

/ / /

CLEAR

2

2

1

3

2

T

:

--

CT

:

---

1

T

:

--

CT

:

---

3

T

:

--

CT

:

---

4

T

:

--

CT

:

---

5

T

:

--

CT

:

---

6

T

:

--

CT

:

---

7

T

:

--

CT

:

---

e.g.

29

Advanced playback

Playing in Random Order

You can play titles, chapters within a title, or tracks in random order .

(Random playback)

Playing titles, chapters or tracks in random order

Press RANDOM.

Each time you press the RANDOM

button, the random playback mode

changes as follows.

2

1

To resume normal playback

Press CLEAR.

Notes

• Some discs may not permit random playback operation.

• You cannot use the random playback function in conjunction

with the memory playback function.

CLEAR

2

1

CLEAR

RANDOM

PLAY

DVD

VCD

CD

If you press the RANDOM button

during playback, the DVD video

player automatically starts random

playback after finishing the current

title, chapter or track.

Press PLAY.

The DVD video player starts random

playback.

Press the PLAY button within about

5 seconds after you press the

RANDOM button.

DVD

DVD

VCD

CD

Chapter Random

Title Random

Track Random

Random Off

Plays chapters within

the current title in

random order.

Plays titles in random

order.

Plays tracks in

random order.

Resumes normal

playback.

Chapter Random

1-14

Page 19

30

Advanced playback

Zooming a Picture

You can magnify areas within a picture.

Zooming a picture

/ / /

ZOOM

CLEAR

ENTER

DVD

Press ZOOM during normal, slow or still

playback.

The DVD video player enters the

zoom playback mode and displays

the icon.

: As you repeatedly press the ENTER

(or ZOOM) button while “ZOOM” is

selected, the magnification level

changes.

Variation of the levels includes

reducing.

: If you press the ENTER button while

“EXIT” is selected, you can turn off

the icon, keeping the current

magnification level.

You can shift the highlight within the

icon by the

/ / /

buttons.

If you press and hold the

/ / /

buttons, the zoom point shifts.

Pressing the CLEAR button restores

the zoom point to the center of the

picture.

To resume normal playback

While “ZOOM” is selected, press ZOOM repeatedly to

turn off the icon.

Picture restores the size when the icon disappears.

• The ENTER button cannot cancel zoom playback if

you have turned off the icon by selecting “EXIT.” To

restore normal picture size, press the ZOOM button

to display the icon, then further press the ZOOM

button until the icon turns off.

Notes

• Some discs may not respond to zoom feature.

• During some scenes, the buttons may not work as described.

• Zooming does not work on subtitles or menus included on

DVD video discs.

• While the icon is displayed, the

/

/ / buttons cannot

work on menus included on DVD video discs. If you want to

view the menus, turn off the icon.

• The magnification level varies depending on the picture size

you select.

40

ZOOM

ENTER

ZOOM

CLEAR

e.g.

31

Advanced playback

Light :

Brighter than in “Normal”.

Normal:

Standard black level.

Movie 1:

To raise brightness to clarify details.

Movie 2:

To deepen colors.

Animation:

To raise contrast enhancing colors.

Selecting the Picture Enhancement (E.P.M.*)

You can easily switch the picture enhancement to your preference.

*E.P.M.: Enhanced Picture Mode

ENTER

2

1, 2

Selecting the picture enhancement

Press E.P.M.

The picture enhancement selection

appears.

2

1

To turn off the picture enhancement selection

Press ENTER.

Alternatively leave the DVD video

player unoperated for about 5

seconds after having made the

selection.

Note

Actual effects to pictures may vary depending on the TV.

Make the selection to your preference.

Select the picture enhancement by

pressing E.P.M. or

/

.

Each time you press the button, the picture

enhancement changes.

E.P.M.

ENTER

DVD

VCD

CD

1-15

Page 20

32

Advanced playback

Normal:

Normal sound.

3D (N-2-2):

To obtain expansive virtual surround

sound effects from just two speakers.

Dialogue:

To control dynamic range to make

dialogues easier to hear (only when

playing a DVD video disc recorded

on the Dolby Digital recording

system).

• To use this enhancement on

sounds output from the

BITSTREAM/PCM (DIGITAL)

AUDIO OUT jack, be sure to set

“Audio Out Select” to “PCM”.

40

Selecting the Sound Enhancement (E.A.M.*)

You can easily switch the sound enhancement to your preference.

*E.A.M.: Enhanced Audio Mode

ENTER

2

1, 2

Selecting the sound enhancement

Press E.A.M.

The sound enhancement selection

appears.

Select the sound enhancement by

pressing E.A.M. or

/ .

Each time you press the button, the sound

enhancement changes.

2

1

To turn off the audio enhancement selection

Press ENTER.

Alternatively leave the DVD video

player unoperated for about 5

seconds after having made the

selection.

Notes

• Actual effects to sounds may vary depending on the

speakers. Make the selection to your preference.

• Actual effects to sounds may vary depending on the disc.

• When the DVD video player is connected to an amplifier

equipped with Dolby Pro Logic Surround, select “Normal”.

Otherwise, Dolby Pro Logic Surround may function

differently than usual.

• Selecting “Dialogue” disables “Dynamic Range Control”

function

40

.

E.A.M.

ENTER

Spatializer

®

3-Dimensional Sound Processing provided by Desper

Products. Inc.

Certain audio features of this product manufactured under a license

from Desper Products, Inc., Spatializer

®

and the circle-in-square

device are trademarks owned by Desper Products, Inc.

DVD

VCD

CD

33

Advanced playback

Selecting the Camera Angle

If the scene was recorded from multiple angles, you can easily change

the camera angle of the scene you are watching.

Changing the camera angle

Press ANGLE while playing a scene

recorded with multiple angles.

While playing a scene recorded with

multiple angles, the angle icon (

)

flashes in the DVD display.

Press the ANGLE button while the

angle icon is flashing.

Press ANGLE or

/ while the angle

number is displayed on the TV screen.

Each time you press the ANGLE

button, the camera angle changes.

You can change the camera angle

directly by pressing the number

buttons corresponding to its angle

number instead of using the

/

buttons.

To turn off the angle number display

Press CLEAR.

Notes

• You can change the camera angle during still playback. The

camera angle changes to the new setting when you resume

normal playback.

• If you pause a picture immediately after changing a camera

angle, the resumed playback picture may not display the new

camera angle.

1

2

2

1, 2

CLEAR

DVD

ANGLE

ANGLE

ENTER

CLEAR

1

2

3

e.g.

1-16

Page 21

34

Advanced playback

Selecting Subtitles

You can display subtitles on the TV screen and select a subtitle language

from those included on the DVD video disc.

Selecting a subtitle language

Press SUBTITLE during playback.

The current subtitle setting is

displayed.

The abbreviation of the language appears instead

of the language name. Refer to the list of

languages and their abbreviations.

46

Press SUBTITLE or

/

while the subtitle

setting is displayed on the TV screen.

Each time you press the SUBTITLE

button, the subtitle languages

included on the DVD video disc

change.

To turn off the subtitle setting display,

press the CLEAR or ENTER button.

To turn subtitles on or off

1 Press SUBTITLE during playback.

2 Press

/ while the subtitle setting is displayed on

the TV screen, to select “On” or “Off.”

Notes

• When you turn on the DVD video player or replace a disc, the player returns to the initial default setting

42

.

When you select a subtitle language which is not included on the disc, the DVD video player plays a prior language

programmed on the disc.

• During some scenes, the subtitles may not appear immediately after you change the subtitle language.

1

2

Notes

• Some DVD video discs are set to display subtitles

automatically, and you cannot turn them off even if you set

the subtitle function to off.

• During some scenes, the subtitles may not appear

immediately after you select “On.”

• Some DVD video discs will allow you to make subtitle

selections and turn subtitles on or off only via the disc menu.

SUBTITLE

/ / /

CLEAR

DVD

SUBTITLE

SUBTITLE

SUBTITLE

ENTER

ENTER

Bonsoir!Good evening! `Buenas tardes!

Off

JP

N

1

FRE 1

SP

A

1

e.g.

35

Advanced playback

Press AUDIO or

/ while the audio

setting is displayed on the TV screen.

Each time you press the AUDIO

button, the audio settings included

on the DVD video disc change.

If you press the

/ buttons, you

can select output sound format.

40

To turn off the audio setting display, press the

CLEAR button.

Selecting a Language

You can select a preferred language and sound recording system from those

included on the DVD video disc.

Selecting a playback audio setting

Press AUDIO during playback.

The current audio setting is

displayed.

The abbreviation of the language appears instead

of the language name. Refer to the list of

languages and their abbreviations.

46

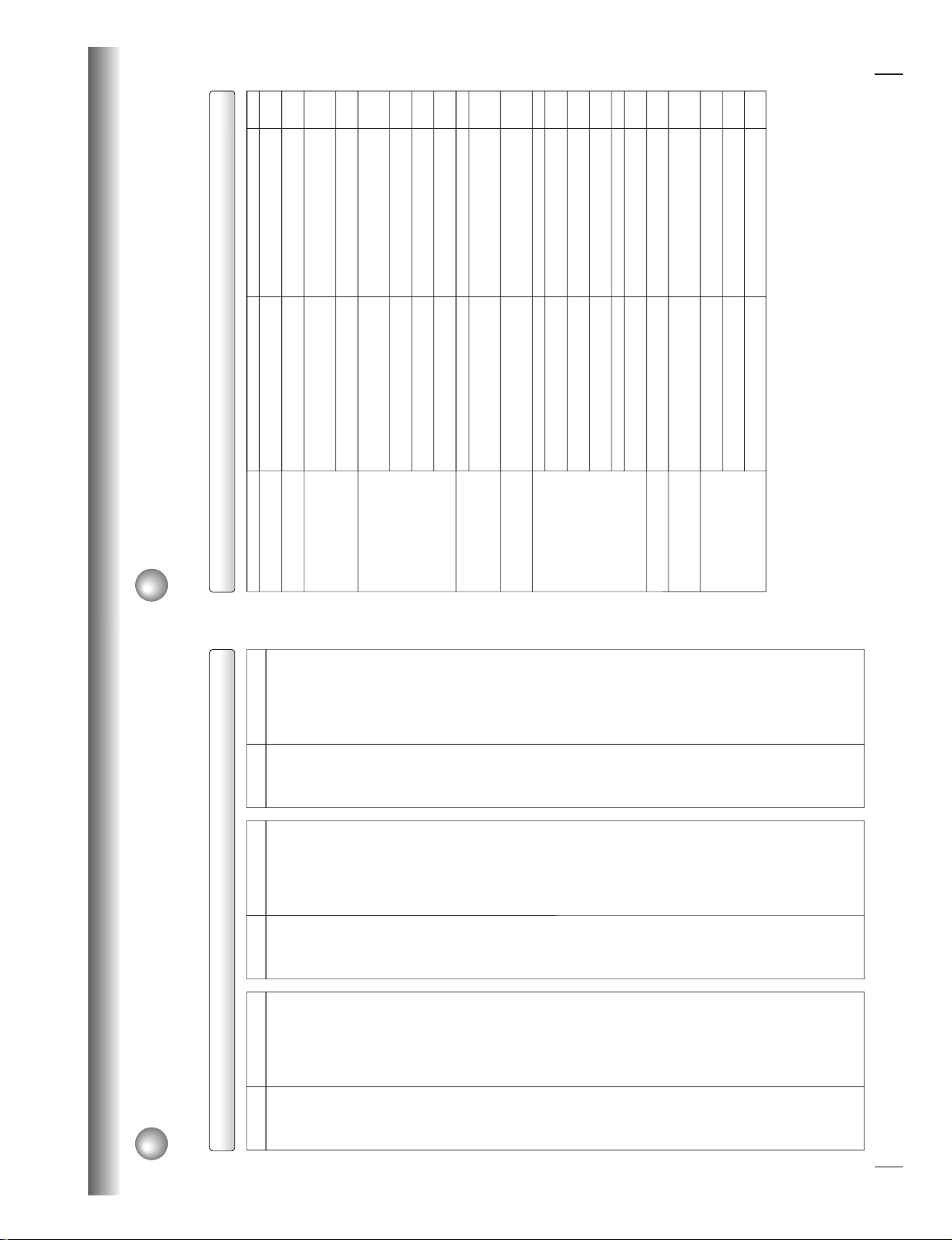

Output sound conversion table (sampling frequency/quantization bit)

12

CLEAR

2

1, 2

DVD

VCD

AUDIO

AUDIO

ENTER

Good morning!

¡Buenos días!

Bonjour!

BITSTREAM/PCM

jack

ANALOG AUDIO

OUT jacks

BITSTREAM/PCM

jack

ANALOG AUDIO

OUT jacks

BITSTREAM/PCM

jack

ANALOG AUDIO

OUT jacks

“Bitstream” “Analog 2ch”

“PCM”

Audio selection from the menu

and output jacks on the rear panel

Recording system

Discs

DVD video

discs

Audio CDs

VIDEO CDs

Linear PCM

Dolby Digital

DTS

MPEG1, MPEG2

Linear PCM

44.1 kHz/16 bit

48 kHz/20 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/20 bit

48 kHz/24 bit

96 kHz/16 bit

96 kHz/20 bit

96 kHz/24 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/16 bit

48 kHz/20 bit

48 kHz/24 bit

48 kHz/16 bit

48 kHz/20 bit

48 kHz/24 bit

Bitstream

Bitstream

Bitstream

Bitstream

44.1 kHz/16 bit

44.1 kHz/16 bit

Bitstream

Bitstream 48 kHz/16 bit 48 kHz/20 bit