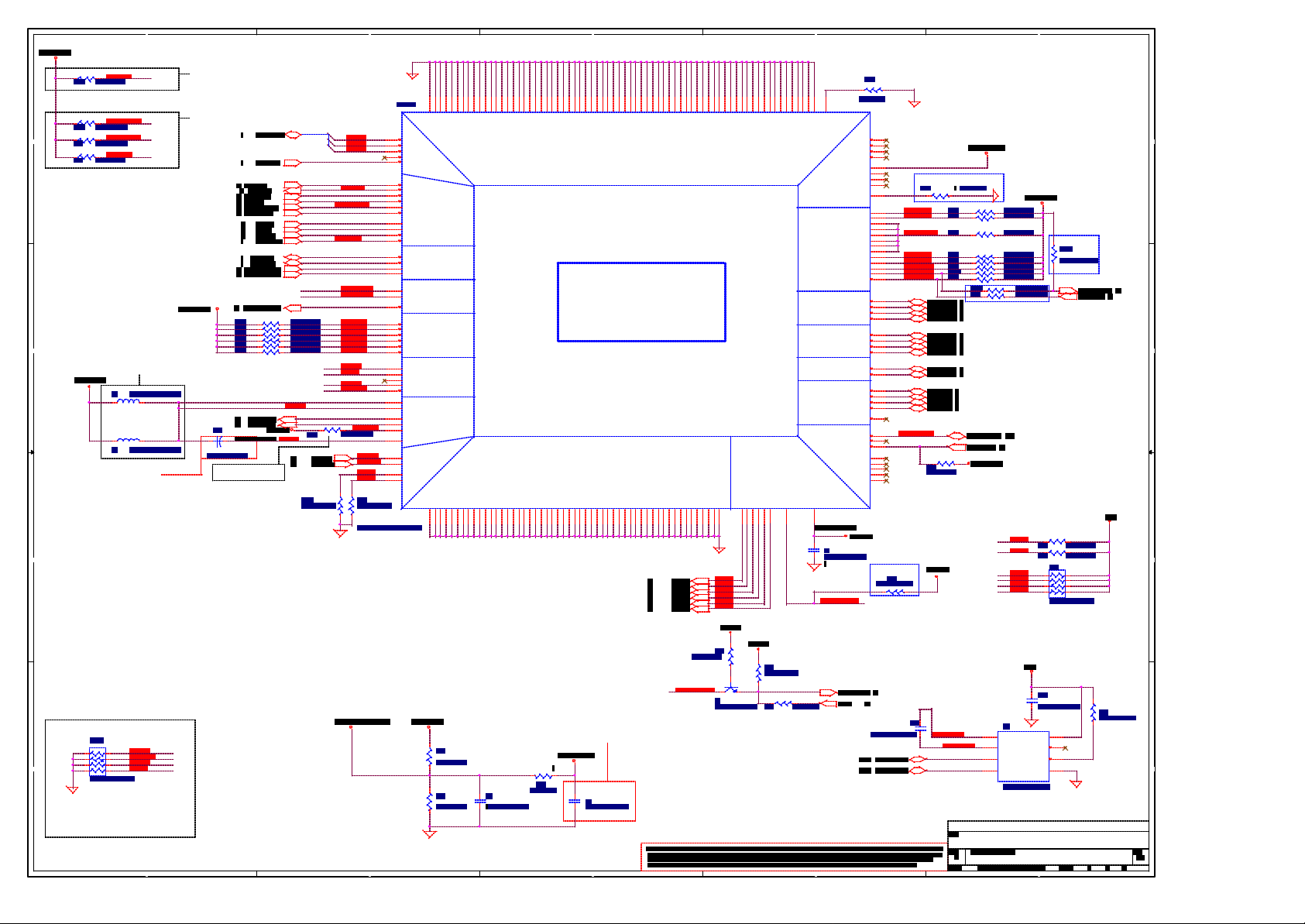

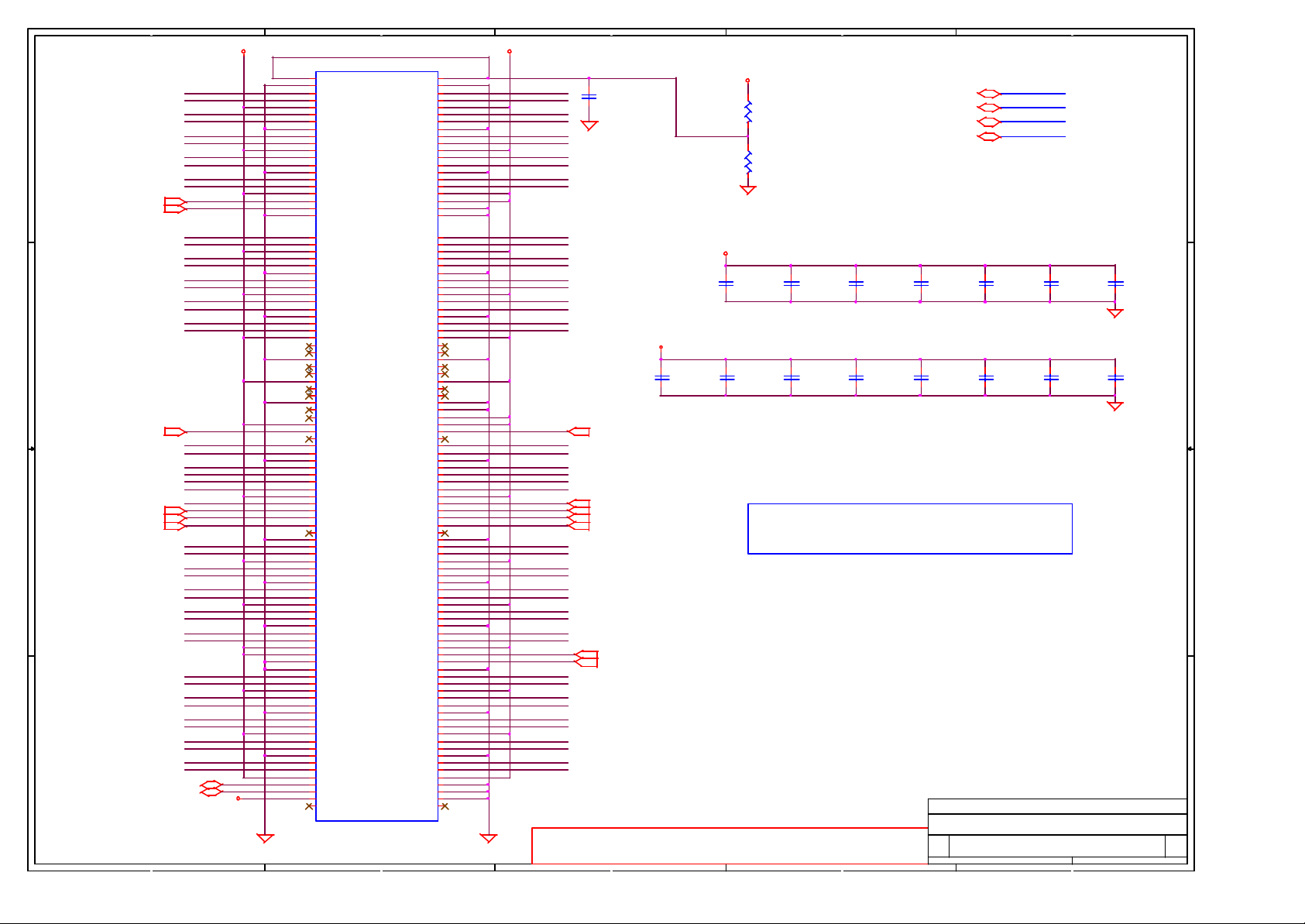

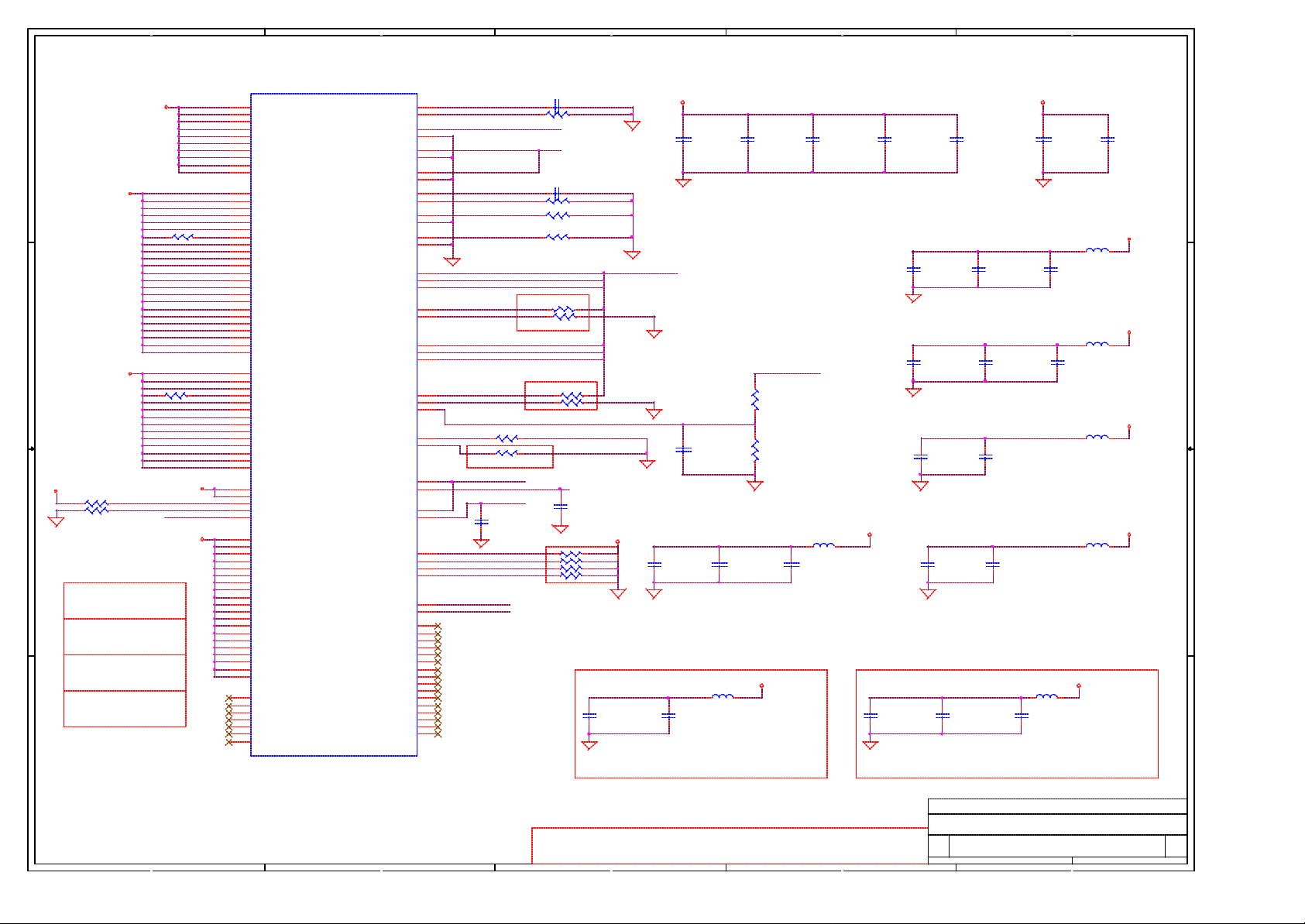

Toshiba P25-S526 Schematics

A

1 1

B

C

D

E

2 2

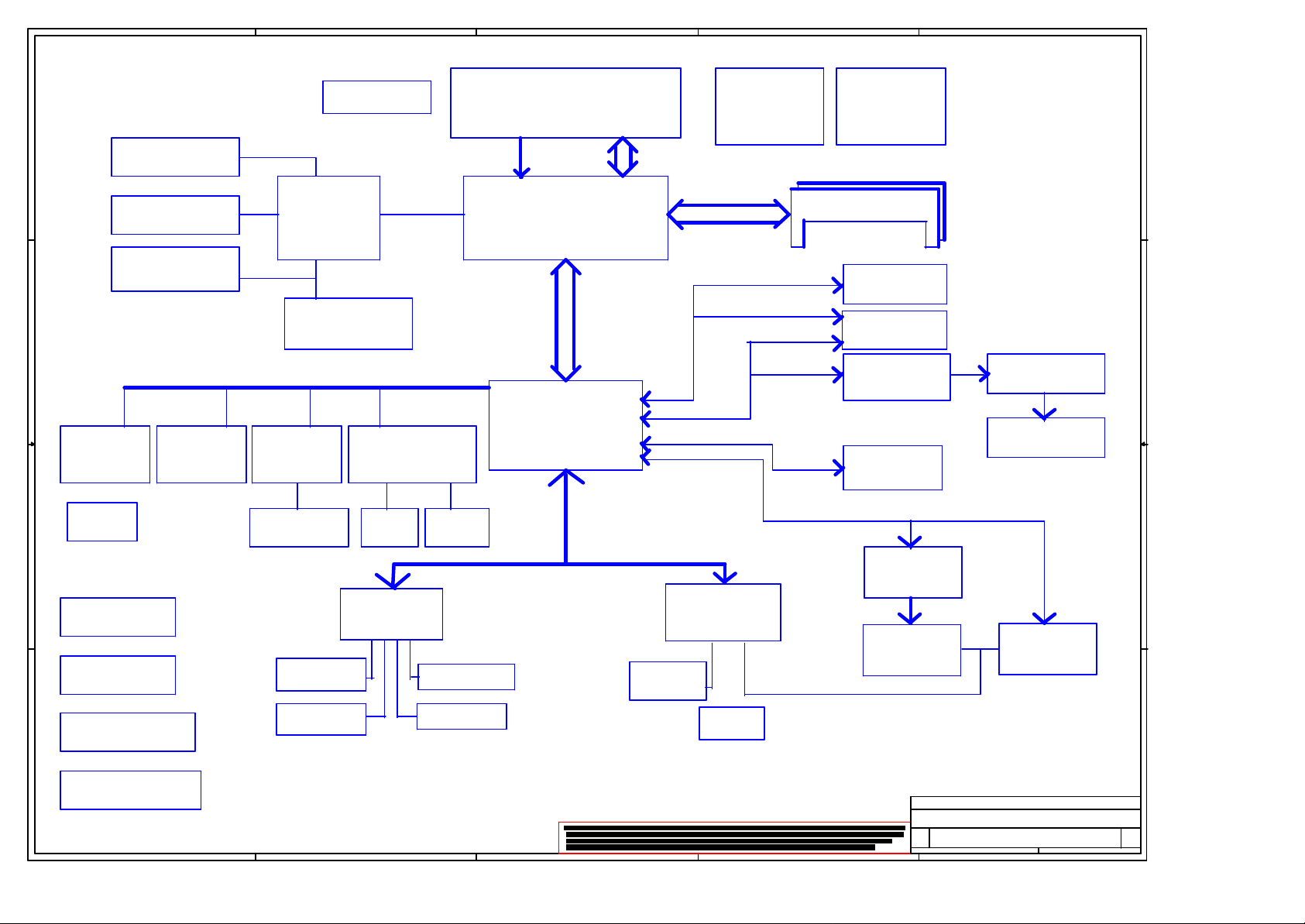

BTQ00 Rev0.1 Schematics Document

Intel Prescott uFCPGA-478 / P4 Northwood

with Springdale / ICH5 / nVIDIA NV18/34/31M chipset

2003/02/20

3 3

4 4

Compal Electronics, Inc.

Title

LA-1841

Cove r Sheet

1 57Thursday, February 20, 2003

E

0.1

Size Document Number Rev

B

A

B

C

D

Date: Sheet of

A

B

C

D

E

Compal Confidential

File Name : BTQ00

1 1

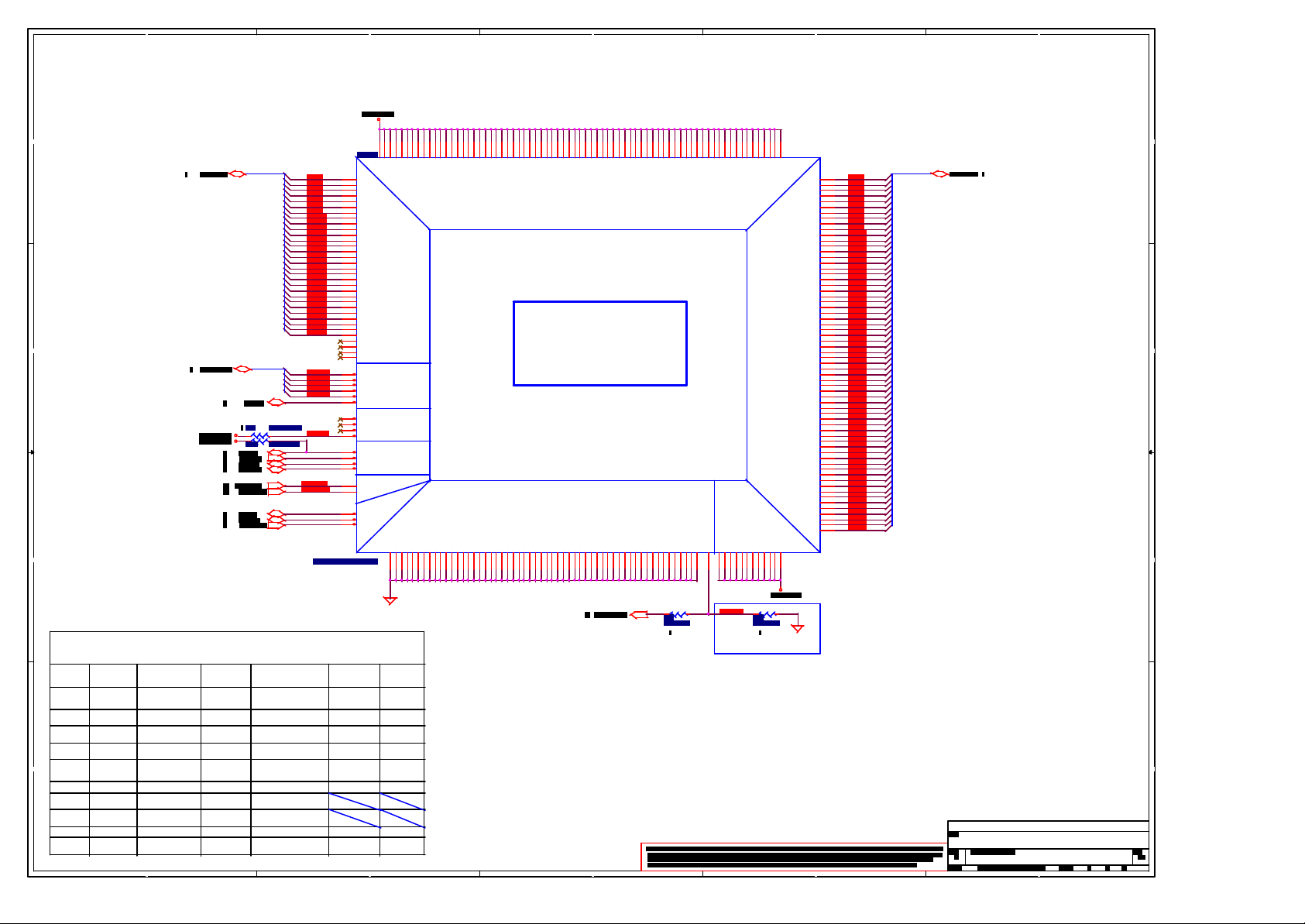

CRT Connector

LVDS Interface

TV OUT Connector

(4Pin Reverse)

2 2

page 22

page 22

page 22

NV18/31/34M

PIRQA#

Fan Control

VGA

page 16,17,

18,19

VRAM DDR

32MB/64MB (FBGA)

page 20,21

page 45

AGP BUS(8X)

Desktop Northwood uFCPGA-478 CPU

page 4,5,6

PSB

400/533/667/800MHz

H_D#(0..63)H_A#(3..31)

Intel Springdale MCH

FCBGA-932

page 7,8,9,10,11

Hub-Link

Thermal Sensor

ADM1032AR

Memory BUS(DDR)

2.5V DDR- 200/266

USB2.0

page 5

DDR-SO-DIMM X2

BANK 0, 1, 2, 3

Desktop Prescott uFCPGA-478 CPU

Clock Generator

ICS 952623

page 15

page 12,13,14

USB Conn *4

page 37

MDC & BT Conn

page 38

3.3V 33 MHz

IDSEL: AD18

IDSEL: AD16

PIRQA#, GNT0#, REQ0#

IEEE 1394

TSB43AB21

page 30

RTC CKT.

3 3

Power OK CKT.

Power On/Off CKT.

DC/DC Interface CKT.

4 4

PIRQC#, PIRQD#

GNT1#, REQ1#

page 41

Mini PCI

socket

page 29

IDSEL: AD17

PIRQB#, GNT3#, REQ3#

LAN

RTL 8101L

page 26

RJ45/11 CONN

page 26

Touch Pad

page 44

EC I/O Buffer

page 40

IDSEL: AD20

PIRQB#, SIRQ, GNT2#, REQ2#

EC

PCI BUS

CardBus Controller

Toshiba TC6385XB

Slot 0,1

page 28

page 27,28

SD Conn.

page 27

NS87591L

page 39

Int.KBD

BIOS (1MB)

page 39

page 40

Intel ICH5

mBGA-460

page 23,24,25

LPC BUS

PARALLEL

AC-LINK

ATA-100

Primary IDE

Secondary IDE

ATA-100

SMsC LPC47N227

Super I/O

page 36

page 38

FIR

page 37

master

Floppy

AC97 Codec

ALC202

page 31

HDD

Connector

page 35

master/slave

Audio DJ

OZ-168

Module Conn.

(Main Module)

page 34

page 35

HW EQ CKT

page 32

Audio AMP

page 32

Module Conn.

(2nd Module)

page 35

Power Circuit DC/DC

Title

Size Document Number Rev

A

B

C

D

Date: Sheet of

Compal Electronics, Inc.

Block Diag ram

LA-1841

2 57Thursday, February 20, 2003

E

0.1

A

B

C

D

E

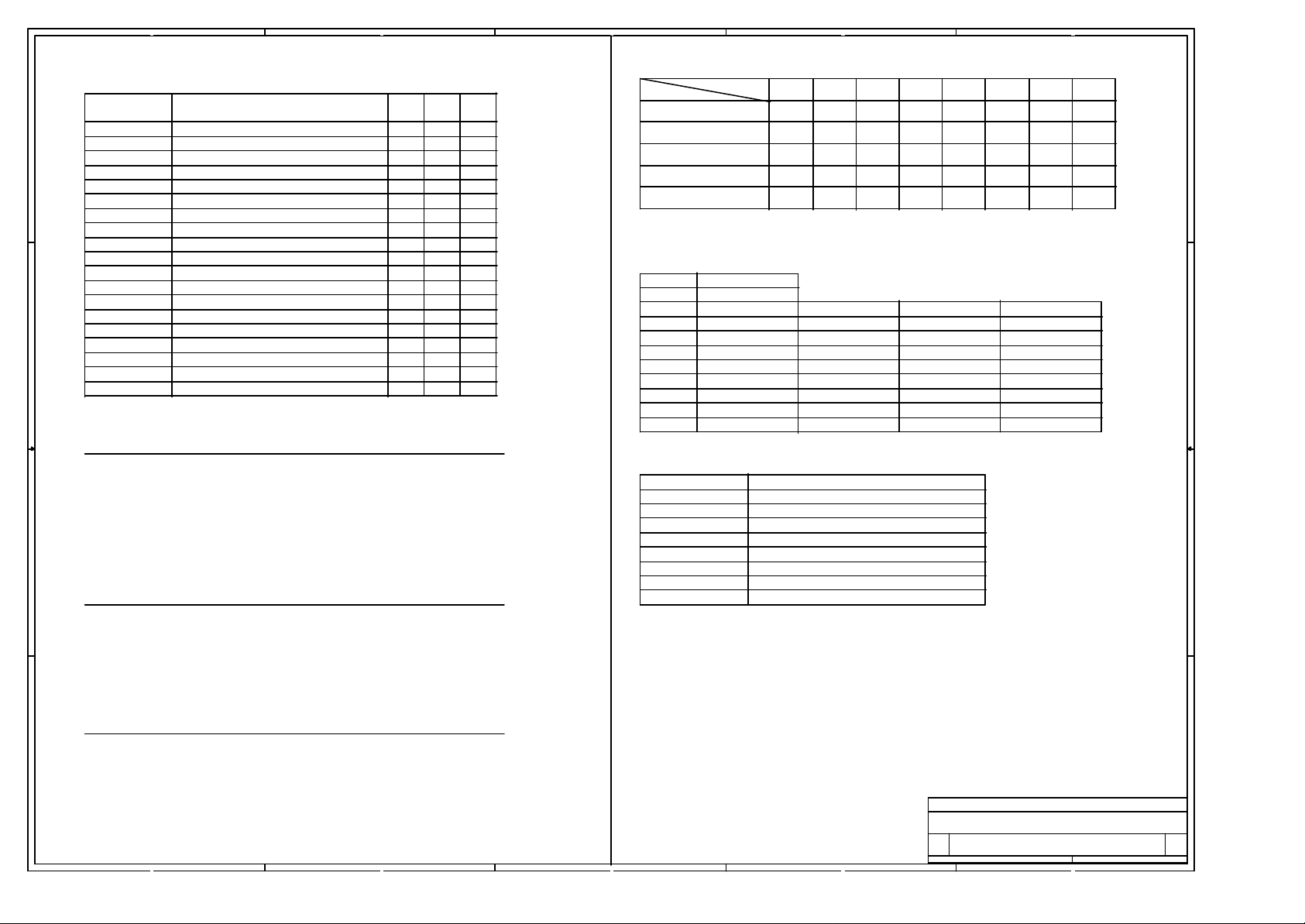

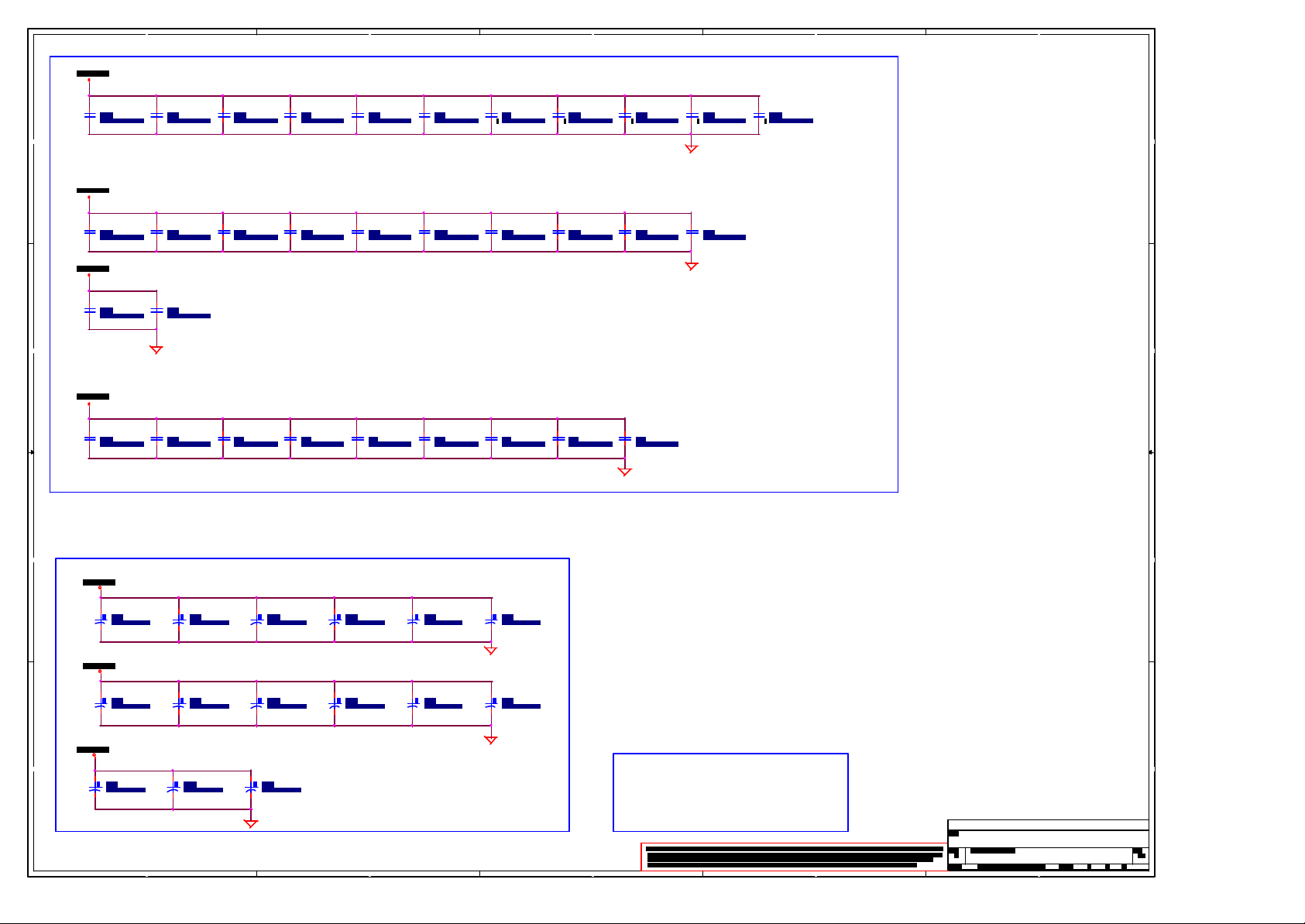

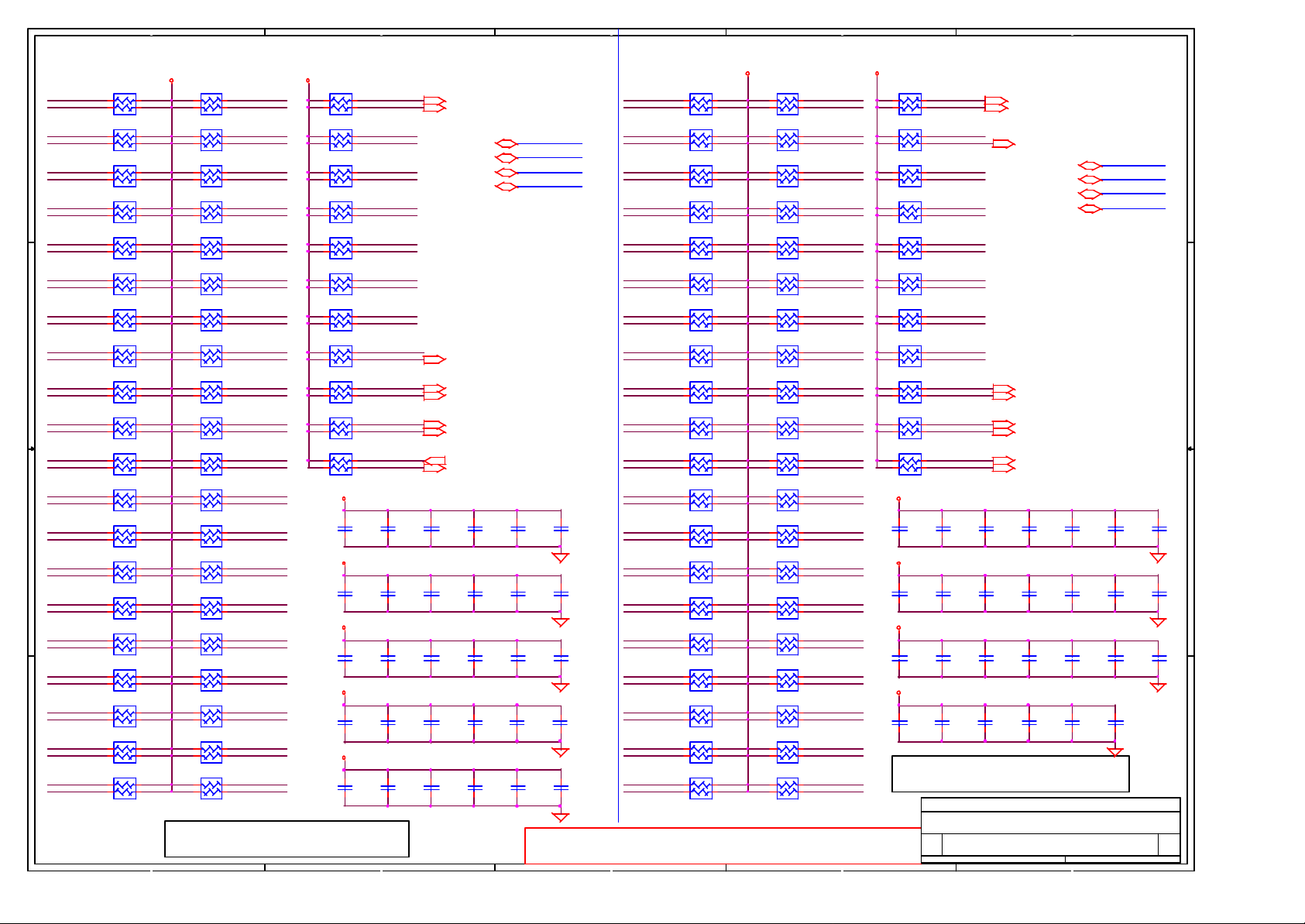

Voltage Ra ils

Power Plane Description

1 1

2 2

VIN

B+

+CPU_CORE

+CPU_VID

+VTT_GMCH +1.225V (Prescott) / +1.45V (Northwood)

+VGA_CORE ON OFF OFF1.2V switched power rail for VGA chip

+1.25VS 1.25V switched power rail

+1.5VS

+2.5V

+2.5VS 2.5V switched power rail

+3VALW

+3V

+3VS

+5VALW

+5V

+5VS

+RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

AGP 4X/8X

2.5V power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail

5V switched power rail

12V always on power rail

RTC power

S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON

ON

ON

ON

ON

ON

ON ON

ON

ON+12VALW

ON

N/AN/AN/A

OFF

OFF

OFF

ON

OFF

OFF

ON ON*

OFF

ON

OFF

OFF

ON

ON*

OFF

OFF

OFF

ON

ON*

ON

ON

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

ON

ON

ON ON

ON

ON

LOW

AD_BID

0 V

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

V typ

AD_BID

ON

ON

ON

0 V 0 V

ON

OFF

OFF

V

AD_BID

ON

OFF

OFF

OFF

max

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

3.300 V

LOW

OFF

OFF

OFF

External PCI Device s

Device IDSEL# REQ#/GNT# Interrupts

VGA

CardBus

LAN

Mini-PCI

1394 AD16 0 PIRQA

3 3

SD AD22

EC SM Bus1 address

Device

Smart Battery

EEPROM(24C16/02)

(24C04)

AD20

AD17

AD18

2

3 PIRQB

1/4

EC SM Bus2 address

Address Address

1010 000X b

1011 000Xb

Device

ADM1032

OZ168

PIRQA

PIRQA/PIRQB

PIRQC/PIRQD

1001 110X b0001 011X b

0011 0100 b

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

ICH4 SM Bus address

4 4

Device

Clock Generator

( ICS 952623)

DDR DIMM0

DDR DIMM1

A

Address

1101 001Xb

1001 000Xb

1001 001Xb

Compal Electronics, Inc.

Title

Size Document Number Rev

B

B

C

D

Date: Sheet of

LA-1841

Notes

3 57Thursday, February 20, 2003

E

0.1

5

4

3

2

1

D D

C C

1 2

1 2

B B

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VSS_0

H1H4H23

VSS_1

VSS_2

H26

VSS_3

A11

VSS_4

A13

VSS_5

A15

VSS_6

A17

VCC_9

VSS_7

A19

VCC_10

VCC_11

VSS_8

VSS_9

A21

A24

VCC_12

VCC_13

VSS_10

VSS_11

A26A3A9

VCC_14

VCC_15

VSS_12

VSS_13

AA1

VCC_16

VCC_17

VSS_14

VSS_15

AA11

AA13

VCC_18

VCC_19

VSS_16

VSS_17

AA15

AA17

VCC_20

VCC_21

VSS_18

VSS_19

AA19

AA23

VCC_22

VCC_23

VSS_20

VSS_21

AA26

AA4

VCC_24

VCC_25

VSS_22

VSS_23

AA7

AA9

VCC_26

VCC_27

VSS_24

VSS_25

AB10

AB12

VCC_28

VSS_26

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

Prescott

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

AB14

AB16

VSS_36

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

VCC_39

VCC_40

VSS_37

VSS_38

AC15

AC17

VCC_41

VCC_42

VSS_39

VSS_40

AC19

AC2

VCC_43

VCC_44

VSS_41

VSS_42

AC22

AC25

VCC_45

VCC_46

VSS_43

VSS_44

AC5

AC7

VCC_47

VCC_48

VSS_45

VSS_46

AC9

AD10

VCC_49

VCC_50

VSS_47

VSS_48

AD12

AD14

VCC_51

VCC_52

VSS_49

VSS_50

AD16

AD18

VCC_53

VCC_54

VSS_51

VSS_52

AD21

AD23

VCC_55

VCC_56

VSS_53

VSS_54

AD4

AD8

VCC_57

VSS_55

VCC_58

VCC_59

VCC_61

BOOTSELECT

AD1

F13

VCC_62

VCC_63

VCC_81

VCC_82

F15

F17

VCC_64

VCC_65

VCC_83

VCC_84

F19

F9

VCC_66

VCC_67

VCC_80

VCC_85

VCC_68

VCC_69

VCC_78

VCC_79

E20E8F11

E18

VCC_70

VCC_71

VCC_76

VCC_77

E16

E14

VCC_72

VCC_73

VCC_74

VCC_75

E12

B21

D#0

B22

D#1

A23

D#2

A25

D#3

C21

D#4

D22

D#5

B24

D#6

C23

D#7

C24

D#8

B25

D#9

G22

D#10

H21

D#11

C26

D#12

D23

D#13

J21

D#14

D25

D#15

H22

D#16

E24

D#17

G23

D#18

F23

D#19

F24

D#20

E25

D#21

F26

D#22

D26

D#23

L21

D#24

G26

D#25

H24

D#26

M21

D#27

L22

D#28

J24

D#29

K23

D#30

H25

D#31

M23

D#32

N22

D#33

P21

D#34

M24

D#35

N23

D#36

M26

D#37

N26

D#38

N25

D#39

R21

D#40

P24

D#41

R25

D#42

R24

D#43

T26

D#44

T25

D#45

T22

D#46

T23

D#47

U26

D#48

U24

D#49

U23

D#50

V25

D#51

U21

D#52

V22

D#53

V24

D#54

W26

D#55

Y26

D#56

W25

D#57

Y23

D#58

Y24

D#59

Y21

D#60

AA25

D#61

AA22

D#62

AA24

D#63

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

J1

REQ#0

K5

REQ#1

J4

REQ#2

J3

REQ#3

H3

REQ#4

G1

ADS#

AC1

AP#0

V5

AP#1

AA3

BINIT#

AC3

IERR#

H6

BR0#

D2

BPRI#

G2

BNR#

G4

LOCK#

AF22

BCLK0

AF23

BCLK1

F3

HIT#

E3

HITM#

E2

DEFER#

1 2

1 2

R_C

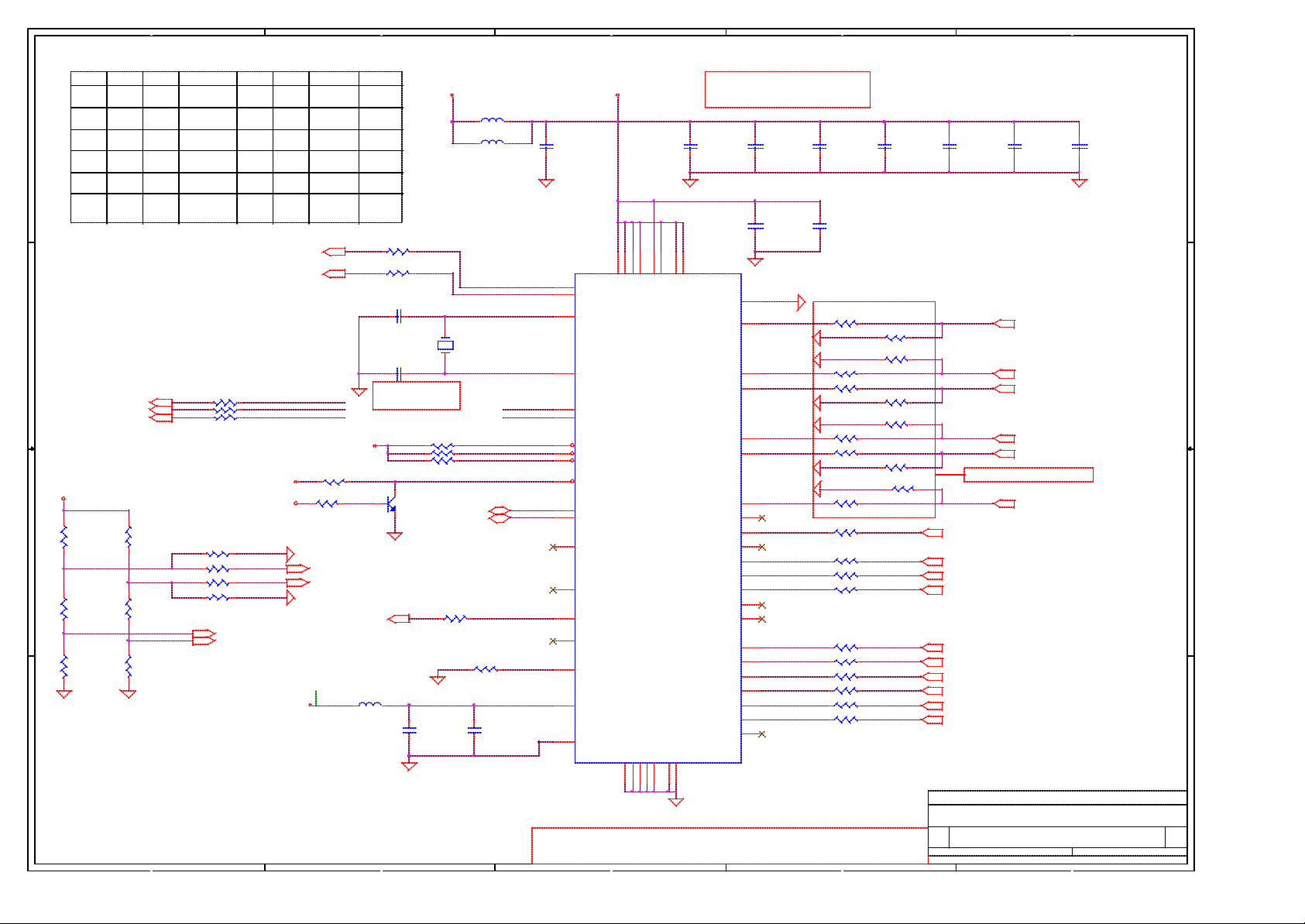

Reference Intel document

Desktop P4 Spec.: 10988 P4 0.13u 512KB L2 EMTS Rev.2.0

Desktop Prescott Spec.: 11910 Prescott EMTS Rev.0.5

Pin number Northwood

P in name

B6 FERR# F ERR#/PBE# Pull-up 62ohm

AA20 I TPCLKOUT0 Pull-up56ohm

AB22 I TPCLKOUT1 Pull-up 56ohm

AD2 NC V IDPWRGD Pull-up 8.2Kohm

AD3 NC float VID5 Pull-up1Kohm to

A A

AF3 NC float V CCVIDLB Connect to +VCCVID

AD20 VCCA V CCIOPLLConnect to CPU

AF23 Connect to CPU

V CCIOPLL VCCA

AD1 VSS B OOTSELECTConnect to GND CPU determine

AE26 VSS Connect to GND OPTIMIZED/

C ommend Commend

Pull-up 62ohm

to +VCC_CORE

to +VCC_CORE

to +VCC_CORE

float

Filter

Filter

5

P rescott

P in name

to +VCC_CORE

T ESTHI6 Pull-up 62ohm

to +VCC_CORE

T ESTHI7 Pull-up 62ohm

to +VCC_CORE

to +VCCVID

+3VRUN & connect

t o PWRIC

Connect to CPU

Filter

Connect to CPU

Filter

float

COMPAT#

N orthwood P rescott

Pop Pop

Pop Pop

Pop Pop

PopDepop

Depop

Depop

Pop

Pop

Pop Depop

Pop Depop

4

3

Pop: Northwood

Depop: Prescott

Compal Electronics, Inc.

Prescott Processor in uFCPGA478 (1/2)

2

LA-1841

1

5

4

3

2

1

1 2

1 2

1 2

D D

1 2

C C

B B

Note: Please change to 10uH, DC current

of 100mA parts and close to cap

1 2

1 2

PLL Layout note :

1.Place cap within 600 mils of

the VCCA and VSSA pins.

2.H_VCCIOPLL,HVCCA,HVSSA trace wide

12 mils(min)

Place near ICH

Place near CPU

+

1 2

Pop: Prescott

Depop: Northwood

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26B4B8

C11

C13

C15

C17

C19C2C22

C25C5C7C9D10

D12

D14

D16

D18

D20

D21

D24D3D6D8E1

E11

E13

E15

E17

E19

E23

E26E4E7E9F10

F12

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_161

VSS_162

T24T3T6U2U22

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

U25U5V1

VSS_99

VSS_100

VSS_169

VSS_170

V23

VSS_101

VSS_102

VSS_171

VSS_172

V26V4W21

VSS_103

VSS_104

VSS_173

VSS_174

W24W3W6Y2Y22

VSS_105

VSS_106

VSS_175

VSS_176

VSS_107

VSS_108

VSS_177

VSS_178

VSS_109

VSS_110

VSS_179

VSS_180

Y25

Y5

VSS_111

VSS_112

VSS_181

VSS_113

VSS_114

AE5

VSS_115

VSS_116

VID0

VID1

AE4

AE3

VSS_117

VSS_118

VID2

VID3

AE2

AE1

VSS_119

VSS_120

VID4

VID5

AD3

VSS_121

F1

RS#0

G5

RS#1

F4

RS#2

AB2

RSP#

J6

TRDY#

C6

A20M#

B6

FERR#

B2

IGNNE#

B5

SMI#

AB23

PWRGOOD

Y4

STPCLK#

D1

LINT0

E5

LINT1

W5

INIT#

AB25

RESET#

H5

DBSY#

H2

DRDY#

AD6

BSEL0

AD5

BSEL1

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AC6

BPM#0

AB5

BPM#1

AC4

BPM#2

Y6

BPM#3

AA5

BPM#4

AB4

BPM#5

D4

TCK

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

AD20

VCCIOPLL

AE23

VCCA

A5

VCCSENSE

A4

VSSSENSE

AF3

VCCVIDLB

AD22

VSSA

AC26

ITP_CLK0

AD26

ITP_CLK1

L24

COMP0

P1

12

12

COMP1

VSS_129

F8

G21

VSS_130

VSS_131

VSS_132

VSS_133

G24G3G6J2J22

VSS_134

VSS_135

J25J5K21

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

K24K3K6L1L23

VSS_142

VSS_143

L26L4M2

VSS_144

VSS_145

VSS_146

VSS_147

M22

M25M5N21

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

N24N3N6P2P22

Prescott

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

P25P5R1

R23

R26R4T21

F14

VSS_122

F16

F18F2F22

VSS_123

VSS_124

VIDPWRGD

AD2

F25

VSS_125

VSS_126

VSS_127

AF26

F5

VSS_128

SKTOCC#

OPTIMIZED/COMPAT#

VCCVID

AF4

1

2

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

PROCHOT#

MCERR#

J26

DP#0

K25

DP#1

K26

DP#2

L25

DP#3

AA21

AA6

F20

F6

AE26

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

DBI#0

G25

DBI#1

P26

DBI#2

V21

DBI#3

AE25

DBR#

C3

V6

AB26

SLP#

A22

NC1

A7

NC2

AF25

NC3

AF24

NC4

AE21

NC5

R_E

1 2

R_G

1 2

1 2

RE

Pop: Prescott

Depop: Northwood

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

Pop: Northwood

Depop: Prescott

1 2

Pop: P4 Protability

Depop: Prescott/Northwood

1 2

1 2

45

36

27

18

122

12

GTL Reference Voltage

Layout note :

1. +CPU_GTLREF Trace wide

12mils(min),Space 15mils

2. Place R_A and R_B near CPU.

3. Place decoupling cap 220PF near CPU.

12

2

1 8

2 7

A A

3 6

4 5

+CPU_GMCH_GTLREF trace

wide 12mils(min),Space

15mils

R_A

R_B

1212

2 1

1

Close to the CPU

31

1 2

1

2

Compal Electronics, Inc.

1

2

2

VDD1

D+

3

ALERT#

D-

8

THERM#

SCLK

7

GND

SDATA

12

1

6

4

5

Prescott Processor in uFCPGA478 (2/2)

5

4

3

2

LA-1841

1

5

4

3

2

1

Place 11 North of Socket(Stuff 8)

1

2

D D

1

2

1

2

1

2

1

2

1

2

1

2

1

2

Place 12 Inside Socket(Stuff all)

1

2

1

2

C C

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

22uF depop reference

Springdale Customer Schematic R1.2 page82

1

2

1

2

1

2

1

2

Place 9 South of Socket(Unstuff all)

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

B B

470uF _ERS10m ohm* 15, ESR=0.5m ohm

1

2

1

2

A A

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

Decoupling Reference Document:

Springdale Chipset Platform Design guide Rev1.11

(12474)page239

Decoupling Reference Requirement:

560uF Polymer, ESR:5m ohm(each) * 10

22uF X5R * 32

Compal Electronics, Inc.

CPU Decoupling

LA-1841

5

4

3

2

1

5

4

3

2

1

+VTT_GMCH

D D

C C

+CPU_GMCH_GTLREF

GTL Reference Voltage

B B

A A

Layout note :

1. +GMCH_GTLREF Trace wide

12mils(min),Space 15mils.

2. Place decoupling cap 220PF near GMCH.

Trace width 10mils,Space

7mils

12

R365

301_0603_1%

HD_SWING

12

R369

102_0603_1%

HDRCOMP

12

R362

24.9_0603_1%

+VTT_GMCH

12

R359

200_0603_1%

1 2

R647 0_0603_5%

1

C159

0.01U_0402_16V7K

2

+GMCH_GTLREF

1

C160

220P_0402_50V8K

2

H_RS#[0..2]5

H_A#[3..31]4

H_REQ#[0..4]4

H_TRDY#5

+GMCH_GTLREF

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_RS#0

H_RS#1

H_RS#2

HDRCOMP

HD_SWING

H_REQ#4

H_ADSTB#05

H_ADSTB#15

CLK_HCLK15

CLK_HCLK#15

H_DSTBP#05

H_DSTBN#05

H_DINV#05

H_DSTBP#15

H_DSTBN#15

H_DINV#15

H_DSTBP#25

H_DSTBN#25

H_DINV#25

H_DSTBP#35

H_DSTBN#35

H_DINV#35

H_ADS#4

H_DRDY#5

H_DEFER#4

H_HITM#4

H_HIT#4

H_LOCK#4

H_BR0#4

H_BNR#4

H_BPRI#4

H_DBSY#5

H_RESET#5 MCH_CLKSEL0 15

SYS_PWROK24,42

U36A

D26

HA3#

D30

HA4#

L23

HA5#

E29

HA6#

B32

HA7#

K23

HA8#

C30

HA9#

C31

HA10#

J25

HA11#

B31

HA12#

E30

HA13#

B33

HA14#

J24

HA15#

F25

HA16#

D34

HA17#

C32

HA18#

F28

HA19#

C34

HA20#

J27

HA21#

G27

HA22#

F29

HA23#

E28

HA24#

H27

HA25#

K24

HA26#

E32

HA27#

F31

HA28#

G30

HA29#

J26

HA30#

G26

HA31#

B29

HREQ0#

J23

HREQ1#

L22

HREQ2#

C29

HREQ3#

J21

HREQ4#

B30

HADSTB0#

D28

HADSTB1#

B7

HCLKP

C7

HCLKN

B19

HDSTBP0#

C19

HDSTBN0#

C17

DINV0#

L19

HDSTBP1#

K19

HDSTBN1#

L17

DINV1#

G9

HDSTBP2#

F9

HDSTBN2#

L14

DINV2#

D12

HDSTBP3#

E12

HDSTBN3#

C15

DINV3#

F27

ADS#

D24

HTRDY#

G24

DRDY#

L21

DEFER#

E23

HITM#

K21

HIT#

E25

HLOCK#

B24

BREQ0#

B28

BNR#

B26

BPRI#

E27

DBSY#

G22

RS0#

C27

RS1#

B27

RS2#

E8

CPURST#

AE14

PWROK#

E24

HDRCOMP

C25

HDSWING

F23

HDVREF

SPRINGDALE_UFCBGA932

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

FSB

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

PROCHOT#

BSEL0

BSEL1

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

B23

E22

B21

D20

B22

D22

B20

C21

E18

E20

B16

D16

B18

B17

E16

D18

G20

F17

E19

F19

J17

L18

G16

G18

F21

F15

E15

E21

J19

G14

E17

K17

J15

L16

J13

F13

F11

E13

K15

G12

G10

L15

E11

K13

J11

H10

G8

E9

B13

E14

B14

B12

B15

D14

C13

B11

D10

C11

E10

B10

C9

B9

D8

B8

L20

L13

L12

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_PROCHOT#

H_D#[0..63] 4

H_PROCHOT# 5,52

MCH_CLKSEL1 15

U36F

AR32

VSS

AR29

VSS

AR27

VSS

AR25

VSS

AR23

VSS

AR20

VSS

AR16

VSS

AR13

VSS

AR11

VSS

AR9

VSS

AN32

VSS

AN30

VSS

AN28

VSS

AN26

VSS

AN24

VSS

AN22

VSS

AN20

VSS

AN18

VSS

AN16

VSS

AN14

VSS

AN12

VSS

AN10

VSS

AM35

VSS

AM29

VSS

AM27

VSS

AM25

VSS

AM23

VSS

AM21

VSS

AM19

VSS

AM17

VSS

AM15

VSS

AM13

VSS

AM11

VSS

AM9

VSS

AL32

VSS

AL1

VSS

AK28

VSS

AK26

VSS

AK24

VSS

AK22

VSS

AK20

VSS

AK18

VSS

AK16

VSS

AK14

VSS

AK12

VSS

AK10

VSS

AK8

VSS

AK3

VSS

AJ35

VSS

AJ32

VSS

AJ9

VSS

AJ4

VSS

AJ1

VSS

AH33

VSS

AH30

VSS

AH24

VSS

AH22

VSS

AH20

VSS

AH18

VSS

AH16

VSS

AH14

VSS

AH12

VSS

AH10

VSS

AH6

VSS

AH3

VSS

AG35

VSS

AG32

VSS

AG28

VSS

AG26

VSS

AG24

VSS

AG22

VSS

AG20

VSS

AG18

VSS

AG16

VSS

AG14

VSS

AG8

VSS

AG4

VSS

AF33

VSS

AF30

VSS

AF25

VSS

AF24

VSS

AF22

VSS

AF20

VSS

AF18

VSS

AF16

VSS

AF14

VSS

AF11

VSS

AF9

VSS

AF6

VSS

AF3

VSS

AE35

VSS

AE32

VSS

AE26

VSS

AE25

VSS

AE13

VSS

AE12

VSS

SPRINGDALE_UFCBGA932

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE11

AE10

AE4

AE1

AD33

AD30

AD28

AD10

AD9

AD8

AD6

AD3

AC35

AC32

AC4

AC1

AB33

AB30

AB28

AB27

AB26

AB10

AB9

AB8

AB6

AB3

AA32

AA4

AA1

Y35

Y33

Y30

Y28

Y27

Y26

Y10

Y9

Y8

Y6

Y3

W32

W18

W17

W4

V33

V30

V28

V27

V26

V19

V17

V10

V9

V8

V6

V3

U32

U19

U18

U4

T35

T33

T30

T28

T27

T26

T10

T9

T8

T6

T3

T1

R32

R4

R1

P33

P30

P28

P27

P26

P9

P8

P6

P3

N35

N32

N4

N1

M33

M30

M28

M27

M26

M6

M3

L35

U36G

L31

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L26

L25

L24

K33

K29

K27

K25

K22

K20

K18

K16

K14

K12

K11

J35

J32

J28

J22

J20

J18

J16

J14

J12

J10

H33

H30

H26

H24

H22

H20

H18

H16

H14

H12

H9

H8

H5

H2

G35

G31

G28

F26

F24

F22

F20

F18

SPRINGDALE_UFCBGA932

F16

F14

F12

F10

F8

F5

F3

F1

E3

E1

D35

D33

D31

D29

D27

D25

D23

D21

D19

D17

D15

D13

D11

D9

D1

C28

C26

C24

C22

C20

C18

C16

C14

C12

C10

C8

C4

A32

A29

A27

A25

A23

A20

A16

A13

A11

A9

A7

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

2

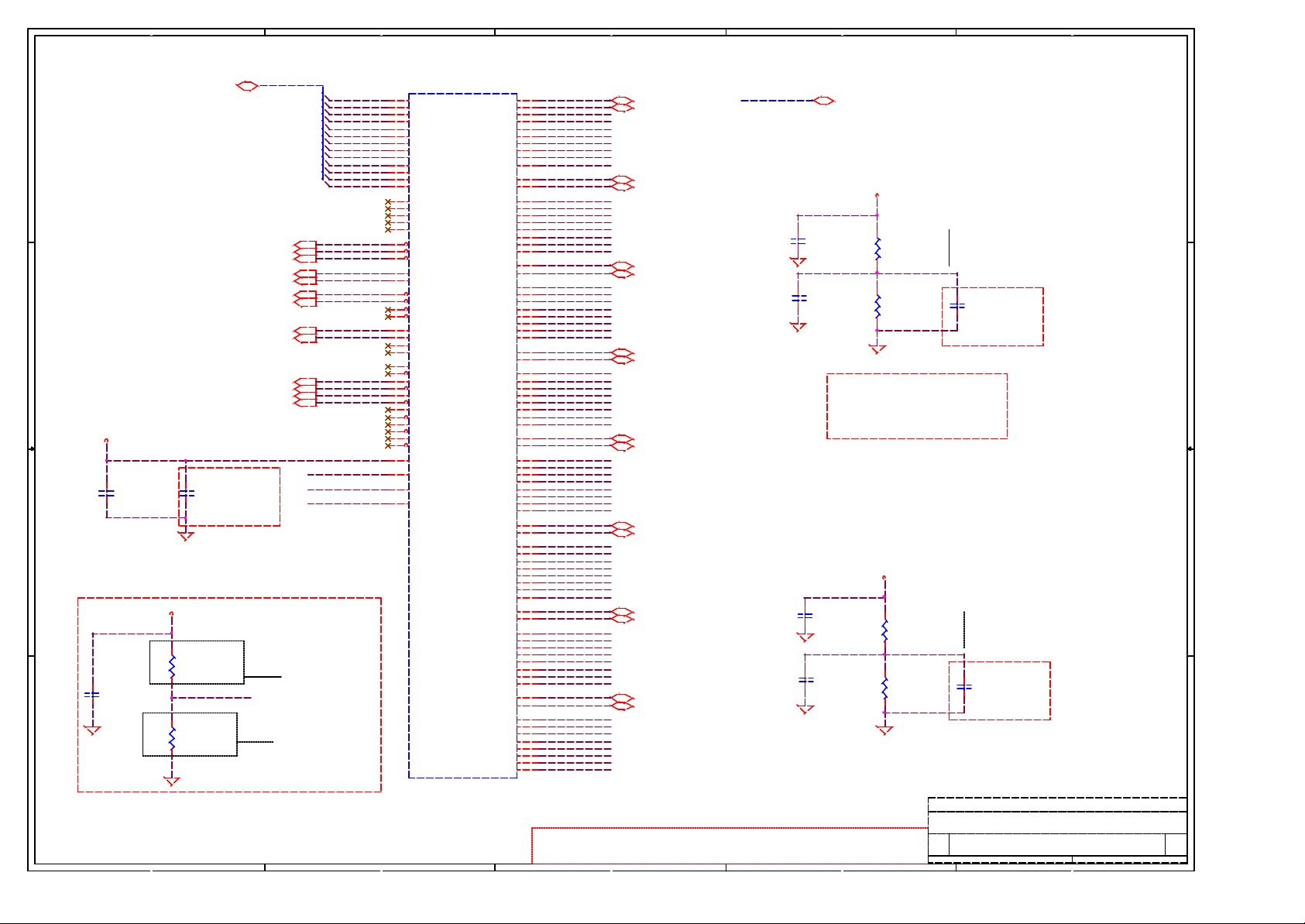

Springdale-Host/GND (1/4)

Size Document Number Rev

B

LA-1841

Date: Sheet of

7 57Thursday, February 20, 2003

1

0.1

5

4

3

2

1

DDRA_SMA[0..12]12,14

D D

C C

+SM_VREF_A

+SM_VREF_A trace width of 12mils and space

12mils(min)

2

1

C528

2.2U_0805_16V4Z

2

1

C522

0.1U_0402_16V4Z

DDRA_SMA[0..12]

DDRA_SWE#12,14

DDRA_SCAS#12,14

DDRA_SRAS#12,14

DDRA_SBS012,14

DDRA_SBS112,14

DDRA_SCS#012,14

DDRA_SCS#112,14

DDRA_CKE012,14

DDRA_CKE112,14

DDRA_CLK112

DDRA_CLK1#12

DDRA_CLK212

DDRA_CLK2#12

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SCS#0

DDRA_SCS#1 DDRA_SDQ18

DDRA_CKE0

DDRA_CKE1

SMXRCOMP

SMXRCOMPVOH

SMXRCOMPVOL

Close to GMCH(E34)

B B

+2.5V

Trace width of 12mils and space

10mils(min)

12

R151

40.2_0603_1%

2

C201

2.2U_0805_16V4Z

1

A A

5

SMXRCOMP

12

R152

40.2_0603_1%

Change to 42.2_1%

Place resistors within

1.0 inch of GMCH (AK9)

Change to 42.2_1%

U36B

AJ34

SMAA_A0

AL33

SMAA_A1

AK29

SMAA_A2

AN31

SMAA_A3

AL30

SMAA_A4

AL26

SMAA_A5

AL28

SMAA_A6

AN25

SMAA_A7

AP26

SMAA_A8

AP24

SMAA_A9

AJ33

SMAA_A10

AN23

SMAA_A11

AN21

SMAA_A12

AL34

SMAB_A1

AM34

SMAB_A2

AP32

SMAB_A3

AP31

SMAB_A4

AM26

SMAB_A5

AB34

SWE_A#

Y34

SCAS_A#

AC33

SRAS_A#

AE33

SBA_A0

AH34

SBA_A1

AA34

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

AL20

SCKE_A0

AN19

SCKE_A1

AM20

SCKE_A2

AP20

SCKE_A3

AK32

SCMDCLK_A0

AK31

SCMDCLK_A0#

AP17

SCMDCLK_A1

AN17

SCMDCLK_A1#

N33

SCMDCLK_A2

N34

SCMDCLK_A2#

AK33

SCMDCLK_A3

AK34

SCMDCLK_A3#

AM16

SCMDCLK_A4

AL16

SCMDCLK_A4#

P31

SCMDCLK_A5

P32

SCMDCLK_A5#

E34

SMVREF_A

AK9

SMXRCOMP

AN9

SMXRCOMPVOH

AL9

SMXRCOMPVOL

SPRINGDALE_UFCBGA932

4

AN11

SDQS_A0

AP12

SDM_A0

AP10

SDQ_A0

AP11

SDQ_A1

AM12

SDQ_A2

AN13

SDQ_A3

AM10

SDQ_A4

AL10

SDQ_A5

AL12

SDQ_A6

AP13

SDQ_A7

AP15

SDQS_A1

AP16

SDM_A1

AP14

SDQ_A8

AM14

SDQ_A9

AL18

SDQ_A10

AP19

SDQ_A11

AL14

SDQ_A12

AN15

SDQ_A13

AP18

SDQ_A14

AM18

SDQ_A15

AP23

SDQS_A2

AM24

SDM_A2

AP22

SDQ_A16

AM22

SDQ_A17

AL24

SDQ_A18

AN27

SDQ_A19

AP21

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_A23

SDQS_A3

SDM_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

AL22

AP25

AP27

AM30

AP30

AP28

AP29

AP33

AM33

AM28

AN29

AM31

AN34

AF34

AF31

AH32

AG34

AF32

AD32

AH31

AG33

AE34

AD34

V34

W33

AC34

AB31

V32

V31

AD31

AB32

U34

U33

M32

M34

T34

T32

K34

K32

T31

P34

L34

L33

H31

H32

J33

H34

E33

F33

K31

J34

G34

F34

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DDR Channel A

DDRA_SDQS0 12,14

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DDRA_SDM0 12,14

DDRA_SDQS1 12,14

DDRA_SDM1 12,14

DDRA_SDQS2 12,14

DDRA_SDM2 12,14

DDRA_SDQS3 12,14

DDRA_SDM3 12,14

DDRA_SDQS4 12,14

DDRA_SDM4 12,14

DDRA_SDQS5 12,14

DDRA_SDM5 12,14

DDRA_SDQS6 12,14

DDRA_SDM6 12,14

DDRA_SDQS7 12,14

DDRA_SDM7 12,14

3

DDRA_SDQ[0..63]

DDRA_SDQ[0..63] 12,14

2

C523

2.2U_0805_16V4Z

1

1

C533

1U_0603_10V6K

2

2

C217

2.2U_0805_16V4Z

1

1

C220

1U_0603_10V6K

2

+2.5V

Trace width of 12mils and space

10mils(min)

12

R390

10K_0603_1%

SMXRCOMPVOH

12

R391

30.9K_0603_1%

*

*

Change to 31.12K

Follow Intel design guide

R1.11(12474) page124,125

+2.5V

Trace width of 12mils and space

10mils(min)

12

R153

30.9K_0603_1%

*

SMXRCOMPVOL

12

R154

10K_0603_1%

Title

Size Document Number Rev

B

2

Date: Sheet of

1

C196

0.01U_0402_16V7K

2

Close to Pin AN9

Close to GMCH <1"

1

C190

0.01U_0402_16V7K

2

Close to Pin AL9

Close to GMCH <1"

Compal Electronics, Inc.

Springdale-DDR Interface-A(2/5)

LA-1841

1

8 57Thursday, February 20, 2003

0.1

5

4

3

2

1

DDRB_SMA[0..12]13,14

D D

C C

SM_VREF_B and SM_VREF_A

are connected inside GMCH.

+2.5V

2

12

R392

150_0603_1%

12

B B

R396

150_0603_1%

1

2

1

C539

2.2U_0805_16V4Z

C547

2.2U_0805_16V4Z

DDRB_SMA[0..12]

DDRB_SWE#13,14

DDRB_SCAS#13,14

DDRB_SRAS#13,14

DDRB_SBS013,14

DDRB_SBS113,14

DDRB_SCS#013,14

DDRB_SCS#113,14

DDRB_CKE013,14

DDRB_CKE113,14

DDRB_CLK113

DDRB_CLK1#13

DDRB_CLK213

DDRB_CLK2#13

+SM_VREF_B

+SM_VREF_B trace width of

12mils and space

12mils(min)

2

C200

0.1U_0402_16V4Z

1

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SCS#0

DDRB_SCS#1

DDRB_CKE0

DDRB_CKE1

SMYRCOMP

SMYRCOMPVOH

SMYRCOMPVOL

Close to GMCH(AP9)

+2.5V

2

12

R399

Change to 42.2_1%

Change to 42.2_1%

A A

40.2_0603_1%

SMYRCOMP

12

R400

40.2_0603_1%

C553

2.2U_0805_16V4Z

1

Trace width of 12mils

and space 10mils(min)

Place resistors within

1.0 inch of GMCH (AA33)

U36C

AG31

SMAA_B0

AJ31

SMAA_B1

AD27

SMAA_B2

AE24

SMAA_B3

AK27

SMAA_B4

AG25

SMAA_B5

AL25

SMAA_B6

AF21

SMAA_B7

AL23

SMAA_B8

AJ22

SMAA_B9

AF29

SMAA_B10

AL21

SMAA_B11

AJ20

SMAA_B12

AE27

SMAB_B1

AD26

SMAB_B2

AL29

SMAB_B3

AL27

SMAB_B4

AE23

SMAB_B5

W27

SWE_B#

W31

SCAS_B#

W26

SRAS_B#

Y25

SBA_B0

AA25

SBA_B1

U26

SCS_B0#

T29

SCS_B1#

V25

SCS_B2#

W25

SCS_B3#

AK19

SCKE_B0

AF19

SCKE_B1

AG19

SCKE_B2

AE18

SCKE_B3

AG29

SCMDCLK_B0

AG30

SCMDCLK_B0#

AF17

SCMDCLK_B1

AG17

SCMDCLK_B1#

N27

SCMDCLK_B2

N26

SCMDCLK_B2#

AJ30

SCMDCLK_B3

AH29

SCMDCLK_B3#

AK15

SCMDCLK_B4

AL15

SCMDCLK_B4#

N31

SCMDCLK_B5

N30

SCMDCLK_B5#

AP9

SMVREF_B

AA33

SMYRCOMP

R34

SMYRCOMPVOH

R33

SMYRCOMPVOL

SPRINGDALE_UFCBGA932

AF15

SDQS_B0

AG11

SDM_B0

AJ10

SDQ_B0

AE15

SDQ_B1

AL11

SDQ_B2

AE16

SDQ_B3

AL8

SDQ_B4

AF12

SDQ_B5

AK11

SDQ_B6

AG12

SDQ_B7

AG13

SDQS_B1

AG15

SDM_B1

AE17

SDQ_B8

AL13

SDQ_B9

AK17

SDQ_B10

AL17

SDQ_B11

AK13

SDQ_B12

AJ14

SDQ_B13

AJ16

SDQ_B14

AJ18

SDQ_B15

AG21

SDQS_B2

AE21

SDM_B2

AE19

SDQ_B16

AE20

SDQ_B17

AG23

SDQ_B18

AK23

SDQ_B19

SDQ_B20

SDQ_B21

SDQ_B22

SDQ_B23

SDQS_B3

SDM_B3

SDQ_B24

SDQ_B25

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_B30

SDQ_B31

SDQS_B4

SDM_B4

SDQ_B32

SDQ_B33

SDQ_B34

SDQ_B35

SDQ_B36

SDQ_B37

SDQ_B38

SDQ_B39

SDQS_B5

SDM_B5

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQS_B6

SDM_B6

SDQ_B48

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQS_B7

SDM_B7

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

SDQ_B63

AL19

AK21

AJ24

AE22

AH27

AJ28

AK25

AH26

AG27

AF27

AJ26

AJ27

AD25

AF28

AD29

AC31

AE30

AC27

AC30

Y29

AE31

AB29

AA26

AA27

U30

U31

AA30

W30

U27

T25

AA31

V29

U25

R27

L27

M29

P29

R30

K28

L30

R31

R26

P25

L32

J30

J31

K30

H29

F32

G33

N25

M25

J29

G32

DDR Channel B

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

DDRB_SDQS0 13,14

DDRB_SDM0 13,14

DDRB_SDQS1 13,14

DDRB_SDM1 13,14

DDRB_SDQS2 13,14

DDRB_SDM2 13,14

DDRB_SDQS3 13,14

DDRB_SDM3 13,14

DDRB_SDQS4 13,14

DDRB_SDM4 13,14

DDRB_SDQS5 13,14

DDRB_SDM5 13,14

DDRB_SDQS6 13,14

DDRB_SDM6 13,14

DDRB_SDQS7 13,14

DDRB_SDM7 13,14

DDRB_SDQ[0..63]

2

C541

2.2U_0805_16V4Z

1

1

C546

1U_0603_10V6K

2

2

C219

2.2U_0805_16V4Z

1

1

C223

1U_0603_10V6K

2

DDRB_SDQ[0..63] 13,14

+2.5V

Trace width of 12mils and space

10mils(min)

12

R394

10K_0603_1%

SMYRCOMPVOH

12

R398

30.9K_0603_1%

1

C213

0.01U_0402_50V7K

2

Close to Pin R14

Close to GMCH <1"

+2.5V

Trace width of 12mils and space

10mils(min)

12

R163

30.9K_0603_1%

SMYRCOMPVOL

12

R164

10K_0603_1%

1

C211

0.01U_0402_50V7K

2

Close to Pin R33

Close to GMCH <1"

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Springdale-DDR Interface-B(3/5)

Size Document Number Rev

B

LA-1841

Date: Sheet of

9 57Thursday, February 20, 2003

1

0.1

5

4

3

2

1

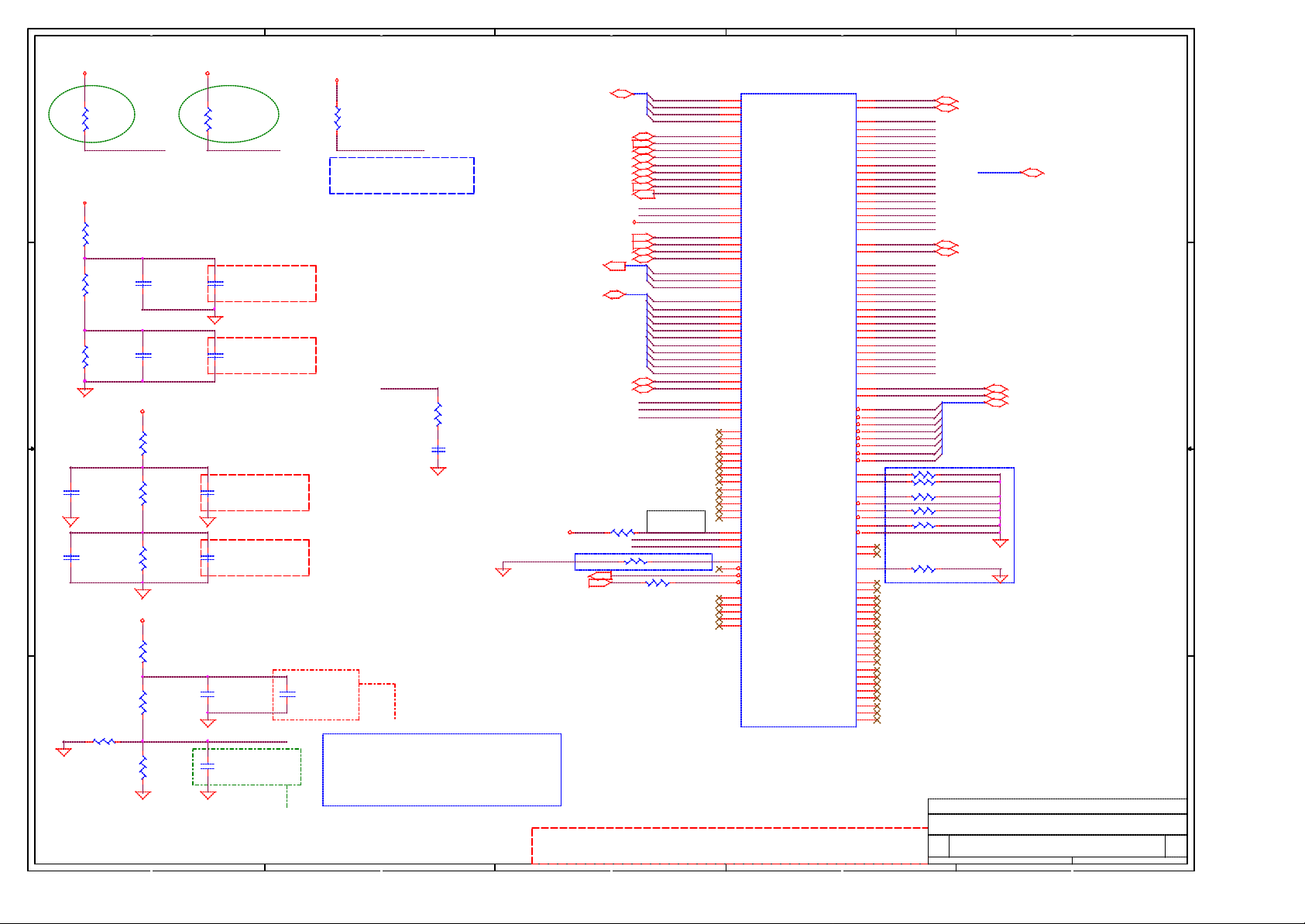

+1.5VS

Change to 43.2_1%

12

R123

43_0402_5%

D D

C C

B B

A A

GRCOMP

+1.5VS

12

R353

226_0603_1%

HI_SWING_MCH

12

R368

147_0603_1%

HI_VREF_MCH

12

R372

113_0603_1%

1

C147

0.1U_0402_16V4Z

2

1

C166

0.1U_0402_16V4Z

2

1 2

R56

33.2_0603_1%

1

2

1

2

+1.5VS

12

CI_SWING_GMCH

12

12

+1.5VS

12

12

12

+1.5VS

Change to 52.3_1%

12

R116

51.1_0603_1%

HI_RCOMP_MCH

Note:

HI_SWING_MCH, HI_VREF_MCH

trace width of 10mils and

space 7mils

Close to GMCH(AE3)

C499

0.1U_0402_16V4Z

C500

0.1U_0402_16V4Z

R122

226_0603_1%

R127

147_0603_1%

CI_VREF_GMCH

R130

113_0603_1%

1

C498

0.01U_0402_16V7K

2

Close to GMCH ball <250mils

Close to GMCH(AE2)

1

C503

0.01U_0402_16V7K

2

Close to GMCH ball <250mils

Note:

CI_SWING_MCH, CI_VREF_MCH

trace width of 10mils and

space 20mils

0.8V

Close to GMCH(AF2)

1

C155

0.01U_0402_16V7K

2

Close to GMCH ball <250mils

0.35V

Close to GMCH(AF4)

1

C165

0.01U_0402_16V7K

2

Close to GMCH ball <250mils

R31

60.4_0603_1%

AGP_SWING

R32

39.2_0603_1%

R55

100_0603_1%

Close GMCH ball (AD2)

less than 250mils

5

Close GMCH ball (AC3) less than 250mils

1

C9

0.1U_0402_16V4Z

2

+AGP_VREF

1

C127

0.01U_0402_16V7K

2

+1.5VS

?

R121

@10K_0402_5%

1 2

AGP_PAR

1: External AGP

0: Internal Graphics

CLK_MCH_66M

12

R337

@10_0402_5%

1

C486

@10P_0402_50V8K

2

AGP_C/BE#[0..3]16

AGP_FRAME#16

CLK_MCH_66M15

AGP_DEVSEL#16

AGP_IRDY#16

AGP_TRDY#16

AGP_STOP#16

AGP_PAR16

AGP_REQ#16

AGP_GNT#16

+AGP_VREF

AGP_RBF#16

AGP_WBF#16

AGP_DBIHI16

AGP_DBILO16

AGP_ST[0..2]16

HUB_HL[0..10]23

HUB_HLSTRF23

HUB_HLSTRS23

change to 52.3_1%

R375 54.9_0603_1%

+1.5VS

R92 0_0402_5%

ICH_SYNC#24

PCIRST#23,26,27,29,30,36,39

1

C113

0.01U_0402_16V7K

2

Follow Springdale Chipset Platform Design guide Rev1.11(12474)

Note:

Springdale Customer Schematic R1.2 page18

AGP_SWING only had 0.1u cap ; But Springdale

Chipset Platform Design guide Rev1.11(12474)

page138 had a 0.01uf cap. need confirm with

Intel.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1 2

R134 0_0402_5%

3

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

CLK_MCH_66M AGP_AD3

AGP_PAR

GRCOMP

AGP_SWING

+AGP_VREF

AGP_ST0

AGP_ST1

AGP_ST2

HUB_HL0

HUB_HL1

HUB_HL2

HUB_HL3

HUB_HL4

HUB_HL5

HUB_HL6

HUB_HL7

HUB_HL8

HUB_HL9

HUB_HL10

HI_RCOMP_MCH

HI_SWING_MCH

HI_VREF_MCH

CI_SWING_GMCH

CI_VREF_GMCH

12

12

U36D

Y7

GCBE0

W5

GCBE1

AA3

GCBE2

U2

GCBE3

U6

GFRAME

H4

GCLKIN

AB4

GDEVSEL

V11

GIRDY

AB5

GTRDY

W11

GSTOP

AB2

GPAR/ADD_DETECT

N6

GREQ

M7

GGNT

AC2

GRCOMP/DVOBCGCOMP

AC3

GVSWING

AD2

GVREF

R10

GRBF

R9

GWBF

M4

DBI_HI

M5

DBI_LO

N3

GST0

N5

GST1

N2

GST2

AF5

HI0

AG3

HI1

AK2

HI2

AG5

AD11

AC10

AG7

AG6

AG2

AG10

AG9

AN35

AP34

HUB

HI3

AK5

HI4

AL3

HI5

AL2

HI6

AL4

HI7

AJ2

HI8

AH2

HI9

AJ3

HI10

AH5

HISTRF

AH4

HISTRS

AD4

HI_RCOMP

AE3

HI_SWING

AE2

HI_VREF

AK7

CI0

AH7

CI1

CI2

AF7

CI3

AD7

CI4

CSA

CI5

AF8

CI6

CI7

AE9

CI8

AH9

CI9

CI10

AJ6

CISTRF

AJ5

CISTRS

CI_RCOMP

AF2

CI_SWING

AF4

CI_VREF

G4

DREFCLK

AP8

EXTTS#

AJ8

ICH_SYNC#

AK4

RSTIN#

RESERVED_1

RESERVED_2

RESERVED_3

RESERVED_4

AR1

RESERVED_5

SPRINGDALE_UFCBGA932

AGP

GADSTBF0

GADSTBS0#

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GADSTBF1

GADSTBS1#

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GSBSTBF

GSBSTBS#

GSBA0#

GSBA1#

GSBA2#

GSBA3#

GSBA4#

GSBA5#

GSBA6#

GSBA7#

DDCA_DATA

DDCA_CLK

RED#

GREEN

GREEN#

VGA

BLUE

BLUE#

HSYNC

VSYNC

REFSET

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

2

RED

AC6

AC5

AGP_AD0

AE6

AGP_AD1

AC11

AGP_AD2

AD5

AE5

AGP_AD4

AA10

AGP_AD5

AC9

AGP_AD6

AB11

AGP_AD7

AB7

AGP_AD8

AA9

AGP_AD9

AA6

AGP_AD10

AA5

AGP_AD11

W10

AGP_AD12

AA11

AGP_AD13

W6

AGP_AD14

W9

AGP_AD15

V7

V4

V5

AGP_AD16

AA2

AGP_AD17

Y4

AGP_AD18

Y2

AGP_AD19

W2

AGP_AD20

Y5

AGP_AD21

V2

AGP_AD22

W3

AGP_AD23

U3

AGP_AD24

T2

AGP_AD25

T4

AGP_AD26

T5

AGP_AD27

R2

AGP_AD28

P2

AGP_AD29

P5

AGP_AD30

P4

AGP_AD31

M2

U11

T11

AGP_SBA0

R6

AGP_SBA1

P7

AGP_SBA2

R3

AGP_SBA3

R5

AGP_SBA4

U9

AGP_SBA5

U10

AGP_SBA6

U5

AGP_SBA7

T7

R88 0_0402_5%12

H3

R84 0_0402_5%12

F2

R91 0_0402_5%12

F4

E4

R101 0_0402_5%12

H6

G5

R104 0_0402_5%

H7

G6

G3

E2

R322 0_0402_5%12

D2

A3

A33

A35

Analog RGB/CRT guidelines for Springdale-P

AF13

AF23

AJ12

AN1

AP2

AR3

AR33

AR35

B2

B25

B34

C1

C23

C35

E26

M31

R25

AGP_AD_STBF0 16

AGP_AD_STBS0 16

AGP_AD[0..31] 16

AGP_AD_STBF1 16

AGP_AD_STBS1 16

AGP_SB_STBF 16

AGP_SB_STBS 16

AGP_SBA[0..7] 16

12

Title

Springdale-AGP/HUB/VGA/CSA (4/5)

Size Document Number Rev

B

LA-1841

Date: Sheet of

10 57Thursday, February 20, 2003

1

0.1

5

Note:

Placed less than 100 mils from ball

Route to GMCH ball without via

D D

1

C490

0.47U_0603_16V7K

2

2

C535

0.1U_0402_10V6K

1

C C

C548

0.1U_0402_10V6K

12

C552 0.22U_0603_10V7K

C520

0.47U_0603_16V7K

12

C532 0.22U_0603_10V7K

C163

Trace 14mils

B B

Note:

Placed less than 100 mils from ball

Route to GMCH ball without via

A A

0.1U_0402_10V6K

12

12

C168 0.1U_0402_10V6K

R321 0_0402_5%12

12

R316 0_0402_5%

1 2

C242 0.1U_0402_10V6K

VTT_DCAP1

VTT_DCAP2

1

C496

0.47U_0603_16V7K

2

+VTT_GMCH

+2.5V

VCC_DDR_DCAP5

12

VCC_DDR_DCAP4

VCC_DDR_DCAP1

12

VCC_AGP_DCAP2

+3VS

+1.5VS

VTT_DCAP3

VCCA_FSB

VCCA_DPLL

VCCA_DAC

VCC_DDR_DCAP2 VCCA_FSB1 VCCA_FSB

VCCA1P5_DDR_SM

(1A)

A15

A21

AA35

AL6

AL7

AM1

AM2

AM3

AM5

AM6

AM7

AM8

AN2

AN4

AN5

AN6

AN7

AN8

AP3

AP4

AP5

AP6

AP7

AR15

AR21

AR31

*

AR4

AR5

AR7

E35

R35

G1

G2

AG1

Y11

A31

AL35

AB25

AC25

AC26

Decoupling Reference Document:

Springdale Chipset Platform Design guide Rev1.11

(12474)page246,248

Decoupling Reference Document:

Springdale Customer Schematic R1.2 page84

4

U36E

VTT

VTT

A4

VTT

A5

VTT

A6

VTT

B5

VTT

B6

VTT

C5

VTT

C6

VTT

D5

VTT

D6

VTT

D7

VTT

E6

VTT

E7

VTT

F7

VTT

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DAC

VCC_DAC

VCCA_AGP

VCCA_AGP

VCCA_FSB

B4

VCCA_FSB

B3

VCCA_DPLL

C2

VCCA_DAC

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

SPRINGDALE_UFCBGA932

POWER

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VSSA_DAC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J6

J7

J8

J9

K6

K7

K8

K9

L6

L7

L9

L10

L11

M8

M9

M10

M11

N9

N10

N11

P10

P11

R11

T16

T17

T18

T19

T20

U16

U17

U20

V16

V18

V20

W16

W19

W20

Y16

Y17

Y18

Y19

Y20

J1

J2

J3

J4

J5

K2

K3

K4

K5

L1

L2

L3

L4

L5

VCC_AGP_DCAP1

Y1

D3

+1.5VS

3

+2.5V

1

C174

22U_1206_10V4Z

2

+2.5V

1

C189

0.1U_0402_10V6K

2

+1.5VS

1

C171

0.1U_0402_10V6K

2

+1.5VS

1

+

C72

470U_D4_2.5VM

2

2

C186

4.7U_0805_6.3V6K

1

1

C185

0.1U_0402_10V6K

2

1

C112

0.1U_0402_10V6K

2

2

C157

4.7U_0805_6.3V6K

1

1

C169

0.1U_0402_10V6K

2

1

C222

0.1U_0402_10V6K

2

1

C135

0.1U_0402_10V6K

2

C156

10U_1206_16V4Z

Place at the output of the 1.5V VR

+VTT_GMCH +2.5V

1

C92

0.1U_0402_10V6K

2

Place near GMCH

1 2

C117

0.1U_0402_10V6K

+1.5VS

1

C126

0.1U_0402_10V6K

2

Place near ball

Y11,routing trace

from cap to ball

Note: Please change to 0.82uH, DC current

of 30mA parts and close to cap

+1.5VS

12

R315

0_0603_5%

Note: Please change to 1uH(0.54uH-D-IN), DC current

of 1000mA parts and close to cap

Trace 50mils

Trace 35mils (under GMCH ball field)

+1.5VS

VCCA_DDR VCCA1P5_DDR_SM

12

R144

0_0603_5%

1

C238

0.1U_0402_10V6K

2

+1.5VS

1

C175

0.1U_0402_10V6K

2

1

C125

0.1U_0402_10V6K

2

+VTT_GMCH

1

+

C28

470U_D4_2.5VM

2

L21

1 2

LQG21F4R7N00_0805

L16

1 2

LQG21F4R7N00_0805

2

1

C191

0.1U_0402_10V6K

2

1

C99

0.1U_0402_10V6K

2

1

C106

0.1U_0402_10V6K

2

2

C70

0.1U_0402_16V4Z

1

1

C183

0.1U_0402_10V6K

2

Place near GMCH

Trace 14milsTrace 14mils

12

C32

+

150U_D2_6.3VM

Trace 35mils

(1A)(1A)

1

C197

22U_1210_6.3V6M

2

1

C198

0.1U_0402_10V6K

2

1

C181

0.1U_0402_10V6K

2

2

C47

4.7U_0805_6.3V6K

1

1

C172

0.1U_0402_10V6K

2

1

C167

0.1U_0402_10V6K

2

2

1

2

C475

0.1U_0402_16V4Z

1

Close to GMCH

2

C212

0.1U_0402_16V4Z

1

Close to GMCH

1

C195

0.1U_0402_10V6K

2

1

C143

0.1U_0402_10V6K

2

C60

4.7U_0805_6.3V6K

1

1

C199

0.1U_0402_10V6K

2

1

C184

0.1U_0402_10V6K

2

1

C42

1U_0603_6.3V6M

2

1

C26

0.47U_0603_16V7K

2

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

B

Date: Sheet of

Springdale-Decoupling (5/5)

LA-1841

1

11 57Thursday, February 20, 2003

0.1

5

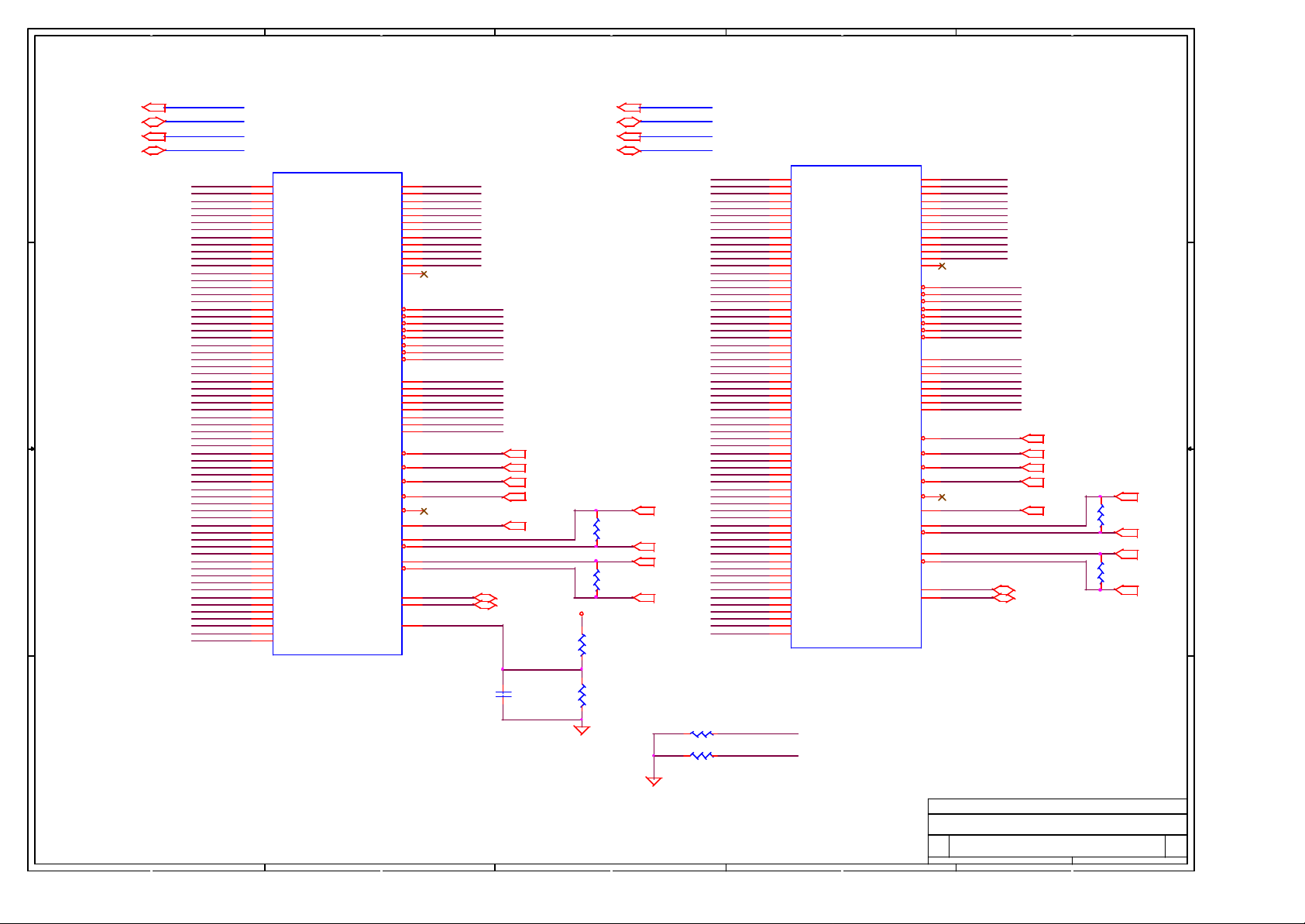

D D

DDRA_CLK18

DDRA_CLK1#8

C C

DDRA_CKE18,14

DDRA_SBS08,14

DDRA_SWE#8,14

DDRA_SCS#08,14

B B

A A

ICH_SMB_DATA13,15,23

ICH_SMB_CLK13,15,23

5

+2.5V

JP26

1

VREF

3

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQS0

DDRA_SDQ6 DDRA_SDQ7

DDRA_SDQ2

DDRA_SDQ12

DDRA_SDQ8

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ15

DDRA_SDQ20

DDRA_SDQ16

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQS3

DDRA_SDQ30

DDRA_SDQ27

DDRA_CKE1

DDRA_SMA12

DDRA_SMA9

DDRA_SMA7

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_SMA10

DDRA_SBS0

DDRA_SWE#

DDRA_SCS#0

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ44

DDRA_SDQ41 DDRA_SDQ45

DDRA_SDQS5

DDRA_SDQ43

DDRA_SDQ46

DDRA_SDQ48

DDRA_SDQ53

DDRA_SDQS6

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQS7

DDRA_SDQ62

DDRA_SDQ59

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169

DQS6

171

DQ50

173

VSS

175

DQ51

177

DQ56

179

VDD

181

DQ57

183

DQS7

185

VSS

187

DQ58

189

DQ59

191

VDD

193

SDA

195

SCL

197

VDD_SPD

199

VDD_ID

KEYLINK_5762-3-111

4

4

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/RESET#

VSS

VSS

VDD

VDD

CKE0

DU/BA2

A11

A8

VSS

A6

A4

A2

A0

VDD

BA1

RAS#

CAS#

S1#

DU

VSS

DQ36

DQ37

VDD

DM4

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1#

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

DU

H = 5.2mm

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

+2.5V

DDRA_SDQ5

DDRA_SDQ4

DDRA_SDM0

DDRA_SDQ3

DDRA_SDQ9

DDRA_SDQ13

DDRA_SDM1

DDRA_SDQ14

DDRA_SDQ11

DDRA_SDQ21

DDRA_SDQ17

DDRA_SDM2

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDM3

DDRA_SDQ26

DDRA_SDQ31

DDRA_CKE0

DDRA_SMA11

DDRA_SMA8

DDRA_SMA6

DDRA_SMA4

DDRA_SMA2

DDRA_SMA0

DDRA_SBS1

DDRA_SRAS#

DDRA_SCAS#

DDRA_SCS#1

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDM4

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDM5

DDRA_SDQ42

DDRA_SDQ47

DDRA_SDQ49

DDRA_SDQ52

DDRA_SDM6

DDRA_SDQ51

DDRA_SDQ50

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDM7

DDRA_SDQ63

DDRA_SDQ58

3

DDRA_VREF trace width of

12mils and space 12mils(min)

DDRA_VREF

1

C305

0.1U_0402_16V4Z

2

Close to SO-DIMM

+2.5V

1

C310

0.1U_0402_10V6K

2

DDRA_CKE0 8,14

DDRA_SBS1 8,14

DDRA_SRAS# 8,14

DDRA_SCAS# 8,14

DDRA_SCS#1 8,14

DDRA_CLK2# 8

DDRA_CLK2 8

+2.5V

+2.5V

1

C331

22U_1206_10V4Z

2

1

C335

0.1U_0402_10V6K

2

12

R204

75_0603_1%

12

R203

75_0603_1%

System Memory Decoupling caps

1

2

1

2

Decoupling Reference Document:

Springdale Customer Schematic R1.2 page22

each Channel(two DIMMs) requirement 22uF*1 ; 0.1uF*14

Decoupling Reference Document:

Springdale Chipset Platform Design guide Rev1.11

(12474)pag 271 each DIMM(two) requirement 0.1uF*42

2

C314

0.1U_0402_10V6K

C334

0.1U_0402_10V6K

1

2

1

2

SO-DIMM 0

REVERSE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

3

2

C339

0.1U_0402_10V6K

C308

0.1U_0402_10V6K

1

DDRA_SDQ[0..63]8,14

D DRA_SDQS[0..7]8,14

DDRA_SMA[0..12]8,14

DDRA_SDM[0..7]8,14

1

C312

0.1U_0402_10V6K

2

1

C333

0.1U_0402_10V6K

2

Title

Size Document Number Rev

Date: Sheet of

DDRA_SDQ[0..63]

DDRA_SDQS[0..7]

DDRA_SMA[0..12]

DDRA_SDM[0..7]

1

C337

0.1U_0402_10V6K

2

1

C307

0.1U_0402_10V6K

2

1

C311

0.1U_0402_10V6K

2

1

C332

0.1U_0402_10V6K

2

Compal Electronics, Inc.

DDR-SODIMM SLOT1

LA-1841

1

1

C336

0.1U_0402_10V6K

2

1

C306

0.1U_0402_10V6K

2

12 57Thursday, February 20, 2003

0.1

5

4

3

2

1

JP24

1

VREF

3

DDRB_SDQ4

DDRB_SDQ0

DDRB_SDQS0

DDRB_SDQ7

D D

DDRB_CLK19

DDRB_CLK1#9

C C

DDRB_CKE19,14

DDRB_SBS09,14

DDRB_SWE#9,14

DDRB_SCS#09,14

B B

A A

ICH_SMB_DATA12,15,23

ICH_SMB_CLK12,15,23

DDRB_SDQ5

DDRB_SDQ9

DDRB_SDQ12

DDRB_SDQS1

DDRB_SDQ10

DDRB_SDQ14

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQS2

DDRB_SDQ22

DDRB_SDQ17

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQS3

DDRB_SDQ26

DDRB_SDQ30

DDRB_CKE1

DDRB_SMA12

DDRB_SMA9

DDRB_SMA7

DDRB_SMA5

DDRB_SMA3

DDRB_SMA1

DDRB_SMA10

DDRB_SBS0

DDRB_SWE#

DDRB_SCS#0

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQS4

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ40

DDRB_SDQ44

DDRB_SDQS5

DDRB_SDQ43 DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ52

DDRB_SDQ49

DDRB_SDQS6

DDRB_SDQ55

DDRB_SDQ60

DDRB_SDQ56

DDRB_SDQS7

DDRB_SDQ58

DDRB_SDQ57

+3VS

5

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135

DQ34

137

VSS

139

DQ35

141

DQ40

143

VDD

145

DQ41

147

DQS5

149

VSS

151

DQ42

153

DQ43

155

VDD

157

VDD

159

VSS

161

VSS

163

DQ48

165

DQ49

167

VDD

169