Toshiba 20VL44 Schematic

TOSHIBA

SERVICE MANUAL

COLOUR TELEVISION

20VL44

PRINTED IN UK. 2003 C

CONTENTS

PAGES

Safety instructions

Technical specifications

Panel Specification

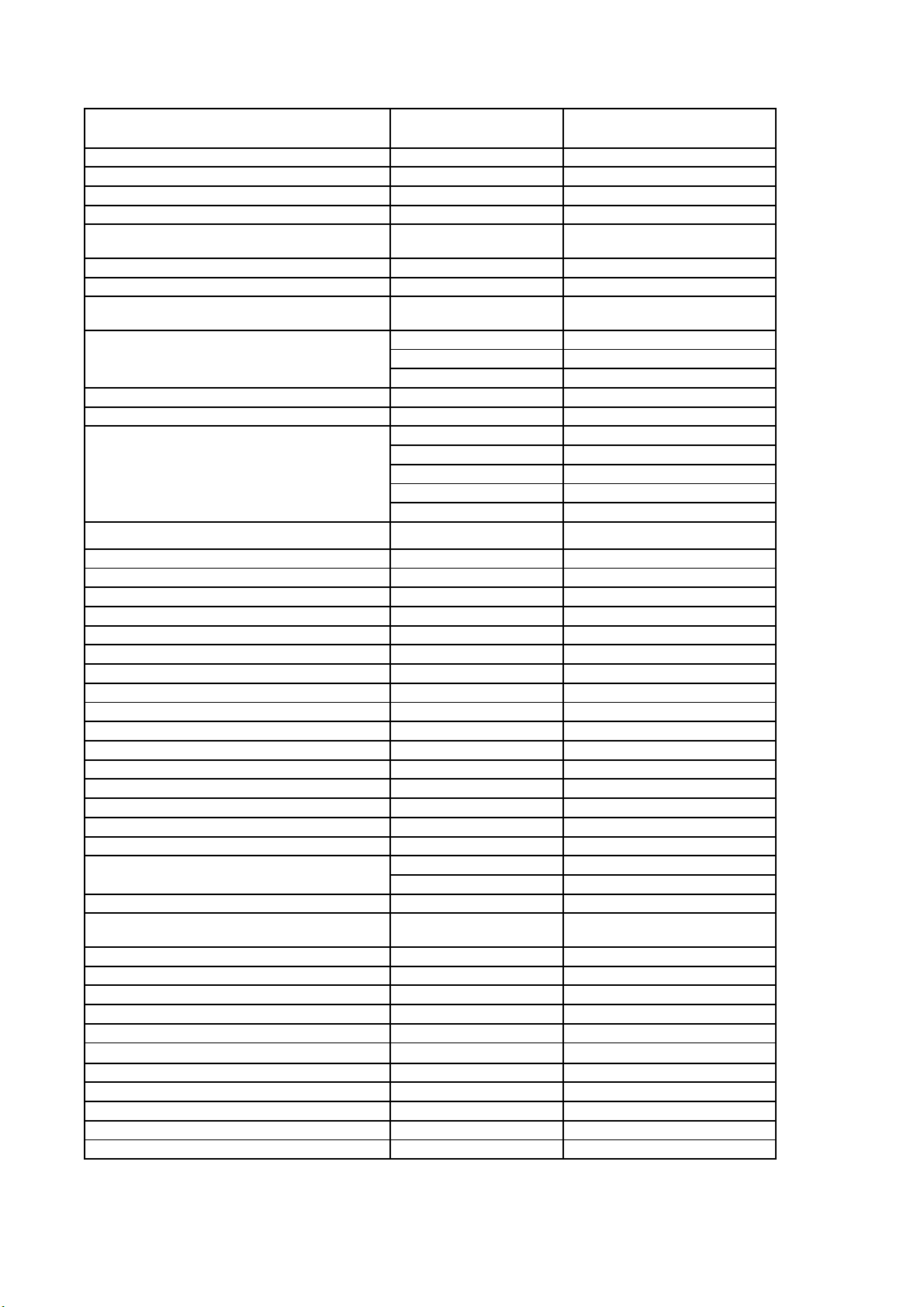

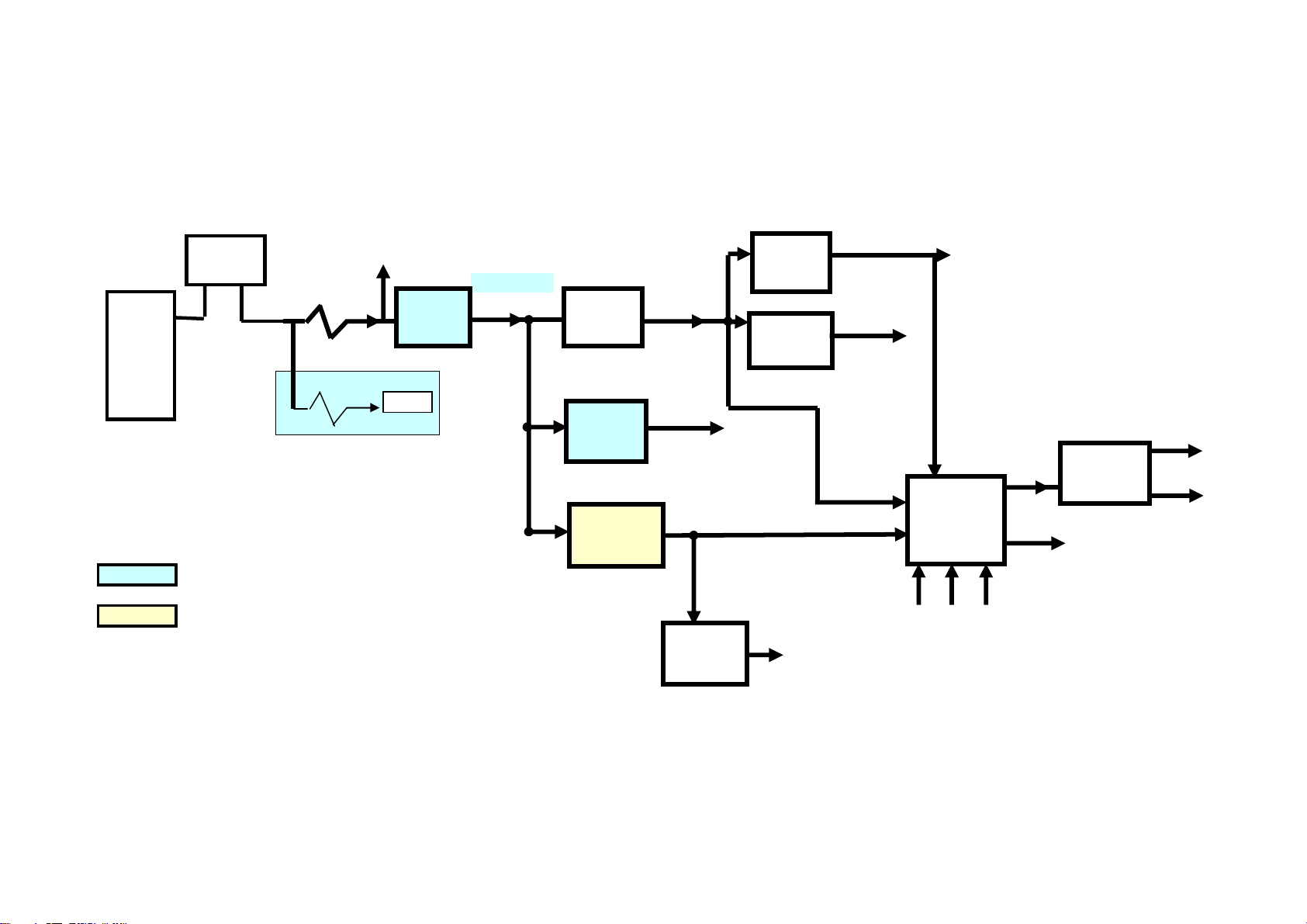

Chassis block diagram

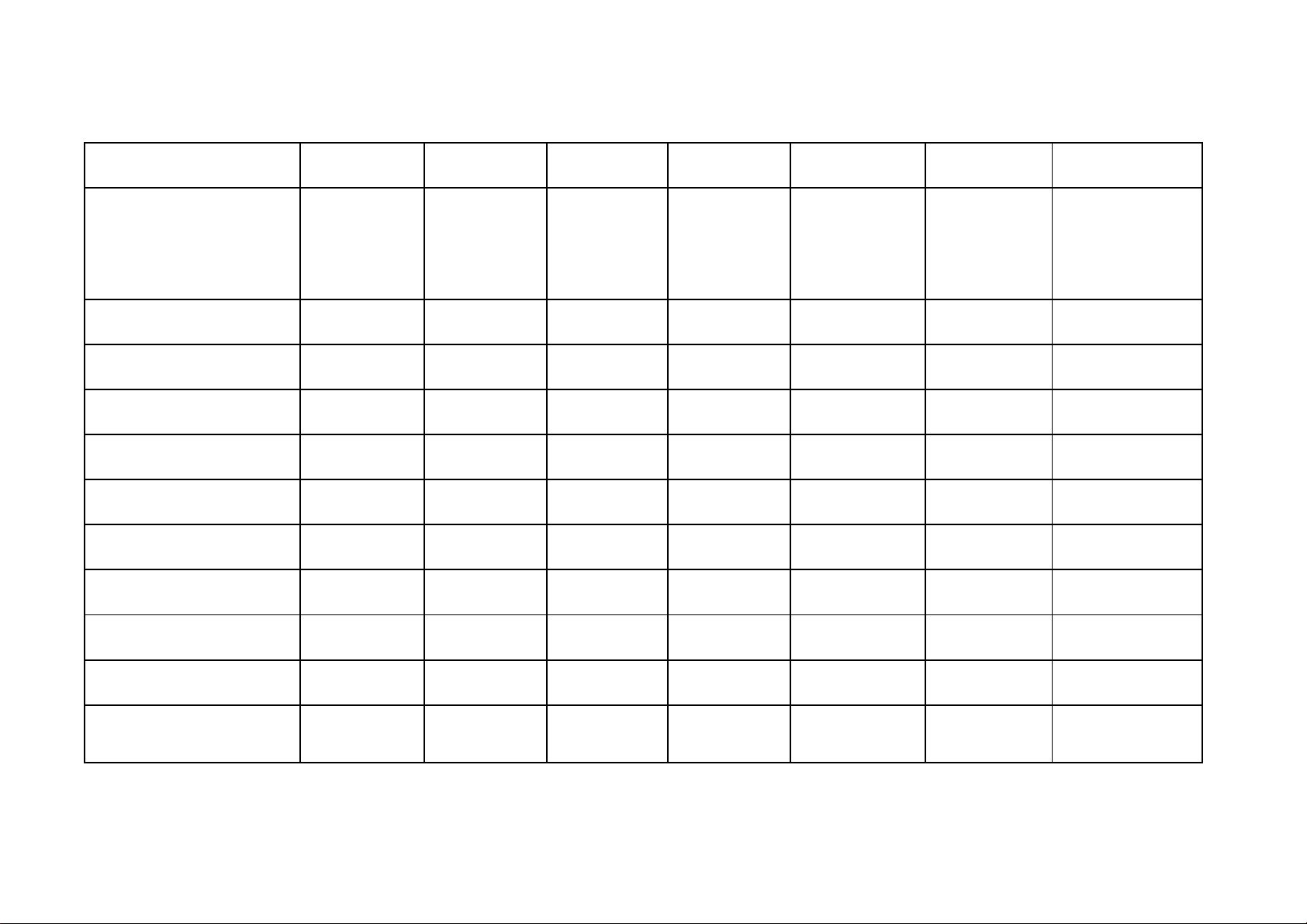

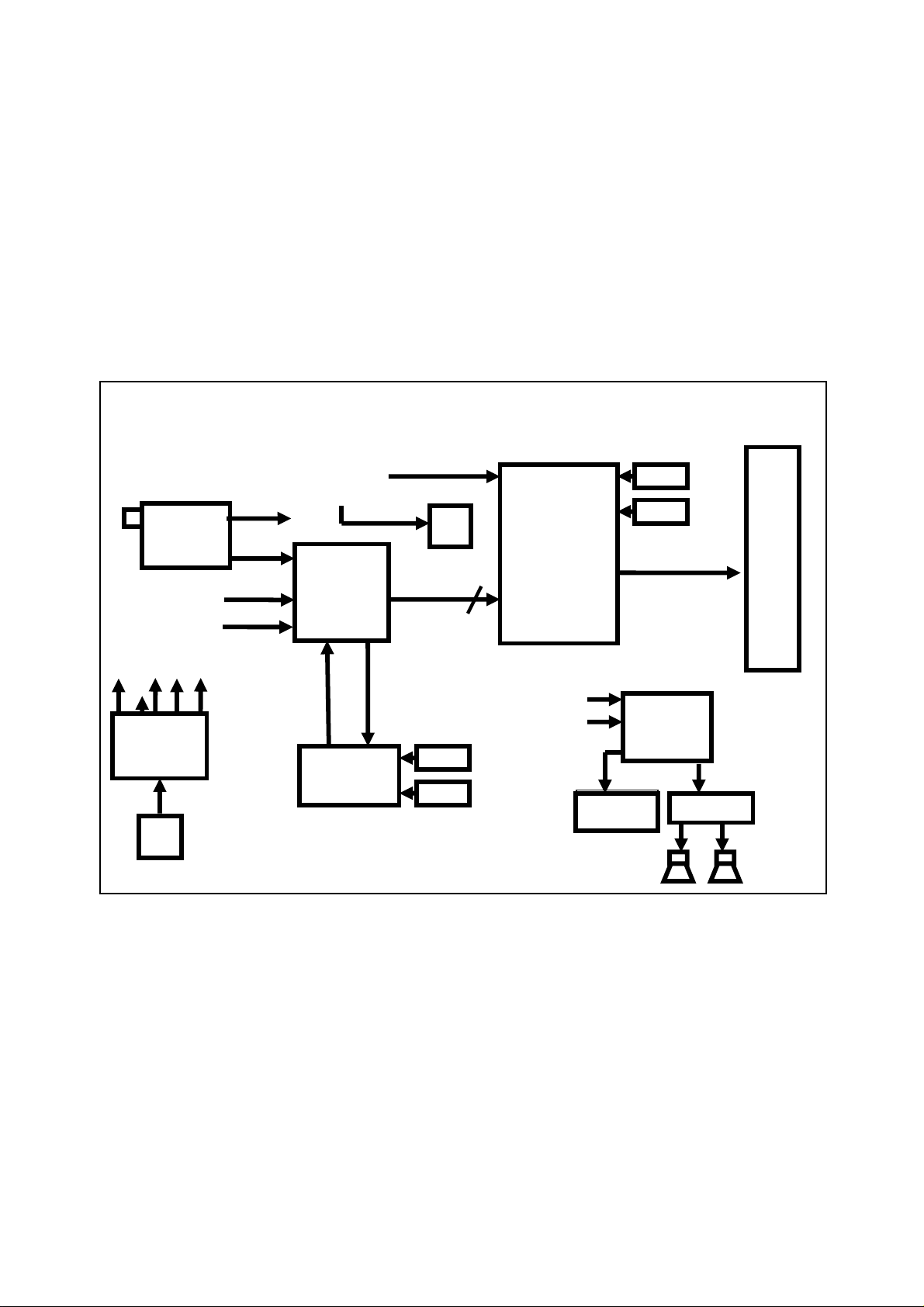

Scaler block diagram

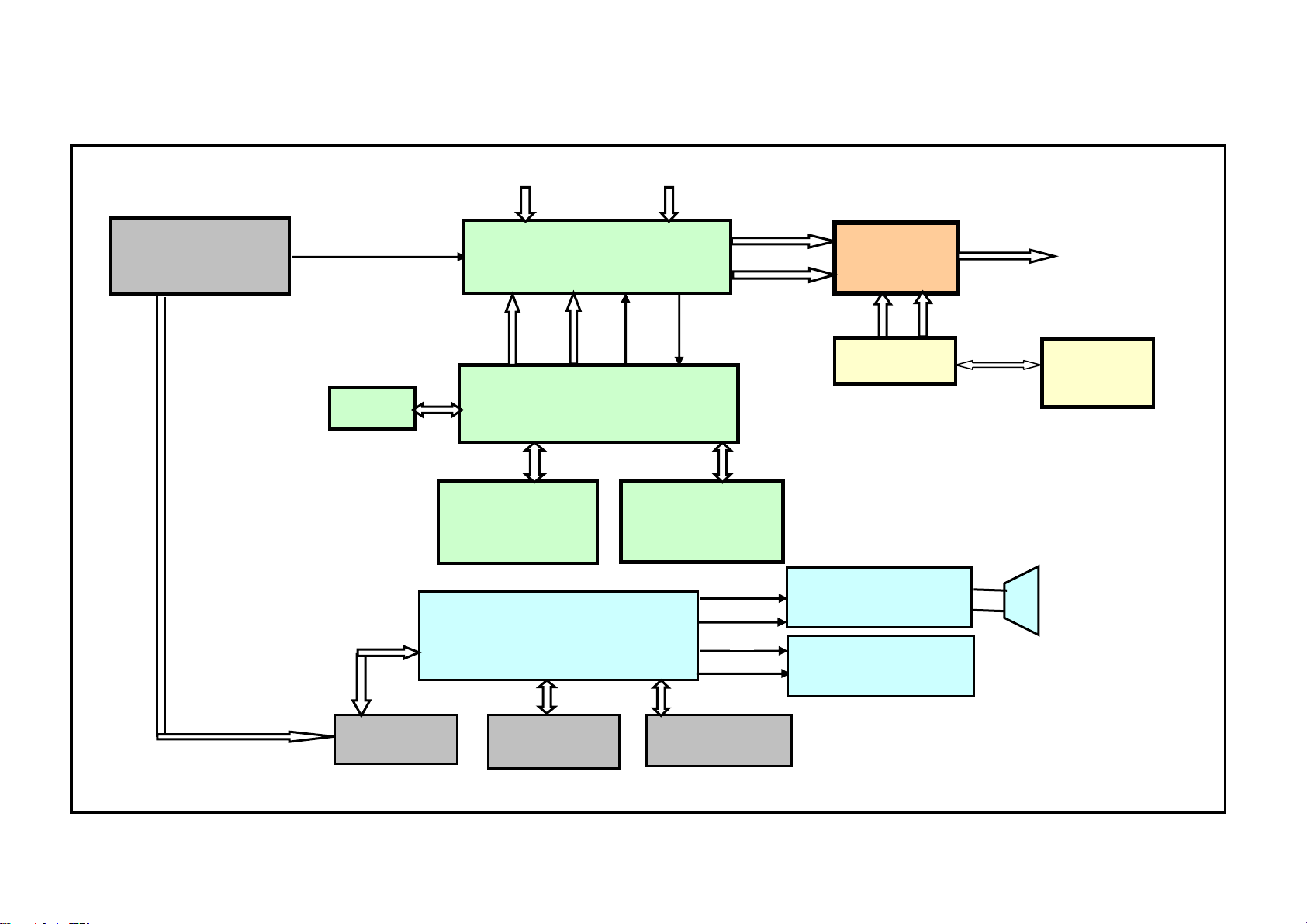

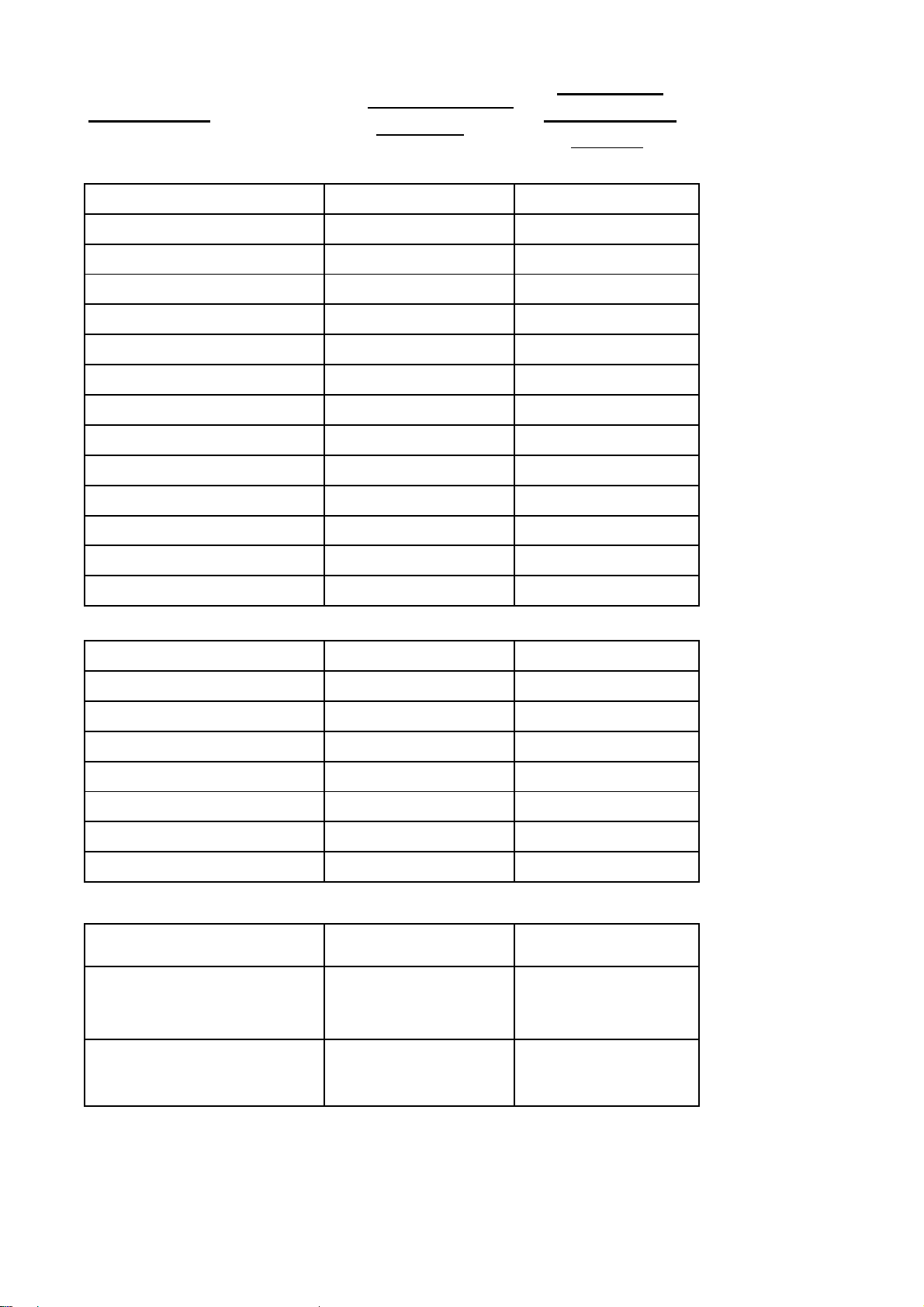

Block diagram of power supply

Chassis overwiev

Service mode items and explanations

Data sheet of important IC’s

Recommended Part List

1

2

3

4

5

6

7

12

17

29

Frequency list of channels

30

SAFETY PRECAUTIONS

GENERAL GUIDELINES

1. Always use the manufacturer’s replacement safety

components. The critical safety components marked

with on the schematics diagrams should not be

by other substitutes. Other substitute may create the

electrical shock , fire or other hazards. Take

attention to replace the spacers with the originals.

Furthermore where a short circuit has occurred ,

replace those components that indicate evidence of

overheating.

2. After servicing , see that all the protective devices

such as insulation barriers, insulation papers, shields

and isolation R-C combinations are correctly

installed.

3. When the receiver is not being used for a long time

of period of time , unplug the power cord of the

Adaptor from the AC outlet.

Color TFT LCD Module is very sensitive

both electrically and physically.Users,

therefore, are requested to follow the

“Guidance of handling color TFT LCD

Module”on the followings.

1 - Be careful not to make scratch on the

polarizer.

Surface of polarizer is soft and can be physically

damaged easily.

Please do not touch, push or rub polarizer surface

with materials over HB hardness.

2 - Keep clean the surface.

Please wear rubber glove when touch the surface of

LCD screen. Please use soft and anti-static material

as cleaner.

3 - Keep out of water.

Water on/in the LCD may cause electrical short or

corrosion. Please wipe out dry or water carefully.

4 - Prevent swift Temperature &

Humidity change.

Instantaneous temperature and/or humidity change

can make dew or ice which cause nonconformance

such as malfunction.

5 High temperature & high humidity

reduce the life-time.

LCD is not proper to be used at high temperature

and high humidity. Please keep specified

temperature and humidity condition.

6 - Keep out of Corrosive Gas.

Corrosive gas effect the polarizer and the circuit

chemically and cause defects accordingly.

7 - Electrostatic discharge can make

Damage

There are electro-static sensitive components such

as CMOS in LCD Module. Please earth human

body when handle the LCD.In addition, please do

not touch the interface connector pin with bare.

8 - Do not operate for a long time under

the same pattern

Operating LCD for a long time under the same

pattern can cause image persistence and can

damage it. Please follow following guidance.

1. Turn the power off when do not use.

2. Change the pattern periodically.

L5A TECHNICAL SPECIFICATION

Receiving System

Comb Filter Adaptive 4H\2H

Scaling Upto SXGA at 75Hz

Gamma Correction 8 to 10-bit LUT

Histogram Equalization YES

Stereo Decoding

(German A2, Nicam, BTSC)

Stereo L, R In 3

Stereo L, R Out 3

Audio Output Power RMS in Max at 10% THD) 2x3W, 2x5W for 22"W

Level (1.5, 2.5, Teleweb) Teletext 1.5

Teletext

WSS +

VPS\PDC +

Picture Formats

(4:3, 16:9, 14:9, Panorama, LetterBox, Subtitle)

WSS (Wide Screen Signalling) +

ATS (Automatic Tuning System) Frequency Search

Manual Search Channel Table Search

Number of Program Storage 100

No Ident Timer +

Picture Freeze +

Equalizer +

Zapping +

AVL (Automatic Volume Level) +

Sound Status Memory +

Picture Status Memory +

Swap +

Child Lock +

Program Lock +

Picture Format Switching Thru Pin 8 +

Auto RGB Detect Thru Pin 16 +

PC Plug & Play (DDC\CI) +

Timer

Picture Smart (User, Soft, Natural, Rich) +

Sound Smart (User, Music, Sports,

Cinema, Speech)

Scart 2

S-video (DIN) 1

AV In (3 RCA) 1

AV Out (3 RCA) 1 (ONLY L, R)

D-Sub 15 1

Headphone 1

CVBS In 3

Y\C In 1

RGB+FB -Video 1

RGB+HS, VS In -Graphics 1

CVBS Out 2

Type (Fast\Top\Simple) Simple, Fast, Top

Page Memory 250p or 10p

4:3 +

16:9 +

Panorama +

Letterbox +

Subtitle +

Off Timer (Sleep Timer) +

On Timer +

PAL B/G+I+D/K SECAM L/L'

German A2, Nicam

+

Manufacturer

PANEL SPECIFICATION

14" 15" 17" 17W" 20" 22W" 23W"

Samsung

AUO

Hannstar

CMO

AUO Sanyo

Samsung Samsung

CMO

AUO

Samsung

Interface

Resolution

Brightness (cd/m2)>

Contrast>

Response Time

(Tr+Tf) msec <

Viewing Angle R\L\H\L >

Adaptor Input

Power consumptions

St-By Power Consumption

Input Range

Single LVDS

VGA (640x480) XGA (1024x768) SXGA (1280x1024) WXGA (1280x768)

450 250 300 400 500 450 450

500 300 400 400 500 500 400

25 35 25 25 16 25 25

85/85/85/85 60/60/40/50 70\70\60\60 70/70 50/60 80\80\60\60 85/85 85/85 85/85 85/85

Double TTL\Single

LVDS

Dual LVDS Single LVDS

Single TTL\Single

LVDS

SVGA (800x600)

VGA (640x480)

Single LVDS Single LVDS

WXGA (1280x720) WXGA (1280x768)

12V 12V 12V 12V 15V 15V 24V

48W 48W 60W 60W 75W 100W

<3W <3W <3W <3W <3W <3W <3W

100-240V/50, 60Hz 100-240V/50, 60Hz 100-240V/50, 60Hz 100-240V/50, 60Hz 100-240V/50, 60Hz 100-240V/50, 60Hz 100-240V/50, 60Hz

BLOCK DIAGRAM OF MAIN CHASSIS (L5A

)

V

Tuner IF

CVBS-IF

EEPROM

24LC16

SVHS-Y/C

HS/VS

K6T1008V2E

(Optional)

YUV

HS/VS

SRAM

AUDIO DECODER

Video Decoder

VPC 3230D

RGB

Teletext Decoder

SDA 5550

R

MSP3410G

L

R

SC1-RGB

FB

M29W040

Flash

Memory

L

L

R

YU

HS/VS

Scaler

Stage

RGB

VGA-IN

TDA1571

Stereo

Amplifier

TDA1308

Headphone

Amplifier

PANEL

HS/VS

EEPROM

24LC02

SIF/AM-mono

Scart 1

Scart 2

SVHS/FAV

BLOCK DIAGRAM OF SCALER

A

HS/VS

RGB

VGA_RGB

VGA HS/VS

BAC LIGHT UNIT

S508 (LVDS) S500(TTL)

BR1_ADJ BLK_EN

GM 5221 U500

CONTROLLER

U501

PARALEL

FLASH

MEMORY

M29W040B

(OPTIONAL)

SERIAL FLASH

Panel_En Standby Mute Reset

LCD

U503

MEMORY

M25P40

KEYBOARD

CON. S509

S506

CONN.

LVDS

CONNECTOR

(20 OR 30 PINS)

(S503,S502)

DAUGHTER

BOARD

FOR TTL

INTERFACES

P

N

E

L

S505

PROGRAMING

CON

U502

EEPROM

24C16

L5A POWER SUPPLY BLOCK DIAGRAM

S600

DC Jack +15V-STBY

S602

V-INV

F600 15V,12V

Fuse

5A

F601

LM2576

V-INV

V-INV

U600

LM2576

U607

78L08

U606

+5V-STBY

+8V

LM1117

3.3V

LM1117

1.8V

U605

INPUT: 12V FOR 14,15,17 INCH 5V-STBY

15V FOR 20, 22 INCH

24V FOR 23 INCH

78L12

U608

+ 12V

3.3V-STBY

1.8V-STBY

+12V

+5V

U602

SDI9933ADY

LM117-3.3V

U604

Panel

Power

ONLY FOR 23 "

ONLY FOR 20, 22, 23 "

78L08

U606

+8V

PNL-EN Power STBY

2.5V

3.3V

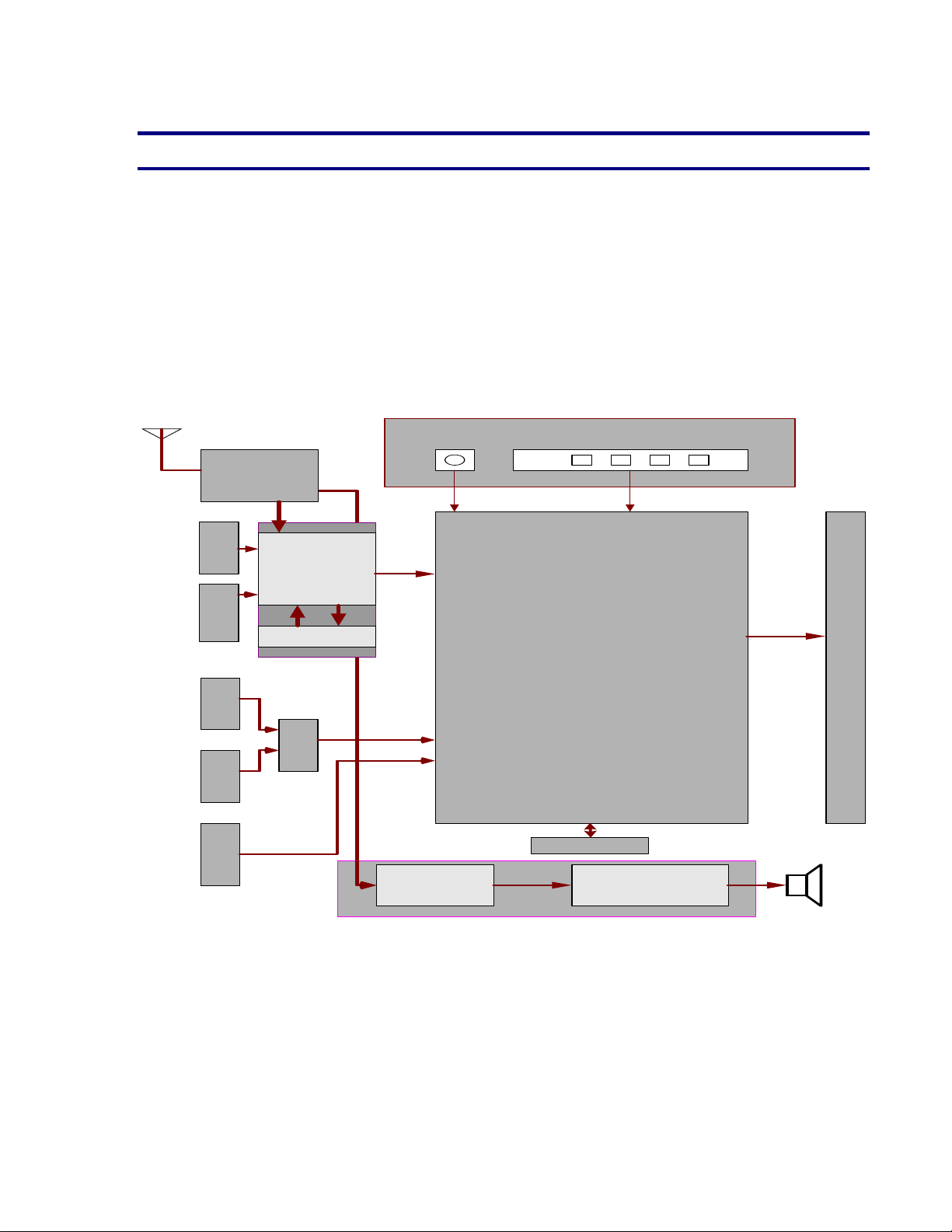

L5-A Low-to-Mid End LCD-TV BOARD OVERVIEW

L5-A Low-to-Mid End LCD TV board incorporates the LCD Controller gm2221, to create a

high quality, stand-alone LCD-based TV system for consumer applications. Figure 1

illustrates the Block diagram of the board.

This board supposed to have two versions:

1. Low-End (to drive 14''-15’’ 4:3 panels)

2. Mid-End (to drive 17’’-20’’ 4:3 and 17’’-22’’-23'' 16:9 panels)

LOW TO MID END LCD TV WITH GM2221

RGB, HS, VS

Selected

Video

EDID

VGA

ITU 656

8-bit

FLASH

SDRAM

GM2221

ADC+PLL

ITU 656

De-interlace

Scaling

MCU X86

OSD(4bit\pixel)

2 LVDS Tx

QSS

Ext L/R

HP

L/R

TDA1308T

FLASH

NVRAM

1p, 2p\clk

LVDS

24-bit TTL

HS, VS, DE

Upto SXGA at 75Hz

Audio

Decoder

MSP 3410G

HP

AudioAmp

TDA1517P

L R

15",

17",

20''

4:3

17''

22''

16:9

TFT

LCD

Main

L/R

3.3V 2.5V

5V

8V

Step Down

& Lineer

Regulators

12V

QSS

Multimedia

Tuner

EXT. CVBS, S-video

Scart RGB, FB

1.8V

CVBS

Graphics

Upto SXGA at 75Hz

UXGA at 60Hz

SDA,SCL

Chroma

Decoder

VPC 3230D

RGB, FB

Teletext

Teletext

Decoder +MCU

SDA5550

Figure 1 System Block Diagram

L5-A board supports 5 types of video and graphics inputs. These inputs are: Analog

terrestrial tuner input for multisystem PAL/SECAM transmission, SCART input (x2), S-VHS

input, RCA input and analog PC video input.

The analog RGB signals coming from the PC input (via D-Sub15 connector P401) are

directly connected to the gm2221 analog input port.

One EDID IC (U400) is provided on board to support VESA standard plug-and play

compatibility.

On the board, one high quality video decoder (U100) is provided (VPC3230D of Micronas)

to process video inputs coming from the video sources. The video processor can process 3

composite video inputs and 1 S-Cideo input from the NTSC/PAL video sources. The CVBS

output recovered from the tuner module is made available to one of the video inputs of the

video decoder.

The digitized video output (in ITU-656 format) from U100 is fed to the dedicated video Port

of gm2221 for decoding and processing.

Gm2221 makes it possible to perform scaling and de-interlacing for the video input.

A 4Mbit serial flash ROM (U503) is used for storing system firmware. Also the footprint for

a parallel flash ROM, which can be upto 2Mbits, is available on the board. This option can

be used either for development or for production purposes.

The gm2221 provides direct connect via the integrated LVDS transmitters to LCD panels

with integrated LVDS receivers. Both single LVDS (via S503) and double LVDS(via S502)

panels can be supported directly from the L5-A main-board. For single LVDS panels, only

S503 connector is soldered on the main-board, which is a 20 pin connector. For Double

LVDS panels, only S502 connector is soldered on the main-board, which is a 30 pin

connector. For supporting different LVDS panels, different LVDS cables (either single or

double LVDS) can be made used.

For supporting different single or double TTL panels, a daughter board interface is used via

40 pin S506 connector. On this connector, the signals are 3x8bit RGB with TTL control

signals (i.e. HSync, VSync, CLK, O/E etc.) to support a wide variety of LCD panels.

Depending on the panel used, different daughter boards will be used to support that

particular panel. For single TTL panels, the daughter board will just be a routing the RGB

and control signals to the particular connector interface for that particular panel. For double

TTL panels, there will be two LVDS receiver IC’s on the daughter board (double TTL is not

directly from GM2221 but double LVDS is supporter due to IC packaging problems) to

demodulate double LVDS signal into double TTL signal.

The LCD panel resolution supported can be up to SXGA at 75 Hz or UXGA at 60 Hz.

It is important to note that at any point in time gm2221 could drive only one type of Panel.

When LVDS Panel is connected (to connector S503 or S502) ensure that the panel

backlight is connected to S508. The integrated PWM output from gm2221 is used to

control the LCD panel backlight intensity for dimming functions.

The on screen display is implemented using OSD capability of gm2221. Infra Remote (IR)

controller connector (S507) is provided as a primary control interface for connecting IR

detector to the GPIO of gm2221. An IR remote controller unit and detector provide remote

OSD menu access at user convenience.

A keypad connector (S507) is provided which utilizes the integrated low bandwidth ADC in

gm2221 for scanning 5-6 keys (menu,V+,V-,P+,P- keys standard- source key optional) on

the keypad. The keypad allows access to the OSD without using the remote IR controller.

The L5-A board also has In System Programming (ISP) capability for the external flash

ROM using DDC2Bi. This can be done using the D-Sub 15 (PC) connector on the board.

ISP can also be performed using G-probe through the RS232 interface.

One channel of the dual channel FET power switch (U602) is used to control the power

sequencing to the LCD panel. Depending on the type of the panel, the input voltage to this

FET device can be chosen as shown below:

For +3.3V panels J601 is soldered on the main-board

For +5V panels J600 is soldered on the main-board

For +12V panels J603 is soldered on the main-board

An LM2576, a step-down regulator IC (U600), is used to generate the main +5V_STBY

voltage on the board. This IC can deliver up-to 3 Ampers of 5Volts. There is no stand-by

control for this regulator, which means this IC is always on, as soon as power is supplied

to the board.

U603(+3.3V_STBY) and U605 (+1.8V_STBY) linear regulators are used to supply the

voltage necessary for the GM2221 IC and some peripherals. These voltages are also

available in stand-by mode to power the microprocessor inside gm2221, LED, IR receiver

IC and EEPROM. These devices are necessary to wake up the board from stand-by state.

Second channel of the dual channel FET power switch (U602) is used to control cut some

voltages in stand-by mode. These voltages are +5V, +3.3V and +2.5V. These voltages are

used by the video processor (VPC 3230D), audio processor (MSP 34x0G), teletext

processor (SDA5550), tuner and some peripheral IC’s and circuitry. In order to limit the

stand-by power consumption, these voltages are not available in stand-by mode. Also the

audio amplifier (TDA1517) is also in its stand-by mode using its dedicated stand-by pin.

The board employs MSP3410G, a multi-system audio processor solution from Micronas.

The system supports 4 audio input ports, one of which is not used on the L5-A board.

Audio output is provided with speaker and headphone jacks (S409, S401) provided on the

board. The sound IF signal from the tuner is connected to the audio processor directly.

4. GM2221 LCD TV CONTROLLER

The gm2221 IC is a highly integrated single channel scaler that can be used for both LCD

monitors up to SXGA/UXGA resolutions and rear projection systems with DLP and HTPS

LCD engines up to 1280x720 (720P). Some of the key features include:

• Single processing channel.

• RGB and YUV signal processing with RGB to YUV and YUV to RGB color space

converters.

• Video signal processing/de-interlacing using spatial, VT (vertical-temporal) diagonal

interpolation.

• The on-chip turbo x86 micro-controller is used as the system CPU.

• The on-chip OSD controller is available for creating bitmapped OSD menus

• The keypad buttons utilize the input of the on-chip low bandwidth ADC.

• Software IR decoders is used with an external remote controller.

• One of the on-chip PWM outputs is used for controlling back-light intensity

• Integrated LVDS transmitters to LCD panels with integrated LVDS receivers.

The LCD panel resolution supported can be up to SXGA resolutions.

6. LCD PANEL INTERFACE

The L5-A board can drive panels both with LVDS and TTL interfaces. The footprints for

single LVDS and double LVDS connectors are available on the board (S503 and S502,

respectively). Either of these connectors can be used without any changes on the board.

The TTL interface is supported by a daughter board (S506 is the connector for the

daughter board). For the TTL case, connecting the daughter board to the connector will be

sufficient.

A Hirose 30-pin connector (S502) is used for double LVDS link from the board to various

LVDS panels. This connector can also be used for single LVDS, but another connector

footprint (S503) is available for single LVDS purposes. Using only S503 for single LVDS

panels decreases the cost. The LVDS traces are routed differentially from the gm2221 IC

to the connector. These are 100-Ohm differential traces.

L5A SERVICE MENU

Service Menu is entered by pressing 9, 3, 0, 1 keys on the remote controller when the Picture icon is

highlighted in the Main Menu.

Service Menu has 3 sub-menus. These are:

• Options

• Adjustments

• Selections.

Navigation through these menus can be done by pressing OK button. Every adjustment made in this

menu is saved automatically.

OPTIONS

Options are adjustments that the user can select On or Off.

• BG

• DK

• I

• LL’

• SCART 2

• FAV

• SVHS

• HOTEL MODE

• STAND BY

• MSP CARRIER MUTE

• WSS SCART

• FIRST ATS

BG / DK / I / L

Enabling or disabling these options will remove / add these standards to Manual Install menu, SYSTEM

item.

SCART 2 / FAV / SVHS

If a source is disabled in the Service Menu, it will be skipped during source switches. If SCART2 is

enabled, SW assumes that the FAV source share the same path as the SVHS source on the HW. If it is

disabled, it is assumed that FAV and SVHS share separate paths. TUNER and SCART1 are enabled by

default.

HOTEL MODE

Enabling Hotel Mode has two effects. First, SETUP menu is no longer accessible by the user. Second,

maximum adjustable volume value is limited to HOTEL VOLUME value. This value can be adjusted in the

ADJUSTMENTS sub-menu of the Service Menu.

STAND BY

If this Option is OFF, the TV will stay in Stand By mode after a Power On. If this Option is ON, the TV will

recall its last stand by status before the Power Off, and switch on from Stand By automatically, if the last

state was ‘Stand by On’.

MSP CARRIER MUTE

If this option is ON, sound processor’s carrier mute functionality will be enabled. The MSP will mute the

sound automatically if the signal quality is bad. Setting this option Off will disable this functionality.

WSS RF / WSS SCART

Automatic picture format switching for WSS and Pin8 can be enabled or disabled through this option.

If WSS SCART is set to OFF, AUTO picture format mode will be disabled for SCART1 and SCART2

modes. Pin8 source switching will still be operational, but no picture format changes from Pin8 voltage

level will be ignored.

ATS

If this option is set to ON, TV will display Country Selection menu in the next start. After some country is

selected, the user will be prompted for the start of AutoProgramming process.

ADJUSTMENTS

This sub-menu contains numeric adjustments. These items are:

• WHITE R

• WHITE G

• WHITE B

• PRESCALE FM

• PRESCALE NICAM

• PRESCALE SCART

• HOTEL VOLUME

WHITE R / WHITE G / WHITE B

These are used for color bias adjustment. Unlike other items in the service menu, changes will take effect

immediately.

PRESCALE FM / PRESCALE NICAM / PRESCALE SCART

These are prescale values that will be used for the initialization of the sound processor (MSP), at the next

switch on.

HOTEL VOLUME

This value is used as the volume limit, when the Hotel Mode is on.

SELECTIONS

This sub-menu contains selections.

• TUNER TYPE SAMSUNG / PHILIPS

• TELETEXT NO TEXT / FAST / FAST&TOP

• MSP CLIP REDUCE VOL / REDUCE TONE / COMPROMISE / DYNAMIC

TUNER TYPE

One of two supported tuner can be selected from this item. System must be restarted for this change to

take effect.

TELETEXT

NO TEXT: Teletext is totally disabled. TXT/MIX button will not be functional. AUTO picture format mode

will be disabled in RF, F-AV and SHVS modes. Naming and sorting functionality during Autoprogramming

will be disabled.

FAST: TOPtext functionality will be disabled.

FAST&TOP: TOPtext functionality is enabled.

TIMER MODE

If OFF TIMER is selected, the user will be able to enter time of the day info for the TV to switch off. If

SLEEP TIMER is selected, the user can specify some time period, after which the TV will go to stand by

automatically.

MSP CLIP

This selection identifies which method will be used by the sound processor to prevent clipping effects on

volume. Details can be found in data sheet msp34x0g_4pd.pdf, page 30.

AUTOPROGRAMMING

When the user selects the Autoprogram item in Setup menu, Country Selection menu is opened. The user

must select a country before the Autoprogramming starts. Broadcast system will be selected according to

the country selected.

Broadcast systems according to countries:

BELGIUM BG + L

CROATIA BG

CZECH REP. DK

DENMARK BG

FINLAND BG

FRANCE L + BG

GERMANY BG

GREECE BG

HUNGARY DK

IRELAND I

ITALY BG

NETHERLANDS BG

NORWAY BG

POLAND DK

PORTUGAL BG

SPAIN BG

SWEDEN BG

SWITZERLAND BG + L

TURKEY BG

UNITED KINGDOM I

For countries France, Belgium and Switzerland, autoprogramming is done twice. For Belgium and

Switzerland, first BG channels will be searched, after the search in BG is done, searching will restart for L

standard. If the selected country is France, the sequence of standards is reversed, thus, first L then BG.

TELETEXT LANGUAGES

L5A SW decides which teletext language group will be used for teletext decoding, according to the

country selected for autoprogramming.Teletext languages according to countries:

EAST EUROPE:CROATIA ,CZECH_REP, POLAND

WEST EUROPE: BELGIUM ,DENMARK, FINLAND, UK, FRANCE, GERMANY,

IRELAND ,ITALY ,NETHERLANDS, NORWAY, PORTUGAL,SPAIN, SWEDEN, SWITZERLAND,

HUNGARY

TURKISH-GREEK:GREECE TURKEY

PC MODE

PC mode can be entered by pressing PC button on the remote controller. User can return back to TV

mode by pressing the PC or TV buttons.

After the switching to PC mode, VGA input will be displayed on screen, as soon as the mode (input

resolution and frequency) is determined.

If there is no input from the VGA input, NO SIGNAL dialog will be displayed for 15 seconds. At the end of

this period if there is no signal from VGA input, the TV will go to Sleep State. While in the sleep state, the

TV will keep monitoring the VGA input. If VGA signal is detected, the TV will wake from Sleep State, to PC

mode. Alternatively, the user may select to switch the TV on from Sleep State, just like switching on from

Stand-by. In this case, the set will switch on from TV mode.

OPTIONS/

DEFAULT

ITEM NAME

VALUES OR

VALUES

SETUP

OPTIONS

BG ON/OFF ON

DK ON/OFF ON

I ON/OFF ON

LL' ON/OFF ON

SCART 2 ON/OFF OFF

FAV ON/OFF ON

SVHS ON/OFF ON

HOTEL MODE ON/OFF OFF

STBY ON/OFF OFF

MSP CARRİER MUTE ON/OFF OFF

WSS SCART ON/OFF ON

FIRST ATS ON/OFF OFF

BACKLIGHT POL ON/OFF OFF

FACTORY MODE ON/OFF OFF

ADJUSTMENTS

WHITE R 0-255 128

WHITE G 0-255 128

WHITE B 0-255 128

PRESCALE FM 0-127 37

PRESCALE NICAM 0-127 63

PRESCALE SCART 0-127 27

HOTEL VOLUME 0-63 16

AGC 0-31 23

SELECTIONS

TUNER TYPE

PHILIPS

SAMSUNG

PHILIPS

TELETEXT

MSP CLIP

FAST&TOP

NO TEXT

FAST

REDUCE TONE

COMPROMISE

DYNAMIC

FAST&TOP

DYNAMIC

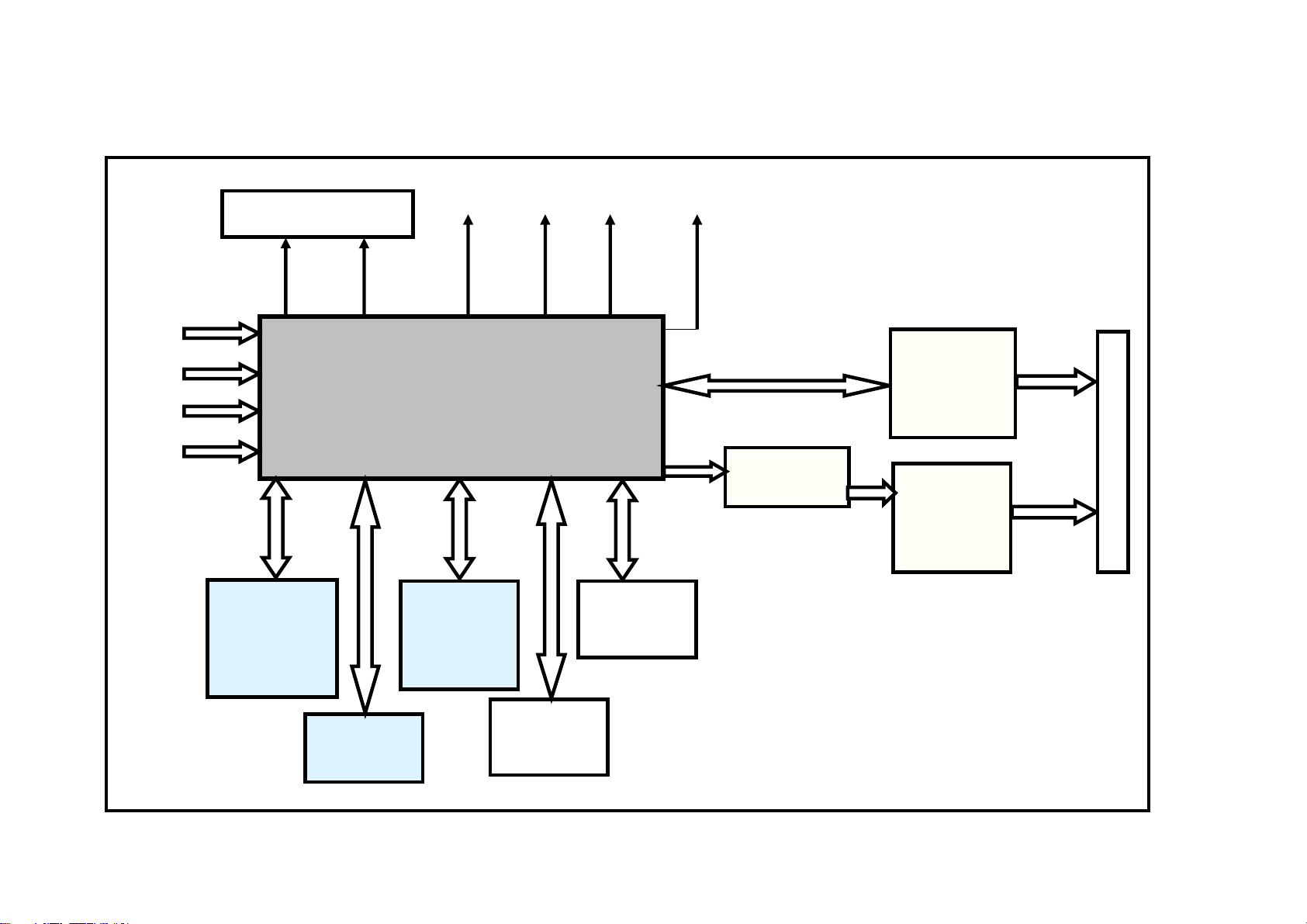

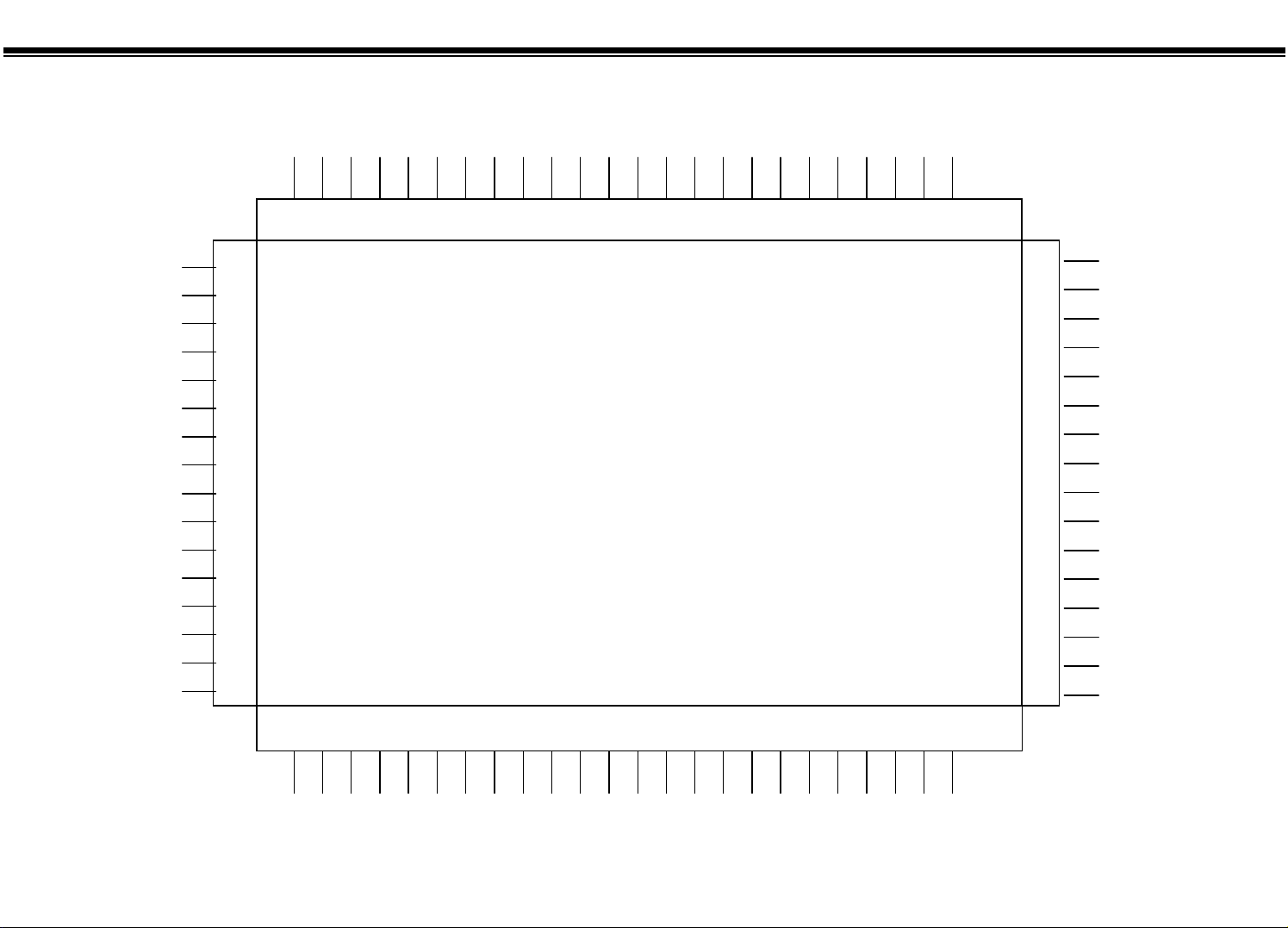

GENESIS GM5221 LCD TV CONTROLLER

The gm5221 is an LCD TV controller supporting resolutions up to SXGA (1280x1024). The gm5221

leverages Genesis patented advanced image-processing technology as well as a proven integrated

ADC/PLL and an Ultra-Reliable DVI™ compliant digital receiver to provide excellent image quality.

gm5221 also integrates a microcontroller, an OSD controller, advanced color management and dual

LVDS transmitters.

1.1 gm5221 System Design Example

Figure 1 below shows a typical dual interface LCD TV system based on the gm5221. Designs based on

the gm5221 have reduced system cost, simplified hardware and firmware design and increased reliability

because only a minimal number of components are required in the system.

C

V

B

S

S

V

I

D

E

O

Y

Pb

Pr

V

G

A

D

V

I

TUNER

PACK

VIDEO

DECODER

V CHIP

M

U

X

AUDIO

PROCESSOR

IR

KEY BOARD

gm5221

EEPROM

AUDIO

AMPL

L

C

D

D

I

S

P

L

A

Y

Figure 1. gm5221 System Design Example

1.2 gm5221 Family Features

• Intelligent Image Processing™

• Fully programmable zoom ratios

• High-quality shrink capability from UXGA resolution

• Programmable coefficients for variable sharpness control

• RealRecovery™ provides full color recovery image for

refresh rates higher than those supported by the LCD panel

• Analog RGB Input Port

• Supports SDTV RGB inputs in interlaced mode

• Supports EDTV (480p) up to 1080i HDTV inputs

• Supports mid level clamp for YPbPr inputs

• Macro vision decoding

• Supports up to 162 MHz (SXGA 75Hz / UXGA 60Hz)

• On-chip high-performance PLLs (single reference crystal

required)

• Composite-sync, Sync-on-Green (SOG) and Sync-on-Y

(SoY) support

• Input format detection

• Phase and image positioning

• Ultra-Reliable DVI-Compliant Input Port

• Operating up to 165 MHz (up to UXGA 60Hz)

• Direct connect to all DVI 1.0-compliant transmitters

• High-bandwidth Digital Content Protection (HDCP)

Note: HDCP function is available H version only.

• CCIR-656 8-bit Video Input Port

• Supporting NTSC / PAL interlaced and progressive

• Direct connect to commercially available video decoders

• Spatial de-interlacing

• Advanced Color Management

• Programmable gamma correction (CLUT)

• TV color controls including hue and saturation controls

• Full color matrix allows end-users to experience the same

colors as viewed on CRTs and other displays (e.g. sRGB

compliance)

• Advanced Active Color Management ™ (ACM-II) provide

flesh-tone compensation and image enhancement for video

preset modes like sport, nature .

• Adaptive Contrast and Color™ (ACC) ensures full dynamic

range is used in video content

• Embedded X86 On-chip Microcontroller

• High-performance X86 MCU with on-chip RAM and ROM

• External parallel ROM or serial SPI ROM interface

• Unified memory architecture simplifies chip programming

• 23 general-purpose inputs/outputs (GPIOs) available

• 2-wire serial bus master to control NVRAM, video decoder

• Two DDC2Bi ports with DMA buffer to internal RAM

• Four PWM outputs for analog backlight control, audio, etc.

• General-purpose ADC’s for keypad and temperature sensing

• Integrated reset circuit

• Slow clock mode for 50mW sleep mode power consumption

• JTAG debug / ICE support for firmware debugging

• Built-in Test Pattern Generator

• Simplifies manufacturing / test

• Energy Spectrum Management (ESM™)

• Digital clock spectrum management

• Eliminates EMI suppression components and shielding

• Built-in LVDS Transmitters

• Four channel 6/8-bit LVDS transmitter

• Support for 8 or 6-bit panels with high-quality dithering

• Single / double wide up to SXGA 75Hz output

• Pin swap, odd / even swap and red / blue group swap of RGB

outputs for flexibility in board layout

• Highly integrated System-on-a-Chip

• All system clocks synthesized from a single external crystal

• 50mW power saving mode

• 5-Volt tolerant inputs

• Two Layer PCB support

• On-chip reset feature to eliminate external reset component

• Integrated Schmitt trigger for HSYNC and VSYNC

PACKAGE

• 208-pin PQFP

• 3.3V IO and 1.8V core power supplies

• On-chip Versatile OSD Controller

• On-chip RAM for high-quality programmable menus

• 1, 2 and 4-bit per pixel character cells

• Horizontal and vertical stretch of OSD menus

• Blinking, transparency and blending

• Supports two independent OSD menu rectangles

• Proportional fonts

2 gm5221 Pinout

The gm5221 devices are packaged in a 208-pin Plastic Quad Flat Pack (PQFP).

ROM_DATA4

ROM_DATA5

CRVSS

RVDD_3.3

ROM_DATA6

ROM_DATA7

ROM_ADDR0

ROM_ADDR1

ROM_ADDR2

ROM_ADDR3

ROM_ADDR4

ROM_ADDR5

ROM_ADDR6

ROM_ADDR7

ROM_ADDR8

ROM_ADDR9

ROM_ADDR10

CRVSS

RVDD_3.3

ROM_ADDR11

ROM_ADDR12

ROM_ADDR13

ROM_ADDR14

ROM_ADDR15

ROM_ADDR16

ROM_ADDR17

VSYNC

HSYNC/CSYNC

CRVSS

CVDD_1.8

RESETn

LBADC_GND

LBADC_RETURN

LBADC_IN3

LBADC_IN2

LBADC_IN1

LBADC_VDD_3.3

AVDD_RPLL_3.3

TCLK

XTAL

AGND_RPLL

ROM_DATA3

ROM_DATA2

ROM_DATA1

ROM_DATA0

ROM_OEn

ROM_WEn

ROM_CSn

CRVSS

CVDD_1.8

RESERVED

AVDD_LV_E_3.3

AVSS_LV_E

CH3P_LV_E/ER0

CH3N_LV_E/ER1

CLKP_LV_E/ER2

CLKN_LV_E/ER3

CH2P_LV_E/ER4

CH2N_LV_E/ER5

CH1P_LV_E/ER6

CH1N_LV_E/ER7

CH0P_LV_E/EG0

CH0N_LV_E/EG1

AVSS_LV_E

AVDD_LV_E_3..3

AVSS_LV

AVDD_LV_3.3

AVDD_LV_O_3.3

AVSS_LV_O

CH3P_LV_O/EG2

CH3N_LV_O/EG3

CLKP_LV_O/EG4

CLKN_LV_O /EG5

CH2P_LV_O/EG6

CH2N_LV_O/EG7

CH1P_LV_O/EB0

CH1N_LV_O/EB1

CH0P_LV_O/EB2

CH0N_LV_O/EB3

AVSS_LV_O

AVDD_LV_O_3..3

CVDD_1..8

RVDD_3.3

CRVSS

CVSS

EB4

EB5

EB6

EB7

DEN

DHS

DVS

N/C

1

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

5354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899

N/C

N/C

DCLK

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

JTAG_RESET

RESERVED

JTAG_TDO

JTAG_TDI

RESERVED

PPWR

PBIAS

GPIO15

RESERVED

HOST_SCL/UART_DI

HOST_SDA/UART_DO

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

CRVSS

CRVSS

RVDD_3.3

CVDD_1.8

DDC_SCL_DVI

DDC_SDA_DVI

DDC_SCL_VGA

DDC_SDA_VGA

CRVSS

CVDD_1.8

168

GPIO6

GPIO9/SCL

GPIO7/IRQin

GPIO10/SDA

GPIO8/IRQout

RESERVED

VDD_RPLL_1.8

167

166

CRVSS

RVDD_3.3

GND_RPLL

165

CVDD_1.8

VDD_ADC_1.8

GND_ADC

164

163

CRVSS

N/C

N/C

N/C

N/C

N/C

N/C

AGND_ADC

162

161

GPIO11/PWM0

GPIO12/PWM1

156

160

159

158

157

RESERVED

155

AVDD_ADC_3.3

154

AGND_RED

153

RED-

152

RED+

151

AVDD_RED_3.3

150

AGND_GREEN

149

GREEN-

148

GREEN+

147

SOG_MCSS

146

AVDD_GREEN_3.3

145

AGND_BLUE

144

BLUE-

143

BLUE+

142

AVDD_BLUE_3.3

141

CRVSS

140

CVDD_1.8

139

RESERVED

138

VDD_RXPLL_1.8

137

GND_RXPLL

136

RESERVED

135

AVDD_RXC_3.3

134

RXC-

133

RXC+

132

AGND_RXC

131

AVDD_RX0_3.3

130

RX0-

129

RX0+

128

AGND_RX0

127

VDD_RX0_1.8

126

AVDD_RX1_3.3

125

RX1-

124

RX1+

123

AGND_RX1

122

VDD_RX1_1.8

121

AVDD_RX2_3.3

120

RX2-

119

RX2+

118

AGND_RX2

117

VDD_RX2_1.8

116

AGND_IMB

115

REXT

114

AVDD_IMB_3.3

113

VCLK

112

GPIO23/VDATA0

111

GPIO22/VDATA1

110

GPIO21/VDATA2

109

GPIO20/VDATA3

108

GPIO19/VDATA4

107

GPIO18/VDATA5

106

N/C

105

100

101

102

103

104

N/C

GPIO13/PWM2

GPIO14/PWM3

GPIO16/VDATA7

GPIO17/VDATA6

Figure 2. gm5221 Pin Out Diagram

Video Processing - VPC3230D

GNDF

VRT

I2CSEL

ISGND

VSUPF

VOUT

CIN

VIN1

VIN2

VIN3

VIN4

VSUPAI

GNDAI

VREF

FB1IN

AISGND

ASGF

XTAL2

XTAL1

NC

CLK5

VSTBY

FPDAT

VS

MSY/HS

FSY/HC

AVO

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

VPC3230D

INTLC

VSUPSY

GNDSYC0C1

C2

C3

GNDC

VSUPC

C4

C5

C6

C7

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

Y0

Y1

Y2

Y3

VSUPY

GNDY

Y4

Y5

Y6

Y7

GNDLLC

VSUPLLC

LLC1

LLC2

VSUPPA

GNDPA

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

B1/CB1IN

G1/Y1IN

NC

ASGF

G2/Y2IN

B2/CB2IN

R1/CR1IN

R2/CR2IN

VSUPCAP

GNDD

VSUPD

SCL

SDA

GNDCAP

RESQ

TEST

VGAV

YCOEQ

FFIE

FFWE

FFRSTW

FFRE

FFOE

CLK20

Loading...

Loading...