Page 1

SERVICE MANUAL

DOCUMENTATION TECHNIQUE

TECHNISCHE DOKUMENTATION

DOCUMENTAZIONE TECNICA

DOCUMENTACION TECNICA

No copying, translation, modification on other use authorized. All rights reserved worldwide. • Tous droits de reproduction, de traduction, d'adaptation et d'exécution réservés pour tous les pays. • Sämtliche Urheberrechte an diesen Texten und Zeichnungen stehen uns zu. Nachdrucke,

Vervielfältigungen - auch auszugsweise - nur mit unserer vorherigen Zustimmung zulässig. Alle Rechte vorbehalten. • I diritti di riproduzione, di traduzione, e esecuzione sono riservati per tutti i paesi. • Derechos de reproduccion, de traduccion, de adaptacion y de ejecucion reservados para todos los paises.

WARNING : Before servicing this chassis please read the safety recommendations.

ATTENTION : Avant toute intervention sur ce châssis, lire les recommandations de sécurité.

ACHTUNG : Vor jedem Eingriff auf diesem Chassis, die Sicherheitsvorschriften lesen.

ATTENZIONE : Prima di intervenire sullo chassis, leggere le norme di sicurezza.

IMPORTANTE : Antes de cualquier intervención, leer las recomendaciones de seguridad.

Code : 35884160 -0105 / 4,8M - DTH8040 Print.

VIDEO

DTH8040

DTH8040E

DTH8040U

Page 2

Indicates critical safety components, and identical components should be used for replacement. Only then can the

operational safety be garanteed.

Le remplacement des éléments de sécurité (repérés avec le symbole ) par des composants non homologués selon la

Norme CEI 65 entraine la non-conformité de l'appareil. Dans ce cas, la responsabilité du fabricant n'est plus engagée.

Wenn Sicherheitsteile (mit dem Symbol gekennzeichnet) nicht durch Original - Ersatzteile ersetzt werden, erlischt die

Haftung des Herstellers.

La sostituzione dei componenti di sicurezza (evidenziati con il segno ) con componenti non omologati secondo la

norma CEI 65 comporta la non conformitá dell'apparecchio. In tal caso è "esclusa la responsabilità " del costruttore.

La sustitución de elementos de seguridad (marcados con el simbolo ) por componentes no homologados segun la

norma CEI 65, provoca la no conformidad del aparato. En ese caso, el fabricante cesa de ser responsable.

MEASUREMENT CONDITIONS - CONDITIONS DE MESURES - MESSBEDINGUNGEN

CONDIZIONI DI MISURA - CONDICIONES DE MEDIDAS

RICEVITORE :

In UHF, livello d'entrata 1 mV, monoscopio barre :

- PAL, norma G. bianco 100%.

Via SCART, livello d'entrata 1 Vpp, monoscopio barre :

Colore, Contrasto, Luminositá media, Suono minimo.

Programma selezionato PR 01.

Tensioni continue rilevate rispetto alla massa con un voltmetro digitale.

RECEIVER :

On UHF,input level : 1 mV, bar test pattern :

- PAL, I standard, 100% white.

Via the scart socket, input level : 1 Vpp, bar test pattern :

Colour, contrast and brightness at mid-position, sound at minimum.

Programme selected : PR 01.

DC voltages measured between the point and earth using a digital

voltmeter.

EMPFÄNGER :

Bei UHF Eingangspegel 1 mV, Farbbalken :

- PAL, Norm G, Weiss 100%.

Über die Scartbuchse : Eingangspegel 1 Vss, Farbbalken :

Farbe, Kontrast, Helligkeit in der Mitte des Bereichs, Ton auf Minimum.

Zugeordnetes Programm PR 01.

Gleichspannungen mit einem digitalen Voltmeter zur Masse gemessen.

RECEPTEUR :

En UHF, niveau d'entrée 1 mV mire de barres

- SECAM, Norm L, Blanc 100%.

Par la prise Péritélévision, niveau d'entrée 1 Vcc, mire de barres .

Couleur, contraste, lumière à mi-course, son minimum.

Programme affecté PR 01.

Tensions continues relevées par rapport à la masse avec un

voltmètre numérique.

RECEPTOR :

En UHF, nivel de entrada 1 mV, mira de barras :

- PAL, norma G, blanco 100%.

Por la toma Peritelevision, nivel de entrada 1 Vpp mira de barra.

Color, Contraste, luz a mitad de carrera, Sonido minimo.

Programa afectado PR 01.

Tensiones continuas marcadas en relacion a la masa con un voltimetro digital.

MAIN

FRANÇAIS ESPAÑOLDEUTSCHENGLISH ITALIANO

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

NC

21

17

19

15

13

20

18

16

14

12

11

9

10

8

7

5

3

1

6

4

2

NC

AUDIO "R"

AUDIO "R"

AUDIO "L"

NOTE :

... etc. identifies each

pcb module.

AUDIO "D"

AUDIO "D"

AUDIO "G"

AUDIO

"BLEU"

AUDIO "G" MONO

"BLEU"

COMMUT. LENTE

"VERT"

"VERT"

"ROUGE"

COMMUT. RAPIDE

COMMUT. RAPIDE

VIDEO

VIDEO SYNCHRO

BLINDAGE PRISE

AUDIO "R"

AUDIO "R"

AUDIO "L"

AUDIO

"BLAU"

AUDIO "L" MONO

"BLAU"

AV

UMSCHALTUNG

"GRÜN"

"GRÜN"

"ROT"

AUSTASTUNG

AUSTASTUNG

VIDEO

VIDEO ODER

SYNCHRO

ABSCHIRMUNG

DES STECKERS

AUDIO "D"

AUDIO "D"

AUDIO "I"

AUDIO

"AZUL"

AUDIO "I" MONO

AZUL

"CONMUTACION

LENTA"

"VERDE"

"VERDE"

"ROJA"

"CONMUTACION

RAPIDA"

"CONMUTACION

RAPIDA"

VIDEO

VIDEO O SINCRO

BLINDAJE

DEL ENCHUFE

AUDIO "D"

AUDIO "D"

AUDIO "S"

AUDIO

"BLU"

AUDIO "S" MONO

BLU

"COMMUTAZIONE

LENTA"

"VERDE"

"VERDE"

"ROSSO"

"COMMUTAZIONE

RAPIDA"

"COMMUTAZIONE

RAPIDA"

VIDEO

VIDEO O SINCRO

INVOLUCRO METAL-

LICO DELLA PRESA

AUDIO "L" MONO

"BLUE"

"GREEN"

AV LINK AV LINK AV LINK AV LINK AV LINK

"GREEN"

"RED"

"ROUGE" "ROT" "ROJA""ROSSO""RED"

SLOW SWITCH

FAST SWITCH

VIDEO

VIDEO VIDEO VIDEOVIDEOVIDEO

PLUG SCREEN

BOX

VIDEO OR "SYNC"

FAST SWITCH

AUDIO

"BLUE"

: OUTPUT - SORTIE - AUSGANG - USCITA - SALIDA •

: EARTH - MASSE - MASSE - MASSA - MASA

MAIN

NOTE :

... etc. repères des

platines constituant l'appareil.

MAIN

NOTA :

... etc. marcas de las

placas que constituyen el

aparato.

MAIN

NOTA :

... ecc. sigla delle

piastre dell' apparecchio.

MAIN

HINWEIS :

... usw. Kennzeichnung

der Platinen, aus denen das

Gerät zusammengesetzt ist.

: INPUT - ENTRÉE - EINGANG - ENTRATA - ENTRADA •

Do not disconnect modules when they are energized!

Repairs on power supply section are to be carried out only with isolating transformer.

Ne pas retirer les modules lorsqu' ils sont sous tension. N'effectuer les travaux de maintenance sur la partie reliée

au secteur (Switch Mode) qu'au travers d'un transformateur d'isolement.

Module nicht bei eingeschaltetem Gerät entfernen!

Servicearbeiten am Netzteil nur unter Verwendung eines Regeltrenntrafos durchführen.

Non scollegare le piastre quando sono alimentate!

Per le riparazioni sulla sezione alimentatore, utilizzare un trasformatore isolatore.

No desconectar los módulos cuando están activados. Las reparaciones en la sección de alimentación de energía

deben ser ejecutadas solamente con un transformador de separación.

Page 3

DTH8005

First issue 12/ 04 3

SOMMAIRE

Page

CARACTERISTIQUES TECHNIQUES . . . . . . . . . . . . . . . . .4

PROCEDURE DE REGLAGES . . . . . . . . . . . . . . . . . . . .7 - 8

SCHEMA D' INTERCONNEXION . . . . . . . . . . . . . . . . .9 - 10

SCHEMA DES CIRCUITS D’ALIMENTATIONS . . . . . .11 - 12

SCHEMA DES CIRCUITS COMMANDES . . . . . . . . . .13 - 14

PLATINE PRISES CASQUE / NAVICLICK . . . . . . . . . .15 / 16

SCHEMA DE L’INTERFACE PERITELEVISION . . . . . . .17 - 28

SCHEMA DE LA PLATINE PRINCIPALE . . . . . . . . . . .29 - 46

Page

CIRCUIT IMPRIME DE L’ALIMENTATION . . . . . . . . .47 - 48

CIRCUITS IMPRIMES PLATINES COMMANDES . . . . .49 - 50

PLATINE INTERFACE PERITELEVISION . . . . . . . . . .51 - 54

CIRCUIT IMPRIME PLATINE PRINCIPALE . . . . . . . .55 - 58

ABREVIATIONS . . . . . . . . . . . . . . . . . . . . . . . . . .59 - 61

CONTENTS

Page

TECHNICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

ADJUSTMENT PROCEDURES . . . . . . . . . . . . . . . . . . .7 - 8

WIRING DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . .9 - 10

POWER SUPPLY SCHEMATIC DIAGRAM . . . . . . . . . .11 - 12

KEYBOARD SCHEMATIC DIAGRAM . . . . . . . . . . . . .13 - 14

POWER AMPLIFIER HEADPHOPNE / NAVICLICK . . . . 15 / 16

SCART INTERFACE SCHEMATIC DIAGRAM . . . . . . . .17 - 28

MAIN SCHEMATIC DIAGRAM . . . . . . . . . . . . . . . . .29 - 46

Page

POWER SUPPLY CIRCUIT BOARD . . . . . . . . . . . . . . . .47 - 48

KEYBOARD CIRCUIT BOARDS . . . . . . . . . . . . . . . . . .49 - 50

SCART INTERFACE CIRCUIT BOARD . . . . . . . . . . . . . .51 - 54

MAIN PRINTED CIRCUIT BOARD . . . . . . . . . . . . . . . . .55 - 58

ABBREVIATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . .59 - 61

INHALT

Page

TECHNISCHE DATEN . . . . . . . . . . . . . . . . . . . . . . . . . . .4

ABGLEICH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 - 8

BLOCKSCHATBILD ALLGEMEIN . . . . . . . . . . . . . . . .9 - 10

SCHALTBILD NETZTEIL . . . . . . . . . . . . . . . . . . . . .11 - 12

SCHALTBILD BEDIENTEIL . . . . . . . . . . . . . . . . . . . .13 - 14

LTPL KOPFHÖRERBUCHSE / NAVICLICK . . . . . . . . . .15 / 16

SCHALTBILD EUROPA NORMBUCHSE . . . . . . . . . . .17 - 28

SCHALTBILD HAUPTPLATINE . . . . . . . . . . . . . . . . .29 - 46

Page

LEITERPLATTE NETZTEIL . . . . . . . . . . . . . . . . . . . . . .47 - 48

LEITERPLATTE BEDIENTEIL . . . . . . . . . . . . . . . . . . . .49 - 50

LEITERPLATTE EUROPA NORMBUCHSE . . . . . . . . . . .51 - 54

GRUNDPLATTE . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55 - 58

ABKÜRZUNGEN . . . . . . . . . . . . . . . . . . . . . . . . . . .59 - 61

SOMMARIO

Page

DATI TECNICI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

PROCEDIMENTO REGOLAZIONI . . . . . . . . . . . . . . . . .7 - 8

DIAGRAMMA DELLE INTERCONNESSIONI . . . . . . . . .9 - 10

SCHEMA DEI CIRCUITI DI ALIMENTAZIONE . . . . . . .11 - 12

SCHEMA DEI CIRCUITI TASTIERA . . . . . . . . . . . . . .13 - 14

PIASTRA PRESE PER CUFFIA / NAVICLICK . . . . . . . .15 / 16

SCHEMA DELLA PRESA PERITEL . . . . . . . . . . . . . .17 - 28

SCHEMA DELLA PIASTRA PRINCIPALE . . . . . . . . . .29 - 46

Page

PIASTRA DEI CIRCUITI DI ALIMENTAZIONE . . . . . . . . .47 - 48

PIASTRE TASTIERA . . . . . . . . . . . . . . . . . . . . . . . . . .49 - 50

PIASTRA PRESA PERITEL . . . . . . . . . . . . . . . . . . . . .51 - 54

PIASTRA PRINCIPALE . . . . . . . . . . . . . . . . . . . . . . . .55 - 58

ABBREVIAZIONI . . . . . . . . . . . . . . . . . . . . . . . . . . .59 - 61

SUMARIO

Page

DATOS TECNICOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

PROCEDIMIENTOS DE AJUSTES . . . . . . . . . . . . . . . .7 - 8

ESQUEMA DE INTERCONEXIONES . . . . . . . . . . . . . .9 - 10

ESQUEMA DE LOS CIRCUITOS DE ALIMENTACIÓN . .11 - 12

ESQUEMA DE LOS CIRCUITOS MANDOS . . . . . . . . .13 - 14

PLATINAS TOMAS AURICULARES / NAVICLICK . . . . .15 / 16

ESQUEMA INTERFAZ EUROTOMA . . . . . . . . . . . . . . . .17 - 28

PLATINA PRINCIPAL . . . . . . . . . . . . . . . . . . . . . . .29 - 46

Page

PLATINA ALIMENTACIÓN . . . . . . . . . . . . . . . . . . . . . .47 - 48

PLATINAS MANDOS . . . . . . . . . . . . . . . . . . . . . . . . .49 - 50

PLATINA INTERFAZ EUROTOMA . . . . . . . . . . . . . . . .51 - 54

PLATINA PRINCIPAL . . . . . . . . . . . . . . . . . . . . . . . . .55 - 58

ABREVIACIONES . . . . . . . . . . . . . . . . . . . . . . . . . . .59 - 61

EN

FR

DE

IT

ES

Page 4

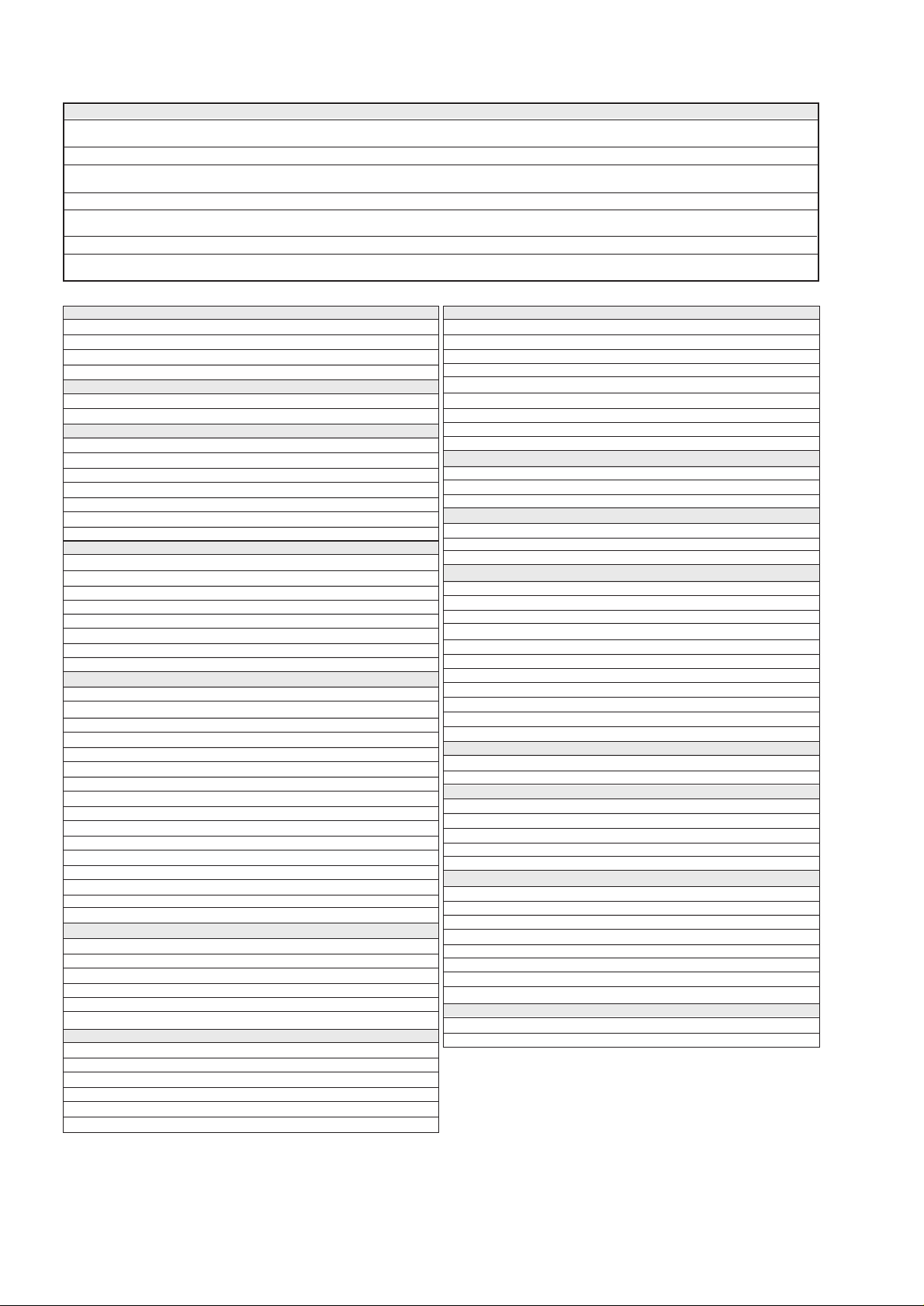

PLAYABLE DISK TYPE

Clock setting Auto(TXT/UTC)+manual

Video DVD-RW/-R/+R/+RW+S-VCD/VCD

Power back-up (min) Product life with auto reset

Audio CD audio + most of CD-R/CD-RW

TIMER

Regional code 2

Timer capacity 8 events / 1 year

Disk sizes 8 + 12 cm

Daily / weekly repeat Mo-Fr/Yes

VIDEO

Power back-up Product life

Output signal PAL / PAL 60 Hz / NTSC

VPS decoder Yes

Digital to analog converter 10 Bit / 27 MHz

PDC decoder Yes

Easy programming Naviclick

AUDIO

Digital to analog converter 96 kHz / 24 bits

Program guide Naviclick with NextView

Signal to Noise ratio 100 dB (Playback)

Dolby Digital 5.1 Passthrough

Instant recording Yes

DTS Passthrough

NextView Link Yes (No TV timer download)

MPEG 2 audio Passthrough

DISPLAY

Graphical user interface Yes

MP3 decoder built in / WMA Yes / No

Menu langages 6 (F/GB/D/E/I/S)

Virtual surround TruSurround

Front display technology Fluorescent

FRONT CONNECTORS

RCA Audio IN 2

RECORD FEATURES

RCA video IN 1

Hard Disk capacity (GB) NA

Y/C IN (HOSIDEN) 1

Recording Quality Levels Selection 6 levels (8h/6h/4h/3h/2h/1h)

Bit Rate Recording Based on Time 1 / 1.7 / 2.5 / 3.3 / 4 / 9.7 Mbps

One Touch Record from Front Panel or Rem Yes

REAR CONNECTORS

Number of scart sockets 2

… of which Y/C input 1

…of which RGB input 1

Scart AV2 with RGB loop 1

RCA video in 1

16/9 identification record / playback Yes

RCA video out 1

PAL Recording from PAL/SECAM signal Yes

Y/C in (Hosiden) 1

Y/C out (Hosiden) 1

RCA Audio IN 2

Disc library Yes (up to 400 titles)

RCA Audio OUT 2

Optimum Recording Level Yes

PLAYBACK FEATURES

Digital audio out Coaxial & Optical

Still picture Yes

Frame advance Yes

REMOTE CONTROL

Model RCT311DBM1

Repeat function DVD Disk / Title / A -B

Type 3 in 1 multibrand TV/SAT/DVD

Repeat function CD Disk/Track/A-B/Program

SUPPLIED ACCESSORIES

Repeat MP3

Song / Folder

RCU battery 2 x AAA

Program play Yes

Power cable / Plug CEE

Random play Yes

Scart cable Yes

Dealers mode Yes

Parental lock Yes

Other RF Antenna Cable

Zoom

Yes (DVD / jpeg)

IB languages F/GB/D/E/I

Variable search speed Yes

GENERAL DATA

Resume memory 1 disc

Product size (W x H x D in mm) 430 x 84 x 350

Introscan Yes (CD)

Packaging size (W x H x D in mm) 530 x 185 x 477

Scene again Yes

Weight : Net / Gross (Kg) 4.5 / 7

jpeg photos playback Yes (Slideshow)

EAN code 3244480137345

Power supply 230 V - 50 Hz

jpeg & music combinations palyback Yes (mp3 during slideshow)

Power consumption 36 W

EDIT FEATURES

Standby Power Consumption 7W / Eco : 5W

Title and Chapter creation Yes / Yes

Quantity by container (20"/40") 576 / 1152

Chapter hide / unhide Yes / Yes

NOTE*

Title Labelling (Text, thumbnail) Yes

Most (CD-R/RW)&( DVD-R/-RW/+R/+RW) Total compatibility not guaranteed

Titles Write Protected by Default (user Yes

Simultaneous Audio / Video Record Yes

Recordable disc type : DVD+R (2.4x / 4x) - DVD+RW (2.4x)

JPEG manipulation : Rotate / Zoom / Pan& Yes / Yes / Yes

RECEPTION

Tuning system PLL

Standard LL', BG, I, DKK'

Programme Number 99

NICAM / FM Stereo Sound L, BG, DK / BG, DK

DTH8005

4 First issue 12 / 04

TECHNICAL DATA - CARACTERISTIQUES TECHNIQUES TECHNISCHE DATEN - DATI TECNICI - DATOS TECNICOS

• THOMSON Multimedia reserves the right to change the specifications without notice

• Tous droits de modification des spécifications réservés.

• Änderungen der technischen Daten sind ohne Ankündigung möglich.

• Con riserva di modifica dei dati tecnici senza preavviso.

• Nos reservamos el derecho de modificar los datos técnicos sin previo aviso.

Digital Video Recorder +RW / +R* (* Recorded +RW/+R discs play on most

DVD-Video players)

Up to 8 hours recording time on a 4.7 GB disc 6 record modes ranging from the 1 hour top quality mode to the extra long 8-hours

NAVICLICK TV program guide on-screen with one-touch- recording Easy timer recordings with automatic naming from Teletext - Store and view instantaneously

Disc library contents of recorded DVD+R/+RW discs (up to 400 titles)

Disc library To store & view instantaneously the contents of your recorded DVD+R / +RW discs (up to 400 titles)

Smart Record Time Base Picture Corrector Automatic adjustment of recording quality to fit contents on the available disc space. Highest picture

RGB input and output For best Video signal reocrding and best playback picture quality from analog sources

Digital Photo View with simultaneous JPEG & mp3 playback Allows mp3 playback during J-PEG photo slideshow, playback of DVD discs, CD audio, Video CDs,

FEATURES BENEFITS

Record from TV, camcorder, or other video device in digital quality on Write once / ReWritable DVDs

(DVD+R /DVD+RW)

quality to copy VHS tape to disc (stabilize Sync & color sub-carrier)

S-VCDs, most CD-R / CD-RW*

Page 5

DTH8005

First issue 12 / 04 5

Invisible laser radiation when open and interlock

failed or defeated. Avoid direct exposure to beam.

Le rayon laser est invisible. Eviter l'exposition directe

lors de la maintenance.

Bei geöffneter Schublade und Defekt der Sicherheitsvorrichtungen besteht die Gefahr unsichtbaren

Laserlichts. Niemals direkt in den Laserstrahl sehen.

Il raggio laser è invisible. Evitare l'esposizione diretta

durante la manutenzione.

El rayo laser es invisible. Evitar la exposición directa

en el momento del mantenimiento.

DANGER :

ATTENTION :

VORSICHT BEI

REPARATUREN :

ATTENZIONE :

IMPORTANTE :

CLASS 1 LASER PRODUCT

APPAREIL A LASER DE CLASSE 1

LASER KLASSE 1

APPARECCHIO CON LASER DI CLASSE 1

APARATO CON LASER DE CLASE 1

IMPORTANT SAFETY NOTICE

There are special components used in this equipment which are imporant for safety. These part are marked by symbol on the schematic

circuit diagrams and replacement part list. It is essential that these safety critical components are replaced with the manufacture’s specified

parts to prevent electric shock, fire, or other hazards. do not attempt to modify the original design without permission of the manufacturer.

REMARQUES DE SECURITE IMPORTANTE

Il y a des composants spéciaux utilise dans cet appareil qui sont important pour la sécurité. Ces pièces sont repérées par un symbole

sur les schémas de principes et la liste de pièces détachées. Il est essentiel que ces composants de sécurité soient remplacés par les

pièces spécifiques du constructeur pour éviter les chocs électriques, feux ou autres risques. Ne tentez pas de modifier la conception

originale sans autorisation du constructeur.

WICHTIGER SICHERHEITSHINWEIS

In diesem Gerät wurden sicherheitsrelevante Komponenten verwendet. Diese Teile sind im Schaltbild und in der Ersatzteilliste mit

einem Symbol markiert. Es ist wichtig, dass diese kritischen Komponenten ausschließlich durch solche ersetzt werden, die den

Spezifikationen des Herstellers entsprechen. Die Produkthaftung des Herstellers erlischt bei Einsatz von nicht den Spezifikationen

entsprechenden Sicherheitsbauteilen und bei eigenmächtigen Schaltungsänderungen.

IMPORTANTE INFORMAZIONE DI SICUREZZA

Ci sono speciali componenti usati in questa apparecchiatura che sono importanti per la sicurezza. queste parti sono facilmente identificabili,

sullo schema e sulla lista parti, da un apposito simbolo . E’ indispensabile che questi componenti di sicurezza, nel caso di alterazioni o

guasti, vengano sostituiti con specifici ricambi originali per evitare shock elettrici, fuoco o altri rischi. Non modificare mai il circuito senza

autorizzazione della casa costruttrice.

AVISO IMPORTANTE SOBRE SEGURIDAD

En este equipo se utilizan componentes especiales que son muy importantes para la seguridad. están marcados con el símbolo en los

esquemas eléctricos y en las listas de repuestos. Es fundamental que estos componentes críticos de seguridad, sean reemplazados por las

piezas originales indicadas por el fabricante para evitar los peligros de electrocución, de fuego, etc. y no modificar el diseño original sin

autorización del fabricante.

EN Prevention of electro static discharge (esd) to Electrostatically Sensitive Devices (ESD)

Some semiconductor devices can be damaged easily by static electricity (integrated circuits, some field-effect transistors and

semiconductor chip components. The following techniques should be used to help reduce the incidence of component damage caused

by static electricity.

1. Immediately before handling any semiconductor component or semiconductor-equipped assembly, drain off any electrostatic charge

on your body by touching a known earth ground or wear a discharging wrist strap device, which should be removed for potential

shock reasons prior to applying power to the unit under test.

2. After removing an electrical assembly equipped with ESD devices, place the assembly on a conductive surface such as aluminum

foil.

3. Use only a grounded-tip soldering iron to solder or unsolder ESD devices.

4. Use only an anti-static solder removal devices.

5. Do not use freon-propelled chemicals.

6. Do not remove a replacement ESD device from its protective package until immediately before your are ready to install it.

7. Immediately before removing the protective materials from the leads of a replacement ESD device, touch the protective material to

the chassis or circuit assembly into which the device will be installed.

CAUTION : Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

8. Minimize bodily motions when handling unpackaged replacement ESD devices

Page 6

DTH8005

6 First issue 12 / 04

FR Prévention des composants et sous-ensembles contre les ESD ( Décharge d'Electricité Statique )

Certains semi-conducteurs peuvent être facilement endommagés par l’électricité statique (les circuits intégrés et certains transistors à

effet de champs, les composants semi-conducteurs de type chip ainsi que les diodes à émission laser équipant les lecteurs optiques ).

Les précautions suivantes doivent être utilisées pour réduire l’incidence des dommages causés par l’électricité statique.

1. Immédiatement avant de manipuler tout composant semi-conducteur ou ensemble équipé de semi-conducteurs, éliminez toute charge

électrostatique de votre corps en touchant une terre connue. Ou bien, mettez un bracelet antistatique, qui doit être retiré, pour des

raisons de choc électrique, avant de mettre l’appareil sous tension.

2. Après démontage d’un ensemble électrique équipé d’éléments sensibles aux ESD, Placez l’ensemble sur une surface conductrice telle

qu’une feuille d’aluminium.

3. N’utilisez qu’un fer à souder relier à la masse pour souder ou dessouder ces composants.

4. Pour dessouder, n’utilisez que du matériel antistatique

5. N’utilisez pas de produits chimiques à propulsion de fréon.

6. Ne retirez pas ces composants de leur emballage de protection jusqu’à ce que vous soyez prêt à l’installer.

7. Juste avant de retirer la protection des broches de ces composants, touchez la protection sur le châssis ou le circuit dans lequel le

composant va être installé.

ATTENTION : Assurez-vous que le châssis ou le circuit n’est pas sous tension, et observez toutes les autres précautions de sécurité.

8. Minimisez les déplacements corporels lorsque vous manipulez un de ces composants de remplacement déballé.

DE Vermeidung von Elektrostatischer Entladung (ESD)

Manche elektronische Komponenten wie Transistoren, Integrierte Schaltkreise oder Chipelemente können leicht durch ESD beschädigt

oder zerstört werden. Die folgenden Richtlinien helfen Schäden durch ESD zu vermeiden.

1. Unmittelbar vor dem Hantieren Halbleitern oder Baugruppen mit Halbleitern leiten Sie die statische Aufladung Ihres Körpers durch

Berühren einen geerdeten Gegenstandes ab. Beschaffen Sie sich ein leitendes Hansgelenkband. Dieses müssen Sie allerdings vor dem

Einschalten des zu prüfenden Gerätes ablegen.

2. Nach dem Ausbau einer empfindlichen elektronischen Baugruppe legen Sie diese auf einen leitende Unterlage wie Aluminium-Folie um

eine elektrostatische Entladung zu vermeiden.

3. Benutzen Sie für Lotarbeiten an empfindlichen Komponenten einen geerdeten Lötkolben.

4. Benutzen Sie antistatisches Entlötwergzeug.

5. Verwenden Sie keine Sprays, die Freon als Treibmittel enthalten. Diese können ausreichend elektrostatische Ladung erzeugen, um

empfindliche Komponenten zu schädigen.

6.

Entfernen Sie die Antistatik-Schutzverpackung (Alu-Folie, Leitgummi, Leitfolie, ..) von Komponenten und Baugruppen erst wenn Sie diese benötigen.

7. Unmittelbar vor dem Entfernen der Schutzverpackung führen Sie ein Potentialausgleich durch Berühren des Gerätes mit der

Komponente/Baugruppe durch. ACHTUNG: Stellen Sie Sicher, Dass das Gerät nicht unter Spannung steht und beachten Sie alle

einschlägigen Sicherheitsvorschriften.

8. Bewegen Sie sich beim Hantieren mit empfindlichen Komponenten/Bausteinen möglichst wenig, da die Reibung Ihrer Kleidung oder

der Füße auf dem Bodenbelag elektrostatische Ladung erzeugen kann.

IT

Azioni preventive contro le scariche elettrostatiche (esd) sui Dispositivi Sensibili Elettrostaticamente (ESD)

Alcuni semiconduttoripossono essere facilmente danneggiati da elettricità statica (circuiti integrati, alcuni transistor ad effetto di campo e

componenti chip semiconduttori). Al fine di ridurre l’incidenza dei componenti danneggiati a causa di elettricità statica si dovrebbero

osservare le seguenti precauzioni.

1.

Immediatamente prima di maneggiare qualsiasi tipo di componente semiconduttore o di apparecchio che impiega semiconduttori, scaricare le

possibili cariche elettrostatiche del proprio corpo toccando un punto sicuramente collegato a terra. In alternativa, indossare un apposito braccialetto

antistatico che dovrebbe però essere tolto, per possibili potenziali shock, immediatamente prima di alimentare l’apparecchiatura sotto test.

2. Dopo il disimballo porre l’apparecchiatura equipaggiata con dispositivi ESD su una superficie conduttiva tipo foglio di alluminio.

3. Usare saldatori con punta a massa per saldare o dissaldare dispositivi ESD.

4. Usare solo saldatorI antistatici.

5. Non usare prodotti chimici tipo freon.

6. Rimuovere il dispositivo ESD dal suo imballo protettivo solo immediatamente prima del suo utilizzo.

7. Immediatamente prima della rimozione del materiale protettivo dai piedini del dispositivo ESD di ricambio, toccare con il materiale

protettivo il telaio o la massa del circuito stampato dove il dispositivo deve essere inserito.

ATTENZIONE : Assicurarsi che il circuito o il telaio non sia alimentato, e osservare tutte le altre precauzioni di sicurezza.

8. Limitare gli spostamenti quando si maneggia un dispositivo ESD disimballato.

ES Prevención contra descargas electro-státicas (esd) para los DISPOSITIVOS SENSIBLES electrostáticamente (ESD)

Algunos dispositivos semiconductores, pueden ser dañados fácilmente por la electricidad estática (los circuitos integrados, algunos

transistores de Efecto de Campo y los semiconductores "chip"). Las siguientes técnicas pueden ser utilizadas para ayudar a reducir la

destrucción de los componentes causada por la electricidad estática.

1. Inmediatamente antes de manejar cualquier componente semiconductor o conjunto equipado con semiconductores, elimine la carga

electrostática de su cuerpo tocando alguna toma de tierra conocida o utilizar una correa conductora conectada a una toma de tierra que

se pone en la muñeca la cual debe ser quitada (por razones de seguridad) antes de conectar la alimentación al equipo bajo prueba.

2. Después de quitar un conjunto equipado con componentes ESD, coloque el conjunto sobre una superficie conductora, como papel aluminio.

3. Utilizar únicamente soldadores con la punta conectada a la toma de tierra para soldar o desoldar componentes ESD.

4. Utilizar solamente soldadores antiestáticos para quitar componentes.

5. No utilizar productos químicos con gas freón como propelente.

6. No sacar de su embalaje protector el nuevo componente ESD hasta inmediatamente antes de estar todo preparado para montarlo.

7. Inmediatamente antes de quitar los materiales de protección de las patillas del componente, tocar el material protector al chasis del

conjunto donde se vaya a montar el componente.

CUIDADO : Asegúrese de que la alimentación no esté aplicada al chasis o circuito, y cumpla todas las precauciones de seguridad.

8. Maneje sin movimientos bruscos el componente ESD una vez desempaquetado.

Page 7

DTH8040

First issue 12 / 04

To RE_INITIALIZE the recorder to factory defaults settings,

- Switch “ON” the recorder and wait until “MENU” is displayed in the front

panel display.

- Simultaneously press the “STOP” and “STANDBY / ON” keys on

the front panel until the display changes to read “INIT” and then release

the keys.

- When the recorder has been re-initialized the display will flash “INIT OK”

for a split second.

- Now all the previous setting will be reset to the original factory default

settings.

Wiederherstellen der Fabrikeinstellungen (Neuinitialisierung)

Schalten Sie das Gerät ein; das normale Hauptmenü erscheint.

- Drücken Sie am Gerät gleichzeitig die Tasten STOP und

STANDBY / ON bis auf dem Geräte-Display " INIT " erscheint.

- Die Neuinitialisierung des Gerätes benötigt einige Zeit.

- Wenn die Neuinitialisierung abgeschlossen ist, erscheint " INIT OK ".

- Alle vorherigen Einstellungen sind nun auf die Fabrikeinstellungen

zurückgesetzt.

Initialisation des valeurs par défaut.

Mettre l’ appareil sous tension. Le menu principal apparait.

-Appuyer et maintenir enfoncées les touches “STOP”

et “STANDBY” / “ON” du clavier de la face avant jusqu’à

l’apparition du message " INIT " dans l’afficheur.

-L ’orsque l’initialisation est complète le message " INIT OK "

s’affiche. Les réglages sont initialisés aux valeurs usines.

Inizializzazione dei valori di default

-Collegare l'apparecchio alla rete e far visualizzare il menu principale.

- Premere e mantenere premuti i tasti "STOP" , e "STANDBY/ON"

del frontale fino all'apparizione del messaggio "INIT" sul display.

- Alla fine dell'operazione, verrà visualizzato il messaggio "INIT OK"

sul display.

Le regolazioni sono inizializzate ai valori di "DEFAULT".

Inicialización de los ajustes a los valores por defecto.

Conectar el aparato a la red. Aparecerá el menú.

- Mantener pulsadas las teclas STOP y STANDBY / ON

en el panel frontal hasta que salga el mensaje " INIT " en el display.

- En unos pocos segundos se habrán restaurado los ajustes.

- Cuando se ha completado, se verá el mensaje " INIT OK ".

- Los ajustes habrán sido inicializados a los valores por defecto de

fábrica.

EN

FR

DE

ES

IT

Accessing the SERVICE MENU

-Connect the recorder to the mains supply and a monitor television

using a SCART lead.

-Switch “ON” the recorder and then press the “MENU” key on the RCU.

-The recorders “MAIN MENU” will now be displayed on the screen of

the television.

-Next simultaneously press the “PLAY” and “RECORD”

keys on the front panel depressed until the Service Menu is displayed

on the screen of the television.

Aktivierung des SERVICE-MENÜS

- Verbinden Sie den Recorder mit der Netzspannung und mittels eines

SCART-Kabels einem TV-Gerät.

- Schalten Sie den Recorder mit „ON“ ein und drücken auf der

Fernbedienung die „MENU“-Taste.

- Auf dem Bildschirm wird das Hauptmenü des Recorder angezeigt.

- Drücken Sie am Bedienfeld des Recorders gleichzeitig die Tasten

„PLAY“ und „RECORD“

bis auf dem Bildschirm das Service-Menü angezeigt wird.

Acceso al modo servicio.

-Conectar el aparato a la red. Un menú aparecerá.

-Seleccionar el menú principal pulsando la tecla “MENU” del

telemando

-Pulsar a la vez las teclas “PAUSE “ y “ RECORD “.

-Mantener las 3 teclas pulsadas hasta que aparezca el menú

principal del Modo Servicio

Accès au mode service.

-Mettre l’ appareil sous tension. Le menu principal apparait.

-Sélectionner le menu principal en appuyant sur la touche

“MENU” de la télécommande

-Appuyer sur les touches “PLAY “ et “ RECORD “.

-Maintenir enfoncées les touches ensembles jusqu’a

l’apparition du menu principal du mode service

Accesso al Service Mode

-Collegare l'apparecchio alla rete

-Premere il tasto "MENU" del telecomando per far apparire il

Menu principale.

-Premere e mantenere premuti i tasti "PLAY" e "RECORD" fino

all'apparizione del menu principale del service

Mode.

Service Menu

I2C BUS I OK

VERSION

ST20 A3GEU_S5.13

ST9 S1.2

KDB S2.2

Gob Version 0xf

Bootloader C3-R4.00

RIC0H V108b

3

I2C BUS II OK

ODD Error 0

HDD Status N.A

HDD Error 0

EN

FR

DE

ES

IT

SERVICE MODE - MODE SERVICE - SERVICE MODE - SERVICE MODE

MODO SERVICIO

INITIALIZATION - INITIALISATION - NEUINITIALISIERUNG - INIZIALIZZAZIONE

INICIALIZACIÓN

CHECKS AND MEASUREMENTS - CONTRÔLES ET VERIFICATIONS

CONTROLLI E VERIFICHE - AJUSTES Y COMBROBACIONES

1Vpp

1Vpp

(Top SCART)

(Top SCART)

N

•

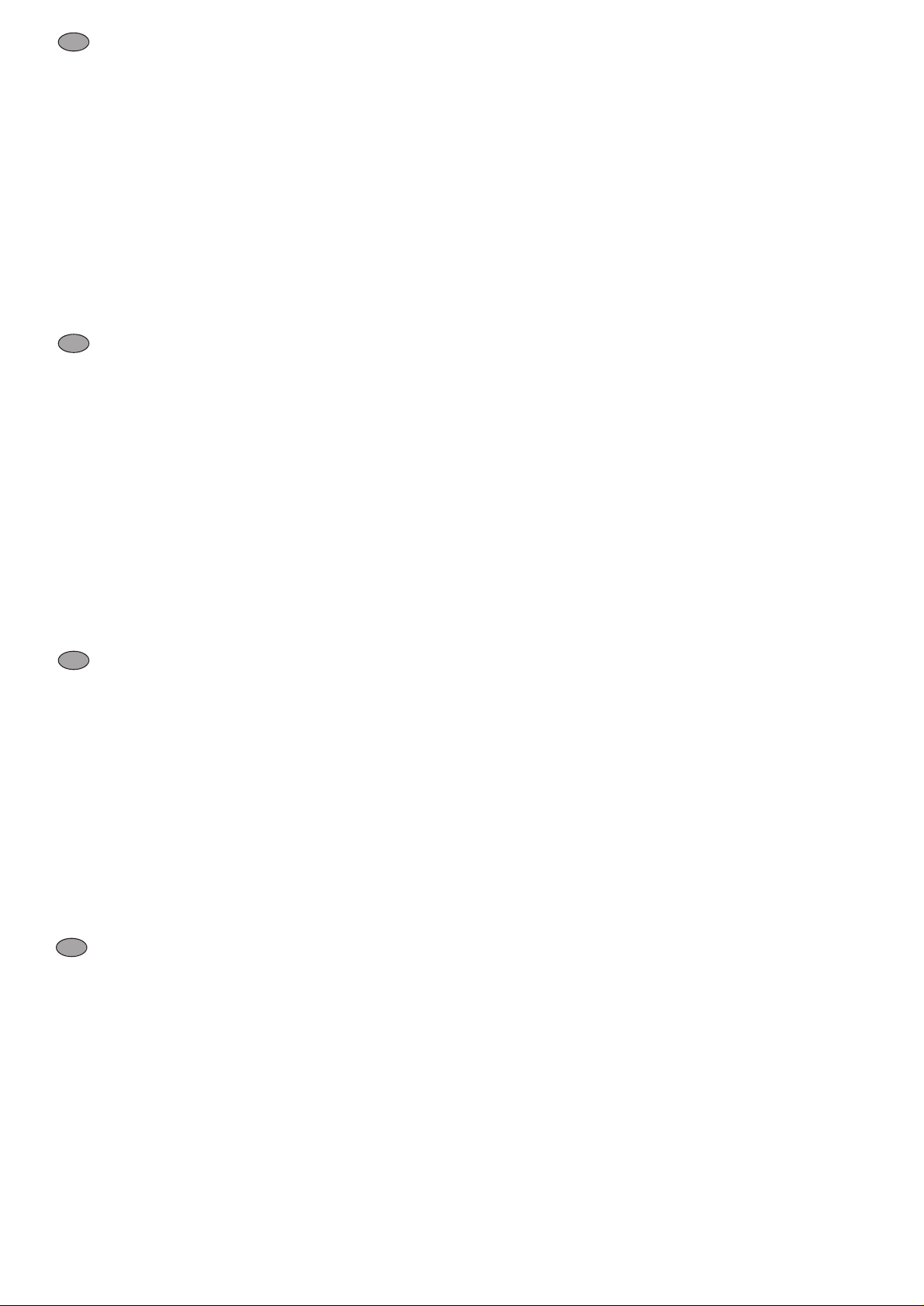

Item Mode & Signal Test equipment Test point Description

A CVBS PB level Oscilloscope AV1 pin19 None Check for CVBS= 1Vpp ± 0.1Vpp

Select AV1

PAL / SECAM

Adjustment

point

BW125

Video Playback Output Signal check - (Disk ) Controle Video Lecture Video - Überprüfung Videowiedergabepegel - Controllo uscita Riproduzione Video

Nivel de salida de reproduccion de video

BURST = 286mVpp ± 28,6 mVpp

( DVD )

( DVD disk test )

colour bar test pattern

20 BW125 (Top SCART)

colour bar test pattern

1Vpp

N

•

Item Mode & Signal Test equipment Test point Description

B CVBS EE level Oscilloscope AV1 pin19 None Check for CVBS= 1Vpp ± 0.1Vpp

Select AV1

PAL / SECAM

Adjustment

point

BW125

Video -E to E (AV input/AV output) - Video EE ( AV . Entree / Sortie AV ) - Video EE (AV-Eingang/AV-Ausgang) - Video -EE ( AV input/AV output - Video

EE (entrada / salida AV )

Page 8

DTH8040

First issue 12 / 04

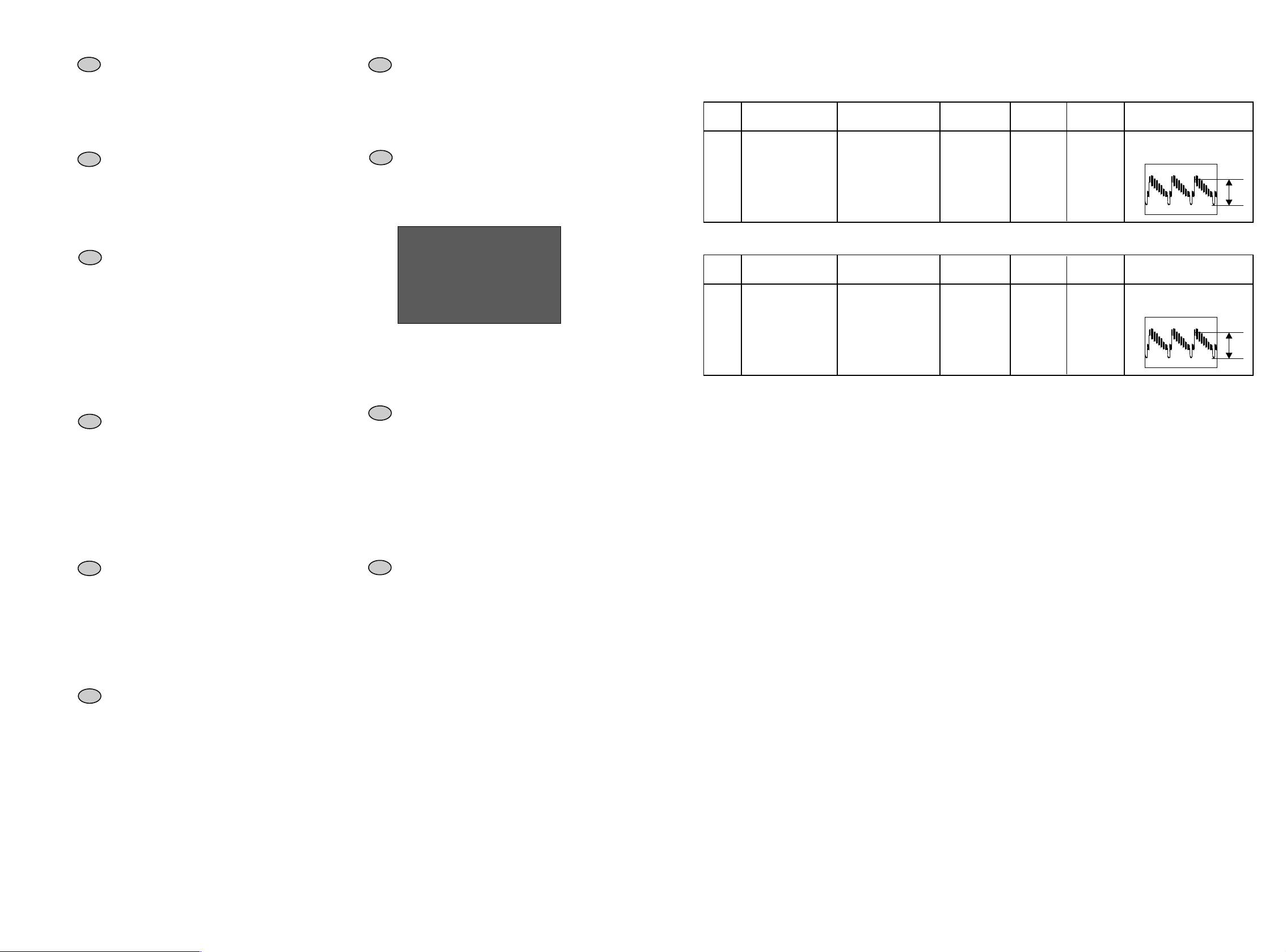

WIRING DIAGRAM - SCHEMA D’INTERCONNEXIONS - VERDRAHTUNGSPLAN - DIAGRAMMA DELLE INTERCONNESSIONI - ESQUEMA DE INTERCONEXIONES

FAN

21

TUNER

AV/TUNER(EU) BOARD

BB601A

+12VE

+40VS

GND

+9VE

+5VS

GND

+12VS

+5VE

9

8

7

6

5

3

24-5VE

1

AC

INLET

246

3

1

DGND

IDE_D7

IDE_RST

BB801H

8

10

9

7

5

1114151617181920212223

IDE_D3

IDE_D4

IDE_D5

IDE_D6

IDE_D9

IDE_D8

IDE_D11

IDE_D10

IDE_CONNECTOR

RICOH RW5240V24T

12

13

IDE_D2

IDE_D12

IDE_D1

IDE_D13

FEM

IDE_D0

IDE_D14

DGND

IDE_D15

NC

DGND

DMARQ

DIOW

24

DGND

25

DIOR

26

DGND

27282930313233343536373839

CS0

CS1

DA1

DA0

DA2

DGND

IORDY

DGND

DMACK

IDE_IRQ

HDD_NODD

PDIAG

BB301H

+12VS

GND

GND

+5VS_HDD

DASP

10

GND

40

DGND

975

864

C_FRONT_REC

Y_FRONT_REC

SV_F

GND

BB309A

1

2

3

4

R_FRONT

GND

3

2

L_FRONT

GND

1

CV_FRONT_REC

1

BW101

2

BB101A

POWER

DGND

DGND

IR_SAT

SPDIF_OUT

R_PR2H_DXX

SCART2_PIN8

246

5

3

1

DGND

IR_SAT

AV2_PIN8

SPDIF_OUT

R_PR2H_DXX

MODU_MODE_CTL

AGND

AVLINK_W

7

AGND

AGND

G_Y2H_DXX

AUDIO_SEL2

AUDIO_SEL1

B_PB2H_DXX

RGB_YUV_SEL

987654321

8

10

12

9

13

1114151617181920212223

AGND

AGND

G_Y2H_DXX

AUDIO_SEL1

AUDIO_SEL2

B_PB2H_DXX

RGB_YUV_SEL

CVBS_DXX

AGND

C_DXX

CVBS_DXX

181716151413121110

1920212223

AGND

Y_DXX

1H2H_SEL

AUD_R_OUT

HW_SW

AUD_R_OUT

AUD_L_OUT

24

24

DGND

AUD_L_OUT

AGND

AGND

AGND

Y_DXX

C_DXX

HW_SW

1H2H_SEL

DIGITAL BOARD

NC

GND

GND

AGND

AUD_R_REC

252627

26

25

DGND

AUD_R_REC

GND

AUD_L_REC

NICAM_RST

CV_TUNER1_REC

30

28

29

313233

272829303132333435363738394041424344454647484950515253545556575859

GND

GND

GND

CVBS1_REC

AUD_L_REC

NICAM_RST

EU_TUNER1_REC

NC

GND

GND

GND

S_CLK1

AVLINK_R

AV3/AV4_CV/Y_REC

34

35373941434547

GND

Y1_REC

AV3/AV4_C_REC

SCART_TV_CV/Y_REC

42

40

38

36

GND

DGND

S_IN1 S_IN1

S_CLK1

C1_REC

TUNER_REC

CVBS2_REC/G

SCART_VCR_CV/Y_REC

44

GND

Y2_REC/B

GND

FAN_FAIL

12C_CLK1

12C_DATA1

AUDIO_SEL3

SCART_VCR_C/R_REC

50

48

46

49

GND

FAN_ON

FAN_FAIL

C2_REC/R

12C_CLK1

12C_DATA1

GND

SCART2_B

SCART2_G

SCART2_FB

54

52

53

51

PR_REC

VDEC_VS

VDEC_HS

GND/SCART_FB

BB101D

SV_F

SV_R

DGND

16/9_S1

58

575655

DGND

16/9_S1

SV_R/SAPR-VS

SV_F/SAPR_HS

BB401D

+3V3SD

+2V5SD

+12VS_FLASH

PWR_DOWN

-5VE

16/9_S2

60

59

60

-5VE

16/9_S2

DGND

DGND

+9VE

+5VSA

AGND

+5VED

DGND

+3V3SD

1

GND

2

3

+2.5VS

4

GND

+12VS

5

6

+9VS

+5VSA

7

GND

8

9

PWR_OK

10

+5.4VE

GND

1

2

3

4

5

6

7

8

9

10

11

11

+12VS

1

GND

2

GND

3

+5VS_FEM

4

BOARD

BB401P

BB301P

DVDR SCH IDR04

WIRING DIAGRAM DTH8040E

DGND

IDE_RST

IDE_D7

IDE_D4

IDE_D5

IDE_D9

IDE_D6

IDE_D8

IDE_D10

987654321

KDB BOARD

IDE_CONNECTOR

IDE_D1

IDE_D2

IDE_D3

IDE_D14

IDE_D13

IDE_D12

IDE_D11

10

NC

DIOR

DIOW

IDE_D0

DGND

IDE_D15

DMARQ

2120191817161514131211

DGND

DGND

DGND

DGND

IORDY

DMACK

22232425262728293031323334353637383940

DGND

IDE_IRQ

HDD_NODD

DA17

PDIAG

BB801D

CS1

CS0

DA2

DA0

DASP

DGND

BB206D

VFD_DATA

VFD_STB

VFD_CLK

DGND

BB206K

I2C_CLK

KDB_RST

I2C_DATA

3

1

2

NC

IR

DGND

VFD_IQR

AV2_PIN8

654

BB201P

1

2

3

4

5

6

1

-VKK

PWR_OK

2

VFD_ON

3

-FL

BB201K

C_FRONT

GND

10

9

S_2

8

Y_FRONT

AGND

6

7

R_FRONT

AGND

4

5

L_FRONT

3

+FL

DGND

+5VE

CV_FRONT

GND

2

1

4

5

6

7

FAV BD

BB309F

BB601P

9

+13.5VE

+40VS

2345678

+12VS_FAN

+5.4VE1

+5VSA

+9VS

-5VE

GND

GND

-FL

+FL

-VKK

VFD_ON

PWR_OK

1234567

DGND

+5.4VE

Page 9

DTH8040

First issue 12 / 04

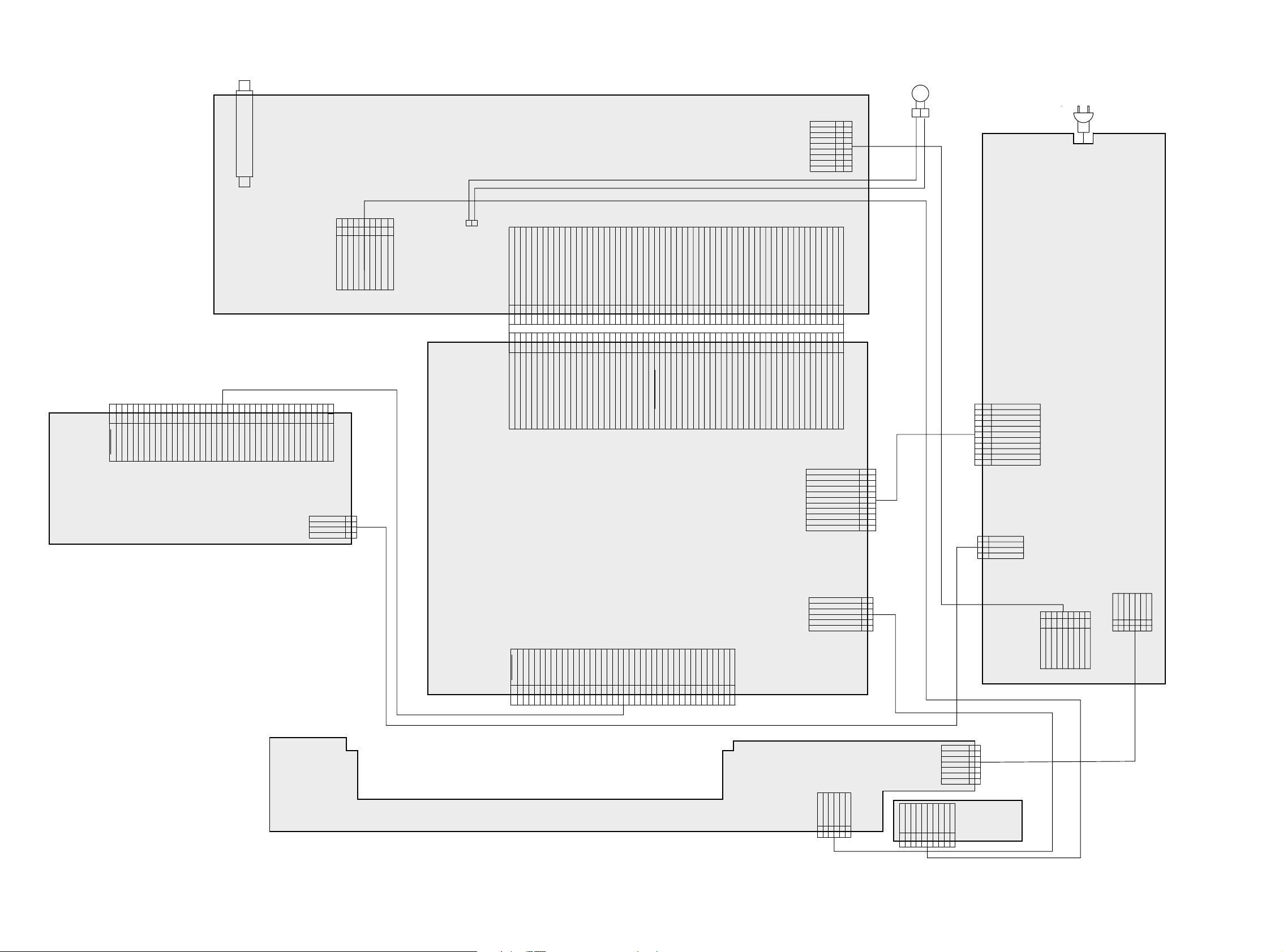

Mainsvoltage

POWE

Part of board connected to mains supply.

Partie du châssis reliée au secteur.

Primärseite des Netzteils.

Parte dello châssis collegata alla rete.

Parte del chassis conectar a la red.

Use isolating mains transformer.

Utiliser un transformateur isolateur du secteur.

Einen Trenntrafo verwenden.

Utilizar un transformador aislador de red.

Utilizzare un transformatore per isolarvi dalla rete.

Achtung :

Bei Messungen im Primärnetzteil

- Primärnetzteilmasse verwenden ( ).

Note :

Power Supply primary circuit measurements.

- Use only ( ) connection point.

Attention :

Mesure dans la partie primaire de l'alimentation

- Utiliser la masse du bloc alimentation ( ).

Attenzione :

misure nell'alimentatore primario

- usare massa alimentazione primario ( ).

Cuidado :

Medida en el bloque de alimentacion

- Utilizar la masa del bloque de alimentacion ( ).

Safety Part

When repairing, use original part only

Pièce de securité

N'utilisez que les pièces d'origine

Utilice solo piezas originales

Bei Ersatz nur Originalteil verwenden

Sicherheitsbauteil

Pieza de seguridad

Per la riparazione utilizzare solo componenti originali

Componenti di sicurezza

220R

RP058

22uF/50V

CP069

10R

RP056

4x1N4007

DP003

DP002

DP005

DP004

1000uF/16V

CP058

*

FP001

STP22NF03L

TP052

*

RP019

RP022

180K/0.25W

100nF

CP002

TL431

IP052

RGP10G

DP013

47uF/50V

CP062

2200uF/6.3V

CP053

6u8H

LP055

470uF/10V

CP061

S410D

DP065

STPS2045CT/MBR2045CT/MBRP2045N

DP052

A2A1

C

4K53/1%

RP080

7K5/1%

RP070

ECK

A

TCET1103G

IP050

1

2

3

4

10K

RP052

*

RP044

10K

RP048

1000uF/16V

CP063

S410D

DP059

JP100

IN4148

DP088

BZX55C6V8

DP069

*

RP054

10k

RP053

BC858B

TP058

*

RP041

20K

RP050

7R5/0.25W

RP078

KTC3112B

TP066

1N4148

DP055

1uF/50V

CP066

3K6/1W

RP083

IN5817

DP063

47uF/50V

CP086

BP001

1

2

6K8

RP059

2K2/1W

RP062

RP011

*

*

CP010

*

RP015

2n2F/400V

CP050

RN2402

TP065

*

RP014

23mH

LP002

1

2

4

3

*

RP013

IN4148

DP070

*

CP014

*

RP012

CP008

*

*

RP018

BZX55B33

DP009

IN4148

DP057

BC848B

TP054

2200uF/6.3V

CP054

390R

RP071

KTC3112B

TP011

1K

RP072

470uF/10V

CP074

47uF/50V

CP057

RP010

470R

BZX55C15

DP012

BZX55C15

DP011

1K24

RP060

BC848B

TP053

1K05

RP061

RGP15G

DP010

*

RP024

10R

RP023

*

CP016

6V2/1.3W

DP056

BB301P

1

2

3

4

*

RP043

*

RP042

*

TP041

*

RP051

*

RP082

BB701P

1

2

3

4

*

TP076

*

RP046

*

DP068

10K/0.25W

RP097

*

TP055

1N4148

DP086

TP010

HEATSINK

STP6NK90ZFP

BC848B

TP059

*

TP077

10K

RP047

9V1

DP089

2n2F

CP071

KTC8050D

TP088

470uF/10V

CP055

6V2/1.3W

DP090

2n2F

CP073

1R5/7W

RP055

RGP10G

DP008

STP22NF03L

TP061

2K

RP092

*

RP085

2K2/1W

RP079

4K7

RP073

10uF

CP065

*

RP081

*

RP069

470R

RP084

2n2F

CP078

2137005C

SCH_SMPS_IDR04_360MM

2n2F

CP079

LP050

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1516

17

120R

RP094

*

TP044

0R

LP010

12

RGP10G

DP066

*

RP095

2n2F

CP080

2n2F

CP081

2n2F

CP087

2n2F

CP085

*

TP078

2n2F

CP082

*

CP013

2n2F

CP084

(PREP)

TP070

100nF

CP068

P

T1.25A_125V

FP051

470uF/10V

CP064

*

RP096

10K

RP074

(PREP)

RP089

(PREP)

RP090

(PREP)

RP091

(PREP)

TP073

100R

RP088

BC848B

TP067

P

T1.25A_125V

FP050

120R

RP093

(PREP)

CP088

*

RP087

BC848B

TP064

10K

RP067

(PREP)

CP017

*

RP021

10K

RP066

*

RP045

2n2F

CP077

*

CP015

*

RP020

(PREP)

CP095

120R

RP101

*

RP077

10uF/50V

CP076

1R

RP100

*

RP098

*

TP056

0R

RP099

BB601P

1

2

3

4

5

6

7

8

9

(PREP)

CP099

(PREP)

CP098

(PREP)

CP096

(PREP)

CP097

BB201P

1

2

3

4

5

6

7

4p7F

CP094

4p7F

CP093

BB401P

1

2

3

4

5

6

7

8

9

10

11

*

CP018

470uF/10V

CP060

(PREP)

CP092

470pF/1KV

CP091

470pF/1KV

CP090

750R/2W

RP063

(PREP)

TP086

330R

RP065

*

RP049

-FL

-FL

VDRIVE

VDRIVE

PWR_OK

PWR_OK

PWR_OK

PWR_OK

VKK

VKK

GND

GND

GND

GND

GND

GND

GNDGND

GND

GND

GNDGND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDGND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PGNDPGND

PGND

PGND

PGND

PGND

PGND

PGNDPGND

PGND

PGND

PGND

PWR_ON/OFF

PWR_ON/OFF

VDRIVE_1

VDRIVE_1

+5VS_FEM

+13.5VE

+5.4VE

VFD_ON

VFD_ON

+FL

+FL

+40VS

100R/1W-RP098

-0RRP077

330R1KRP013

200R/2W470R/2WRP024

1nF/1KV

4n7F/63V33nF/63VCP014

27K47KRP012

-

-

18K

180K

180K

180K

180K

18K

150uF/400V

13-05-0

B

BD434TP056

100R/1WRP098

KTC8050DTP076

100pF/1KV470pF/2KVCP010

RP046

-0RRP096

0RRP095

RN2402

TP077

TP078

RN2402

3K6/1W-

-

-

-

-

RP082

-0RRP081

8n2F/63VCP016

10uF/50V-CP018

-100nFCP015

KTA1273Y

100K

1K

620R

2n2FCP013

-0RRP087

100R/1W

1N4148DP068

TP055

9K1RP049

RP014

47K

"-" MEANS NO PART INSERTED

NOTE:

T_1.0AL_250VT_1.6AL_250V

FP001

10M8M2RP015

EU(VAL)US(VAL)EU(VAL)US(VAL)

0RRP085

BC858BTP044

BC858BTP041 -

-

-

-

-

-

-

12K100KRP069

68K100KRP054

9K110KRP051

-RP045

-RP044

22K-RP043

-RP042

1K0RRP041

RP021

RP020

RP019

R390/2W R68/2.5WRP011

220uF/200VCP008

91K

91K

91K

91K

RP018

* REF. DES. * REF. DES.

(PREP)

/1%

/1%

PGND

PGND

PGND

PGND

PGND

SCH_SMPS_IDR04_360MM

2

2

0,1

0,3

-18,5

-18,5

-17,7

5,2 5,3 5,4

0,1

-1

-1

4,8

5,3

5,4

5,4

6

5,4

13,5

13,5

9,3

9,9

13,7

12,3

0

4,3

4,8

5,2

2,5

4,6

4,6

3,9

39

38,8

19,3

0,2

5

0,7

3,4

3,3

2,8

5,4

5,7

5,3

5,2

5,5

0

+40VE

+40VE

+3.3VS

+3.3VS

+5VS_FEM

+12VS

+12VS

+12VS

+13.5VE

+2.5VS

+2.5VS

+5.4VE

+5.4VE

+5.4VE

+5.4VE

+5.4VE

+5.4VE

+5.4VE

+5.4VE

+5.4VE

+5.4VE

+9VS

+9VS

+9VS

+12VS_FAN

+12VS_FAN

-5VE

-5VE

+5VSA

+5VSA

+5VSA

+5VSA

+5VSA

+40VS

+300

+40VS

+40VS

Somes Models

300 : On, EE Voltage

T=4,6us

T=4,6us

700Vpp

0

0

10Vpp

(+303)

(0)

(0,5)

(1,6)

(2,5)

(2)

(4)

(0)

(-15,6)

(5,2)

(12,8)

(5,4)

(5,4)

(5,4)

(3,3)

(2,6)

(0,2)

(0,7)

(0,2)

(0,7)

(0,7)

(5,4)

(5)

(5,4)

(5,4)

(9,3)

(0)

(0,1)

(0)

(5,3)

(5,4)

(0,1)

(--16,3)

(--16,4)

(0,8)

(-0,8)

(-0,9)

(0,1)

(5,5)

(5)

(0)

(0)

(5,5)

(5)

(35,1)

(303) : Standby, EE Voltage

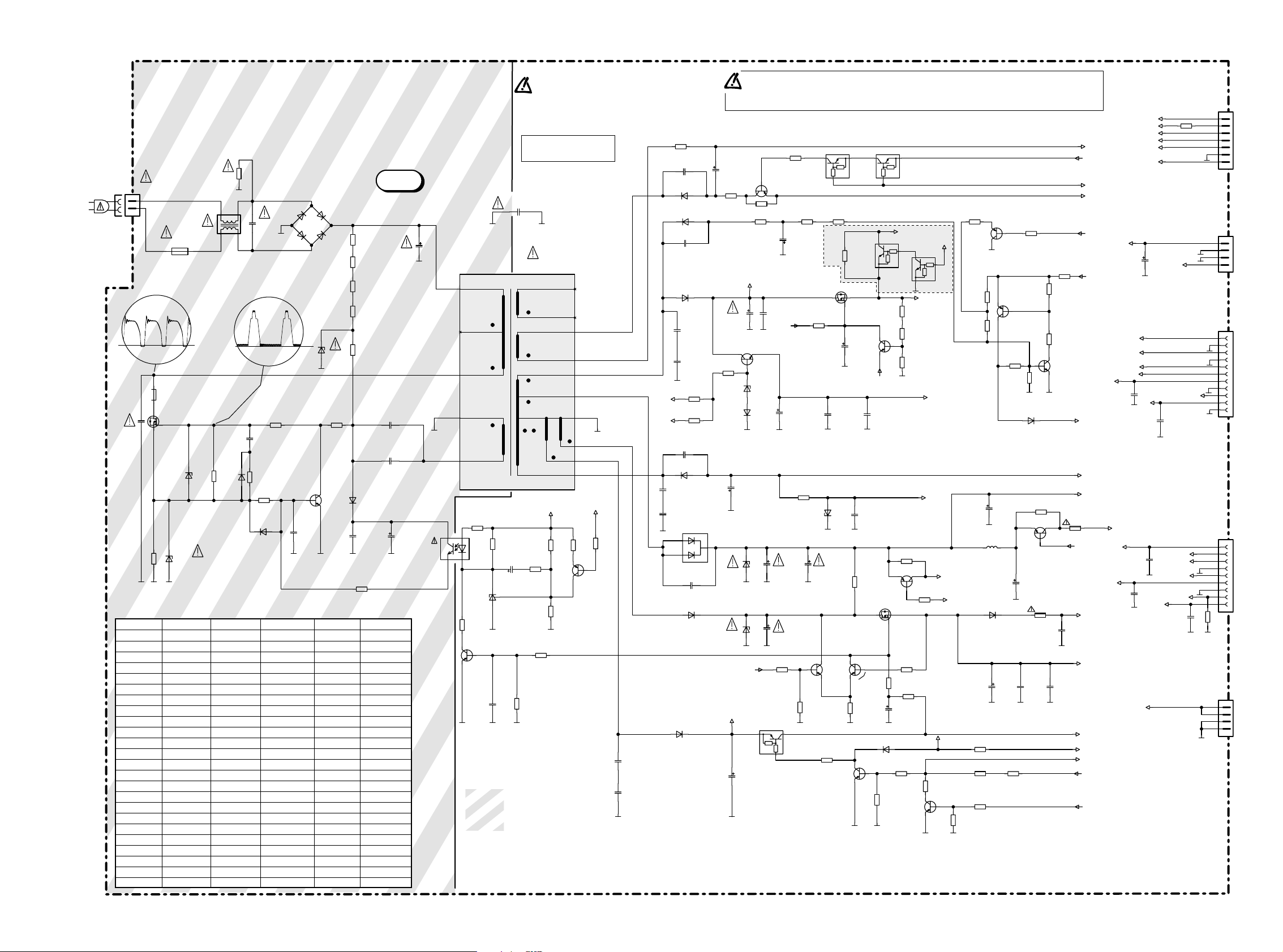

POWER SUPPLY INTERFACE - INTERFACE ALIMENTATION - NETZTEIL - ALIMENTAZIONE - INTERFAZ ALIMENTACIÓN

SCHEMATIC DIAGRAM - SCHEMA DE PRINCIPE - SCHALTBILD - SCHEMA - ESQUEMA

Page 10

DTH8040

First issue 12 / 04

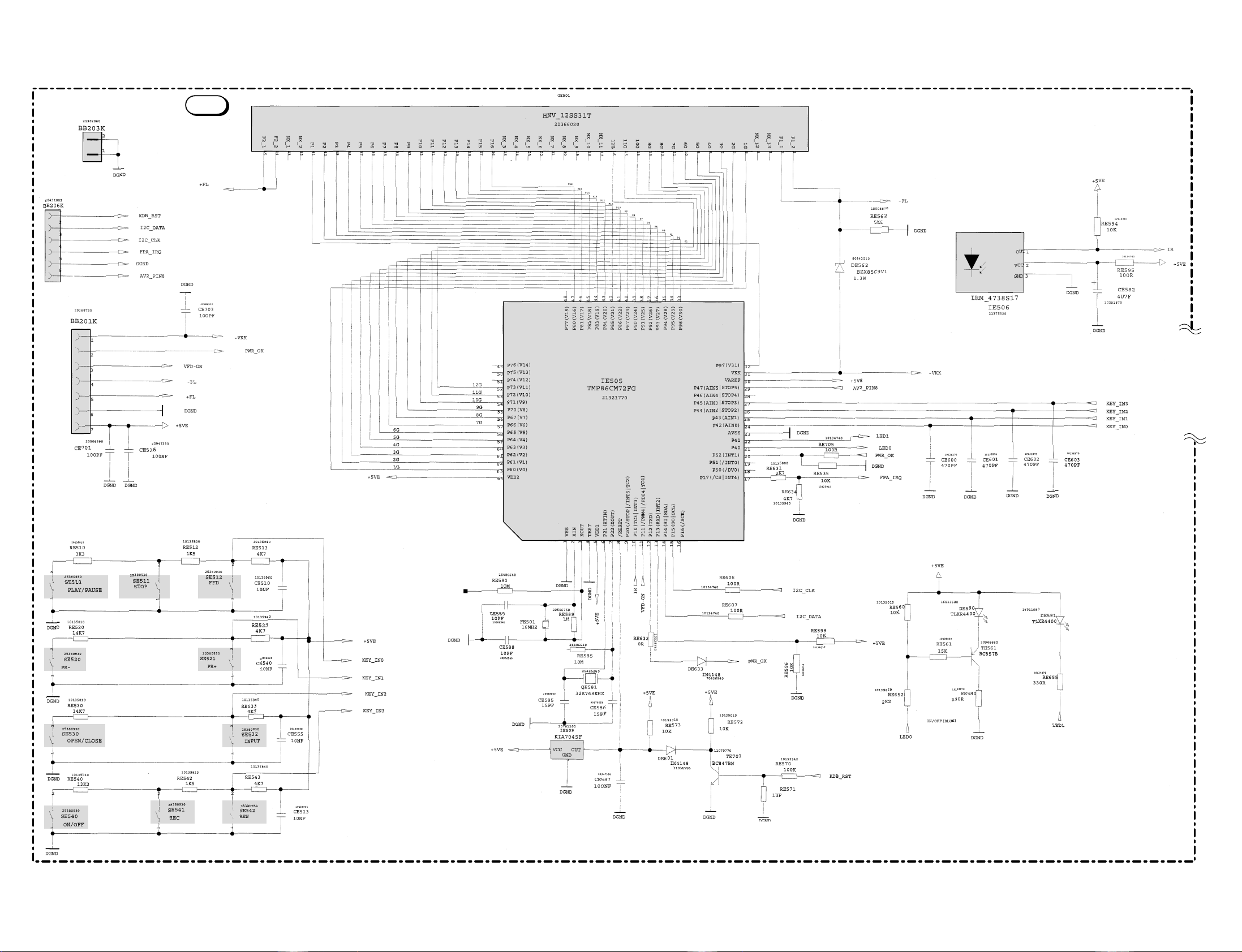

KEYBOARD WITH DISPLAY - PLATINE DE COMMANDES AVEC AFFICHEUR - BEDIENTEIL MIT DISPLAY - TASTIERA CON DISPLAY - PLATINA MANDOS CON VISUALIZADOR

SCHEMATIC DIAGRAM - SCHEMA DE PRINCIPE - SCHALTBILD - SCHEMA - ESQUEMA

KDBSCH IDR04 KDB LP03

Page 11

DTH8040

First issue 12 / 04

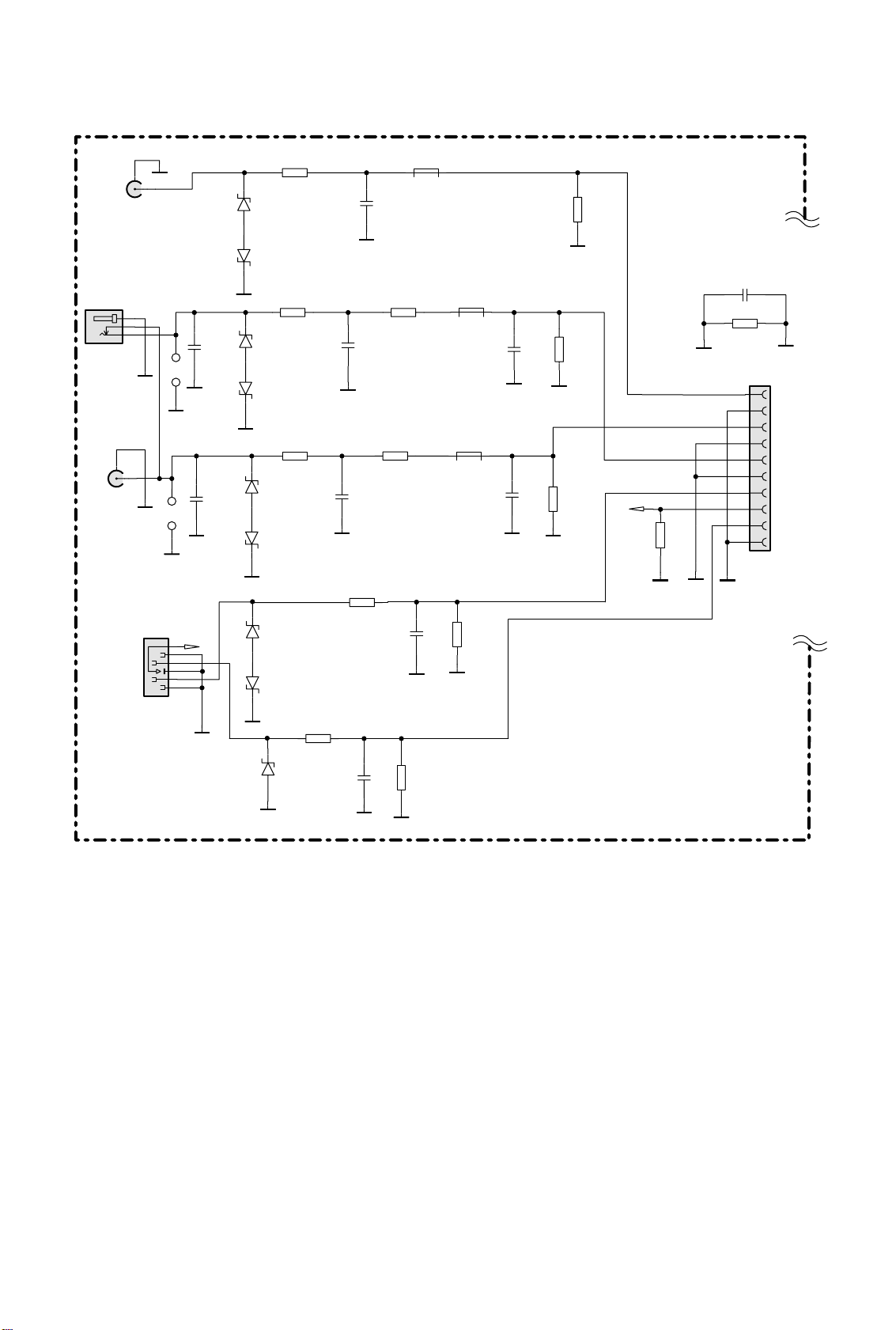

SOCKETS SCHEMATIC DIAGRAM - SCHEMA PRISES SCHALTUNG ANSCHLUSSPLATTE

SCHEMA PRESE - ESQUEMA TOMAS

RE808

DE801

6V8

DE810

6V8

DE802

6V8

DE803

6V8

DE804

6V8

DE805

6V8

0R

RE807

330R

RE833

330R

CE802

47PF

AGND

AGND

GND

CE806

1NF

RE810

18R

CE805

1NF

RE801

330R

RE800

330R

LE800

18R

LE801

F.BEAD

680R

LE802

F.BEAD

680R

CE801

330PF

(PREP)

CE800

330PF

(PREP)

AGND

AGND

AGND

AGND

GND

RE811

470K

RE812

470K

RE802

56R

S_2

RE817

270PF

GND

AGND

AGND

GND

CE815

12PF

RE815

0R

BB309F

1

2

3

4

5

6

7

8

9

10

GND

CV_FRONT

GND

L_FRONT

AGND

R_FRONT

AGND

Y_FRONT

S_2

C_FRONT

GND

BE803

AUDIO_R

BE802

AUDIO_L

1

GND

2

BE801

VIDEO

AGND

1

3

2

12

CE833

330PF

(PREP)

SG01

AGND

1

2

AGND

AGND

12

SG02

AGND

AGND

AGND

CE832

330PF

(PREP)

AGND

AGND

YKF51-5558

BE804

S_VIDEO

DE806

DE807

6V8

AGND

GND

6V8

DE809

6V8

RE809

18R

CE803

47PF

6

S_2

2

4

5

3

1

GND

GND

CE804

47PF

GND

GND

RE803

56R

GND

RE804

56R

FRONT_AV_LP03 21376190

SCH_IDR04_FAV_LP03

00_LR10.0.04

Page 12

DTH8040

First issue 12 / 04

( AV TUNER BOARD 1/6 )

SCART INTERFACE / TUNER SCHEMATIC DIAGRAM SCHEMA DE L’INTERFACE PERITELEVISION / TUNER - SCHALTBILD EUROPA NORMBUCHSE / TUNER

SCHEMA DELLA PRESA PERITEL / SINTONIZZATORE - ESQUEMA INTERFAZ EUROTOMA / SINTONIZADOR

BB101A

SKC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

DGND

AGND_OUT

GND

GND

DGND

SCART2_PIN8

IR_SAT

15K

RW104

SPDIF_OUT

R/PR2H_DXX

AVLINK_W

G/Y2H_DXX

B/PB2H_DXX

GND

AUDIO_SEL1

AUDIO_SEL2

RGB_YUV_SEL

CVBS_DXX

C_DXX

Y_DXX

1H/2H_SEL

HW_SW

AUD_R_OUT

AUD_L_OUT

AUDIO_R_REC

NICAM_RST

AUDIO_L_REC

CV_TUNER1_REC

AV3/AV4_CV/Y_REC

SCART_TV_CV/Y_REC

S_IN1

S_CLK1

AV3/AV4_C_REC

AVLINK_R

SCART_VCR_CV/Y_REC

SCART_VCR_C/R_REC

AUDIO_SEL3

FAN_FAIL

I2C_DATA1

I2C_CLK1

SCART2_G

SCART2_FB

SCART2_B

SV_F

SV_R

16/9_S1

16/9_S2

-5VE

SCART_VCR_C/R_REC

SCART_VCR_CV/Y_REC

RW105

10K

AUDIO_SEL1

AUDIO_SEL2

AUDIO_SEL3

TUNER1_L_1

TUNER1_R_1

TUNER1_L

SCART_TV_L

SCART_TV_R

SCART_VCR_L

SCART_VCR_R

Y_OUTPUT

C_OUTPUT

SCART_VCR_G

SCART_VCR_B

S_CLK1

CVBS_DXX

R/PR2H_DXX

G/Y2H_DXX

B/PB2H_DXX

AUD_L_OUT

AUD_R_OUT

R/PR2H_DXX

B/PB2H_DXX

RGB_YUV_SEL

AUD_L_OUT

AUD_R_OUT

I2C_CLK1

I2C_DATA1

SPDIF_OUT

TUNER1_R

S_IN1

Y_DXX

C_DXX

G/Y2H_DXX

1H/2H_SEL

HW_SW

16/9_S1

16/9_S2

CVBS_DXX

Y_DXX

C_DXX

AUDIO_SEL1

AUDIO_SEL2

AUDIO_SEL3

TUNER1_L_1

TUNER1_R_1

TUNER1_L

TUNER1_R

SCART_TV_L

SCART_TV_R

SCART_VCR_L

SCART_VCR_R

Y_OUTPUT

C_OUTPUT

+33VS

SCART_VCR_G

SCART_VCR_B

S_IN1

S_CLK1

CVBS_DXX

Y_DXX

C_DXX

R/PR2H_DXX

G/Y2H_DXX

B/PB2H_DXX

AUD_L_OUT

AUD_R_OUT

SCART_VCR_C/R_REC

SCART_VCR_CV/Y_REC

R/PR2H_DXX

G/Y2H_DXX

B/PB2H_DXX

1H/2H_SEL

RGB_YUV_SEL

HW_SW

16/9_S1

16/9_S2

CVBS_DXX

Y_DXX

C_DXX

AUD_L_OUT

AUD_R_OUT

+5VE

+5VS

sheet 2

I2C_CLK1

I2C_DATA1

SPDIF_OUT

TUNER

DGND

DGND

+5VE+5VS

+5VE+5VS -5VE

Sheet 3

A/V SWITCHIN G

INPUTS

AGND_OUT

AGND_OUT

-5VE

+12VS

A/V SWITCHIN G

+5VE

SCARTS

sheet 4

+5VS

+5VS

Sheet 5

A/V OUTPUTS

AGND_OUT

AGND_OUT

+33VS+9VE +12VS

+12VS +33VS+5VE +5VS+9VE

FAN_FAIL

NICAM_RST

S_CLK1

S_IN1

TUNER1_L

TUNER1_R

CV_TUNER1_REC

CVBS_VPS/PDC

-5VE

SV_R

SV_F

AUDIO_R_REC

AUDIO_L_REC

AV3/AV4_CV/Y_REC

AV3/AV4_C_REC

+5VS

+5VS+5VE-5VE+12VS+33VS

+12VE

+9VE

+12VE+9VE

CVBS_VPS/PDC

TUNER1_L_1

TUNER1_R_1

SCART_TV_CV/Y_REC

SCART_TV_CV/Y

SCART_TV_L

SCART_TV_R

SCART2_FB

SCART2_R

SCART2_G

SCART2_B

SCART_VCR_CV/Y

SCART_VCR_C/R

SCART_VCR_L

SCART_VCR_R

AV_PIN10

SCART2_PIN8

C_OUTPUT

Y_OUTPUT

AV TUNER IDR04 EU

DTH8040E AV/TUNER

FAN_FAIL

NICAM_RST

S_CLK1

S_IN1

TUNER1_L

TUNER1_R

CV_TUNER1_REC

CVBS_VPS/PDC

SV_R

SV_F

AUDIO_R_REC

AUDIO_L_REC

AV3/AV4_CV/Y_REC

AV3/AV4_C_REC

CVBS_VPS/PDC

TUNER1_L_1

TUNER1_R_1

SCART_TV_CV/Y_REC

SCART_TV_CV/Y

SCART_TV_L

SCART_TV_R

SCART2_FB

SCART2_R

SCART2_G

SCART2_B

SCART_VCR_CV/Y

SCART_VCR_C/R

SCART_VCR_L

SCART_VCR_R

AV_PIN10

SCART2_PIN8

C_OUTPUT

Y_OUTPUT

AV_PIN10

+5VS

0A-SO

2138236B

+5VS

DGND

+5VS

DGND

CVBS_VPS/PDC

Sheet 6

VPS/PDC CIRCUIT

+5VE

4K7

+5VE

10K

RW133

TW127

BC847B

SPDIF_OUT

IR_SAT

RW130

GND

RW131

RW137

LA504

22U

12K

DW126

1N4148W

100R

CW106

100N0

RW112

5K6

14-06-04

RW132

LA503

1K/100MHZ

CW107

100P

120K

DGND

DGND

S_CLK1

GND

CA502

100N

S_IN1

DGND

RW134

RW138

33K

DGND

RW113

150R

8K2

GND

RW139

33K

DGND

BA501

1

INPUT

2

VCC

3

GND

LW114

4U7

TW102

BC847B

2

1

DGND

BC858B

TW126

RW136

10K

CA503

100P

BW100

CVBS_VPS/PDC

S_CLK1

S_IN1

RW135

39K

OPTICAL

COAXIAL

B

A

AVLINK_R

AVLINK_W

DIGITAL

OUTPUT

+5VS

Page 13

DTH8040

First issue 12 / 04

( AV TUNER BOARD 2/6 )

SCART INTERFACE / TUNER SCHEMATIC DIAGRAM - SCHEMA DE L’INTERFACE PERITELEVISION / TUNER - SCHALTBILD EUROPA NORMBUCHSE / TUNER

SCHEMA DELLA PRESA PERITEL / SINTONIZZATORE - ESQUEMA INTERFAZ EUROTOMA / SINTONIZADOR

ZI601

FE6235

(FM_SW)

AGC

SCL

SDA

+5V_T1

+5V_T2

NC1

NC2

NC3

AUDIO

SIF/AS

GND

VIDEO

FM_IF

+5V_IF

NC4

NC5

LUG1

LUG2

SKCTUNER

TUNER_MONO_AUDIO

+5VE

CI500

1

2

PS

3

AS

4

5

6

7

8

9

VT

10

11

12

13

14

15

16

17

18

19

20

21

22

RI601

GND

100P0

GND

10K0

CI601

47P

GND

GND

CI604

100N0

GND

CI549

47N0

GND

TUNER_MONO_AUDIO

GND

RI610

82R

1

GND

CI608

100N0

GND

100N0

GND

RI602

150R

RI603

150R

CI602

47P

CI603

100P0

GND GND

GND

GND

CI605

100P0

TUNER_SIF

RI611

270R

CI607

47P

CI609

100P0

+5VS_TUNER

GND GND

CI508

22U0

CI511

22U0

GND

CI606

47P

CI501

100P0

LI505

10U0

CI502

GND

+5VS_TUNER

RI604

FBEAD

RI605

FBEAD

GND

LI504

4.7U

RI612

620R

+5VS

+33VS

LI501

4.7U

CVBS_VPS/PDC

CV_TUNER1_REC

I2C_CLK1

I2C_DATA1

+5VS

AGND

LA100

4.7U

TUNER_SIF

AGND

AGND

CA101

470P0

CA104

I2C @

S_CLK1

S_IN1

TUNER

DTH8040E AV/TUNER

AGND

5P0

CA105

5P0

W:0x88 R:0x89

AGND

CA122

CA103

56P0

QA100

18M432

1U0

RA100

100R0

CA100

10U0

AGND

CA102

56P0

RA108

0

10

11

RA101

100R0

AGND

1

AVSUP

2

ANA_IN1+

3

ANA_IN-

4

TESTEN

5

XTAL_IN

6

XTAL_OUT

7

TP

8

D_CTR_OUT1

9

D_CTR_OUT0

ADR_SEL

STANDBYQ

AGND

CA123

470P0

2

1

CW108

100U

16V

44

12

MGND

BW101

43

AVSS

I2C_CL

13

CW102

100U

MGNDMGND

42

VREFTOP

I2C_DA MONO_IN

TP

14

CA106

470P0

LW101

10U0

RW108

180R

CA120

100N0

CA121

10U0

39

40

41

NC

SC1_IN_L

SC1_IN_R

IA100

MSP3417D

TP

TPTPTP

151617

CA107

10U0

AGND

RW101

10K

RW103

4K7

AGND

AGND

AGND

38

NC

TP

18

AGND

+12VS

37

NC

DVSUP

19

AGND

MGND

AGND

36

AGNDC

DVSS

20

RA102

10K0

+5VS

MGND

RW114

10K

CA117

100N0

CA116

10U0

35

AHVSS

21

22

AGND

RW102

1K

TW103

BC847B

34

CAPL_M

RESETQ

CA108

100N0

+5VS

MGND

AGND

AGND

AHVSUP

SC1_OUT_L

SC1_OUT_R

VREF1

DACM_L

DACM_R

VREF2

RA103

100R0

BC857B

TW104

RW106

4K7

CA115

1U0

NC

TP

TP

TP

1N4148W

DW101

33

32

31

30

29

28

27

26

25

24

23

+5VS

MGND

DA100

1N4148W

CA114

100N0

AGNDAGND

RA104

1K0

RA105

1K0

AGND

AGND

TV SOUND DEMODULATOR DECODER

0

Reset

1

No Reset

NICAM_RST

RW107

1N4148W

1K

DW102

TW105

RN1402N

MGND

CA113

10U0

RW109

4K7

LA101

10U0

CA109

3N3

CA110

3N3

FAN_FAIL

+9VE

AGND

AGND

RX863

RX865

GND

Power FROM Upper Level

Signal FROM Upper Level

Signal TO Upper Level

CV_TUNER1_REC

TUNER1_L

TUNER1_R

CVBS_VPS/PDC

FAN_FAIL

TUNER1_L

TUNER1_R

RX891

0

RX892

0

DGND

0

0

AGND

+33VS

+5VS

+5VE

+9VE

+12VS

DGND

S_CLK1

S_IN1

I2C_CLK1

I2C_DATA1

SPDIF_OUT

NICAM_RST

MGND

RX862

0

RX864

0

DGND

LUG3

LUG4

23

24

Address Btye

For Tuner

For IF

Hex Code

C2

86

Page 14

DTH8040

First issue 12 / 04

( AV TUNER BOARD 3/6)

SCART INTERFACE / TUNER SCHEMATIC DIAGRAM - SCHEMA DE L’INTERFACE PERITELEVISION / TUNER - SCHALTBILD EUROPA NORMBUCHSE / TUNER

SCHEMA DELLA PRESA PERITEL / SINTONIZZATORE - ESQUEMA INTERFAZ EUROTOMA / SINTONIZADOR

A/V Switching Inputs

BB309A

1

2

3

4

5

6

7

8

9

10

GND

CX021

CX020

47P0

47P0

GND

BW520

MTJ-035-33R-BBA-432

YELLOW

WHITE

RED

S-VIDEO IN

BW541

YKF51-5571

S-VIDEO OUT

GND

5

4

3

2

1

GND

SKC

CX022

47P0

10

9

8

7

11

4

3

2

1

5

6

12

GND

CX023

47P0

GND

GND

GND

AGND_OUT

GND

GND

CW544

PREP

CW541

PREP

CX024

47P0

DW548

BZT55C6V8

RW543

470R

RW540

470R

TUNER1_R

TUNER1_L

+5VS

GND

GND

RW550

6K2

RW551

18K

GND

GND

GND

CW543

470P0

CW540

470P0

SV_R

C_OUTPUT

Y_OUTPUT

GND

RX026

18K

CW545

47P0

(prep)

RX025

6K2

RW547

22R

RW545

470R

RW542

470R

10U

CW582

10U

CW583

RX871

0R0

L_FRONT

R_FRONT

Y_FRONT_REC

SV_F

C_FRONT_REC

GND

CW549

47P0

RW546

56R

GND

GND

GND

CW547

47P0

CX013

100P0

GND

+5VE

CV_REAR_REC

RW544

100K0

RW541

100K0

GND

RW515

33K0

GND

CV_FRONT_REC

-5VE

RW553

22R

DW554

BZT55C6V8

RW548

22R

RW549

56R

GND

GND

LW570

L_REAR

R_REAR

RW516

33K0

GND

GND

4U7

CW571

100U0

RW552

56R

GND

CV_REAR_REC

Y_REAR_REC

-5VE_VIDEO

GND

DW551

BZT55C6V8

L_REAR

AV3/AV4_L

L_FRONT

CW572

100N0

C_REAR_REC

Y_REAR_REC

GND

2

3

4

5

6

7

8

GND

SCART_TV_R

SCART_TV_L

SCART_VCR_R

SCART_VCR_L

AV3/AV4_L

AV3/AV4_R

Y0

Z1

Z

Z0

E

VEE

GND

HEF4053

PART_TYPE=10292210

Audio_sel2

L

L

H

H

IW510

TUNER1_L_1

AUD_L_REC1

-5VE

GND

L

H

L

H

TUNER1_R_1

1

2

3

4

5

6

7

8

Output signalAudio_sel1

AV1

AV2

Tuner_Audio

AV3/AV4

VCCY1

Y

X

X1

X0

A

B

C

-5VE_VIDEO

2Y2

2Z

2Y3

2Y1

E

VEE

GND

161

15

AV4_CV/Y

14

AV3_CV/Y

13

CV_FRONT_REC

12

Y_FRONT_REC

11

SV_F

10

SV_R

9

AUDIO_SEL3

C_REAR_REC

C_FRONT_REC

AV3/AV4_R

CW573

100N0

GND

IW501

744052

R_REAR

R_FRONT

A/V Switching Inputs

DTH8040E AV/TUNER

22-06-04

2138236B

GND

0A-SO

+5VE_VIDEO

CW427

100N0

GND

VCC2Y0

1Y2

1Y1

1Y0

1Y3

2

Y0

3

Z1

4

Z

5

Z0

6

E

7

VEE

8

GND

16

15

14

13

1Z

12

11

10

S0

9

S1

AUD_L_REC1

AUD_R_REC1

LW360

4U7

21369280

CW426

100U0

GND

IW520

HEF4053

PART_TYPE=10292210

+5VE

GND

RW579

1K

RW578

1K

+5VE

CW504

100N0

AUD_R_REC1

RW517

10K0

GND

GND

CW579

100P0

(prep)

CW578

100P0

(prep)

Power FROM Upper Level

+5VE

+5VS

-5VE

+5VE_VIDEO

CW428

161

VCCY1

15

Y

14

X

13

X1

12

X0

11

A

10

B

9

C

+5VE

RW518

10K0

CW580

10U

CW581

10U

100N0

GND

AV3/AV4_C_REC

AV3/AV4_CV/Y_REC

AV4_CV/Y

AV3_CV/Y

10K0

RW372

AUDIO_SEL3

AUDIO_SEL2

AUDIO_SEL1

AUDIO_L_REC

AUDIO_R_REC

+5VE

AGND_OUT

Signal FROM Upper Level

AUDIO_SEL1

AUDIO_SEL2

AUDIO_SEL3

TUNER1_L

TUNER1_R

SCART_TV_R

SCART_TV_L

SCART_VCR_R

SCART_VCR_L

C_OUTPUT

Y_OUTPUT

Signal TO Upper Level

AUDIO_R_REC

AUDIO_L_REC

AV3/AV4_CV/Y_REC

AV3/AV4_C_REC

SV_F

SV_R

Page 15

DTH8040

First issue 12 / 04

( AV TUNER BOARD 4/6)

SCART INTERFACE / TUNER SCHEMATIC DIAGRAM - SCHEMA DE L’INTERFACE PERITELEVISION / TUNER - SCHALTBILD EUROPA NORMBUCHSE / TUNER

SCHEMA DELLA PRESA PERITEL / SINTONIZZATORE - ESQUEMA INTERFAZ EUROTOMA / SINTONIZADOR

A/V SWITCHING SCARTS

SKC

BB601A

+12VE

+40VS

+12VS

SCART_VCR_B

SCART_VCR_CV/Y

9

8

7

GND

6

+9VE

5

+5VS

4

GND

3

2

-5VE

1

+5VE

SCART_VCR_G

+5VE

CW123

100N0

CVBS_VPS/PDC

CVBS_DXX

TUNER1_R_1

TUNER1_L_1

R/PR2H_DXX

AUD_R_OUT

G/Y2H_DXX

AUD_L_OUT

B/PB2H_DXX

SCART_TV_CV/Y

SCART_VCR_L

SCART_VCR_R

SCART_TV_L

SCART_TV_R

GND

+12VE

GND

Y_DXX

C_DXX

GND

GND

LW124

4U7

CW125

100U0

GND

GND

GND

CX855

100P

CX861

100P

LW010

39N

LW011

39N

GND

GND

CW147

100P

CW191

47P0

+12VE

GND

RW182

0R0

RW183

0R0

LW121

4U7

CW126

100N0

CW127

CW128

CW129

CW130

CW131

CW132

CW133

CW134

CW135

CW136

CW137

CW138

GND

+5VS

GND

CX863

100P

+5VE_F

GND

1U0

100N0

1U0

1U0

1U0

1U0

1U0

1U0

1U0

1U0

1U0

1U0

CW148

100P

CW192

47P0

GND

CX854

100P

+5VE

1N4148W

DW130

+9VE

RX860

100R0

0.25W

SCART2_G

SCART2_B

CW122

100U0

SCART_VCR_B

CW139

220N0

GND

CW141

CW143

CW145

GND

DX860

5V1

1U

1U0

1U0

GND

GND

GND

CX853

100P

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

CW140

100U0

+33VS

RX852

1K2

2.0W

CX860

10U

GND

CW159

100N0

GND

CW160

220N0

VCC

CVBSIN_AUX

DEC

Y/CVBSIN_ENC

GND1

YIN_ENC

RIN_AUX

C_ENC

LIN_AUX

R/CIN_ENC

RIN_ENC

GIN_ENC

LIN_ENC

BIN_ENC

NC1

VREF

CW142

1U0

CW144

1U

CW146

A/V SWITCHING SCARTS

DTH8040E A/V TUNER

DX852

BZX55B33

+12VS

GND

-5VE

CX851

100P

GND

220N0

CW158

CW157

220N0

64

SDA

G_VCR

R/C_VCR

SLB_VCR

LIN_VCR

RIN_VCR

CVBSIN_TV

GND3

IT_OUT

SLB_TV

IW151

STV6412AD

LIN_TV

RIN_TV

VCCA

GNDA

GND

VCC12

B_VCR

GND2

Y/CVBSIN_VCR

171819202122232425262728293031

GND

1U0

CX852

100U0

GND

RW120

0

RW121

0

GND

SCL

VDD

ADD

C_GATE

NC2

ROUT_CINCH

LOUT_CINCH

ROUT_VCR

SCART_VCR_C/R

SCART_VCR_C/R_REC

LW123

10U0

CW156

100N0

495051525354555657585960616263

FBIN_ENC

FBIN_VCR

FBOUT_TV

Y/CVBSOUT_VCR

COUT_VCR

Y/CVBSOUT_TV

R/COUT_TV

GOUT_TV

BOUT_TV

VOUT_RF

AOUT_RF

LOUT_TV

LOUT_VCR

VCCAO

ROUT_TV

32

CW151

47N0

GND

CW150

22U0

SCART_VCR_G

SLB_VCR

SCART_VCR_C/R

SLB_TV

S_IN1

S_CLK1

+5VE_F

GND

48

47

VCCB1

46

45

VCCB2

44

43

VCCB3

42

41

GNDB

40

39

VCCB4

38

37

VCCB5

36

35

34

FILTER

33

RW124

22R

GND

CW149

22U0

Y/CV_VCR

GND

CW153

22U0

CW124

100N0

RW370

56R

GND

BZT55C6V8

GND

CW155

100N0

22U0

CW152

GND

SCART_VCR_B

SCART_VCR_G

RW146

22R

DW812

CW113

5N6

FB_VCR

FSTV_OUT

Y/CV_VCR

+5VE_F

Y/CV_TV

C/R_TV

G_TV

B_TV

LOUT_TV

LW137

10U0

CW185

100U0

LOUT_VCR

ROUT_VCR

GND

SLB_VCR

BZT55C6V8

GND

G_TV

GND

ROUT_TV

DW815

RW152

75R0

RW151

1K0

1(L)

0(H)

DEFAULT

CW154

100N0

+9VE

AV_PIN10

GND

RW140

470R0

CW163

1N0

SCART2_PIN8

GND

DW816

BZT55C6V8

GND

RW304

CW172

47P0

GND

GND

ROUT_TV

SCART_TV_R

LOUT_TV

SCART_TV_L

C/R_VCRC-gate TW125

OFF OUT

ON MUTE

ON MUTE

DW806

BZT55C6V8

GND

SCART_TV_CV/Y_REC

GND

DW803

BZT55C6V8

0

CW114

5N6

SLB_TV

RW156

1K0

C/R_TV

FSTV_OUT

Y/CV_TV

SCART_TV_CV/Y

RW369

56R

ROUT_VCR

SCART_VCR_R

LOUT_VCR

SCART_VCR_L

GND

FB_VCR

SCART2_FB

SCART_VCR_CV/Y

SCART_VCR_CV/Y_REC

CW095

100P0

B_TV

RW157

75R0

CW175

47P0

GND

RW169

22R

GND

75R0

RW147

RW149

470R0

RW371

RW164

470R0

GND

BZT55C6V8

56R

GND

GND

RW148

CW096

100P0

BZT55C6V8

DW813

GND

75R0

GND GNDGND GND

DW819

BZT55C6V8

RW153

22R

DW814

BZT55C6V8

RW199

470K0

BZT55C6V8

DW820

DW808

BZT55C6V8

GND

GN

CW094

100P0

CW168

DW805

GND

47P0

GND

GND

GND

CW092

100P0

RW189

RW194

330R0

GND

GND

GND

DW807