Page 1

Service Manual

CHASSIS MT35

Contents

1. Caution…………………………………......….…………………...……………2

2. Product Specification………………………..……………………...…….…….6

3. Test and Alignment………………….………………………………...………..9

4. Main IC Brief Instruction

MT5335PU……………………………………....................................................16

MT5133……………………………………........................................................22

MT8295…………………............................................................................…..24

WL6702F………………………………………....….............…..........…………..25

WM8501..........................................................................................................30

SiL9185A.........................................................................................................33

RT8110............................................................................................................47

MP1411...........................................................................................................50

TDA7266.........................................................................................................54

AO4459...........................................................................................................55

13N03LT..........................................................................................................56

5. Block Diagram………………………………….…….. .......................……..57

6. Schematic Diagram……………………………..............................……….58

7. Exploded View

26E90……………………………………………..……….…..............…….…..…86

26E92……………………………………… ...... …………......……................….87

32E90…………………….………………..……….....……..….…..............……..88

32E92..............................................................................................................89

Page 2

CAUTION:

1

Use of controls, adjustments or procedures other than those specified herein may result in

hazardous radiation exposure.

CAUTION: TO REDUCE THE RISK OF

CAUTION

RISK OF ELECTRIC

SHOCK DO NOT OPEN.

The lighting flash with arrowhead symbol, with an equilateral triangle is intended to

alert the user to the presence of uninsulated voltage within the products

enclosure that may be of sufficient magnitude to constitute a risk of electric shock to

the person.

The exclamation point within an equilateral triangle is intended to alert the user to the

presence of important operating and maintenance (servicing) instructions in the

literature accompanying the appliance.

ELECTRICAL SHOCK, DO NOT REMOVE

COVER (OR BACK). NO USER SERVICEABLE

PARTS INSIDE. REFER SER VICING TO

QUALIFIED SERVICE PERSONNEL.

dangerous

WARNING: TO REDUCE RISK OF FIRE OR ELECTRIC SHOCK, DO NOT

EXPOSE THIS APPLIANCE TO RAIN OR MOISTURE.

2

Page 3

IMPORTANT SAFETY INSTRUCTIONS

CAUTION:

Read all of these instructions. Save these instructions for later use. Follow all Warnings and

Instructions marked on the audio equipment.

1. Read Instructions- All the safety and operating instructions should be read before the product is operated.

2. Retain Instructions- The safety and operating instructions should be retained for future reference.

3. Heed Warnings- All warnings on the product and in the operating instructions should be adhered to.

4. Follow Instructions- All operating and use instructions should be followed.

FOR YOUR PERSONAL SAFETY

1. When the power cord or plug is damaged or frayed, unplug this television set from the wall outlet and refer servicing to

qualified service personnel.

2. Do not overload wall outlets and extension cords as this can result in fire or electric shock.

3. Do not allow anything to rest on or roll over the power cord, and do not place the TV where power cord is subject to

traffic or abuse. This may result in a shock or fire hazard.

4. Do not attempt to service this television set yourself as opening or removing covers may expose you to dangerous

voltage or other hazards. Refer all servicing to qualified service personnel.

5. Never push objects of any kind into this television set through cabinet slots as they may touch dangerous voltage

points or short out parts that could result in a fire or electric shock. Never spill liquid of any kind on the television set.

6. If the television set has been dropped or the cabinet has been damaged, unplug this television set from the wall outlet

and refer servicing to qualified service personnel.

7. If liquid has been spilled into the television set, unplug this television set from the wall outlet and refer servicing to

qualified service personnel.

8. Do not subject your television set to impact of any kind. Be particularly careful not to damage the picture tube surface.

9. Unplug this television set from the wall outlet before cleaning. Do not use liquid cleaners or aerosol cleaners. Use a

damp cloth for cleaning.

10.1. Do not place this television set on an unstable cart, stand, or table. The television set may fall, causing serious injury

to a child or an adult, and serious damage to the appliance. Use only with a cart or stand recommended by the

manufacturer, or sold with the television set. Wall or shelf mounting should follow the manufacturer s instructions, and

should use a mounting kit approved by the manufacturer.

10.2. An appliance and cart combination should be moved with care. Quick stops, excessive force, and uneven surfaces

may cause the appliance and cart combination to overturn.

3

Page 4

PROTECTION AND LOCATION OF YOUR SET

11. Do not use this television set near water ... for example, near a bathtub, washbowl, kitchen sink, or laundry tub, in a

wet basement, or near a swimming pool, etc.

Never expose the set to rain or water. If the set has been exposed to rain or water, unplug the set from the wall

outlet and refer servicing to qualified service personnel.

12. Choose a place where light (artificial or sunlight) does not shine directly on the screen.

13. Avoid dusty places, since piling up of dust inside TV chassis may cause failure of the set when high humidity persists.

14. The set has slots, or openings in the cabinet for ventilation purposes, to provide reliable operation of the receiver, to

protect it from overheating. These openings must not be blocked or covered.

Never cover the slots or openings with cloth or other material.

Never block the bottom ventilation slots of the set by placing it on a bed, sofa, rug, etc.

Never place the set near or over a radiator or heat register.

Never place the set in enclosure, unless proper ventilation is provided.

a built-in

PROTECTION AND LOCATION OF YOUR SET

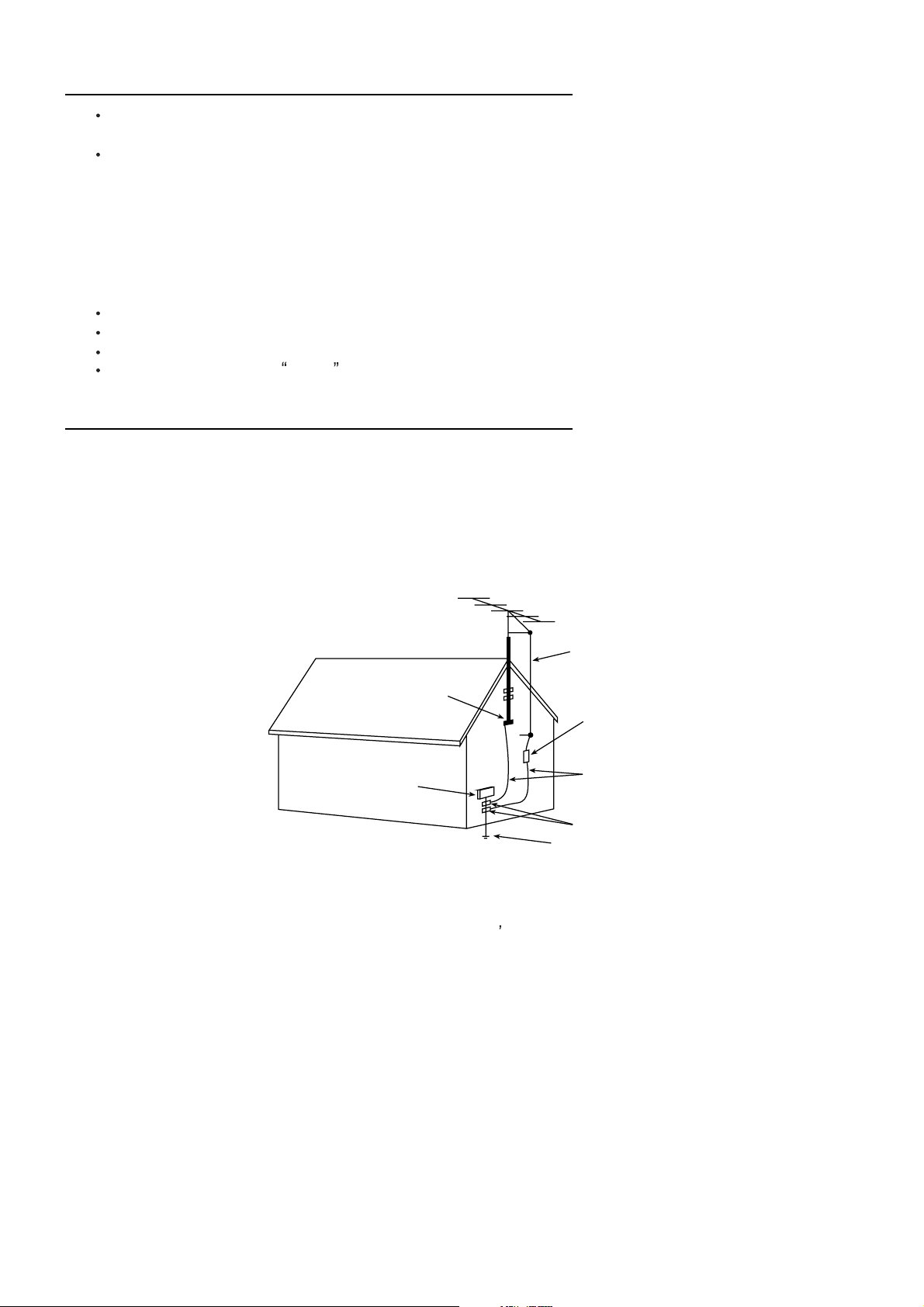

15.1. If an outside antenna is connected to the television set, be sure the antenna system is grounded so as to provide some

protection against voltage surges and built up static charges, Section 810 of the National Electrical Code, NFPA No.

70-1975, provides information with respect to proper grounding of the mast and supporting structure, grounding of the

lead-in wire to an antenna discharge unit, size of grounding conductors, location of antenna discharge unit, connection

to grounding electrode, and requirements for the grounding electrode.

EXAMPLE OF ANTENNA GROUNDING AS PER NATIONAL ELECTRICAL CODE INSTRUCTIONS

EXAMPLE OF ANTENNA GROUNDING AS PER

NATIONAL ELECTRICAL CODE

ANTENNA

LEAD- IN WIRE

GROUND CLAMP

ANTENNA DISCHARGE

UNIT (NEC SECTION

810-20)

GROUNDING

ELECTRIC SERVICE

EQUIPMENT

NEC-NATIONAL ELECTRICAL CODE

15.2. Note to CATV system installer : (Only for the television set with CATV reception)

This reminder is provided to call the CATV system attention to Article 820-40 of the NEC that provides

installer s

guidelines for proper grounding and, in particular, specifies that the cable ground shall be connected to the grounding

system of the building, as close to the point of cable entry as practical.

16. An outside antenna system should not be located in the vicinity of overhead power lines or other electric lights or power

circuits, or where it can fall into such power lines or circuits. When installing an outside antenna system, extreme care

should be taken to keep from touching such power lines or circuits as contact with them might be fatal.

CONDUCTORS

(NEC SECTION810-21)

GROUND CLAMPS

POWER SERVICE GROUNDING

ELECTRODE SYSTEM

(NEC ART 250. PART H)

17. For added protection for this television set during a lightning storm, or when it is left unattended and unused for long

periods of time, unplug it from the wall outlet and disconnect the antenna. This will prevent damage due to lightning

and power-line surges.

4

Page 5

OPERATION OF YOUR SET

18.

This television set should be operated only from the type of power source indicated on the marking label.If you are not

sure of the type of power supply at your home, consult your television dealer or local power company. For television

sets designed to operate from battery power, refer to the operating instructions.

19. If the television set does not operate normally by following the operating instructions, unplug this television set from the

wall outlet and refer servicing to qualified service personnel. Adjust only those controls that are covered in the operating

instructions as improper adjustment of other controls may result in damage and will often require extensive work by a

qualified technician to restore the television set to normal operation.

20. When going on a holiday : If your television set is to remain unused for a period of time, for instance, when you go on

a holiday, turn the television set and unplug the television set from the wall outlet.

off

IF THE SET DOES NOT OPERATE PROPERLY

21. If you are unable to restore normal operation by following thedetailed procedure in your operating instructions,

do not attempt any further adjustment. Unplug the set and call your dealer or service technician.

22. Whenever the television set is damaged or fails, or a distinct change in performance indicates a need for

service, unplug the set and have it checked by a professional service technician.

23. It is normal for some TV sets to make occasional snapping or popping sounds, particularly when being

turned on or off. If the snapping or popping is continuous or frequent, unplug the set and consult your

dealer or service technician.

FOR SERVICE AND MODIFICATION

24. Do not use attachments not recommended by the television set manufacturer as they may cause hazards.

25. When replacement parts are required, be sure the service technician has used replacement parts specified

by the manufacturer that have the same characteristics as the original part. Unauthorized substitutions

may result in fire, electric shock, or other hazards.

26. Upon completion of any service or repairs to the television set, ask the service technician to perform

routine safety checks to determine that the television is in safe operating condition.

5

Page 6

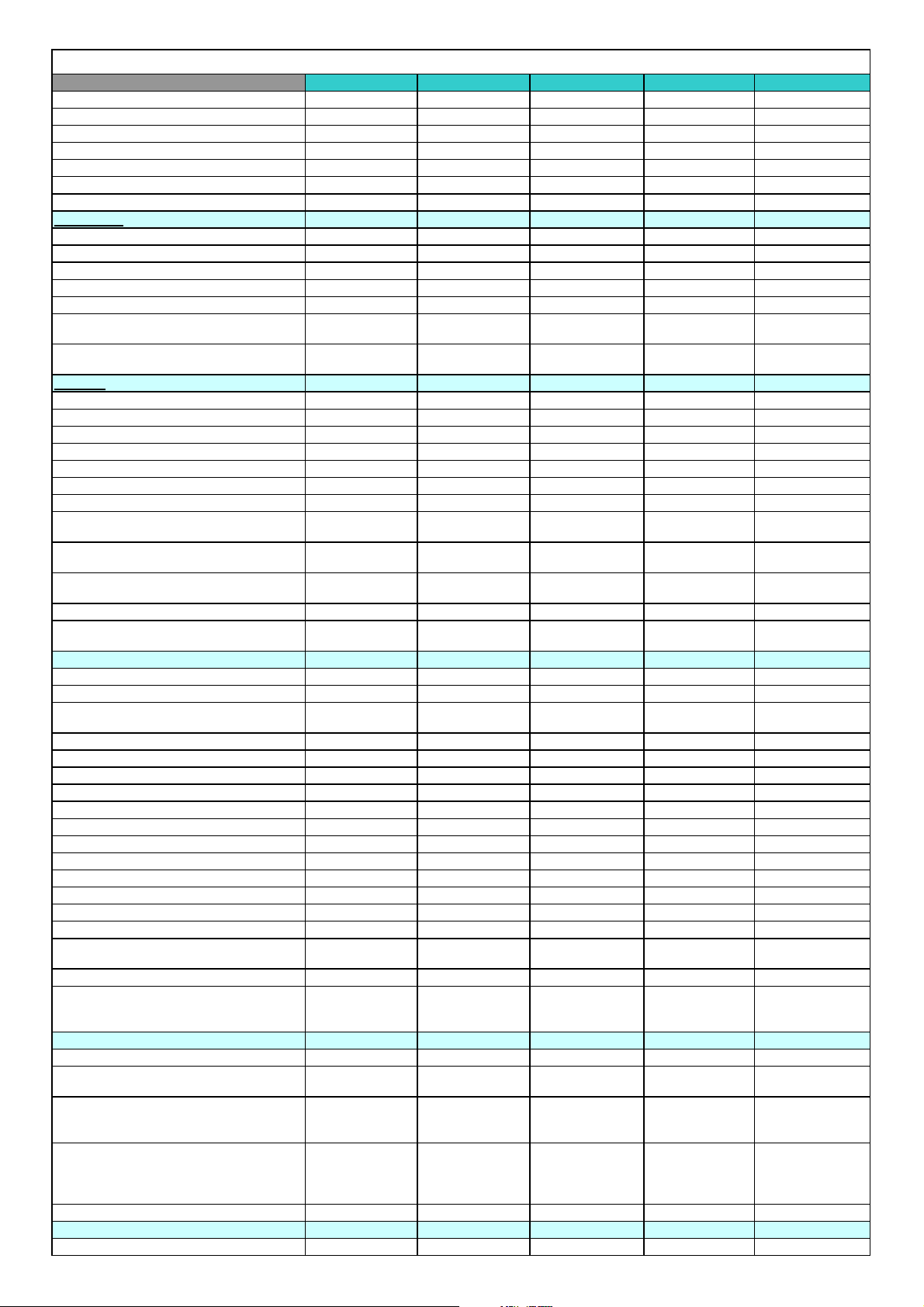

MT35-EU Product Specification

Model # 22E92NH22 26E90NH22 26E92NH22 32E90NH22 32E92NH22

Brand THOMSON THOMSON THOMSON THOMSON THOMSON

Panel technology (LCD / PDP) LCD LCD LCD LCD LCD

Cabinet Design (Example: SC VII, V 6,,,) E9B E9A E9B E9A E9B

PJO Nb 22E92 26E90 26E92 32E90 32E92

EAN Code 3244480284643 3244480284629 3244480284636 3244480284445 3244480284612

Chassis name MT5335 MT5335 MT5335 MT5335 MT5335

Certification(Gostandard/CE/MPTT/…) CE CE CE CE CE

COUNTRIES

France Yes Yes Yes Yes Yes

Germany Yes Yes Yes Yes Yes

Italy, Greece Yes Yes Yes Yes Yes

Spain, Portugal Yes Yes Yes Yes Yes

Benelux (Belgium, Netherland, Luxemburg) Yes Yes Yes Yes Yes

Northern Europe (Sweden, Norway, Denmark,

Finland)

Eastern Europe (Russia, Poland, Czech,

Hungary)

PICTURE

Screen size : diagonale (inch) 22" 26" 26" 32" 32"

Aspect ratio (16/9 // 4/3 // 15/9) 16/9 16/9 16/9 16/9 16/9

Color depth (8/10/12 bits) 8 8 8 8 8

1st panel supplier : panel suppliers AUO CMO CMO LG-Philips LG-Philips

1st panel supplier : panel reference T220SW01 V0 V260B1-L02 V260B1-L02 LC320WXN-SAC1 LC320WXN-SAC1

1st panel supplier : resolution 1680x1050 1366x768 1366x768 1366x768 1366x768

1st panel supplier : pixel Pitch (mmxmm) 0.282x0.282 0.1405x0.4215 0.1405x0.4215 0.17x0.51

1st panel supplier : Horizontal and vertical

viewing angle

1st panel supplier : Typical response time (Grey

to Grey)

1st panel supplier : Typical white luminance

(Nits)

1st panel supplier : Contrast VESA std 1000:1 800:1 800:1 1100:1 1100:1

1st panel supplier : Typical panel Life Time

(Hours)

VIDEO

Noise Reduction (adaptative/…) Yes Yes Yes Yes Yes

Comb Filter (2D/3D) 3D 3D 3D 3D 3D

Deinterlacer (no/linerar/motion adaptive/motion

compensative)

Film mode / reverse 3:2 pull down Yes/Yes Yes/Yes Yes/Yes Yes/Yes Yes/Yes

Format control (Pin8/WSS) Yes/Yes Yes/Yes Yes/Yes Yes/Yes Yes/Yes

Zoom type : 4/3 format Yes Yes Yes Yes Yes

Zoom type : 14/9 Zoom Yes Yes Yes Yes Yes

Zoom type : 16/9 Zoom Yes Yes Yes Yes Yes

Zoom type : 16/9 Zoom up/down Yes Yes Yes Yes Yes

Zoom type : Cinerama Yes Yes Yes Yes Yes

Zoom type : 16/9Format Yes Yes Yes Yes Yes

Colour preset (Cool/Normal/Warm/Favourite) Cool/Normal/Warm Cool/Normal/Warm Cool/Normal/Warm Cool/Normal/Warm Cool/Normal/Warm

Contrast expend (low/medium/high) high high high high high

Picture Reset Yes Yes Yes Yes Yes

Backlight Adjust on factory menu on factory menu on factory menu on factory menu on factory menu

Dynamic Contrast

Picture Autoadjustment (PC mode) Yes Yes Yes Yes Yes

Picture presets : Standard / Film / Studio /

Sport / Personal / Game / Video Camera

Sound

RMS Power (Watt) 2x3W 2x6W 2x6W 2x6W 2x6W

Treble, Bass, Balance, Volume, Mute Control

Sound presets (My

sound/Music/Film/Voice/Flat/Standard/Panoram

a)

Sound techno (Stereo Nicam/Virtual Dolby

Surround/SRS Trusurround XT/BBE Viva/SRS

WoW /…)

Loudspeakers built in (T/M/B) -/2/- -/2/- -/2/- -/2/- -/2/-

Decoding capability

Standard BG/DK/I/LL` BG/DK/I/LL` BG/DK/I/LL` BG/DK/I/LL` BG/DK/I/LL`

Yes Yes Yes Yes Yes

Yes Yes Yes Yes Yes

0.17x0.51

170(H)/160(V) 160(H)/150(V) 160(H)/150(V) 178(H)/178(V) 178(H)/178(V)

5mS 8mS 8mS 8mS 8mS

300 400 400 500 500

50000 50000 50000 50000 50000

Frame buffer Frame buffer Frame buffer Frame buffer Frame buffer

Dynamic Backlight

adjustment

Vivid/Standard

/Movie/ Power

saver/ Personal

Yes/Yes/Yes/Yes/YesYes/Yes/Yes/Yes/YesYes/Yes/Yes/Yes/YesYes/Yes/Yes/Yes/YesYes/Yes/Yes/Yes/Ye

personal/speech/mu

sic/movies/Multimed

ia

NICAM,German

Stereo/AVL/Wide

stereo/Visually

Impaired

Dynamic Backlight

adjustment

Vivid/Standard

/Movie/ Power

saver/ Personal

personal/speech/mu

sic/movies/Multimed

ia

NICAM,German

Stereo/AVL/Wide

stereo/Visually

Impaired

Dynamic Backlight

adjustment

Vivid/Standard

/Movie/ Power saver/

Personal

personal/speech/mu

sic/movies/Multimedi

a

NICAM,German

Stereo/AVL/Wide

stereo/Visually

Impaired

Dynamic Backlight

adjustment

Vivid/Standard

/Movie/ Power

saver/ Personal

personal/speech/mu

sic/movies/Multimed

ia

NICAM,German

Stereo/AVL/Wide

stereo/Visually

Impaired

Dynamic Backlight

adjustment

Vivid/Standard

/Movie/ Power saver/

Personal

s

personal/speech/mus

ic/movies/Multimedia

NICAM,German

Stereo/AVL/Wide

stereo/Visually

Impaired

Page 7

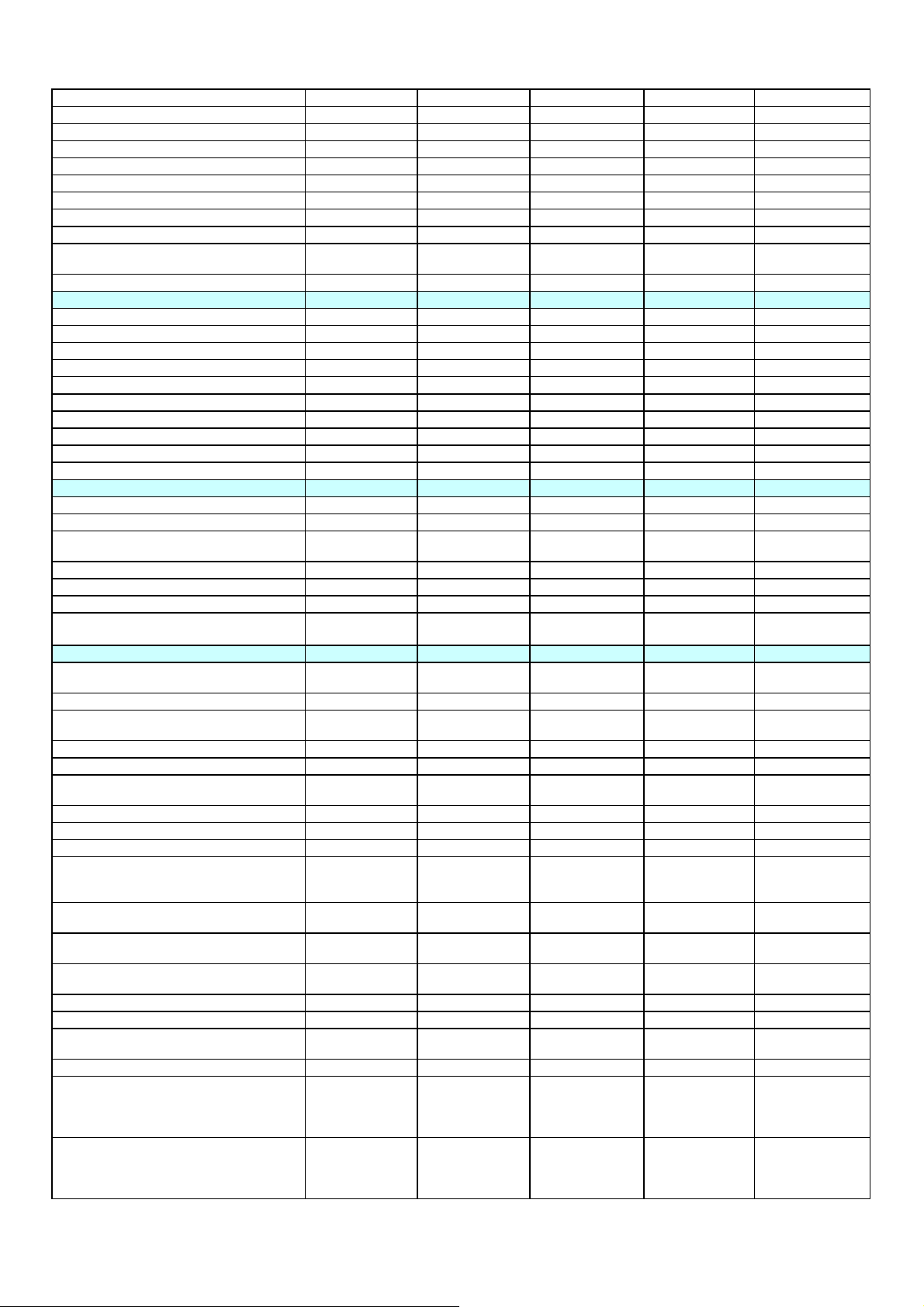

Color System (PAL/SECAM/NTSC)

English\C

h\Ger

DVBT (yes/no) Yes(MPEG 2) Yes(MPEG 2) Yes(MPEG 2) Yes(MPEG 2) Yes(MPEG 2)

Video standard NTSC 3.58 / 4.43 (AV) Yes Yes Yes Yes Yes

HD capability

PC capability (up to maximum format) UXGA UXGA UXGA UXGA UXGA

User convenience

IB languages

Program Numbers (example: 99+3AV)

Number of buttons on cabinet (Power; Vol+/-;

Pr+/-, Menu )

Main switch button (yes/no) No No No No No

Clock Yes Yes Yes Yes Yes

Sleep timer Yes Yes Yes Yes Yes

wake-up timer Yes Yes Yes Yes Yes

Parent Control - Channel lock (Input code for

certain channel)

Parent Control - Child lock (set the lock of the

keyboard, only the RCU can control the TV)

Parent Control - Kid pass (preset the ontime,

channel for each day of the week)

Parent Control - Channel lock (For digital

transmission and DVD program, to filter some

programms)

Program auto switch off Yes Yes Yes Yes Yes

OSD Language*

OSD Positioning No No No No No

OSD Transparency Adjust No No No No No

OSD Timeout Adjust No No No No No

Text Standard: (Top, FLOF,,,) TOP & FLOF TOP & FLOF TOP & FLOF TOP & FLOF TOP & FLOF

Teletext Level: 2.5 / 1.5 1.5 1.5 1.5 1.5 1.5

Pages for teletext 1000 1000 1000 1000 1000

Teletext character sets ****

TV Guide Yes Yes Yes Yes Yes

Auto Naming/Auto Sorting Yes/Yes Yes/Yes Yes/Yes Yes/Yes Yes/Yes

Auto update (for DVBT software ugrades) No No No No No

Multipicture : PIP (Double Tuner) / PIP (AV) /

PAP / PAT / PIC

Hotel mode (Y/N) No No No No No

Tuner FM (yes/no) Yes(in DVB-T) Yes(in DVB-T) Yes(in DVB-T) Yes(in DVB-T) Yes(in DVB-T)

Connectors (if possible, please indicate the

position)

RF Input (Antenna): Analogical / Digital 2 in 1 2 in 1 2 in 1 2 in 1 2 in 1

Scart 1 : CVBS / RGB / S-VIDEO 1/1/- 1/1/- 1/1/- 1/1/- 1/1/CINCH audio in / out (No volumpe control on

Audio out/can be jack 3,5mm)

CINCH video in / out 1(side)/- 1(side)/- 1(side)/- 1(side)/- 1(side)/S-video in / out 1(side)/- 1(side)/- 1(side)/- 1(side)/- 1(side)/-

PAL/SECAM/NTSC(

AV)

YES (720p, 1080i;

1080P 480i/p;

576i/p)

English\Czech\Germ

an\Spanish\Finnish\

French\Greek\Hung

arian\Italian\Dutch\P

olish\Portuguese\Ru

ssian\Swedish\Slova

k\Ukrainian\Estonian

\Latvian\Lithuanian\

Turkish\Norwegian

999+1AV+1SVIDEO

+1CMP+1VGA+2HD

MIs+1SCART

Power, CH +/–, Vol

+/–, Menu

Yes Yes Yes Yes Yes

No No No No No

No No No No No

No No No No No

Bulgarian\Czech\Da

nish\German\Greek\

English\Spanish\Fre

nch\Croatian\Italian\

Hungarian\Dutch\No

rwegian\Polish\Portu

guese\Romanian\Ru

ssian\Slovak\Sloveni

an\Serbian\Finnish\

Swedish\Turkish

Latin Pan-Euro

West

Latin Pan-Euro East

Cyrillic(RussiaBulgarian/Ukrainian/

Byelorussia)

Greek

Arabic

only PAT only PAT only PAT only PAT only PAT

1(side)/- 1(side)/- 1(side)/- 1(side)/- 1(side)/-

PAL/SECAM/NTSC(

AV)

YES (720p, 1080i;

1080P 480i/p;

576i/p)

English\Czech\Germ

an\Spanish\Finnish\

French\Greek\Hung

arian\Italian\Dutch\P

olish\Portuguese\Ru

ssian\Swedish\Slova

k\Ukrainian\Estonian

\Latvian\Lithuanian\

Turkish\Norwegian

999+1AV+1SVIDEO

+1CMP+1VGA+2HD

MIs+1SCART

Power, CH +/–, Vol

+/–, Menu

Bulgarian\Czech\Da

nish\German\Greek\

English\Spanish\Fre

nch\Croatian\Italian\

Hungarian\Dutch\No

rwegian\Polish\Portu

guese\Romanian\Ru

ssian\Slovak\Sloveni

an\Serbian\Finnish\

Swedish\Turkish

Latin Pan-Euro

West

Latin Pan-Euro East

Cyrillic(RussiaBulgarian/Ukrainian/

Byelorussia)

Greek

Arabic

PAL/SECAM/NTSC(

AV)

YES (720p, 1080i;

1080P 480i/p;

576i/p)

English\Czech\Germ

an\Spanish\Finnish\F

rench\Greek\Hungari

an\Italian\Dutch\Poli

sh\Portuguese\Russi

an\Swedish\Slovak\

Ukrainian\Estonian\L

atvian\Lithuanian\Tur

kish\Norwegian

999+1AV+1SVIDEO

+1CMP+1VGA+2HD

MIs+1SCART

Power, CH +/–, Vol

+/–, Menu

Bulgarian\Czech\Dan

ish\German\Greek\E

nglish\Spanish\Frenc

h\Croatian\Italian\Hu

ngarian\Dutch\Norwe

gian\Polish\Portugue

se\Romanian\Russia

n\Slovak\Slovenian\

Serbian\Finnish\Swe

dish\Turkish

Latin Pan-Euro West

Latin Pan-Euro East

Cyrillic(RussiaBulgarian/Ukrainian/

Byelorussia)

Greek

Arabic

PAL/SECAM/NTSC(

AV)

YES (720p, 1080i;

1080P 480i/p;

576i/p)

zec

man\Spanish\Finnis

h\French\Greek\Hun

garian\Italian\Dutch\

Polish\Portuguese\

Russian\Swedish\Sl

ovak\Ukrainian\Esto

nian\Latvian\Lithuan

ian\Turkish\Norwegi

999+1AV+1SVIDEO

+1CMP+1VGA+2H

DMIs+1SCART

Power, CH +/–, Vol

+/–, Menu

Bulgarian\Czech\Da

nish\German\Greek\

English\Spanish\Fre

nch\Croatian\Italian\

Hungarian\Dutch\No

rwegian\Polish\Port

uguese\Romanian\R

ussian\Slovak\Slove

nian\Serbian\Finnish

\Swedish\Turkish

Latin Pan-Euro

West

Latin Pan-Euro East

Cyrillic(RussiaBulgarian/Ukrainian/

Byelorussia)

Greek

Arabic

PAL/SECAM/NTSC(

AV)

YES (720p, 1080i;

1080P 480i/p; 576i/p)

English\Czech\Germ

an\Spanish\Finnish\F

rench\Greek\Hungari

an\Italian\Dutch\Polis

h\Portuguese\Russia

n\Swedish\Slovak\Uk

rainian\Estonian\Latv

ian\Lithuanian\Turkis

h\Norwegian

999+1AV+1SVIDEO

+1CMP+1VGA+2HD

MIs+1SCART

Power, CH +/–, Vol

+/–, Menu

Bulgarian\Czech\Dan

ish\German\Greek\E

nglish\Spanish\Frenc

h\Croatian\Italian\Hu

ngarian\Dutch\Norwe

gian\Polish\Portugue

se\Romanian\Russia

n\Slovak\Slovenian\S

erbian\Finnish\Swedi

sh\Turkish

Latin Pan-Euro West

Latin Pan-Euro East

Cyrillic(RussiaBulgarian/Ukrainian/

Byelorussia)

Greek

Arabic

Page 8

Component Video Input (YCrCb/YPrPb) 1(rear) 1(rear) 1(rear) 1(rear) 1(rear)

Component Audio Input (YCrCb/YPrPb) 1(rear) 1(rear) 1(rear) 1(rear) 1(rear)

VGA in / Audio L/R in / Jack audio in 3.5mm 1/-/1 1/-/1 1/-/1 1/-/1 1/-/1

HDMI1.3 2(1.3) 2(1.3) 2(1.3) 2(1.3) 2(1.3)

DVI-HDCP Share with HDMI Share with HDMI Share with HDMI Share with HDMI Share with HDMI

Audio input for DVI – HDCP share with VGA share with VGA share with VGA share with VGA share with VGA

CINCH subwoofer out / Coaxial out (SP-DIF) -/Yes -/Yes -/Yes -/Yes -/Yes

Headphone connector (mm) 3.5mm,x1 (side) 3.5mm,x1 (side) 3.5mm,x1 (side) 3.5mm,x1 (side) 3.5mm,x1 (side)

RS232 (Y/N) share with VGA share with VGA share with VGA share with VGA share with VGA

USB slot (NO/1.1/2)

Yes(only for SW

update)

Yes(only for SW

update)

Yes(only for SW

update)

Yes(only for SW

update)

Yes(only for SW

update)

DVB-CI (common interface) Yes Yes Yes Yes Yes

Accessories included

Remote control reference RC1994906 RC1994906 RC1994906 RC1994906 RC1994906

Carton (English/French/Spanish) Yes(English) Yes(English) Yes(English) Yes(English) Yes(English)

Batteries Yes Yes Yes Yes Yes

IB Yes Yes Yes Yes Yes

Product registration Card No No No No No

AC power cords 1 1 1 1 1

Audio Cord (Cinch to Jack 3.5mm) No No No No No

VGA Cord No No No No No

Wallmount No No No No No

Antenna Cable No No No No No

General Data

Size (W x H x D, with stand) in mm 529x439x180 663x504x205 663x504x205 796x582x230 796x582x230

Size (W x H x D, without stand) in mm 529x403x73.5 663x461x108 663x461x108 796x535x102 796x535x102

Package Size (W x H x D, with stand but not

mount) in mm

640x520x202 771x548x237 771x548x237 915x652x249 915x652x249

Net Weight in kg 4.9 12 12 15.5 15.5

Gross Weight in Kg 7 14 14 18 18

Power supply 220-240V 50HZ 220-240V 50HZ 220-240V 50HZ 220-240V 50HZ 220-240V 50HZ

Power consumption working / standby / Annual 53W/1W/85KWH 85W/<1W/132KWH 85W/<1W/132KWH

130W/<1W/197KW

h

130W/<1W/198KWh

Design / Mechanical

Wallmount VESA compatible (standard

reference)

VESA compatible VESA compatible VESA compatible VESA compatible VESA compatible

Wallmount VESA Size 100mmx100mm 100mmx100mm 100mmx100mm 200mmx100mm 200mmx100mm

Adaptor for VESA wallmount compatibility

(accessory ref)

No No No No No

Desktop Stand (included/optionnal + ref/NO) Yes Yes Yes Yes Yes

Panel Tilt (Fowards/Backwards/Rotation) No No No No No

Swivel function desktop stand (yes/no) +

motorized?

No No No No No

Docking station (yes/no) No No No No No

Floor Stand (included/optionnal + ref/NO) No No No No No

Glass shield (yes/no) No No No No No

Finish on Front

Finish on side

Finish on back

Finish on stand

HG Spray

paint(Black Q8257)

Black A8252 as

moulded

Black A8252 as

moulded

HG Spray

paint(Black Q8257)

Half translucent as

moulded (high

glossy black)

Black A8252 as

moulded

Black A8252 as

moulded

HG Spray

paint(Black Q0003)

HG Spray

paint(Black Q8257)

Black A8252 as

moulded

Black A8252 as

moulded

HG Spray

paint(Black Q8257)

Half translucent as

moulded (high

glossy black)

Black A8252 as

moulded

Black A8252 as

moulded

HG Spray

paint(Black Q0003)

HG Spray

paint(Black Q8257)

Black A8252 as

moulded

Black A8252 as

moulded

HG Spray

paint(Black Q8257)

number of colors on carton box 1 1 1 1 1

Brand logo THOMSON THOMSON THOMSON THOMSON THOMSON

External AC/DC Power with DC power cord

(yes/no)

Number of Speaker

Rating Label langages

Rating Label Logos/Icons (GOST, Bin,

Recycling, Caution, …)

No/No grounded

plug

2 2 2 2 2

DE, FR, IT, ES, EN,

PL, CS, HU, RU,

PT, EL, NL, SV, DA,

FI, NO

CE, GOST,

Recycling, Class

II,DTB, WEEE bin,

Caution

No/No grounded

plug

DE, FR, IT, ES, EN,

PL, CS, HU, RU,

PT, EL, NL, SV, DA,

FI, NO

CE, GOST,

Recycling, Class

II,DTB, WEEE bin,

Caution

No/No grounded

plug

DE, FR, IT, ES, EN,

PL, CS, HU, RU, PT,

EL, NL, SV, DA, FI,

NO

CE, GOST,

Recycling, Class

II,DTB, WEEE bin,

Caution

No/No grounded

plug

DE, FR, IT, ES, EN,

PL, CS, HU, RU,

PT, EL, NL, SV, DA,

FI, NO

CE, GOST,

Recycling, Class

II,DTB, WEEE bin,

Caution

No/No grounded plug

DE, FR, IT, ES, EN,

PL, CS, HU, RU, PT,

EL, NL, SV, DA, FI,

NO

CE, GOST,

Recycling, Class

II,DTB, WEEE bin,

Caution

Page 9

Test and Alignment Specification for MT35-V0.20

The xxE90/E92NH22 models are Europe LCD platform with DVB-T designed for driving below

panels:

• 32” LPL (LVDS)

• 26” CMO(LVDS)

• 22” AUO(DUAL LVDS)

The main chip is from Mediatec (MTK5335 series) and supports below inputs:

• one analog and digital mixed RF (PAL B/G D/K I, SECAM B/G D/K L/L’,DVB-T)

• one SCART (CVBS & RGB)

• one CMP (YPrPb can support from 480i up to 1080p)

• one VGA

• two HDMI (can support 480i/p, 576i/p, 720p up to 1080i/p)

compliant v1.2. with HDCP, audio included as EIA-861B standard

• one S-Video input

• one Headphone output

• one SPDIF output

More relevant details are listed into the Spec.

INFO:

ª All tests and measurements mentioned hereafter have to be carried out at a normal mains

voltage (110 ~ 240 VAC)

ª All voltages have to be measured with respect to ground, unless otherwise stated

ª All final tests have to be done on a complete set including LCD panel in a room with temperature

of 25+/-7°C

ª The White Balance (color temperature) has to be performed into subdued lighted room after at

least 1 hour of warm-up/burn-in. This is applicable for both Alignment and Picture Performance

evaluation at OQA in order to be set free of any temperature drift (colorimetry vs time)

1. Electrical Assembly Alignment

1.1. Preconditions – DC/DC Check

Before Power On the chassis, please check and make sure that U801,U802,U805, U809, U803,

U804, U811,U201,C817(positive) outputs are not shorted to ground.

Supply 12v and 5v to P804 and test the relative voltage.

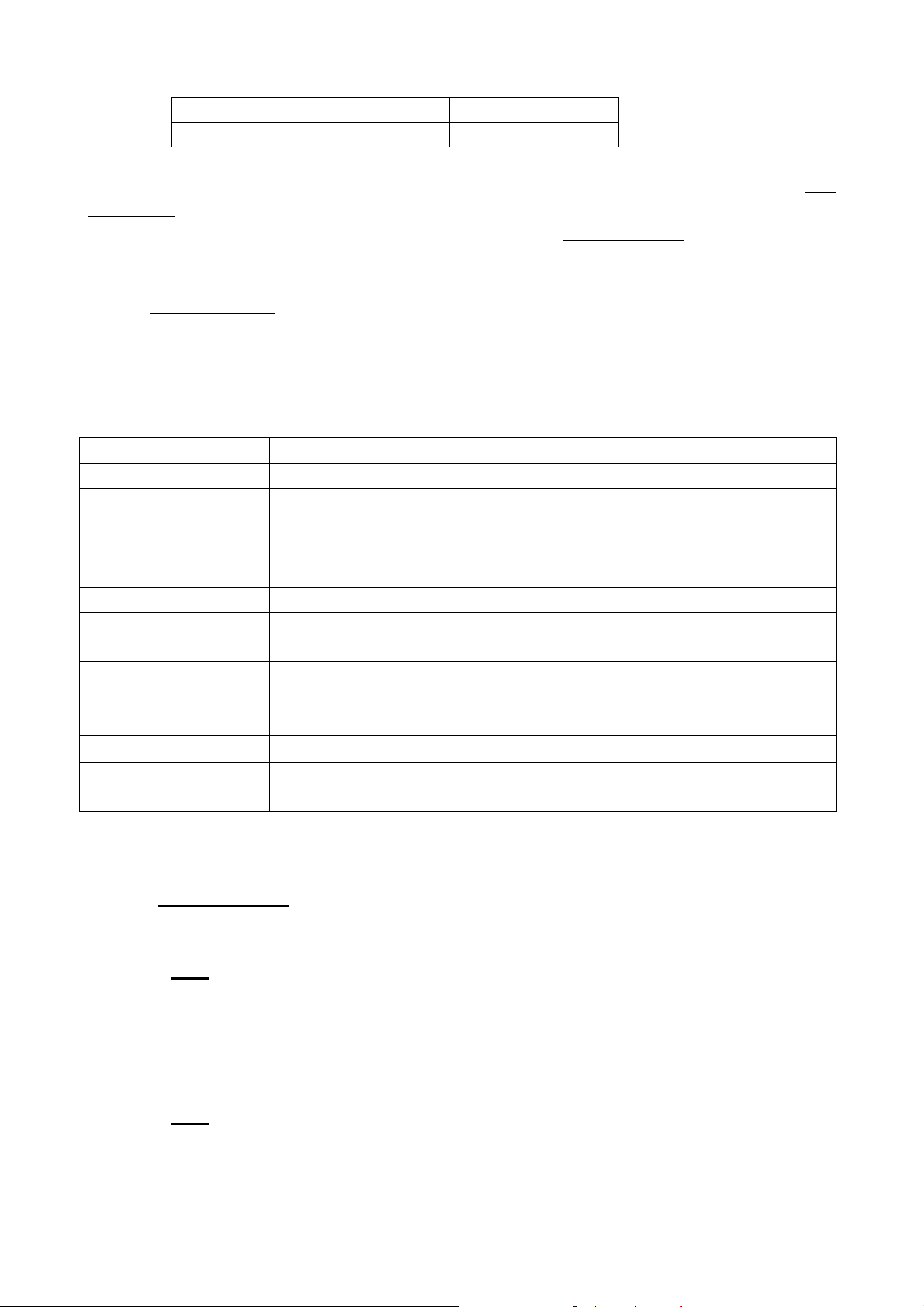

position value

U811 3.3V +/-5%

U801 3.3V +/-5%

U802 9V +/-5%

U803 1.2V +/-5%

U804 2.5V +/-5%

U805 5V +/-5%

U809 3.3V +/-5%

Page 10

U201 2.6V +/-5%

C817(+) 1.19V +/-5%

Download latest release MCU_SW into the Standby CPU(U810) using WT_MCU_ISP SW tool. See

Appendixn “How to download MCU SW”.

Download latest release SW into the flash using MTK SW tool. See Appendixo

“How to download

FLASH SW”. Or download the SW from USB port.

1.2. Functional Test

Once the boards (chassis, FAV, KB, IR, PSU…) and the panel are well interconnected, connect all

external generator devices to relevant inputs/outputs below according to their respective test

patterns format and check picture content and sound quality accordingly:

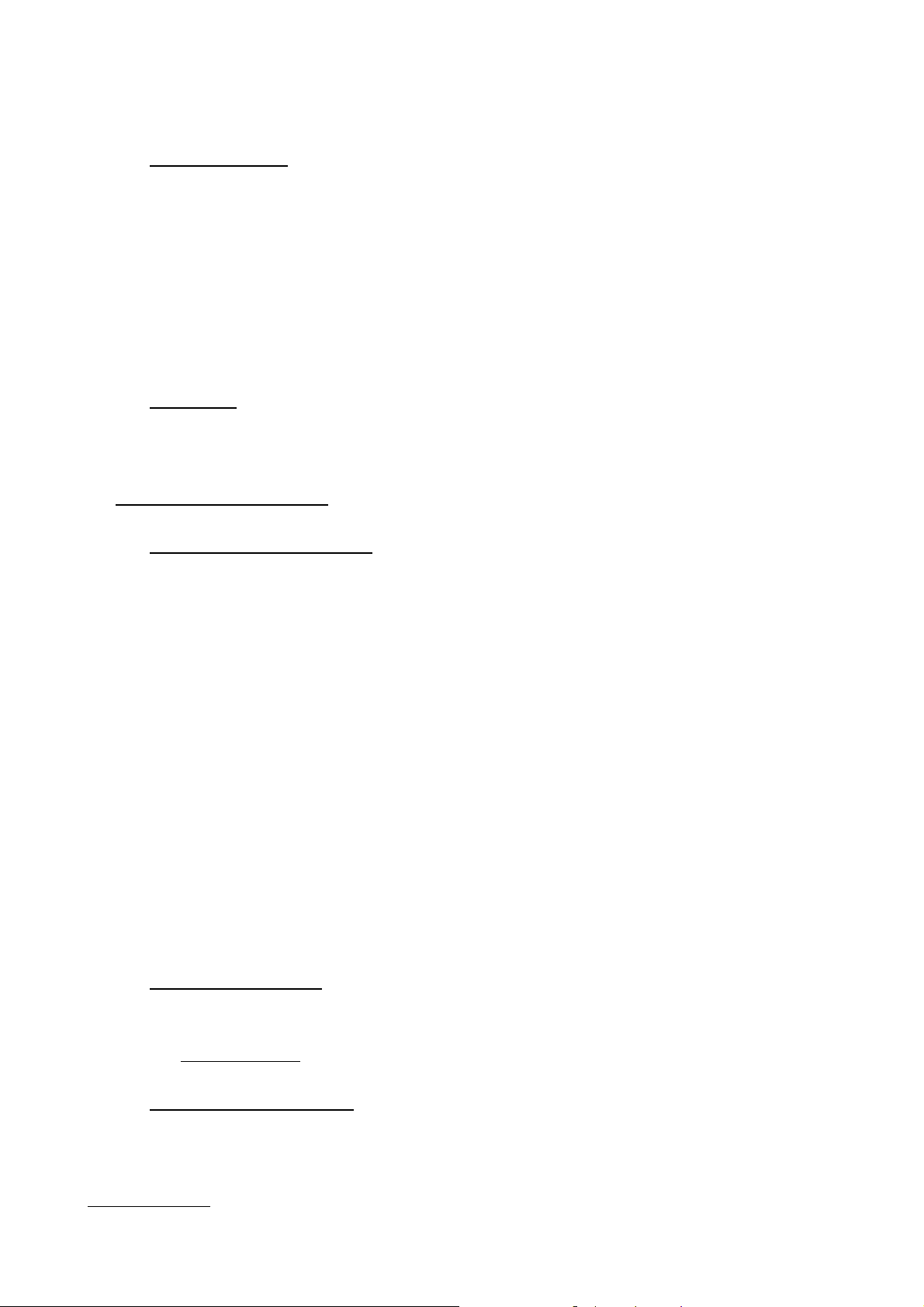

Source Test signal (generator) Test pattern (format/image)

Analog /Digital Tuner RF cable Full Band (VHF/UHF) + CATV DVB-T

SCART1 (CVBS) Chroma/Fluke PAL Half Color & Gray bars

Side av (cvbs)–

Chroma/Fluke PAL Half Color & Gray bars

SVideo(Y/C)

SCART1 (RGB) Chroma/Fluke Half Color & Gray bars

SCART1 (CVBSOut) RF cable First channel

HDMI DVD with HDMI

Movie 720p@60Hz

compliancy

VGA Chroma/QuantumData 1024x768@60Hz

Half Color & Gray bars

Headphone RF cable First channel

Loud Speakers RF cable First channel

CMP (YPrPb) Chroma/QuantumData 1080i@60Hz

Half Color & Gray bars

Audio tones can be defined by the factory (ie: 1KHz & 3KHz, sweep, …).

Picture video formats can be changed by the factory according to their own standard.

1.3. ADC Calibration

Two inputs require an ADC calibration for the time being, That are:

VGA

Provide a test signal 1024×768@60Hz with White Black squares.

Select the corresponding “Auto Color” submenu item from “Factory Menu”, then press ”OK” to

start.

When VGA channel is aligned, SCAR T-RGB is also aligned, so it is not necessary for RGB to be

separately aligned.

CMP

Provide a test signal 576i@50Hz with 100% 8 steps Color Bar.

Select the corresponding “Auto Color” submenu item from “Factory Menu”, then press ”OK” to

start.

Page 11

The ADC is well performed when it’s displayed “CMP” after few seconds.

1.4. DDC & EDID Test

The E-EDID data structure are according to VESA Enhanced EDID 1.3 (and EIA/CEA-861B for

HDMI).

Both VGA and HDMI have their own separate bin files:

For EDID check, it’s needed to check whether the correct EDID is downloaded by checking

corresponding EDID NVM Checksum or read them out to check bit by bit if it is in line with the

released EDID bin file.

• **Before check the EDID please ensure the “Factory Key” in factory menu is disabled

1.5. HDCP Test

For HDCP compliancy, it’s needed to check whether the HDCP key has been well set.

2. Final Assembly Alignment

2.1. Entering to “Factory Menu”

To enter into Factory Menu in case of “Factory Key” is disabled, please to follow below steps:

- press Remote Control key “MENU” to display main menu

- press the subsequence Remote Control keys “7”, “9”, “1” and “5”

- press Remote Control key “MENU” to exit main menu

- press Remote Control key “MENU” to display main menu again

The main menu will display ”FACTCORY” at the last item

To pop-up Factory Menu in case of “Factory Key” is enabled, please to follow below step:

- press Remote Control key “Blue”

To enable/disable “Factory Key”, please to follow below steps:

- press Remote Control “OK” key to enter into “System” submenu

- press Remote Control “RIGHT ”or “LEFT” key till “Factory Key” item

- press Remote Control “OK” key to toggle mode

To exit “Factory Menu”, press “Exit” key from Remote Control.

To comeback to “Factory Menu” root when you are into a submenu:

- press Remote Control “RED” key.

Entering to “P” Mode

2.2.

To enter into “P” mode, an external serial 3.3VDC device is required for sending relevant

commands. See appendixp

“Serial Command Protocol for MTKxx”.

2.3. White Balance Alignment

Only VGA input requires color temperature adjustment as all other inputs or relative ones. Both

Warm and Cool Color Coordinates are also relatives to Normal Color Temperature mode ones.

See appendixq

“CVBS/RGB/CMP/HDMI Relative Matrix Offsets” and “WARM/COOL Relative

Page 12

Matrix Offsets”. Those offsets values don’t require any alignment but can be fine-tuned in Factory

Menu as well.

<The appendix is just a template, Every lot the relative offset is different. We need to align 5 sets

first to get the relative offset data every lot. >

Expected Targets and Tolerances

The measured parameters should be “x, y” coordinates.

The White Balance alignment should be performed using a contact less analyzer (ei: Minolta

CA-210). The analyzer may not touch the screen surface, and measurement must be performed in

a dark environment keeping the probe(s) at 90+/-2° from the panel.

The alignment has to fulfill the requirements in Application Form.

2.4. High Pot. and Insulating Resistance Tests

At the end of the process, a High Pot. and an Insulating Resistance tests are required for

matching Safety Electrical requirements (ei: xxxx)

High Voltage Withstanding requirements

- “Voltage” Ö 4240 VDC

- “Max Leakage Current” Ö 1 mA

- “Test Time” Ö 3 sec

Insulating Resistance requirements

- “Voltage” Ö DC500V

- “Threshold Max” Ö

- “Threshold Min” Ö 4MΩ

- “Test Time” Ö 3 sec

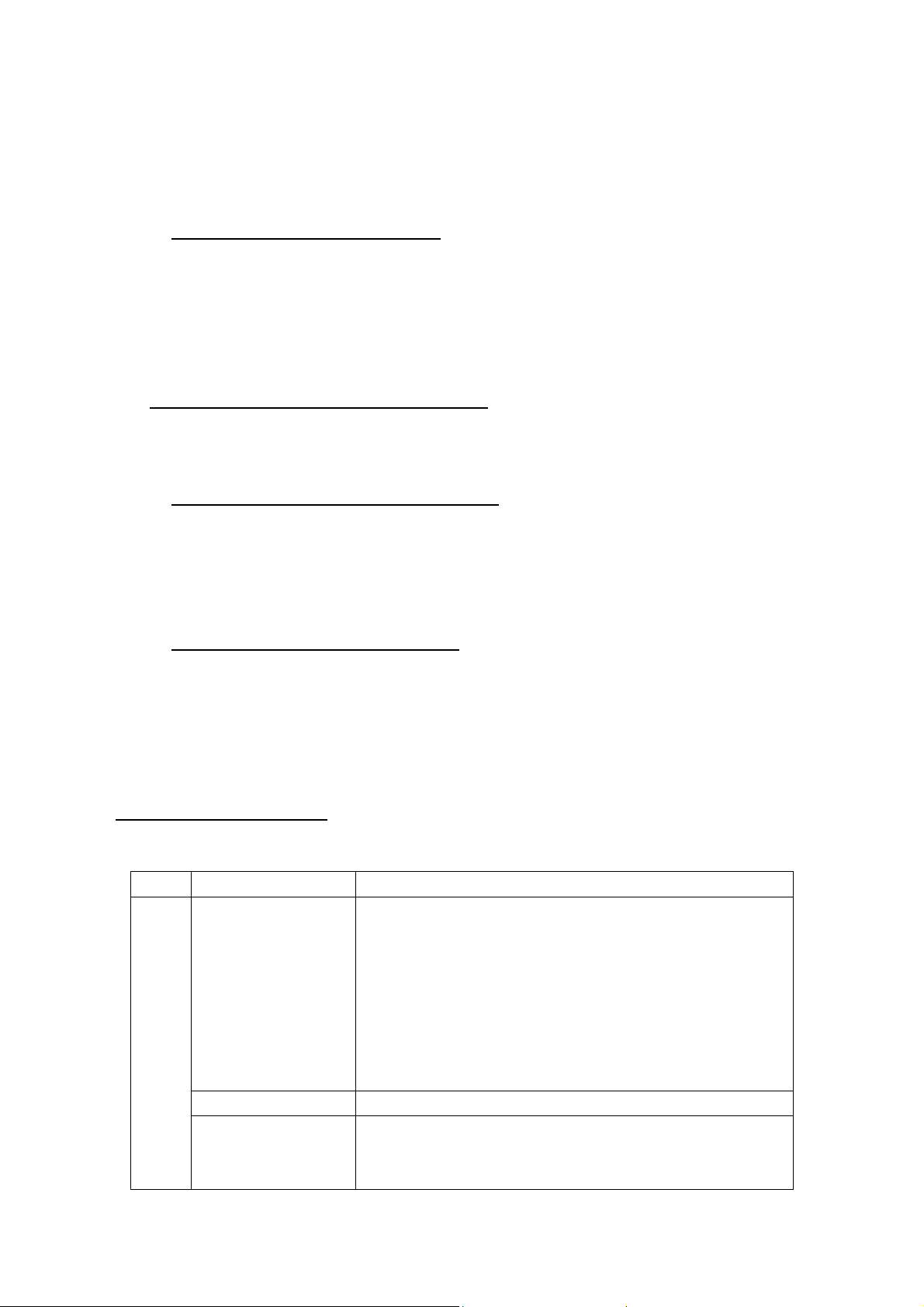

3. “Factory Menu” Definition

1). System

Item Sub-item

Factory Key OFF:Factory Key is invalidation

ON :Factory Key is availability, and BLUE key is the shortcut key.

Note: option step

1)Enter menu

2)7915

3)Exit/Enter menu

4)Enter Factory Item

Enter Factory menu .(Or Enter Factory mode by hotkey )

Burning Mode Off/On

Power Mode Boot/Standby/Previous

Boot: Enter power on mode

Standby: Enter standby mode

Page 13

Pre- frequency

table

Reset

TECI command

2). Balance

Item Sub-item

Balance

Source For balance source

Tone Normal/Warm/Cool

Auto Color

White R R White balance

White G G White balance

White B B White balance

Gray R R Gray balance

Gray G G Gray balance

Gray B B Gray balance

3).Sound Volume Curve

Item Sub-item

Sound

VOL_0 0

Previous: power on according to last status

HuiZhou/ Poland

Note:Pre-Frequency table(HuiZhou/ Poland)

Reset EEPROM data, and load the default value of EEPROM

All: clear NVM values,and set to default value。

User: Clear date of NVM in user menu, except the value of

language / related installation/Factory setting, then set to the

default value.

Shop: Clear date of NVM in user menu, include the val ue related

installation, and Clear date of factory menu except the item

of Balance and sound ,set to default value

Note:Priority below basic function of Factory menu

Note:Switch SOURCE used left/right key

Note: RGB gain range is 0-255

The value of Warm and cool is the

offset of Normal mode, their range is

-128-127, if the offset value beyond

the boundary,set to max or min

value.

Note:display the completed source name

on the right of item,If all the sourcs is

ok ,show “All”

VOL_10 2

VOL_50 14

VOL_90 135

VOL_100 255

Note:mapping volume value

to 0—255 of the MCU

register

Page 14

TV Pre 186

AV Pre 186

4).INFO SW version information

Info

Project LCD_5335_TCL

MTK Version XXXXXX

Version IDTV-XXXXXX_XX

DATE 2008-XX-XX

5).Factory default settings

Followed as OOB setting.

Appendix n

“How to download MCU SW”

Prepare WT_MCU_ISP SW tool for update.

1. Connect the PC to board using MCU updating tool on P802 connector form chassis board.

2. Provide the +5VDC on P804 connector form chassis board and check U811 output voltage

should be 3.3V.

3. Start “WT_MCU_ISP.exe” and download the MCU SW. ( please see file

ISPToolGuideV33-08-2-17)

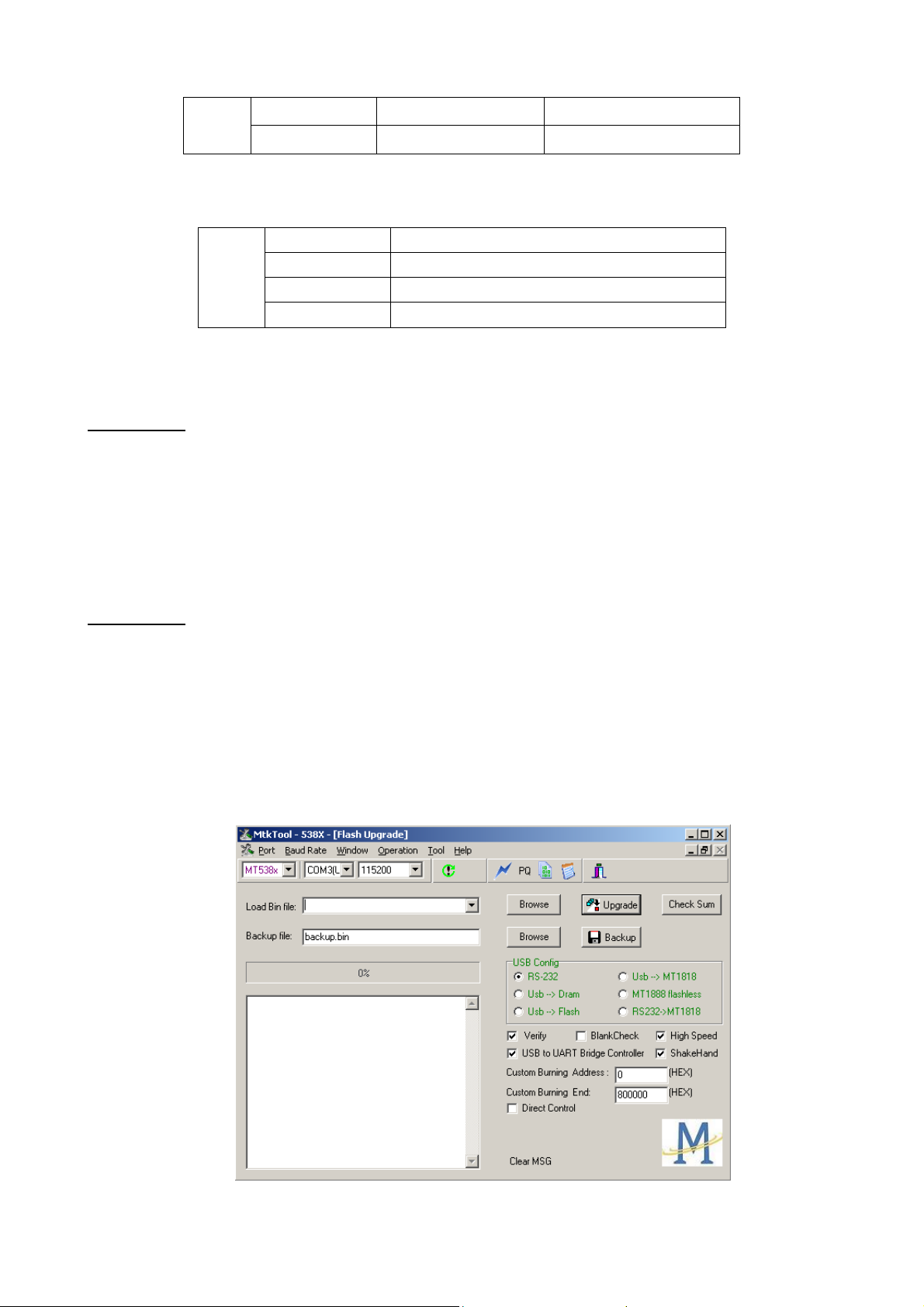

Appendix o

“How to download FLASH SW”

Prepare MTK SW tool for update.

1. Connect the PC to the board using an external +3.3VDC serial device (USB or COMx) on

P201 connector from chassis board. VGA input can also be used using pin12 (RXD) & pin15

(TXD) just taking care that “Factory Key” from Factory Menu is enabled.

2. Provide the +5VDC STB on P804 connector from chassis board

3. Start “MTKTOOL.exe” application under MTKxx folder, and set the parameters as below

picture:

Page 15

4. Press “Browse” button to select the corresponding SW bin file to upload

5. Press “Upgrade” button to start downloading the SW and wait the gauge displayed “100%”

that means the SW has been successfully downloaded.

In the meanwhile, all operations such erasing flash and so… are parsed into the debug

window script.

6. Once the SW is downloaded, switch-off/on the chassis board and wait few seconds for

Eeprom update.

Appendix p

“Serial Command Protocol for MTKxx”

1. A serial protocol for driving MTK µchip through external +3.3VDC serial device (USB or

COMx) is available. It may facilitate manufacturing process. Thus, both P201 connector from

chassis board or either VGA input can also be used using pin12 (RXD) & pin15 (TXD) just

taking care that “Factory Key” from Factory Menu is enabled.

2. The required serial port settings are as below

• 115200 bps

• 8 data bit

• 1 bit stop

• none parity

3. The command format is like hereafter described into BNS representation:

• 0xBB + Command + Data[[..] + ..] + 0xEE

Both 0xBB and 0xEE bytes are mandatory and used as header and footer of the

transmitted frame. Apart from INIT frame that is described further, all sent bytes need to be triggered

before by an additional one as 0x50. So a complete frame might match following one:

• 0x50+0xBB+0x50+Command+0x50+Data[[..]+0x50+..]+0x50+0xEE

4. At first time, it might be required to initialize MTK µchip by using once below INIT command

(without any triggering byte):

• 0x02 + 0x00 + 0x00 + 0x13 + 0x01 + 0x00

5. A none exhaustive list of commands is already available.

Appendix q

“ WARM/COOL Relative Matrix Offsets”

1. These offsets should be done in the production by AOE.

Page 16

MT5335PU Approval Datasheet

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE

MTK CONFIDENTIAL, NO DISCLOSURE

GENERAL DESCRIPTION

The MediaTek MT5335PU family consists of a backend decoder and a TV controller and offers high

integration for advanced applications. It combines a transport de-multiplexer, a high definition MPEG-2

video decoder, an MPEG2 audio decoder, an LVDS transmitter, and an NTSC/PAL/SECAM TV decoder

with a 3D comb filter. The MT5335PU enables consumer electronics manufactures to build high quality, low

cost and feature-rich iDTVs.

World-Leading Audio/Video Technology: The MT5335PU family has built-in high resolution and

TM

high-quality audio codec. It includes MediaTek MDDi

de-interlace solution to generate very smooth

picture quality for motions. A 3D comb filter added to the TV decoder recovers great detail for still pictures.

The special color processing technology provides natural, deep colors and true studio quality graphics.

Rich Features for High Value Products: The MT5335PU family enables a true single-chip experience. It

integrates high-quality HDMI1.3, high speed VGA ADC, dual-channel LVDS, and USB2.0 receiver

Reliable Front-end Receiving Capability: Excellent adjacent and co-channel rejection capability grants

customers never miss any wonderful stream. Professional error-concealment provides stable, smooth and

mosaic-free video quality.

Key Features:

An transport demultiplexer

An MPEG2 video decoder

An AC3 audio decoder

Note: All Package are Lead Free

HDMI1.3 receiver

Audio codec

FEATURES

1/14

Page 17

MT5335PU Approval Datasheet

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE

Host CPU

ARM 926EJS

8K I-Cache and 8K D-Cache

4K Instruction TCM

JTAG ICE interface

Watch Dog timers

Transport Demultiplexer

Supports a serial or parallel transport stream input

Supports DVB-T, MPEG-2 transport stream input

Supports DES/3-DES/DVB de-scramblers

Up to 8-PID even/odd keys for descrambling

Supports 32 PID filters and 32 section filters

Supports positive/negative/mask section filtering

Supports hardware CRC-32 check

Supports PCR recovery function

Supports a micro-processor for stream process and MPEG start code detection

MPEG2 Decoder

Supports one MPEG-2 HD decoder

MPEG MP@ML, MP@HL and MPEG-1 video standards

2D Graphics

Supports multiple color modes

Point, horizontal/vertical line primitive drawings

Rectangle fill and gradient fill functions

Bitblt with transparent options

Alpha blending and alpha composition Bitblt

Stretch Bitblt

Font rendering by color expansion

YCbCr to RGB color space conversion

Supports off-line scaler

MTK CONFIDENTIAL, NO DISCLOSURE

OSD Plane

Two linking list OSDs with multiple color mode and one of them has scaler

Video Plane

Supports video capture and over scan.

Flesh tone management

Gamma/anti-Gamma correction

Color Transient Improvement (CTI)

2D Peaking

Saturation/hue adjustment

Brightness and contrast adjustment

Black and White level extender

Adaptive Luma/Chroma management

Automatic detect film or video source

3:2/2:2 pull down source detection

The MT5335PU support bob mode de-interlace with excellent low angle image processing.

Arbitrary ratio vertical/horizontal scaling of video, from 1/32X to 32X

Advanced non-linear panorama scaling.

2/14

Page 18

MT5335PU Approval Datasheet

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE

Programmable zoom viewer

Progressive or interlace scan output

Supports alpha blending

Dithering processing for flat panel display

Frame rate conversion.

The MT5335PU supports up to 1680x1050 panel and VGA dot-to-dot.

Supports 2 video source PIP/POP feature.

LVDS

MT5335PU supports 6/8/10-bit one–channel or 6/8-bit dual-channel LVDS transmitter, LVDS speeding

up to 75 MHz

Built-in spread spectrum for EMI performance

Programmable panel timing output

CVBS In

On-chip 54 MHz 10-bit video ADC

Supports PAL (B,G,D,H,M,N,I,Nc), NTSC, NTSC-4.43, SECAM

Macrovision detection

NTSC/PAL support 3D comb filter, SECAM supports 2D comb filter

Built-in motion-adaptive 3D Noise Reduction

VBI data slicer for CC/TT decoding

Supports 2-S-Video.

The MT5335PU supports 3-channel CVBS.

Supports SCART connector

VGA In

Supports VGA input up to UXGA 162 MHz

Supports full VESA standards

Component Video In

Supports two component video inputs

Supports 480i / 480p / 576i / 576p / 720p / 1080i / 1080p

Audio line in interface

The MT5335PU support 1-bit line in data (two channels)

HDMI Receiver

Mixed 3 channels of HDMI1.3, data rate can be up to 2.25 GHz

EIA/CEA-861B

CEC

Audio ADC

The MT5335PU supports 8-channel (4 R/L pairs) analog audio input.

MTK CONFIDENTIAL, NO DISCLOSURE

TV audio demodulator

Supports BTSC/EIA-J/A2/NICAM/PAL FM/SECAM world-wide formats

Standard automatic detection

Stereo demodulation, SAP demodulation

Mode selection (Main/SAP/Stereo)

Audio DAC

Four on-chip audio DACs (2 R/L pairs) support R/L channel and subwoofer outputs

DRAM Controller

3/14

Page 19

MT5335PU Approval Datasheet

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE

Supports 64 Mb to 512 Mb DDR DRAM devices

The MT5335PU supports 16-bit data bus; address offers up to 64 M bytes space.

Supports DDR1-333, DDR1-400, DDR2-400, DDR2-533, DDR2-667, DDR2-800

Audio DSP

Supports Dolby Digital AC-3 decoding

MPEG-1 layer I/II decoding (DVB)

Dolby Prologic II

Audio output: 7.1ch + 2ch (down mix)

Pink noise and white noise generator

Equalizer

Bass management

3D surround processing with virtual surround

Audio and video lip synchronization

Supports reverberation

Automatic volume control

One SPDIF out

If internal audio DAC is disabled, the MT5335PU supports 1-bit (2-channel) main audio I

interface. Each channel is up to 24-bit resolution.

Flash Interface

The MT5335PU supports two one serial flash

Serial flash interface supports up to 60 MHz clock rate, depending on the spec. of the flash device

(currently 20 MHz at maximum)

Supports on-the-fly decompression from Serial Flash to DRAM

MTK CONFIDENTIAL, NO DISCLOSURE

2

S output

Peripherals

The MT5335PU has one dedicated UART and one shared UART with GPIO.

The MT5335PU has three basic serial interfaces; one is for the tuner, one is the master for general

purpose and the other is the slave for HDMI EDID data.

Three PWMs

IR blaster and receiver

Real-time clock and watchdog controller

1-port USB2.0/1.1 host supports USB mass storage class devices.

Supports five-channel servo ADC.

IC Outline

The MT5335PU is 256-pin LQFP-EPAD Package

3.3V/1.1V and 2.5V for DDR1, 1.8V for DDR2

4/14

Page 20

MT5335PU Approval Datasheet

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE

MTK CONFIDENTIAL, NO DISCLOSURE

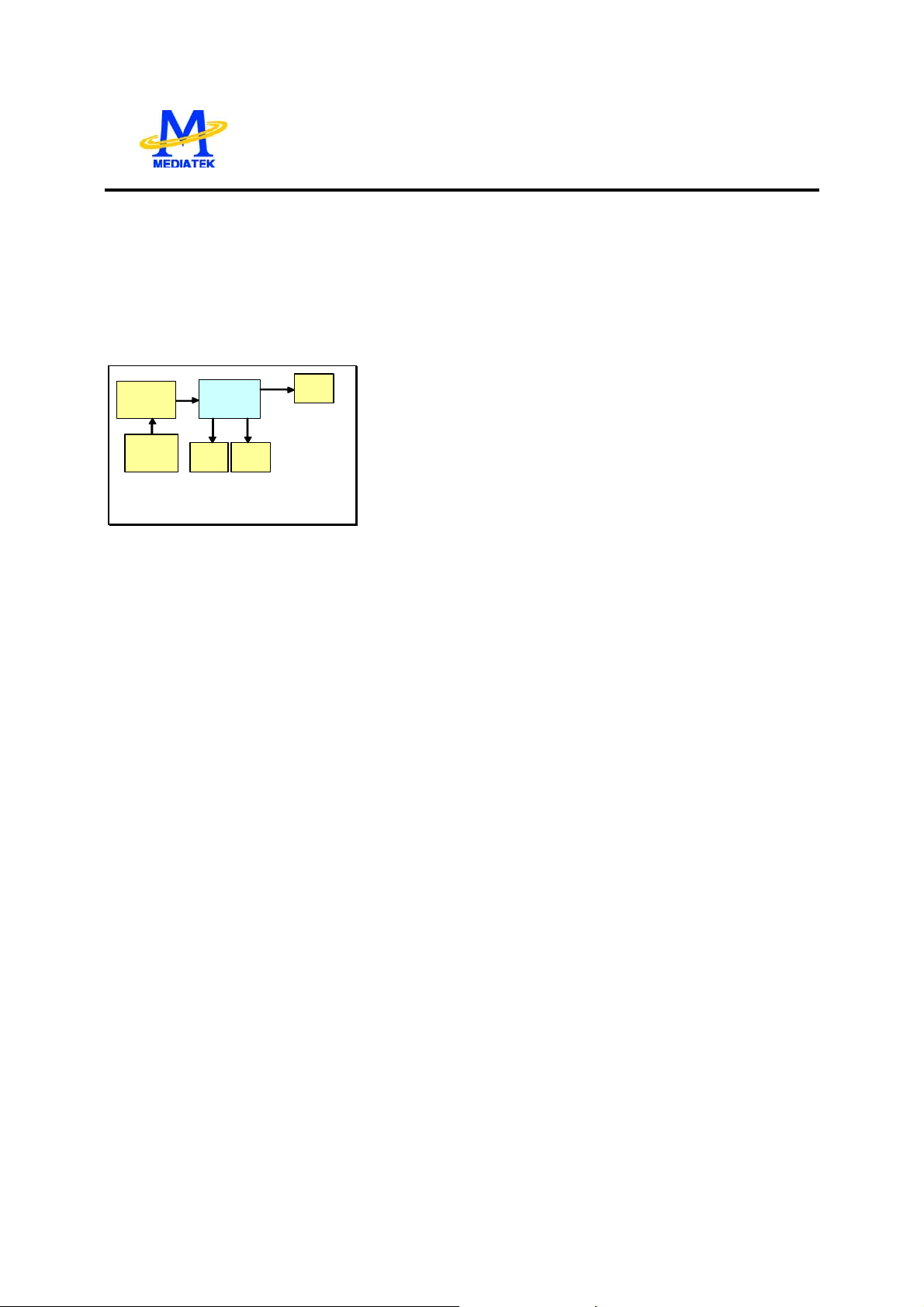

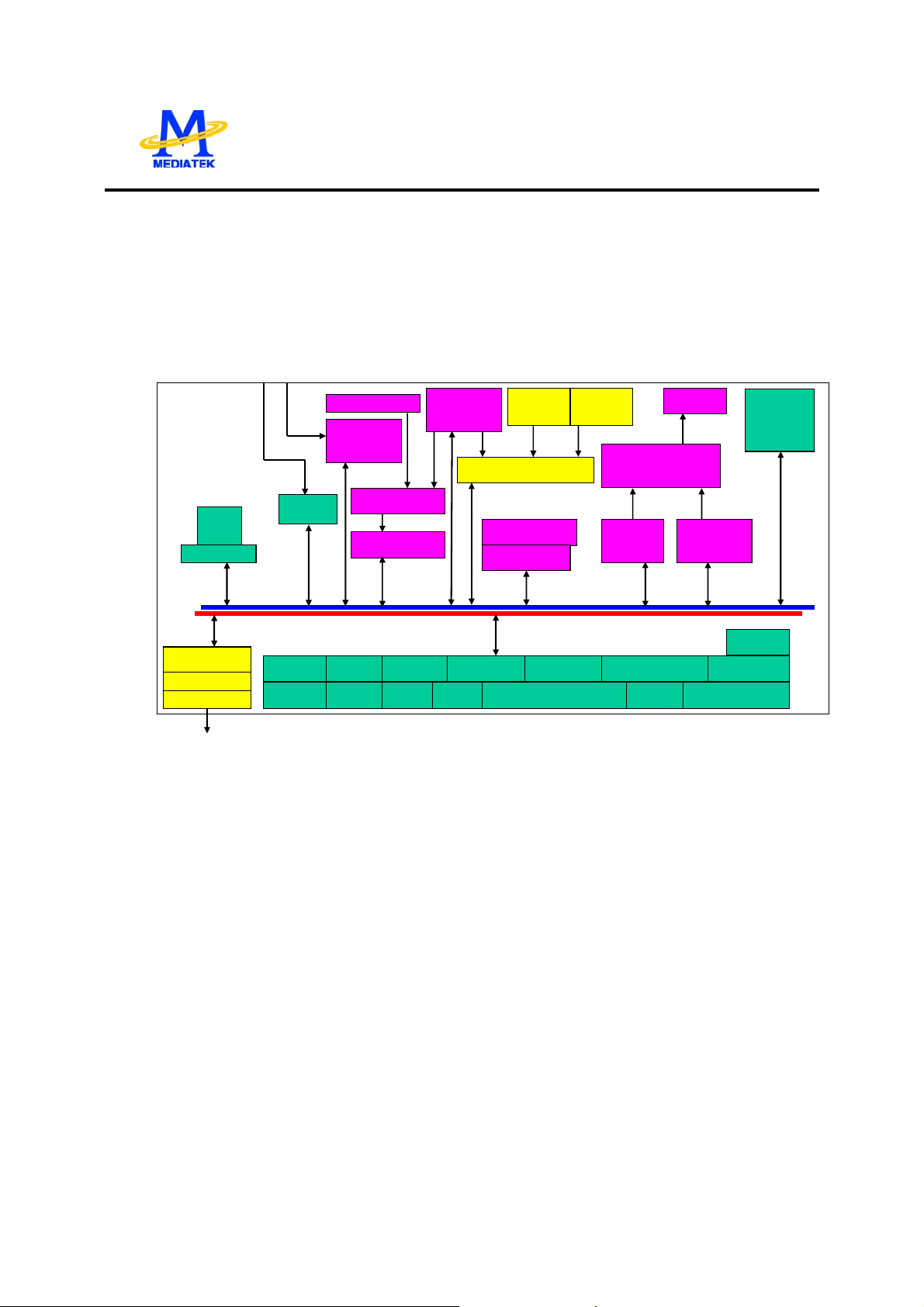

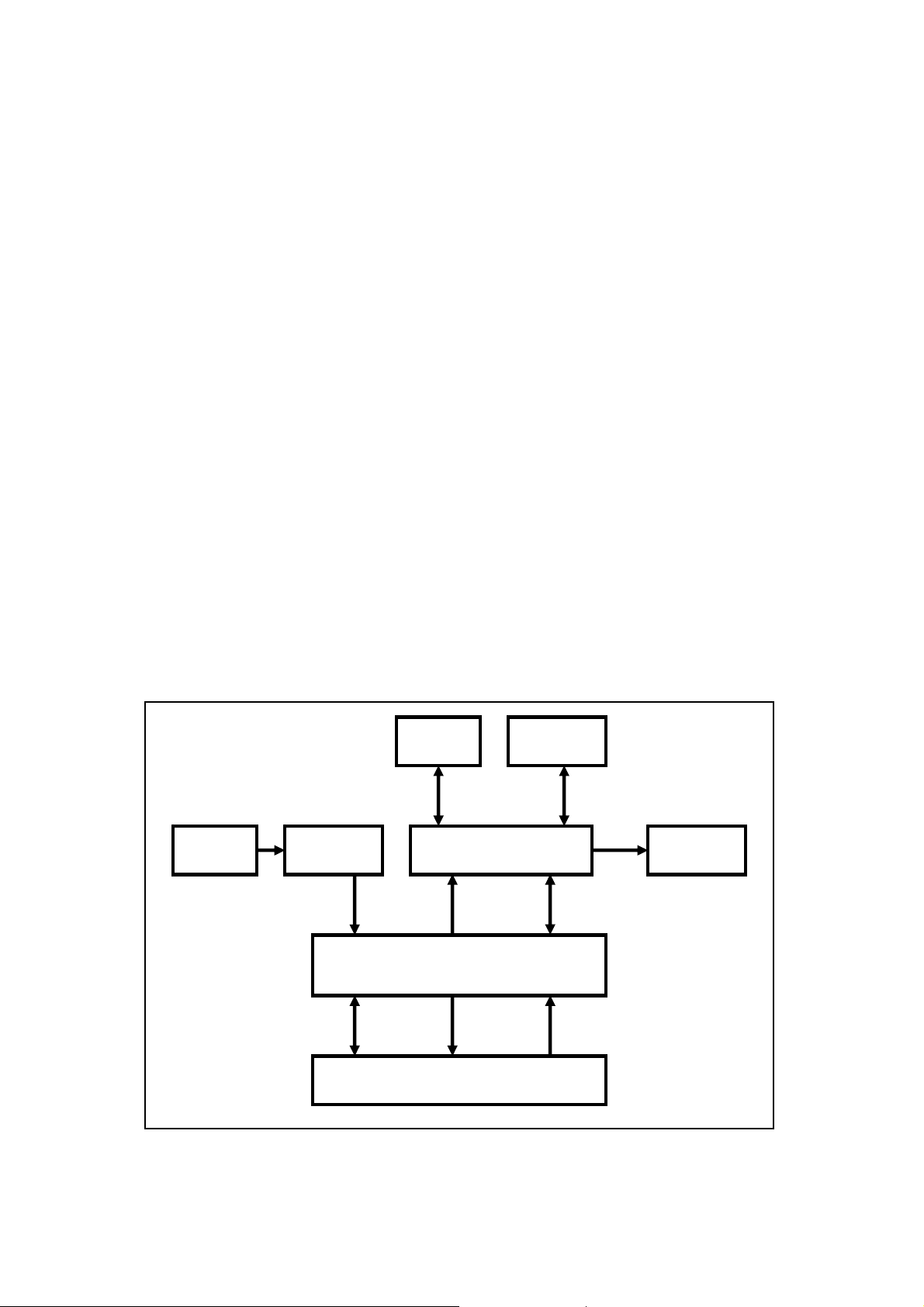

The MT5335PU is designed as an advanced, highly integrated SoC with improved connectivity features

including HDMI interface and component/composite signal connections. Figure 1-1 shows the MT5335PU

system block diagram while Figure 1-2 shows the MT5335PU functional block diagram.

LVDS

LCD

MT5131/3

Tuner

MT 5335P U

DRAMFlash

Pa ne l

Figure 1-1 System Block Diagram

5/14

Page 21

MT5335PU Approval Datasheet

DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE

TS

In

YC Input

CVBS/

VADCx4

Component

Analog

Input

HDMI

Rx

HDMI In

I/F

Tuner

In

Audio

Demod

TV

Decoder

Audio In

VDO-In

De-interlace

IrDA

Serial IF

JPEG,MPEG

2-D Graphic

USB2.0

Watchdog

ARM

BIM

Audio DSP

TS

Demux

JTAG

Audio I/F

Audio DAC

BScan

PCR MS,SD,SM,xD

RTC

UART

MTK CONFIDENTIAL, NO DISCLOSURE

Audio

Input

Audio

ADC

Panel

LVDS

16-bit DDR

DDR

DRAM

Controller

Mix and Post

Processing

OSD

scaler

Vplane

scaler

DRAM Bus

IO Bus

CKGEN

Serial Flash Servo ADC

PWM

NAND Flash

SPDIF, I

2

S

Figure 1-2 Functional Block Diagram

6/14

Page 22

MT5133 DATA SHEET

General Description

1. Introduction

MT5133 is Media Tak’s 2nd generation COFDM (Coded Orthogonal Frequency

Division Multiplex) channel demodulator for DVB-T receiver. It is fully compliant with

the DVB-T specification (ETSI 300744) and Nordig Unified. MT5133 implements the

functions from tuner IF out to MPEG-2 transport stream input. The device can support

2K, 4K or 8K mode with 6, 7, 8MHz channel. By integrating high performance A/D

converters into the chip, MT5133 can accept first or second IF signal from

conventional tuner thus eliminating the need for an external down-converter. Pure

digital synchronization, advance channel estimation and equalization guarantee the

wide acquisition range of MT5133. User can easily access on-chip information,

including signal-to-noise ratio, Bit Error Ratio (BER) before and after Viterbidecoder.

Serial or parallel MPEG transport stream output can be interfaced to all commonly

available backend processor chips.

2. Features

z ETSI300744 and Nordig Unified compliant

z Suitable for Single Frequency Network (SFN) operation

z Support 2K, 4K, 8K modes

z Support QPSK, 16QAM,64QAM constellations

z 1/4, 1/8, 1/16, 1/32 Guard interval

z Support hierarchical & non-hierarchical modes

z Automatic mode detection

z Full-digital timing/frequency with wide acquisition range

z Support triple offset

z On-chip high-performance 10-bit ADC

z Excellent adjacent Channel interference (ACI) rejection capability

z Excellent Co-Channel interference (CCI) rejection capability

z Build-in PID filters

z Very low power consumption < 180Mw

z Controlled by I2C interface

z Package: QFN48

Page 23

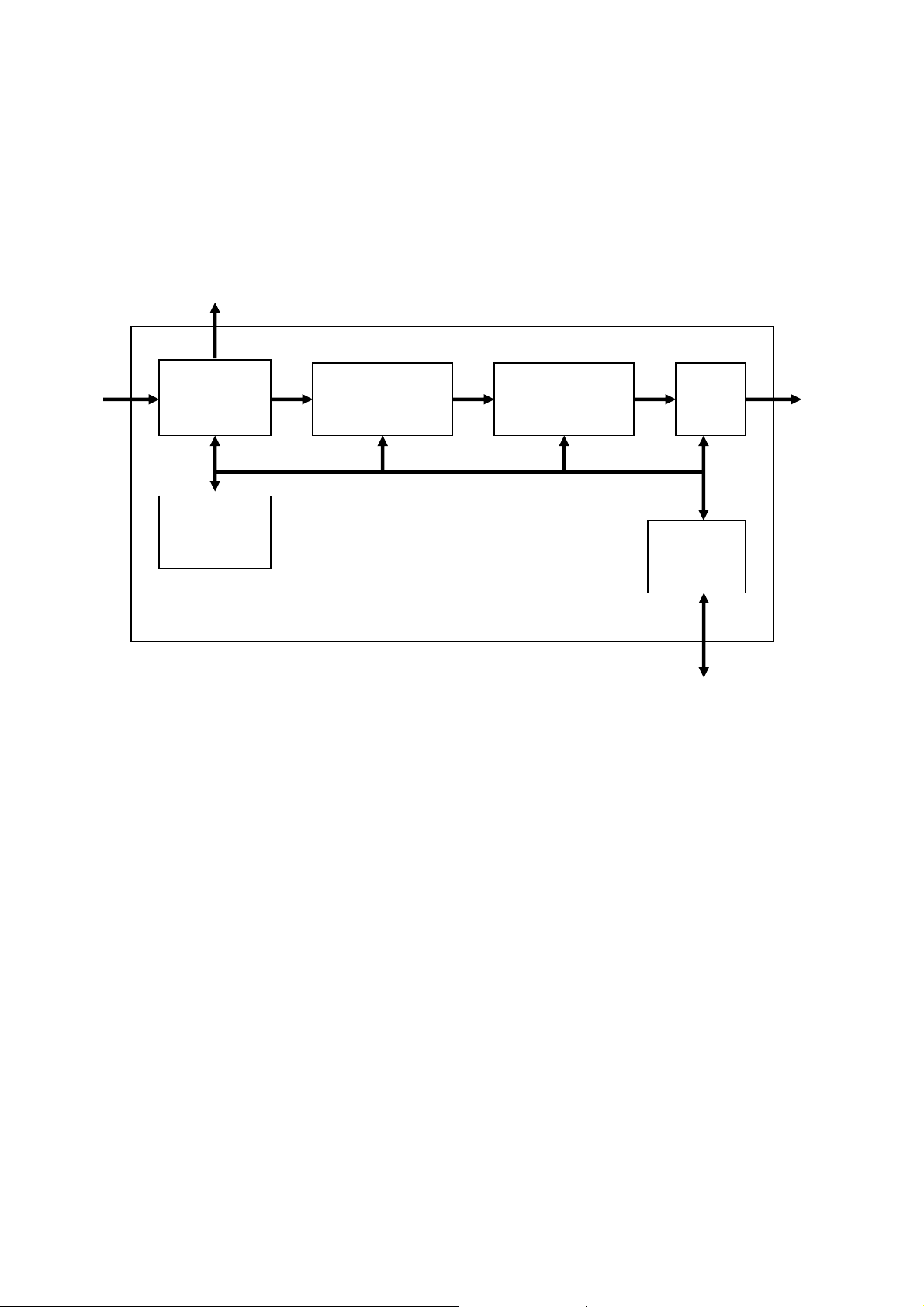

3. Block Diagram

IF

ADC&RF

interface

System

Control

AGC

Time Domain

Processing

Freq. Domain

Processing

FEC

Host

interface

I2C

TSIF

Block Diagram of MT5133

Page 24

MT8295 DATA SHEET

1. Introduction

The MediaTek MT8295 is a companion chip combined with MT533X serial chips to

enable Common Interface (CI) and with the second generation of the Common

Interface (CIV2) functions. It supports DVB compliant Conditional Access Module

(CAM) and PCMCIA type memory cards. A NAND-flash-like bus bridge is built-in to

perform the communication between a host and the card.

Highly Flexible Interface: MT8295 supports one parallel or two serial MPEG2

transport stream interfaces from the front end demodulator and a serial MPEG2

transport stream interface to MPEG2 decoder. Also, the MT8295 is designed with

highly flexible interface timing to compliant with the maximum vendor’s CAMs in the

word.

Extra Value for Your TV: MT8295 enables TV to receive DVB-CI protected program. It

helps content providers to protect their programs and allows customers to receive

more high-value TV programs. Fully tested compliant software is also available for

this device.

2. DTV System Use MT8295

Tuner MT513X MT5335/6/7 Panel

Demod

TS in

CI/PCMCIA

interface

DRAM FLASH

Decoder

TS out

Host

interface

MT8295

Card

TS out

Card

TS in

CAM

Page 25

WT6702F Data Sheet v0.93

1. General Description

The WT6702F is a microcontroller for system power manager with 1)Turbo 8051 compatible (3T) CPU, 2)

8K bytes flash memory, 3) 256 bytes SRAM, 4) 2 PWMs, 5) DPMS detector, 6) 8051 2 timers and UART,

7) Three Slave IIC interface, 8) 4 channel 8-bit A/D converter, 9) Real Time Clock, 10) watch-dog timer,

11) Embedded ISP, 12) Power down mode, 13) Embedded ICE mode.

1.1. Features

Embedded turbo 8051(3T) CPU

• Normal operation mode : 12MHz, 2MHz

• Stand by mode : 32KHz

Memory :

• RAM: 256 Bytes

• Flash memory: 8K Bytes

Turbo 8051 Timer0, Timer1, & UART

Sync processor for monitoring DPMS (VGA connector) wake up signal

8-bit A/D converter with 4 selectable inputs, shared with IO pin

2 PWM pin output

3 slave mode IIC interface

Universal IR Receiver

INT pin to main chip

Watch Dog timer

Low voltage reset

32.768KHz crystal Oscillator & build-in RC Oscillator

Build-in RTC

Maximum 18 programmable IO pins

• 18-IO: 24 pin package

• 14-IO: 20 pin package

• 11/12-IO: 16 pin package

Power consumption :

• Lower than 6mA at 12Mhz mode

• Lower than 4mA at 2Mhz mode

• Lower than 2mA at low speed mode(32KHz)

Operating voltage range : 3.6V – 2.5V

Package:

• SOP16

• SOP20/SSOP20

• SOP24

1.2. Application

• Display system power management MCU with RTC.

• I/O expander with RTC and ADC.

Copyright 2006 Weltrend Semiconductor, Inc. All Rights Reserved.

Weltrend reserves right to modify all information contained in this document without notice.

- 4 -

Page 26

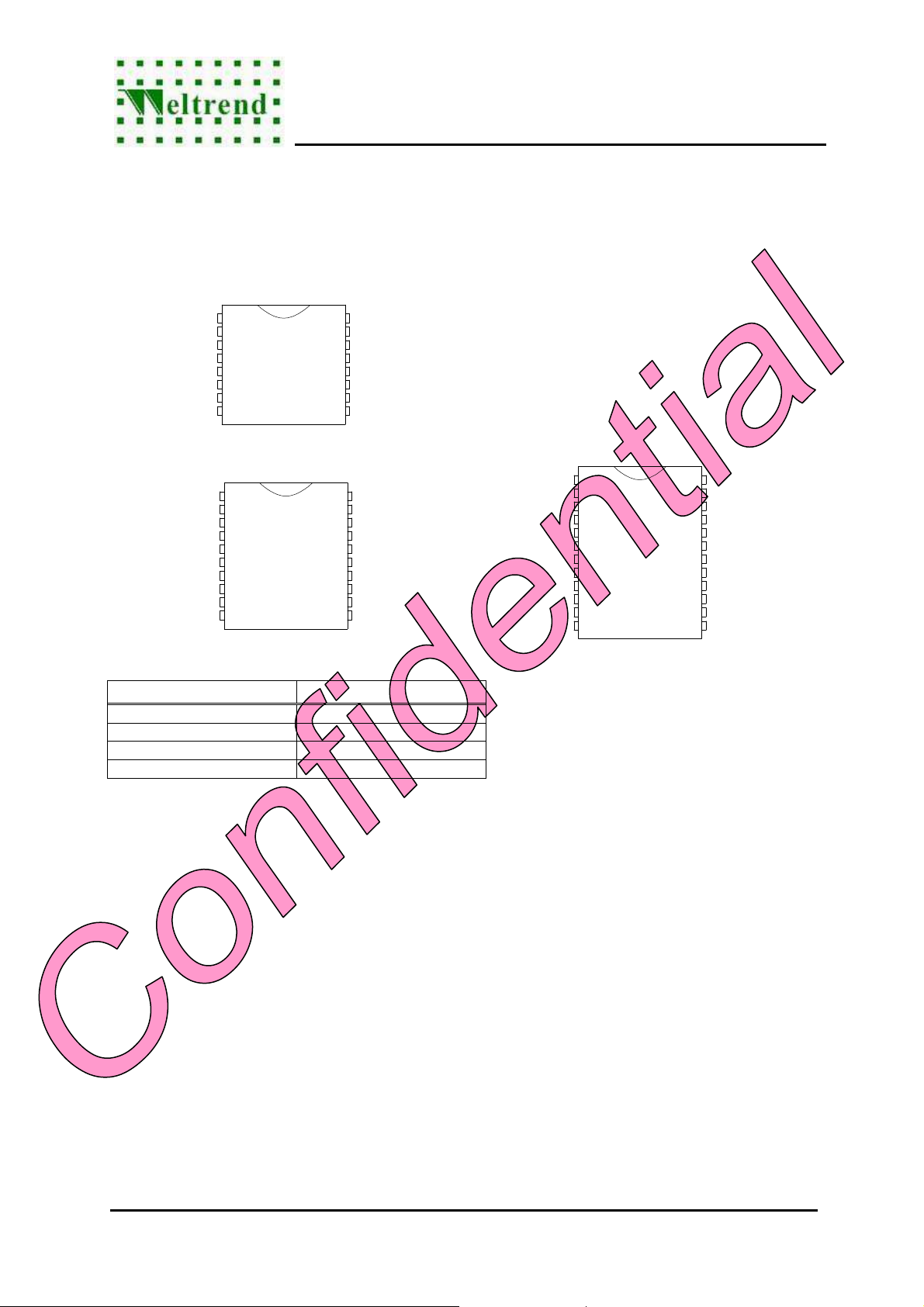

2. Pin Assignment

2.1. Package Type

WT6702F Data Sheet v0.93

32KOSCO

32KOSCI

PWM1/GPIOC1

RXD/IRQ3/GPIOB7

TXD/IRQ2/GPIOB6

HIN/GPIOB5 GPIOB4/VIN

32KOSCO

PWM1/GPIOC1

RXD/IRQ3/GPIOB7

TXD/IRQ2/GPIOB6

HIN/GPIOB5

VIN/GPIOB4

IRQ1/P1.3/GPIOB3

1

2

3

VSS

4

NRST

5

6

7

8 9

1

32KOSCI

2

3

VSS

4

NRST

5

6

7

8

9

10 11

WT6702F_S161

WT6702F_S200

16

VDD

15

GPIOA0/AD0

14

GPIOA3/AD3/IR

13

GPIOA6/SCL1

12

GPIOA7/SDA1

11

GPIOB0/SCL2

10

GPIOB1/SDA2

20

VDD_RTC

19

VDD

18

GPIOA0/AD0

17

GPIOA3/AD3/IR

16

GPIOA4/SCL3/P1.0

15

GPIOA5/SDA3/P1.1

14

GPIOA6/SCL1

13

GPIOA7/SDA1

12

GPIOB0/SCL2

GPIOB1/SDA2

Package Type Package Outline

SOP 16 pin 150mil

SOP 20 pin 300mil

SSOP 20 pin 150mil

SOP 24 pin 300mil

32KOSCO

32KOSCI

VSS

NRST

PWM1/GPIOC1

PWM0/GPIOC0

RXD/IRQ3/GPIOB7

TXD/IRQ2/GPIOB6

HIN/GPIOB5

VIN/GPIOB4

IRQ1/P1.3/GPIOB3

IRQ0/P1.2/GPIOB2

2

3

4

5

6

WT6702F_S240

7

8

9

10

11

12

241

VDD_RTC

23

VDD

22

GPIOA0/AD0

21

GPIOA1/AD1

20

GPIOA2/AD2

19

GPIOA3/AD3/IR

18

GPIOA4/SCL3/P1.0

17

GPIOA5/SDA3/P1.1

16

GPIOA6/SCL1

15

GPIOA7/SDA1

14

GPIOB0/SCL2

13

GPIOB1/SDA2

Copyright 2006 Weltrend Semiconductor, Inc. All Rights Reserved.

Weltrend reserves right to modify all information contained in this document without notice.

- 5 -

Page 27

2.2. Pin Description

WT6702F Data Sheet v0.93

S240 S200 S161

23 19 16

24 20 16 VDD_RTC PWR RTC Power (<3.3V)

1 1 1 32KOSCO O 32kHz oscillator output

2 2 2 32KOSCI I 32kHz oscillator input

3 3 3 VSS GND Ground

4 4 4 NRST I Reset pin, active low (internal pull high)

5 5 5 GPIOC1 I/O PWM1 output. Shared with GPIO C1

6 GPIOC0 I/O PWM0 output. Shared with GPIO C0

7 6 6 GPIOB7 I/O 8051 UART RXD or external IRQ3 interrupt input. Shared with GPIO

8 7 7 GPIOB6 I/O 8051 UART TXD or external IRQ2 interrupt input. Shared with GPIO

9 8 8 GPIOB5 I/O HIN input. Shared with GPIO B5

10 9 9 GPIOB4 I/O VIN input. Shared with GPIO B4

11 10

12

13 11 10 GPIOB1 I/O 2

14 12 11 GPIOB0 I/O 2nd slave IIC SCL2. Shared with GPIO B0

15 13 12 GPIOA7 I/O 1st slave IIC SDA1. Shared with GPIO A7

16 14 13 GPIOA6 I/O 1st slave IIC SCL1. Shared with GPIO A6

17 15

18 16

19 17 14 GPIOA3 I/O Key pad ADC input3 or IR detector input. Shared with GPIO A3

20

21

22 18 15 GPIOA0 I/O Key pad ADC input0. Shared with GPIO A0

GPIOB3 I/O 8051 P1.3 or external IRQ1 interrupt input. Shared with GPIO B3

GPIOB2 I/O 8051 P1.2 or external IRQ0 interrupt input. Shared with GPIO B2

GPIOA5 I/O 3rd slave IIC SDA or 8051 P1.1. Shared with GPIO A5

GPIOA4 I/O 3rd slave IIC SCL or 8051 P1.0. Shared with GPIO A4

GPIOA2 I/O Key pad ADC input2. Shared with GPIO A2

GPIOA1 I/O Key pad ADC input1. Shared with GPIO A1

Pin

Name

VDD PWR Power 3.3V

I/O

B7

B6

nd

slave IIC SDA2. Shared with GPIO B1

Function Description

(a) All GPIOs have Schmitt trigger input.

(b) When use Slave IIC or 8051 P1.x (or UART), the external circuit need pull high(4.7kΩ)

(c) GPIOA3, GPIOA2, GPIOA1, GPIOA0 MAX input are +3.6v(=3.3v+0.3v)

and the other GPIOs MAX input is +5v (5v tolerant PAD)

Copyright 2006 Weltrend Semiconductor, Inc. All Rights Reserved.

Weltrend reserves right to modify all information contained in this document without notice.

- 6 -

Page 28

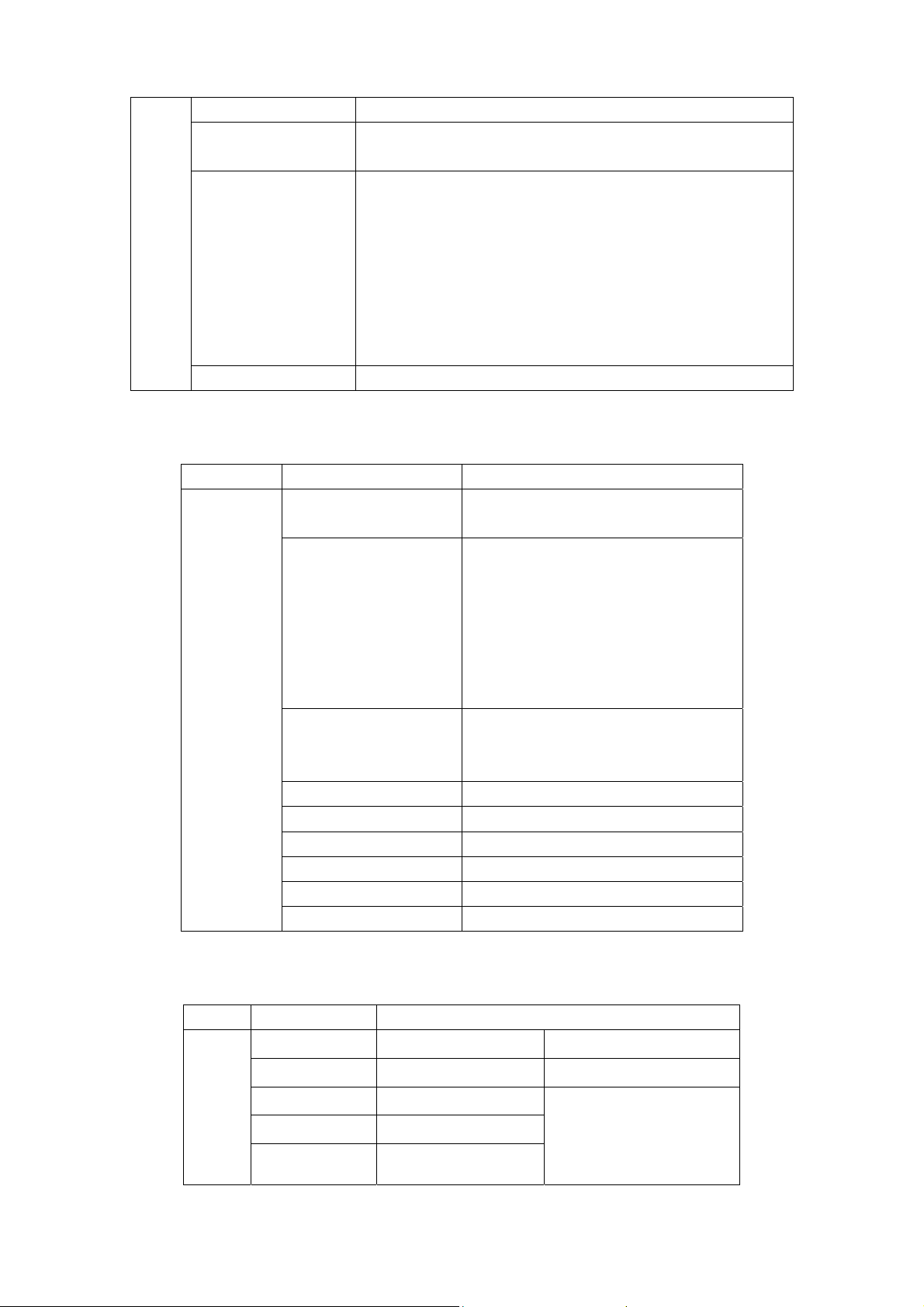

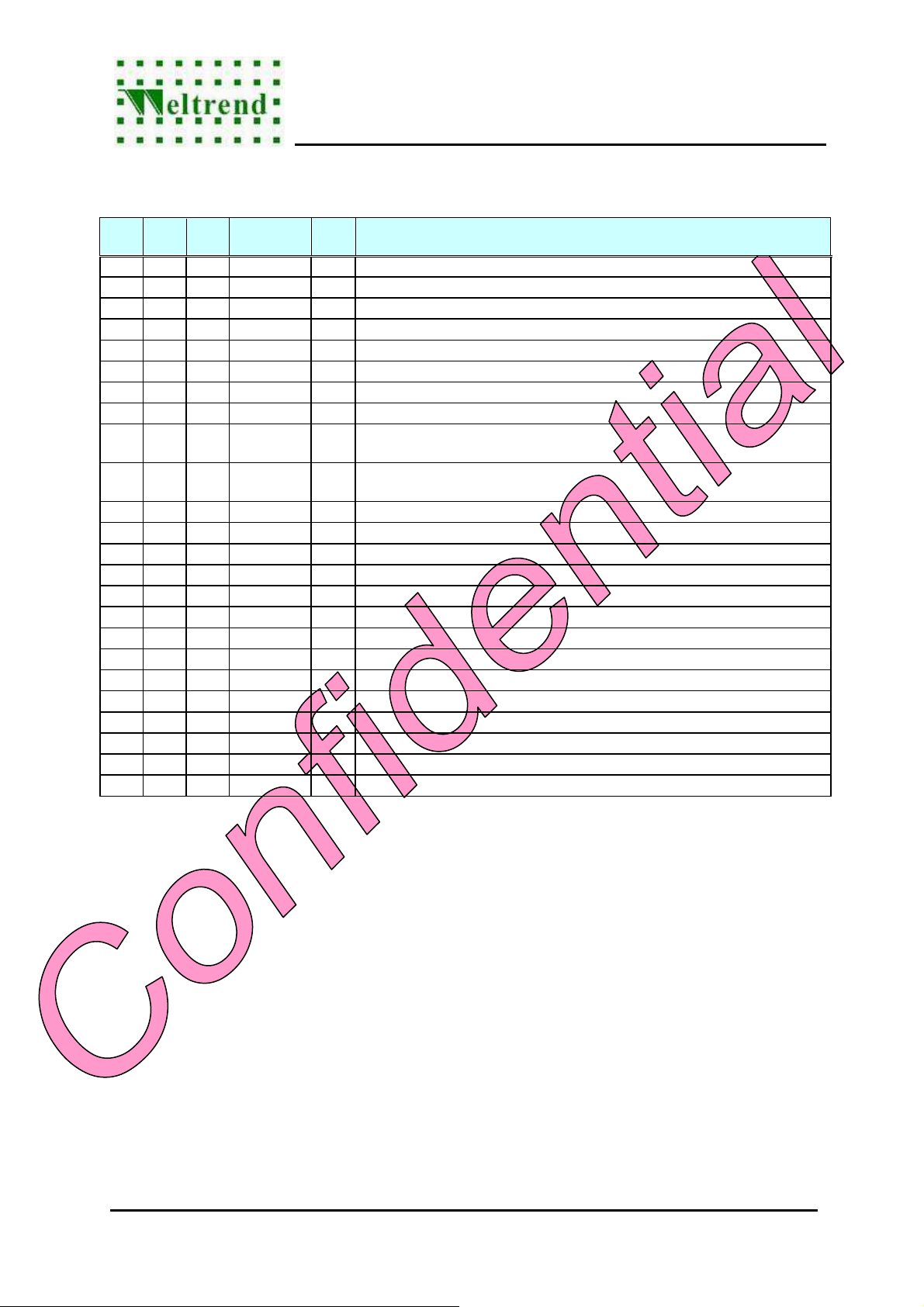

3. Selection Guide

Part NO. WT6702F_S240 WT6702F_S200 WT6702F_S161

DPMS Detection V V V

UART V V V

8K Flash Memory V V V

RAM 256 Byte V V V

PWM Output 2 1 1

Slave I2C 3 3 2

RTC V V V

IO 18max 14max 11 max

Oscillator

8-bit ADC 4 selectable inputs 2 selectable inputs 2 selectable inputs

Package 24-pin SOP 20-pin SOP/SSOP 16-pin SOP

32KHz Crystal/

RC OSC

WT6702F Data Sheet v0.93

32KHz Crystal/

RC OSC

32KHz Crystal/

RC OSC

Copyright 2006 Weltrend Semiconductor, Inc. All Rights Reserved.

Weltrend reserves right to modify all information contained in this document without notice.

- 7 -

Page 29

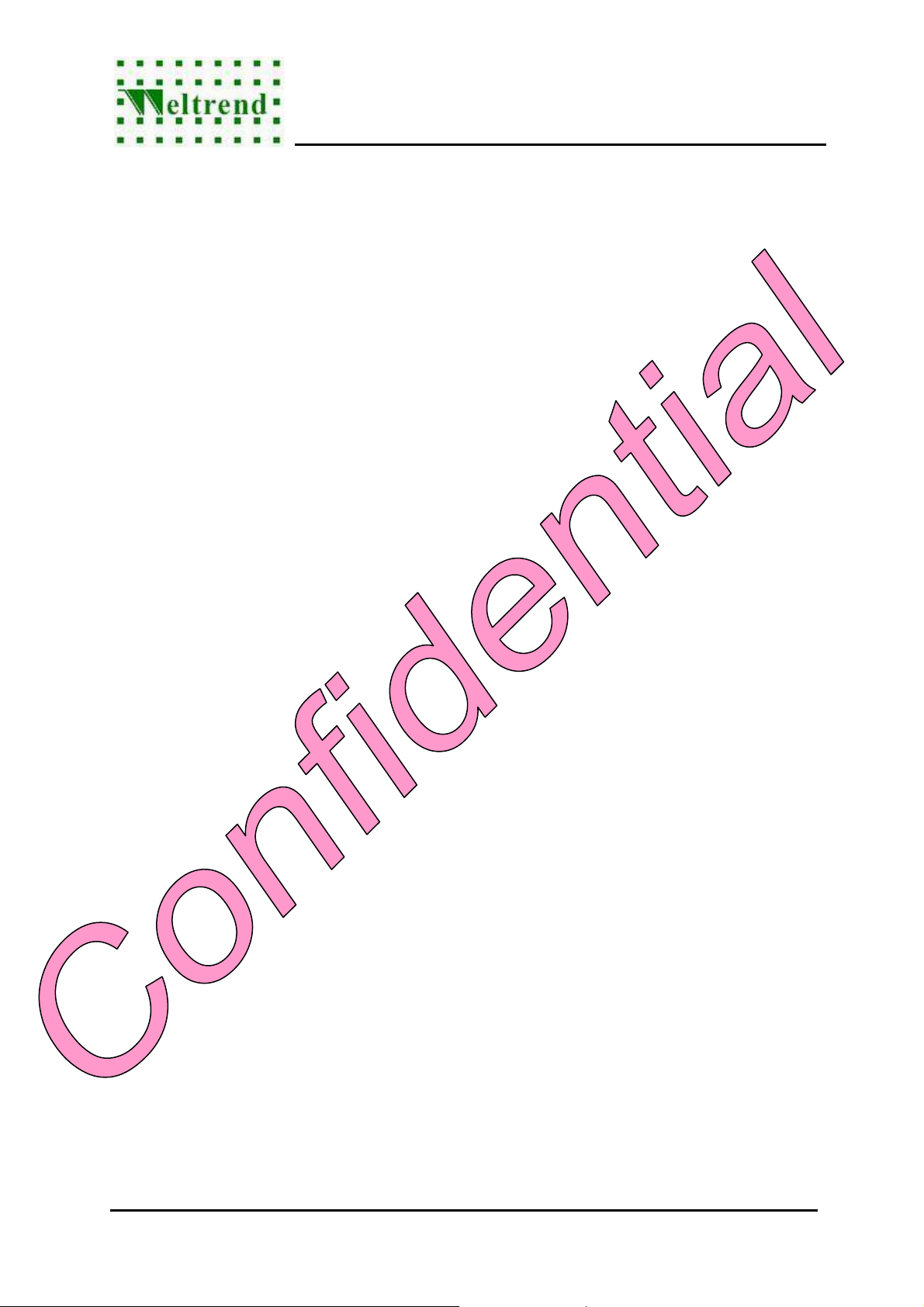

4. Functional Block Diagram

Turbo 8031 MCU

WT6702F Data Sheet v0.93

8K bytes code

flash

Internal 256

bytes SRAM

32K Oscillator

RTC

RC

Oscillator

Key Pad ADC

Reset

Processor

Clock

Processor

8051

UART,Timer0,

Timer1

1st SIIC

2nd SIIC

internal bus

3rd SIIC

HV DPMS

Detector

Interrupt

Processor

IR Detector

PWM

Clock off &

Wake Up

4 IRQ

Watchdog

Processor

timer

GPIO

Processor

Copyright 2006 Weltrend Semiconductor, Inc. All Rights Reserved.

Weltrend reserves right to modify all information contained in this document without notice.

- 8 -

Page 30

w

24-bit 192kHz Stereo DAC with 1.7Vrms Line Driver

DESCRIPTION

The WM8501 is a high performance stereo DAC with an

integrated 1.7Vrms line driver. It is designed for audio

applications that require a high voltage output along with

enhanced load drive capability.

The WM8501 supports data input word lengths from 16 to

24-bits and sampling rates up to 192kHz. The WM8501

consists of a serial interface port, digital interpolation filters,

multi-bit sigma delta modulators and stereo DAC in a 14lead SOIC package.

The hardware control interface is used for the selection of

audio data interface format, enable and de-emphasis. The

WM8501 supports I

Operating on separate analog and digital supplies the

WM8501 offers very lower power consumption from the

digital section, whilst supporting enhanced load drive from

the analogue output.

2

S, right Justified or DSP interfaces.

WM8501

FEATURES

• Stereo DAC with 1.7Vrms line driver from 5V analogue

supply

• Audio performance

- 100dB SNR (‘A’ weighted @ 48kHz)

- -88dB THD

• DAC Sampling Frequency: 8kHz – 192kHz

• Pin Selectable Audio Data Interface Format

• 14-lead SOIC package

• 4.5V - 5.5V analogue, 2.7V - 5.5V digital supply operation

APPLICATIONS

• STB

• DVD

• Digital TV

2

- I

S, 16-bit Right Justified or DSP

BLOCK DIAGRAM

WOLFSON MICROELECTRONICS plc

To receive regular email updates, sign up at http://www.wolfsonmicro.com/enews/

Pre-Production, May 2006, Rev 3.1

Copyright 2006 Wolfson Microelectronics plc

Page 31

Pre-Production WM8501

PIN CONFIGURATION

ORDERING INFORMATION

DEVICE

WM8501GED/V -25 to +85oC

WM8501GED/RV -25 to +85oC

Note:

Reel quantity = 3,000

TEMPERATURE

RANGE

PACKAGE

14-lead SOIC

(Pb-free)

14-lead SOIC

(Pb-free, tape and reel)

MOISTURE SENSITIVITY

LEVEL

MSL3

MSL3

PEAK SOLDERING

TEMPERATURE

260°C

260°C

w

PP Rev 3.1 May 2006

3

Page 32

WM8501 Pre-Production

PIN DESCRIPTION

PIN NAME TYPE DESCRIPTION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Note:

1. Digital input pins have Schmitt trigger input buffers.

LRCLK Digital input Sample rate clock input

DIN Digital input Serial audio data input

BCLK Digital input Bit clock input

ENABLE Digital input Enable input – 0 = powered down, 1 = enabled

VMID Analogue output Analogue internal reference

ROUT Analogue output Right channel DAC output

AGND Supply Ground reference for analog circuits and substrate connection

AVDD Supply Positive supply for analog circuits

LOUT Analogue output Left channel DAC output

DGND Digital Supply Digital ground supply

DVDD Digital Supply Digital positive supply

DEEMPH Digital input De-emphasis select, Internal pull down

High = de-emphasis ON

Low = de-emphasis OFF

FORMAT Digital input Data input format select, Internal pull up

Low = 16-bit right justified or DSP (Mode B)

High = 16-24-bit I

MCLK Digital input Master clock input

2

S or DSP (Mode A)

w

PP Rev 3.1 May 2006

4

Page 33

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

.

General Description

The SiI9185A is the first generation of TMDS switch device supporting Revision 1.3 of the HDMI Specification (HDMI

Consortium; June 2006). With three HDMI inputs and a single output, the SiI9185A provides a low-cost method of

adding additional HDMI ports to the latest Digital TVs. New DTVs can easily connect to the many HDMI sources

coming on the market, including DVDs, STB, game consoles, PCs, camcorders, and digital still cameras. The SiI9185A

is a fully HDMI compliant device providing a simple, low-cost method of retransmitting protected digital audio and

video, giving end-users a truly all-digital experience. Built-in backward compatibility with DVI 1.0 allows HDMI

systems to connect to any DVI 1.0 source.

The SiI9185A provides additional integrated features to help lower system cost and provide enhanced features to the end

consumer. To lower system cost, the SiI9185A provides a complete solution for switching sink-side HDMI signals. This

includes DDC switching, individual HPD control, and 5V sense. The addition of these features eliminates additional

external components, helping to lower cost. For source-side applications, the SiI9185A DDC switching can be bypassed

with an external 4-channel I

The SiI9185A is the first generation of device from Silicon Image to integrate the Extended Display Identification Data

(EDID). The EDID is stored in on-board RAM that is downloaded from the system microcontroller during power up or

initialization. The EDID is reflected on each of the three HDMI ports through the DDC bus. Flexibility is built in to

allow mixing different EDID formats in an application. This allows elimination of up to three EDID ROMs while also

saving board space.

Finally, the SiI9185A provides a complete, simple solution to enabling Consumer Electronics Control (CEC) in a DTV.

CEC is a single-wire bus that transmits remote control commands throughout a home network. The SiI9185A integrates

both an HDMI-compliant I/O and Silicon Image’s CEC API. The CEC I/O meets all HDMI compliance tests and

eliminates the need for additional external components, again saving board space. The CEC API manages reception and

transmission of all CEC signals according to the CEC protocol and makes the information available to the system

microcontroller. This significantly lowers the system-level control by the system microcontroller, simplifying firmware

overhead.

A very low power standby mode is available, allowing DTVs to meet industry low-power requirements such as Energy

Star. During this mode both the CEC and EDID are still functional.

Silicon Image’s SiI9185A uses the latest generation of TMDS core technology. These TMDS cores are guaranteed to

pass all HDMI compliance tests.

2

C-bus switch (e.g., Texas Instruments PCA95445) to allow clock stretching.

SiI-DS-1016-0.80

© 2007 Silicon Image, Inc. CONFIDENTIAL 1

Page 34

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

Features

• Three-input, single-output HDMI switch

• Integrated TMDS® receiver and transmitter cores capable of receiving and transmitting 2.25 Gbps:

• Supports video resolutions up to 1080p, 60 Hz, 12-bit or 720p/1080i, 120 Hz, 12-bit

• Built-in adaptive equalizer provides long cable support even at deep-color resolutions

• Pre-emphasis in transmitter

• DVI 1.0, HDCP 1.1 and HDMI 1.3 compliant receiver and transmitter

• Uses HDMI-compliant TMDS core for recovery and retransmission, unlike TMDS switches, which use

high-speed analog switches and degrade TMDS signals

• Built-in Consumer Electronics Control (CEC) support:

• HDMI-compliant CEC I/O simplifies and lowers cost for adding CEC support to DTV

• Integrated CEC API lowers overhead requirements on system microcontroller, speeds design

• Integrated EDID capability to lower system cost

• DDC switching on each input port simplifies board layout and lowers cost

• Individual control of Hot Plug Detect (HPD) for each port

• 5V detect to help speed soft mute of audio during plug-in, plug-out conditions

2

• Control via local I

• Stand-alone mode option:

• Acts as simple switcher

2

• No I

• Low-power standby mode to meet Energy Star and other power saving requirements

• 80-pin QFP package

C control required in this mode

C bus

Silicon Image, Inc.

2 © 2007 Silicon Image, Inc. CONFIDENTIAL SiI-DS-1016-0.80

Page 35

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

Silicon Image, Inc.

SiI9185A Pin Mapping

I2CSEL/

HPD1

AVCC18

R1XC-

R1XC+

AGND

35

36

37

38

39

40

R1X0–

R1X0+

AVCC33

R1X1–

R1X1+

AGND

R1X2–

R1X2+

AVCC18

DSDA1

DSCL1

RPWR1

CEC_D

CEC_A

AVCC33

HPD2

AVCC18

R2XC-

R2XC+

AGND

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

INT

DGND

34

67

DVCC18

33

68

AVCC18

DSDA0

DSCL0

RPWR0

29

30

31

32

80-Pin TQFP

(Top View)

69

70

71

72

R0X2+

28

73

R0X2–

27

74

AGND

26

75

R0X1+

25

76

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

R0X0–

R0X0+

AVCC33

R0X1–

21

22

23

24

77

78

20

AGND

19

R0XC+

18

R0XC-

17

AVCC18

HPD0

16

LSCL/

15

EPSEL[1]

LSDA/

14

EPSEL[0]

RESET#

13

EXTSWING

12

TxC–

11

10

TxC+

9

AGND

8

Tx0–

7

Tx0+

6

AVCC18

5

Tx1–

4

Tx1+

3

AGND

2

Tx2–

1

Tx2+

79

80

R2X0–

R2X0+

R2X1–

AVCC33

R2X1+

AGND

R2X2–

R2X2+

Figure 1. Pin Mapping

SiI-DS-1016-0.80 © 2007 Silicon Image, Inc. CONFIDENTIAL 3

DSDA2

AVCC18

DSCL2

RPWR2

DVCC18

DGND

TSCL

TSDA

HPDIN

RSVDL

TPWR/

I2CADDR

AGND

Page 36

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

Silicon Image, Inc.

Functional Description

The SiI9185A provides a low-cost method of providing additional HDMI inputs to a DTV. System cost is reduced by

integrating DDC and HPD switching along with integrated EDID. Feature enhancements like the embedded CEC API

provide a simple method of adding CEC to a DTV without burdening the system microcontroller.

Figure 2 and Figure 3 show the functional blocks of the device as applied to sink and source applications, respectively.

Pin descriptions begin on page 20.

Figure 2. System Architecture, Sink Application

4 © 2007 Silicon Image, Inc. CONFIDENTIAL SiI-DS-1016-0.80

Page 37

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

Silicon Image, Inc.

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

Figure 3. System Architecture, Source Application

SiI-DS-1016-0.80 © 2007 Silicon Image, Inc. CONFIDENTIAL 5

Page 38

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

Silicon Image, Inc.

Block Level Functionality

The SiI9185A 3:1 HDMI 1.3 switch is used to select a single set of HDMI/DVI signals from one of three HDMI/DVI

receiver-ports, and to generate a fully compliant HDMI/DVI stream as an output. It also provides DDC/HDCP, HPD,

and +5V switching to allow full compliance to the HDMI/DVI specifications.

The combination of dynamic equalizer and state-of-the-art DPLL can overcome signal distortion due to the long lengths

of HDMI/DVI cables. SiI9185A-based switches can be cascaded many times to regenerate TMDS and HDCP signals.

Figure 4. Functional Block Diagram

As shown in Figure 4, the SiI9185A consists of five major blocks:

• Receiver block

• Transmitter block

• CEC Interface block

• EDID RAM block

• Configuration block

Receiver Block

The three HDMI/ DVI receive ports are defined as Port 0, Port 1, and Port 2. Each of the ports is terminated separately

and equalized under the control of the receiver digital block and controlled by the local I

power down of all ports are selected by using the Port Select (PSEL[1:0]) signals. PSEL[1:0] can either be controlled by

a register in I

2

The I

HDCP specifications, the SiI9185A also switches and relays information with correct timing from three bidirectional I

Rx-ports to one bidirectional Tx-port. The HDCP switching and relaying operation is also done in the Receive block by

monitoring the I

provide correct HDCP data flow between the selected Receiver and the Transmitter port.

2

C mode, or pins in stand-alone mode.

C Switch conveys bidirectional DDC/EDID and HDCP information. In order to comply with the HDMI/DVI and

2

C/HDCP protocol to decide the right direction of signal transfer. The port selection signal is used to

6 © 2007 Silicon Image, Inc. CONFIDENTIAL SiI-DS-1016-0.80

2

C bus. Port 0, Port 1, Port 2, or

2

C

Page 39

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

Silicon Image, Inc.

Transmitter Block

The Transmit block consists of a fully compliant, HDMI 1.3 transmitter. This transmitter re-transmits the data received

by the selected receiver port.

CEC Interface

The Consumer Electronics Control (CEC) Interface block provides CEC electrically compliant signals between CEC

devices and a CEC master. It allows products to meet the electrical specifications of CEC signaling by translating the

LVTTL signals of an external microcontroller (CEC host-side or Tx-side) to CEC signaling levels for CEC devices at the

Rx-side, and vice versa.

Additionally, a CEC controller compatible with the Silicon Image CEC API is included on-chip. This CEC controller has

a high-level register interface accessible through the I

commands. This controller makes CEC control very easy and straightforward, and removes the burden of having a host

CPU perform these low-level transactions on the CEC bus.

In order to use the high-level CEC API, the host must perform a calibration of the internal CEC clock inside the

SiI9185A. This calibration is performed by setting the calibration bit, and then sending a 10ms pulse (±1%) on the

CEC_D signal input to the SiI9185A. The SiI9185A uses this pulse to calibrate an internal clock that is then used to

generate all CEC timing to guarantee CEC compliance to the HDMI specification. This calibration must be repeated at

time intervals corresponding to changes in temperature of 15°C.

EDID RAM Block

The EDID RAM block consists of 256 bytes of RAM that is shared by all ports. This means the timing information must

be identical among all the ports if the internal EDID is used. Independent registers for the CEC physical address and

checksum values for each port are also included, as these are unique to each port. On-board logic controls arbitration

when reading the 256 bytes of EDID RAM, CEC physical address, and checksum values. This allows simultaneous reads

of all ports from three different source devices if they are connected and attempt an EDID read at the same time.

The internal EDID can be selected on a per-port basis using registers on the local I

can use the internal EDID, and Port 2 can use a discrete EEPROM for the EDID.

2

C interface which can be used to send and receive CEC

2

C bus. For example: Port 0 and Port 1

Configuration Block

The Configuration block is used to configure and control the operation of the SiI9185A. The SiI9185A has two modes of

operation: I

All of these registers are accessible over the local I

control, CEC control, EDID loading, and power-down control.

In Standalone mode, all functions are controlled and observed by using pins on the SiI9185A. The mode is determined

by the level of the I2CSEL/INT pin at the rising edge of RESET#. A high indicates I

Standalone mode. In Standalone mode, the SiI9185A operates independently, and has no need for an external

microprocessor.

2

C and Standalone. In I2C mode, all functions of the SiI9185A are controlled and observed with I2C registers.

2

C Interface. These registers are used to perform port select, HPD

Figure 5. Standalone Mode Configuration

2

C mode, and a low indicates

SiI-DS-1016-0.80 © 2007 Silicon Image, Inc. CONFIDENTIAL 7

Page 40

Silicon Image

Confidential for Philips

Consumer Electronics

Internal Use Only

SiI9185A 3:1 HDMI 1.3 Switch

Preliminary Data Sheet

Silicon Image, Inc.