Page 1

48-V to 3.3-V Forward Converter with

Active Clamp Reset Using the

UCC2891 Active Clamp Current Mode

PWM Controller

User's Guide

December 2006 Power Supply MAN

SLUU178A

Page 2

48-V to 3.3-V Forward Converter with Active

Clamp Reset Using the UCC2891 Active

Clamp Current Mode PWM Controller

User's Guide

Literature Number: SLUU178A

November 2003 – Revised December 2006

Page 3

User's Guide

SLUU178A – November 2003 – Revised December 2006

Using the UCC2891 Active Clamp Current Mode PWM

Controller

1 Introduction

The UCC2891EVM evaluation module (EVM) is a forward converter providing a 3.3-V regulated output at

30 A of load current, operating from a 48-V input. The EVM operates over the full 36 V to 72 V telecom

input range, and is able to fully regulate down to zero load current. The module uses the UCC2891 current

mode active clamp PWM controller for effectively demonstrating the active clamp transformer reset

technique.

Benefits of the active clamp include a control driven transformer reset scheme allowing zero voltage

switching (ZVS) to increase overall efficiency, lower drain-to-source voltage stress, extended duty cycle

beyond 50% and reduced electromagnetic radiated emissions. Combined with synchronous rectification,

this EVM is configured to operate at 300 kHz and exhibits a peak efficiency of just over 92%, with a full

load efficiency of 89%. The EVM displays many features that might be typical of a more complex design,

yet its compact board layout and low component count make it elegantly simple.

2 Description

The UCC2891 controller family provides advanced active clamp control features such as programmable

maximum duty cycle clamp, programmable dead time between the two primary switches and the ability to

drive either a P-channel, or N-channel MOSFET in either a high-side or low-side active clamp

configuration. The UCC2891 also allows the ability to start-up directly from the 48-V telecom bus voltage,

eliminating the need for external start-up circuitry. It includes programmable soft start, internal slope

compensation for peak current mode control, internal low-line voltage sensing, internal syncronizable clock

input, cycle-by-cycle current limiting, and a robust 2-A sink/source TrueDrive™ internal gate drive circuit.

The result is a highly efficient design loaded with features, requiring very few external components.

The TrueDrive™ hybrid output architecture used in the UCC2891 uses TI's unique TrueDrive™

Bipolar/CMOS output. To the user, this simply means ultra-fast rise and fall times by providing the highest

possible drive current where it is needed most, at the MOSFET Miller plateau region.

The UCC2891/2/3/4 is available in either a 16-pin SOIC or 16-pin TSSOP package for applications where

absolute minimal board space is required.

The UCC2891EVM highlights the many benefits of using the UCC2891 active clamp current mode PWM

controller. This user's guide provides the schematic, component list, assembly drawing, artwork and test

set up necessary to evaluate the UCC2891 in a typical telecom application. More detailed design

information can be found listed in the References section.

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 3

Submit Documentation Feedback

Page 4

www.ti.com

Description

2.1 Applications

The UCC2891 is suited for use in isolated telecom 48-V input systems requiring high-efficiency and

high-power density for very low-output voltage, high-current converter applications, including:

• Server Systems

• Datacom

• Telecom

• DSP's, ASIC's, FPGA's

2.2 Features

The UCC2891EVM features include:

• ZVS transformer reset using active clamp technique in forward converter

• All surface mount components, double sided half brick (2.2 × 2.28 × 0.5) inches

• Complementary auxilliary drive for active clamp with programmable dead time for ZVS

• Current mode control with synchronization function

• Internal PWM slope compensation

• Start-up directly from telecom input voltage

• Synchronous rectifier output stage allows high-efficiency operation

• Programmable soft-start

• Up to 30-A dc output current

• Regulation to zero load current

• Non-latching, output overcurrent and short circuit protection

• Non-latching, Input undervoltage protection

• 1500-V isolation primary to secondary

Using the UCC2891 Active Clamp Current Mode PWM Controller4 SLUU178A – November 2003 – Revised December 2006

Submit Documentation Feedback

Page 5

www.ti.com

3 UCC2891EVM Electrical Performance Specifications

The UCC2891EVM electrical performance specifications are listed in Table 1 .

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Input Characteristics

Input voltage range 36 48 72 V

No load intput current VIN= 36 V, I

Maximum input current VIN= 36 V, I

Input voltage ripple VIN= 72 V, I

Input voltage ripple

Output voltage 36 V ≤ VIN≤ 72 V, 0 A ≤ I

Output voltage regulation Line regulation (36 V ≤ VIN≤ 72 V, I

Output voltage ripple VIN= 48 V, I

Output load current VIN= 48 V, I

Output current limit 36 V ≤ VIN≤ 72 V 32

Output current limit

Switching frequency 275 325

Control loop bandwidth 36 V ≤ VIN≤ 72 V, I

Control loop bandwidth 36 V ≤ VIN≤ 72 V, 2 A ≤ I

Peak efficiency 92%

Full load efficiency VIN= 48 V, I

Table 1. UCC2891EVM Performance Summary

= 0 A 75 100 mA

OUT

= 30 A 3.00 3.25 A

OUT

= 30 A 1.50 1.75 V

OUT

≤ 30 A 3.25 3.30 3.35 V

OUT

Load regulation (0 A ≤ I

= 30 A 30 35 mV

OUT

= 30 A 0 30

OUT

= 30 A 89%

OUT

≤ 30 A, VIN= 48 V) 0.060%

OUT

= 10 A 5 8

OUT

≤ 30 A 30 50 ° C

OUT

UCC2891EVM Electrical Performance Specifications

= 0 A) 0.003%

OUT

P-P

P-P

A

kHz

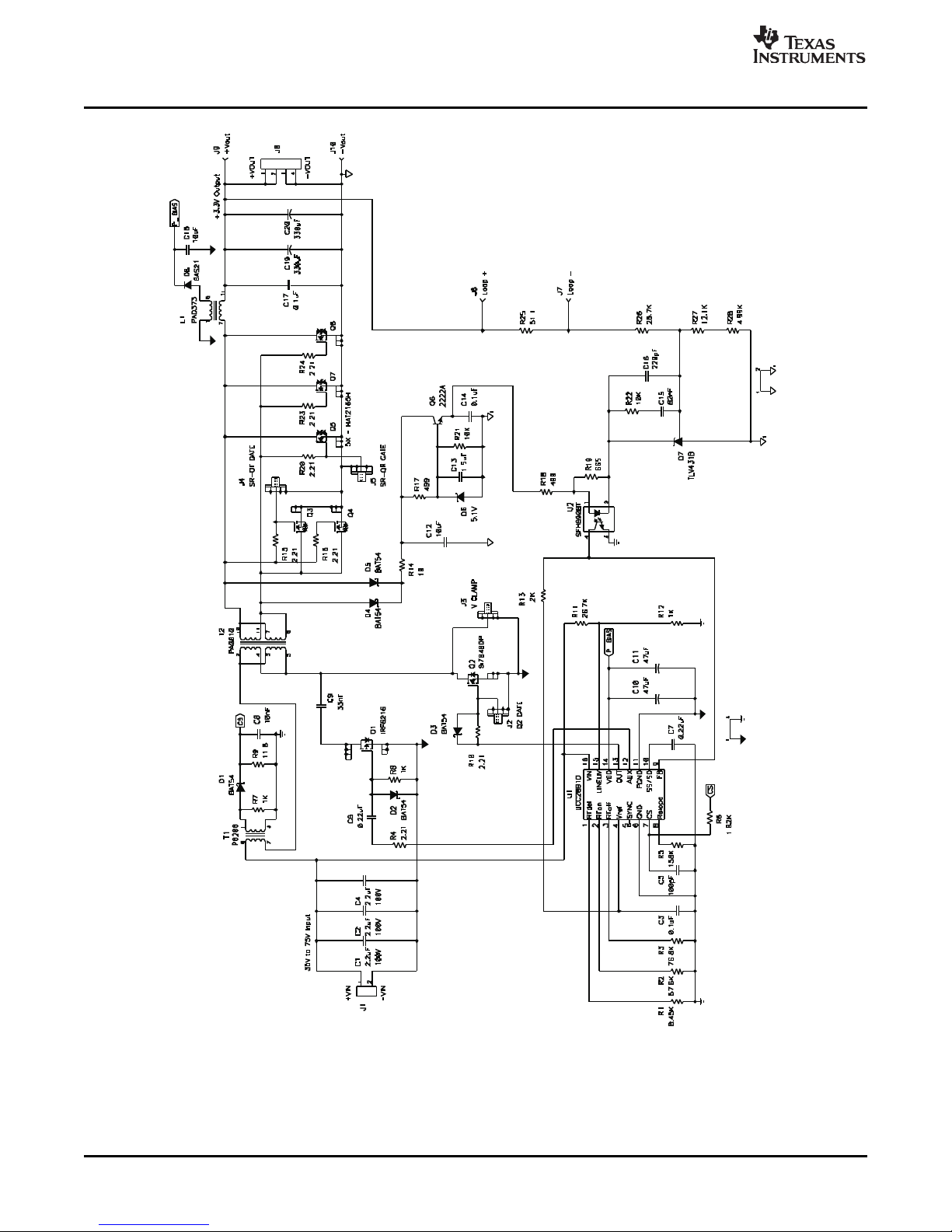

4 Schematic

A schematic of the UCC2891EVM is shown in Figure 1 . Terminal block J1 is the 48-V input voltage source

connector and J8 is the output and return for the 3.3-V output voltage.

On the primary side, U1 is the UCC2891 shown with the necessary discrete circuitry for configuring the

controller to operate at 300 kHz with the maximum duty clamp set for 0.65. The EVM is programmed to

start at VIN=36 V, as determined by R11 and R12. To minimize power dissipation in the current sense, a

current sense transformer, T1 is used, as opposed to simply using a sense resistor between the source of

Q2 and power ground. Q2 is the primary switching MOSFET and is selected based upon VDS and low

RDS(on). Q1 is the AUX (active reset) MOSFET and is selected based upon preferred package only, with

only minor consideration given for R

referenced, Q1 must be a P-channel type MOSFET. The reason for this is further explained in application

note SLUA299[2]. C9 is the clamp capacitor used to maintain a constant dc voltage. The input voltage is

subtracted from the clamp voltage to allow transformer reset during the active clamp period.

and Qg. Since the active clamp used in this design is low-side

DS(on)

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 5

Submit Documentation Feedback

Page 6

www.ti.com

+

+

+

+

Schematic

6 Using the UCC2891 Active Clamp Current Mode PWM Controller SLUU178A – November 2003 – Revised December 2006

Figure 1. UCC2891EVM Schematic

Submit Documentation Feedback

Page 7

www.ti.com

V2

-

+

J1

+Vout -V out

J9

J10

Loop+

Loop-

J6

J7

Texas Instruments

HPA034

UCC2891 Active Clamp Converter

J3

V-Clamp

J2

Q2 Gate

J4

SR-QF Gate

J5

SR-QR Gate

LOAD1

3.3V/30A

-

+

A1

VIN

-

+

V1

FAN

+

+

--

-+

+VIN

-VIN

DANGER HIGH VOLTAGE

+VOUT

-VOUT

J8

High efficiency is achieved using self-driven synchronous rectification on the secondary side. Q3 and Q4

are placed in parallel and make up the forward synchronous rectifier (SR), while the reverse SR is made

up of the parallel combination of Q5, Q7 and Q8. If the duty cycle were limited to 50% then the reverse SR

could be reduced to only two parallel MOSFETs, but since these devices are operating near 60% duty

cycle during the freewheel mode, they carry a higher average current than seen by Q3 and Q4. The

output inductor L1 has a coupled secondary, referenced to the primary side, used to provide bootstrapping

voltage to U1. A stable bias for the optocoupler, U2 is provided by the series pass regulator made up of

D6, Q6 and some associated filtering.

Scope jacks J2 and J3 allow the user to measure the gate-to-source and drain-to-source signals for Q2,

the primary MOSFET. J4 and J5 allow convenient access to the gate drive signals of each SR on the

secondary side. J6 and J7 are available allowing the option of using a network analyzer to non-invasively

measure the control to output loop gain and phase.

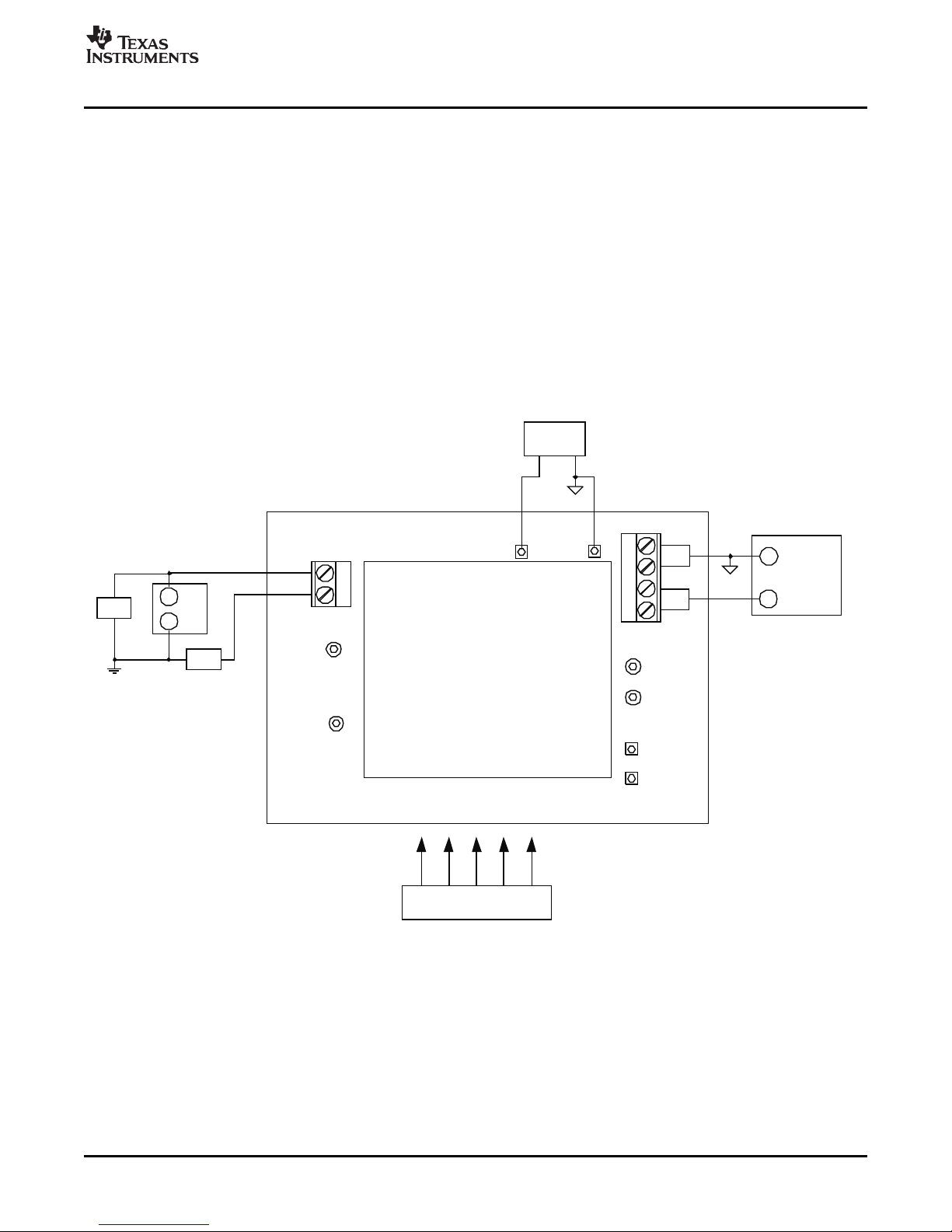

5 EVM Test Setup

Figure 2 shows the basic test set up recommended to evaluate the UCC2891EVM.

EVM Test Setup

Figure 2. Recommended EVM Test Configuration

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 7

Submit Documentation Feedback

Page 8

www.ti.com

EVM Test Setup

5.1 Output Load (LOAD1)

For the output load to VOUT, a programmable electronic load set to constant current mode and capable of

sinking between 0A

voltage measurements directly at J9 and J10 pins. Unless the load has remote sense capability,

measuring VOUT at LOAD1 results in some voltage measurement error, especially at higher load current,

due to finite voltage drops across the wires between J8 and the electronic load.

5.2 DC Input Source (VIN)

The input voltage is a variable DC source capable of supplying between 0 V

3.5 A

, and connected to J1 and A1 as shown in Figure 2 . For fault protection to the EVM, good common

DC

practice is to limit the source current to no more than 4 A

also be inserted between VIN and J1 as shown in Figure 2 .

5.3 Network Analyzer

A network analyzer can be connected directly to J6 and J7. The UCC2891EVM provides a 51.1- Ω resistor

(R25) between the output and the voltage feedback to allow easy non-invasive measurement of the

control to output loop response.

5.4 Recommended Wire Guage

The connection between the source voltage, VIN and J1 of the EVM can carry as much as 3.25A

minimum recommended wire size is AWG #20 with the total length of wire less than 8 feet (4 feet input, 4

feet return). The connection between J8 of the EVM and LOAD1 can carry as much as 30A

minimum recommended wire size is AWG #16, with the total length of wire less than 8 feet (4 feet output,

4 feet return).

and 30A

DC

, is used. Using a dc voltmeter, V2, it is also advised to make all output

DC

and 72 V

DC

for a 36 V input. A dc ammeter, A1 should

DC

DC

at no less than

. The

DC

. The

DC

5.5 Fan

Most power converters include components that can be hot to the touch when approaching temperatures

of 605C. Because this EVM is not enclosed to allow probing of circuit nodes, a small fan capable of

200-400 LFM is recommended to reduce component temperatures when operating at or above 50%

maximum rated load current.

Using the UCC2891 Active Clamp Current Mode PWM Controller8 SLUU178A – November 2003 – Revised December 2006

Submit Documentation Feedback

Page 9

www.ti.com

6 Power Up/Down Test Procedures

The following test procedure is recommended primarily for power up and shutting down the EVM.

Whenever the EVM is running above an output load of 15 A

walk away from a powered EVM for extended periods of time.

1. Working at an ESD workstation, make sure that any wrist straps, bootstraps or mats are connected

referencing the user to earth ground before power is applied to the EVM. Electrostatic smock and

safety glasses should also be worn.

2. Prior to connecting the DC input source, VIN, it is advisable to limit the source current from VIN to

3.5-A maximum. Make sure VIN is initially set to 0 V and connected to J1 as shown in Figure 2 .

3. Connect the ammeter A1 (0A to10A range) between VIN and J1 as shown in Figure 2 .

4. Connect voltmeter (can optionally use voltmeter from VIN source if available), V1 across VIN as shown

in Figure 2 .

5. Connect LOAD1 to J8 as shown in Figure 2 . Set LOAD1 to constant current mode to sink 0 A

VIN is applied.

6. Connect voltmeter, V2 across J9 and J10 as shown in Figure 2 .

7. Increase VIN from 0 V to 36 V

8. Observe that VOUT is regulating when VIN is at 36 V.

9. Increase VIN to 48 V.

10. Increase LOAD1 from 0 A to 15 A

11. Turn on fan making sure to blow air directly on the EVM.

12. Increase LOAD1 from 15 A

13. Decrease LOAD1 to 0 A.

14. Decrease VIN from 48 V

15. Shut down VIN.

Power Up/Down Test Procedures

, the fan should be turned on. Also, never

DC

before

DC

.

DC

.

DC

to 30 A

DC

to 0 V.

DC

.

DC

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 9

Submit Documentation Feedback

Page 10

www.ti.com

81

79

87

83

91

89

93

85

2 6 18 262210 14

I

OUT

- Output Current - A

VIN= 36 V

VIN= 72 V

VIN= 48 V

Percent Efficiency - %

V

OUT

= 3.3 V

f

S

= 300 kHz

OVERALL EFFICIENCY

vs

OUTPUT CURRENT

10

-40

-60

100

1 k 10 k 100 k

0

-20

40

20

60

-120

-180

0

-60

120

60

180

VIN= 36 V

I

OUT

= 10 A

g

M

= -8 dB

FM= 50°

Gain

Phase

f - Frequency - Hz

Gain - dB

Phase - °

GAIN AND PHASE

vs

FREQUENCY

4

2

10

6

12

8

6 18 26 302210 14

2

I

OUT

- Output Current - A

VIN= 36 V

VIN= 72 V

VIN= 48 V

P

LOSS

- Power Loss - W

V

OUT

= 3.3 V

f

S

= 300 kHz

POWER LOSS

vs

OUTPUT CURRENT

Power Up/Down Test Procedures

7 Power Up/Down Test Procedures

Using the UCC2891 Active Clamp Current Mode PWM Controller10 SLUU178A – November 2003 – Revised December 2006

Figure 4.

Figure 3.

Figure 5.

Submit Documentation Feedback

Page 11

www.ti.com

t − Time − 2.5 µs/div

VIN = 36 V

I

OUT

= 30 A

500 mV/div

1 V peak-to-peak

Input Ripple Voltage

10

-40

-60

100 1 k 10 k 100 k

0

-20

40

20

60

-120

-180

0

-60

120

60

180

VIN= 48 V

I

OUT

= 10 A

g

M

= -10 dB

FM= 50°

Gain

Phase

f - Frequency - Hz

Gain - dB

Phase - °

GAIN AND PHASE

vs

FREQUENCY

t − Time − 2.5 µs/div

VIN = 72 V

I

OUT

= 30 A

50 mV/div

36 mV peak-to-peak

Output Ripple Voltage

10

-40

-60

100 1 k 10 k 100 k

0

-20

40

20

60

-120

-180

0

-60

120

60

180

VIN= 72 V

I

OUT

= 10 A

g

M

= -9 dB

FM= 50°

Gain

Phase

f - Frequency - Hz

Gain - dB

Phase - °

GAIN AND PHASE

vs

FREQUENCY

Power Up/Down Test Procedures

Figure 6.

Figure 7.

Figure 8.

Figure 9.

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 11

Submit Documentation Feedback

Page 12

www.ti.com

t − Time − 1 µs/div

VIN = 36 V

6.3 V , QF Gate (J5)

(5 V/div)

8.4 V , QR Gate (J6)

(5 V/div)

SR Gate Drive

t − Time − 2.5 µs/div

VIN = 36 V

I

OUT

= 30 A

50 mV/div

23 mV peak-to-peak

Output Ripple Voltage

t − Time − 1 µs/div

VIN = 72 V

12.3 V , QF Gate (J5)

(5 V/div)

5.4 V , QR Gate (J6)

(5 V/div)

SR Gate Drive

t − Time − 2.5 µs/div

VIN = 48 V

I

OUT

= 10 A

V

PRI

(40 V/div)

I

PRI

(0.5 A/div)

Transformer Primary

Power Up/Down Test Procedures

Figure 10.

Figure 11.

Figure 12.

Figure 13.

12 Using the UCC2891 Active Clamp Current Mode PWM Controller SLUU178A – November 2003 – Revised December 2006

Submit Documentation Feedback

Page 13

www.ti.com

8 EVM Assembly Drawing and Layout

Figure 14 through Figure 20 show the top-side and bottom-side component placement for the EVM, as

well as device pin numbers where necessary. A four layer PCB was designed using the top and bottom

layers for signal traces and component placement along with an internal ground plane. The PCB

dimensions are 3.6" x 2.7" with a design goal of fitting all components within the industry standard

half-brick format, as outlined by the box dimensions 2.28" x 2.20" shown in Figure 15 . All components are

standard OTS surface mount components placed on the both sides of the PCB. The copper-etch for each

layer is also shown.

EVM Assembly Drawing and Layout

Figure 14. Top Side Component Assembly

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 13

Submit Documentation Feedback

Page 14

www.ti.com

EVM Assembly Drawing and Layout

Figure 15. Top Side Silk Screen

14 Using the UCC2891 Active Clamp Current Mode PWM Controller SLUU178A – November 2003 – Revised December 2006

Figure 16. Top Signal Trace Layer

Submit Documentation Feedback

Page 15

www.ti.com

EVM Assembly Drawing and Layout

Figure 17. Internal Split Ground Plane

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 15

Submit Documentation Feedback

Figure 18. Internal Signal Trace Layer

Page 16

www.ti.com

EVM Assembly Drawing and Layout

Figure 19. Bottom Signal Trace Layer

Figure 20. Bottom Side Component Assembly

Using the UCC2891 Active Clamp Current Mode PWM Controller16 SLUU178A – November 2003 – Revised December 2006

Submit Documentation Feedback

Page 17

www.ti.com

9 List of Materials

The following table lists the UCC2891EVM components corresponding to the schematic shown in

Figure 1 .

Table 2. List of Materials

REF DESCRIPTION MFR PART NUMBER

C1, C2, C4 3 Capacitor, ceramic, 2.2 µ F, 100 V, X7R, 20%, 1812 TDK C4532X7R2A225M

C3, C14, C17 3 Capacitor, ceramic, 0.1 µ F, 50 V, X7R, 20%, 805 Vishay VJ0805Y104MXAA

C5 1 Capacitor, ceramic, 100 pF, 50 V, NPO, 10%, 805 Vishay VJ0805A101KXAA

C6, C7 2 Capacitor, ceramic, 0.22 µ F, 50 V, X7R, 20%, 805 TDK C2012X7R1H224M

C8 1 Capacitor, ceramic, 10 nF, 50 V, X7R, 20%, 805 Vishay VJ0805Y103MXAA

C9 1 Capacitor, ceramic, 33 nF, 250 V, X7R, 10%, 1206 MuRata GRM31CR72E333KW03L

C10, C11 2 Capacitor, tantalum chip, 47 µ F, 16 V, C Vishay 595D476X9016C2T

C12, C18 2 Capacitor, ceramic, 10 µ F, 16 V, X5R, 20%, 1206 TDK C3216X5R1C106M

C13 1 Capacitor, ceramic, 1.5 µ F, 10 V, X5R, 20%, 805 TDK C2012X5R1A155M

C15 1 Capacitor, ceramic, 82 nF, 50 V, X7R, 10%, 805 Vishay VJ0805Y823KXAA

C16 1 Capacitor, ceramic, 220 pF, 50 V, NPO, 10%, 805 Vishay VJ0805A221KXAA

C19, C20 2 Capacitor, POSCAP, 330 µ F, 6.3 V, 20%, 7343 (D) Sanyo 6TPD330M

D1, D2, D3, D4, D5 5 Diode, schottky, 200 mA, 30 V, SOT23 Vishay BAT54

D8 1 Diode, switching, 200 mA, 200 V, SOT23 Philips/NXP BAS21

D6 1 Diode, zener, 5.1 V, 350 mW, SOT23 Vishay BZX84C5V1

D7 1 Adjustable precision shunt regulator, 0.5%, SOT23 TI TLV431BCDBZ

J1 1 Terminal block, 2 pin, 15 A, 5.1 mm, 0.40 × 0.35 OST ED500/2DS

J2, J3, J4, J5 4 Adaptor, 3.5 mm probe clip (or 131-5031-00), 3.5 mm Tektronix 131 4244 00

J6, J7, J9, J10 4 Printed circuit pin, 0.043 hole, 0.3 length, 0.043 Mill Max 3103-1-00-15-00-00-0X-0

J8 1 Terminal block, 4 pin, 15 A, 5.1mm, 0.80 × 0.35 OST ED500/4DS

L1 1 Inductor, 2 µ H, 1 pri, 1 sec, 0.920 × 0.780 Pulse PA0373

Q1 1 MOSFET, P-channel, 150 V, 2.2 A, 240 m Ω , SO-8 IR IRF6216

Q2 1 Vishay Si7846DP

Q3, Q4, Q5, Q7, Q8 5 MOSFET, N-channel, 30 V, 55 A, 2.5 m Ω , LFPAK Renesas HAT2165H

Q6 1 Bipolar, NPN, 40 V, 600 mA, 225 mW, SOT23 Vishay MMBT2222A

QT

Y

MOSFET, N-channel, 150 V, 6.7 A, 50 m Ω ,

PowerPak SO-8

List of Materials

SLUU178A – November 2003 – Revised December 2006 Using the UCC2891 Active Clamp Current Mode PWM Controller 17

Submit Documentation Feedback

Page 18

www.ti.com

References

Table 2. List of Materials (continued)

REF DESCRIPTION MFR PART NUMBER

R1 1 Resistor, chip, 8.45 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-8451-F

R2 1 Resistor, chip, 57.6 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-5762-F

R3 1 Resistor, chip, 76.8 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-7682-F

R4, R10, R15, R16,

R20, R23, R24

R5 1 Resistor, chip, 158 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-1583-F

R6 1 Resistor, chip, 1.82 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-1821-F

R7, R8, R12 3 Resistor, chip, 1 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-1001-F

R9 1 Resistor, chip, 11.8 Ω , 1/10 W, 1%, 805 Vishay CRCW0805-11R8-F

R11 1 Resistor, chip, 26.7 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-2672-F

R13 1 Resistor, chip, 2 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-2001-F

R14 1 Resistor, chip, 10 Ω , 1/10 W, 1%, 805 Vishay CRCW0805-10R0-F

R17, R18 2 Resistor, chip, 499 Ω , 1/10 W, 1%, 805 Vishay CRCW0805-4990-F

R19 1 Resistor, chip, 665 Ω , 1/10 W, 1%, 805 Vishay CRCW0805-6650-F

R21, R22 2 Resistor, chip, 10 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-1002-F

R25 1 Resistor, chip, 51.1 Ω , 1/10 W, 1%, 805 Vishay CRCW0805-51R1-F

R26 1 Resistor, chip, 28.7 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-2872-F

R27 1 Resistor, chip, 12.1 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-1212-F

R28 1 Resistor, chip, 4.99 k Ω , 1/10 W, 1%, 805 Vishay CRCW0805-4991-F

T1 1 Transformer, current sense, 10-A, 1:100, SMD Pulse P8208

T2 1 Transformer, high-frequency planar, planar Pulse PA0810

U1 1 TI UCC2891D

U2 1 IC, phototransistor, CTR 100%-300%, SOP-4 Vishay SFH690BT

QT

Y

7 Resistor, chip, 2.21 Ω , 1/10 W, 1%, 805 Vishay CRCW0805-2R21-F

IC, current mode active clamp PWM controller,

SO-16

10 References

1. UCC2891 Current Mode Active Clamp PWM Controller, Datasheet, (SLUS542)

2. Designing for High Efficiency with the UCC2891 Active Clamp PWM Controller, by Steve Mappus,

Application Note (SLUA299)

18 Using the UCC2891 Active Clamp Current Mode PWM Controller SLUU178A – November 2003 – Revised December 2006

Submit Documentation Feedback

Page 19

EVM IMPORTANT NOTICE

Texas Instruments (TI) provides the enclosed product(s) under the following conditions:

This evaluation kit being sold by TI is intended for use for ENGINEERING DEVELOPMENT OR

EVALUATION PURPOSES ONLY andis not considered by TI to be fitfor commercialuse. As such,

the goods being provided may not be complete in terms of required design-, marketing-, and/or

manufacturing-related protective considerations, including product safety measures typically

found in the end product incorporating the goods. As a prototype, this product does not fall within

the scope of the European Union directive on electromagneticcompatibility and therefore may not

meet the technical requirements of the directive.

Should this evaluation kit not meet the specifications indicated in the EVM User’s Guide, the kit may

be returned within 30 days from the date of delivery for a full refund. THE FOREGOING

WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU

OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY

WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further,

the user indemnifies TI from all claims arising from the handling or use of the goods. Please be

aware that the products received may not be regulatory compliant or agency certified (FCC, UL,

CE, etc.). Due to the open construction of the product, it is the user’s responsibility to take any and

all appropriate precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL

BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR

CONSEQUENTIAL DAMAGES.

TI currently deals with a variety of customers for products, and therefore our arrangement with the

user is not exclusive.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein.

Please read the EVM User’s Guide and, specifically, the EVM Warnings and Restrictions notice

in the EVM User’s Guide prior to handling the product. This notice contains important safety

information about temperatures and voltages. For further safety concerns, please contact the TI

application engineer.

Persons handling the product must have electronics training and observe good laboratory practice

standards.

No license is granted under any patent right or other intellectual property right of TI covering or

relating to any machine, process, or combination in which such TI products or services might be

or are used.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003-- 2006, Texas Instruments Incorporated

Page 20

DYNAMIC WARNINGS AND RESTRICTIONS

It is important to operate this EVM within the input voltage range of 0 Vdc to 72 Vdc.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage

to the EVM. If there are questions concerning the input range, please contact a TI field

representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or

possible permanent damage to the EVM. Please consult the EVM User’s Guide prior to connecting

any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI

field representative.

During normal operation, some circuit components may have case temperatures greater than

50°C. The EVM is designed to operate properly with certain components above 50°C as long as

the input and output ranges are maintained. These components include but are not limited to linear

regulators, switching transistors, pass transistors, and current sense resistors. These types of

devices can be identified using the EVM schematic located in the EVM User ’s Guide. When placing

measurement probes near these devices during operation, please be aware that these devices

may be very warm to the touch.

Mailing Address:

Texas Instruments

Post Office Box 655303

Dallas, Texas 75265

Copyright © 2003-- 2006, Texas Instruments Incorporated

Page 21

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements,

improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.

Customers should obtain the latest relevant information before placing orders and should verify that such information is current and

complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s

standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this

warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily

performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should

provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask

work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services

are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such

products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under

the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is

accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an

unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties

may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service

voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business

practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would

reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement

specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications

of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related

requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any

applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its

representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is

solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in

connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products

are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any

non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Interface interface.ti.com Digital Control www.ti.com/digitalcontrol

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

RFID www.ti-rfid.com Telephony www.ti.com/telephony

Low Power www.ti.com/lpw Video & Imaging www.ti.com/video

Wireless

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Wireless www.ti.com/wireless

Copyright © 2007, Texas Instruments Incorporated

Loading...

Loading...