Texas Instruments TVP5031PFP Datasheet

TVP5031

NTSC/P AL Digital Video Decoder

April 2000 MSDS Multimedia

Data Manual

SLAS267

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 2000, Texas Instruments Incorporated

iii

Contents

Section Title Page

1 Introduction 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Applications 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Functional Block Diagram 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 Terminal Assignments 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.5 Ordering Information 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Terminal Functions 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.7 Strapping Terminals Description 1–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Functional Description 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Analog Video Processing and A/D Converters 2–1. . . . . . . . . . . . . . . . . . .

2.1.1 Video Input Selection 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Analog Input Clamping and Automatic Gain

Control Circuits 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.3 A/D Converter 2–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Digital Processing 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Decimation Filter 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.2 Y/C Separation 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.3 Luminance Processing 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.4 Chrominance Processing 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.5 Clock Circuits 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 Genlock Control 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Video Output Format 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.1 Sampling Frequencies and Patterns 2–12. . . . . . . . . . . . . . . . . . .

2.4.2 Video Port 20-Bit and 16-Bit 4:2:2 Output

Format Timing 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.3 Video Port 10-Bit and 8-Bit 4:2:2 and ITU-R BT.656

Output Format Timing 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Synchronization Signals 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6 Host Interface 2–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.1 I

2

C Host Interface 2–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 Parallel Host Interface A 2–22. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.3 Parallel Host Interface B 2–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.4 Parallel Host Interface C 2–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.5 Parallel Host Interface Register Map 2–27. . . . . . . . . . . . . . . . . .

2.6.6 Parallel Host Interface Microcode Write Operation 2–28. . . . . .

2.6.7 Parallel Host Interface Microcode Read Operation 2–29. . . . . .

2.7 VBI Data Processor 2–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7.1 Teletext Data Byte Order 2–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

2.7.2 Teletext as Ancillary Data in Video Stream 2–31. . . . . . . . . . . . .

2.8 Raw Video Data Output 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.9 Reset and Initialization 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.10 Internal Control Registers 2–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11 Register Definitions 2–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.1 Video Input Source Selection 1 2–35. . . . . . . . . . . . . . . . . . . . . . .

2.11.2 Analog Channel Controls 2–35. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.3 Operation Mode Controls 2–35. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.4 Miscellaneous Control 2–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.5 Color Killer Threshold Control 2–38. . . . . . . . . . . . . . . . . . . . . . . .

2.11.6 Luminance Processing Control 1 2–38. . . . . . . . . . . . . . . . . . . . .

2.11.7 Luminance Processing Control 2 2–39. . . . . . . . . . . . . . . . . . . . .

2.11.8 Brightness Control 2–39. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.9 Color Saturation Control 2–39. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.10 Hue Control 2–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.11 Contrast Control 2–40. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.12 Outputs and Data Rates Select 2–40. . . . . . . . . . . . . . . . . . . . . .

2.11.13 Horizontal Sync HSYN Start NTSC/PAL 2–41. . . . . . . . . . . . . . .

2.11.14 Vertical Blanking VBLK Start 2–42. . . . . . . . . . . . . . . . . . . . . . . . .

2.11.15 Vertical Blanking VBLK Stop 2–42. . . . . . . . . . . . . . . . . . . . . . . . .

2.11.16 Chrominance Control 1 2–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.17 Chrominance Control 2 2–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.18 Interrupt Reset Register B 2–44. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.19 Interrupt Enable Register B 2–44. . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.20 Interrupt Configuration Register B 2–45. . . . . . . . . . . . . . . . . . . .

2.11.21 Program RAM Write 2–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.22 Microprocessor Reset Clear 2–45. . . . . . . . . . . . . . . . . . . . . . . . .

2.11.23 Major Software Revision Number 2–45. . . . . . . . . . . . . . . . . . . . .

2.11.24 Status Register 1 2–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.25 Status Register 2 2–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.26 Status Register 3 2–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.27 Status Register 4 2–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.28 Interrupt Status Register B 2–48. . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.29 Interrupt B Active Register 2–48. . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.30 Minor Software Revision Number 2–48. . . . . . . . . . . . . . . . . . . . .

2.11.31 Status Register 5 2–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.32 Program RAM Read 2–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.33 TXF Filter 1 Parameters 2–50. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.34 TXF Filter 2 Parameters 2–51. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.35 TXF Error Filtering Enables 2–52. . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.36 TXF Transaction Processing Enables 2–52. . . . . . . . . . . . . . . . .

2.11.37 TTX Control Register 2–53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.38 Line Enable Registers A, B 2–53. . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.39 Sync Pattern Register 2–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

2.11.40 Teletext FIFO 2–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.41 Closed Caption Data 2–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.42 Buffer Status 2–55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.43 Interrupt Threshold 2–55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.44 Interrupt Line Number 2–55. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.45 FIFO Control 2–56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.46 FIFO RAM Test 2–56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.47 Interrupt Status Register A 2–57. . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.48 Interrupt Enable Register A 2–57. . . . . . . . . . . . . . . . . . . . . . . . . .

2.11.49 Parallel Host Interface Teletext FIFO 2–58. . . . . . . . . . . . . . . . . .

2.11.50 Parallel Host Interface Status/Interrupt A 2–58. . . . . . . . . . . . . .

3 Electrical Specifications 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Absolute Maximum Ratings 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Recommended Operating Conditions 3–1. . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Crystal Specifications 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Electrical Characteristics Over Recommended Voltage and

Temperature Ranges, DV

DD

= 3.3 V, AVDD = 3.3 V, TA = 70°C 3–2. . . .

3.3.1 DC Electrical Characteristics 3–2. . . . . . . . . . . . . . . . . . . . . . . . .

3.3.2 Analog Processing and A/D Converters 3–2. . . . . . . . . . . . . . . .

3.3.3 Clocks, Video Data, Sync Timing 3–3. . . . . . . . . . . . . . . . . . . . .

3.3.4 I

2

C Host Port Timing 3–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.5 Parallel Host Interface A 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.6 Parallel Host Interface B 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3.7 Parallel Host Interface C 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Mechanical Data 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

List of Illustrations

Figure Title Page

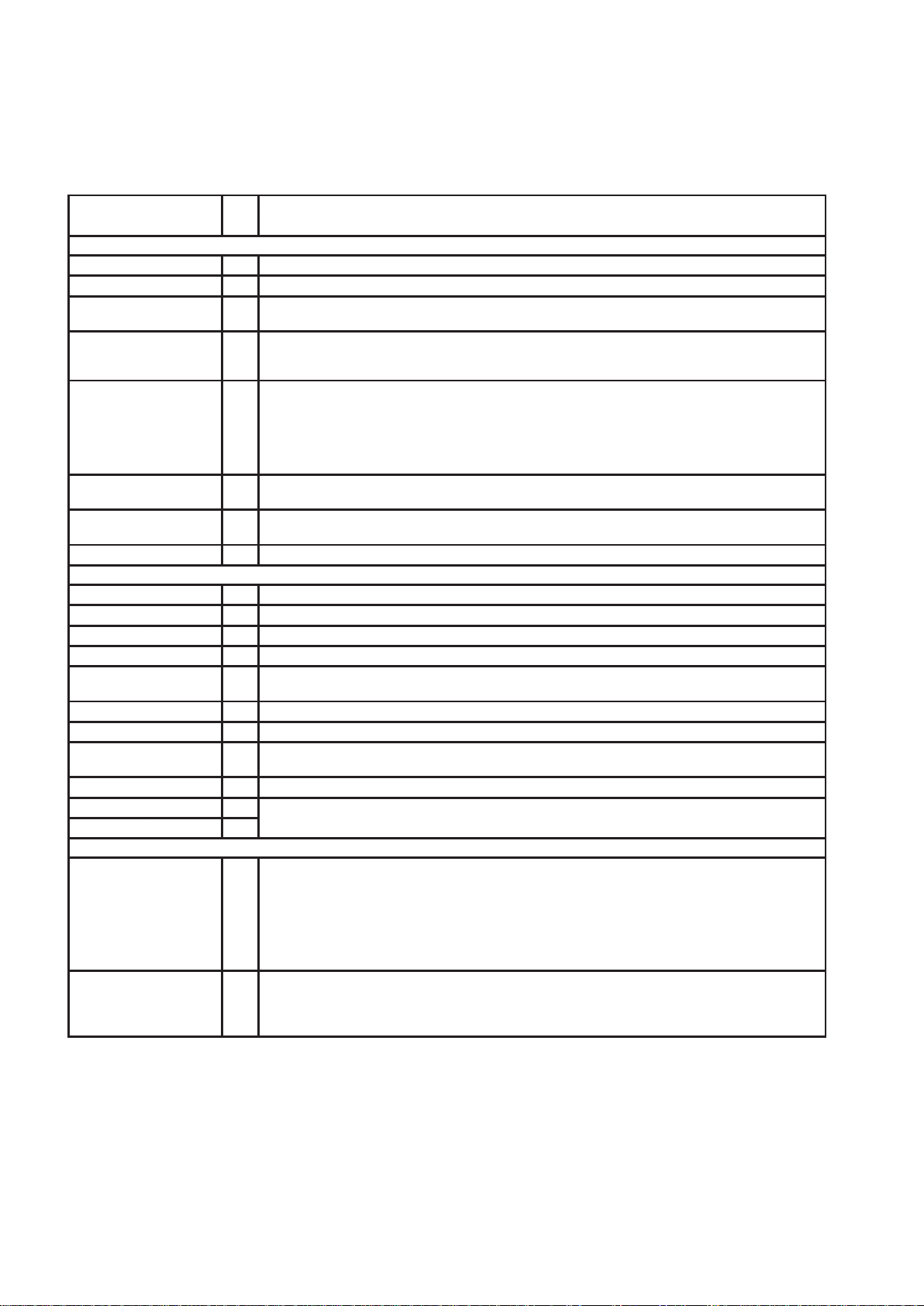

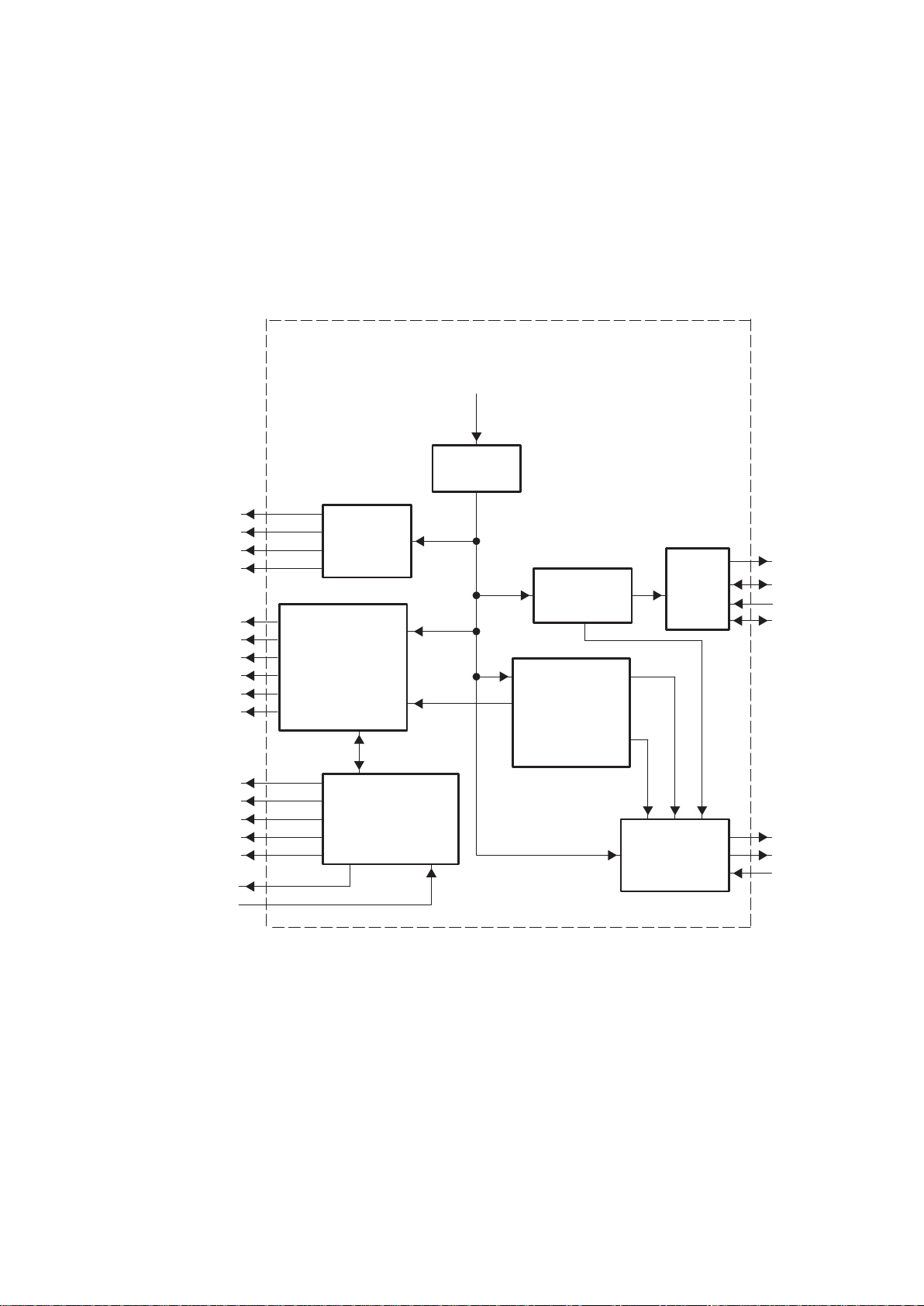

2–1 Analog Video Processors and A/D Converters 2–1. . . . . . . . . . . . . . . . . . . . . . . .

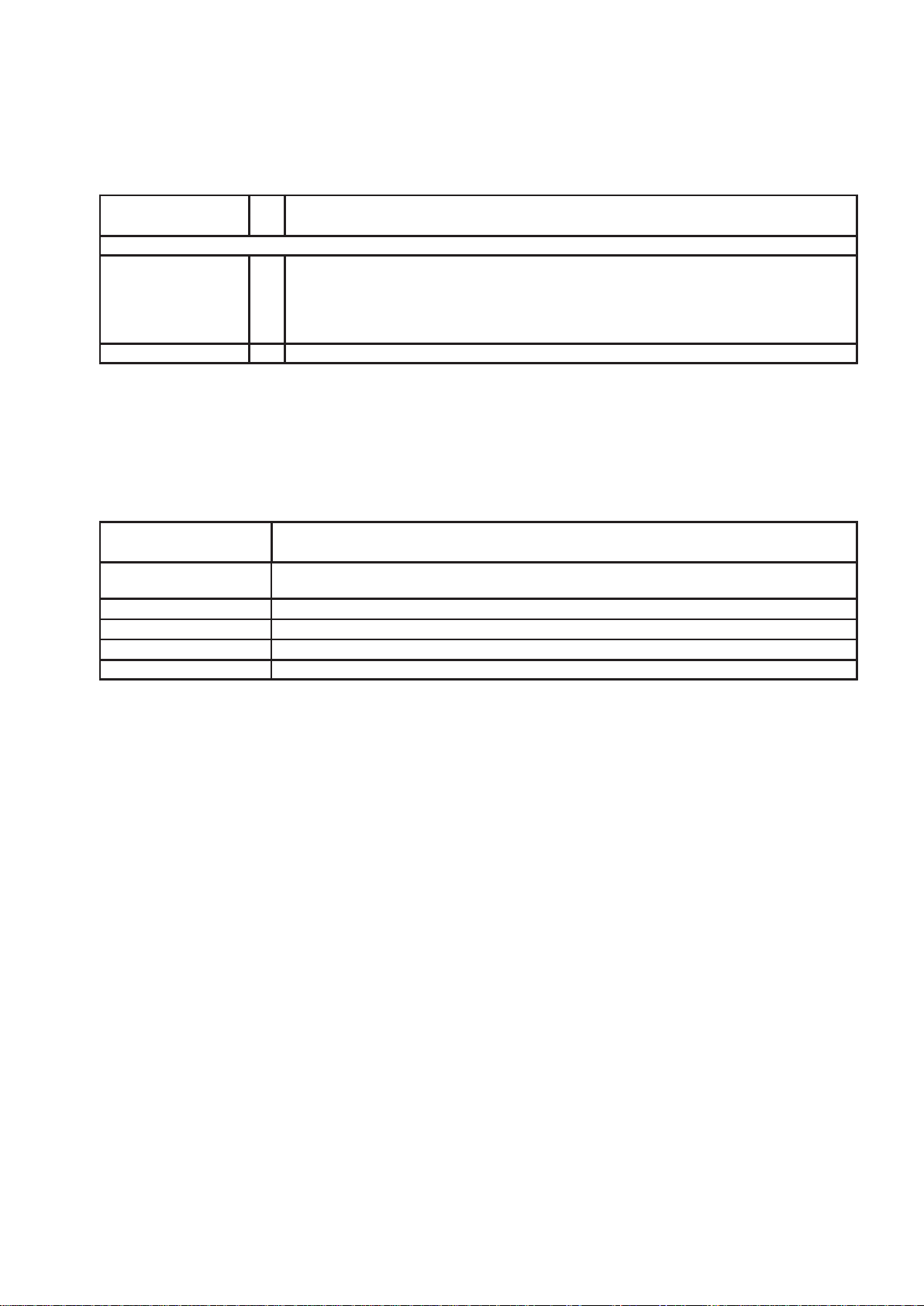

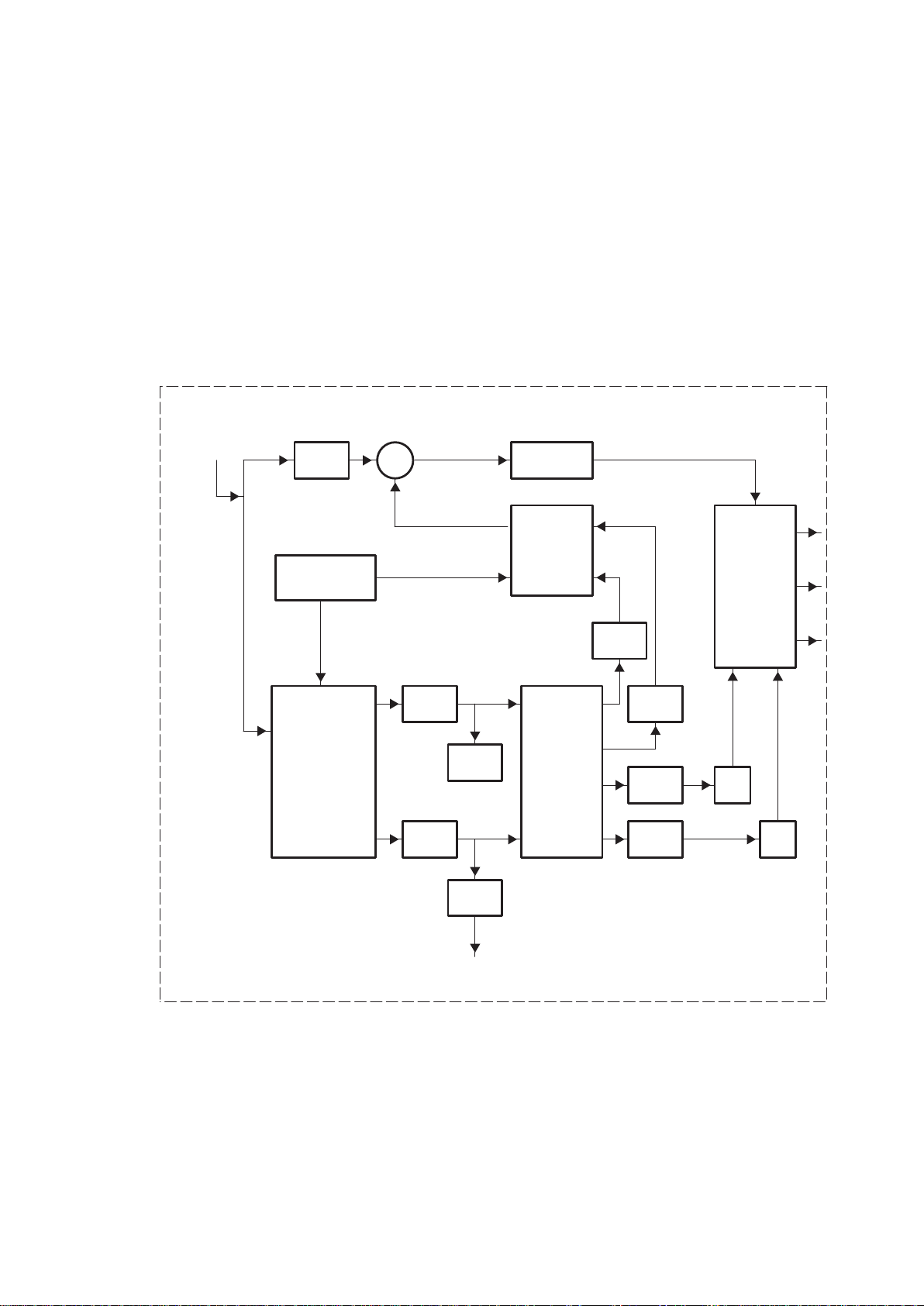

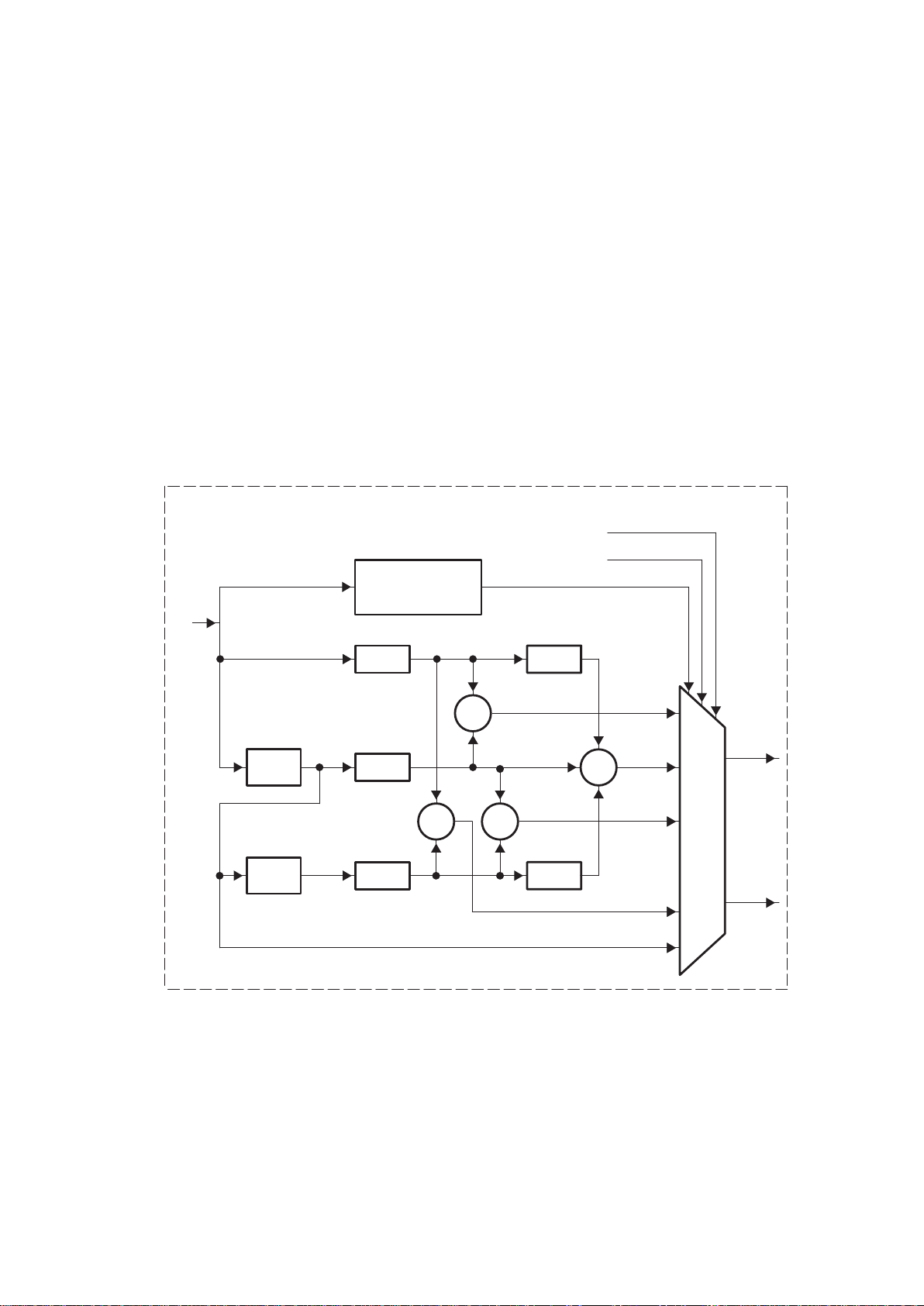

2–2 Digital Video Signal Processing Block Diagram 2–3. . . . . . . . . . . . . . . . . . . . . . .

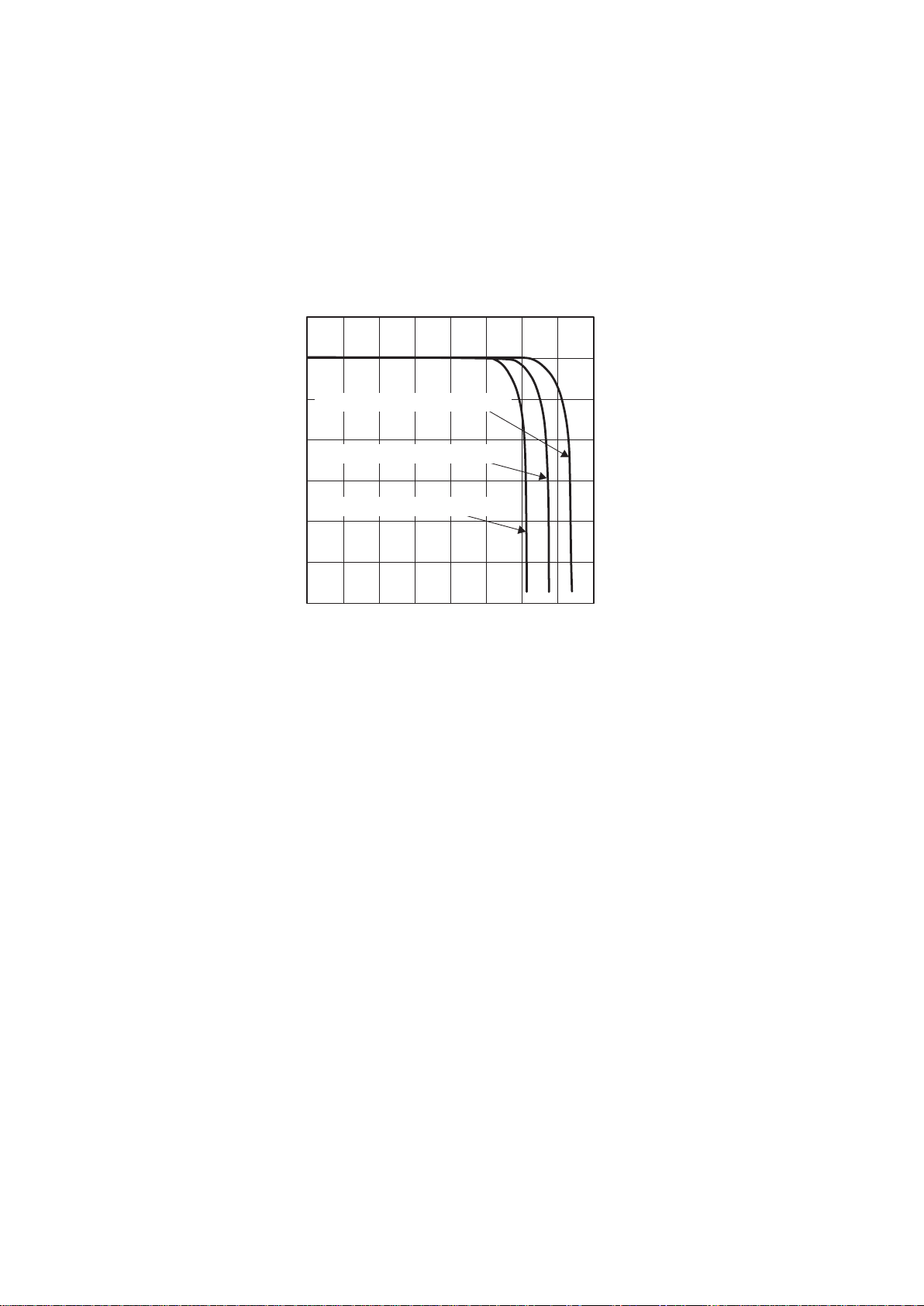

2–3 Decimation Filter Frequency Response 2–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Y/C Separation Block Diagram 2–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

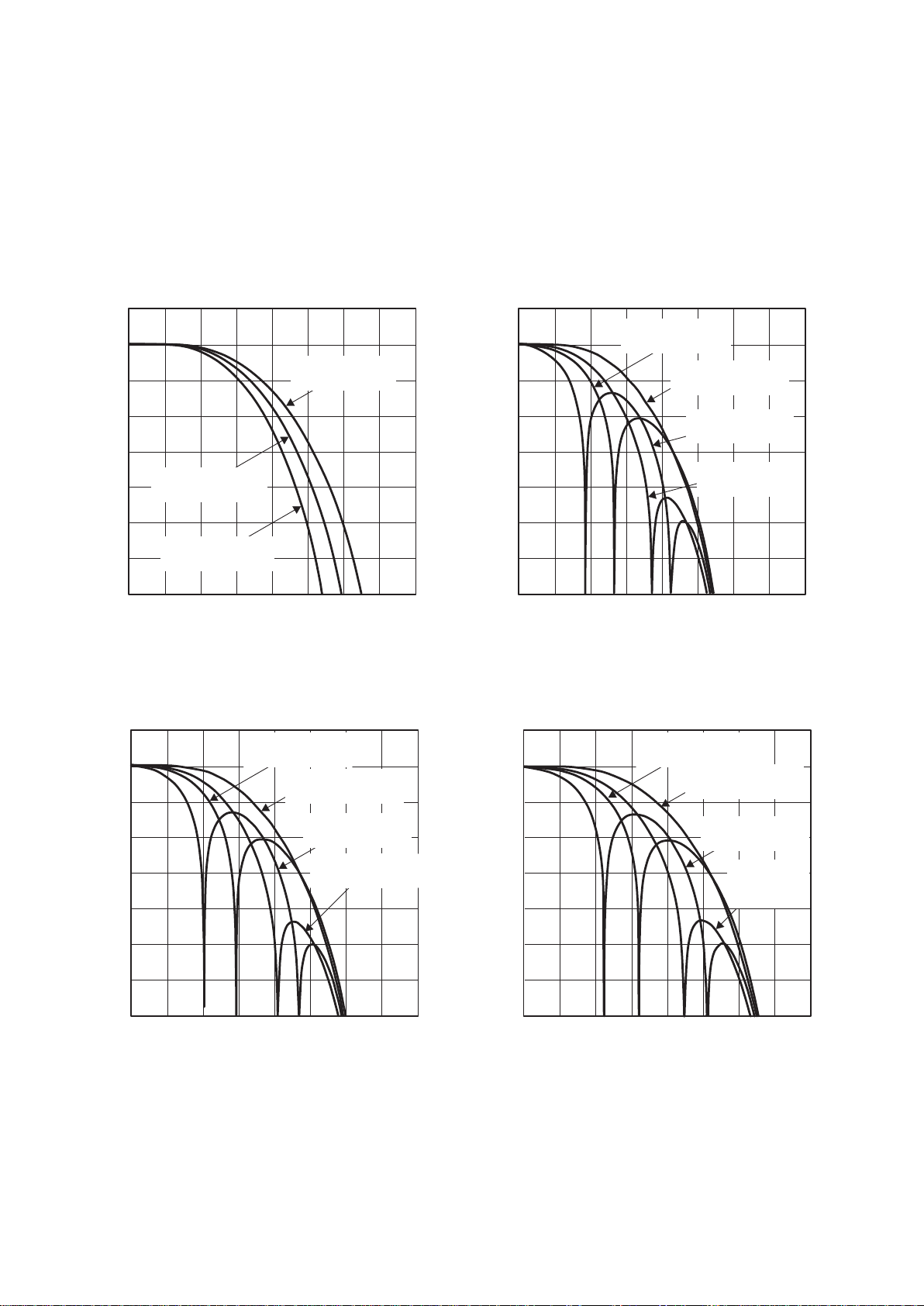

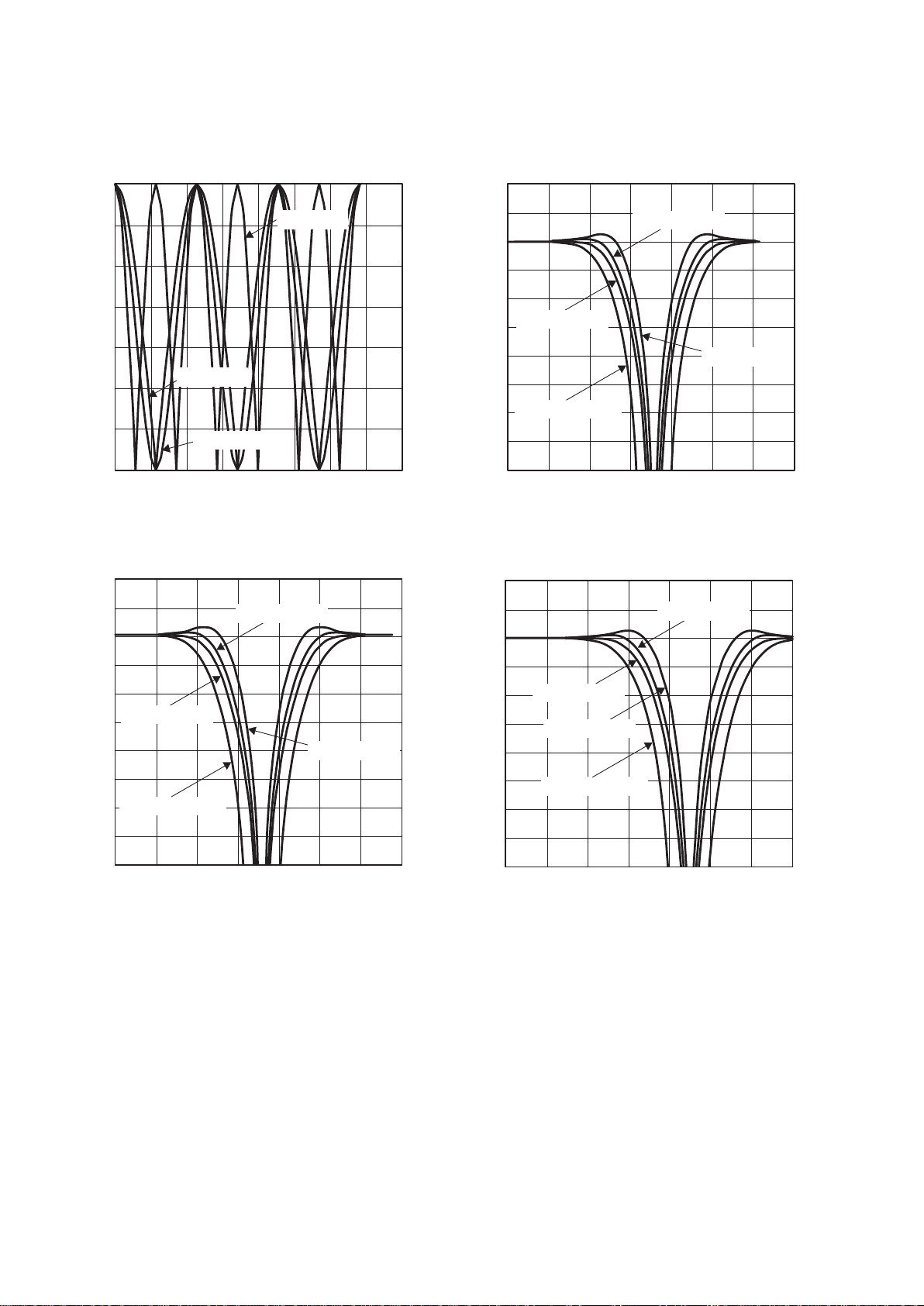

2–5 Color Low-Pass Filter Frequency Response 2–6. . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 Color Low-Pass Filter With Notch Filter Frequency Response

(NTSC and PAL-M Square Pixel Sampling) 2–6. . . . . . . . . . . . . . . . . . . . . . . .

2–7 Color Low-Pass Filter With Notch Filter Characteristics

(13.5 MHz Sampling) 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Color Low-Pass Filter With Notch Filter Frequency Response

(PAL Square Pixel Sampling) 2–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 3-Line Adaptive Comb Filtering 2–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 Comb Filters Frequency Response 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–11 Chroma Trap Filter Frequency Response 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . .

2–12 Chroma Trap Filter Frequency Response (13.5 MHz Sampling) 2–8. . . . . . . .

2–13 Chroma Trap Filter Frequency Response

(PAL Square Pixel Sampling) 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

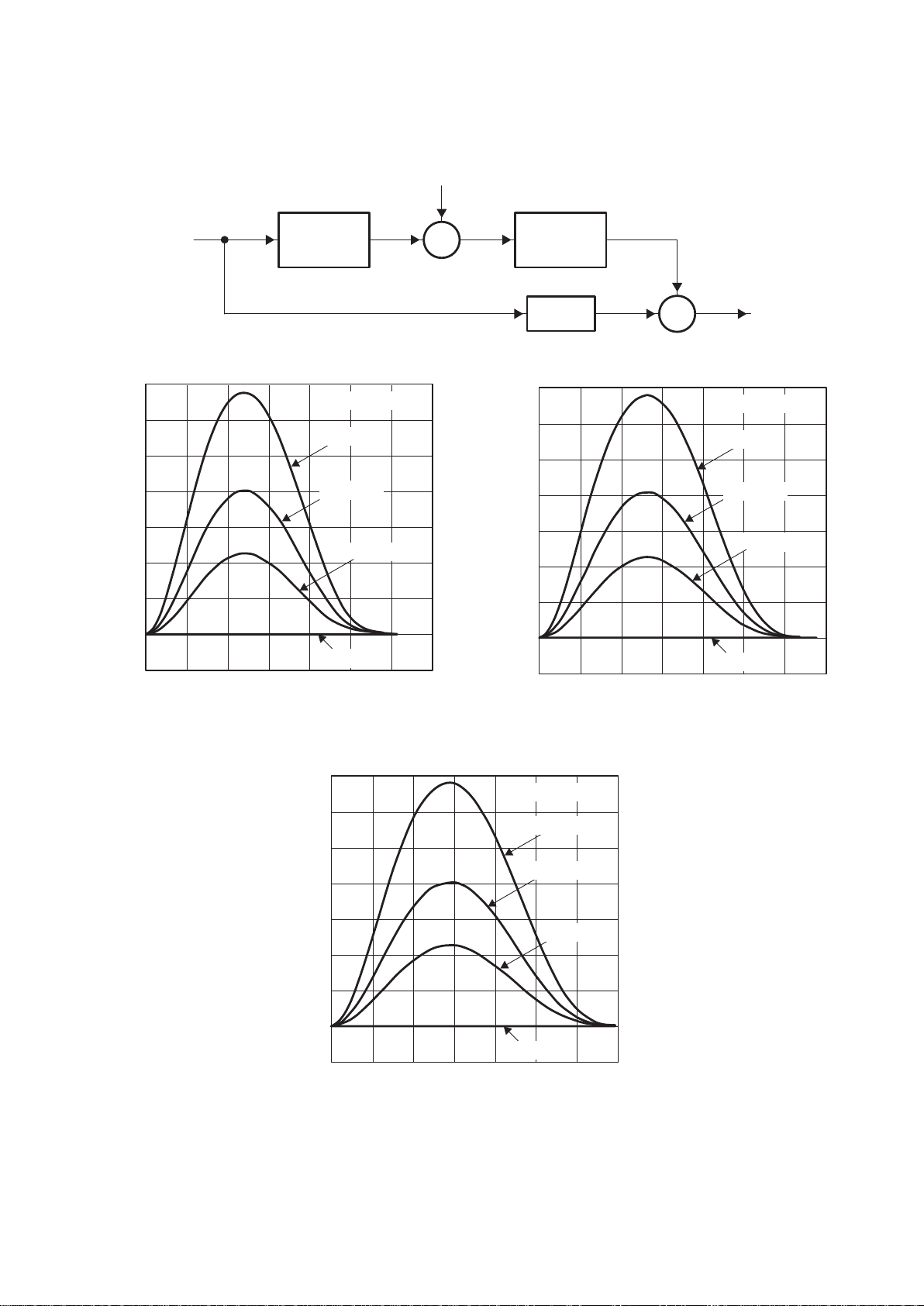

2–14 Luminance Edge-Enhancer Peaking Block Diagram 2–9. . . . . . . . . . . . . . . . . .

2–15 Peaking Filter Response, NTSC and PAL-M Square Pixel Sampling 2–9. . . .

2–16 Peaking Filter Response, 13.5 MHz Sampling Rate 2–9. . . . . . . . . . . . . . . . . .

2–17 Peaking Filter Response, PAL Square Pixel 2–9. . . . . . . . . . . . . . . . . . . . . . . . .

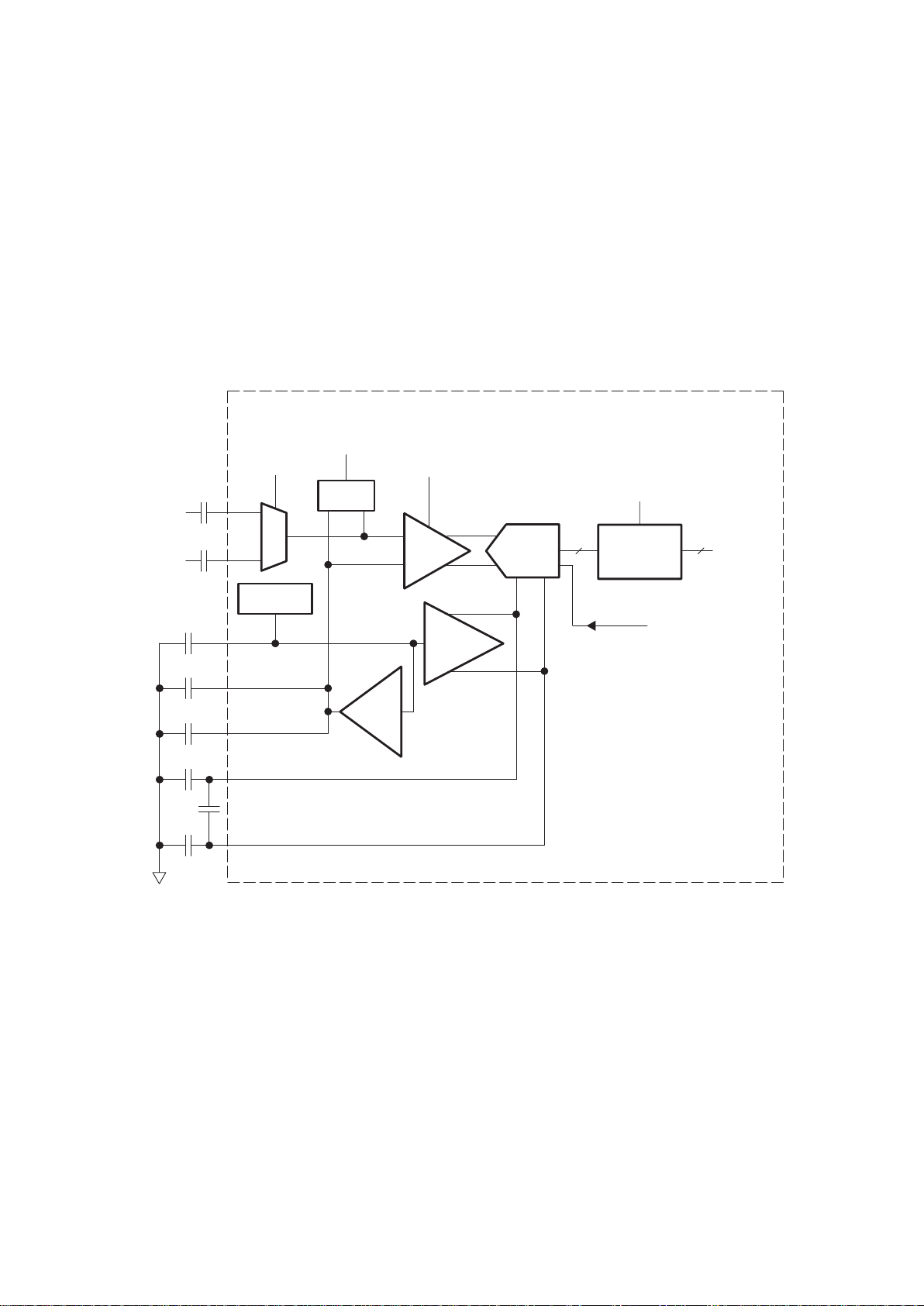

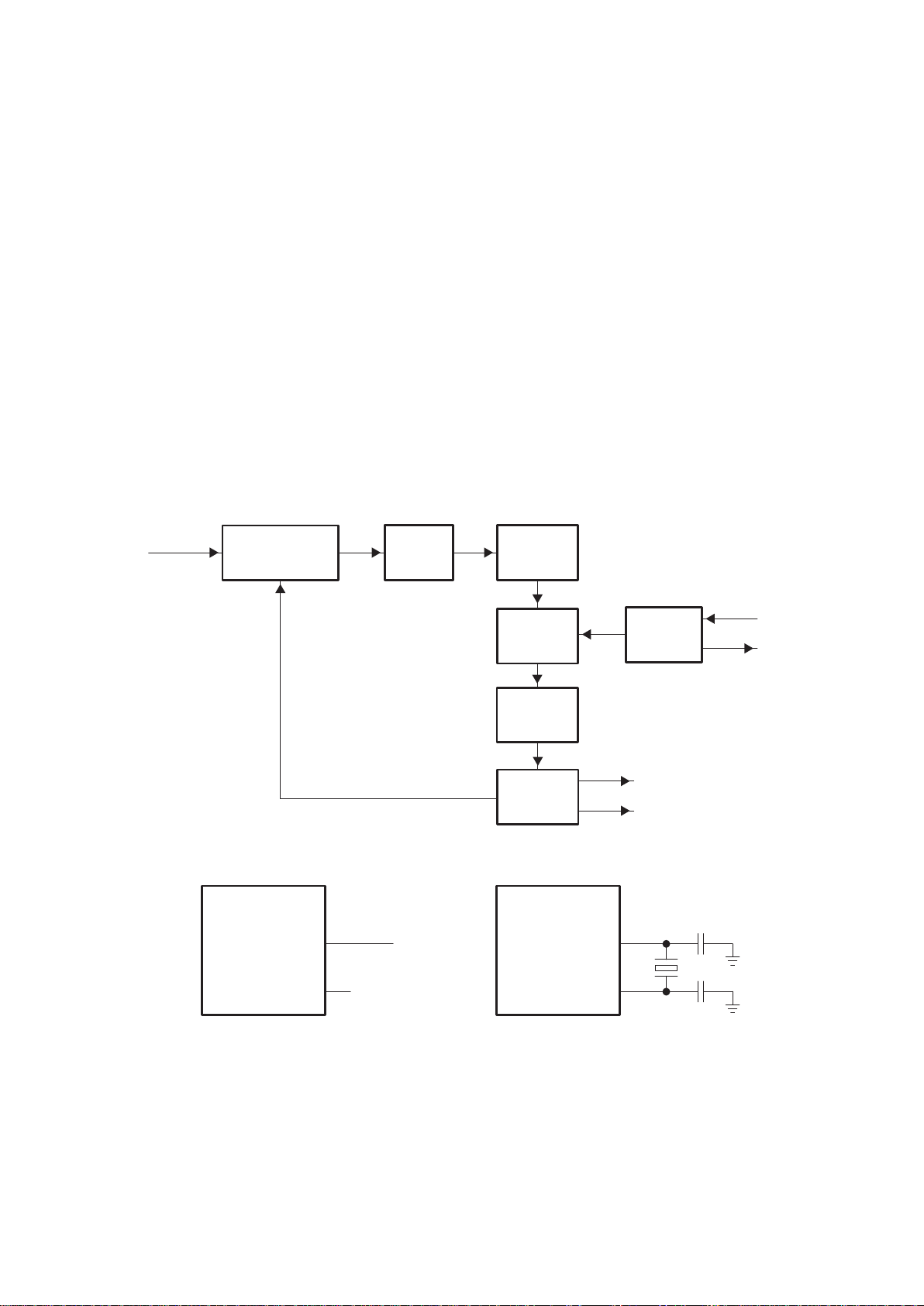

2–18 Clock Circuit Diagram 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–19 Example Reference Clock Configurations 2–10. . . . . . . . . . . . . . . . . . . . . . . . . . .

2–20 GLCO Timing 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–21 4:2:2 Sampling 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–22 20-Bit 4:2:2 Output Format 2–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–23 20-Bit 4:2:2 Output Format 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–24 Vertical Synchronization Signals 2–14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–25 Horizontal Synchronization Signals 2–15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–26 I2C Data Transfer Example 2–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–27 Parallel Host Interface A Timing 2–23. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–28 Parallel Host Interface B Timing 2–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–29 Parallel Host Interface C Timing 2–26. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–30 PHI Address Register Map 2–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

3–1 Parallel Host Interface A Timing 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 Parallel Host Interface B Timing 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Parallel Host Interface C Timing 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

List of Tables

Table Title Page

2–1 Summary of Line Frequencies, Data Rates, and Pixel Counts 2–12. . . . . . . . . . .

2–2 Host Port Mode Select 2–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 I2C Host Port Terminal Description 2–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Parallel Host Interface A Terminal Description 2–22. . . . . . . . . . . . . . . . . . . . . . . .

2–5 Parallel Host Interface B Terminal Description 2–24. . . . . . . . . . . . . . . . . . . . . . . .

2–6 Parallel Host Interface C Terminal Description 2–26. . . . . . . . . . . . . . . . . . . . . . . .

2–7 Teletext Data Byte Order 2–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 NABTS 525-Line Ancillary Data Sequence 2–31. . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 Dummy Timing Ancillary Data Sequence 2–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 Data ID 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–11 Reset Sequence 2–32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–12 Registers Summary 2–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–13 Analog Channel and Video Mode Selection 2–35. . . . . . . . . . . . . . . . . . . . . . . . .

2–14 Digital Output Control 2–37. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–15 Vertical Blanking Interval Start and End 2–42. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–16 Chrominance Comb Filter Selection 2–43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

1–1

1 Introduction

The TVP5031 is a high quality single-chip digital video decoder that converts base-band analog National Television

System Committee (NTSC) and phase alternating line (PAL) video into digital component video. The TVP5031

includes a 9-bit A/D converter with 2x sampling. Sampling is square-pixel or ITU-R BT .601 (27 MHz) and is line-locked

for correct pixel alignment. The output formats can be 8-bit, 10-bit or 16-bit 4:2:2, and 8-bit or 10-bit ITU-R BT.656

with embedded synchronization. The TVP5031 utilizes Texas Instruments patented technology for locking to weak,

noisy , or unstable signals, and a chroma frequency control output is generated for synchronizing downstream video

encoders.

Complementary three-line adaptive (2-H delay) comb filtering is available for both the luma and chroma data paths

to reduce both cross-luma and cross-chroma artifacts; a chroma trap filter is also available. Video characteristics

including hue, contrast, and saturation may be programmed using one of four supported host port interfaces; I

2

C and

three parallel host interface (PHI) modes. The TVP5031 generates synchronization, blanking, field, lock and clock

signals in addition to digital video outputs.

The TVP5031 includes methods for advanced vertical blanking interval (VBI) data retrieval. The VBI data processor

slices, parses, and performs error checking on teletext data in several formats. A built-in FIFO stores up to 14 lines

of teletext data, and with proper host synchronization full-screen teletext retrieval is enabled. The VBI data processor

also retrieves closed-caption data. The TVP5031 can also pass through over sampled raw composite data for

host-based software VBI processing.

The main blocks of the TVP5031 include:

• Analog processors and A/D converters

• Y/C separation

• Chrominance processor

• Luminance processor

• Clock/timing processor and power-down control

• Output formatter

• Host port interface

• VBI data processor

1.1 Features

• Accepts NTSC (M) and PAL (B, D, G, H, I, M, N) composite video

• Two analog video inputs for composite video

• A fully differential CMOS analog preprocessing channel with clamping and AGC for best S/N performance

• High speed 2x over-sampling 9-bit A/D converter

• Patented architecture for locking to weak, noisy, or unstable signals

• Single 14.31818 MHz reference crystal for all standards

• Line-locked clock and sampling at square-pixel or 27 MHz rates

• Programmable output data rates:

– 12.2727 MHz Square-Pixel (NTSC)

– 14.7500 MHz Square-Pixel (PAL)

– 13.5 MHz ITU-R BT.601 (NTSC and PAL)

• Optional automatic switching between P AL and NTSC standards

1–2

• Complementary 3-line (2-H delay) adaptive comb filters for both cross-luminance and cross-chrominance

noise reduction

• Subcarrier genlock output for synchronizing color subcarrier of external encoder

• Standard programmable video output formats:

– 16-bit 4:2:2 YCbCr

– 20-bit 4:2:2 YCbCr

– 8-bit 4:2:2 YCbCr

– 10-bit 4:2:2 YCbCr

– ITU-R BT.656 8-bit 4:2:2 with embedded syncs

– ITU-R BT.656 10-bit 4:2:2 with embedded syncs

• Advanced programmable video output formats:

– 2x oversampled raw VBI data during active video

– Sliced VBI data as ancillary data in video stream

• Teletext (NABTS, WST) and closed-caption decode with FIFO

• Programmable host port options including I

2

C and three parallel host interface (PHI) modes

• Brightness, contrast, saturation , and hue control through host port

• 5-V tolerant digital I/O ports

• 80-pin TQFP package

1.2 Applications

• Digital image processing

• Video conferencing

• Multimedia

• Digital video

• Desktop video

• Video capture

• Video editing

• Security applications

1–3

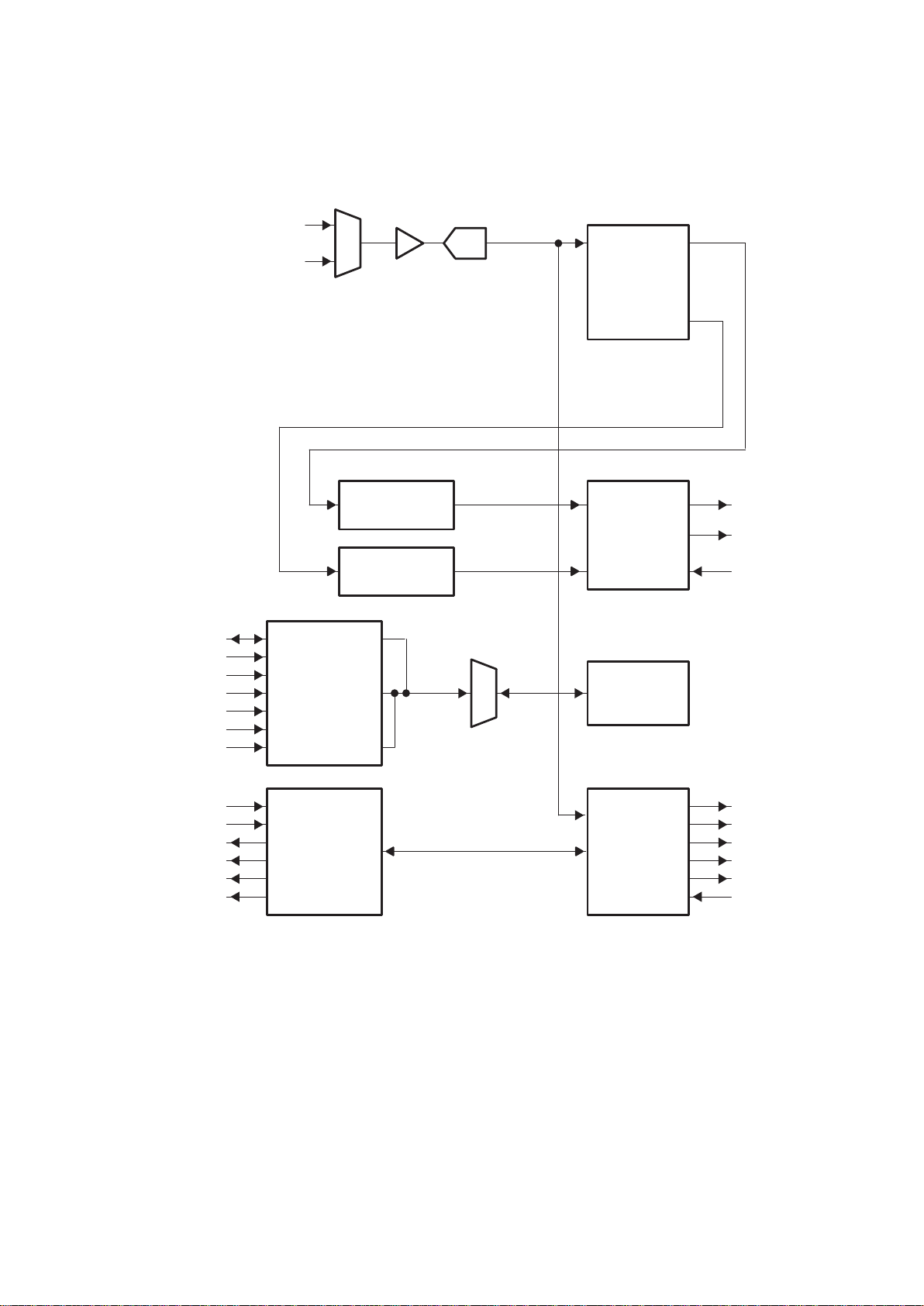

1.3 Functional Block Diagram

Luma/Chroma

Separation

VI_1A

VI_1B

A/D

AGC

Channel 1

Output

Formatter

Y[9:0]

OEB

UV[9:0]

Luminance

Processing

Chrominance

Processing

M

U

X

VBI

I2C Interface

D[7:0]

VC0

VC3

A0

A1

VC1

VC2

Parallel Host

Interface

XTAL1

SCLK

PCLK

PREF

GLCO

Line

and

Chroma

PLLs

XTAL2

Sync

Processor

HSYN

VSYN

FID

PALI

GPCL

RSTINB

1–4

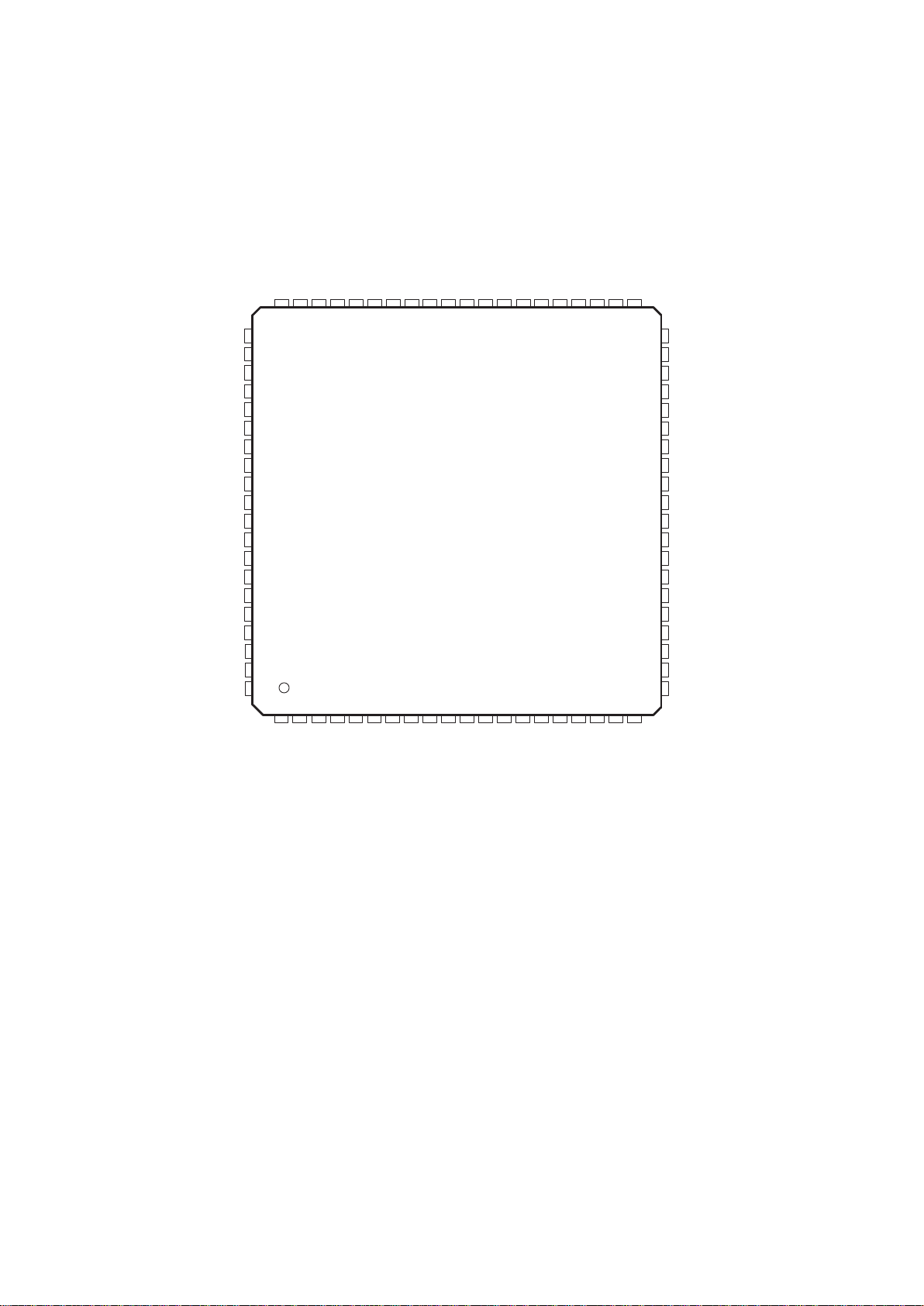

1.4 Terminal Assignments

23

Y1

Y0

GPCL

DGND

XTAL2

XTAL1

DV

DD

FID

PALI

GLCO

HSYN

VSYN

AVID

PCLK

PREF

SCLK

OEB

RSTINB

RSTOUTB

TESTE

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

4

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

UV8

UV9

D0

D1

DV

DD

D2

D3

DGND

D4

D5

D6

D7

A0

A1

DV

DD

VC3

VC2

VC1

VC0

INTREQ

5678

TQFP PACKAGE

(TOP VIEW)

59 58 57 56 5560 54 52 51 5053

9 10 11 12 13

49 48147 46 45 44

14 15 16 17 18 19 20

43 42 41

UV7

UV6

UV5

DGND

UV4

UV3DVUV2

UV1

UV0Y9Y8Y7DGNDY6Y5

Y4Y3Y2

BG

CLAMP1

AGND

VI_1B

VI_1A

DD

REFM

REFP

NC

NC

AGND

CLAMP2

NC

NC

AFE_GND

NSUB

PLL_AGND

AV

DD

AV

DD

AFE_V

DD

PLL_AV

DD

DV

DD

1.5 Ordering Information

DEVICE: TVP5031CPFP

PFP: Plastic flat-pack with PowerPAD

PowerPAD is a trademark of Texas Instruments.

1–5

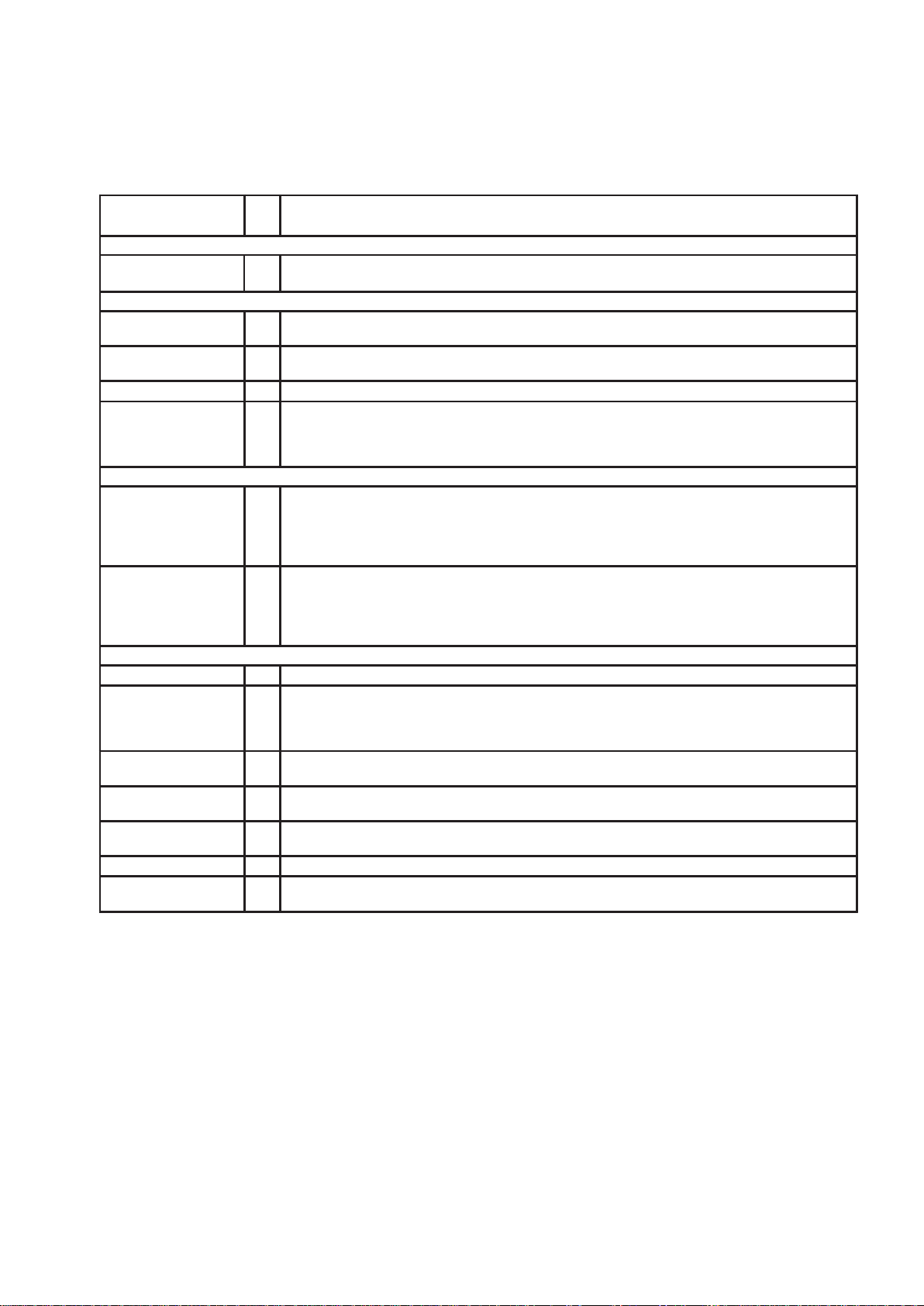

1.6 Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

Analog Video

VI_1A

VI_1B

5

4

I Analog video inputs. Up to two composite inputs. The inputs must be AC coupled. The recommended coupling

is 0.1 µF

Clock Signals

PCLK 27 O Pixel clock output. The frequency is 12.2727 MHz for square-pixel NTSC, 14.75 MHz for square-pixel P AL,

and 13.5 MHz for ITU-R.BT.601 sampling modes.

PREF 26 I/O Clock phase reference signal. This signal qualifies clock edges when SCLK is used to clock data that is

changing at the pixel clock rate.

SCLK 25 O System clock output with twice the frequency of the pixel clock (PCLK).

XTAL1

XTAL2

35

36

I External clock reference. The user may connect XTAL1 to a TTL-compatible oscillator or to one terminal of

a crystal oscillator. The user may connect XT AL2 to the other terminal of the crystal oscillator or not connect

XTAL2 at all. One single 14.31818 MHz crystal or oscillator is needed for square pixel sampling and ITU-R

BT .601 sampling.

Digital Video

UV[9:0] 62, 61,

60, 59,

58, 56,

55, 53,

52, 51

I/O 10-bit digital chrominance outputs. These terminals may also be configured to output the data from the

channel 2 A/D converter.

Y[9:0] 50, 49,

48, 46,

45, 43,

42, 41,

40, 39

I/O 10-bit digital luminance outputs, or 10-bit multiplexed luminance and chrominance outputs. These terminals

may also be configured to output the data from the channel 1 A/D converter.

Host Port-Bus

A[1:0] 74, 73 I PHI mode: PHI address port.

D[7:0] 72, 71,

70, 69,

67, 66,

64, 63

I/O PHI mode: PHI data port-bit [7:0].

INTREQ 80 I/O PHI mode: Interrupt Request (INTREQ). Pullup is required if configured as open drain.

I2C mode: Interrupt Request (INTREQ). Pullup is required if configured as open drain.

VC0 79 I/O PHI mode: PHI port data acknowledgement or ready signal (DTACK)

I2C mode: Serial clock (SCL) pullup is required.

VC1 78 I/O PHI mode: PHI port read-write or write (RW/WR)

I2C mode: Serial data (SDA) pullup is required.

VC2 77 I/O PHI mode: PHI port data strobe or read signal (DS/RD)

VC3 76 I PHI mode: PHI port chip select (VC)

I2C mode: Slave address select (I2CA)

1–6

1.6 Terminal Functions (Continued)

TERMINAL

NAME NO.

I/O

DESCRIPTION

Miscellaneous Signals

RSTOUTB 22 O Reset output, active low

RSTINB 23 I Reset input, active low

OEB 24 I/O Output enable for Y and UV terminals. Output enable is also controllable via the host port. When this terminal

is a logic 1 forces Y and UV output terminals to high impedance states (active low).

GLCO 31 I/O This serial output carries color PLL information. A slave device can decode the information to allow chroma

frequency control by the TVP5031. Data is transmitted at the SCLK rate. Additionally, this terminal, in

conjunction with PALI and FID, is used to determine the host port mode configuration during initial powerup.

GPCL 38 I/O General-purpose control logic. This terminal has three functions:

1) General-purpose output. In this mode the state of GPCL is directly programmed via the host port.

2) Vertical blank output. In this mode the GPCL terminal is used to indicate the vertical blanking interval

of the output video. The beginning and end times of this signal are programmable via the host port.

3) Sync lock control input. In this mode when GPCL is high, the output clock frequencies and the sync timing

are forced to nominal values.

CLAMP1,

CLAMP2

2,

13

O Clamp voltage outputs. Connect a 0.1 µF decoupling capacitor from each terminal to AGND.

NC 10, 11, 14,

15

No connection

BG 1 O Connect a 1.0-µF capacitor from this terminal to AGND.

Power Supplies

AFE_V

DD

18 Analog supply. Connect to 3.3-V analog supply

AFE_GND 16 Analog ground

AGND 3, 12 Analog grounds

AV

DD

6, 9 Analog supply. Connect to 3.3-V analog supply

DGND 37, 47, 57,

68

Digital grounds

PLL_AGND 20 PLL ground. Connect to analog ground

PLL_AV

DD

19 PLL supply. Connect to 3.3-V analog supply

DV

DD

34, 44, 54,

65, 75

Digital supply. Connect to 3.3-V

NSUB 17 Substrate ground. Connect to analog ground

REFP 8 O

A/D reference supply. Connect a 4.7-µF capacitor from each terminal to AGND. Connect a 1.0-µF capacitor

REFM 7 O

across the REFM and REFP terminals.

Sync Signals

AVID 28 I/O Active video indicator. This signal is high during the horizontal active time of the video output on the Y and

UV terminals. AVID continues to toggle during vertical blanking intervals.

This terminal may be placed in a high-impedance state. During reset, AVID is an input, used to program the

behavior of Y[9:0], UV[9:0], HSYN, VSYN, A VID and FID immediately after the completion of reset. If A VID

is pulled up during reset, Y[9:0], UV[9:0], HSYN, VSYN, AVID, PALI and FID will be actively driving after

reset. If AVID is pulled down during reset, Y[9:0], UV[9:0], HSYN, VSYN, AVID, PALI and FID will remain

in high-impedance state after reset.

FID 33 I/O Odd/even field indicator or vertical lock indicator. For odd/even indicator, a logic 1 indicates the odd field.

For vertical lock indicator, a logic 1 indicates the internal vertical PLL is in a locked state. Additionally, this

terminal in conjunction with GLCO and P ALI is used to determine the host port configuration during initial

power up and reset.

1–7

1.6 Terminal Functions (Continued)

TERMINAL

NAME NO.

I/O

DESCRIPTION

Sync Signals (Continued)

PALI 32 I/O PAL line indicator or horizontal lock indicator.

For PAL line indicator, a logic 1 indicates a noninverted line, and a logic 0 indicates an inverted line. For

horizontal lock indicator, a logic 1 indicates the internal horizontal PLL is in a locked state.

This terminal is an input terminal during reset and is used in conjunction with GLCO and FID to select the

mode of the host interface. During reset, this terminal can be pulled up to set a 1, or pulled down to set a 0.

VSYN 29 O Vertical sync signal

1.7 Strapping Terminals Description

All of the following terminals have reset strapping options. The states of these terminals are sampled during reset

to configure TVP5031 for various modes of operation. These terminals are temporarily turned into inputs with weak

internal pulldowns (~40 kΩ resistor) during reset and return to their normal operation after reset. Each of the following

terminals can be pulled up with a 10-KΩ resistor to set a 1 to the corresponding bit or be left undriven during reset,

relying on the internal pulldown resistor to pull the terminal low to set a 0 to the corresponding bit.

TERMINAL

NAME NO.

DESCRIPTION

AVID 28 Y , U/V output enable (bit 4) and HSYN, VSYN, AVID, FID, and PALI output enable (bit 3) of miscellaneous

control ( Register 03)

PREF 26 Clock enable bit (bit 0) of miscellaneous control ( Register 03)

FID 33 Host interface mode (see Table 2-2).

PALI 32 Host interface mode (see Table 2-2).

GLCO 31 Host interface mode (see Table 2-2).

1–8

2–1

2 Functional Description

2.1 Analog Video Processing and A/D Converters

Figure 2–1 shows a functional diagram of the analog video preprocessor and A/D converter. This block provides the

analog interface to all the video inputs. It accepts up to two inputs and performs source selection, video clamping,

video amplification, analog-to-digital conversion, and fine gain and offset adjustments to center the digitized video

signal.

M

U

X

VI_1A

CH1_MUX_CTRL

0.1 µF

VI_1B

0.1 µF

CLAMP

CH1_CLAMP_MODE

BANDGAP

– +

+–

AGC

CH1_GAIN_OFFSET

FINE GAIN,

OFFSET

ADJUST

ADC

CLK

+

–

9

BITS

CH1_FINE_ADJUST

9

BITS

CH1_OUT

–

+

ADC REF

BUFFER

CLAMP

BUFFER

1.0 µF

0.1 µF

0.1 µF

4.7 µF

4.7 µF

1.0 µF

CLAMP1

BG

CLAMP2

REFP

REFM

TVP5031 ANALOG FRONT END

SCLK

Figure 2–1. Analog Video Processors and A/D Converters

2.1.1 Video Input Selection

The TVP5031 has one analog channel that accepts two video inputs ac coupled through 0.1 µF capacitors. The

internal video multiplexers can be configured via the host port. The two analog video inputs may be connected as

two selectable individual composite video inputs.

2–2

2.1.2 Analog Input Clamping and Automatic Gain Control Circuits

An internal clamping circuit restores the ac coupled video signal to a fixed dc level. The clamping circuit provides

line-by-line restoration of the video sync level to a fixed dc reference voltage. Two modes of clamping are provided,

coarse and fine. In coarse mode, the most negative portion of the input signal (typically the sync tip) is clamped to

a fixed dc level. Fine clamp mode may be enabled to prevent spurious level shifting caused by noise more negative

than the sync tip on the input signal. If fine clamp mode is selected, clamping is only enabled during the sync period.

S-video requires fine clamp mode on the chroma channel for proper operation. External capacitors of 0.1 µF on

terminal CLAMP1 and CLAMP2 are required to store and filter the clamp voltage.

Input video signal amplitude may vary significantly from the nominal level of 1V

pp

. An automatic gain control circuit

(AGC) adjusts the signal amplitude to utilize the maximum range of the A/D converter without clipping. The AGC

adjusts gain to achieve desired sync amplitude. Some nonstandard video signals contain peak white levels that

saturate the A/D converter. In these cases, AGC automatically cuts back gain to avoid clipping.

In the digital data path, scaling is applied to the A/D output data to reach CCIR601 Y, Cr, Cb levels. This scaling

introduces distortion if digitized sync tip and back porch levels are not precise. The fine gain and offset adjustment

block precisely controls the sync tip and back porch levels to achieve best linearity performance.

2.1.3 A/D Converter

The TVP5031 contains one 9-bit oversampling A/D converter that digitizes the analog video inputs. As the input is

digitized at greater than two times the Nyquist sampling rate, only a simple external antialiasing low pass filter is

needed to prevent out-of-band frequencies. A/D converter reference voltages on terminals REFP and REFM require

an external capacitor network for filtering, as shown in Figure 2–1.

2–3

2.2 Digital Processing

Figure 2–2 is a block diagram of the TVP5031 digital video decoder processing. This block receives digitized

composite video signal from the A/D converter and performs Y/C separation, and Y , U/V signal enhancements. It also

generates horizontal and vertical syncs. The Y U/V digital output may be programmed into various formats: 20-bit,

16-bit, 10-bit or 8-bit 4:2:2, and 10-bit or 8-bit ITU-R BT .656 parallel interface standard. This block also retrieves VBI

data and stores it in a FIFO. The data from the FIFO can be read either through the host port or output as ancillary

data on the video port.

OUTPUT

FORMATTER

Y[9:0]

OEB

UV[9:0]

GAIN

CH1 A/D

DECIMATION

FILTER

COMPOSITE

ANALOG

PROCESSOR

CONTROL

CLAMP CTRL

INPUT MUX

FINE CTRL

Y/C SEPARATION

LUMA/CHROMA

PROCESSING

VBI DATA

SLICER

AVID

SYNCHRONIZATION

VSYN

HSYN

PALI

FID

GLCO

HOST

PORT

INTREQ

D[7:0]

VC[3:0]

VBI DATA BYPASS

Y

U/V

XTAL1

CLOCK SIGNAL

GENERATION

XTAL2

SCLK

PREF

PCLK

POWER UP

CONTROL

TVP5031 DIGITAL PROCESSING

RSTINB

RSTOUTB

A[1:0]

Figure 2–2. Digital Video Signal Processing Block Diagram

2–4

2.2.1 Decimation Filter

Digitized composite video at 2x PCLK rate first passes through the decimation filter that reduces the data rate from

2x to 1x PCLK. The decimation filter is a half-band filter whose frequency response is shown in Figure 2–3. For

applications that cannot tolerate high frequency rolloff, the decimation filter can be bypassed the host port. 2x

oversampling and decimation filtering can effectively increase the overall signal-to-noise ratio by 3 dB. This

advantage is lost if decimation filtering is bypassed.

f – Frequency – MHz

–60

–50

–40

–30

–20

–10

0

10

012345678

PAL SQP –3 dB at 6.66 MHz

CCIR 601 –3 dB at 6.10 MHz

NTSC SQP –3 dB at 5.54 MHz

Amplitude – dB

Figure 2–3. Decimation Filter Frequency Response

2–5

2.2.2 Y/C Separation

Figure 2–4 illustrates the luminance/chrominance (Y/C) separation process in the TVP5031. The 9-bit composite

video is multiplied by subcarrier signals in the quadrature demodulator to generate color difference signals U and V .

U and V are then low-pass filtered to achieve the desired bandwidth. An adaptive 3-line comb filter separates UV from

Y based on the unique property of color phase shift from line to line. Chroma is remodulated through a quadrature

modulator and subtracted from line-delayed composite video to generate luma. This form of Y/C separation is

completely complementary , thus there is no loss of information. However in some applications, it is desirable to limit

the U/V bandwidth to avoid crosstalk. In that case, notch filters can be turned on. To accommodate some viewing

preferences, a peaking filter is also available in the luma path. Contrast, brightness, hue, and saturation are

programmable.

Line

Delay

TVP5031 Y/C SEPARATION

– Peaking

Quadrature

Modulation

Composite

Quadrature

Demodulation

Subcarrier

Generation

Notch

Filter

Color

LPF

Burst

Accum

3-Line

Adaptive

Comb

Filter

Color

LPF

Burst

Accum

Notch

Filter

Notch

Filter

Notch

Filter

To

Sync Block

Delay

Contrast

Brightness

Saturation

Control

Delay

V

Y

U

UV

Y

Figure 2–4. Y/C Separation Block Diagram

2–6

2.2.2.1 Color Low-Pass Filter

Color low-pass filter frequency responses are shown in Figures 2–5 to 2–8. High filter bandwidth preserves sharp

color transitions and produces crisp color boundaries. However for nonstandard video sources that have

asymmetrical U and V side bands, it is desirable to limit the filter bandwidth to avoid UV crosstalk. Color low-pass

filter bandwidth is programmable by enabling one of the three notch filters.

f – Frequency – MHz

–70

–60

–50

–40

–30

–20

–10

0

10

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

PAL SQP –3 dB

@ 1.33 MHz

NTSC SQP –3 dB

@ 1.11 MHz

CCIR 601 –3 dB

@ 1.22 MHz

Amplitude – dB

Figure 2–5. Color Low-Pass Filter Frequency

Response

f – Frequency – MHz

–70

–60

–50

–40

–30

–20

–10

0

10

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

Amplitude – dB

No Notch Filter

–3 dB @ 1.11 MHz

Notch1 Filter –3

dB @ 798 kHz

Notch3 Filter –3

dB @ 454 kHz

Notch2 Filter –3

dB @ 664 kHz

Figure 2–6. Color Low-Pass Filter With Notch

Filter Frequency Response

(NTSC and PAL-M Square Pixel Sampling)

f – Frequency – MHz

–70

–60

–50

–40

–30

–20

–10

0

10

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

Amplitude – dB

No Notch Filter

–3 dB @ 1.22 MHz

Notch3 Filter –3

dB @ 499 kHz

Notch2 Filter –3

dB @ 730 kHz

Notch1 Filter –3

dB @ 878 kHz

Figure 2–7. Color Low-Pass Filter With Notch

Filter Characteristics (13.5 MHz Sampling)

f – Frequency – MHz

–70

–60

–50

–40

–30

–20

–10

0

10

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

Amplitude – dB

No Notch Filter

–3 dB @ 1.33 MHz

Notch3 Filter –3

dB @ 545 kHz

Notch2 Filter –3

dB @ 798 kHz

Notch1

Filter –3 dB

@ 959 kHz

Figure 2–8. Color Low-Pass Filter With

Notch Filter Frequency Response (PAL

Square Pixel Sampling)

2–7

2.2.2.2 Adaptive Comb Filter

Y/C separation may be done using adaptive 3-line (2-H delay), fixed 3-line, fixed 2-line comb filters, or a chroma trap

filter as shown in Figure 2–9. Adaptive comb filtering is available for both luminance and chrominance. The adaptive

comb filter algorithm computes the vertical and horizontal contours of color based on a block of 3×3 pixels. If there

is a sharp color transition, comb filtering is applied to the two lines that have less color changes. If there is no color

transition, 3-line comb filtering is used with a choice of filter coefficients [1/4, 1/2, 1/4] or [1/2, 0, 1/2] programmable

via the host port. Characteristics of 2-line and 3-line comb filters are shown in Figure 2–10. The filter frequency plots

show that both 2-line and 3-line (with filter coefficients [1/4,1/2,1/4]) comb filters have zeros at 1/2 of the horizontal

line frequency to separate the interleaved Y/C spectrum in NTSC. The 3-line comb filter has less cross-luma and

cross-chroma noise due to slightly sharper filter cut off. The 3-line comb filter with filter coefficients[1/2, 0, 1/2] has

two zeros at 1/4 and 3/4 of the horizontal line frequency . This should be used for P AL only because of its 90 degrees

U/V phase shifting from line to line. The comb filter can be selectively bypassed in the luma or chroma path. If the

comb filter is bypassed in the luma path, then chroma trap filters are used which are shown in Figures 2–1 1 to 2–13.

TI’s patented adaptive comb filter algorithm reduces artifacts such as hanging dots at color boundary and detects

and properly handles false colors in high frequency luminance images such as a multiburst pattern or circle pattern.

Adaptive comb filtering is the recommended mode of operation.

Line

Delay

ADAPTIVE COMB FIL TER

IN

Luma

Comb

Adaptive Comb

Filter Algorithm

>> 1

+

>> 1

>> 1

+

Line

Delay

>> 1 >> 1

++

Comb12

Comb123

Comb23

Comb13

Comb Bypass

Chroma

Comb

Filter Select

Comb_EN

Adap_EN

Figure 2–9. 3-Line Adaptive Comb Filtering

2–8

Figure 2–10. Comb Filters Frequency Response

f – Frequency – MHz

–40

–35

–30

–25

–20

–15

–10

–5

0

5

10

01234567

No Notch Filter

Notch3 Filter

Notch1 Filter

Notch2 Filter

Figure 2–11. Chroma Trap Filter

Frequency Response

Amplitude – dB

f – Frequency – MHz

–60

–50

–40

–30

–20

–10

0

10

012345678

A

mp

li

tu

d

e –

dB

0.5, 0, 0.5

0.5, 0.5, 0

0.25, 0.5, 0.25

f – Frequency – MHz

–40

–35

–30

–25

–20

–15

–10

–5

0

5

10

01234567

No Notch Filter

Notch3 Filter

Notch1 Filter

Notch2 Filter

Figure 2–12. Chroma Trap Filter Frequency

Response (13.5 MHz Sampling)

f – Frequency – MHz

–40

–35

–30

–25

–20

–15

–10

–5

0

5

10

01234567

No Notch Filter

Notch1 Filter

Notch2 Filter

Notch3 Filter

Amplitude – dB

Figure 2–13. Chroma Trap Filter Frequency

Response (PAL Square Pixel Sampling)

Amplitude – dB

2.2.3 Luminance Processing

The digitized composite video signal passes through either a luminance comb filter or a chroma trap filter, either of

which removes chrominance information from the composite signal to generate a luminance signal. The luminance

signal is then fed to the input of a peaking circuit. Figure 2–14 illustrates the basic functions of the luminance data

path. High frequency components of the luminance signal are enhanced by a peaking filter (edge-enhancer).

Figure 2–15, Figure 2–16, and Figure 2–17 show the characteristics of the peaking filter at four different gain settings

programmable via the host port.

2–9

BANDPASS

Filter

x

Gain

Peaking

Filter

IN

+

OUT

Delay

Figure 2–14. Luminance Edge-Enhancer Peaking Block Diagram

f – Frequency – MHz

–1

0

1

2

3

4

5

6

7

01234567

Gain = 0

Gain = 2

Gain = 1

Gain = 0.5

F = 2.40 MHz

Amplitude – dB

Figure 2–15. Peaking Filter Response, NTSC

and PAL-M Square Pixel Sampling

Figure 2–16. Peaking Filter Response,

13.5 MHz Sampling Rate

f – Frequency – MHz

–1

0

1

2

3

4

5

6

7

01234567

Gain = 0

Gain = 2

Gain = 1

Gain = 0.5

F = 2.64 MHz

Amplitude – dB

f – Frequency – MHz

–1

0

1

2

3

4

5

6

7

01234567

Gain = 0

Gain = 2

F = 2.89 MHz

Gain = 0.5

Gain = 1

Amplitude – dB

Figure 2–17. Peaking Filter Response, PAL Square Pixel

2–10

2.2.4 Chrominance Processing

A quadrature demodulator extracts U and V components from the composite signal. The U/V signals then pass

through the gain control stage for chroma saturation adjustment. A comb filter is applied to both U and V to eliminate

cross-chrominance noise. Hue control is achieved with phase shift of the digitally controlled oscillator. An automatic

color killer (ACK) circuit is also included in this block. The ACK will suppress the chroma processing when the color

burst of the video signal is weak or not present.

2.2.5 Clock Circuits

An internal line-locked PLL generates the system and pixel clocks. Figure 2–18 shows a simplified clock circuit

diagram. The digital control oscillator (DCO) generates the reference signal for the horizontal PLL. A 14.318 MHz

clock is required to drive the DCO. This may be input to the TVP5031 at TTL level on the XT AL1 terminal, or a crystal

of 14.318 MHz fundamental resonant frequency may be connected across terminals XT AL1 and XTAL2. Figure 2–19

shows the reference clock configurations. For the example crystal circuit shown in Figure 2–19 (a parallel-resonant

crystal with 14.31818 MHz fundamental frequency), the external capacitors should have the following relationship:

CL1 = CL2 = 2CL – C

stray

Where C

stray

is the terminal capacitance with respect to ground.

Lowpass Filter

Sync Detector

Digitized

Video

XTAL1

Phase

Detector

Loop

Filter

Digital

Control

Oscillator

XTAL2

Crystal

Clock

Generator

Clock

Generation

Circuit

Line-Locked

Clock

PLL

SCLK

PCLK

Figure 2–18. Clock Circuit Diagram

TVP5031

35

XTAL1

14.31818 MHz

Crystal

36

XTAL2

TVP5031

35

XTAL1

36

XTAL2

C

L1

C

L2

14.31818 MHz

TTL Clock

Figure 2–19. Example Reference Clock Configurations

The TVP5031 generates three signals PCLK, SCLK, and PREF used for clocking data. PCLK, the pixel clock, can

be used for clocking data in the 20-bit and 16-bit 4:2:2 output formats. SCLK is twice the PCLK frequency and may

be used for clocking data in the 10-bit and 8-bit 4:2:2 as well as in ITU-R BT.656 formats. PREF is used as a clock

qualifier with SCLK to clock data in the 20-bit and 16-bit 4:2:2 formats.

Loading...

Loading...