www.ti.com

1

FEATURES

23

• USB On-the-Go (OTG) Controller Core • Integrated USB 2.0 OTG PHY

USB 2.0 HIGH-SPEED ON-THE-GO DUAL-ROLE CONTROLLER

SCPS170E – JANUARY 2007 – REVISED MARCH 2008

– Uses Mentor Graphics USB 2.0 OTG Core – Fully Compliant with USB 2.0 Standard and

– Dual-Role Controller Can Operate Either as

a Function Controller for a USB Peripheral

USB 2.0 Transceiver Macrocell Interface

(UTMI) Revision 1.05

or as the Host/Peripheral in Point-to-Point – Optimized One-Port Operation at Low

or Multipoint Communications With Other Speed (1.5 Mbps), Full Speed (12 Mbps),

USB Functions and High Speed (480 Mbps)

– Compliant With the USB 2.0 Standard for – Supports UTMI+3 Level 3 (Host and OTG

High-Speed (480-Mbps) Functions and With Devices, High/Full/Low Speed and

OTG Supplement to USB 2.0 Specification Preamble Packet)

– Supports OTG Communications With One – Protection Circuitry to Withstand Possible

or More High-, Full-, or Low-Speed Devices VBUS Short

– Supports Session Request Protocol (SRP) – Use 19.200-MHz or 24.000-MHz Reference

and Host Negotiation Protocol (HNP) Clock Input as a Crystal or External Clock

– Supports Suspend-and-Resume Signaling

– Configurable for up to 4 Transmit

Endpoints or up to 4 Receive Endpoints

– Configurable FIFOs, Including the Option of

Dynamic FIFO Sizing

– 16k-Byte RAM for USB Endpoint FIFO

Shared by USB In/Out Endpoints

– Support for External Direct Memory Access

(DMA) to FIFOs

– Soft Connect/Disconnect Option

– Performs All Transaction Scheduling in

Hardware

• System Control Module

– Controls Clock and Reset Generation and

Distribution

– Controls and Observes Device Power

States

– Supports External Power Management

Driver

– At-Speed Built-In Self Test (BIST) With

Internal Asynchronous Capability Through

Loopback

– On-Chip Integrated Accurate 45- Ω

High-Speed Termination, 1.5-k Ω Pullup, and

15-k Ω Pulldown Resistors

– On-Chip Phase-Locked Loop (PLL) to

Reduce Noise on High-Speed Clocks

– Active Power Consumption Less Than

100 mW

• VLYNQ 2.0 Interface to External Host

Controller

– High-Speed (150-MHz) Point-to-Point Serial

Interface for Direct Connection to Other

VLYNQ Interface

– Supports 4 Receive (RX) and 4 Transmit

(TX) Lines

– Memory-Mapped Master/Slave

– Hardware Flow Control Internal Loopback

Mode

– Multichannel DMA Controller

– Integrated List Processor Capable of

Parsing Communications Port

Programming Interface (CPPI)

3.0-Compliant Buffer Descriptors

• High-Performance 80-Pin

MicroStar BGA™/ MicroStar Junior™

ZQE Package

• High-Performance 80-Pin PFC Package

TUSB6020

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2 MicroStar BGA, MicroStar Junior are trademarks of Texas Instruments.

3 All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2007 – 2008, Texas Instruments Incorporated

www.ti.com

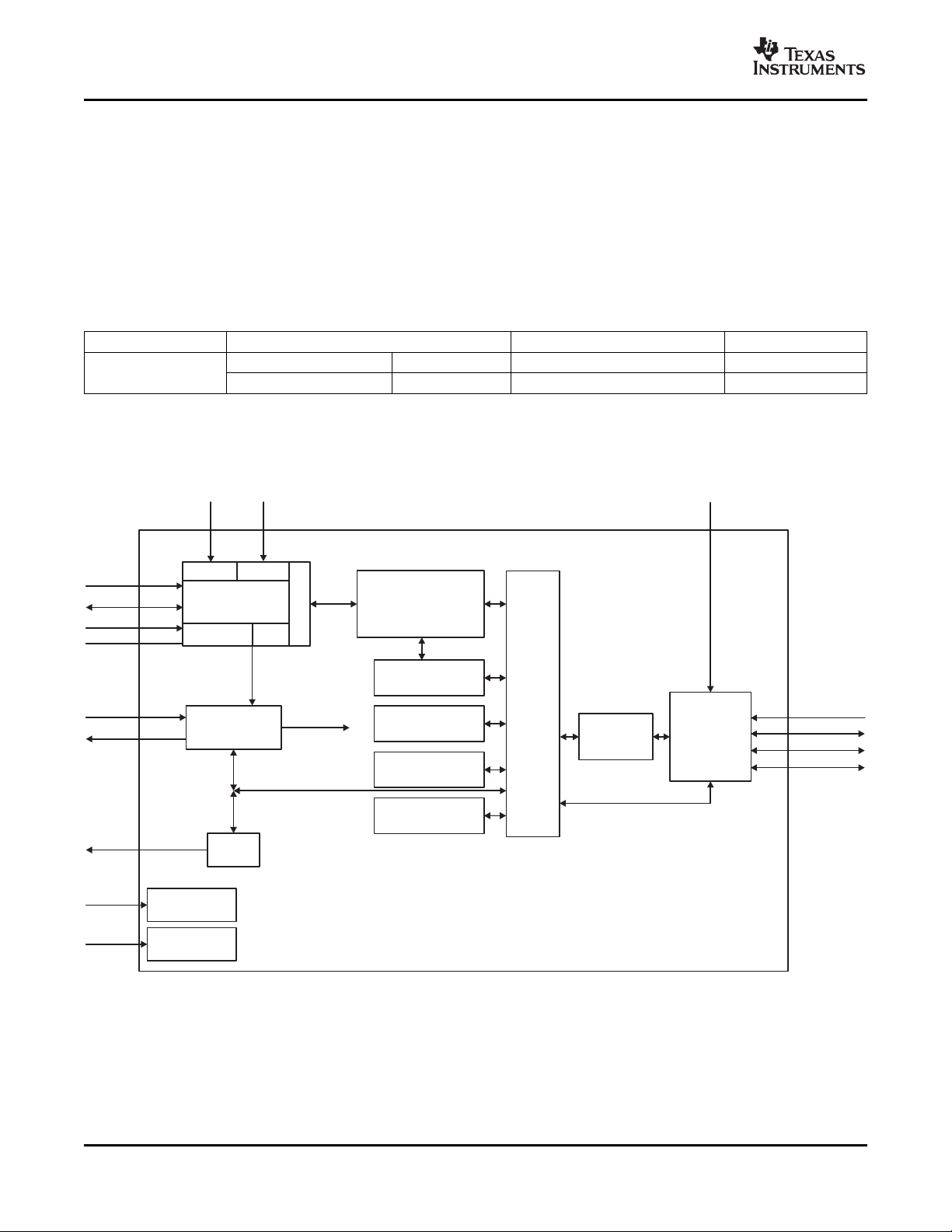

8 bit

@ 60 MHz

Central

Resource

Switch

TUSB6020

3.3 V 1.5 V

sys_clk

Digital Core

Power Distribution

IO Power

Distribution

Power/Reset/Clock

Management

(PRCM)

GPIO

CPPI 3.0

DMA

3.3 V 1.5 V

USB 2.0

PHY Macro

OTG Analog PLL

UTMI+ Le

vel 3

USB 2.0 Dual Role OTG

Controller IP Core

USB EP Buffer RAM

(16k x 8)

DMA State RAM

(DMA FIFOs)

Interrupt

Controller

XFER RAM

1.8 V

1.5 V

GPIO

5 V VBus

ID

DP/DM

XI/CLKIN

RSTn

SLEEP

3.3 V

VLYNQ_CLK

VLYNQ_CLKRUN

VLYNQ_TXD[3:0]

VLYNQ_RXD[3:0]

VLYNQ

Interface

(Ext Host Interface)

TUSB6020

USB 2.0 HIGH-SPEED ON-THE-GO DUAL-ROLE CONTROLLER

SCPS170E – JANUARY 2007 – REVISED MARCH 2008

DESCRIPTION/ORDERING INFORMATION

The TUSB6020 is a USB 2.0 high-speed, on-the-go (OTG) dual-role controller designed for a seamless interface

to the VLYNQ serial interface, and is ideal for a wide range of applications. The USB OTG dual-role controller

can operate either as a function controller for a USB peripheral or as the host/peripheral in point-to-point or

multipoint communications with other functions. The integrated USB 2.0 PHY provides one-port operation at low

speed (1.5 Mbps), full speed (12 Mbps), and high speed (480 Mbps). The VLYNQ serial interface is a low pin

count, high-speed, point-to-point interface.

The device is fully compliant with Universal Serial Bus Specification Revision 2.0 and On-the-Go Supplement to

the USB Specification Revision 1.3.

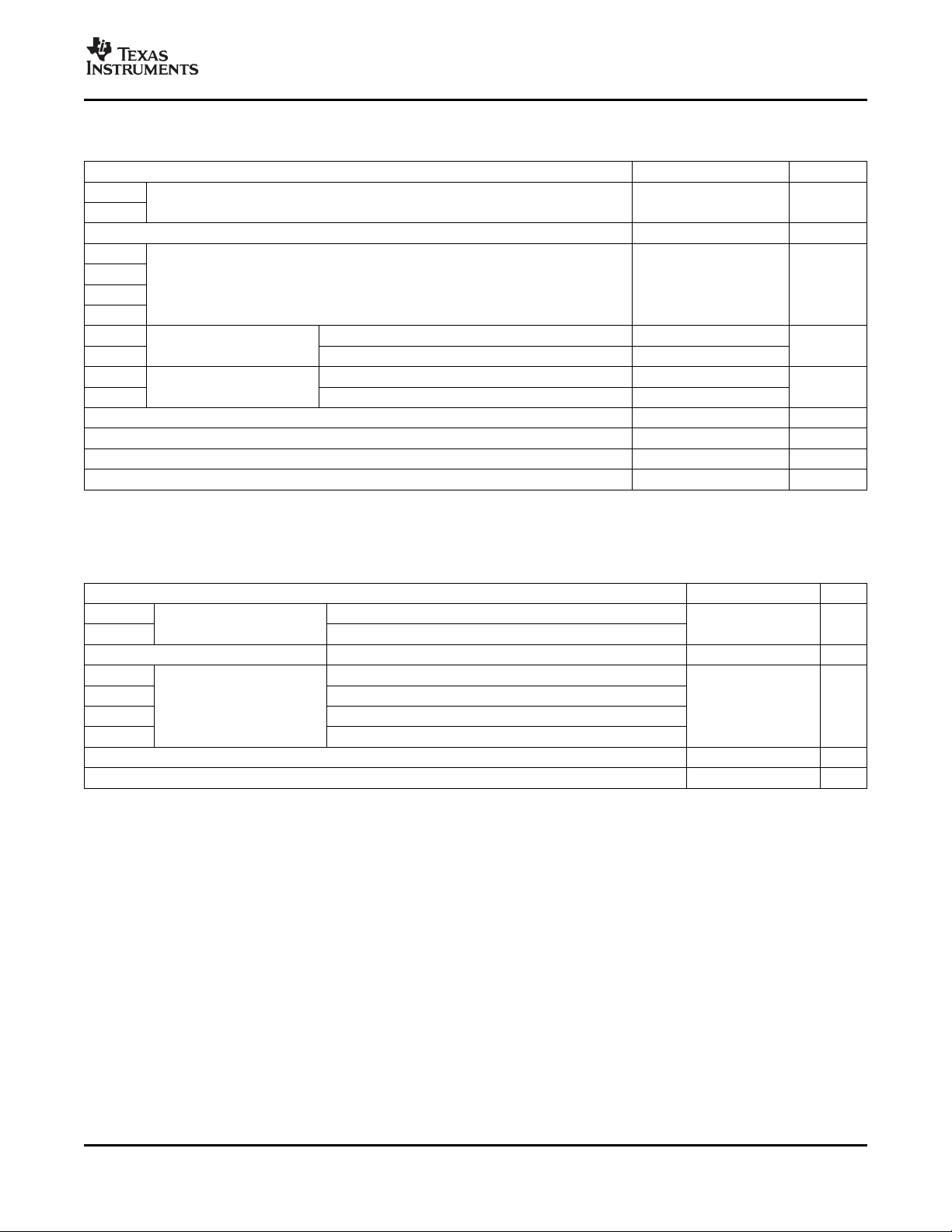

ORDERING INFORMATION

(1) (2)

ORDERABLE PART NUMBER TOP-SIDE MARKING

BLOCK DIAGRAM

0 ° C to 70 ° C

T

A

MicroStar BGA™ – ZQE Reel of 360 TUSB6020ZQE PREVIEW

TQFP – PFC Tube of 96 TUSB6020PFC PREVIEW

PACKAGE

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging .

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

website at www.ti.com .

2 Submit Documentation Feedback Copyright © 2007 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TUSB6020

www.ti.com

USB 2.0 HIGH-SPEED ON-THE-GO DUAL-ROLE CONTROLLER

SCPS170E – JANUARY 2007 – REVISED MARCH 2008

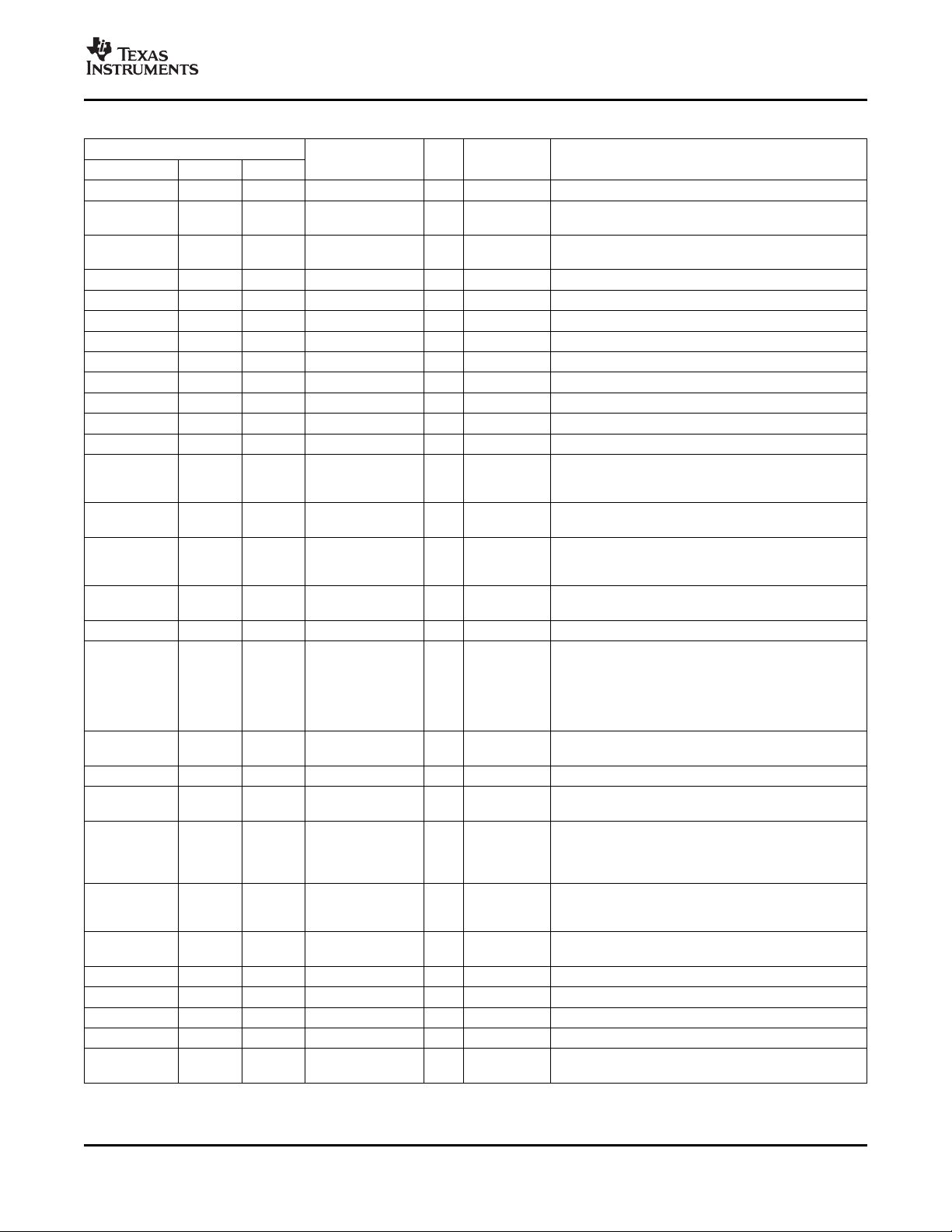

TERMINAL FUNCTIONS

TERMINAL

NAME ZQE NO. PFC NO.

1.5V_SWEN G2 18 LVCMOS O 0 Switch enable for 1.5-V LDO for VBAT/VBUS switch

3.3V_SWEN G3 19 LVCMOS O 0

CLKIN A5 71 I In

CPEN H2 22 LVCMOS O 0 5-V power distribution switch enable

DM E2 10 USB I/O – USB differential pair

DP D1 9 USB I/O – USB differential pair

GPIO0 H4 26 LVCMOS I/O In with pullup GPIO 0

GPIO1 D5 68 LVCMOS I/O In with pullup GPIO 1

GPIO2 B6 66 LVCMOS I/O In with pullup GPIO 2

GPIO3 E6 54 LVCMOS I/O In with pullup GPIO 3

GPIO4 C4 79 LVCMOS I/O In with pullup GPIO 4

GPIO5 C9 55 LVCMOS I In with pullup GPIO 5

GPIO6 F5 27 LVCMOS I/O In with pullup GPIO6 = HIGH, CLKIN is reference clock.

GPIO7 B2 2 LVCMOS I/O In with pullup

ID F2 15 USB I – information, see On-the-Go Supplement to the USB

R1 C2 5 Bias I –

RSTn H1 20 LVCMOS I In with pullup Reset active low

A8, B7, 64, 65,

B8, B9, 62, 58,

RSVD – – –

RSVD – NC – – – Reserved, should be left unconnected

SLEEP H3 24 LVCMOS O 0 OTG sleep

TEST D4 80 LVCMOS I –

VBUS F3 16 USB I –

VDD15 B3, C5, 56, 61, Supply – – Digital core power supply, 1.5 V

VDD18 Supply – – I/O power supply, 1.8 V

VDDA1P5 E3 11 Supply – – 1.5-V analog supply

VDDA3P3 C1 7 Supply – – 3.3-V analog supply

VDDCM1P5 D2 6 Supply – – 1.5-V PLL supply

VDDD1P5 F1 14 Supply – – 1.5-V digital supply

VDDS3P3 Supply – – VLYNQ supply, 3.3 V

C6, C7, 63, 60, Reserved, must be pulled low by individual pulldown

C8, D6, 57, 59, resistors. A 1-k Ω value is recommended.

D8, E7, 53, 50,

G4, J5 23, 31

G5, H5, 29, 30,

J4, F6 28, 32

A1, A9, 1, 25,

D7, J3 72, 77

A7, B5, 21, 49,

E8, J1 67, 70

F8, G6, 33, 39,

J9 44

TYPE I/O DESCRIPTION

LVCMOS 19.2-MHz system clock in. Connect directly to ground if

(1)

failsafe

RESET

STATE

Switch enable for 3.3-V CP/LDO for VBAT/VBUS

switch

not used.

GPIO 6. Input clock source select at reset.

GPIO6 = LOW, XI is reference clock.

GPIO 7. Must be pulled low for proper operation. It is

recommended to tie this signal directly to GND.

Indicates default master for OTG. For more

Specification, Revision 1.2.

High-precision external resistor used for calibration

(R1 value: 10.7 k Ω ± 1%)

Test mode. Under normal operation, this signal should

be tied directly to GND.

Charged, discharged, and monitored for OTG host

negotiation protocol and session request protocol.

External power distribution switch provides up to 500

mA.

TUSB6020

(1) Failsafe means that CLKIN can toggle when VDD18 is not present without damaging the part.

Copyright © 2007 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Link(s): TUSB6020

www.ti.com

TUSB6020

USB 2.0 HIGH-SPEED ON-THE-GO DUAL-ROLE CONTROLLER

SCPS170E – JANUARY 2007 – REVISED MARCH 2008

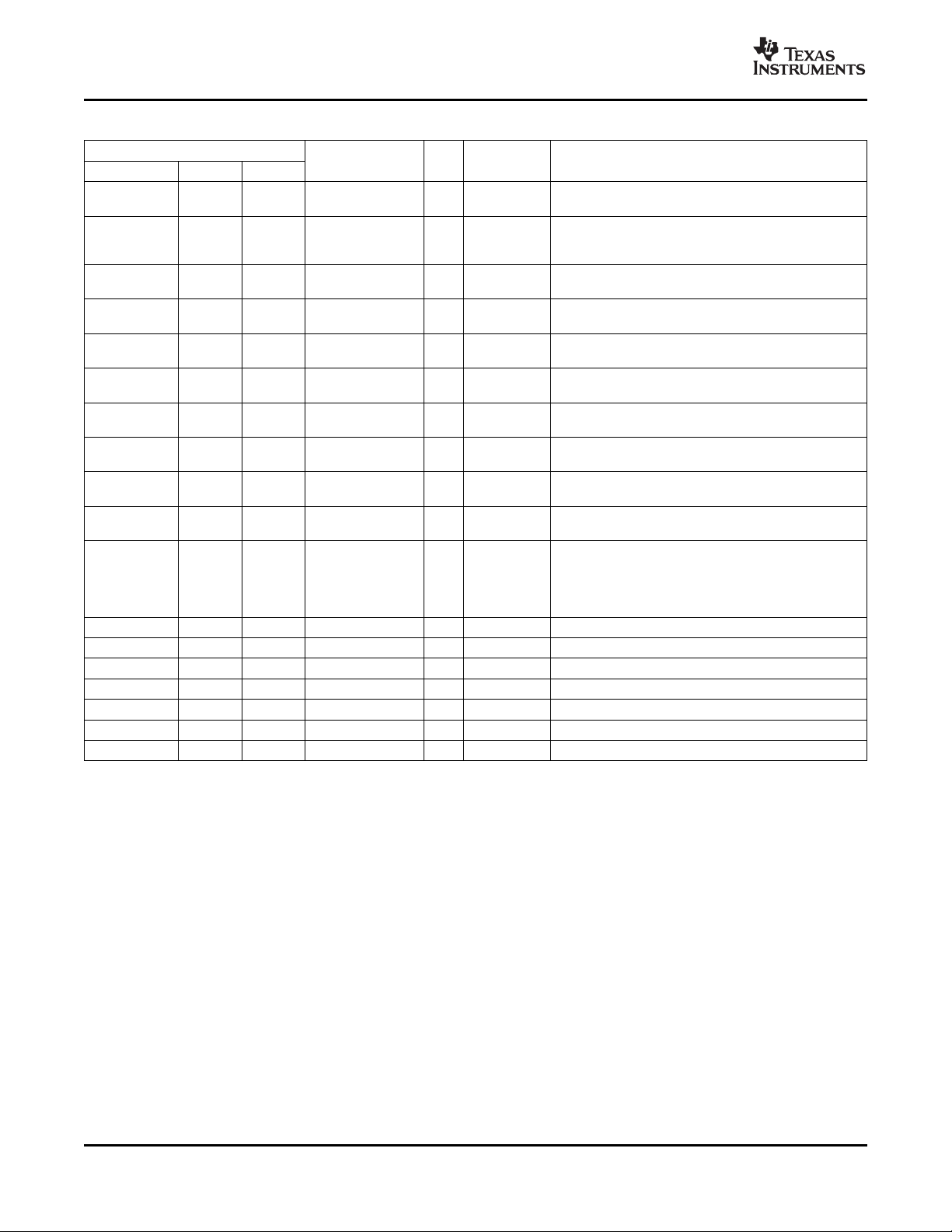

TERMINAL FUNCTIONS (continued)

TERMINAL

NAME ZQE NO. PFC NO.

VLYNQ_CLK F9 45 I In with pullup VLYNQ clock

VLYNQ_CRUN E9 48 3.3-V VLYNQ I/O In with pullup VLYNQ clock run

VLYNQ_RXD0 H7 38 I In with pullup VLYNQ receive data bit 0

VLYNQ_RXD1 J7 37 I In with pullup VLYNQ receive data bit 1

VLYNQ_RXD2 H6 35 I In with pullup VLYNQ receive data bit 2

VLYNQ_RXD3 J6 34 I In with pullup VLYNQ receive data bit 3

VLYNQ_TXD0 H9 40 O In with pullup VLYNQ transmit data bit 0

VLYNQ_TXD1 G9 42 O In with pullup VLYNQ transmit data bit 1

VLYNQ_TXD2 H8 43 O In with pullup VLYNQ transmit data bit 2

VLYNQ_TXD3 F7 47 O In with pullup VLYNQ transmit data bit 3

A2, A6, 17, 36,

B4, D9, 41, 46,

VSS E5, G1, 51, 52, Supply – – Ground

G7, G8, 69, 74,

J2, J8 76, 78

VSSA1P5 E1 12 Supply – – 1.5-V analog ground

VSSA3P3 E4 8 Supply – – 3.3-V analog ground

VSSCM1P5 D3 3 Supply – – 1.5-V PLL ground

VSSD1P5 F4 13 Supply – – 1.5-V digital ground

VSSREF B1 4 Supply – – Ground for the reference circuits

XI A4 73 Crystal I In Crystal input. Should be left unconnected if not used.

XO A3 75 Crystal O In Crystal output. Should be left unconnected if not used.

TYPE I/O DESCRIPTION

LVCMOS

3.3-V VLYNQ

LVCMOS

open drain

LVCMOS

3.3-V VLYNQ

LVCMOS

3.3-V VLYNQ

LVCMOS

3.3-V VLYNQ

LVCMOS

3.3-V VLYNQ

LVCMOS

3.3-V VLYNQ

LVCMOS

3.3-V VLYNQ

LVCMOS

3.3-V VLYNQ

LVCMOS

3.3-V VLYNQ

RESET

STATE

4 Submit Documentation Feedback Copyright © 2007 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TUSB6020

www.ti.com

USB 2.0 HIGH-SPEED ON-THE-GO DUAL-ROLE CONTROLLER

TUSB6020

SCPS170E – JANUARY 2007 – REVISED MARCH 2008

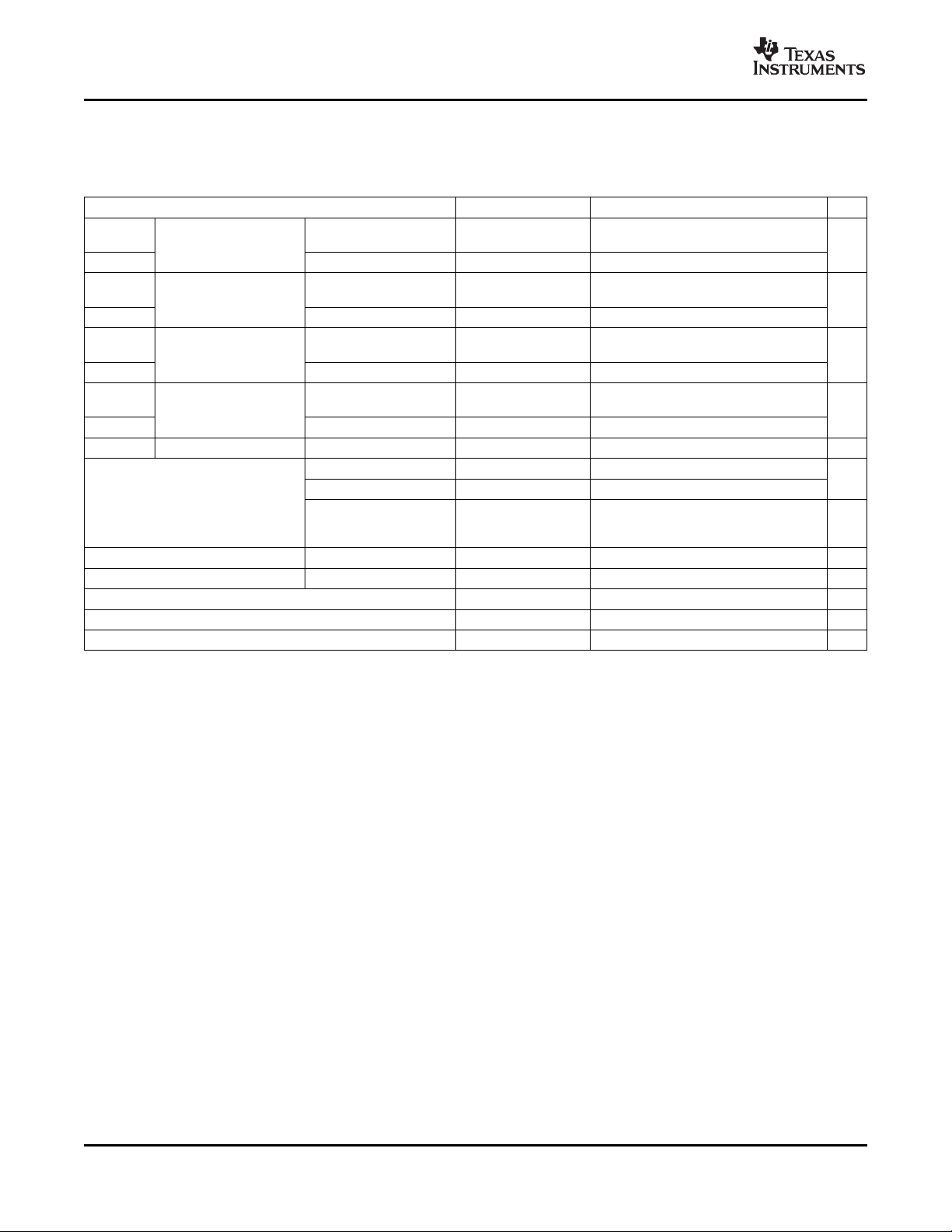

ABSOLUTE MAXIMUM RATINGS

(1)

over operating free-air temperature range (unless otherwise noted)

MIN MAX UNIT

V

DDA3P3

V

DDS3P3

V

DD18

V

DD15

V

DDD1P5

V

DDCM1P5

V

DDA1P5

V

I

V

I-VLYNQ

V

O

V

O-VLYNQ

V

DD

I

IK

I

OK

T

stg

3.3-V supply voltage – 0.5 4.2 V

1.8-V supply votlage – 0.5 2.1 V

1.5-V supply voltage – 0.5 2.1 V

Input voltage range V

Output voltage range V

3.3-V USB – 0.5 V

3.3-V VLYNQ – 0.5 V

3.3-V USB – 0.5 V

3.3-V VLYNQ – 0.5 V

+0.5

DDA3P3

+0.5

DDS3P3

+0.5

DDA3P3

+0.5

DDS3P3

Core supply voltage – 0.5 2.1 mA

Input clamp current ± 20 mA

Output clamp current ± 20 mA

Storage temperature range – 65 150 ° C

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

RECOMMENDED OPERATING CONDITIONS

MIN TYP MAX UNIT

V

DDA3P3

V

DDS3P3

V

DD18

V

DD15

V

DDD1P5

V

DDCM1P5

V

DDA1P5

T

A

T

J

Supply voltage 3 3.3 3.6 V

Supply voltage Digital I/O 1.62 1.8 1.98 V

Supply voltage 1.35 1.5 1.65 V

Operating temperature 0 70 ° C

Operating junction temperature 0 ° C

OTG PHY analog

VLYNQ digital

Digital core

OTG PHY digital

OTG PHY common module

OTG PHY analog

Copyright © 2007 – 2008, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Link(s): TUSB6020

www.ti.com

TUSB6020

USB 2.0 HIGH-SPEED ON-THE-GO DUAL-ROLE CONTROLLER

SCPS170E – JANUARY 2007 – REVISED MARCH 2008

DIGITAL I/O

Electrical Characteristics

TA= 0 ° C to 70 ° C, V

V

I-VLYNQ

V

I

V

O-VLYNQ

V

O

V

IH-VLYNQ

V

IH

V

IL-VLYNQ

V

IL

V

OH

V

OL

I

IH

I

IL

I

OZ

C

i

tr, t

f

Input voltage V

Output voltage V

High-level input voltage V

Low-level input voltage V

High-level output voltage LVCMOS 0.8 × V

Low-level output voltage

High-level input current LVCMOS VI= VImax ± 1 µ A

Low-level input current LVCMOS VI= VImin ± 1 µ A

Output leakage current (high Z) VI= VImax or V

Input capacitance 2 pF

Input rise/fall time 0 25 ns

= 1.8 V ± 10%, V

DD18

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

3.3-V LVCMOS

(VLYNQ only)

LVCMOS 0 V

3.3-V LVCMOS

(VLYNQ only)

LVCMOS 0 V

3.3-V LVCMOS

(VLYNQ only)

LVCMOS 0.7 × V

3.3-V LVCMOS

(VLYNQ only)

LVCMOS 0 0.3 × V

LVCMOS open drain IOL= 4 mA 0.22 × V

LVCMOS IOL= 8 mA 0.22 × V

LVCMOS

(1.5V_SWEN, IOL= 100 µ A 10 mV

3.3V_SWEN only)

DDS3P3

= 3.3 V ± 10%, V

= 0 V (unless otherwise noted)

SS

SS

0.7 × V

0 V

0 V

DDS3P3

DD18

0 0.3 × V

DD18

DDS3P3

DD18

DDS3P3

DD18

V

DDS3P3

V

DD18

DDS3P3

DD18

V

DDS3P3

V

DD18

± 20 µ A

6 Submit Documentation Feedback Copyright © 2007 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TUSB6020

Loading...

Loading...