Texas Instruments TPS77333DGKR, TPS77333DGK, TPS77328DGKR, TPS77328DGK, TPS77327DGKR Datasheet

...

TPS77301, TPS77318, TPS77327, TPS77328, TPS77333 WITH RESET OUTPUT

TPS77401, TPS77418, TPS77427, TPS77428, TPS77433 WITH POWER GOOD OUTPUT

250-mA LDO REGULATORS WITH INTEGRATED RESET OR PG

SLVS281A – FEBRUARY 2000 – REVISED MARCH 2000

D

Open Drain Power-On Reset With 220-ms

Delay (TPS773xx)

D

Open Drain Power-Good (PG) Status

Output (TPS774xx)

D

250-mA Low-Dropout Voltage Regulator

D

Available in 1.8-V, 2.7-V, 2.8-V, 3.3-V, Fixed

Output and Adjustable Versions

D

Dropout Voltage Typically 200 mV

at 250 mA (TPS77333, TPS77433)

D

Ultra Low 92-µA Quiescent Current (Typ)

D

8-Pin MSOP (DGK) Package

D

Low Noise (55 µV

) Without an External

rms

Filter (Bypass) Capacitor (TPS77318,

TPS77418)

D

2% Tolerance Over Specified Conditions

For Fixed-Output Versions

D

Fast Transient Response

D

Thermal Shutdown Protection

D

See the TPS779xx Family of Devices for

Active High Enable

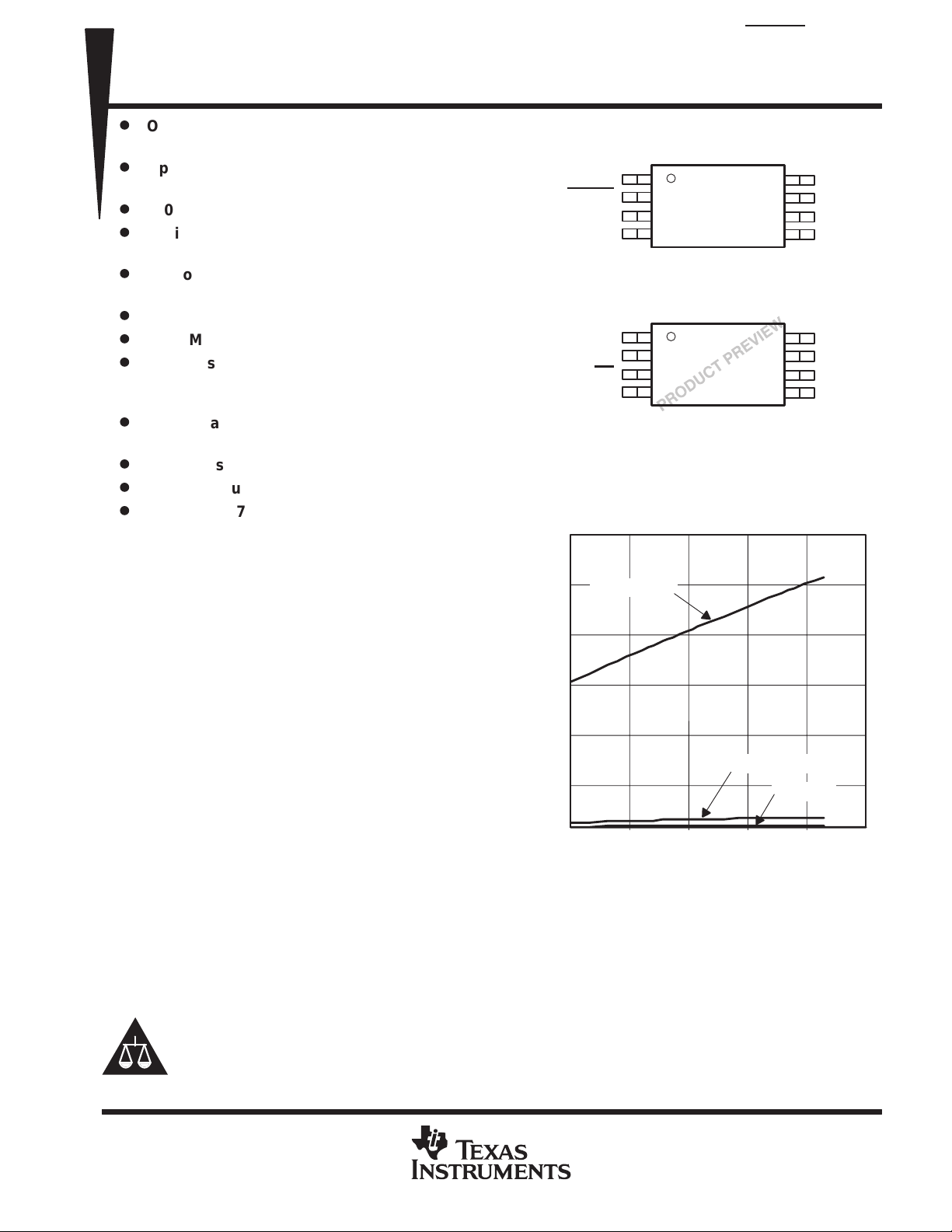

FB/SENSE

RESET

EN

GND

FB/SENSE

PG

EN

GND

300

TPS773xx

DGK PACKAGE

(TOP VIEW)

1

2

3

4

TPS774xx

DGK PACKAGE

(TOP VIEW)

1

2

3

4

TPS77x33

DROPOUT VOLTAGE

vs

JUNCTION TEMPERATURE

8

7

6

5

8

7

6

5

OUT

OUT

IN

IN

OUT

OUT

IN

IN

description

250

IO = 250 mA

The TPS773xx and TPS774xx are low dropout

regulators with integrated power-on reset and

power good (PG) function respectively. These

200

devices are capable of supplying 250 mA of output

current with a dropout of 200 mV (TPS77333,

150

TPS77433). Quiescent current is 92 µA at full load

dropping down to 1 µA when device is disabled.

– Dropout Voltage – mV

These devices are optimized to be stable with a

wide range of output capacitors including low ESR

ceramic (10 µF) or low capacitance (1 µF)

tantalum capacitors. These devices have extremely low noise output performance (55 µV

rms

without using any added filter capacitors.

TPS773xx and TPS774xx are designed to have

fast transient response for larger load current

)

100

DO

V

50

0

–40 0 40 80

TJ – Junction Temperature – °C

IO = 10 mA

IO = 0 A

changes.

The TPS773xx or TPS774xx is offered in 1.8-V, 2.7-V, 2.8-V and 3.3-V fixed-voltage versions and in an

adjustable version (programmable over the range of 1.5 V to 5.5 V). Output voltage tolerance is 2% over line,

load, and temperature ranges. The TPS773xx and TPS774xx families are available in 8-pin MSOP (DGK)

packages.

120 140

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This document contains information on products in more than one phase

of development. The status of each device is indicated on the page(s)

specifying its electrical characteristics.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 2000, Texas Instruments Incorporated

1

TPS77301, TPS77318, TPS77327, TPS77328, TPS77333 WITH RESET OUTPUT

J

–40 C to 125 C

TPS77401, TPS77418, TPS77427, TPS77428, TPS77433 WITH POWER GOOD OUTPUT

250-mA LDO REGULATORS WITH INTEGRATED RESET OR PG

SLVS281A – FEBRUARY 2000 – REVISED MARCH 2000

description (continued)

Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (typically 200 mV

at an output current of 250 mA for 3.3 volt option) and is directly proportional to the output current. Additionally ,

since the PMOS pass element is a voltage-driven device, the quiescent current is very low and independent

of output loading (typically 92 µA over the full range of output current, 0 mA to 250 mA). These two key

specifications yield a significant improvement in operating life for battery-powered systems.

The device is enabled when the EN

pin is connected to a low-level input voltage. This LDO family also features

a sleep mode; applying a TTL high signal to EN (enable) shuts down the regulator, reducing the quiescent

current to less than 1 µA at TJ = 25°C.

The TPS773xx features an integrated power-on reset, commonly used as an supply voltage supervisor (SVS),

or reset output voltage. The RESET output of the TPS773xx initiates a reset in DSP, microcomputer or

microprocessor systems at power-up and in the event of an undervoltage condition. An internal comparator in

the TPS773xx monitors the output voltage of the regulator to detect an undervoltage condition on the regulated

output voltage. When OUT

reaches 95% of its regulated voltage, RESET will go to a high-impedance state after

a 220 ms delay . RESET will go to low-impedance state when OUT is pulled below 95% (i.e. over load condition)

of its regulated voltage.

For the TPS774xx, the power good terminal (PG) is an active high output, which can be used to implement a

power-on reset or a low-battery indicator. An internal comparator in the TPS774xx monitors the output voltage

of the regulator to detect an undervoltage condition on the regulated output voltage. When OUT falls below 82%

of its regulated voltage, PG will go to a low-impedance state. PG will go to a high-impedance state when OUT

is above 82% of its regulated voltage.

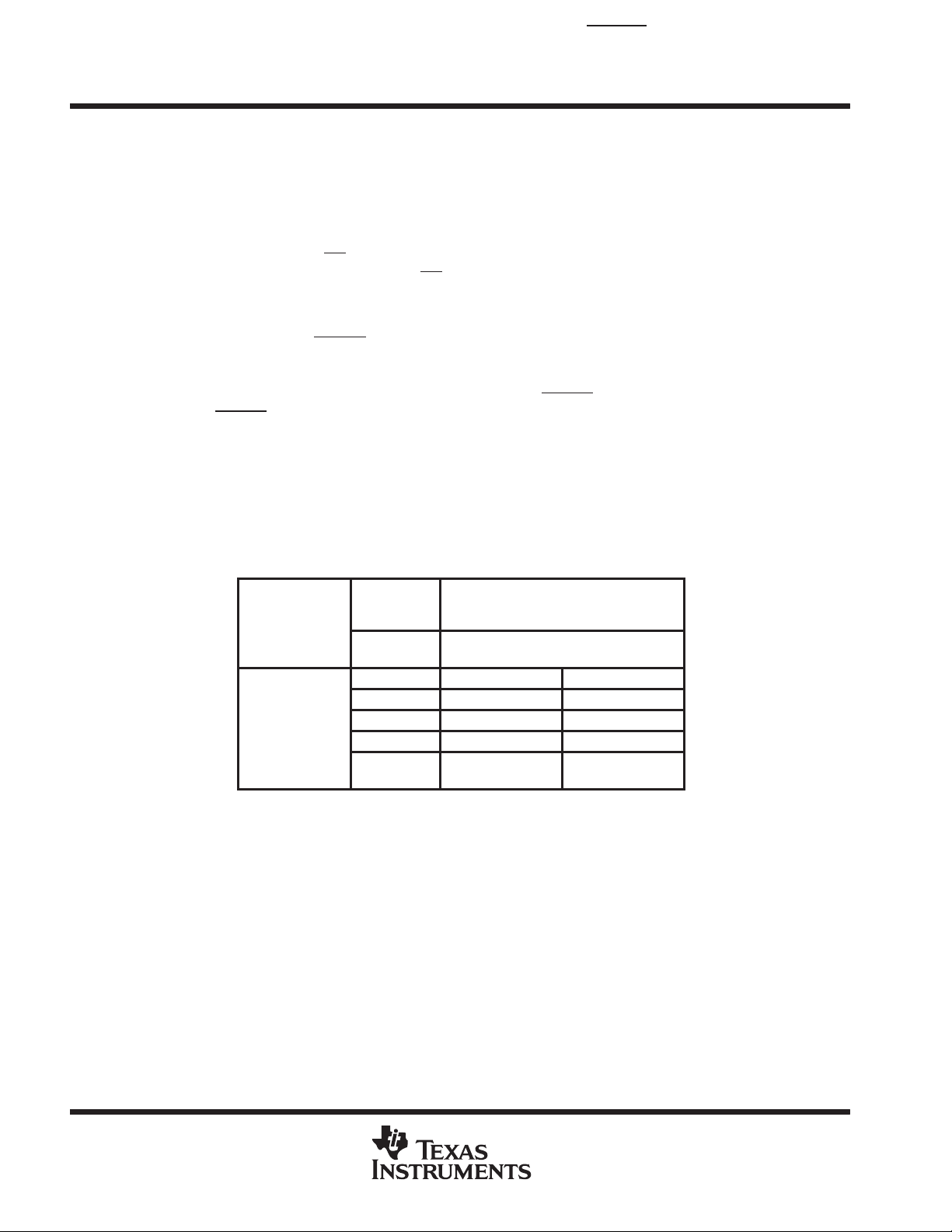

AVAILABLE OPTIONS

OUTPUT

VOLTAGE

T

–

°

The TPS77301 and TPS77401 are programmable using an external resistor divider

(see application information). The DGK package is available taped and reeled. Add

an R suffix to the device type (e.g., TPS77301DGKR).

°

(V)

TYP

3.3 TPS77333DGK TPS77433DGK

2.8 TPS77328DGK TPS77428DGK

2.7 TPS77327DGK TPS77427DGK

1.8 TPS77318DGK TPS77418DGK

Adjustable

1.5 V to 5.5 V

PACKAGED DEVICES

MSOP

(DGK)

TPS77301DGK TPS77401DGK

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS77301, TPS77318, TPS77327, TPS77328, TPS77333 WITH RESET OUTPUT

TPS77401, TPS77418, TPS77427, TPS77428, TPS77433 WITH POWER GOOD OUTPUT

250-mA LDO REGULATORS WITH INTEGRATED RESET OR PG

SLVS281A – FEBRUARY 2000 – REVISED MARCH 2000

V

I

0.1 µF

5

6

3

Figure 1. Typical Application Configuration (For Fixed Output Options)

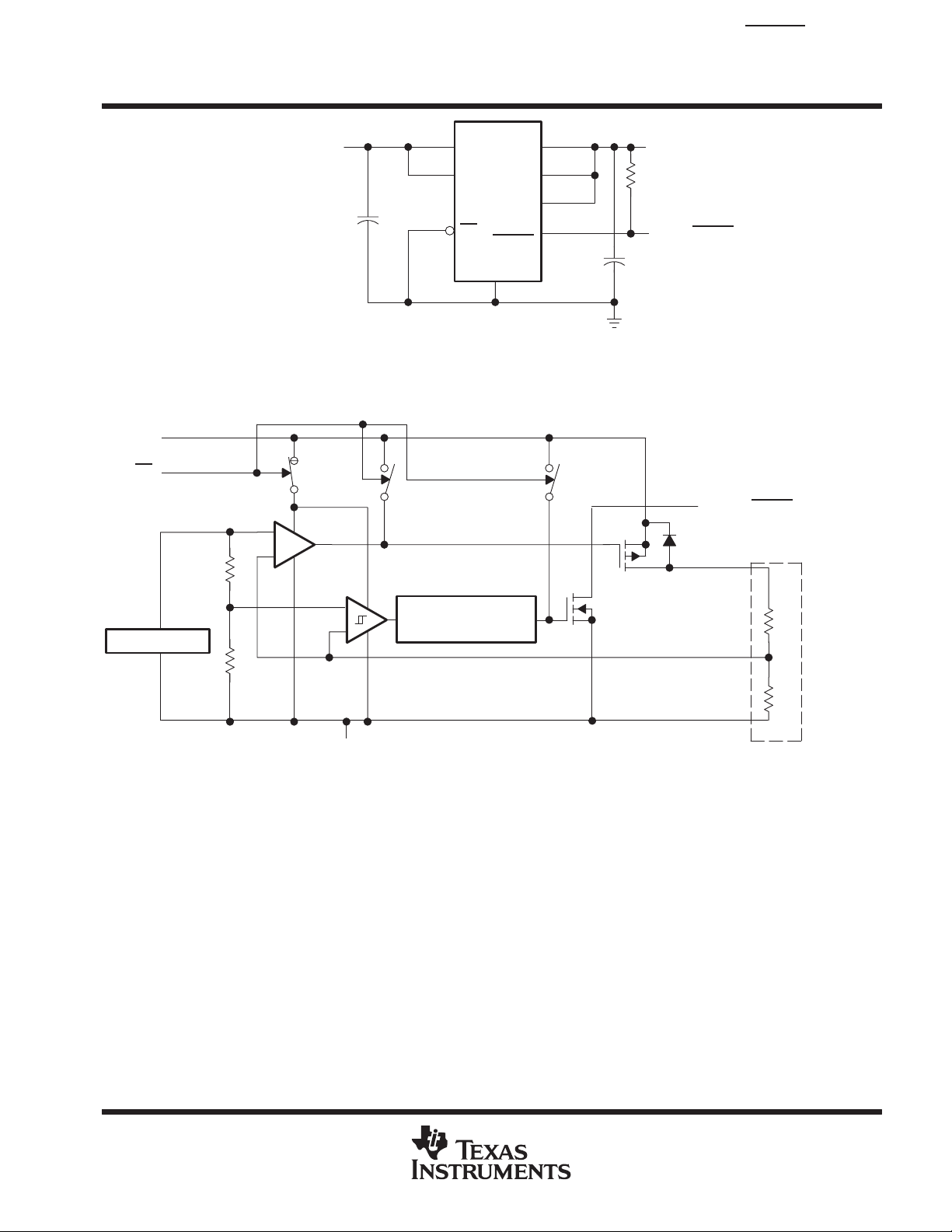

functional block diagram—adjustable version

IN

EN

_

+

IN

IN

EN

GND

4

OUT

OUT

SENSE

PG or

RESET

7

8

1

2

V

O

PG or RESET Output

+

10 µF

PG or RESET

OUT

V

= 1.1834 V

ref

GND

+

_

220 ms Delay

(for TPS773xx Option)

R1

FB/SENSE

R2

External to the device

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

TPS77301, TPS77318, TPS77327, TPS77328, TPS77333 WITH RESET OUTPUT

I/O

DESCRIPTION

I/O

DESCRIPTION

TPS77401, TPS77418, TPS77427, TPS77428, TPS77433 WITH POWER GOOD OUTPUT

250-mA LDO REGULATORS WITH INTEGRATED RESET OR PG

SLVS281A – FEBRUARY 2000 – REVISED MARCH 2000

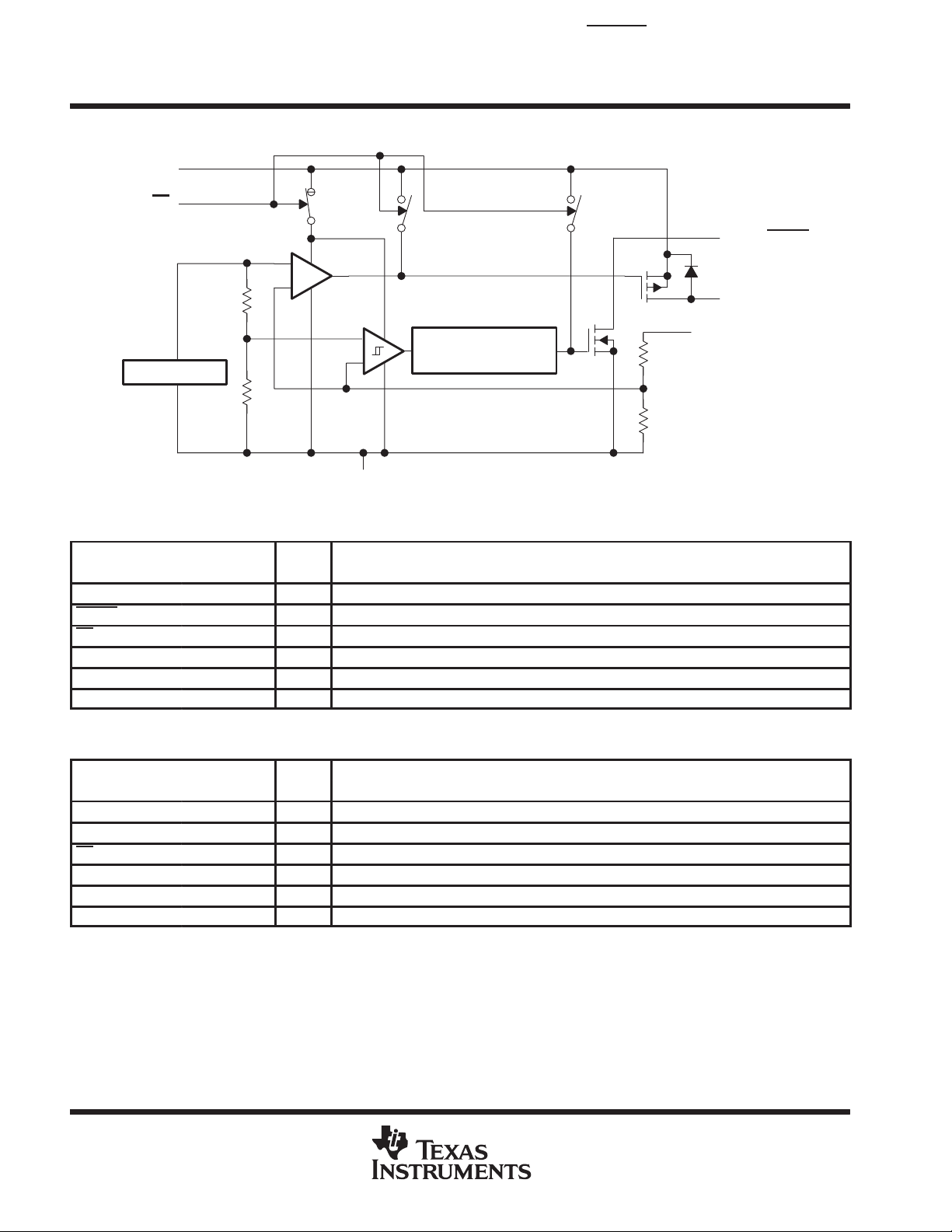

functional block diagram—fixed-voltage version

IN

EN

PG or RESET

_

V

= 1.1834 V

ref

+

+

_

GND

220 ms Delay

(for TPS773xx Option)

R1

R2

OUT

SENSE

Terminal Functions (TPS773xx)

TERMINAL

NAME NO.

FB/SENSE 1 I Feedback input voltage for adjustable device (sense input for fixed options)

RESET 2 O Reset output

EN 3 I Enable input

GND 4 Regulator ground

IN 5, 6 I Input voltage

OUT 7, 8 O Regulated output voltage

Terminal Functions (TPS774xx)

TERMINAL

NAME NO.

FB/SENSE 1 I Feedback input voltage for adjustable device (sense input for fixed options)

PG 2 O Power good

EN 3 I Enable input

GND 4 Regulator ground

IN 5, 6 I Input voltage

OUT 7, 8 O Regulated output voltage

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS77301, TPS77318, TPS77327, TPS77328, TPS77333 WITH RESET OUTPUT

TPS77401, TPS77418, TPS77427, TPS77428, TPS77433 WITH POWER GOOD OUTPUT

250-mA LDO REGULATORS WITH INTEGRATED RESET OR PG

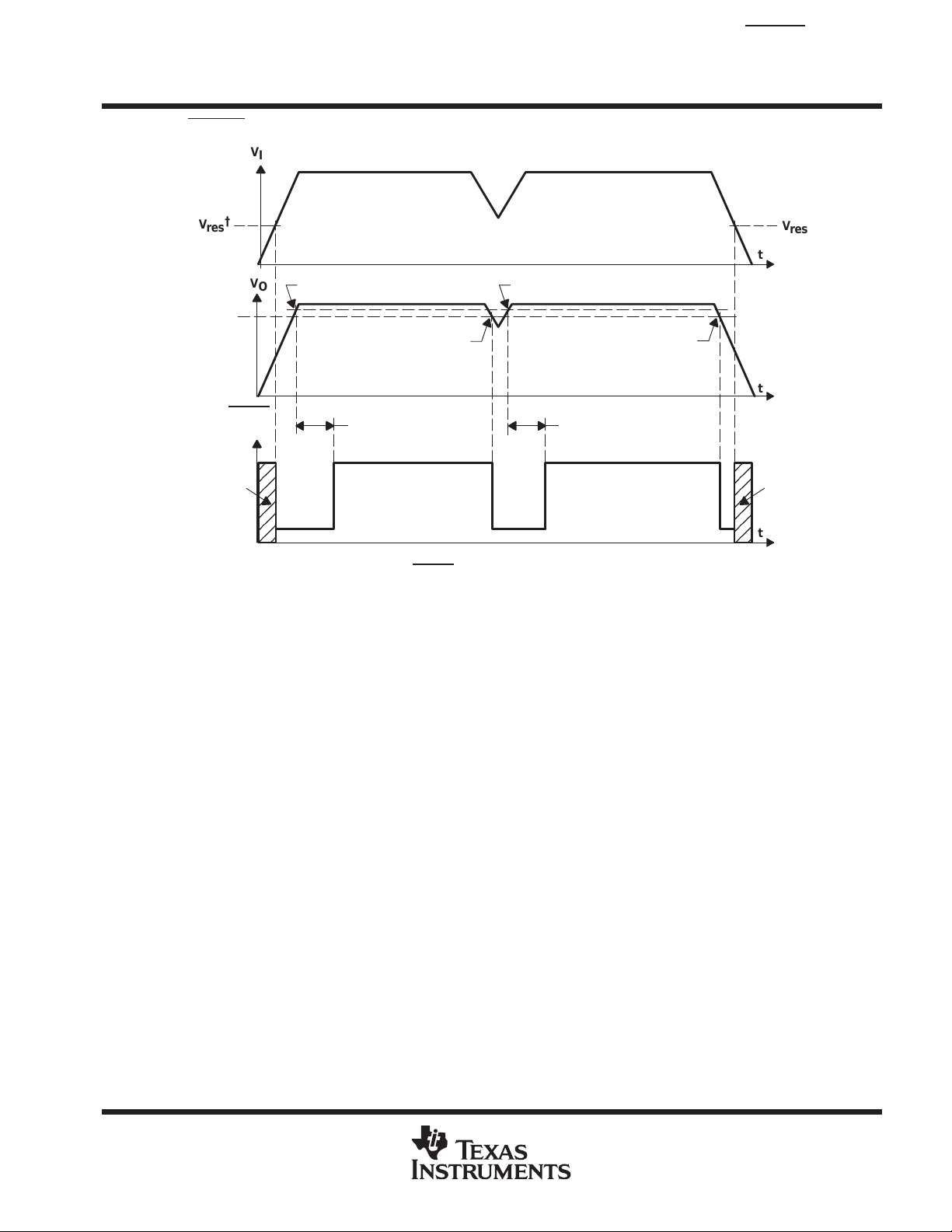

TPS773xx RESET timing diagram

V

I

†

V

res

SLVS281A – FEBRUARY 2000 – REVISED MARCH 2000

V

res

t

V

O

Threshold

Voltage

RESET

Output

Output

Undefined

†

V

is the minimum input voltage for a valid RESET . The symbol V

res

for semiconductor symbology.

‡

VIT –Trip voltage is typically 5% lower than the output voltage (95%VO) V

to V

is the hysteresis voltage.

IT+

V

IT+

‡

220 ms

Delay

V

IT+

‡

V

IT–

res

‡

‡

V

IT–

t

220 ms

Delay

Output

Undefined

t

is not currently listed within EIA or JEDEC standards

IT–

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

TPS77301, TPS77318, TPS77327, TPS77328, TPS77333 WITH RESET OUTPUT

TPS77401, TPS77418, TPS77427, TPS77428, TPS77433 WITH POWER GOOD OUTPUT

250-mA LDO REGULATORS WITH INTEGRATED RESET OR PG

SLVS281A – FEBRUARY 2000 – REVISED MARCH 2000

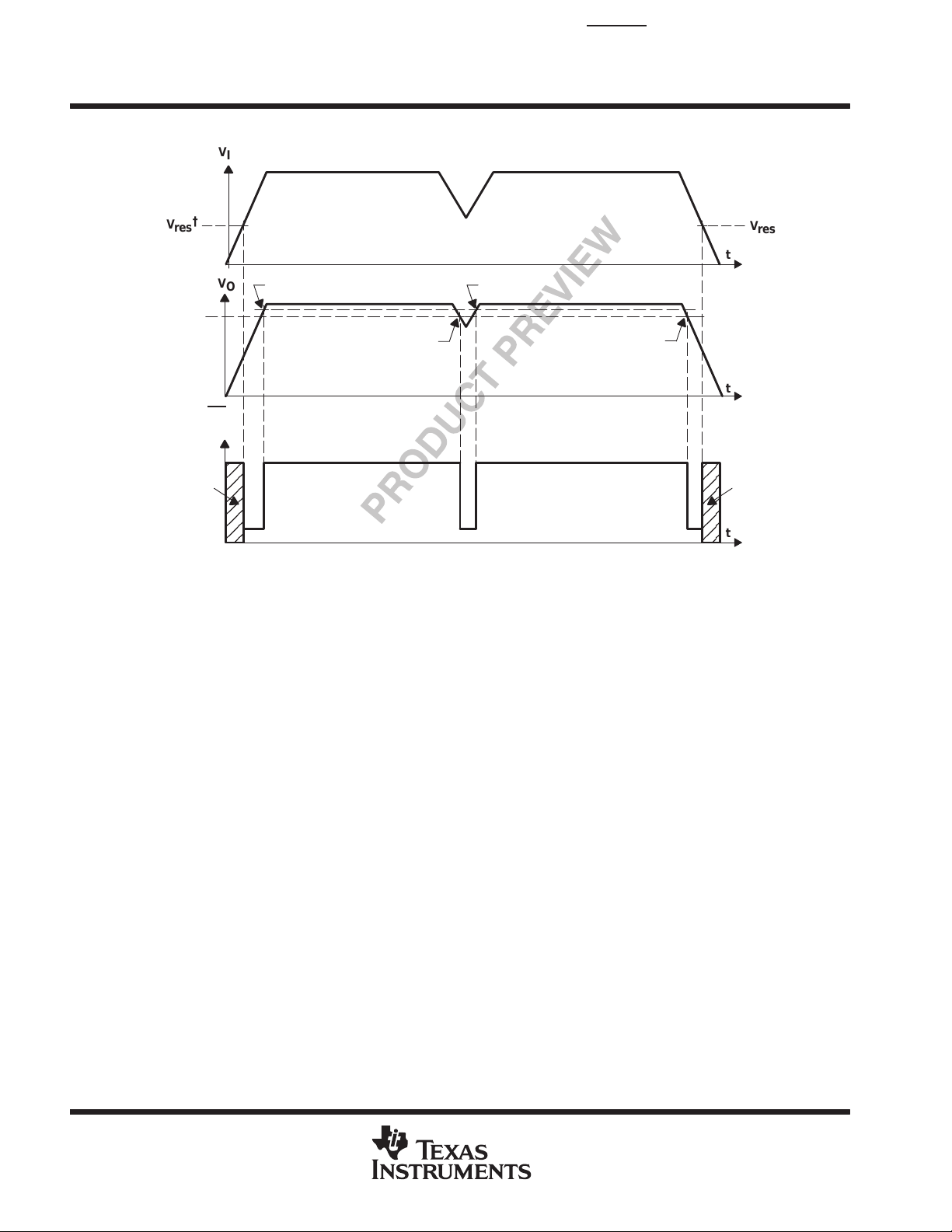

TPS774xx PG timing diagram

V

I

†

V

res

V

res

t

V

O

Threshold

Voltage

PG

Output

Output

Undefined

†

V

is the minimum input voltage for a valid PG. The symbol V

res

semiconductor symbology .

‡

VIT –Trip voltage is typically 18% lower than the output voltage (82%VO) V

to V

is the hysteresis voltage.

IT+

‡

V

IT+

‡

V

IT–

V

IT+

is not currently listed within EIA or JEDEC standards for

res

‡

‡

V

IT–

t

Output

Undefined

t

IT–

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TPS77301, TPS77318, TPS77327, TPS77328, TPS77333 WITH RESET OUTPUT

TPS77401, TPS77418, TPS77427, TPS77428, TPS77433 WITH POWER GOOD OUTPUT

250-mA LDO REGULATORS WITH INTEGRATED RESET OR PG

SLVS281A – FEBRUARY 2000 – REVISED MARCH 2000

absolute maximum ratings over operating junction temperature range

(unless otherwise noted)

Input voltage range‡, VI –0.3 V to 13.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage range at EN –0.3 V to 16.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Maximum RESET voltage (TPS773xx) 16.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Maximum PG voltage (TPS774xx) 16.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peak output current Internally limited. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation See dissipation rating tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage, V

Operating virtual junction temperature range, TJ –40°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

ESD rating, HBM 2 kV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

‡

All voltage values are with respect to network terminal ground.

PACKAGE

DGK

(OUT, FB) 5.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

O

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

DISSIPATION RATING TABLE – FREE-AIR TEMPERATURES

AIR FLOW

(CFM)

0 266.2 3.84 376 mW 3.76 mW/°C 207 mW 150 mW

150 255.2 3.92 392 mW 3.92 mW/°C 216 mW 157 mW

250 242.8 4.21 412 mW 4.12 mW/°C 227 mW 165 mW

θ

JA

(°C/W)

θ

JC

(°C/W)

TA < 25°C

POWER RATING

DERATING FACTOR

ABOVE TA = 25°C

Ĕ

TA = 70°C

POWER RATING

TA = 85°C

POWER RATING

recommended operating conditions

MIN MAX UNIT

Input voltage, V

Output voltage range, V

Output current, IO (see Note 1) 0 250 mA

Operating virtual junction temperature, TJ (see Note 1) –40 125 °C

§

To calculate the minimum input voltage for your maximum output current, use the following equation: V

NOTE 1: Continuous current and operating junction temperature are limited by internal protection circuitry, but it is not recommended that the

§

I

O

I(min)

device operate under conditions beyond those specified in this table for extended periods of time.

= V

2.7 10 V

1.5 5.5 V

+ V

O(max)

DO(max load)

.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

Loading...

Loading...