Page 1

TPS65951

Integrated Power Management/Audio Codec

Silicon Revision 1.0

Version F

Data Manual

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Literature Number: SWCS053F

September 2010–Revised May 2012

Page 2

WARNING: EXPORT NOTICE

Recipient agrees to not knowingly export or re-export, directly or

indirectly, any product or technical data (as defined by the U.S., EU, and

other Export Administration Regulations) including software, or any

controlled product restricted by other applicable national regulations,

received from Disclosing party under this Agreement, or any direct

product of such technology, to any destination to which such export or

re-export is restricted or prohibited by U.S. or other applicable laws,

without obtaining prior authorisation from U.S. Department of Commerce

and other competent Government authorities to the extent required by

those laws. This provision shall survive termination or expiration of this

Agreement.

According to our best knowledge of the state and end-use of this

product or technology, and in compliance with the export control

regulations of dual-use goods in force in the origin and exporting

countries, this technology is classified as follows:

US ECCN: EAR99

EU ECCN: EAR99

And may require export or re-export license for shipping it in compliance

with the applicable regulations of certain countries.

Page 3

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

Contents

1 Introduction ...................................................................................................................... 12

1.1 TPS65951 Block Diagram ................................................................................................ 13

2 Terminal Description .......................................................................................................... 14

2.1 Corner Balls ................................................................................................................ 14

2.2 Ball Characteristics ........................................................................................................ 15

2.2.1 ESD Electrical Parameters .................................................................................... 20

2.3 Ball Placement (Top View) ............................................................................................... 21

2.4 Signal Description ......................................................................................................... 22

2.5 Ground Connection Usage ............................................................................................... 30

3 Electrical Characteristics .................................................................................................... 31

3.1 Absolute Maximum Ratings .............................................................................................. 31

3.2 Minimum Voltages and Associated Currents .......................................................................... 31

3.3 Recommended Operating Conditions .................................................................................. 32

3.4 Digital I/O Electrical Characteristics ..................................................................................... 32

4 Clock Specifications .......................................................................................................... 36

4.1 Features .................................................................................................................... 36

4.2 Clock Slicer ................................................................................................................. 36

4.2.1 Modes of Operation ............................................................................................ 37

4.2.1.1 Bypass Mode (BP) ................................................................................. 37

4.2.1.2 Power-Down Mode (PD) .......................................................................... 37

4.2.1.3 Low-Power Application Mode (LP) ............................................................... 37

4.2.1.4 High-Performance Application Mode (HP) ...................................................... 37

4.2.2 Clock Slicer Electrical Characteristics ....................................................................... 38

4.3 Input Clock Specifications ................................................................................................ 39

4.3.1 Clock Source Requirements .................................................................................. 39

4.3.2 High Frequency Input Clock ................................................................................... 39

4.3.3 32-kHz Input Clock ............................................................................................. 41

4.3.3.1 External Crystal Description ...................................................................... 41

4.3.3.2 External Clock Description ........................................................................ 43

4.4 Output Clock Specifications .............................................................................................. 46

4.4.1 32KCLKOUT Output Clock .................................................................................... 46

4.4.2 HFCLKOUT Output Clock ..................................................................................... 47

4.4.3 Output Clock Stabilization Time .............................................................................. 48

5 Audio/Voice Module ........................................................................................................... 50

5.1 Audio/Voice Downlink (RX) Module ..................................................................................... 50

5.1.1 Earphone Output ................................................................................................ 51

5.1.1.1 Earphone Output Characteristics ................................................................ 51

5.1.1.2 External Components and Application Schematics ........................................... 52

5.1.2 8-Ω Stereo Hands-Free ........................................................................................ 52

5.1.2.1 8-Ω Stereo Hands-Free Output Characteristics ................................................ 52

5.1.2.2 External Components and Application Schematics ........................................... 54

5.1.3 Headset .......................................................................................................... 55

5.1.3.1 Headset Output Characteristics .................................................................. 55

5.1.3.2 External Components and Application Schematics ........................................... 57

5.1.4 Headset Pop-Noise Attenuation .............................................................................. 61

5.1.5 Predriver for External Class D Amplifier ..................................................................... 62

5.1.5.1 Predriver Output Characteristics ................................................................. 62

5.1.5.2 External Components and Application Schematics ........................................... 63

5.1.6 Vibra H-Bridge .................................................................................................. 64

5.1.6.1 Vibra H-Bridge Output Characteristics .......................................................... 64

5.1.6.2 External Components and Application Schematics ........................................... 64

Copyright © 2010–2012, Texas Instruments Incorporated Contents 3

Page 4

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

5.1.7 Digital Audio Filter Module .................................................................................... 65

5.1.8 Digital Voice Filter Module ..................................................................................... 65

5.1.8.1 Voice Downlink Filter (with Sampling Frequency at 8 kHz) .................................. 65

5.1.8.2 Voice Downlink Filter (with Sampling Frequency at 16 kHz) ................................. 67

5.1.9 Boost Stage ..................................................................................................... 67

5.2 Audio/Voice Uplink (TX) Module ......................................................................................... 69

5.2.1 MIC Bias Module ................................................................................................ 69

5.2.1.1 Analog MIC Bias Module Characteristics ....................................................... 70

5.2.1.2 Digital MIC Bias Module Characteristics ........................................................ 73

5.2.1.3 Silicon MIC Module Characteristics ............................................................. 74

5.2.2 Stereo Differential Input ........................................................................................ 75

5.2.3 Headset Differential Input ...................................................................................... 75

5.2.4 FM Radio/Auxiliary Stereo Input .............................................................................. 76

5.2.4.1 External Components ............................................................................. 76

5.2.5 Pulse Density Modulated (PDM) Interface for Digital Microphone ....................................... 76

5.2.6 Uplink Characteristics .......................................................................................... 77

5.2.7 Microphone Amplification Stage .............................................................................. 78

5.2.8 Digital Audio Filter Module .................................................................................... 79

5.2.9 Digital Voice Filter Module ..................................................................................... 79

5.2.9.1 Voice Uplink Filter (with Sampling Frequency at 8 kHz) ...................................... 79

5.2.9.2 Voice Uplink Filter (with Sampling Frequency at 16 kHz) .................................... 81

www.ti.com

6 Power Module ................................................................................................................... 82

6.1 Power Provider ............................................................................................................ 84

6.1.1 VDD1 DC-DC Regulator ....................................................................................... 84

6.1.1.1 VDD1 DC-DC Regulator Characteristics ........................................................ 84

6.1.1.2 External Components and Application Schematics ........................................... 86

6.1.2 VDD2 DC-DC Regulator ....................................................................................... 87

6.1.2.1 VDD2 DC-DC Regulator Characteristics ........................................................ 87

6.1.2.2 External Components and Application Schematics ........................................... 89

6.1.3 VIO DC-DC Regulator .......................................................................................... 91

6.1.3.1 VIO DC-DC Regulator Characteristics .......................................................... 91

6.1.3.2 External Components and Application Schematics ........................................... 93

6.1.4 VDAC LDO Regulator .......................................................................................... 94

6.1.5 VPLL1 LDO Regulator ......................................................................................... 95

6.1.6 VPLL2 LDO Regulator ......................................................................................... 96

6.1.7 VMMC1 LDO Regulator ....................................................................................... 97

6.1.8 VMMC2 LDO Regulator ....................................................................................... 98

6.1.9 VAUX1 LDO Regulator ........................................................................................ 99

6.1.10 VAUX2 LDO Regulator ....................................................................................... 100

6.1.11 VAUX3 LDO Regulator ....................................................................................... 101

6.1.12 VAUX4 LDO Regulator ....................................................................................... 102

6.1.13 VINTDIG LDO Regulator ..................................................................................... 103

6.1.14 VINTANA1 LDO Regulator ................................................................................... 104

6.1.15 VINTANA2 LDO Regulator ................................................................................... 105

6.1.16 VUSB3V1 Regulator .......................................................................................... 106

6.1.17 VUSB1V8 Regulator .......................................................................................... 108

6.1.18 VUSB1V5 Regulator .......................................................................................... 109

6.1.19 Charge Pump .................................................................................................. 110

6.1.20 USB LDOs Short-Circuit Protection Scheme .............................................................. 111

6.1.21 RC Oscillators ................................................................................................. 112

6.2 Power References ....................................................................................................... 112

6.3 Power Control ............................................................................................................ 113

6.3.1 Backup Battery Charger ...................................................................................... 113

4 Contents Copyright © 2010–2012, Texas Instruments Incorporated

Page 5

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

6.3.2 Battery Monitoring and Threshold Detection .............................................................. 113

6.3.2.1 Switch On/Switch Off and BACKUP Conditions .............................................. 113

6.3.3 VRRTC LDO Regulator ...................................................................................... 114

6.3.4 VBRTC Clamp ................................................................................................. 115

6.3.5 Hot-Die Detection and Thermal Shutdown ................................................................ 115

6.3.5.1 Hot-Die Characteristics .......................................................................... 115

6.3.5.2 Thermal Shutdown Characteristics ............................................................. 115

6.3.5.3 Thermal Detect System Consumption ......................................................... 116

6.4 Power Consumption ..................................................................................................... 116

6.5 Power Management ..................................................................................................... 118

6.5.1 Master/Slave Modes .......................................................................................... 118

6.5.2 Boot Modes .................................................................................................... 118

6.5.3 Process Modes ................................................................................................ 118

6.5.3.1 C021/C014 Mode ................................................................................. 118

6.5.4 Switch-On Sequence ......................................................................................... 118

6.5.4.1 Timings Before Sequence_Start ................................................................ 118

6.5.4.2 Switch On in Master_C021/C014_Generic Mode ............................................ 120

6.5.5 Switch-Off Sequence ......................................................................................... 121

7 Connectivity .................................................................................................................... 122

7.1 Timing Parameters ....................................................................................................... 122

7.2 Target Frequencies ...................................................................................................... 123

7.3 USB Transceiver ......................................................................................................... 123

7.3.1 PHY Electrical Characteristics ............................................................................... 124

7.3.1.1 LS/FS Single-Ended Receivers ................................................................. 125

7.3.1.2 LS/FS Differential Receiver ..................................................................... 125

7.3.1.3 LS/FS Transmitter ................................................................................ 125

7.3.1.4 HS Differential Receiver ......................................................................... 126

7.3.1.5 HS Differential Transmitter ...................................................................... 126

7.3.1.6 UART Transceiver ................................................................................ 127

7.3.1.7 Pullup/Pulldown Resistors ....................................................................... 128

7.3.2 OTG Electrical Characteristics .............................................................................. 128

7.3.2.1 OTG VBUS Electrical ............................................................................ 129

7.3.2.2 OTG ID Electrical ................................................................................. 129

7.3.3 Charger Detection ............................................................................................. 130

7.4 Inter-Integrated Circuit (I

2

C) Timing ................................................................................... 130

7.5 Audio Interface: TDM/I2S Protocol .................................................................................... 132

7.5.1 I2S Right- and Left-Justified Data Format ................................................................. 133

7.5.2 TDM Data Format ............................................................................................. 134

7.6 Voice PCM Interfaces ................................................................................................... 135

7.7 JTAG Interfaces .......................................................................................................... 138

8 Battery Interface .............................................................................................................. 140

8.1 General Description ...................................................................................................... 140

8.1.1 BCI Overview .................................................................................................. 140

8.1.2 Battery Backup Overview .................................................................................... 140

8.2 Block Diagram ............................................................................................................ 140

8.2.1 BCI References (BCI_PM) ................................................................................... 140

8.2.2 Thermistor Current Source for GPADC (BCI_BTEMP) .................................................. 142

8.2.3 BCI Power (BCI_PWR) ....................................................................................... 142

8.2.4 Battery Removal ............................................................................................... 143

8.2.5 BCI VBAT-VBUS Detection (BCI_DET) .................................................................... 143

8.2.6 BCI Interface (BCI_IOS) ...................................................................................... 145

8.2.7 External USB Charger Control .............................................................................. 145

8.2.7.1 USB Charger Detection .......................................................................... 145

Copyright © 2010–2012, Texas Instruments Incorporated Contents 5

Page 6

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

8.2.7.2 Internal Charger Error Signal (USBCHRG_STATZ) ......................................... 147

8.2.7.3 Battery Discharge Timimg ....................................................................... 147

8.2.7.4 Watchdog .......................................................................................... 147

8.3 External Charger Control ................................................................................................ 148

8.3.1 USB Charger Detection ...................................................................................... 148

8.3.2 Battery Charger Control State Machine .................................................................... 149

8.3.3 Charger Watchdog ............................................................................................ 151

www.ti.com

9 MADC ............................................................................................................................. 151

9.1 General Description ..................................................................................................... 151

9.2 Main Electrical Characteristics ......................................................................................... 152

9.3 Channel Voltage Input Range .......................................................................................... 153

9.3.1 Sequence Conversion Time ................................................................................. 154

9.4 Power Consumption ..................................................................................................... 155

10 LED Drivers ..................................................................................................................... 156

10.1 General Description ..................................................................................................... 156

11 Debouncing Time ............................................................................................................. 157

12 External Components ....................................................................................................... 158

13 TPS65951 Package ........................................................................................................... 163

13.1 TPS65951 Standard Package Symbolization ........................................................................ 163

13.2 Package Thermal Resistance Characteristics ....................................................................... 163

13.3 Packaging Information .................................................................................................. 163

13.4 Mechanical Data ......................................................................................................... 164

14 Glossary ......................................................................................................................... 165

14.1 Revision History .......................................................................................................... 167

6 Contents Copyright © 2010–2012, Texas Instruments Incorporated

Page 7

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

List of Figures

1-1 TPS65951 Block Diagram....................................................................................................... 13

2-1 PBGA Bottom View .............................................................................................................. 14

2-2 Top View .......................................................................................................................... 21

4-1 Clock Overview ................................................................................................................... 36

4-2 Clock Slicer Block Diagram ..................................................................................................... 37

4-3 HFCLKIN Clock Distribution .................................................................................................... 40

4-4 Example of Wired-OR Clock Request......................................................................................... 40

4-5 HFCLKIN Squared Input Clock................................................................................................. 41

4-6 32-kHz Oscillator Block Diagram In Master Mode With Crystal............................................................ 42

4-7 32-kHz Crystal Input ............................................................................................................. 43

4-8 32-kHz Oscillator Block Diagram Without Crystal Option 1................................................................. 45

4-9 32-kHz Oscillator in Bypass Mode Block Diagram Without Crystal Option 2 ............................................ 45

4-10 32-kHz Square- or Sine-Wave Input Clock ................................................................................... 46

4-11 32.768-kHz Clock Output Block Diagram ..................................................................................... 46

4-12 32KCLKOUT Output Clock...................................................................................................... 47

4-13 HFCLKOUT Output Clock....................................................................................................... 48

4-14 32KCLKOUT and HFCLKOUT Clock Stabilization Time.................................................................... 48

4-15 HFCLKOUT Behavior ........................................................................................................... 49

5-1 Audio/Voice Module Block Diagram ........................................................................................... 50

5-2 Earphone Amplifier............................................................................................................... 51

5-3 Earphone Speaker ............................................................................................................... 52

5-4 8-Ω Stereo Hands-Free Amplifiers............................................................................................. 52

5-5 Class-D: Short-Circuits .......................................................................................................... 54

5-6 8-Ω Stereo Hands-Free ......................................................................................................... 54

5-7 Ferrite Bead: Equivalent Circuit ................................................................................................ 55

5-8 Headset Amplifier ................................................................................................................ 55

5-9 Connection of External Actuator Driver to Headset Amplifier ............................................................. 56

5-10 Headset 4-Wire Stereo Jack Without External FET ......................................................................... 57

5-11 Headset 4-Wire Stereo Jack With External FET ............................................................................. 59

5-12 Headset 5-Wire Stereo Jack.................................................................................................... 60

5-13 Headset 4-Wire Stereo Jack Optimized ....................................................................................... 61

5-14 Headset Pop-Noise Cancellation Diagram.................................................................................... 62

5-15 Predriver for External Class D.................................................................................................. 63

5-16 Vibra H-Bridge.................................................................................................................... 64

5-17 Digital Audio Filter Downlink Path Characteristics ........................................................................... 65

5-18 Digital Voice Filter Downlink Path Characteristics ........................................................................... 65

5-19 Voice Downlink Frequency Response F

5-20 Voice Downlink Frequency Response F

5-21 Analog and Digital Microphone Muxing ....................................................................................... 70

5-22 Analog Microphone Pseudodifferential........................................................................................ 72

5-23 Analog Microphone Differential................................................................................................. 72

5-24 Digital Microphone Block Diagram............................................................................................. 73

5-25 Digital Microphone Timing Diagram ........................................................................................... 74

5-26 Silicon Microphone............................................................................................................... 75

5-27 Audio Auxiliary Input............................................................................................................. 76

5-28 Example of Circuitry.............................................................................................................. 77

5-29 Uplink Amplifier................................................................................................................... 78

Copyright © 2010–2012, Texas Instruments Incorporated List of Figures 7

= 8 kHz........................................................................... 66

S

= 16 kHz ......................................................................... 67

S

Page 8

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

www.ti.com

5-30 Digital Audio Filter Uplink Path Characteristics .............................................................................. 79

5-31 Digital Audio Filter Uplink Path Characteristics .............................................................................. 79

5-32 Voice Uplink Frequency Response with F

5-33 Voice Uplink Frequency Response with F

5-34 Voice Uplink Frequency Response with F

5-35 Voice Uplink Frequency Response with F

= 8 kHz (Frequency Range 0 to 600 Hz) .................................. 80

S

= 8 kHz (Frequency Range 3000 to 3600 Hz) ............................ 81

S

= 16 kHz (Frequency Range 0 to 600 Hz) ................................ 81

S

= 16 kHz (Frequency Range 6200 to 7000 Hz) .......................... 81

S

6-1 Power Provider Block Diagram................................................................................................. 83

6-2 VDD1 DC-DC Regulator Efficiency in Active Mode.......................................................................... 86

6-3 VDD1 DC-DC Regulator Efficiency in Sleep Mode.......................................................................... 86

6-4 VDD1 DC-DC Application Schematic.......................................................................................... 87

6-5 VDD2 DC-DC Regulator Efficiency in Active Mode.......................................................................... 89

6-6 VDD2 DC-DC Regulator Efficiency in Sleep Mode.......................................................................... 89

6-7 VDD2 DC-DC Application Schematic.......................................................................................... 90

6-8 VIO DC-DC Regulator Efficiency in Active Mode............................................................................ 92

6-9 VIO DC-DC Regulator Efficiency in Sleep Mode............................................................................. 93

6-10 VIO DC-DC Application Schematic ............................................................................................ 93

6-11 VUSB3V1 LDO Supply Selection for the Different Modes of Operation................................................. 106

6-12 General Overview of the Charge Pump and its Interfaces................................................................ 110

6-13 Timings Before Sequence Start .............................................................................................. 119

6-14 Timings—Switch On in Master_C021/C014_Generic Mode .............................................................. 120

6-15 Switch-Off Sequence in Master Modes ...................................................................................... 121

7-1 USB 2.0 PHY Highlight......................................................................................................... 123

7-2 USB System Application Schematic.......................................................................................... 124

7-3 USB UART Data Flow.......................................................................................................... 127

7-4 I

2

C Interface—Transmit and Receive in Slave Mode ...................................................................... 130

7-5 I2S Interface—I2S Master ModeI............................................................................................. 133

7-6 I2S Interface—I2S Slave Mode ............................................................................................... 133

7-7 TDM Interface—TDM Master Mode.......................................................................................... 135

7-8 Voice PCM Interface—Master Mode (Mode 1) ............................................................................. 136

7-9 Voice PCM Interface—Slave Mode (Mode 1)............................................................................... 136

7-10 JTAG Interface Timing ......................................................................................................... 138

8-1 Battery Charger Block Diagram............................................................................................... 140

8-2 BCI References Block Diagram............................................................................................... 141

8-3 Charging LED/Battery Discharge Driver Block Diagram................................................................... 142

8-4 Battery Removal and Discharge Control..................................................................................... 143

8-5 Charger Detection Block Diagram............................................................................................ 144

8-6 Battery Charger Digital Interface.............................................................................................. 145

8-7 Charging Error Frame.......................................................................................................... 149

8-8 Battery Charger Control State Machine...................................................................................... 150

8-9 Charging Flow chart ............................................................................................................ 151

9-1 One Conversion Sequence General Timing Diagram ..................................................................... 155

10-1 LED Driver Block Diagram..................................................................................................... 156

13-1 TPS65951 Mechanical Package.............................................................................................. 164

8 List of Figures Copyright © 2010–2012, Texas Instruments Incorporated

Page 9

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

List of Tables

2-1 Ball Characteristics............................................................................................................... 15

2-2 ESD Electrical Parameters...................................................................................................... 20

2-3 Signal Description ................................................................................................................ 22

2-4 Ground Connections ............................................................................................................. 30

3-1 Absolute Maximum Ratings..................................................................................................... 31

3-2 VBAT Min Required Per VBAT Ball and Associated Maximum Current.................................................. 31

3-3 Recommended Operating Maximum Ratings ................................................................................ 32

3-4 Digital I/O Electrical Characteristics ........................................................................................... 33

4-1 Clock Slicer Electrical Characteristics ......................................................................................... 38

4-2 TPS65951 Input Clock Source Requirements................................................................................ 39

4-3 HFCLKIN Input Clock Electrical Characteristics ............................................................................. 41

4-4 HFCLKIN Square Input Clock Timing Requirements with Slicer in Bypass .............................................. 41

4-5 Crystal Electrical Characteristics ............................................................................................... 42

4-6 Base Oscillator Switching Characteristics..................................................................................... 43

4-7 32-kHz Crystal Input Clock Timing Requirements ........................................................................... 43

4-8 32-kHz Input Square- or Sine-wave Clock Source Electrical Characteristics ............................................ 45

4-9 32-kHz Square-wave Input Clock Source Timing Requirements .......................................................... 45

4-10 32KCLKOUT Output Clock Electrical Characteristics ....................................................................... 47

4-11 32KCLKOUT Output Clock Switching Characteristics....................................................................... 47

4-12 HFCLKOUT Output Clock Electrical Characteristics ........................................................................ 47

4-13 HFCLKOUT Output Clock Switching Characteristics........................................................................ 47

5-1 Earphone Amplifier Output Characteristics ................................................................................... 51

5-2 8-Ω Stereo Hands-Free Output Characteristics.............................................................................. 53

5-3 Headset Output Characteristics ................................................................................................ 56

5-4 Output Characteristics Headset 4-Wire Stereo Jack Without External FET.............................................. 58

5-5 Output Characteristics Headset 4-Wire Stereo Jack With External FET.................................................. 59

5-6 Output Characteristics Headset 5-Wire Stereo Jack ........................................................................ 60

5-7 Headset Pop-Noise Characteristics............................................................................................ 62

5-8 Predriver Output Characteristics ............................................................................................... 63

5-9 Vibra H-Bridge Output Characteristics ........................................................................................ 64

5-10 Digital Audio Filter RX Electrical Characteristics............................................................................. 65

5-11 Digital Voice Filter RX Electrical Characteristics with F

5-12 Digital Voice Filter RX Electrical Characteristics with F

5-13 Boost Electrical Characteristics vs FSFrequency (F

5-14 Boost Electrical Characteristics vs FSFrequency (F

5-15 Analog Microphone Bias Module Characteristics ............................................................................ 70

5-16 Analog Microphone Bias Module Characteristics, Bias Resistor........................................................... 71

5-17 Digital Microphone Bias Module Characteristics ............................................................................. 73

5-18 Digital Microphone Module Characteristics (2) ............................................................................... 74

5-19 Silicon Microphone Module Characteristics................................................................................... 74

5-20 Uplink Characteristics............................................................................................................ 78

5-21 Digital Audio Filter TX Electrical Characteristics ............................................................................. 79

5-22 Digital Voice Filter TX Electrical Characteristics with F

5-23 Digital Voice Filter TX Electrical Characteristics with F

6-1 Summary of the Power Provider ............................................................................................... 84

6-2 VDD1 DC-DC Regulator Characteristics...................................................................................... 85

6-3 VDD2 DC-DC Regulator Characteristics...................................................................................... 88

Copyright © 2010–2012, Texas Instruments Incorporated List of Tables 9

= 8 kHz.......................................................... 66

S

= 16 kHz........................................................ 67

S

≤ 22.05 kHz)....................................................... 68

S

≥ 24 kHz)........................................................... 68

S

= 8 kHz.......................................................... 80

S

= 16 kHz ........................................................ 81

S

Page 10

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

www.ti.com

6-4 VIO DC-DC Regulator Characteristics ........................................................................................ 91

6-5 VDAC LDO Regulator Characteristics......................................................................................... 94

6-6 VPLL1 LDO Regulator Characteristics ........................................................................................ 95

6-7 VPLL2 LDO Regulator Characteristics ........................................................................................ 96

6-8 VMMC1 LDO Regulator Characteristics....................................................................................... 97

6-9 VMMC2 LDO Regulator Characteristics....................................................................................... 98

6-10 VAUX1 LDO Regulator Characteristics ....................................................................................... 99

6-11 VAUX2 LDO Regulator Characteristics...................................................................................... 100

6-12 VAUX3 LDO Regulator Characteristics...................................................................................... 101

6-13 VAUX4 LDO Regulator Characteristics...................................................................................... 102

6-14 VINTDIG LDO Regulator Characteristics.................................................................................... 103

6-15 VINTANA1 LDO Regulator Characteristics.................................................................................. 104

6-16 VINTANA2 LDO Regulator Characteristics.................................................................................. 105

6-17 VUSB3V1 Internal LDO Regulator Characteristics......................................................................... 107

6-18 VUSB1V8 Internal LDO Regulator Characteristics......................................................................... 108

6-19 VUSB1V5 Internal LDO Regulator Characteristics......................................................................... 109

6-20 Charge Pump Characteristics................................................................................................. 111

6-21 RC Oscillator Characteristics.................................................................................................. 112

6-22 Voltage Reference Characteristics ........................................................................................... 112

6-23 Backup Battery Charger Characteristics..................................................................................... 113

6-24 Battery Threshold Levels ...................................................................................................... 113

6-25 VRRTC LDO Regulator Characteristics ..................................................................................... 114

6-26 VBRTC Clamp Characteristics................................................................................................ 115

6-27 Thermal Hot-Die Selection..................................................................................................... 115

6-28 Thermal Enable Selection ..................................................................................................... 115

6-29 Thermal Detect System Consumption ....................................................................................... 116

6-30 Power Consumption (for C027 and C021/C014 Boot Modes)............................................................ 116

6-31 Regulator States Depending on Use Cases ................................................................................ 117

6-32 BOOT Mode Description....................................................................................................... 118

6-33 C021/CO14 Mode Description ............................................................................................... 118

7-1 Timing Parameters ............................................................................................................. 122

7-2 TPS65951 Interface Target Frequencies.................................................................................... 123

7-3 LS/FS Single-Ended Receivers ............................................................................................... 125

7-4 LS/FS Differential Receiver.................................................................................................... 125

7-5 LS Transmitter................................................................................................................... 125

7-6 FS Transmitter .................................................................................................................. 126

7-7 HS Differential Receiver ....................................................................................................... 126

7-8 HS Transmitter .................................................................................................................. 127

7-9 USB UART Interface Timing Parameters.................................................................................... 127

7-10 CEA-2011/UART Interface Timing Parameters............................................................................. 127

7-11 Pullup/Pulldown Resistors..................................................................................................... 128

7-12 OTG VBUS Electrical........................................................................................................... 129

7-13 OTG ID Electrical ............................................................................................................... 129

7-14 I

7-15 I

2

C Interface Timing Requirements .......................................................................................... 131

2

C Interface Switching Requirements ....................................................................................... 132

7-16 I2S Interface—Timing Requirements......................................................................................... 134

7-17 I2S Interface—Switching Characteristics.................................................................................... 134

7-18 TDM Interface Master Mode Timing Requirements ........................................................................ 135

10 List of Tables Copyright © 2010–2012, Texas Instruments Incorporated

Page 11

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

7-19 TDM Interface Master Mode Switching Characteristics ................................................................... 135

7-20 Voice PCM Interface Timing Requirements (Mode 1) ..................................................................... 137

7-21 Voice PCM Interface Switching Characteristics (Mode 1)................................................................. 137

7-22 JTAG Interface Timing Requirements........................................................................................ 138

7-23 JTAG Interface Switching Characteristics................................................................................... 139

8-1 References Electrical Conditions ............................................................................................. 141

8-2 ADCIN1 Current Source Electrical Parameters............................................................................. 142

8-3 Charging LED/Battery Discharge Electrical Characteristics............................................................... 142

8-4 Battery Discharge and Charging LED Timing............................................................................... 143

8-5 Charger Detection Electrical Characteristics................................................................................ 144

8-6 MADC Input Attenuation ....................................................................................................... 144

8-7 USB Charger Detection Debounce Timing.................................................................................. 145

8-8 Electrical Specifications – Voltages .......................................................................................... 145

8-9 Electrical Specifications – Currents .......................................................................................... 146

8-10 Electrical Specifications – Resistances...................................................................................... 146

8-11 Wait and Debounce Timing.................................................................................................... 146

8-12 Error Delay Timing.............................................................................................................. 147

8-13 Battery Discharge Timing...................................................................................................... 147

8-14 Watchdog Timing ............................................................................................................... 147

9-1 Electrical Characteristics....................................................................................................... 152

9-2 MADC Analog Input Range and Prescaler Divide Ratio................................................................... 153

9-3 Sequence Conversion Timing Characteristics .............................................................................. 154

9-4 Power Consumption ............................................................................................................ 155

10-1 Electrical Characteristics....................................................................................................... 156

11-1 Debouncing Time ............................................................................................................... 157

12-1 TPS65951 External Components............................................................................................. 158

13-1 TPS65951 Nomenclature Description........................................................................................ 163

13-2 TPS65951 Thermal Resistance Characteristics............................................................................ 163

13-3 Orderable Parts ................................................................................................................. 163

Copyright © 2010–2012, Texas Instruments Incorporated List of Tables 11

Page 12

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

Integrated Power Management/Audio Codec

1 Introduction

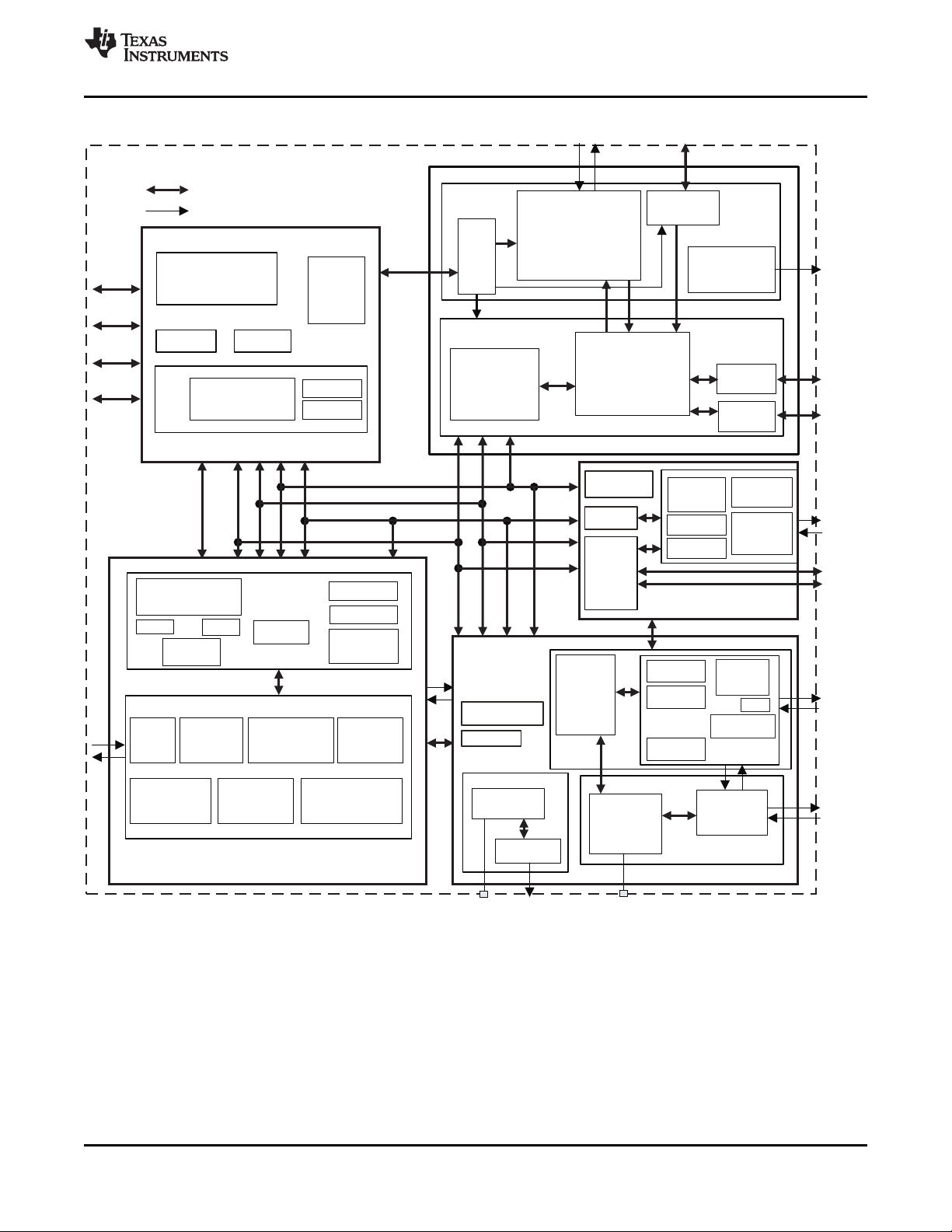

The TPS65951 device is a power-management IC for mobile cellular handsets powered by a Li-ion, Li-ion

polymer, or cobalt-nickel-manganese cell battery. It can be connected to an application processor and/or a

modem. This optimized power-management IC is designed to support the specific power requirements of

the OMAP processor devices. The TPS65951 contains several buck converters, low dropout (LDO)

regulators, battery charger interface, and a host of other features and functions. The audio portion of the

TPS65951 is an entire audio module with audio codecs, digital filters, input preamplifiers/amplifiers, and

class D output amplifiers.

This TPS65951 Data Manual presents the electrical and mechanical specifications for the TPS65951

device. It covers the following topics:

• A description of the TPS65951 terminals: assignment, multiplexing, electrical characteristics, and

functional description (see Section 2)

• A presentation of the electrical characteristic requirements: maximum and recommended operating

conditions, digital I/O characteristics (see Section 3)

• The clock specifications: clock slicer, input and output clocks (see Section 4)

• The audio/voice module with the electrical characteristics and the application schematics for the

downlink and uplink path (see Section 5)

• The power module including the power provider, power references, power control, the power

consumption, and the power management with the sequence on and off (see Section 6)

• The timing requirements and switching characteristics (ac timings) of the interfaces (see Section 7)

• The battery charger interface (see Section 8)

• A description of different modules: MADC and LED drivers (see Section 9 and Section 10)

• The deboucing time (see Section 11)

• A description of the external components for the application schematics (see Section 12)

• The thermal resistance characteristics, device nomenclature, and mechanical data about the available

packaging (see Section 13)

• A glossary of acronyms and abbreviations used in this data manual (see Section 14)

1

www.ti.com

Check for Samples: TPS65951

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright © 2010–2012, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to

specifications per the terms of the Texas Instruments standard warranty. Production

processing does not necessarily include testing of all parameters.

Page 13

SWCS053-001

Power Subchip (A-D)

Power analog

Power digital

Auxiliary Subchip (A-D)

Audio subchip (A-D)

Interface Subchip(D)

AUDIO digita l

MADCTOP

BCITOP

BCI analog

USB Subchip (A-D)

Card Det 1

Card Det 2

GPIO

TAP

OCP

RTC

RFID

PMC master

PMC slave

LED digital

LED analog

LEDTOP

Device

Clocks

Digital signal(s)

Analog signal(s)

PCM (4)

TDM (4)

StartADC

LedSync

ULPI (12)

UART (2)

Clocks

OCP

SIH_INT

TAP

OCP

Clocks

SIH_INT

Clo cks

TAP

I2C A pad

I2C B pad

Clk In/Out

GPIO pad

SHIFTERS

SIH_INT

OCP

TAP

Clocks

SIH_INT

OCP

TAP

TAP

EEprom

CLED

PIH

Clock

generator

SIH

AUDIO

analog

Audio

PLL

Wrapper

digital

Audio RX amplifiers

Mic amplifiers

Analog volume control

D/A converters

A/D converters

Differential vibrator

Digital mic

interface

Analog and

digital mic

bias

Audio and voice filters

(RX and TX paths)

+

Vibrator control

PCM

interface

TDM/I2S

interface

VBUS –2v..20v

tolerance

Charge

pump

USB

charger

detection

USB Power

supply

USB

precharge

module

USB

digital

(ULPI/

registers

interrupts)

OTG

module

USB2.0

transceiver

Audio loop

control

BCI

digital

USB charger

EXT charger

-control

-status

USB charger

driver

EXT charge

driver

VBAT

removal

discharger

VBAT –2v..20v

tolerance

MADC

digital

state-machine

MADC analog

(SAR-Vref)

Secondary

interrupt handler

SIH

SmartReflex

Vibrator

control (D)

Slave OCP

wrapper

13 MHz/32 kHz

RTC

32 kHz

Clock slicer

Thermal monitor

system

RC oscillator

Power control

(BBS-backup

VRRTC-UVLO)

Power provider

(LDOs-DCDCs)

Power references

(Vref-Iref-BandGap)

OCP SR

TPS65951

www.ti.com

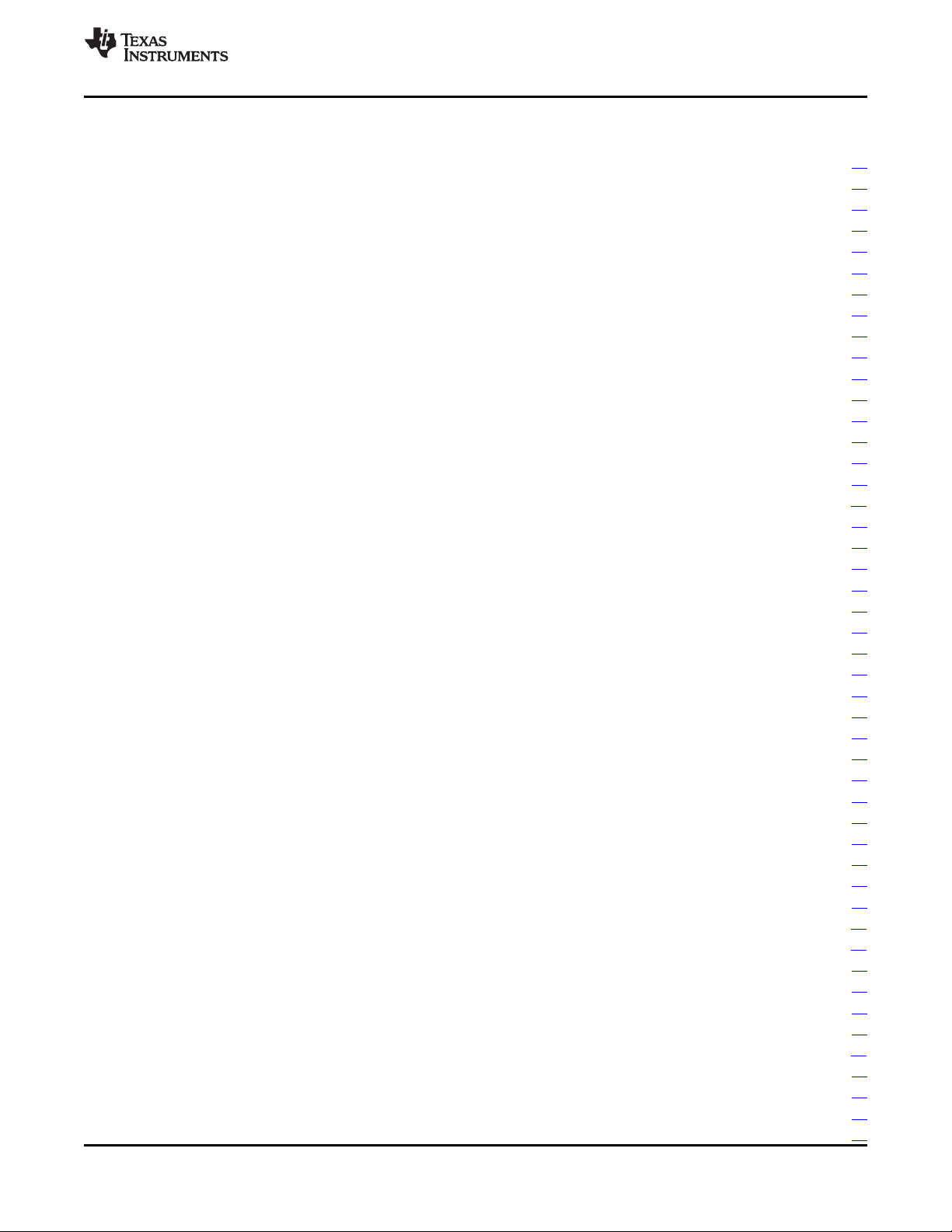

1.1 TPS65951 Block Diagram

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

Copyright © 2010–2012, Texas Instruments Incorporated Introduction 13

Figure 1-1. TPS65951 Block Diagram

Submit Documentation Feedback

Product Folder Link(s): TPS65951

Page 14

9,60 TYP

0,80

0,80

N

M

L

K

J

H

G

F

E

D

C

B

A

1 2 3 4 5

Bottom View

6 7 8 9 10 11 12 13

SWCS053-002

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

2 Terminal Description

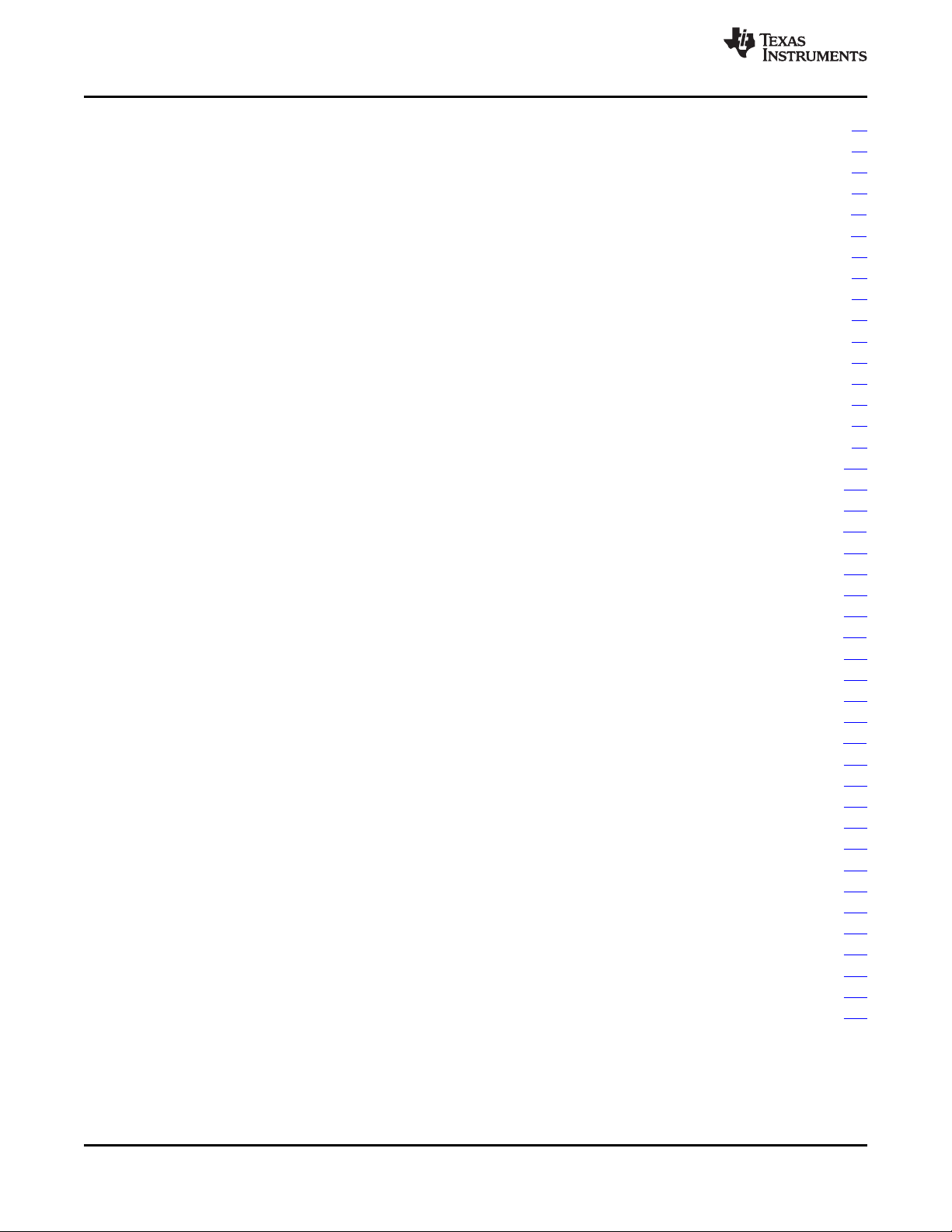

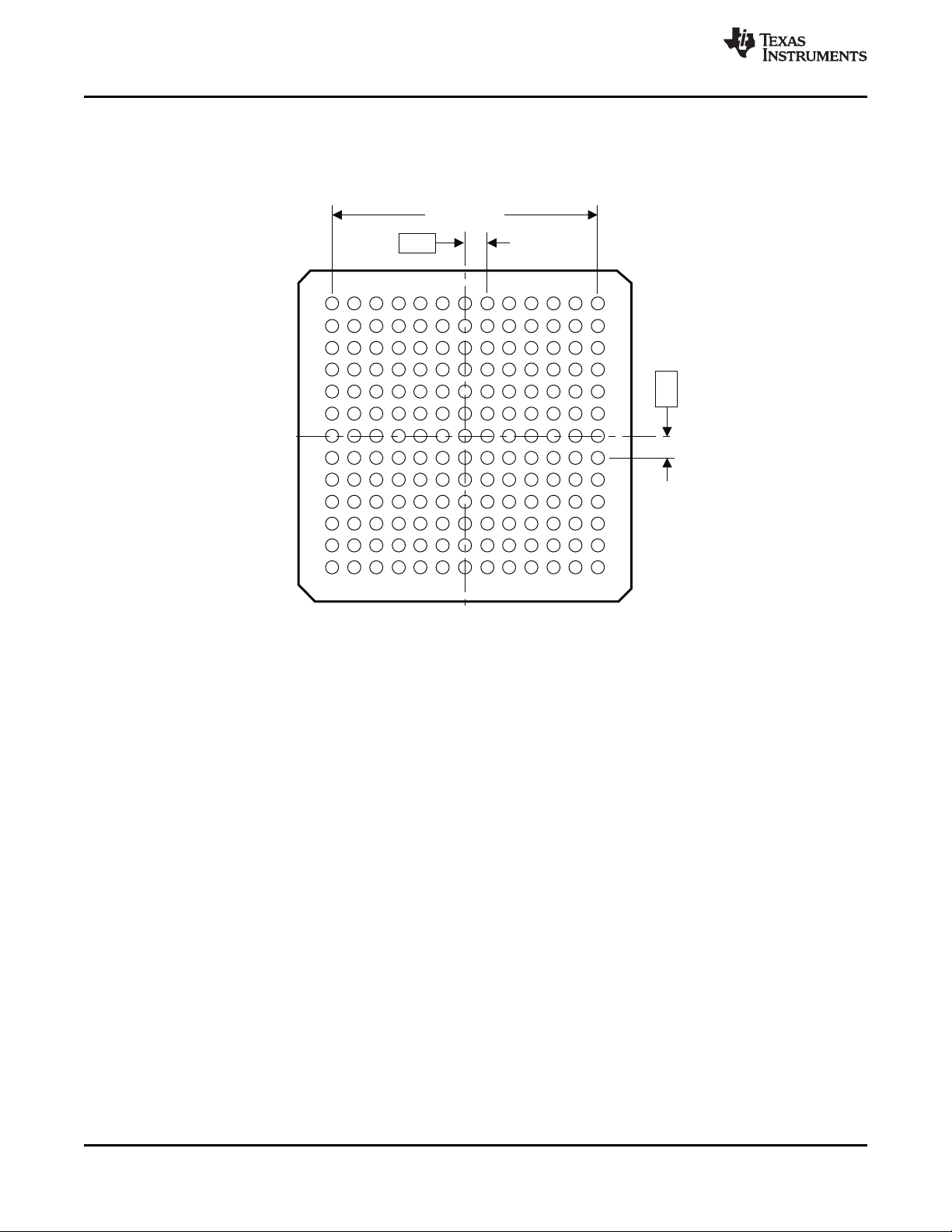

Figure 2-1 illustrates the ball locations for the 169-ball plastic ball grid array (PBGA) package and is used

in conjunction with Table 2-1 to locate signal names and ball grid numbers.

www.ti.com

Figure 2-1. PBGA Bottom View

2.1 Corner Balls

The four corner balls (TEST, TESTV1, TEST.RESET, and TESTV2) are not useable for functional pins.

14 Terminal Description Copyright © 2010–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65951

Page 15

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

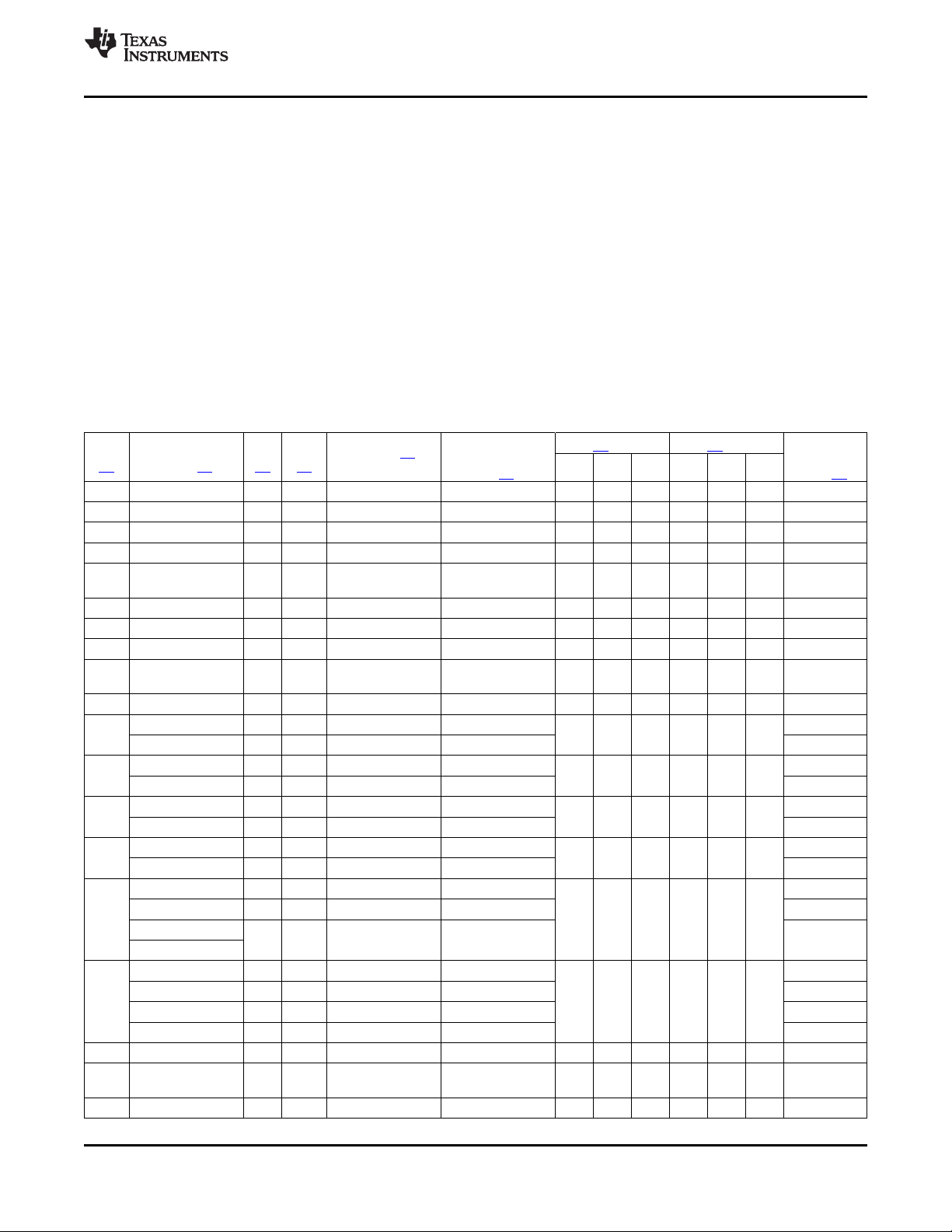

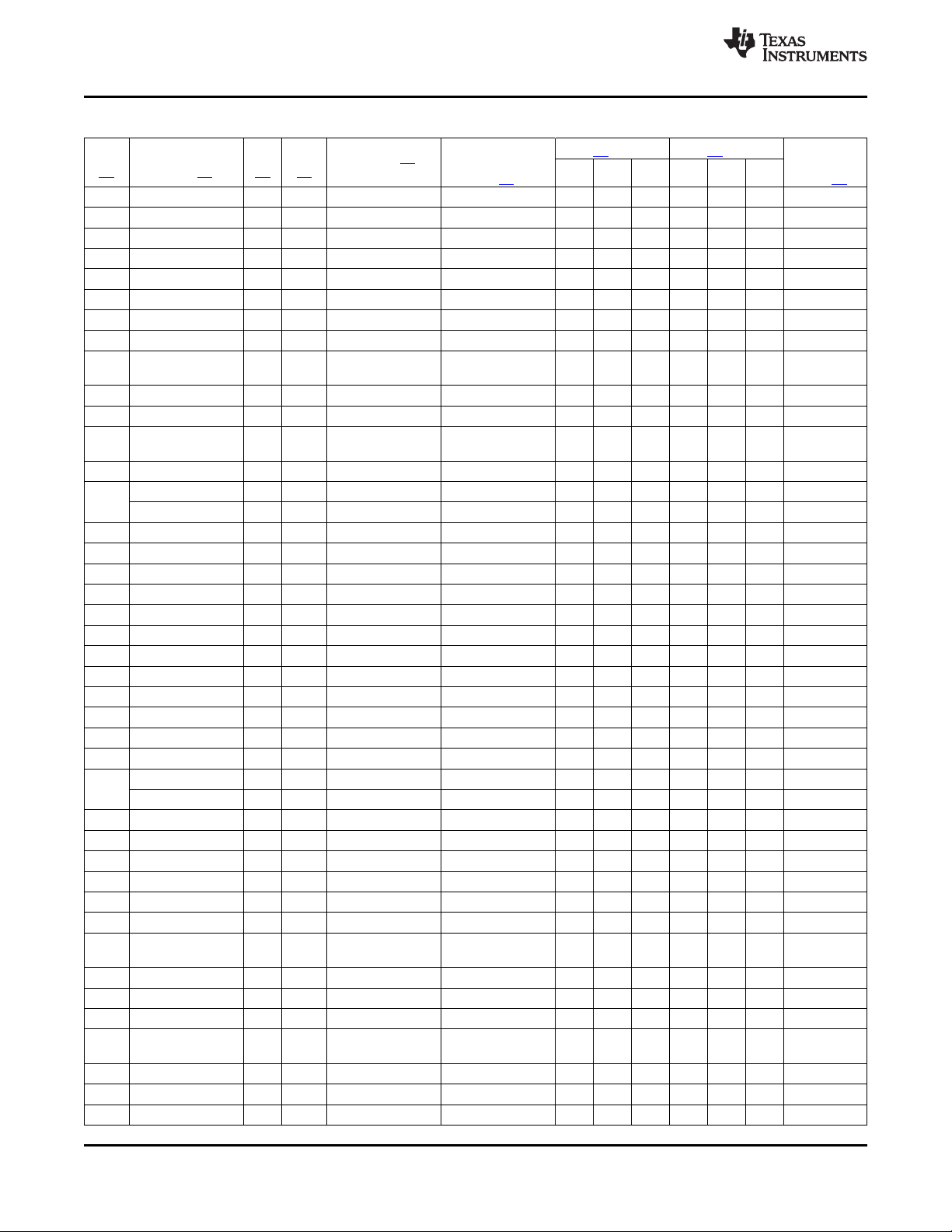

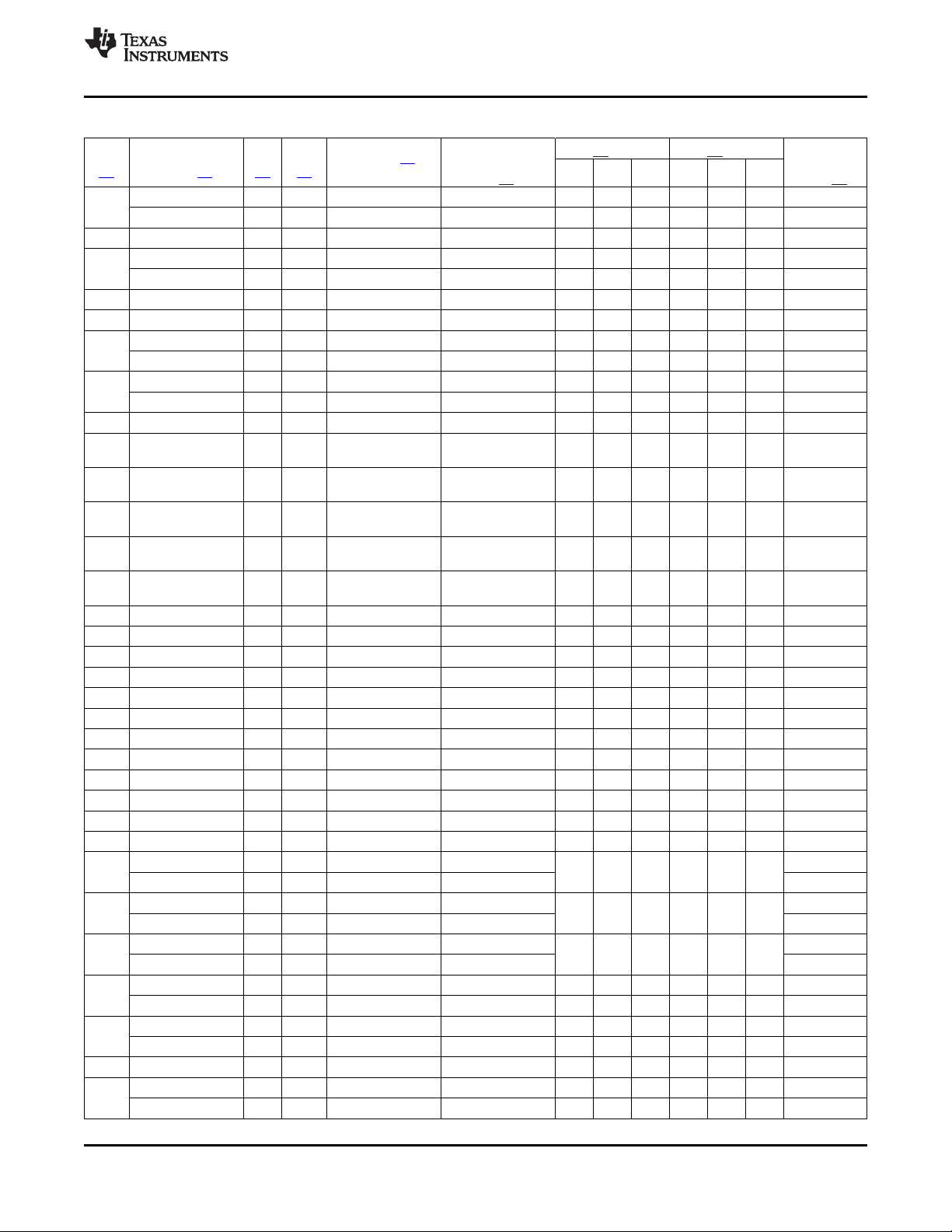

2.2 Ball Characteristics

Table 2-1 describes the terminal characteristics and the signals multiplexed on each pin. The following list

describes the table column headers:

1. BALL: ball number(s) associated with each signal(s)

2. PIN NAME: the names of all the signals that are multiplexed on each ball

3. A/D: analog or digital signal

4. TYPE: the terminal type when a particular signal is multiplexed on the terminal

5. REFERENCE LEVEL: the voltage applied to the I/O cell (see Section 6 and Section 8 for values).

6. PU/PD: denotes the presence of an internal pullup or pulldown. Pullups and pulldowns can be enabled

or disabled via software.

7. BUFFER STRENGTH: drive strength of the associated output buffer

8. ESD RAIL: power reference for ESD protection

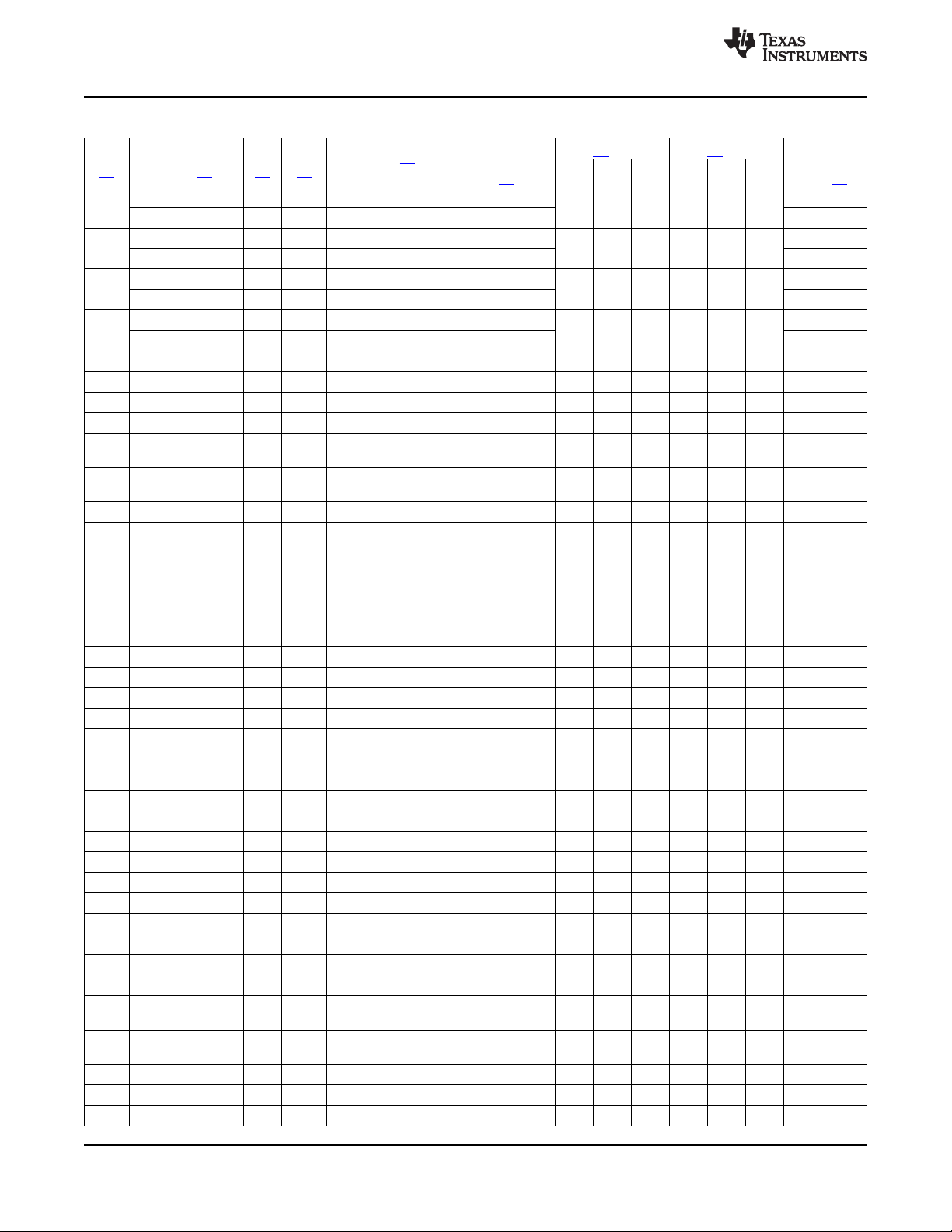

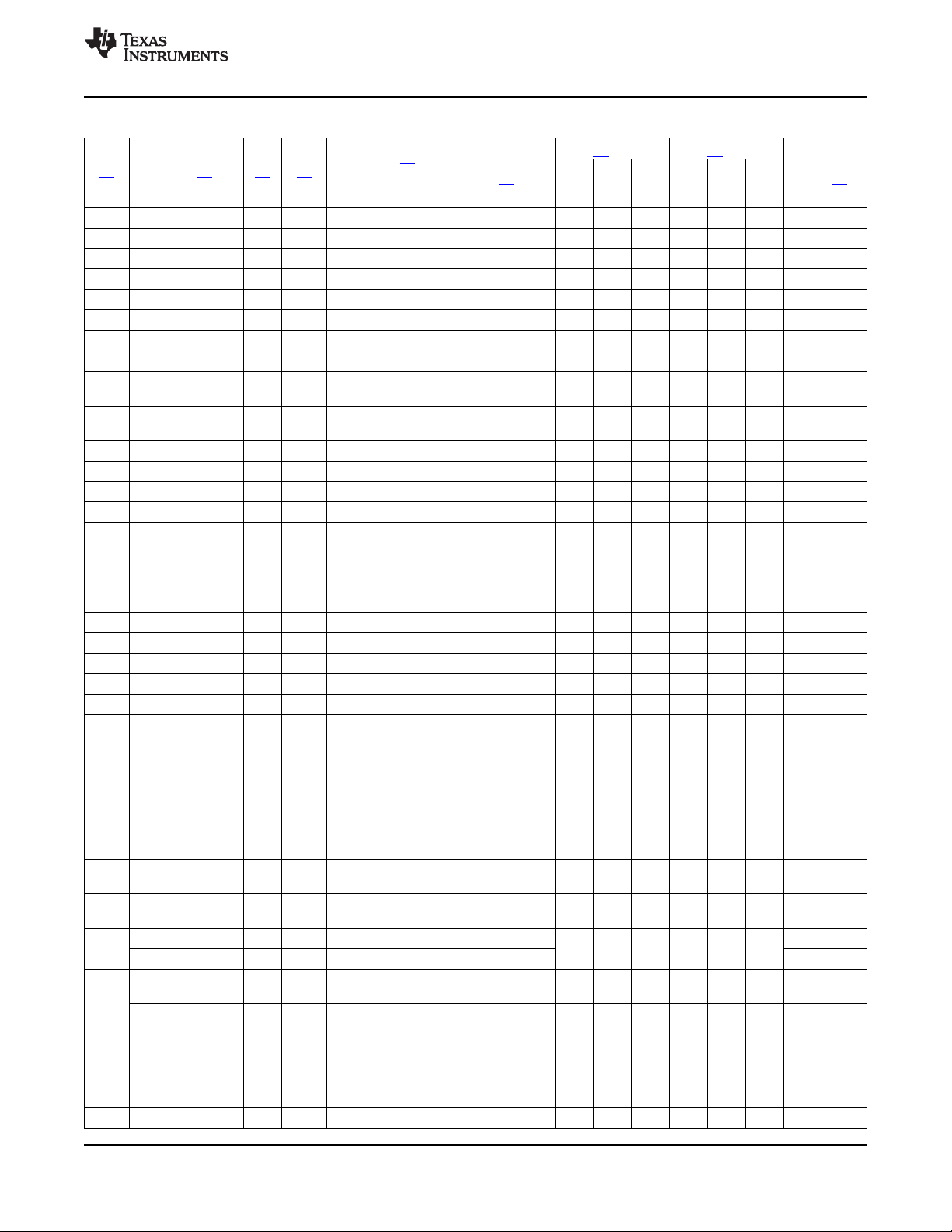

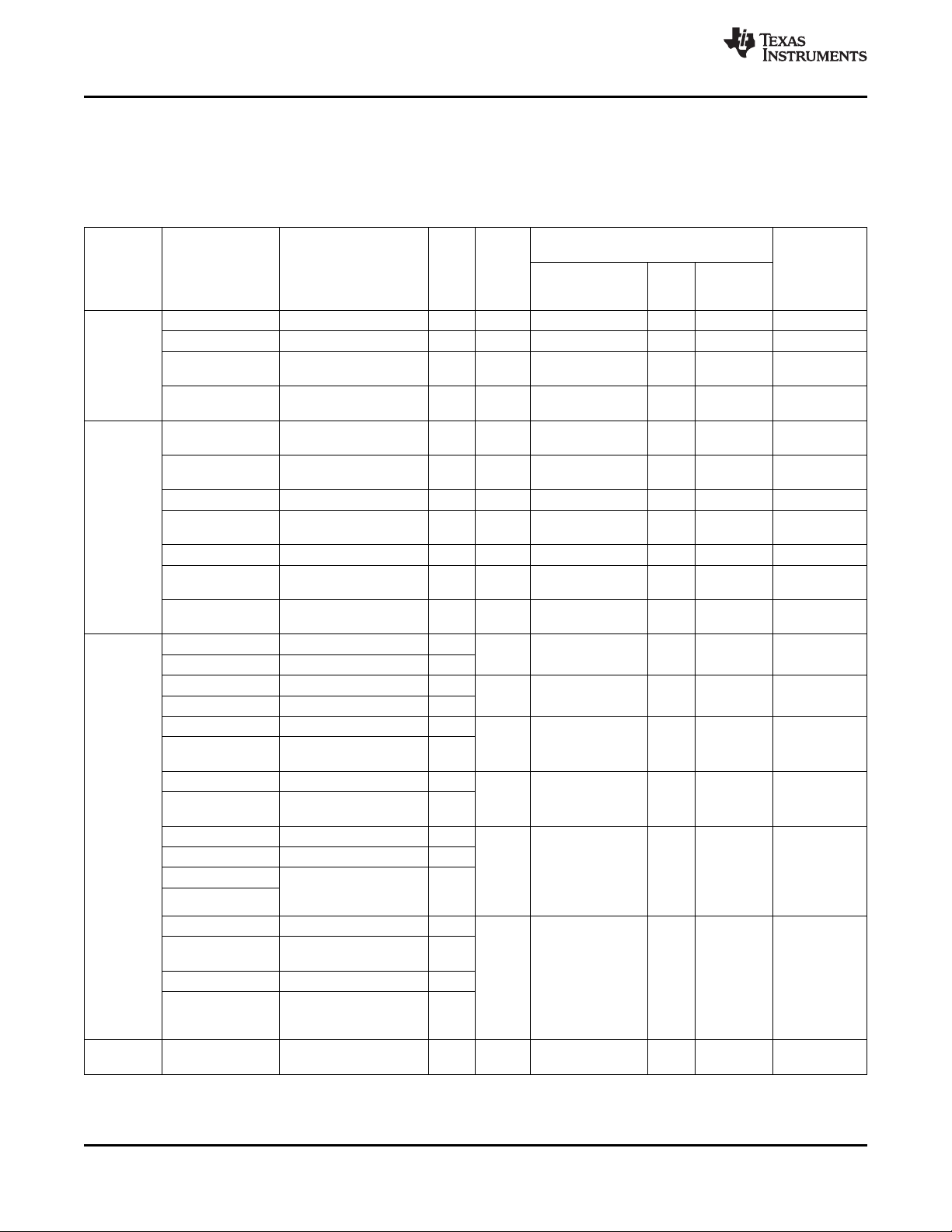

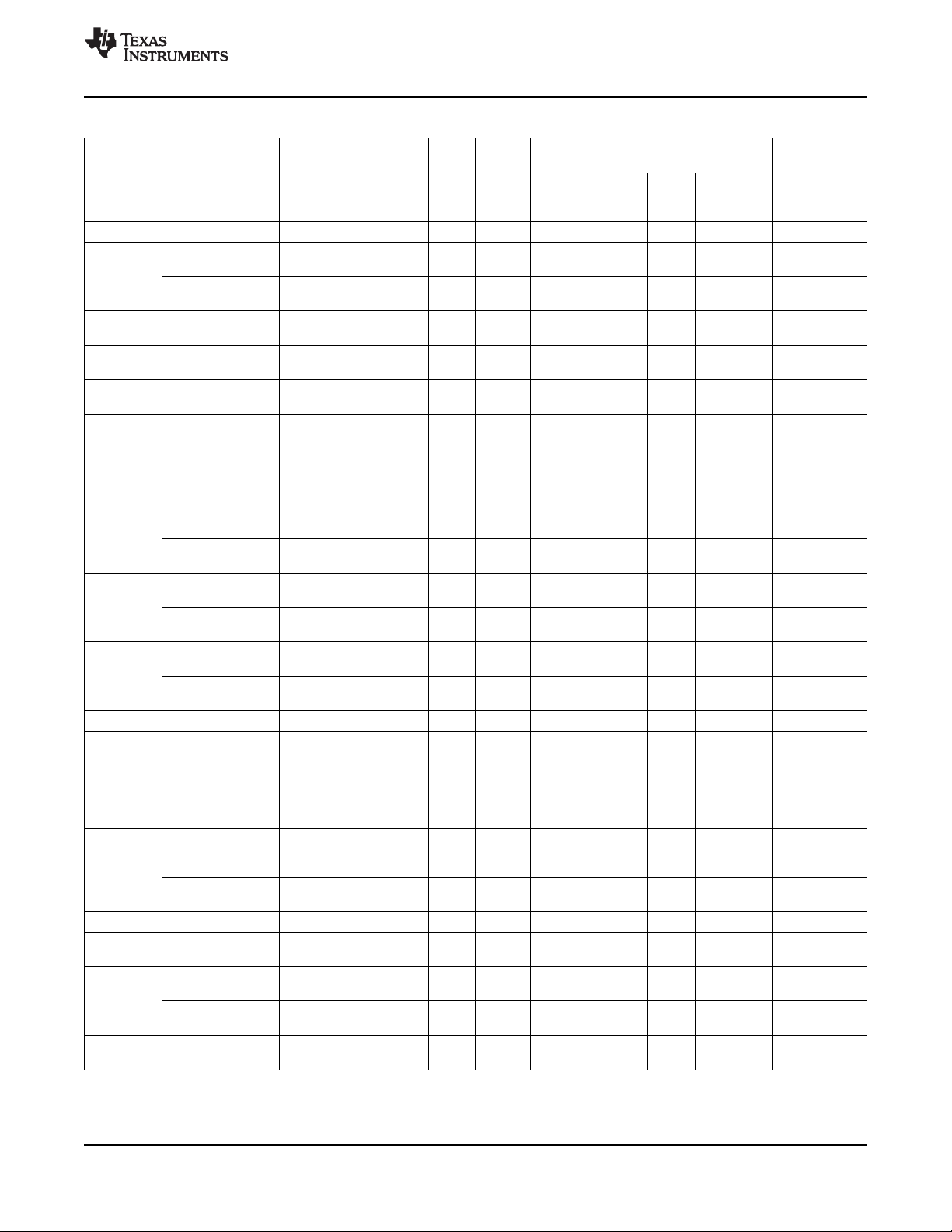

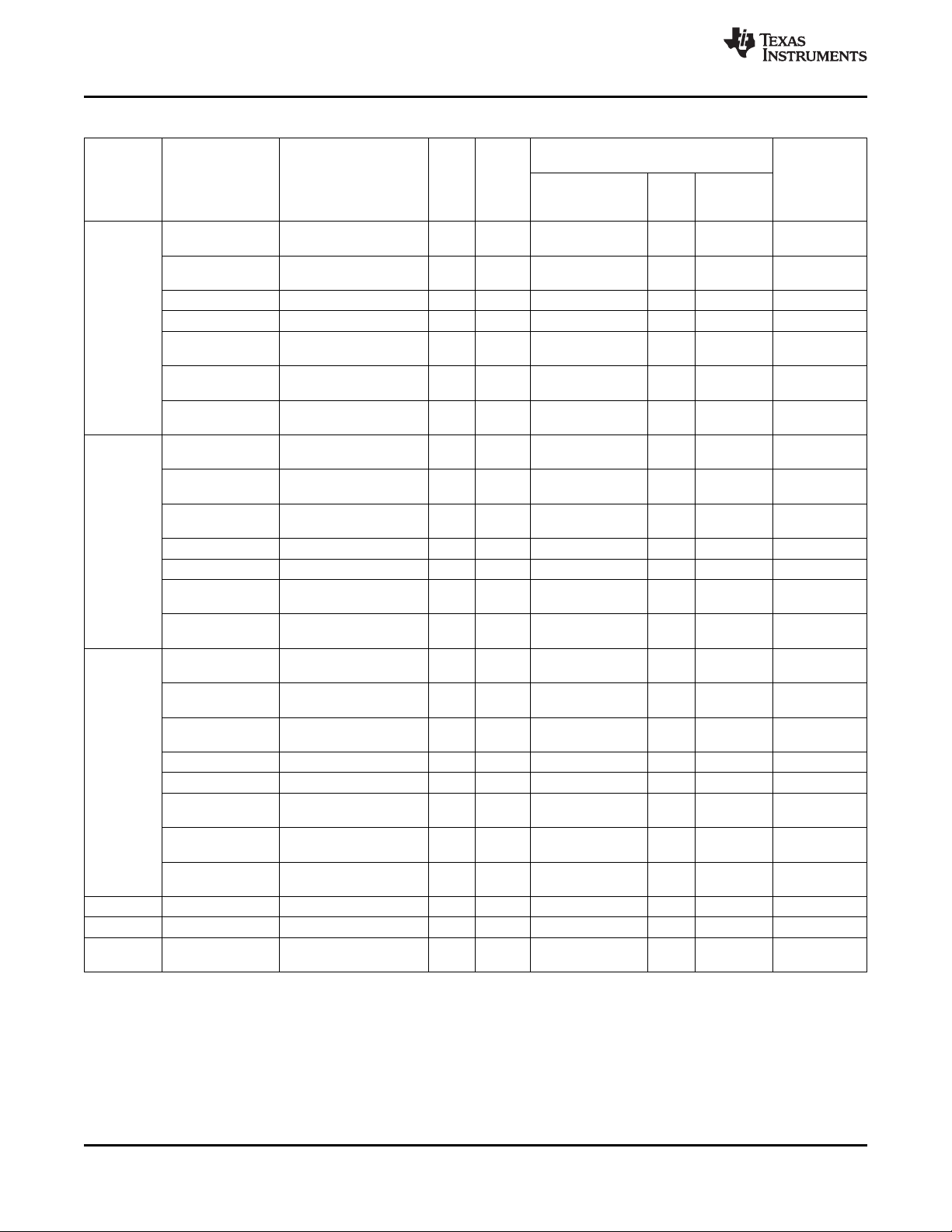

Table 2-1. Ball Characteristics

REFERENCE PU[6] (kΩ)

BALL PIN A/D TYPE ESD RAIL[8]

[1] NAME[2] [3] [4] VDD

K1 ADCIN0 A I/O ADCIN0 VINTANA1.OUT

G3 ADCIN1 A I/O None VINTANA1.OUT

F4 ADCIN2 A I VINTANA2.OUT VINTANA2.OUT

J5 USBCHRG_ENZ A O VPRECH VPRECH 4

H5 USBCHRG_STAT A I VPRECH VPRECH 65 139

Z

K4 VPROG A I None VPP

L1 VPRECH A O None VPRECH

K6 CHRG_DET_N A O VPRECH VPRECH 4

K12 VREFGND A Power None GND

GND

L5 VBAT A Power AGND VBAT

M8 GPIO.0/CD1 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 8

JTAG.TDO D I/O IO.1P8 IO.1P8 8

L9 GPIO.1/CD2 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 2

JTAG.TMS D I IO.1P8 IO.1P8

J3 GPIO.2 D I/O IO.1P8 IO.1P8 156 220 450 59 100 144 2

TEST1 D I/O IO.1P8 IO.1P8 2

L10 GPIO.15 D I/O IO.1P8 IO.1P8 156 220 450 59 100 144 2

TEST2 D I/O IO.1P8 IO.1P8 2

K3 GPIO.6 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 2

PWM0 D O IO.1P8 IO.1P8 4

TEST3 D I/O IO.1P8 IO.1P8 2

CLKOK

M13 GPIO.7 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 2

VIBRA.SYNC D I IO.1P8 IO.1P8

PWM1 D O IO.1P8 IO.1P8 4

TEST4 D I/O IO.1P8 IO.1P8 2

L11 START.ADC D I IO.1P8 IO.1P8

E8 SYSEN D Open IO.1P8 IO.1P8 4.7 7.35 10 2

drain/I

F6 CLKEN D O IO.1P8 IO.1P8 2

(3)

LEVEL STRENGTH

RL[5] (mA)[7]

MIN TYP MAX MIN TYP MAX

(4)

PD[6] (kΩ)

(4)

BUFFER

Copyright © 2010–2012, Texas Instruments Incorporated Terminal Description 15

Submit Documentation Feedback

Product Folder Link(s): TPS65951

Page 16

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

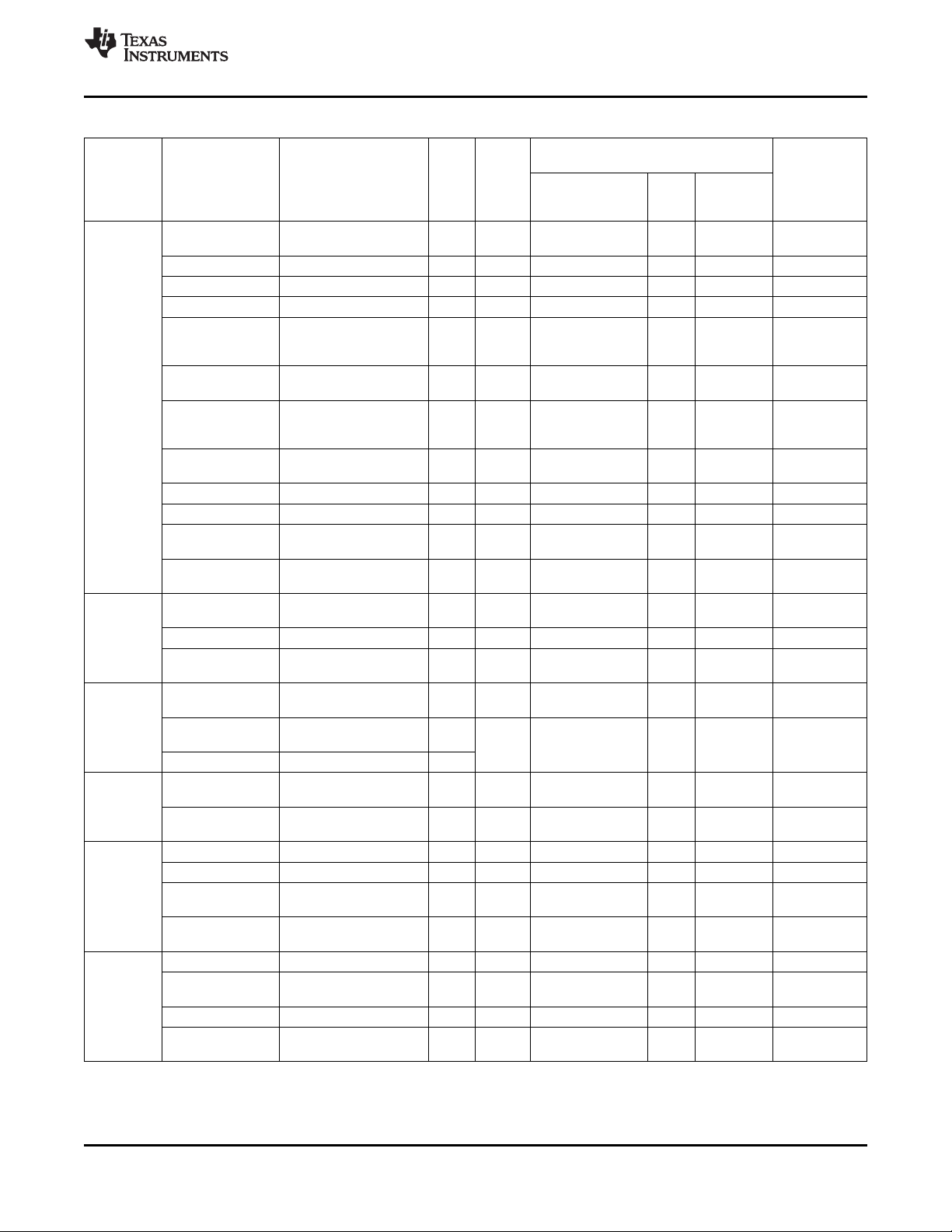

Table 2-1. Ball Characteristics (continued)

BALL PIN A/D TYPE ESD RAIL[8]

[1] NAME[2] [3] [4] VDD

REFERENCE PU[6] (kΩ)

(3)

LEVEL STRENGTH

RL[5] (mA)[7]

MIN TYP MAX MIN TYP MAX

(4)

PD[6] (kΩ)

B13 CLKREQ D I IO.1P8 IO.1P8 60 100 146

B10 INT1 D O IO.1P8 IO.1P8 2

C10 NRESPWRON D O IO.1P8 IO.1P8 2

A11 NRESWARM D I IO.1P8 IO.1P8 2

F7 PWRON D I VBAT.RIGHT VBAT

C11 NSLEEP1 D I IO.1P8 IO.1P8

J13 BOOT0 A/D I/O VPLLA3R.IN VBAT

G10 BOOT1 A/D I/O VPLLA3R.IN VBAT

D8 REGEN D Open VBAT.LEFT VBAT 5.5 8 12 2

Drain

B7 MSECURE D I IO.1P8 IO.1P8

K13 VREF A Power None VREF

G7 AGND A Power None GND

GND

C4 I2C.SR.SDA D I/O IO.1P8 IO.1P8 2.5 3.4 12

B5 VMODE2 D I IO.1P8 IO.1P8 2

I2C.SR.SCL D I/O IO.1P8 IO.1P8 2.5 3.4 12

E5 I2C.CNTL.SDA D I/O IO.1P8 IO.1P8 2.5 3.4 12

D5 I2C.CNTL.SCL D I IO.1P8 IO.1P8 2.5 3.4 12

M1 PCM.VCK D I/O IO.1P8 IO.1P8 2

L4 PCM.VDR D I/O IO.1P8 IO.1P8 2

H8 PCM.VDX D I/O IO.1P8 IO.1P8 2

N12 PCM.VFS D I/O IO.1P8 IO.1P8 2

J4 I2S.CLK D I/O IO.1P8 IO.1P8 2

K2 I2S.SYNC D I/O IO.1P8 IO.1P8 2

H3 I2S.DIN D I IO.1P8 IO.1P8 2

H4 I2S.DOUT D O IO.1P8 IO.1P8 2

D2 MIC.MAIN.P A I VINTANA1.OUT MICBIAS1.OUT

E2 MIC.MAIN.M A I VINTANA1.OUT MICBIAS1.OUT

F5 MIC.SUB.P A I VINTANA1.OUT MICBIAS2.OUT

DIG.MIC.0 A I VINTANA1.OUT VMIC1.OUT

G5 MIC.SUB.M A I VINTANA1.OUT MICBIAS2.OUT

E4 HSMIC.P A I VINTANA1.OUT VINTANA2.OUT

E3 HSMIC.M A I VINTANA1.OUT VINTANA2.OUT

A7 VBAT.LEFT A Power VINTANA1.OUT

B8 IHF.LEFT.P A O VINTANA1.OUT

A8 IHF.LEFT.M A O VINTANA1.OUT

(2)

VBAT

(2)

VBAT

(2)

VBAT

C8 GND.LEFT A Power None GND

GND

A10 VBAT.RIGHT A Power VINTANA1.OUT

B9 IHF.RIGHT.P A O VINTANA1.OUT

A9 IHF.RIGHT.M A O VINTANA1.OUT

(2)

VBAT

(2)

VBAT

(2)

VBAT

C9 GND.RIGHT A Power None GND

GND

C6 EAR.P A O IO.1P8

D6 EAR.M A O IO.1P8

C5 HSOL A O IO.1P8

(2)

(2)

(2)

VINTANA2.OUT

VINTANA2.OUT

VINTANA2.OUT

(4)

www.ti.com

BUFFER

16 Terminal Description Copyright © 2010–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65951

Page 17

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

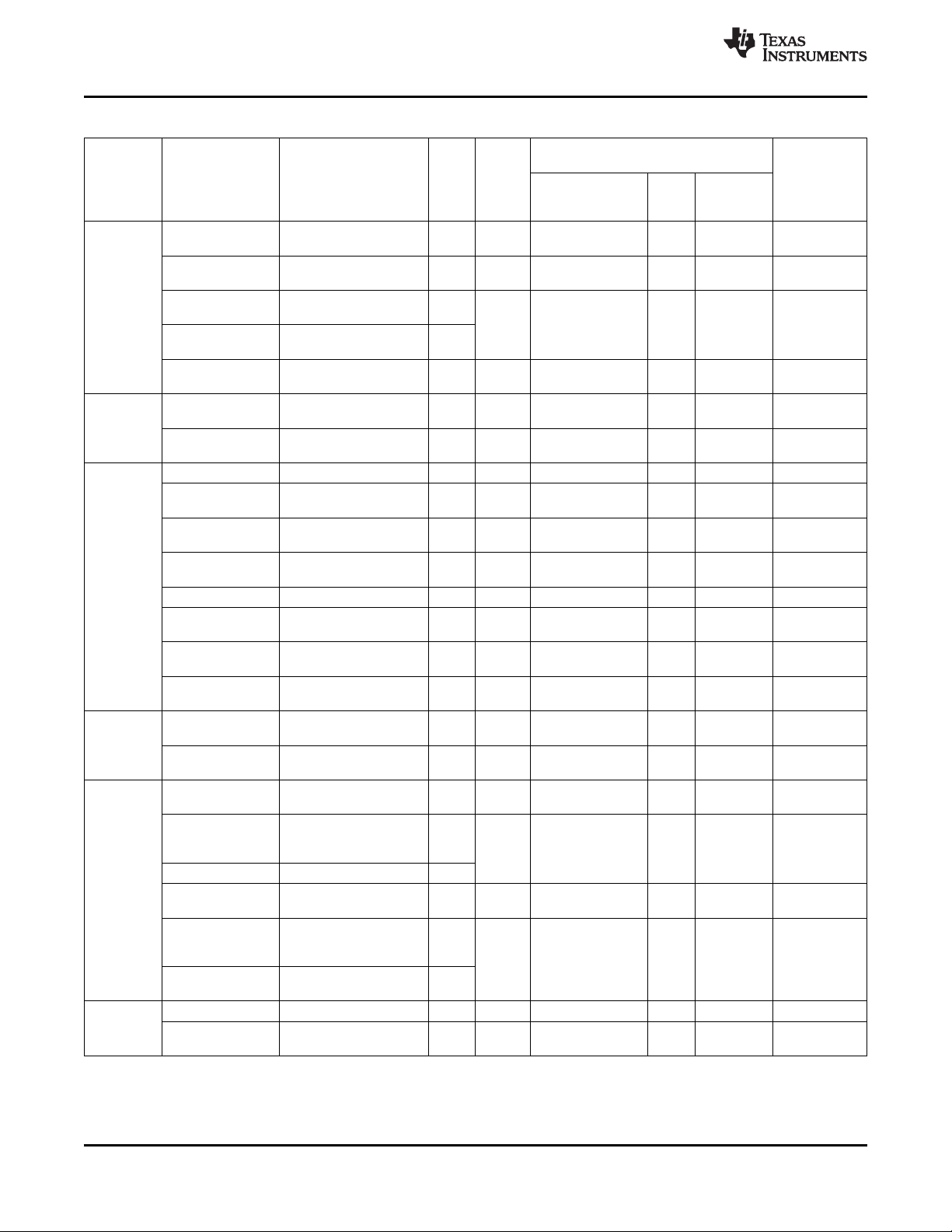

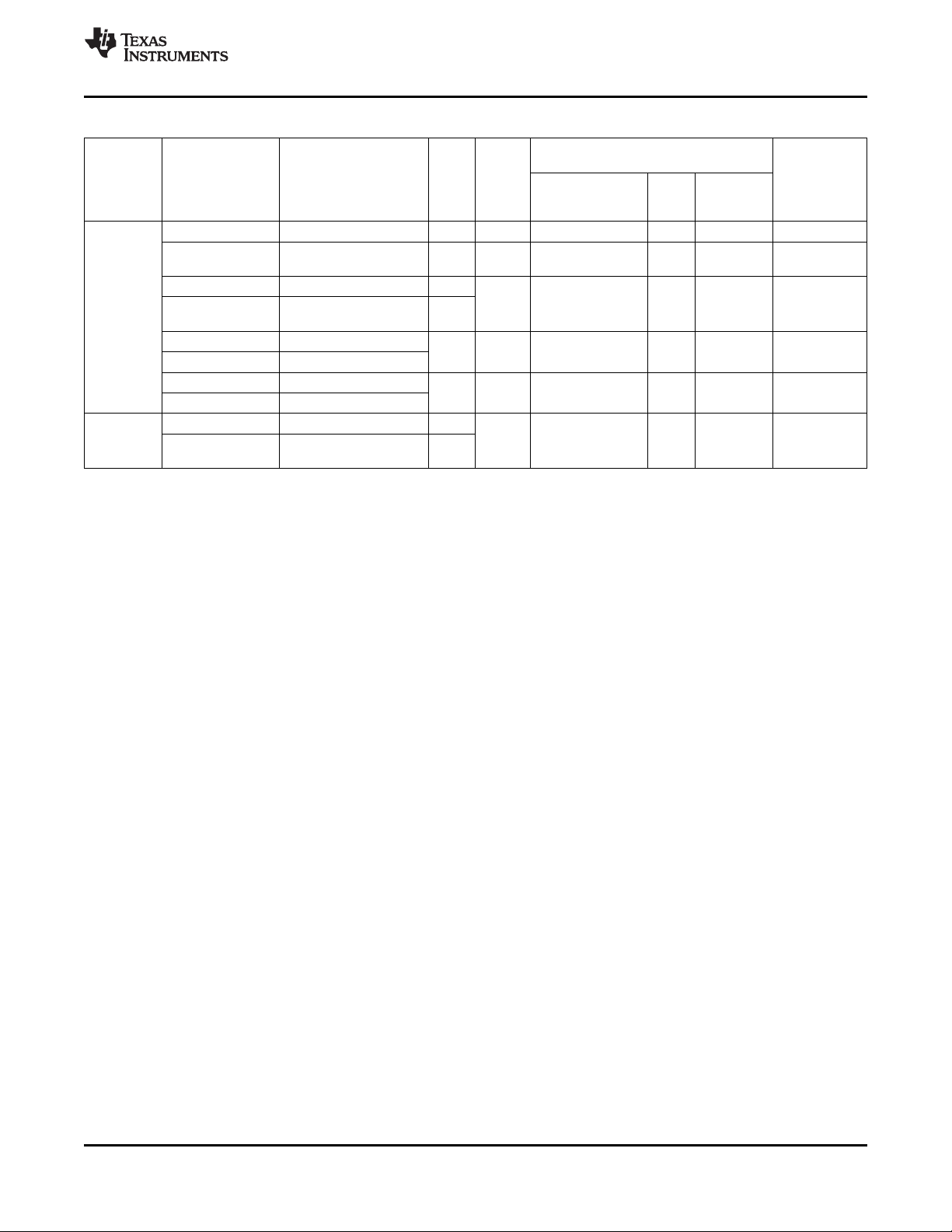

Table 2-1. Ball Characteristics (continued)

BALL PIN A/D TYPE ESD RAIL[8]

[1] NAME[2] [3] [4] VDD

E6 PreDriv.LEFT A O IO.1P8

VMID A Power IO.1P8

A5 HSOR A O IO.1P8

D7 PreDriv.RIGHT A O IO.1P8

ADCIN7 A I IO.1P8

(2)

(2)

(2)

(2)

(2)

REFERENCE PU[6] (kΩ)

(3)

LEVEL STRENGTH

RL[5] (mA)[7]

VINTANA2.OUT

VINTANA2.OUT

VINTANA2.OUT

VINTANA2.OUT

VINTANA2.OUT

MIN TYP MAX MIN TYP MAX

(4)

PD[6] (kΩ)

E1 AUXL A I VINTANA1.OUT VINTANA2.OUT

F3 AUXR A I VINTANA1.OUT VINTANA2.OUT

B1 MICBIAS1.OUT A Power VINTANA2.OUT VINTANA2.OUT

VMIC1.OUT A Power VINTANA2.OUT VINTANA2.OUT

C1 MICBIAS2.OUT A Power VINTANA2.OUT VINTANA2.OUT

VMIC2.OUT A Power VINTANA2.OUT VINTANA2.OUT

D3 VHSMIC.OUT A Power VINTANA2.OUT VINTANA2.OUT

D1 MICBIAS.GND Power None GND

GND

G4 AVSS1 A Power None GND

GND

K7 AVSS2 A Power None GND

GND

K11 AVSS3 A Power None GND

GND

A6 AVSS4 A Power None GND

GND

K8 ADCIN3 A I VUSB.3P1 VINTANA2.OUT

K9 MANU_BRIX D O IO.1P8 IO.1P8

J6 32KCLKOUT D O IO.1P8 IO.1P8

L12 32KXIN A I VRTC.OUT IO.1P8

L13 32KXOUT A O VRTC.OUT IO.1P8

B11 HFCLKIN A I IO.1P8 IO.1P8

N8 HFCLKOUT D O IO.1P8 IO.1P8

H7 VBUS A Power None VBUS

J7 DP/UART3.RXD A I/O None VBUS 2

J8 DN/UART3.TXD A I/O None VBUS 2

L8 ID A I/O None VBUS 2

J9 UCLK D I/O IO.1P8 IO.1P8 16

K10 STP D I IO.1P8 IO.1P8 75 100 202 59 100 144 16

GPIO.9 D I/O IO.1P8 IO.1P8 2

J10 DIR D O IO.1P8 IO.1P8 75 100 202 59 100 144 16

GPIO.10 D I/O IO.1P8 IO.1P8 2

J11 NXT D O IO.1P8 IO.1P8 75 100 202 59 100 144 16

GPIO.11 D I/O IO.1P8 IO.1P8 2

H11 DATA0 D I/O IO.1P8 IO.1P8 16

UART4.TXD D I IO.1P8 IO.1P8

H10 DATA1 D I/O IO.1P8 IO.1P8 16

UART4.RXD D O IO.1P8 IO.1P8 2

G8 DATA2 D I/O IO.1P8 IO.1P8 16

H9 DATA3 D I/O IO.1P8 IO.1P8 60 100 140 60 100 140 16

GPIO.12 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 16

(4)

BUFFER

Copyright © 2010–2012, Texas Instruments Incorporated Terminal Description 17

Submit Documentation Feedback

Product Folder Link(s): TPS65951

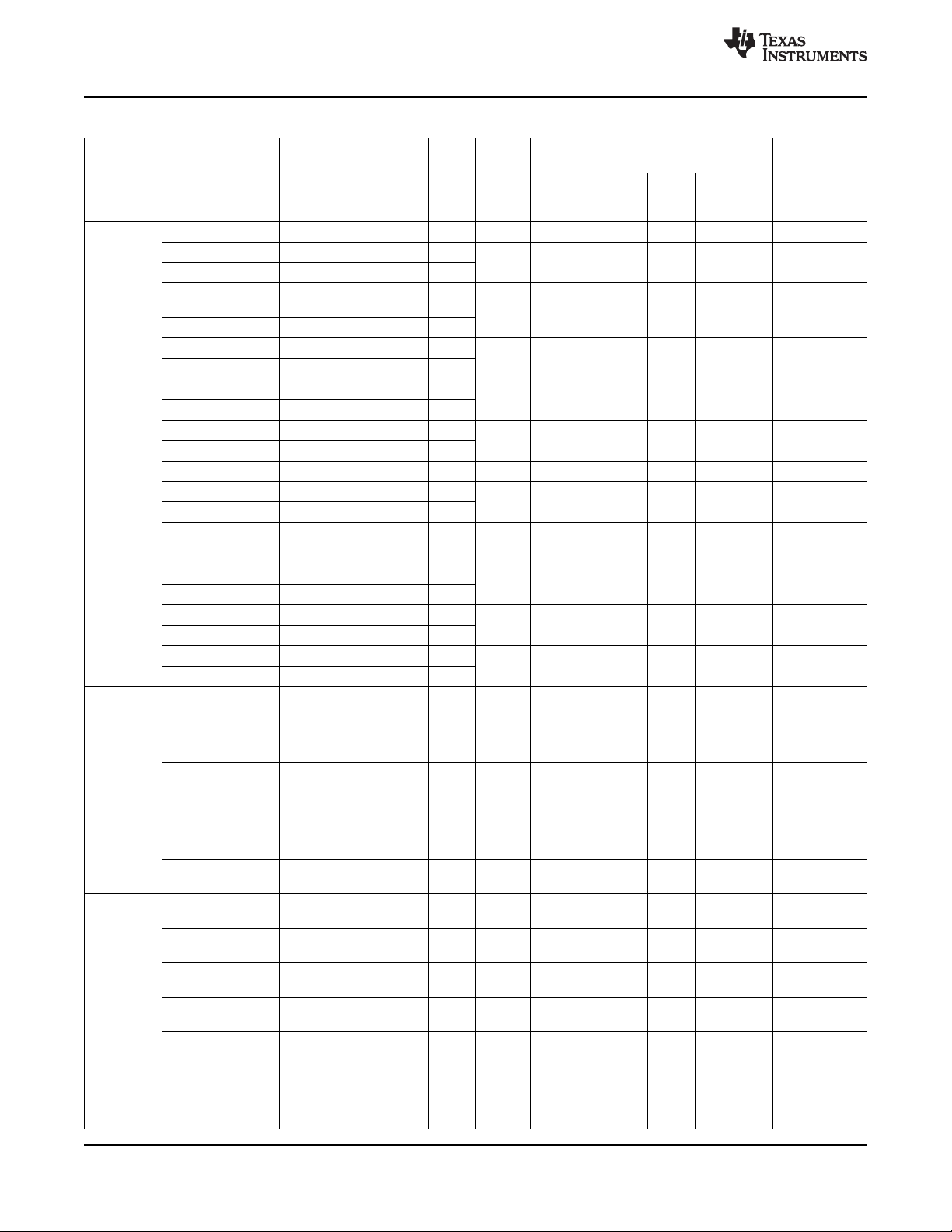

Page 18

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

Table 2-1. Ball Characteristics (continued)

BALL PIN A/D TYPE ESD RAIL[8]

[1] NAME[2] [3] [4] VDD

REFERENCE PU[6] (kΩ)

(3)

LEVEL STRENGTH

RL[5] (mA)[7]

MIN TYP MAX MIN TYP MAX

(4)

PD[6] (kΩ)

F9 DATA4 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 16

GPIO.14 D I/O IO.1P8 IO.1P8 2

F8 DATA5 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 16

GPIO.3 D I/O IO.1P8 IO.1P8 2

E10 DATA6 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 16

GPIO.4 D I/O IO.1P8 IO.1P8 2

E11 DATA7 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144 16

GPIO.5 D I/O IO.1P8 IO.1P8 2

N13 TEST.RESET A/D I None VBAT 30 50 70

N1 TESTV1 A I/O None VBAT

A13 TESTV2 A I/O IO.1P8

(2)

VINTANA2.OUT

A1 TEST D I IO.1P8 IO.1P8 60 100 146

B12 JTAG.TDI/ D I IO.1P8 IO.1P8

BERDATA

D11 JTAG.TCK/ D I IO.1P8 IO.1P8

BERCLK

M5 CP.IN A Power None VBAT/VBUS

N6 CP.CAPP A O VINTUSB1P8.OU CP.CAPP

N5 CP.CAPM A O VINTUSB1P8.OU CP.CAPM

(2)

T

(2)

T

K5 CP.GND A Power None GND

GND

L6 VUSBIN.CPOUT A Power None VBAT

N7 VBAT.USB A Power None VBAT

L7 VUSB.3P1 A Power VUSB.3P1 VUSB.3P1

H1 VAUX12S.IN A Power None VBAT

J2 VAUX1.OUT A Power VAUX1.OUT VAUX1.OUT

J1 VAUX2.OUT A Power VAUX2.OUT VAUX2.OUT

F13 VPLLA3R.IN A Power AGND VBAT

G12 VRTC.OUT A Power None VRTC.OUT

G9 VPLL1.OUT A Power VPPL1.OUT VPLL1.OUT

G13 VPLL2.OUT A Power VPLL2.OUT VPLL2.OUT

F12 VAUX3.OUT A Power VAUX3.OUT VAUX3.OUT

A2 VAUX4.IN A Power None VBAT

B3 VAUX4.OUT A Power VAUX4.OUT VAUX4.OUT

C2 VMMC1.IN A Power None VBAT

B2 VMMC1.OUT A Power VMMC1.OUT VMMC1.OUT

A4 VMMC2.IN A Power None VBAT

B4 VMMC2.OUT A Power VMMC2.OUT VMMC2.OUT

G2 VSL.OUT A Power IO.1P8

(2)

VSL.OUT

M6 VINTUSB1P5.OU A Power None VINTUSB1P5.OU

T T

M7 VINTUSB1P8.OU A Power None VINTUSB1P8.OU

T T

G1 VDAC.IN A Power None VBAT

H2 VDAC.OUT A Power VDAC.OUT VDAC.OUT

H13 VINT.IN A Power None VBAT

(4)

www.ti.com

BUFFER

18 Terminal Description Copyright © 2010–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65951

Page 19

TPS65951

www.ti.com

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

Table 2-1. Ball Characteristics (continued)

REFERENCE PU[6] (kΩ)

BALL PIN A/D TYPE ESD RAIL[8]

[1] NAME[2] [3] [4] VDD

(3)

LEVEL STRENGTH

RL[5] (mA)[7]

MIN TYP MAX MIN TYP MAX

F2 VINTANA1.OUT A Power None VINTANA1.OUT

B6 VINTANA2.OUT A Power VINTANA2.OUT VINTANA2.OUT

F1 VINTANA2.OUT A Power VINTANA2.OUT VINTANA2.OUT

H12 VINTDIG.OUT A Power None VINTDIG.OUT

E12 VDD1.IN A Power VINTDIG.OUT

E13 VDD1.IN A Power VINTDIG.OUT

(2)

VBAT

(2)

VBAT

D12 VDD1.SW A O VDD1.IN VBAT

D13 VDD1.SW A O VDD1.IN VBAT

D10 VDD1.FB A I None

C12 VDD1.GND A Power None GND

GND

C13 VDD1.GND A Power None GND

GND

N9 VDD2.IN A Power VINTDIG.OUT

M9 VDD2.IN A Power VINTDIG.OUT

(2)

VBAT

(2)

VBAT

M12 VDD2.FB A I None

M10 VDD2.SW A O VDD2.IN VBAT

N10 VDD2.SW A O VDD2.IN VBAT

M11 VDD2.GND A Power None GND

GND

N11 VDD2.GND A Power None GND

GND

M4 VIO.IN A Power VINTDIG.OUT

N4 VIO.IN A Power VINTDIG.OUT

(2)

VBAT

(2)

VBAT

L2 VIO.FB A I None

M3 VIO.SW A O VIO.IN VBAT

N3 VIO.SW A O VIO.IN VBAT

N2 VIO.GND A Power None GND

GND

M2 VIO.GND A Power None GND

GND

L3 VIO.GND A Power None GND

GND

J12 BKBAT A Power BKBAT VBACK

E7 IO.1P8 A Power None IO.1P8

G11 DGND A Power None GND

GND

F10 LEDGND A Power None GND

GND

A12 GPIO.13 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144

LEDSYNC D I IO.1P8 IO.1P8

E9 LEDA A Open IO.1P8

(2)

VBAT

Drain

VIBRA.P A Open IO.1P8

(2)

VBAT

Drain

F11 LEDB A Open IO.1P8

(2)

VBAT

Drain

VIBRA.M A Open IO.1P8

(2)

VBAT

Drain

D9 VBATVIBRA A Power IO.1P8

(2)

VBAT

(4)

PD[6] (kΩ)

(4)

BUFFER

Copyright © 2010–2012, Texas Instruments Incorporated Terminal Description 19

Submit Documentation Feedback

Product Folder Link(s): TPS65951

Page 20

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

Table 2-1. Ball Characteristics (continued)

REFERENCE PU[6] (kΩ)

BALL PIN A/D TYPE ESD RAIL[8]

[1] NAME[2] [3] [4] VDD

C3 GPIO.16 D I/O IO.1P8 IO.1P8 75 100 202 59 100 144

DIG.MIC.CLK0 D O IO.1P8 IO.1P8

(1) To avoid reflection on this pin due to impedance mismatch, a serial resistance of 33 Ω needs to be added.

(2) VDD rail used as bias in ESD protection during functional mode.

(3) AGND is used as ESD Ground for all PADs.

(4) PUs/PDs are enabled when TPS65952 is in any other state than NO SUPPLY

(3)

LEVEL STRENGTH

RL[5] (mA)[7]

MIN TYP MAX MIN TYP MAX

(4)

PD[6] (kΩ)

(4)

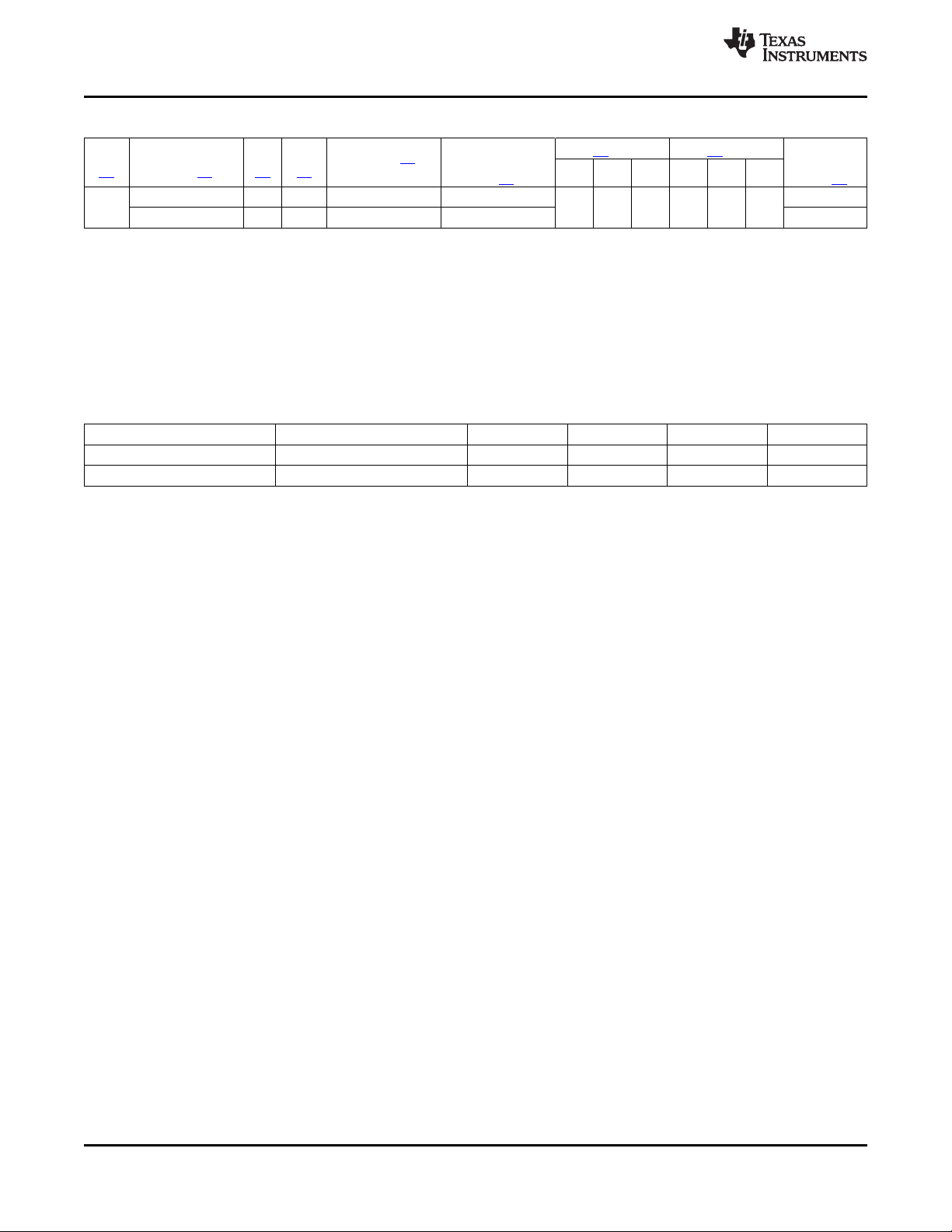

2.2.1 ESD Electrical Parameters

ESD conditions for CDM and HBM listed in Table 2-2.

Table 2-2. ESD Electrical Parameters

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

CDM stress voltage All pads 500 V

HBM stress voltage All pads 2000 V

www.ti.com

BUFFER

20 Terminal Description Copyright © 2010–2012, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65951

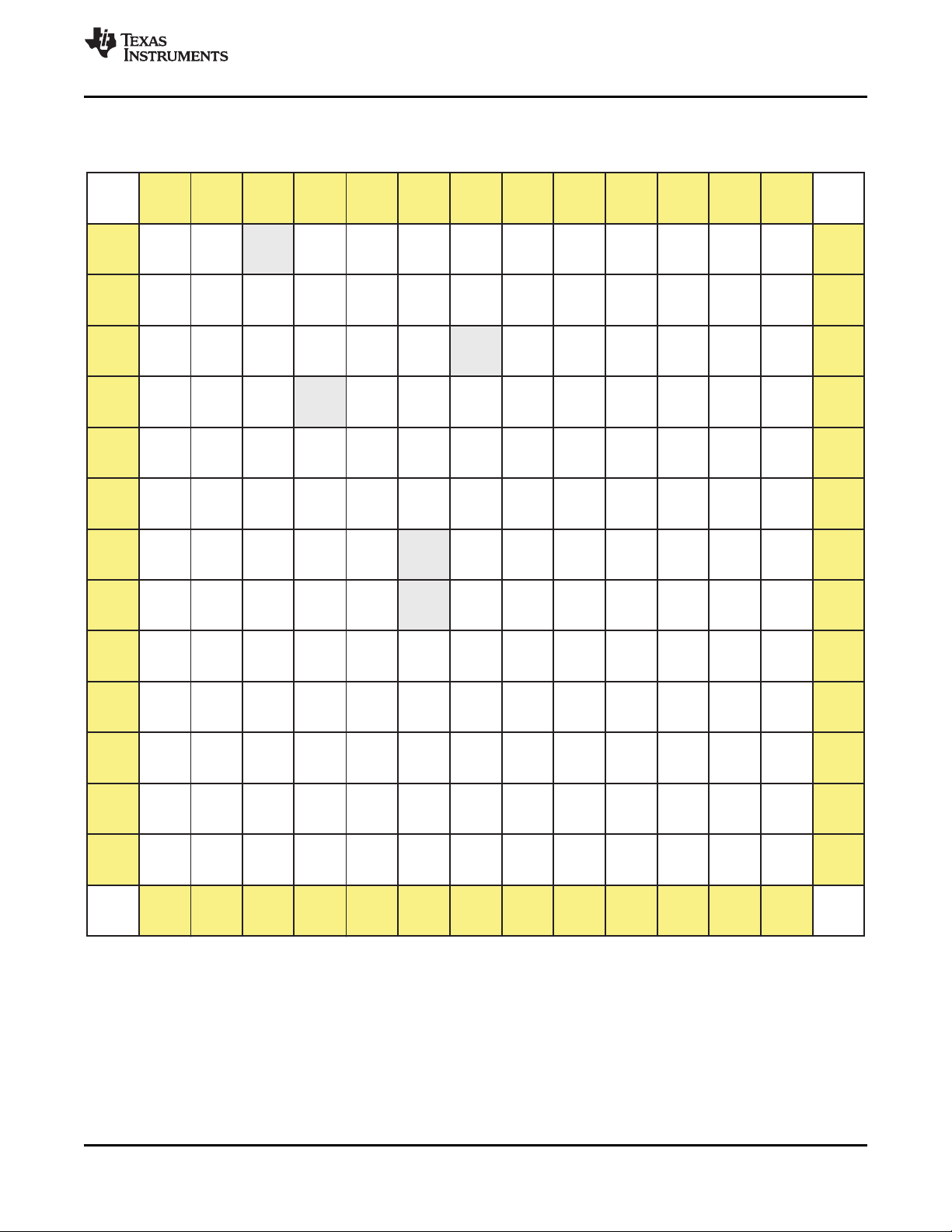

Page 21

SWCS053-092

12345678910111213

A

TEST

VAUX4.IN

Reserved

VMMC2.IN

HSOR

AVSS4

VBAT.LEFT

IHF.LEFT.M

IHF.RIGHT.M

VBAT.RIGHT

NRESWARM

LEDSYNC/

GPIO.13

TESTV2

A

B

MICBIAS1.

OUT/

VMIC1 OUT.

VMMC1.OUT

VAUX4.OUT

VMMC2.OUT

VMODE2/

I2C.SR.SCL

VINTANA2

.OUT

MSECURE

IHF.LEFT.P

IHF.RIGHT.P

INT1

HFCLKIN

JTAG.TDI/

BERDATA

CLKREQ

B

C

MICBIAS2.

OUT/

VMIC2 OUT.

VMMC1.IN

GPIO16/

DIG.MIC.

CLK0

I2C.SR.SDA

HSOL

EAR.P

Reserved

GND.LEFT

GND.RIGHT

NRESPWRON

NSLEEP1

VDD1.GND

VDD1.GND

C

D

MICBIAS.

GND

MIC.MAIN.P

VHSMIC.OUT

Reserved

I2C.CNTL.

SCL

EAR.M

PreDriv.

RIGHT/

ADCIN7

REGEN

VBATVIBRA

VDD1.FB

JTAG.TCK/

BERCLK

VDD1.SW

VDD1.SW

D

E

AUXL

MIC.MAIN.M

HSMIC.M

HSMIC.P

I2C.CNTL.

SDA

PreDriv

.LEFT/

VMID

IO.1P8

SYSEN

LEDA/

VIBRA.P

DATA6/

GPIO.4

DATA7/

GPIO.5

VDD1.IN

VDD1.IN

E

F

VINTANA2.

OUT

VINTANA1.

OUT

AUXR

ADCIN2

MIC.SUB./

DIG.MIC.0

CLKEN

PWRON

DATA5/

GPIO.3

DATA4/

GPIO.14

LEDGND

LEDB/

VIBRA.M

VAUX3.OUT

VPLLA3R.IN

F

G

VDAC.IN

VSL.OUT

ADCIN1

AVSS1

MIC.SUB.M

Reserved

AGND

DATA2

VPPL1.OUT

BOOT1

DGND

VRTC.OUT

VPLL2.OUT

G

H

VAUX12S.IN

VDAC.OUT

I2S.DIN

I2S.DOUT

USBCHRG

_STATZ

Reserved

VBUS

PCM.VDX

DATA3/

GPIO.12

DATA1/

UART4.RXD

DATA0/

UART4.TXD

VINTDIG.OUT

VINT.IN

H

J

VAUX2.OUT

VAUX1.OUT

GPIO.2/

TEST1

I2S.CLK

USBCHRG

_ENZ

32KCLKOUT

DP/UART3.

RXD

DN/

UART3.TXD

UCLK

DIR/

GPIO.10

NXT/

GPIO.11

BKBAT

BOOT0

J

K

ADCIN0

I2S.SYNC

GPIO6/

CLKOK/

PWM0/

TEST3

VPROG

CP.GND

CHRG_

DET_N

AVSS2

ADCIN3

MANU_BRIX

STP/GPIO.9

AVSS3

VREFGND

VREF

K

L

VPRECH

VIO.FB

VIO.GND

PCM.VDR

VBAT

VUSBIN.

CPOUT

VUSB.3P1

ID

GPIO.1/CD2/

JTAG.TMS

GPIO.15/

TEST2

START.ADC

32KXIN

32KXOUT

L

M

PCM.VCK

VIO.GND

VIO.SW

VIO.IN

CP.IN

VINTUSB1

P5.OUT

VINTUSB1

P8.OUT

GPIO.0/CD1/

JTAG.TD0

VDD2.IN

VDD2.SW

VDD2.GND

VDD2.FB

GPIO.7/

VIBRA.SY

NC.PWM1/

TEST4

M

N

TESTV1

VIO.GND

VIO.SW

VIO.IN

CP.CAPM

CP.CAPP

VBAT.USB

HFCLKOUT

VDD2.IN

VDD2.SW

VDD2.GND

PCM.VFS

TEST.RES

ET

N

12345678910111213

TPS65951

www.ti.com

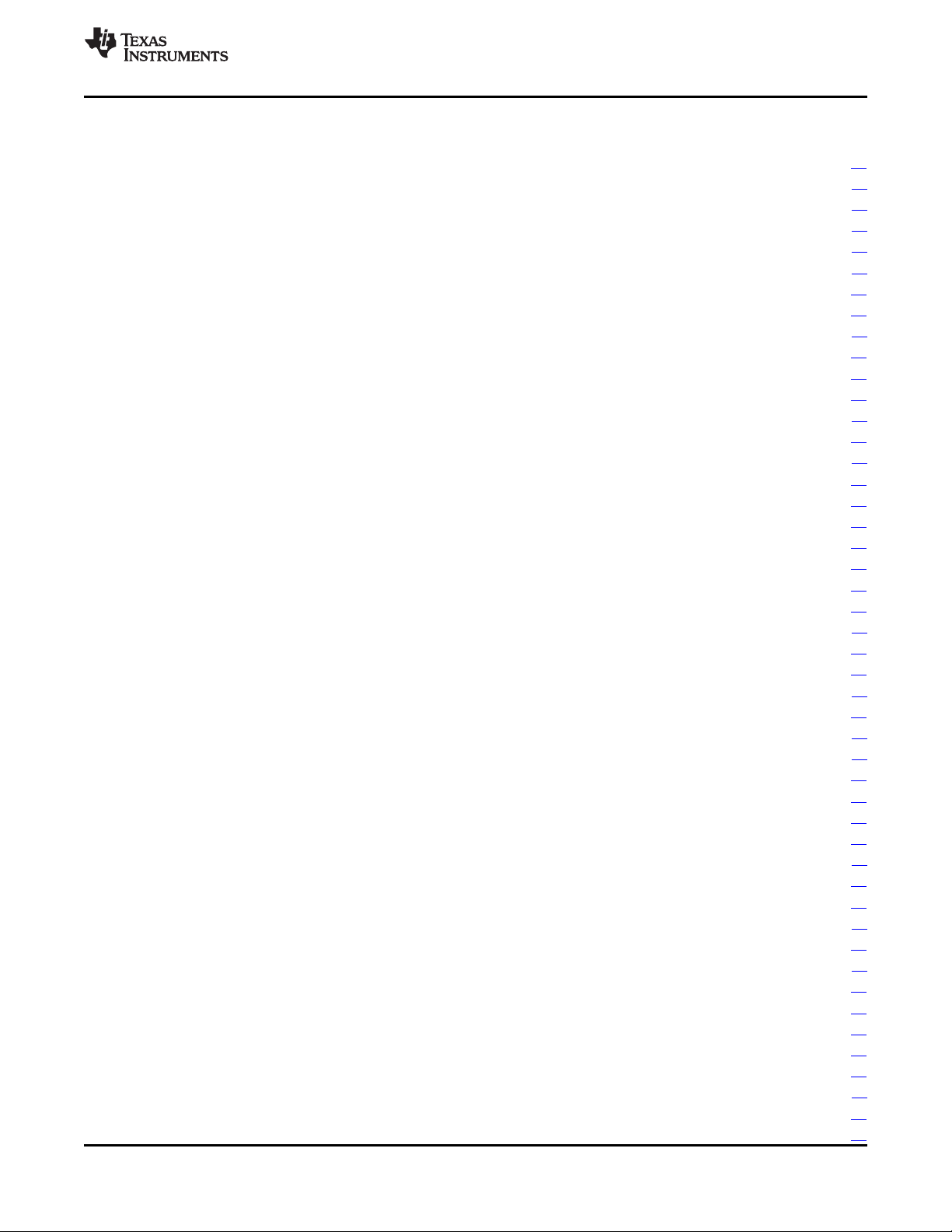

2.3 Ball Placement (Top View)

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

Figure 2-2. Top View

Copyright © 2010–2012, Texas Instruments Incorporated Terminal Description 21

Submit Documentation Feedback

Product Folder Link(s): TPS65951

Page 22

TPS65951

SWCS053F –SEPTEMBER 2010–REVISED MAY 2012

www.ti.com

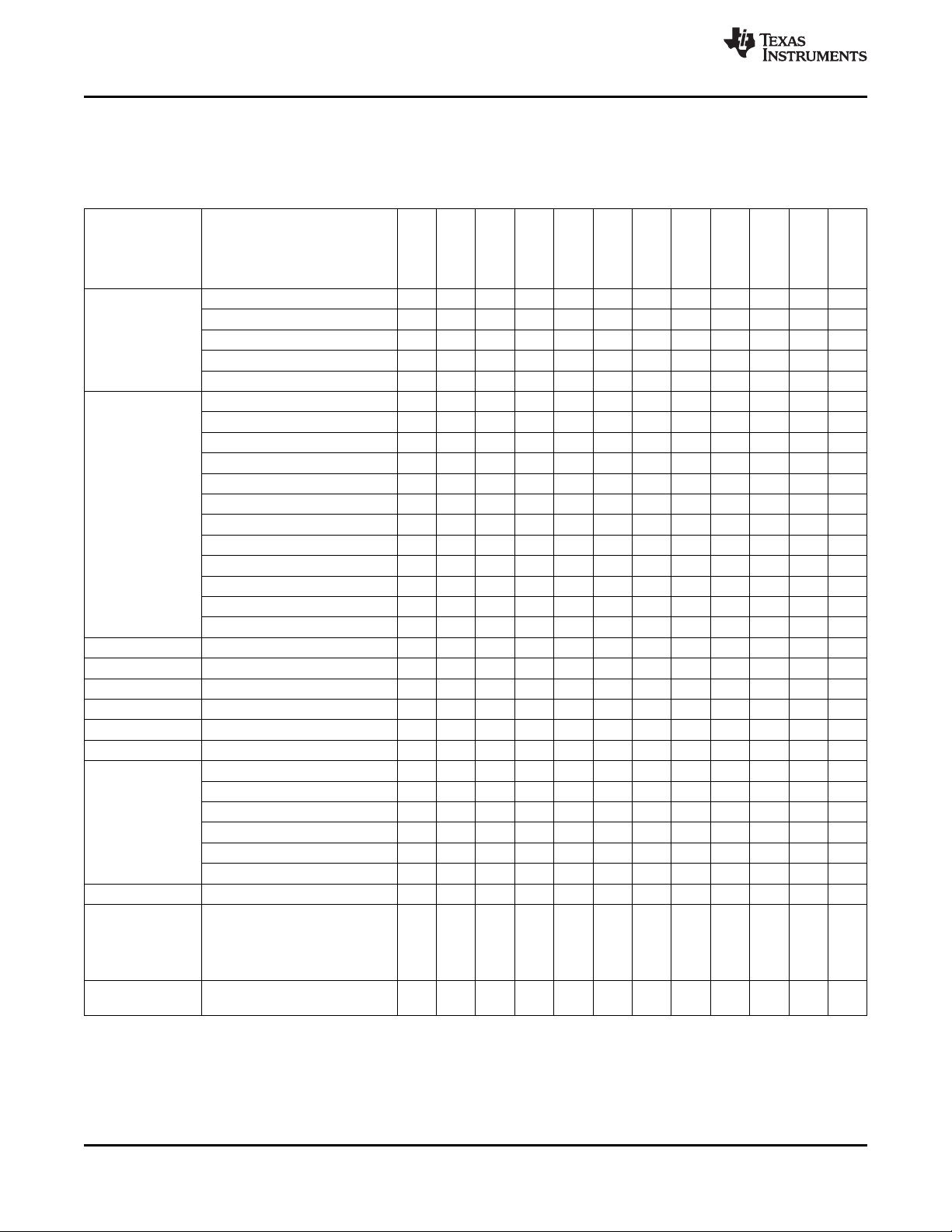

2.4 Signal Description

Table 2-3 provides a description of the signals on the TPS65951; some signals are available on multiple

pins.

Table 2-3. Signal Description

CONFIGURATION BY DEFAULT AFTER

MODULE SIGNAL NAME DESCRIPTION TYPE BALLS