TPS65950

Integrated Power Management/Audio Codec

Silicon Revision 1.2

Data Manual

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Literature Number: SWCS032E

October 2008–Revised January 2011

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

www.ti.com

Contents

1 Introduction ...................................................................................................................... 11

1.1 Features .................................................................................................................... 12

1.2 TPS65950 Block Diagram ................................................................................................ 13

2 Terminal Description .......................................................................................................... 14

2.1 Corner Balls ................................................................................................................ 14

2.2 Ball Characteristics ........................................................................................................ 15

2.3 Signal Description ......................................................................................................... 20

3 Electrical Characteristics .................................................................................................... 27

3.1 Absolute Maximum Ratings .............................................................................................. 27

3.2 Minimum Voltages and Associated Currents .......................................................................... 27

3.3 Recommended Operating Conditions .................................................................................. 28

3.4 Digital I/O Electrical Characteristics ..................................................................................... 28

4 Power Module ................................................................................................................... 32

4.1 Power Providers ........................................................................................................... 34

4.1.1 VDD1 dc-dc Regulator ......................................................................................... 35

4.1.1.1 VDD1 dc-dc Regulator Characteristics .......................................................... 35

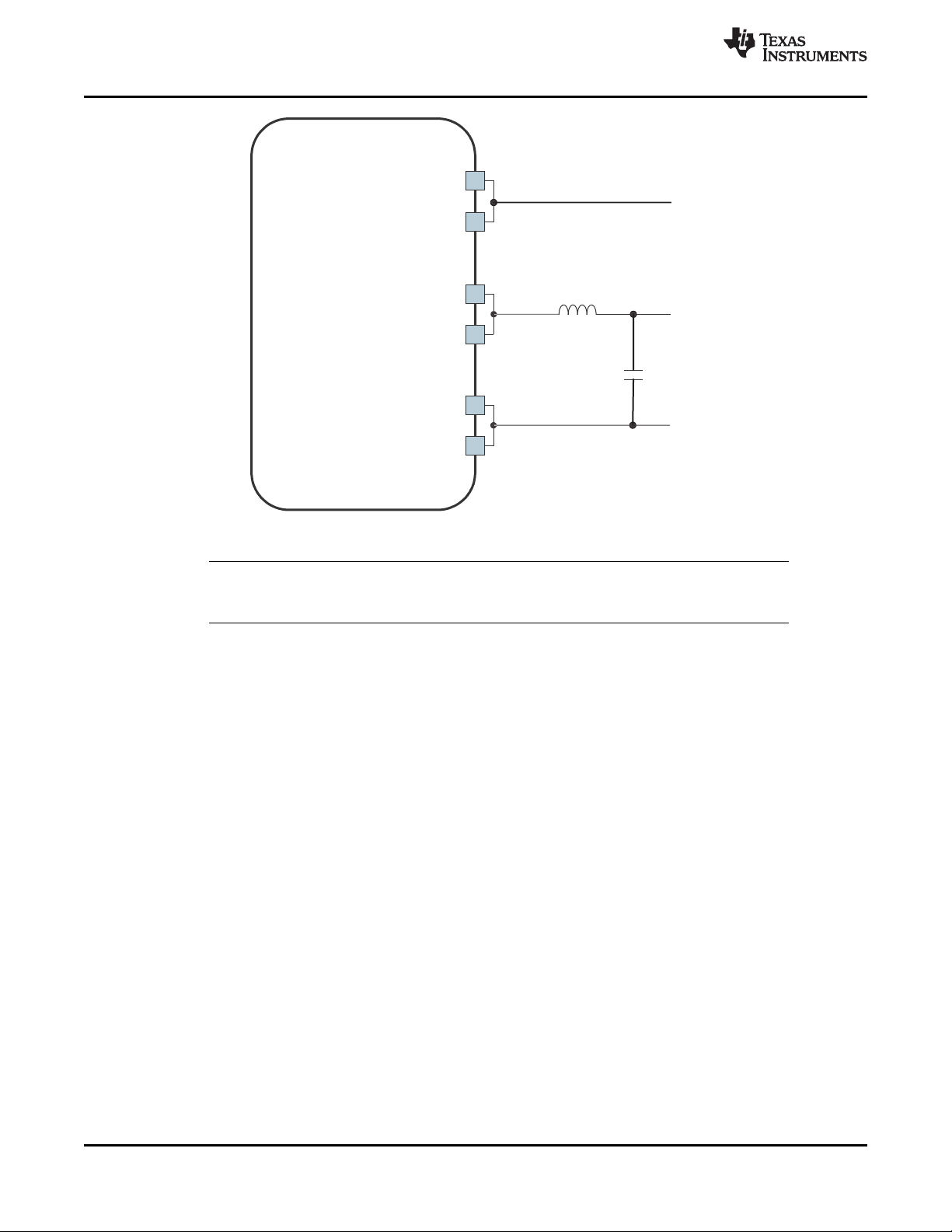

4.1.1.2 External Components and Application Schematic ............................................. 36

4.1.2 VDD2 dc-dc Regulator ......................................................................................... 38

4.1.2.1 VDD2 dc-dc Regulator Characteristics .......................................................... 38

4.1.2.2 External Components and Application Schematic ............................................. 39

4.1.3 VIO dc-dc Regulator ............................................................................................ 41

4.1.3.1 VIO dc-dc Regulator Characteristics ............................................................ 41

4.1.3.2 External Components and Application Schematic ............................................. 42

4.1.4 VDAC LDO Regulator .......................................................................................... 44

4.1.5 VPLL1 LDO Regulator ......................................................................................... 45

4.1.6 VPLL2 LDO Regulator ......................................................................................... 46

4.1.7 VMMC1 LDO Regulator ....................................................................................... 47

4.1.8 VMMC2 LDO Regulator ....................................................................................... 48

4.1.9 VSIM LDO Regulator ........................................................................................... 49

4.1.10 VAUX1 LDO Regulator ........................................................................................ 50

4.1.11 VAUX2 LDO Regulator ........................................................................................ 51

4.1.12 VAUX3 LDO Regulator ........................................................................................ 52

4.1.13 VAUX4 LDO Regulator ........................................................................................ 53

4.1.14 Internal LDOs ................................................................................................... 54

4.1.15 CP ................................................................................................................ 54

4.1.16 USB LDO Short-Circuit Protection Scheme ................................................................. 55

4.2 Power References ......................................................................................................... 55

4.3 Power Control .............................................................................................................. 56

4.3.1 Backup Battery Charger ....................................................................................... 56

4.3.2 Battery Monitoring and Threshold Detection ................................................................ 56

4.3.2.1 Power On/Power Off and Backup Conditions .................................................. 56

4.3.3 VRRTC LDO Regulator ........................................................................................ 57

4.4 Power Consumption ....................................................................................................... 58

4.5 Power Management ....................................................................................................... 59

4.5.1 Boot Modes ...................................................................................................... 59

4.5.2 Process Modes .................................................................................................. 59

2 Contents Copyright © 2008–2011, Texas Instruments Incorporated

TPS65950

www.ti.com

4.5.2.1 C027.0 Mode ....................................................................................... 59

4.5.2.2 C021.M Mode ...................................................................................... 59

4.5.3 Power-On Sequence ........................................................................................... 59

4.5.3.1 Timings Before Sequence_Start ................................................................. 59

4.5.3.2 OMAP2 Power-On Sequence .................................................................... 60

4.5.3.3 OMAP3 Power-On Sequence .................................................................... 61

4.5.3.4 Power On in Slave_C021_Generic Mode ....................................................... 63

4.5.4 Power-Off Sequence ........................................................................................... 63

4.5.4.1 Power-Off Sequence in Master Modes .......................................................... 63

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

5 Real-Time Clock and Embedded Power Controller ................................................................. 65

5.1 RTC ......................................................................................................................... 65

5.1.1 Backup Battery .................................................................................................. 65

5.2 EPC ......................................................................................................................... 65

6 Audio/Voice Module ........................................................................................................... 66

6.1 Audio/Voice Downlink (RX) Module ..................................................................................... 67

6.1.1 Earphone Output ................................................................................................ 67

6.1.1.1 Earphone Output Characteristics ................................................................ 67

6.1.1.2 External Components and Application Schematic ............................................. 68

6.1.2 8-Ω Stereo Hands-Free ........................................................................................ 68

6.1.2.1 8-Ω Stereo Hands-Free Output Characteristics ................................................ 68

6.1.2.2 External Components and Application Schematic ............................................. 69

6.1.3 Headset .......................................................................................................... 70

6.1.3.1 Headset Output Characteristics .................................................................. 70

6.1.3.2 External Components and Application Schematic ............................................. 72

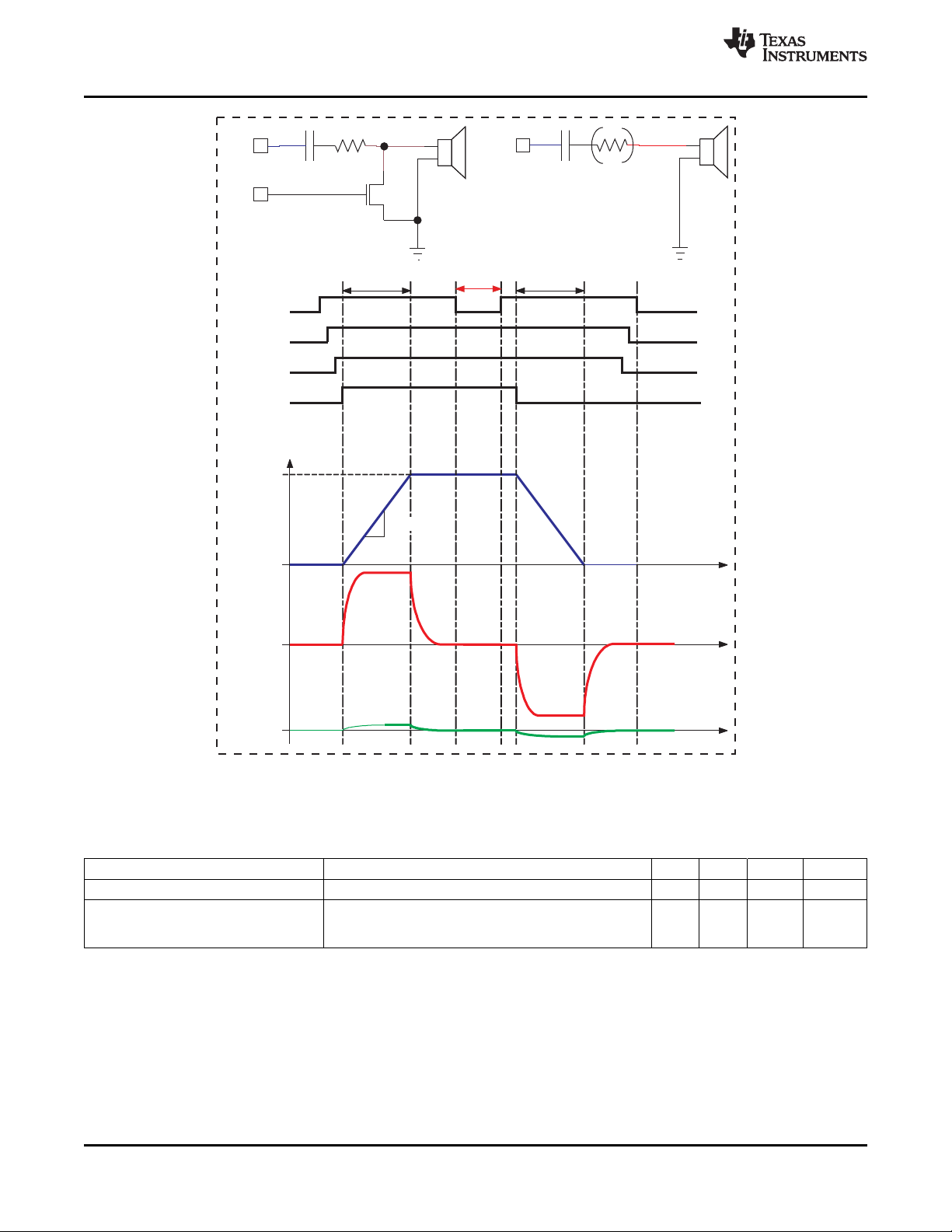

6.1.4 Headset Pop-Noise Attenuation .............................................................................. 75

6.1.5 Predriver for External Class-D Amplifier ..................................................................... 76

6.1.5.1 Predriver Output Characteristics ................................................................. 76

6.1.5.2 External Components and Application Schematic ............................................. 77

6.1.6 Vibrator H-Bridge ............................................................................................... 78

6.1.6.1 Vibrator H-Bridge Output Characteristics ....................................................... 78

6.1.6.2 External Components and Application Schematic ............................................. 78

6.1.7 Carkit Output .................................................................................................... 79

6.1.8 Digital Audio Filter Module .................................................................................... 80

6.1.9 Digital Voice Filter Module ..................................................................................... 80

6.1.9.1 Voice Downlink Filter (Sampling Frequency at 8 kHz) ........................................ 81

6.1.9.2 Voice Downlink Filter (Sampling Frequency at 16 kHz) ...................................... 82

6.1.10 Boost Stage ..................................................................................................... 82

6.2 Audio/Voice Uplink (TX) Module ......................................................................................... 84

6.2.1 Microphone Bias Module ...................................................................................... 84

6.2.1.1 Analog Microphone Bias Module Characteristics .............................................. 85

6.2.1.2 External Components and Application Schematic ............................................. 86

6.2.1.3 Digital Microphone Bias Module Characteristics ............................................... 87

6.2.1.4 Silicon Microphone Characteristics .............................................................. 89

6.2.2 Stereo Differential Input ........................................................................................ 90

6.2.3 Headset Differential Input ...................................................................................... 90

6.2.4 FM Radio/Auxiliary Stereo Input .............................................................................. 91

6.2.4.1 External Components ............................................................................. 91

6.2.5 PDM Interface for Digital Microphones ...................................................................... 91

Copyright © 2008–2011, Texas Instruments Incorporated Contents 3

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

6.2.6 Uplink Characteristics .......................................................................................... 92

6.2.7 Microphone Amplification Stage .............................................................................. 93

6.2.8 Carkit Input ...................................................................................................... 93

6.2.9 Digital Audio Filter Module .................................................................................... 94

6.2.10 Digital Voice Filter Module ..................................................................................... 95

6.2.10.1 Voice Uplink Filter (Sampling Frequency at 8 kHz) ........................................... 95

6.2.10.2 Voice Uplink Filter (Sampling Frequency at 16 kHz) .......................................... 97

www.ti.com

7 USB HS 2.0 OTG Transceiver .............................................................................................. 99

7.1 USB Features .............................................................................................................. 99

7.2 USB Transceiver ......................................................................................................... 100

7.2.1 MCPC Carkit Port Timing .................................................................................... 102

7.2.2 USB-CEA Carkit Port Timing ................................................................................ 103

7.2.3 HS USB Port Timing .......................................................................................... 105

7.2.4 PHY Electrical Characteristics ............................................................................... 106

7.2.4.1 5-V Tolerance ..................................................................................... 106

7.2.4.2 LS/FS Single-Ended Receivers ................................................................. 106

7.2.4.3 LS/FS Differential Receiver ..................................................................... 107

7.2.4.4 LS/FS Differential Transmitter .................................................................. 107

7.2.4.5 HS Differential Receiver ......................................................................... 108

7.2.4.6 HS Differential Transmitter ...................................................................... 108

7.2.4.7 CEA/MCPC/UART Driver ........................................................................ 109

7.2.4.8 Pullup/Pulldown Resistors ....................................................................... 110

7.2.4.9 PHY DPLL Electrical Characteristics .......................................................... 110

7.2.4.10 PHY Power Consumption ....................................................................... 111

7.2.5 OTG Electrical Characteristics .............................................................................. 111

7.2.5.1 OTG VBUS Electrical ............................................................................ 112

7.2.5.2 OTG ID Electrical ................................................................................. 112

8 Battery Interface .............................................................................................................. 114

8.1 General Description ...................................................................................................... 114

8.1.1 Battery Charger Interface Overview ........................................................................ 114

8.1.2 Battery Backup Overview .................................................................................... 114

8.2 Typical Application Schematics ........................................................................................ 114

8.2.1 Functional Configurations .................................................................................... 114

8.2.2 In-Rush Current Limitation Schematic ...................................................................... 115

8.2.3 Configuration With BCI Not Used ........................................................................... 116

8.3 Electrical Characteristics ................................................................................................ 118

8.3.1 Main Charge ................................................................................................... 118

8.3.2 Precharge ...................................................................................................... 121

8.3.3 Constant Voltage Mode ...................................................................................... 122

8.4 Charge Sequence Timing Diagram .................................................................................... 124

8.5 CEA Charger Type ....................................................................................................... 124

9 MADC ............................................................................................................................. 126

9.1 General Description ...................................................................................................... 126

9.2 Main Electrical Characteristics ......................................................................................... 126

9.3 Channel Voltage Input Range .......................................................................................... 127

9.3.1 Sequence Conversion Time (Real-Time or Nonaborted Asynchronous) .............................. 127

10 LED Drivers ..................................................................................................................... 129

4 Contents Copyright © 2008–2011, Texas Instruments Incorporated

TPS65950

www.ti.com

10.1 General Description ...................................................................................................... 129

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

11 Keyboard ........................................................................................................................ 130

11.1 Keyboard Connection ................................................................................................... 130

12 Clock Specifications ........................................................................................................ 131

12.1 Features ................................................................................................................... 131

12.2 Input Clock Specifications .............................................................................................. 132

12.2.1 Clock Source Requirements ................................................................................. 132

12.2.2 High-Frequency Input Clock ................................................................................. 132

12.2.3 32-kHz Input Clock ............................................................................................ 135

12.2.3.1 External Crystal Description ..................................................................... 136

12.2.3.2 External Clock Description ...................................................................... 138

12.3 Output Clock Specifications ............................................................................................ 140

12.3.1 32KCLKOUT Output Clock .................................................................................. 140

12.3.2 HFCLKOUT Output Clock .................................................................................... 142

12.3.3 Output Clock Stabilization Time ............................................................................. 143

13 Timing Requirements and Switching Characteristics ........................................................... 144

13.1 Timing Parameters ....................................................................................................... 144

13.2 Target Frequencies ...................................................................................................... 144

13.3 I

13.4 Audio Interface: TDM/I2S Protocol .................................................................................... 146

13.5 Voice/Bluetooth PCM Interfaces ....................................................................................... 149

13.6 JTAG Interfaces .......................................................................................................... 151

2

C Timing ................................................................................................................. 145

13.4.1 I2S Right- and Left-Justified Data Format ................................................................. 146

13.4.2 TDM Data Format ............................................................................................. 148

14 Debouncing Time ............................................................................................................. 153

15 External Components ....................................................................................................... 155

16 TPS65950 Package ........................................................................................................... 160

16.1 TPS65950 Standard Package Symbols .............................................................................. 160

16.2 Package Thermal Resistance Characteristics ....................................................................... 160

16.3 Mechanical Data ......................................................................................................... 161

16.4 ESD Specifications ...................................................................................................... 162

17 Glossary ......................................................................................................................... 163

Copyright © 2008–2011, Texas Instruments Incorporated Contents 5

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

www.ti.com

List of Figures

1-1 TPS65950 Block Diagram....................................................................................................... 13

2-1 PBGA Bottom View .............................................................................................................. 14

4-1 Power Provider Block Diagram................................................................................................. 33

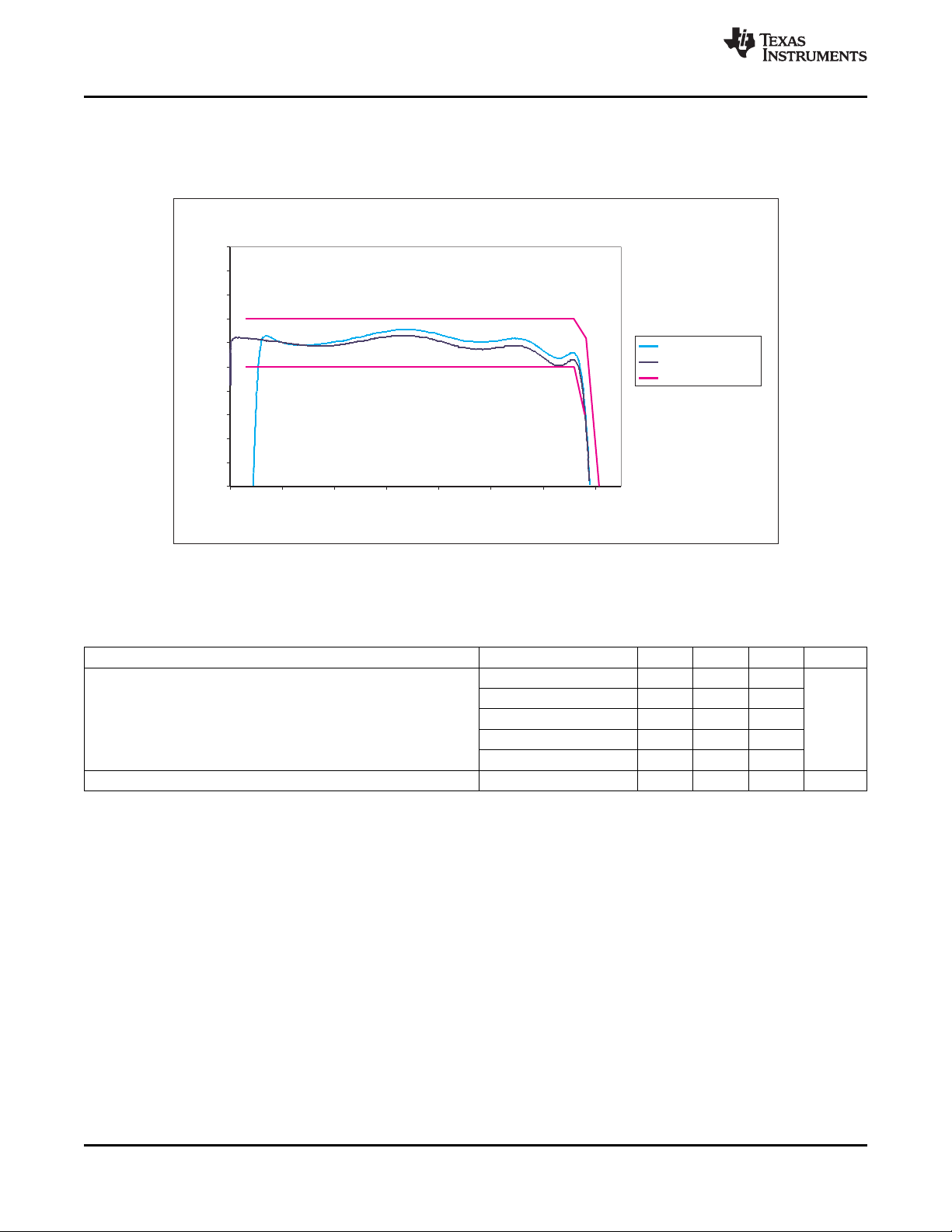

4-2 VDD1 dc-dc Regulator Efficiency .............................................................................................. 36

4-3 VDD1 dc-dc Application Schematic............................................................................................ 37

4-4 VDD2 dc-dc Regulator Efficiency .............................................................................................. 39

4-5 VDD2 dc-dc Application Schematic............................................................................................ 40

4-6 VIO dc-dc Regulator Efficiency in Active Mode .............................................................................. 42

4-7 VIO dc-dc Application Schematic .............................................................................................. 43

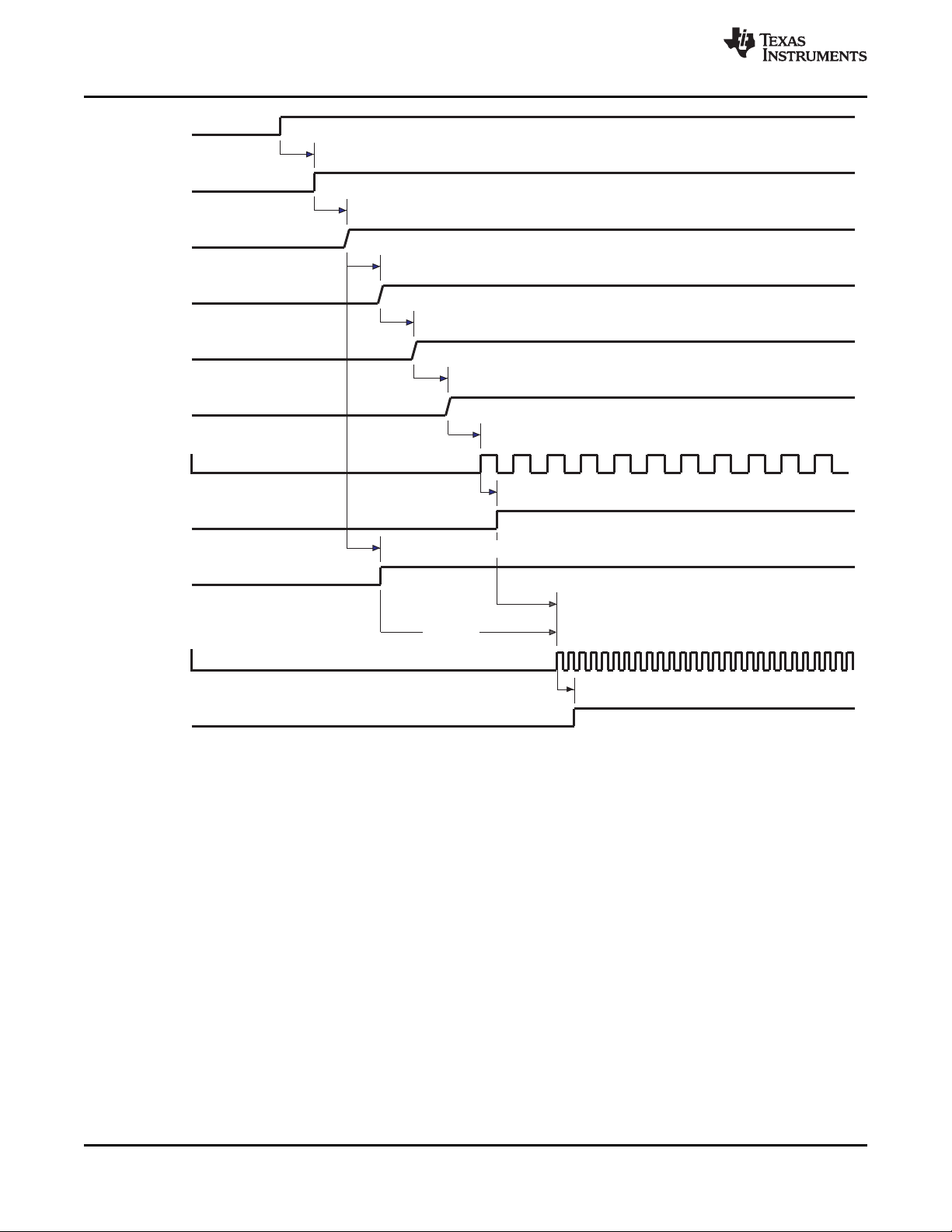

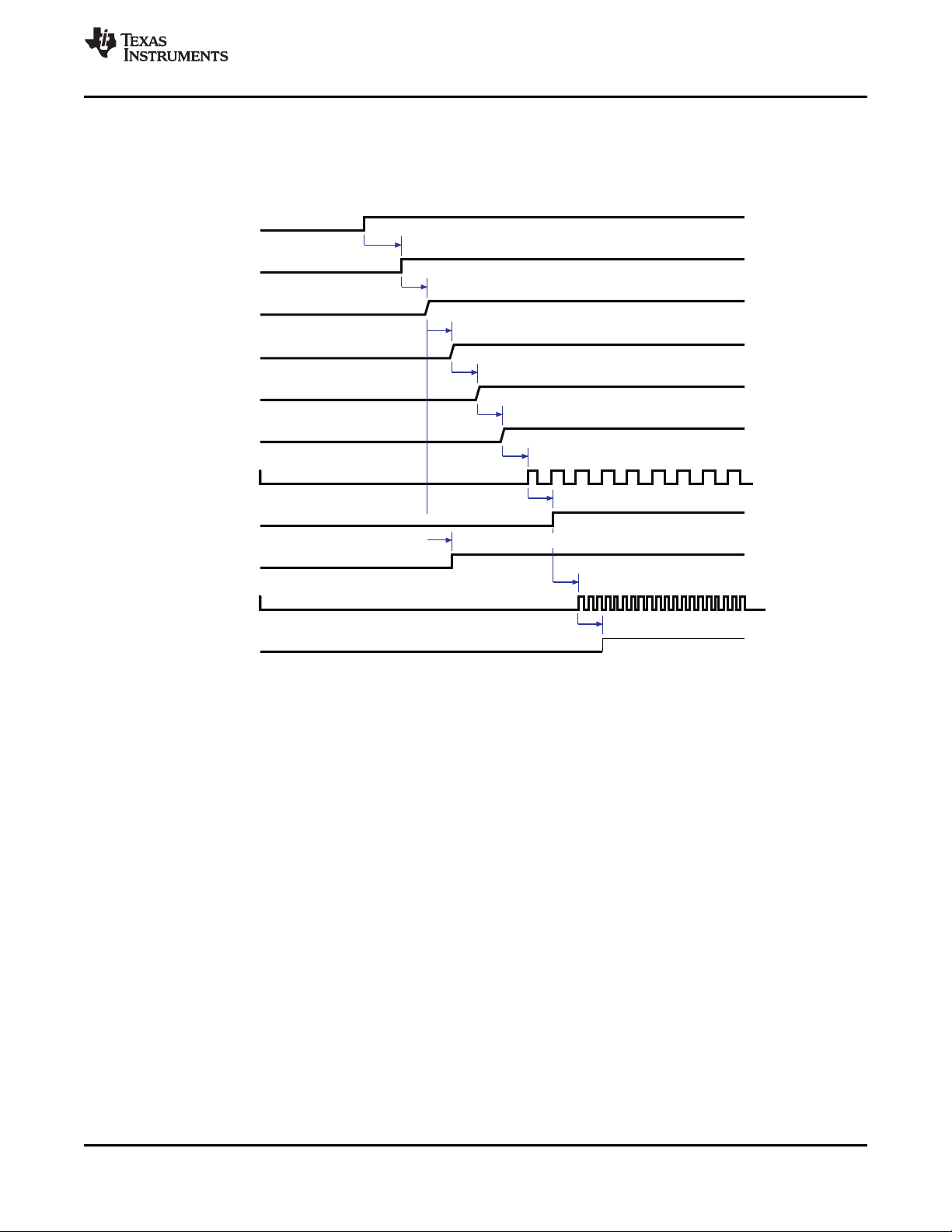

4-8 Timings Before Sequence Start ............................................................................................... 60

4-9 Timings—OMAP2 Power-On Sequence ...................................................................................... 61

4-10 Timings—OMAP3 Power-On Sequence ...................................................................................... 62

4-11 Timings—Power On in Slave_C021_Generic Model ........................................................................ 63

4-12 Power-Off Sequence in Master Modes........................................................................................ 64

6-1 Audio/Voice Module Block Diagram ........................................................................................... 67

6-2 Earphone Amplifier............................................................................................................... 67

6-3 Earphone Speaker ............................................................................................................... 68

6-4 8-Ω Stereo Hands-Free Amplifiers............................................................................................. 68

6-5 8-Ω Stereo Hands-Free ......................................................................................................... 70

6-6 Headset Amplifier ................................................................................................................ 70

6-7 Headset 4-Wire Stereo Jack Without an External FET...................................................................... 72

6-8 Headset 4-Wire Stereo Jack With an External FET ......................................................................... 73

6-9 Headset 5-Wire Stereo Jack.................................................................................................... 74

6-10 Headset 4-Wire Stereo Jack Optimized ....................................................................................... 75

6-11 Headset Pop-Noise Cancellation Diagram.................................................................................... 76

6-12 Predriver for External Class D.................................................................................................. 77

6-13 Vibrator H-Bridge................................................................................................................. 79

6-14 Carkit Output Downlink Path Characteristics ................................................................................. 79

6-15 Digital Audio Filter Downlink Path Characteristics ........................................................................... 80

6-16 Digital Voice Filter Downlink Path Characteristics ........................................................................... 80

6-17 Voice Downlink Frequency Response With F

6-18 Voice Downlink Frequency Response With F

6-19 Analog and Digital Microphone Multiplexing.................................................................................. 85

6-20 Analog Microphone Pseudodifferential........................................................................................ 87

6-21 Analog Microphone Differential................................................................................................. 87

6-22 Digital Microphone Bias Module Block Diagram ............................................................................. 88

6-23 Digital Microphone Bias Module Timing Diagram............................................................................ 89

6-24 Silicon Microphone Module ..................................................................................................... 90

6-25 Audio Auxiliary Input............................................................................................................. 91

6-26 Example of PDM Interface Circuitry ........................................................................................... 92

6-27 Uplink Amplifier................................................................................................................... 93

6-28 Carkit Input Uplink Path Characteristics ...................................................................................... 93

6-29 Digital Audio Filter Uplink Path Characteristics .............................................................................. 94

6-30 Digital Audio Filter Uplink Path Characteristics .............................................................................. 95

6-31 Voice Uplink Frequency Response With F

6-32 Voice Uplink Frequency Response With F

6-33 Voice Uplink Frequency Response With F

6 List of Figures Copyright © 2008–2011, Texas Instruments Incorporated

= 8 kHz..................................................................... 81

S

= 16 kHz ................................................................... 82

S

= 8 kHz (Frequency Range 0 to 600 Hz) ................................. 96

S

= 8 kHz (Frequency Range 3000 to 3600 Hz) ........................... 96

S

= 16 kHz (Frequency Range 0 to 600 Hz)................................ 97

S

TPS65950

www.ti.com

6-34 Voice Uplink Frequency Response With F

= 16 kHz (Frequency Range 6200 to 7000 Hz).......................... 97

S

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

7-1 USB 2.0 PHY Overview ......................................................................................................... 99

7-2 USB System Application Schematic.......................................................................................... 101

7-3 MCPC UART and Handshake Mode Data Flow............................................................................ 102

7-4 MCPC UART and Handshake Mode Timings............................................................................... 103

7-5 USB-CEA Carkit UART Data Flow ........................................................................................... 104

7-6 USB-CEA Carkit UART Timing Parameters................................................................................. 105

7-7 HS USB Interface—Transmit and Receive Modes (ULPI 8-Bit) .......................................................... 105

8-1 Typical Application Schematics ............................................................................................... 115

8-2 Typical Application Schematic (In-Rush Current Limitation).............................................................. 116

8-3 Typical Application Schematic (BCI Not Used)............................................................................. 117

8-4 Automatic Charge Sequence Timing Diagram.............................................................................. 124

9-1 Conversion Sequence General Timing Diagram ........................................................................... 128

10-1 LED Driver Block Diagram..................................................................................................... 129

11-1 Keyboard Connection .......................................................................................................... 130

12-1 Clock Overview ................................................................................................................. 131

12-2 HFCLKIN Clock Distribution................................................................................................... 133

12-3 Example of Wired-OR Clock Request........................................................................................ 135

12-4 HFCLKIN Squared Input Clock ............................................................................................... 135

12-5 32-kHz Oscillator Block Diagram In Master Mode With Crystal .......................................................... 136

12-6 32-kHz Crystal Input............................................................................................................ 137

12-7 32-kHz Oscillator Block Diagram Without Crystal Option 1............................................................... 139

12-8 32-kHz Oscillator Block Diagram Without Crystal Option 2............................................................... 139

12-9 32-kHz Oscillator in Bypass Mode Block Diagram Without Crystal Option 3........................................... 139

12-10 32-kHz Square- or Sine-Wave Input Clock.................................................................................. 140

12-11 32.768-kHz Clock Output Block Diagram.................................................................................... 141

12-12 32KCLKOUT Output Clock .................................................................................................... 142

12-13 HFCLKOUT Output Clock ..................................................................................................... 142

12-14 32KCLKOUT and HFCLKOUT Clock Stabilization Time .................................................................. 143

12-15 HFCLKOUT Behavior ......................................................................................................... 143

13-1 I

2

C Interface—Transmit and Receive in Slave Mode ...................................................................... 145

13-2 I2S Interface—I2S Master Mode.............................................................................................. 147

13-3 I2S Interface—I2S Slave Mode............................................................................................... 147

13-4 TDM Interface—TDM Master Mode.......................................................................................... 148

13-5 Voice/BT PCM Interface—Master Mode (Mode 1) ......................................................................... 150

13-6 Voice PCM Interface—Slave Mode (Mode 1)............................................................................... 150

13-7 JTAG Interface Timing ......................................................................................................... 152

14-1 Debouncing Sequence Chronogram Example.............................................................................. 154

16-1 Printed Device Reference ..................................................................................................... 160

16-2 TPS65950 Mechanical Package Top View.................................................................................. 161

16-3 Ball Size.......................................................................................................................... 161

Copyright © 2008–2011, Texas Instruments Incorporated List of Figures 7

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

www.ti.com

List of Tables

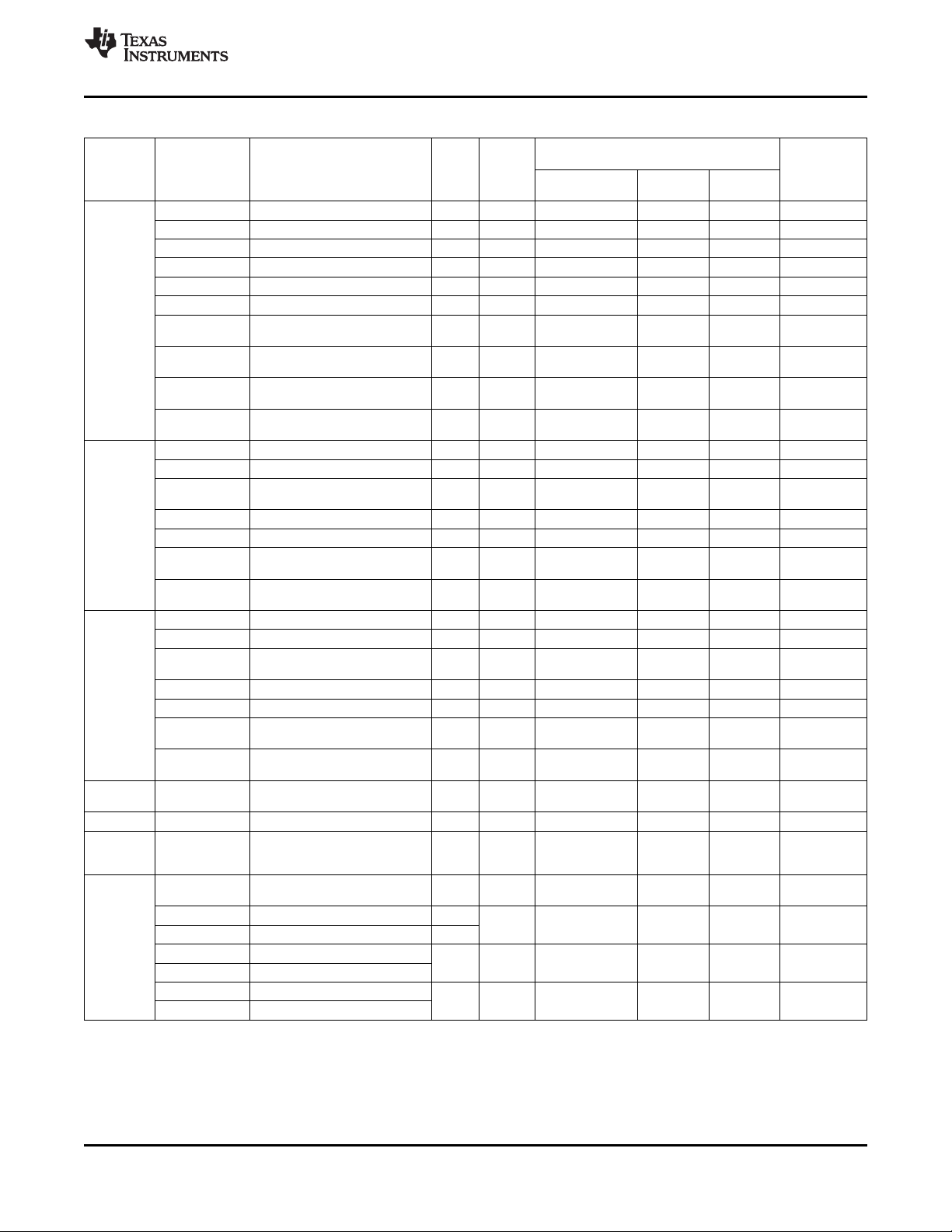

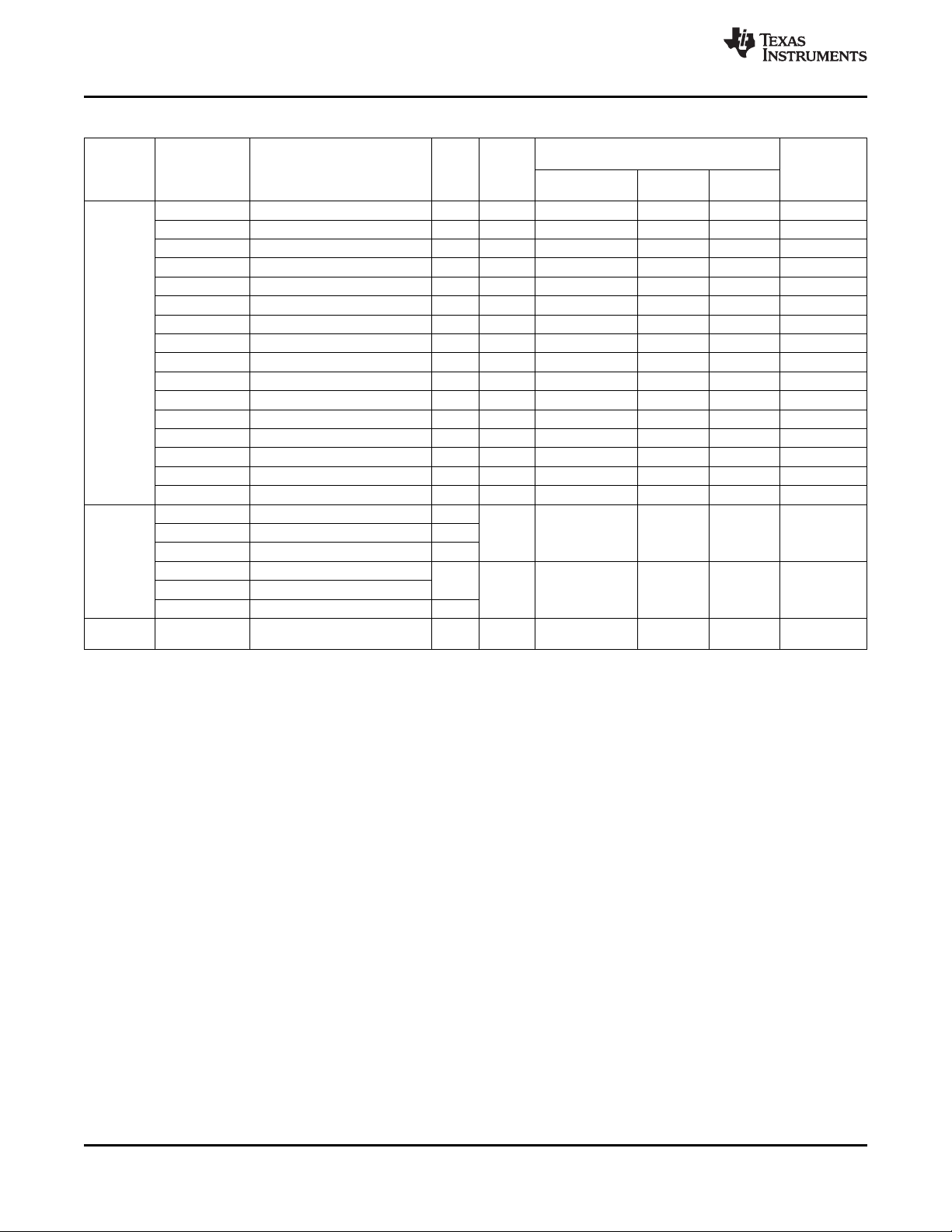

2-1 Ball Characteristics............................................................................................................... 15

2-2 Signal Description ................................................................................................................ 20

3-1 Absolute Maximum Ratings..................................................................................................... 27

3-2 VBAT Min Required Per VBAT Ball and Associated Maximum Current.................................................. 27

3-3 Recommended Operating Maximum Ratings ................................................................................ 28

3-4 Digital I/O Electrical Characteristics ........................................................................................... 29

4-1 Summary of the Power Providers.............................................................................................. 34

4-2 Part Names With Corresponding VDD1 Current Support................................................................... 35

4-3 VDD1 dc-dc Regulator Characteristics........................................................................................ 35

4-4 VDD2 dc-dc Regulator Characteristics........................................................................................ 38

4-5 VIO dc-dc Regulator Characteristics........................................................................................... 41

4-6 VDAC LDO Regulator Characteristics......................................................................................... 44

4-7 VPLL1 LDO Regulator Characteristics ........................................................................................ 45

4-8 VPLL2 LDO Regulator Characteristics ........................................................................................ 46

4-9 VMMC1 LDO Regulator Characteristics....................................................................................... 47

4-10 VMMC2 LDO Regulator Characteristics....................................................................................... 48

4-11 VSIM LDO Regulator Characteristics.......................................................................................... 49

4-12 VAUX1 LDO Regulator Characteristics ....................................................................................... 50

4-13 VAUX2 LDO Regulator Characteristics ....................................................................................... 51

4-14 VAUX3 LDO Regulator Characteristics ....................................................................................... 52

4-15 VAUX4 LDO Regulator Characteristics ....................................................................................... 53

4-16 Output Load Conditions ......................................................................................................... 54

4-17 CP Characteristics ............................................................................................................... 54

4-18 Voltage Reference Characteristics............................................................................................. 55

4-19 Backup Battery Charger Characteristics ...................................................................................... 56

4-20 Battery Threshold Levels........................................................................................................ 56

4-21 VRRTC LDO Regulator Characteristics....................................................................................... 57

4-22 Power Consumption ............................................................................................................. 58

4-23 Regulator States Depending on Use Cases.................................................................................. 58

4-24 BOOT Mode Description ........................................................................................................ 59

4-25 C027.0 Mode Description ...................................................................................................... 59

4-26 C021.M Mode Description ...................................................................................................... 59

5-1 System States .................................................................................................................... 65

6-1 Earphone Amplifier Output Characteristics ................................................................................... 67

6-2 8-Ω Stereo Hands-Free Output Characteristics.............................................................................. 68

6-3 Headset Output Characteristics ................................................................................................ 70

6-4 Output Characteristics of a Headset 4-Wire Stereo Jack Without an External FET..................................... 72

6-5 Output Characteristics of a Headset 4-Wire Stereo Jack With an External FET ........................................ 73

6-6 Output Characteristics of a Headset 5-Wire Stereo Jack ................................................................... 74

6-7 Headset Pop-Noise Characteristics............................................................................................ 76

6-8 Predriver Output Characteristics ............................................................................................... 77

6-9 Vibrator H-Bridge Output Characteristics ..................................................................................... 78

6-10 MCPC and USB-CEA Carkit Audio Downlink Electrical Characteristics.................................................. 79

6-11 Digital Audio Filter RX Electrical Characteristics............................................................................. 80

6-12 Digital Voice Filter RX Electrical Characteristics With F

6-13 Digital Voice Filter RX Electrical Characteristics With F

6-14 Boost Electrical Characteristics Versus FSFrequency (F

8 List of Tables Copyright © 2008–2011, Texas Instruments Incorporated

= 8 kHz......................................................... 81

S

= 16 kHz ....................................................... 82

S

≤ 22.05 kHz) ................................................. 83

S

TPS65950

www.ti.com

6-15 Boost Electrical Characteristics Versus FSFrequency (F

≥ 24 kHz)..................................................... 83

S

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

6-16 Analog Microphone Bias Module Characteristics ............................................................................ 85

6-17 Characteristics of Analog Microphone Bias Module With a Bias Resistor................................................ 86

6-18 Digital Microphone Bias Module Characteristics ............................................................................. 88

6-19 Digital Microphone Bias Module Characteristics (2)......................................................................... 88

6-20 Silicon Microphone Module Characteristics................................................................................... 90

6-21 Uplink Amplifier Characteristics ................................................................................................ 93

6-22 MCPC and USB-CEA Carkit Audio Uplink Electrical Characteristics ..................................................... 94

6-23 Digital Audio Filter TX Electrical Characteristics ............................................................................. 94

6-24 Digital Voice Filter TX Electrical Characteristics With F

6-25 Digital Voice Filter TX Electrical Characteristics With F

= 8 kHz ......................................................... 96

S

= 16 kHz........................................................ 97

S

7-1 MCPC UART and Handshake Mode Timings............................................................................... 102

7-2 USB-CEA Carkit Interface Timing Parameters ............................................................................. 103

7-3 USB-CEA Carkit UART Timing Parameters................................................................................. 104

7-4 HS USB Interface Timing Requirement Parameters....................................................................... 105

7-5 HS USB Interface Switching Requirement Parameters ................................................................... 105

7-6 5V-Tolerant Electrical Summary .............................................................................................. 106

7-7 LS/FS Single-Ended Receivers ............................................................................................... 106

7-8 LS/FS Differential Receiver.................................................................................................... 107

7-9 LS/FS Differential Transmitter................................................................................................. 107

7-10 HS Differential Receiver ....................................................................................................... 108

7-11 HS Differential Transmitter .................................................................................................... 109

7-12 CEA/MCPC/UART Driver...................................................................................................... 109

7-13 Pullup/Pulldown Resistors..................................................................................................... 110

7-14 PHY DPLL Electrical Characteristics......................................................................................... 110

7-15 PHY Power Consumption...................................................................................................... 111

7-16 OTG VBUS Electrical........................................................................................................... 112

7-17 OTG ID Electrical ............................................................................................................... 112

8-1 Main Charge Electrical Characteristics

VBAT = 3.6 V, R

= 0.22 Ω, unless otherwise specified .................................................................. 118

S

8-2 Precharge Electrical Characteristics

R

= 0.22 Ω, unless otherwise specified..................................................................................... 121

S

8-3 CV Mode Electrical Characteristics .......................................................................................... 123

8-4 Precharge Detection Characteristics ......................................................................................... 124

8-5 Main Charge Current Limit Indication ........................................................................................ 125

9-1 Electrical Characteristics....................................................................................................... 126

9-2 Analog Input Voltage Range .................................................................................................. 127

9-3 Sequence Conversion Timing Characteristics .............................................................................. 127

10-1 Electrical Characteristics....................................................................................................... 129

12-1 TPS65950 Input Clock Source Requirements .............................................................................. 132

12-2 HFCLKIN Input Clock Electrical Characteristics ............................................................................ 135

12-3 HFCLKIN Square Input Clock Timing Requirements With Slicer in Bypass............................................ 135

12-4 Crystal Electrical Characteristics ............................................................................................. 136

12-5 Base Oscillator Switching Characteristics................................................................................... 137

12-6 32-kHz Crystal Input Clock Timing Requirements.......................................................................... 137

12-7 32-kHz Input Square- or Sine-Wave Clock Source Electrical Characteristics.......................................... 140

12-8 32-kHz Square-Wave Input Clock Source Timing Requirements ........................................................ 140

12-9 32KCLKOUT Output Clock Electrical Characteristics...................................................................... 141

12-10 32KCLKOUT Output Clock Switching Characteristics ..................................................................... 141

Copyright © 2008–2011, Texas Instruments Incorporated List of Tables 9

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

www.ti.com

12-11 HFCLKOUT Output Clock Electrical Characteristics....................................................................... 142

12-12 HFCLKOUT Output Clock Switching Characteristics ...................................................................... 142

13-1 Timing Parameters ............................................................................................................. 144

13-2 TPS65950 Interface Target Frequencies.................................................................................... 144

13-3 I

13-4 I

2

C Interface Timing Requirements .......................................................................................... 145

2

C Interface Switching Requirements ....................................................................................... 146

13-5 I2S Interface—Timing Requirements......................................................................................... 147

13-6 I2S Interface—Switching Characteristics.................................................................................... 148

13-7 TDM Interface Master Mode Timing Requirements ........................................................................ 148

13-8 TDM Interface Master Mode Switching Characteristics ................................................................... 149

13-9 Voice PCM Interface Timing Requirements (Mode 1) ..................................................................... 150

13-10 Voice PCM Interface Switching Characteristics (Mode 1)................................................................. 150

13-11 JTAG Interface Timing Requirements........................................................................................ 152

13-12 JTAG Interface Switching Characteristics ................................................................................... 152

14-1 Debouncing Time ............................................................................................................... 153

15-1 TPS65950 External Components............................................................................................. 155

16-1 TPS65950 Nomenclature Description........................................................................................ 160

16-2 TPS65950 Thermal Resistance Characteristics............................................................................ 160

10 List of Tables Copyright © 2008–2011, Texas Instruments Incorporated

TPS65950

www.ti.com

1 Introduction

The TPS65950 device is a highly integrated power-management and audio coder/decoder (codec)

integrated circuit (IC) that supports the power and peripheral requirements of the OMAP™ application

processors. The device contains power management, an audio codec, a universal serial bus (USB)

high-speed (HS) transceiver, an ac/USB charger, light-emitting diode (LED) drivers, an analog-to-digital

converter (ADC), a real-time clock (RTC), and embedded power control.

The power portion of the device contains three buck converters, two controllable by a dedicated

SmartReflex™ class-3 interface, multiple low-dropout (LDO) regulators, an embedded power controller

(EPC) to manage the power-sequencing requirements of OMAP, and an RTC and backup module. The

RTC can be powered by a backup battery when the main supply is not present, and the device contains a

coin-cell charger to recharge the backup battery as needed.

The USB module provides a HS 2.0 on-the-go (OTG) transceiver suitable for direct connection to the

OMAP universal transceiver macrocell interface (UTMI) + low pin interface (ULPI) with an integrated

charge pump (CP) and full support for the carkit Consumer Electronics Association (CEA)-936A

specification.

The Li-ion battery charger supports charging from ac chargers, USB host devices, USB chargers, or

carkits. The type of charger is detected automatically by the device, which provides hardware-controlled

linear charging with ac chargers, USB chargers, and carkits, in addition to software-controlled charging for

all charger types.

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

Integrated Power Management/Audio Codec

Check for Samples: TPS65950

The audio codec in the device includes five digital-to-analog converters (DACs) and two ADCs to provide

multiple voice channels and stereo downlink channels that can support all standard audio sample rates

through several inter-IC sound (I2S™)/time division multiplexing (TDM) format interfaces. The audio output

stages on the device include stereo headset amplifiers, two integrated class-D amplifiers providing stereo

differential outputs, predrivers for line outputs, and an earpiece amplifier. The input audio stages include

three differential microphone inputs, stereo line inputs, and interface for digital micrphones. Automatic and

programmable gain control is available with all necessary digital filtering, side-tone functions, and

pop-noise reduction.

The device also provides a auxiliary modules, including LED drivers, and ADC, keypad interface, and

general-purpose inputs/outputs (GPIOs). The LED driver can power two LED circuits to illuminate a panel

or provide user indicators. The drivers also provide pulse width modulation (PWM) circuits to control the

illumination levels of the LEDs. The ADC monitors signals entering the device, such as supply and

charging voltages, and has multiple additional external ADC inputs for system use. The keypad interface

implements a built-in scanning algorithm to decode hardware-based key presses and to reduce software

use, with multiple additional GPIOs that can be used as interrupts when they are configured as inputs.

This TPS65950 Data Manual describes the electrical and mechanical specifications for the TPS65950. It

covers the following topics:

• TPS65950 terminals: Assignment, multiplexing, electrical characteristics, and functional description

(see Section 2, Terminal Description)

• Electrical characteristic requirements: Maximum and recommended operating conditions, digital

input/output (I/O) characteristics (see Section 3, Electrical Characteristics)

• Power module, including the power provider, power references, power control, power consumption,

and power management with the on and off sequences (see Section 4, Power Module)

• RTC and EPC (see Section 5, Real-Time Clock and Embedded Power Controller)

• Audio/voice module with the electrical characteristics and the application schematics for the downlink

and uplink paths (see Section 6, Audio/Voice Module)

Copyright © 2008–2011, Texas Instruments Incorporated Introduction 11

TPS65950

www.ti.com

• Battery charger interface (see Section 8, Battery Interface)

• Various modules: Monitoring analog-to-digital conversion (MADC), LED drivers, and keyboard (see

Section 9, MADC, Section 10, LED Drivers, and Section 11, Keyboard)

• Clock specifications: Clock slicer, input and output clocks (see Section 12, Clock Specifications)

• Timing requirements and switching characteristics (ac timings) of the interfaces (see Section 13,

Timing Requirements and Switching Characteristics)

• Deboucing time (see Section 14, Debouncing Time)

• External components for the application schematics (see Section 15, External Components)

• Thermal resistance characteristics, device nomenclature, and mechanical data about the available

packaging (see Section 16, TPS65950 Package)

• Glossary of acronyms and abbreviations used in this data manual (see Section 17, Glossary)

1

1.1 Features

2

• Power:

– Three efficient stepdown converters

• VDD1: TPS65950A2 with 1.2A and

TPS65950A3 with 1.4A (for 1GHz speed)

• VDD2: 600mA

• VIO: 700mA

– 10 external linear LDOs for clocks and

peripherals

– SmartReflex dynamic voltage management

• Audio:

– Voice codec

– 15-bit linear codec (8 and 16 kHz)

– Differential input main and submicrophones

– Differential headset microphone input

– Auxiliary/FM input (mono or stereo)

– Differential 32-Ω speaker and 16-Ω headset

drivers (external predrivers for class D)

– 8-Ω stereo class-D drivers

– Pulse code modulation (PCM) and TDM

interfaces

– Bluetooth®interface

– Automatic level control (ALC)

– Digital and analog mixing

– 16-bit linear audio stereo DAC (96, 48, 44.1,

and 32 kHz, and derivatives)

– 16-bit linear audio stereo ADC (48, 44.1, and

32 kHz, and derivatives)

– Digital microphone inputs

– Carkit

• Charger:

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

– Li-ion, Li-on polymer, and

cobalt-nickel-manganese charger

– Supports charging with ac-regulated charger

(maximum 7 V), USB host devices, Mobile

Computing Promotion Consortium (MCPC)

devices, USB chargers, and carkit chargers

(maximum 7 V)

– Backup battery charger

• USB:

– USB 2.0 OTG-compliant HS transceivers

– 12-bit ULPI

– USB power supply (5-V CP for VBUS)

– CEA-2011: OTG transceiver interface

specification

– CEA-936A: Mini-USB analog carkit interface

specification

– MCPC ME-universal asynchronous

receiver/transmitter (UART) GL-006

specification

• Additional features:

– LED driver circuit for two external LEDs

– 10-bit MADC with 3 to 8 external inputs

– RTC and retention modules

– HS inter-integrated circuit (I2C™) serial

control

– Thermal shutdown and hot-die detection

– Keypad interface (up to 8 × 8)

– External vibrator (vibrator) control

– 19 GPIO devices

– 0.4-mm pitch, 209 pin, 7 × 7 mm package

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2Bluetooth is a registered trademark of Bluetooth SIG, Inc.

Copyright © 2008–2011, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Powercontrol

(BBS-backup

VRRTC-UVLO)

Powerreferences

(Vref-Iref-BandGap)

Powerprovider

(LDOs-DCDCs)

RTC

32kHz

Clockslicer RCoscillator

Thermalmonitor

system

Powersubchip(A-D)

Poweranalog

Powerdigital

Auxiliarysubchip(A-D)

Audiosubchip(A-D)

Interfacesubchip(D)

Audio

PLL

AUDIOdigital

Bluetooth

interface

PCM

interface

TDM/I2S

interface

Audioandvoicefilters

(RXand TXpaths)

+

Vibratorcontrol

AUDIO

analog

Wrapper

digital

Analogand

digitalmic

bias

Digitalmic

interface

AudioRXamplifiers

Micamplifiers

Analogvolumecontrol

D/A converters

A/Dconverters

Differentialvibrator

Carkitpreamplifiers

MADCTOP

MADC

digital

state-machine

MADCanalog

(SAR-Vref)

BCITOP

BCI

digital

BCIanalog

USBsubchip(A-D)

SIH

CardDet1

CardDet2

GPIO

PIH

TAP

OCP

SIH

RTC

Felica

PMCmaster

PMCslave

SlaveOCP

wrapper

13MHz/32kHz

LEDdigital

LEDanalog

LEDTOP

Vibrator

control(D)

Keypad

(D)

USB

digital

(ULPI/

registers

interrupts

CEA and

MCPC

carkit)

Device

Shundan

Smart

Reflex

Precharge

loop

Mainloop

MainDAC

Mainaux

Analog

carkit

interfaces

OTG

module

USB2.0

transceiver

USBpower

supply

USB

precharge

module

Clocks

Digitalsignal(s)

Analogsignal(s)

Clock

generator

PCM(2)

PCM(4)

TDM(4)

StartADC

LedSync

ULPI(12)

UART(2)

BERCLK

BERDATA

Clocks

OCP

SIH_INT

TAP

OCP

Clocks

SIH_INT

Clo cks

TAP

I2C A pad

I2CBpad

ClkIn/Out

GPIOpad

Precharge

PM

Precharge

status

Shifters

OCP SR

SIH_INT

OCP

TAP

Clocks

SIH_INT

OCP

TAP

TAP

032-003

TPS65950

www.ti.com

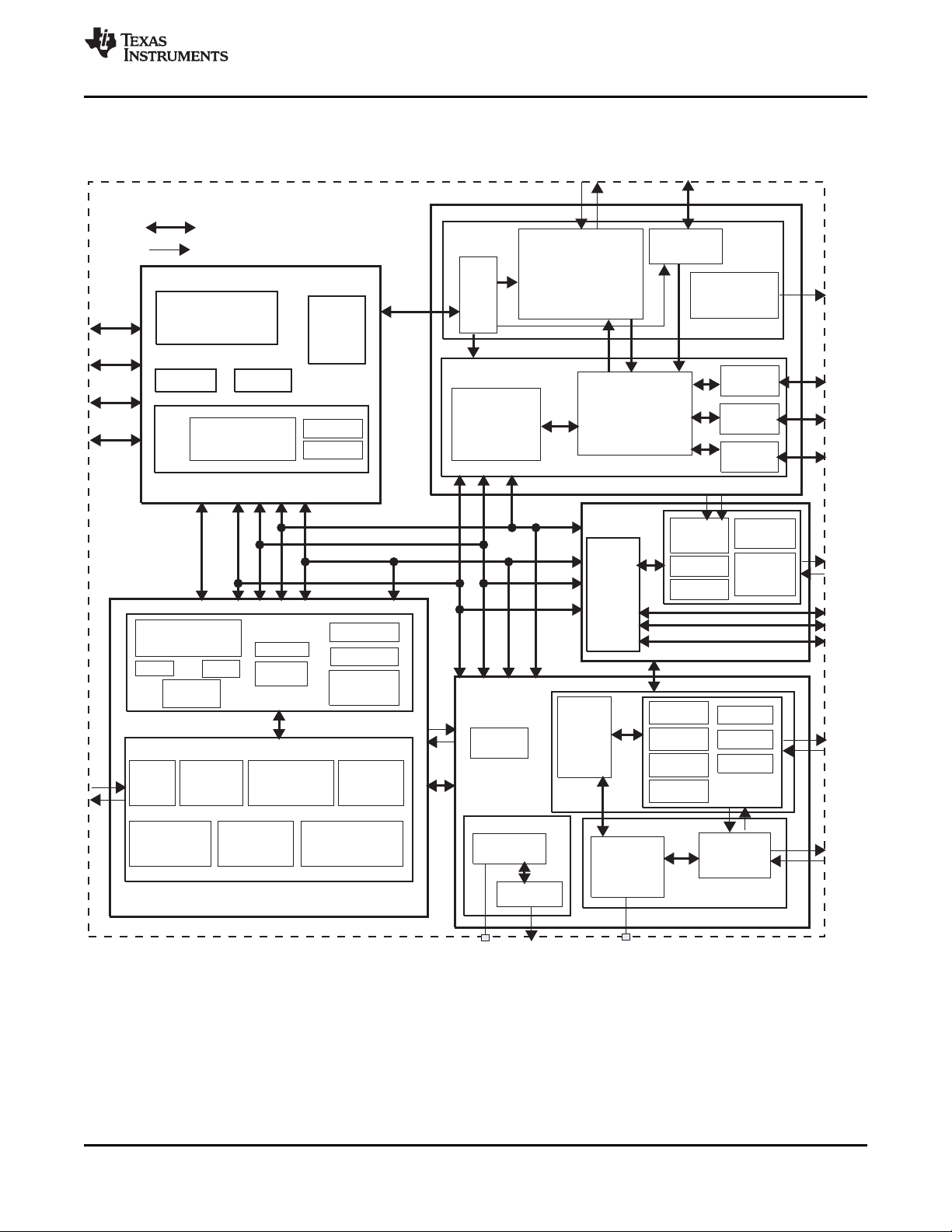

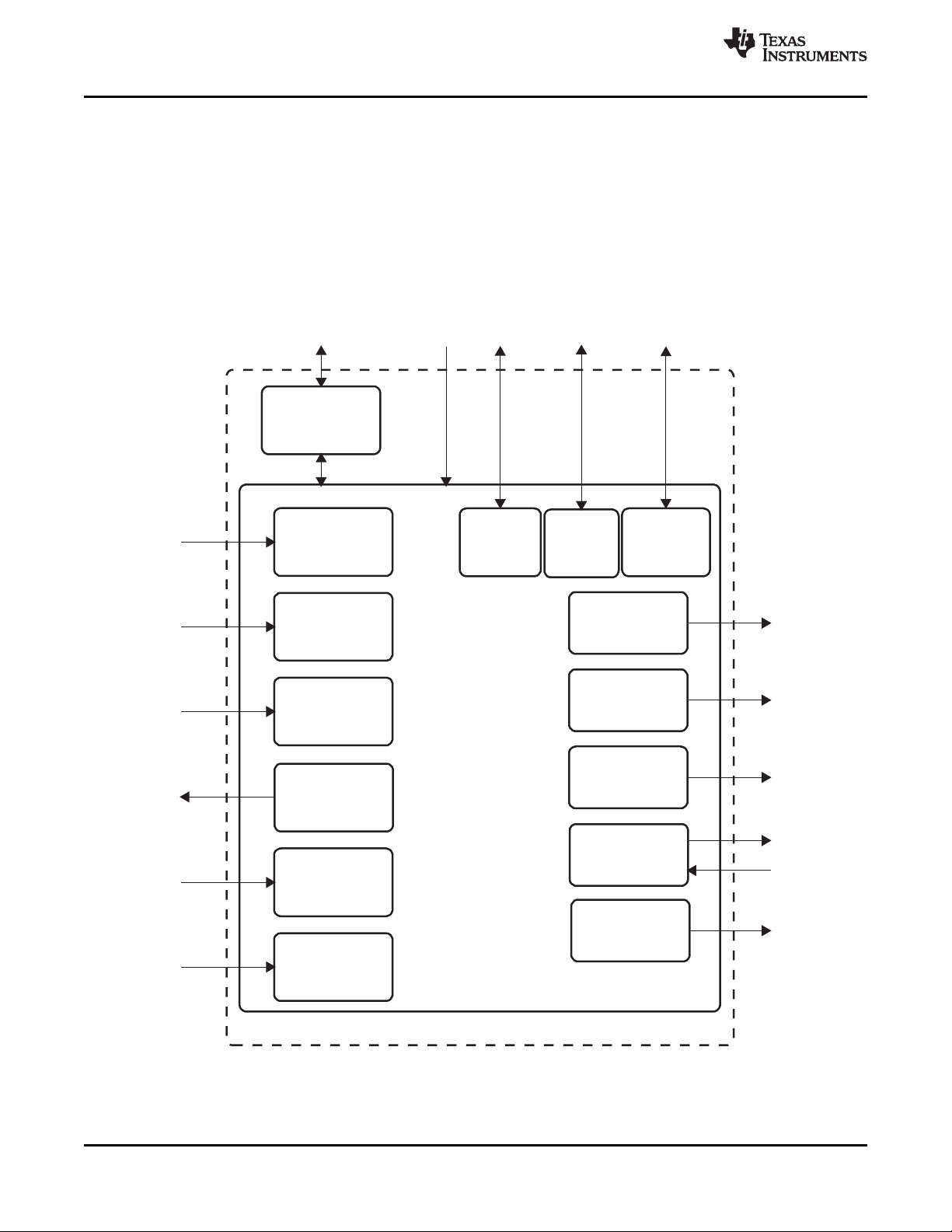

1.2 TPS65950 Block Diagram

Figure 1-1 is a block diagram of the TPS65950.

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

Copyright © 2008–2011, Texas Instruments Incorporated Introduction 13

Figure 1-1. TPS65950 Block Diagram

Submit Documentation Feedback

Product Folder Link(s): TPS65950

032-088

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

2 Terminal Description

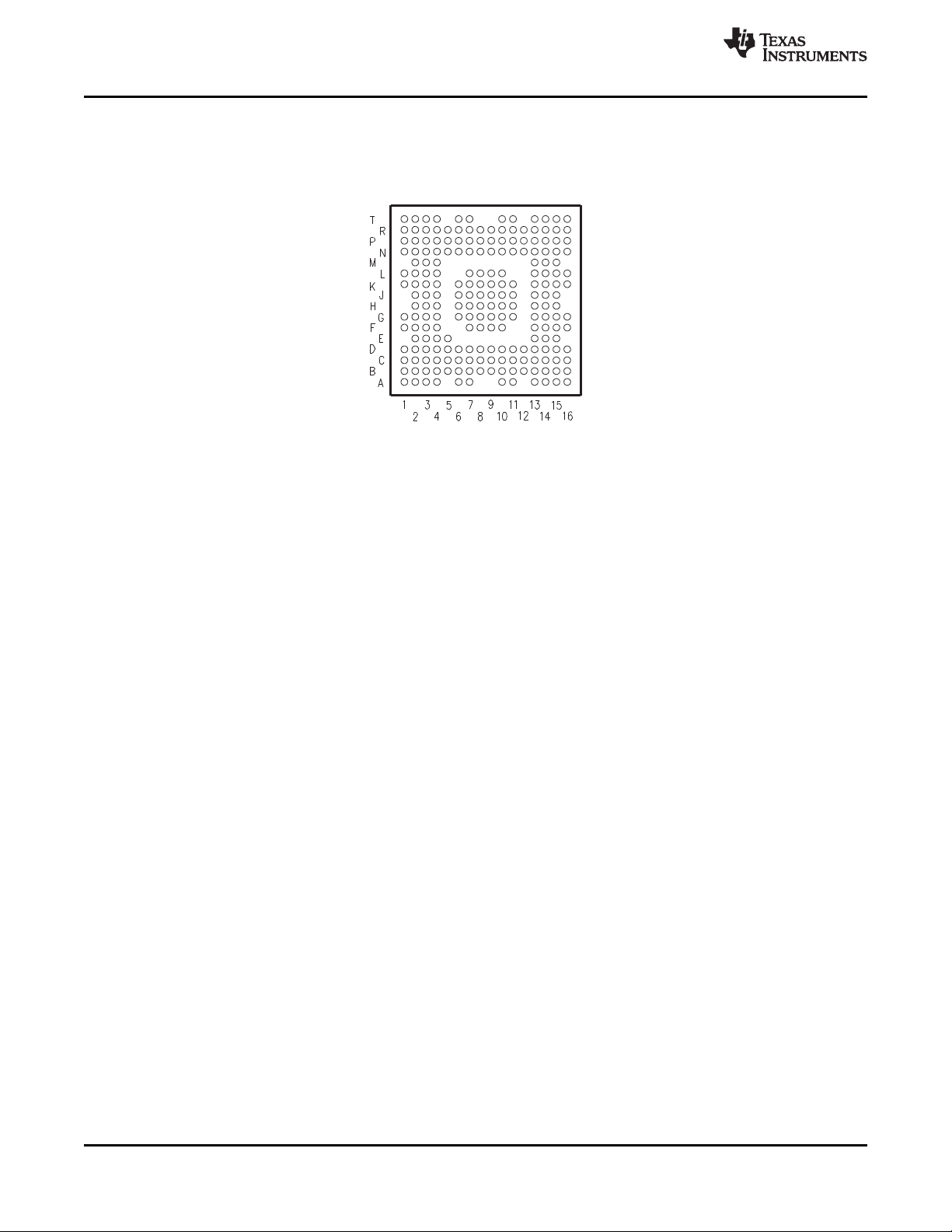

Figure 2-1 shows the ball locations for the 209-ball plastic ball grid array (PBGA) package and is used

with Table 2-1 to locate signal names and ball grid numbers.

2.1 Corner Balls

The four corner balls (see the following list) are not usable for functional pins:

• Test

• TestV1

• Test.RESET

• TestV2

www.ti.com

Figure 2-1. PBGA Bottom View

The eight corner adjacent balls are:

• RFID.EN

• UART1.TXD

• JTAG.TDI/BERDATA

• JTAG.CLK/BERCLK

• PCM.VFS

• PCM.VDX

• PCM.VDR

• PCM.VCK

14 Terminal Description Copyright © 2008–2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65950

TPS65950

www.ti.com

2.2 Ball Characteristics

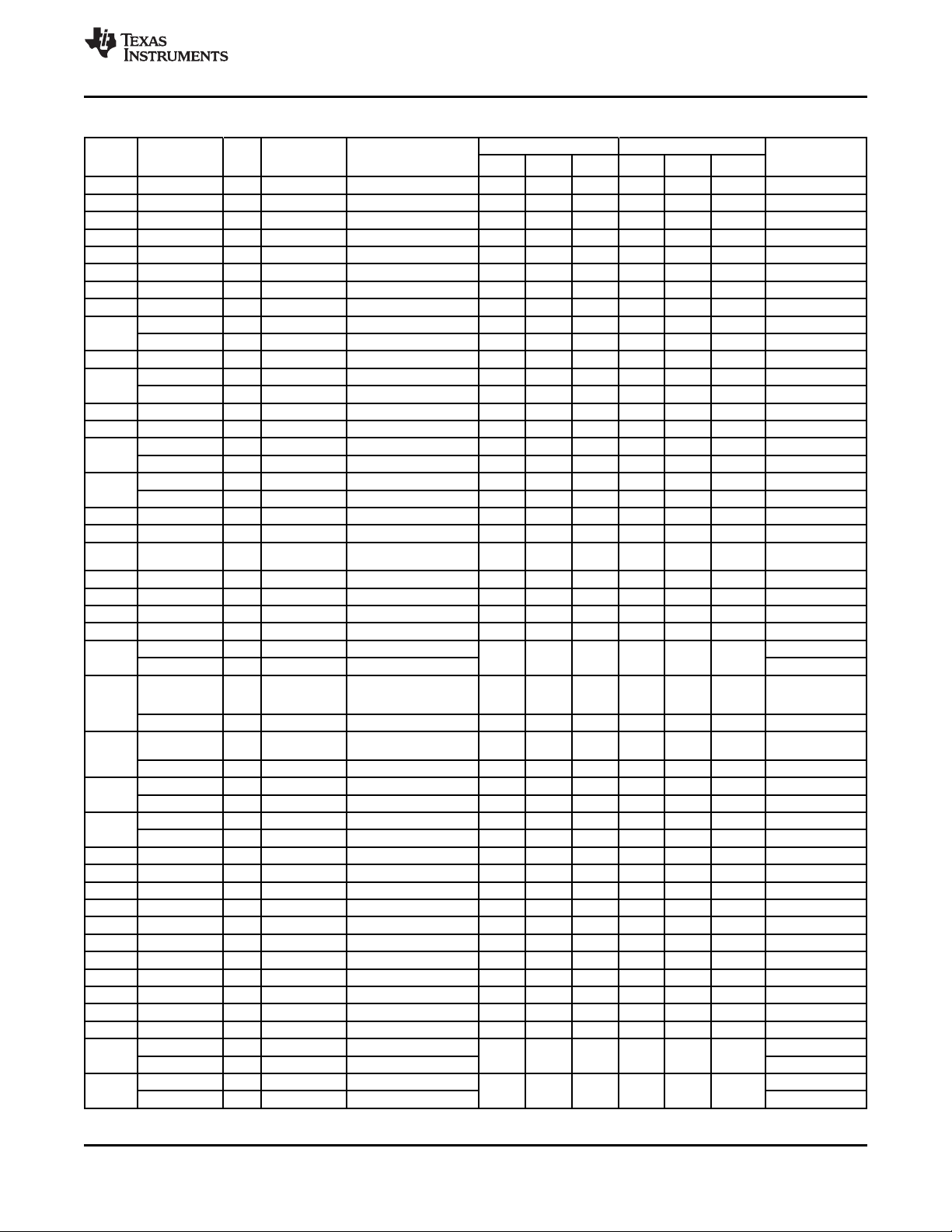

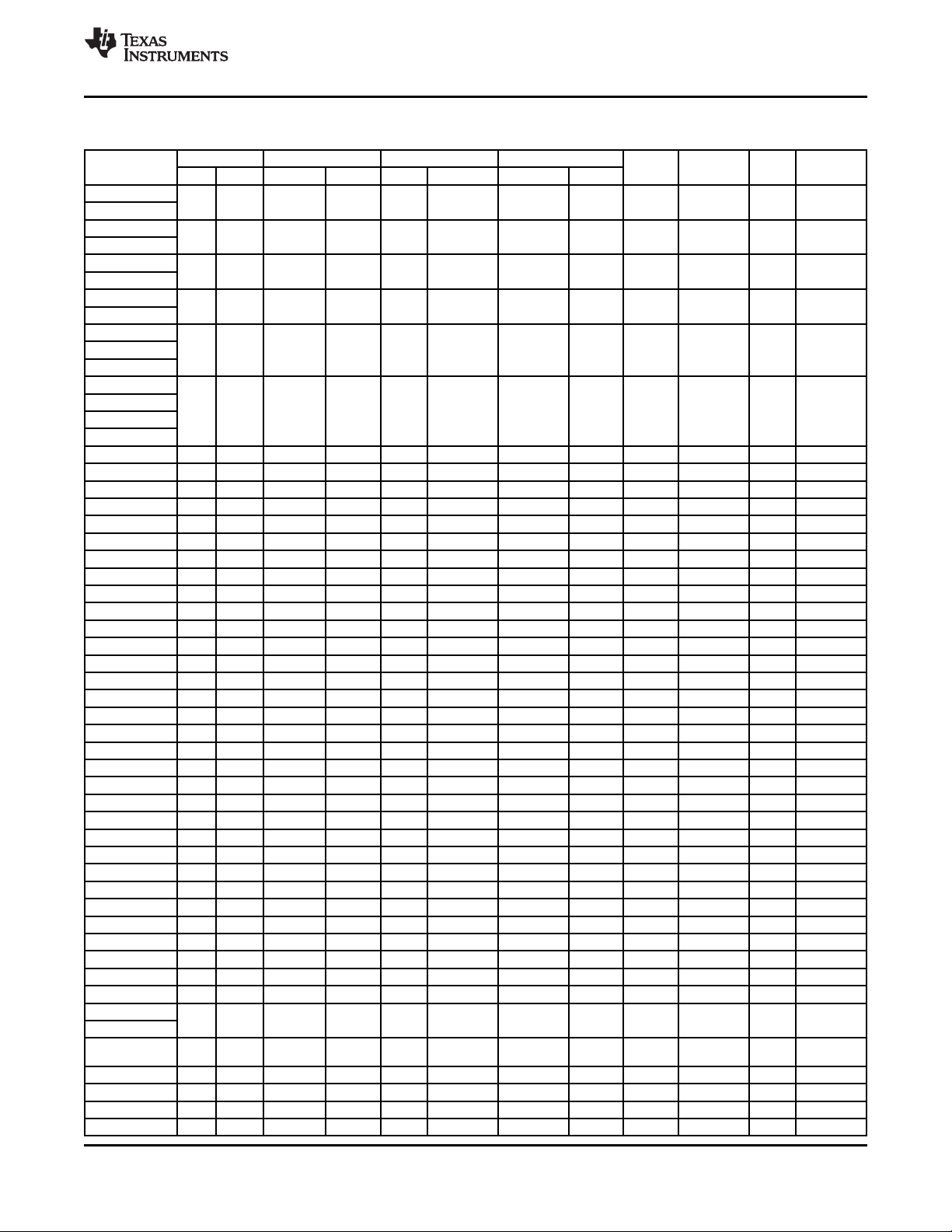

Table 2-1 describes the terminal characteristics and the signals multiplexed on each pin. The following list

describes the column headings in Table 2-1:

1. Ball: Ball number(s) associated with each signal(s)

2. Pin Name: Names of all the signals that are multiplexed on each ball

3. A/D: Analog or digital signal

4. Type: Terminal type when a particular signal is multiplexed on the terminal

– I = Input

– O = Output

– OD = Open drain

5. Reference Level: Voltage applied to the I/O cell (see the power module and battery charger interface

[BCI] chapters for values).

6. PU/PD: Denotes the presence of an internal pullup or pulldown. Pullups and pulldowns can be enabled

or disabled through software.

7. Min = Minimum value

8. Typ = Typical value

9. Max = Maximum value

10. Buffer Strength: Drive strength of the associated output buffer

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

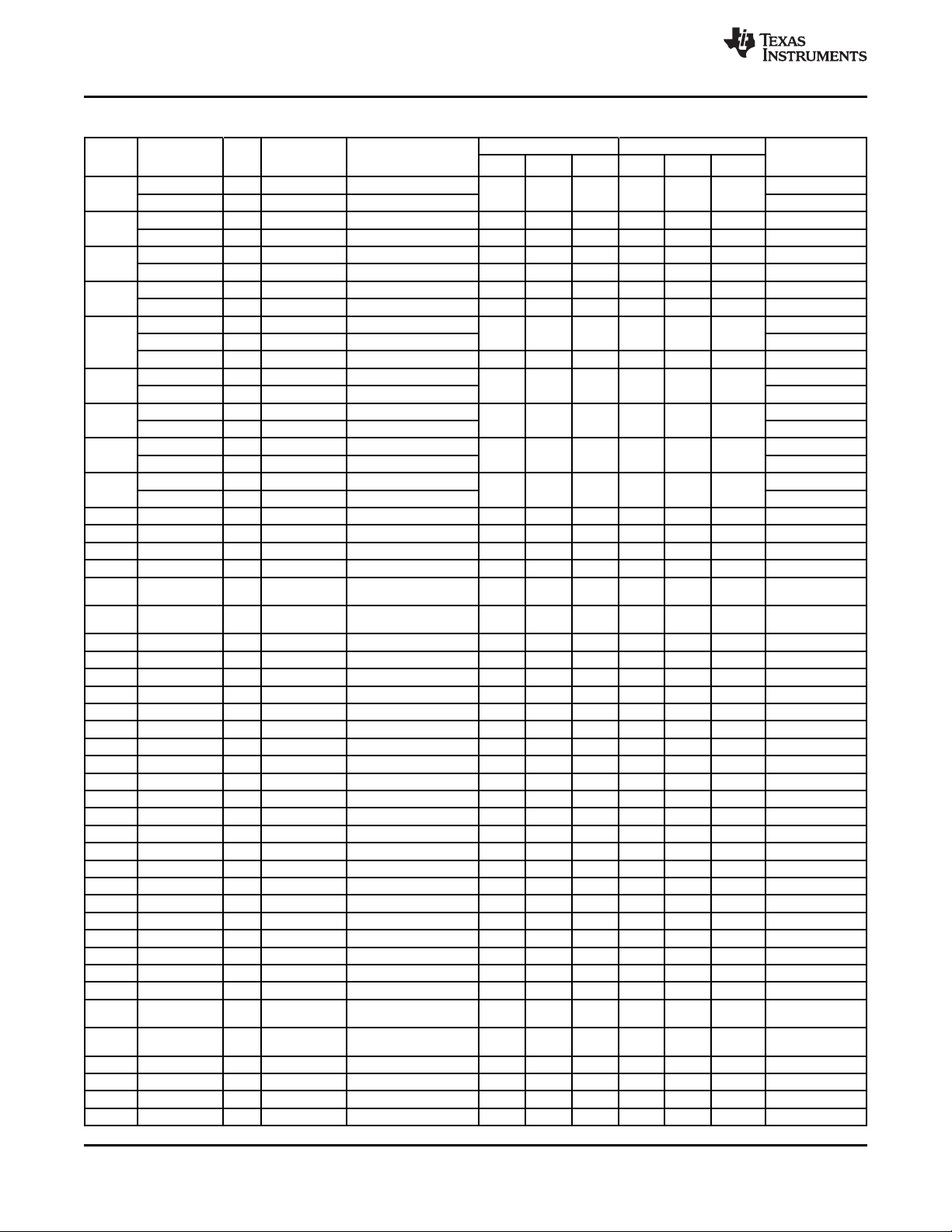

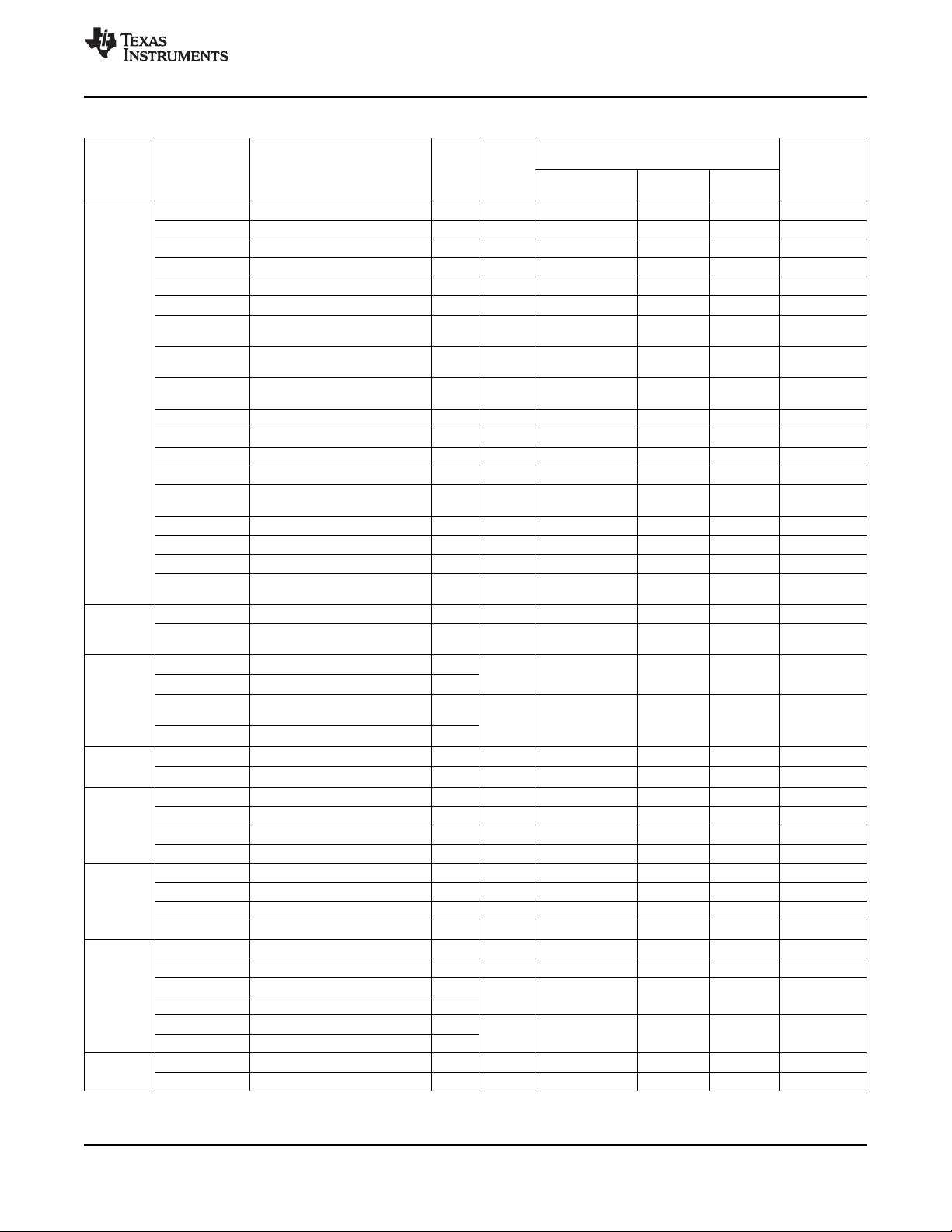

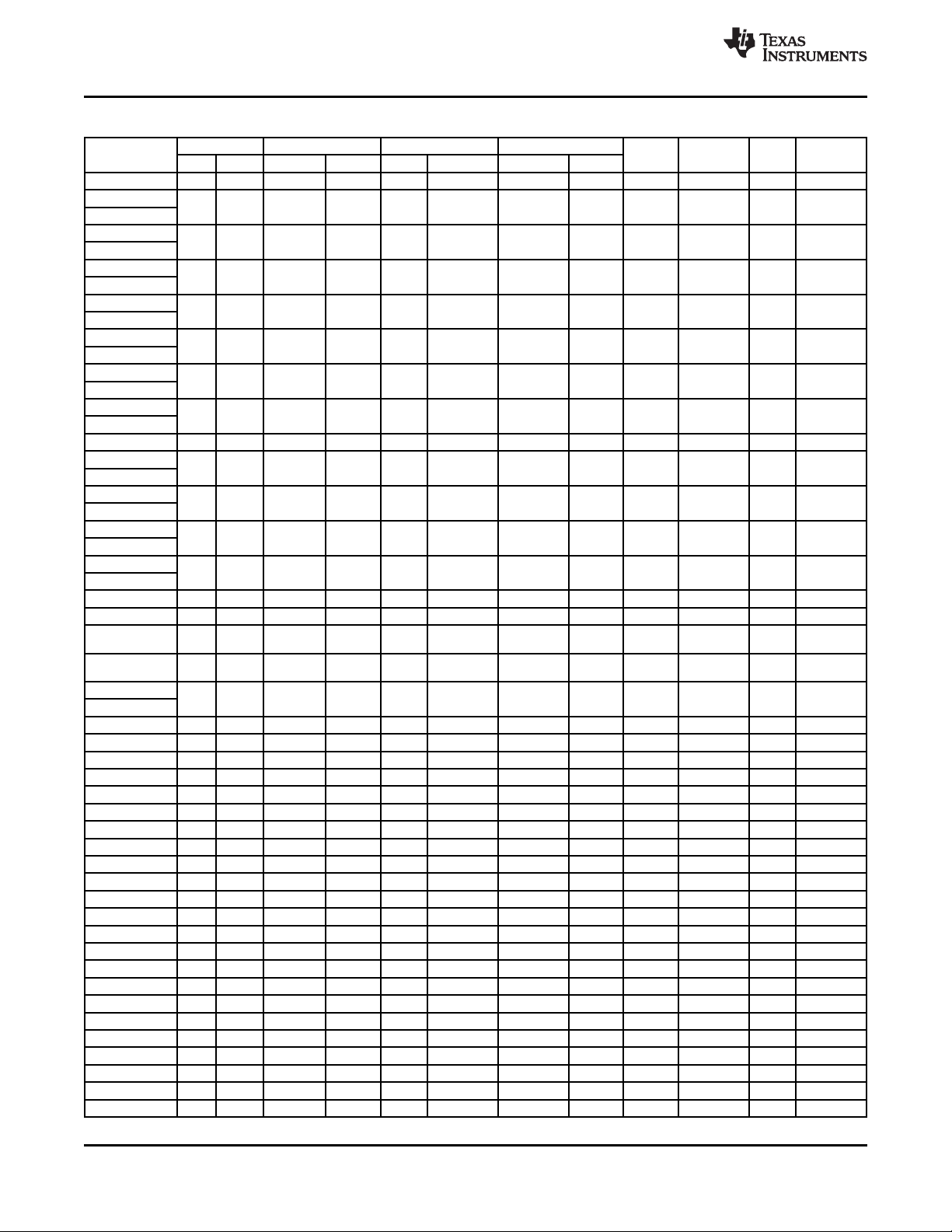

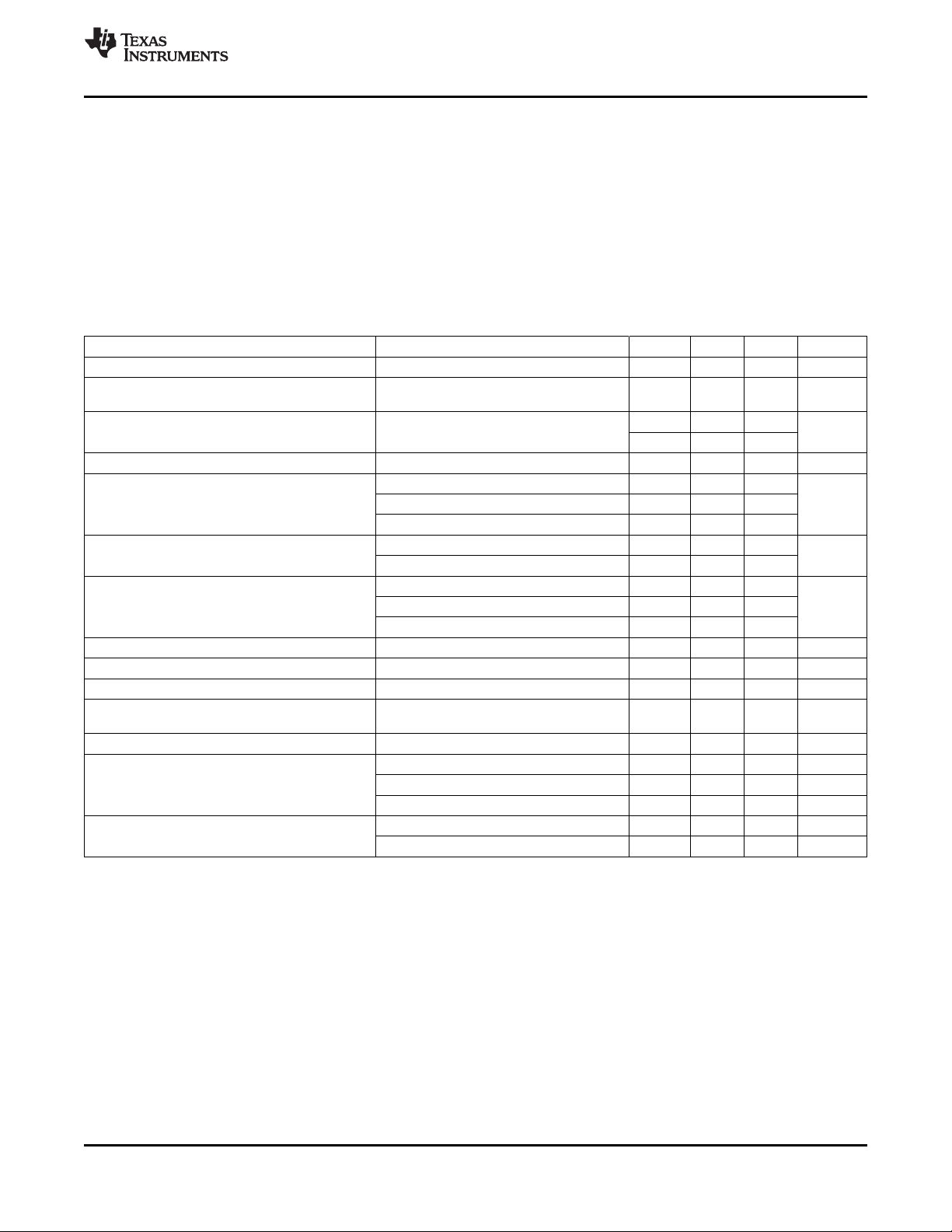

Table 2-1. Ball Characteristics

Ball[1] Type[4] Strength

H4 ADCIN0 A I/O VINTANA1.OUT

J3 ADCIN1 A I/O VINTANA1.OUT

G3 ADCIN2 A I VINTANA2.OUT

P5 VCCS A I VBAT + 0.2

N5 VAC A Power VACCHARGER

P4 VBATS A I VBAT

N4 PCHGAC A I VACCHARGER

N6 PCHGUSB A I VBUS

N2 VPRECH A O VPRECH

N1 BCIAUTO A I VPRECH

P6 ICTLUSB1 A O VBUS

P1 ICTLUSB2 A O VCCS

N7 ICTLAC1 A O VACCHARGER

P2 ICTLAC2 A O VCCS

R5 VBAT A Power VBAT

P12 75 100 202 59 100 144

N12 75 100 202 59 100 144

L4 156 220 450 59 100 144

P13 156 220 450 59 100 144

M4 PWM0 D O IO_1P8 75 100 202 59 100 144 4

Pin A/D Reference Level

Name[2] [3] RL[5]

GPIO0/CD1 D I/O IO_1P8 8

JTAG.TDO D I/O IO_1P8 8

GPIO1/CD2 D I/O IO_1P8 2

JTAG.TMS D I IO_1P8

GPIO2 D I/O IO_1P8 2

Test1 D I/O IO_1P8 2

GPIO15 D I/O IO_1P8 2

Test2 D I/O IO_1P8 2

GPIO6 D I/O IO_1P8 2

Test3 D I/O IO_1P8 2

PU[6] (kΩ) PD[6] (kΩ) Buffer

Min[7] Typ[8] Max[9] Min Typ Max

(mA)[10]

Copyright © 2008–2011, Texas Instruments Incorporated Terminal Description 15

Submit Documentation Feedback

Product Folder Link(s): TPS65950

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

www.ti.com

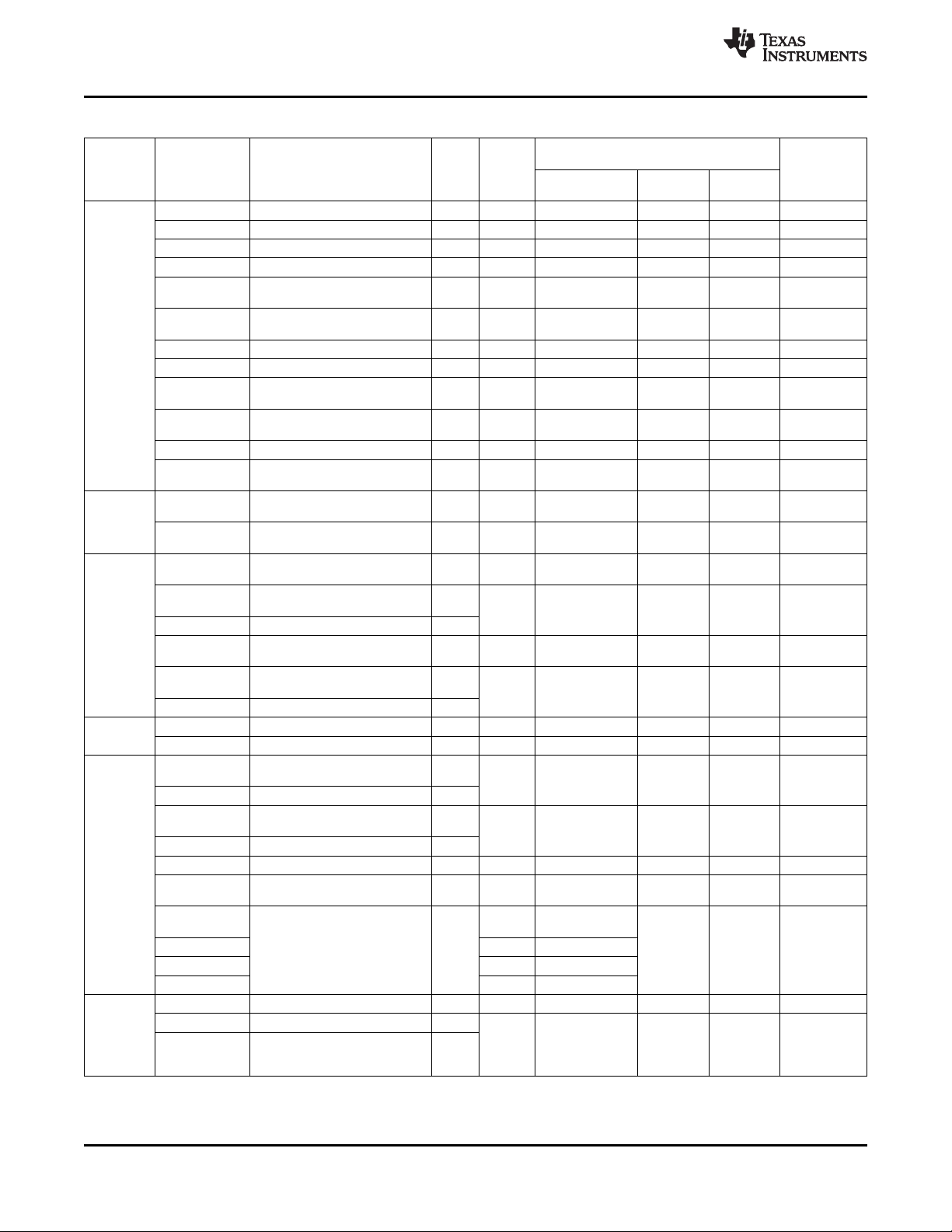

Table 2-1. Ball Characteristics (continued)

Ball[1] Type[4] Strength

N14 75 100 202 59 100 144

J9 START.ADC D I IO_1P8

C13 SYSEN D OD/I IO_1P8 4.7 7.35 10 2

C6 CLKEN D O IO_1P8 2

D7 CLKEN2 D O IO_1P8 2

G10 CLKREQ D I IO_1P8 60 100 146

F10 INT1 D O IO_1P8 2

F9 INT2 D O IO_1P8 2

A13 NRESPWRON D O IO_1P8 2

B13 NRESWARM D I IO_1P8 2

A11 PWRON D I VBAT

B14 NC

P7 NSLEEP1 D I IO_1P8

G9 NSLEEP2 D I IO_1P8

D13 CLK256FS

F8 VMODE1 D I IO_1P8

K11 BOOT0 A/D I/O VBAT

J11 BOOT1 A/D I/O VBAT

A10 REGEN D OD VBAT 5.5 8 12 2

H8 MSECURE D I IO_1P8

N16 VREF A Power VREF

N15 AGND A Power GND GND

C4

D6

D4 I2C.CNTL.SDA D I/O IO_1P8 2.5 3.4 12

D5 I2C.CNTL.SCL D I IO_1P8 2.5 3.4 12

R1 PCM.VCK D I/O IO_1P8 2

T2 PCM.VDR D I/O IO_1P8 2

T15 PCM.VDX D I/O IO_1P8 2

R16 PCM.VFS D I/O IO_1P8 2

L3 I2S.CLK D I/O IO_1P8 2

K6 I2S.SYNC D I/O IO_1P8 2

K4 I2S.DIN D I IO_1P8 2

K3 I2S.DOUT D O IO_1P8 2

E2 MIC.MAIN.P A I MICBIAS1.OUT

F2 MIC.MAIN.M A I MICBIAS1.OUT

G2

H2

E3 HSMIC.P A I VINTANA2.OUT

F3 HSMIC.M A I VINTANA2.OUT

D10 VBAT.LEFT A Power VBAT

D9 VBAT.LEFT A Power VBAT

B9 IHF.LEFT.P A O VBAT

B10 IHF.LEFT.M A O VBAT

C10 GND.LEFT A Power GND GND

C9 GND.LEFT A Power GND GND

D12 VBAT.RIGHT A Power VBAT

Pin A/D Reference Level

Name[2] [3] RL[5]

GPIO7 D I/O IO_1P8 2

VIBRA.SYNC D I IO_1P8

PWM1 D O IO_1P8 4

Test4 D I/O IO_1P8 2

(1)

NC

I2C.SR.SDA D I/O IO_1P8 2.5 3.4 12

VMODE2 D I IO_1P8 2

I2C.SR.SCL D I/O IO_1P8 2.5 3.4 12

MIC.SUB.P A I MICBIAS2.OUT

DIG.MIC.0 A I VMIC1.OUT

MIC.SUB.M A I MICBIAS2.OUT

DIG.MIC.1 A I VMIC2.OUT

D O IO_1P8 2

(1) To avoid reflection on this pin caused by impedance mismatch, a serial resistance (Rs) of 33 Ω must be added.

16 Terminal Description Copyright © 2008–2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65950

PU[6] (kΩ) PD[6] (kΩ) Buffer

Min[7] Typ[8] Max[9] Min Typ Max

(mA)[10]

TPS65950

www.ti.com

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

Table 2-1. Ball Characteristics (continued)

Ball[1] Type[4] Strength

D11 VBAT.RIGHT A Power VBAT

B11 IHF.RIGHT.P A O VBAT

B12 IHF.RIGHT.M A O VBAT

C12 GND.RIGHT A Power GND GND

C11 GND.RIGHT A Power GND GND

A6 EAR.P A O VINTANA2.OUT

A7 EAR.M A O VINTANA2.OUT

B4 HSOL A O VINTANA2.OUT

B7

B5 HSOR A O VINTANA2.OUT

B8

F1 AUXL A I VINTANA2.OUT

G1 AUXR A I VINTANA2.OUT

D1

D2

E4 VHSMIC.OUT A Power VINTANA2.OUT

D3 MICBIAS.GND PowerGND GND

J4 / J6 /J7 /

J8 / E5

R10 AVSS2 A Power GND GND

M15 AVSS3 A Power GND GND

C7 AVSS4 A Power GND GND

B1 UART1.TXD D OD External 1.8 to 3.3 V 2

D8

N11

P11

N8

N9

L10 MANU D I VUSB.3P1 162 280 414

N10 32KCLKOUT D O IO_1P8

P16 32KXIN A I IO_1P8

P15 32KXOUT A O IO_1P8

A14 HFCLKIN A I IO_1P8

R12 HFCLKOUT D O IO_1P8

R8 VBUS A Power VBUS

T10 DP/UART3.RXD A I/O VBUS 2

T11 DN/UART3.TXD A I/O VBUS 2

R11 ID A I/O VBUS 2

L15 UCLK D I IO_1P8 16

L14 75 100 202 59 100 144

L13 75 100 202 59 100 144

Pin A/D Reference Level

Name[2] [3] RL[5]

PreDriv.LEFT A O VINTANA2.OUT

VMID A Power VINTANA2.OUT

PreDriv.RIGHT A O VINTANA2.OUT

ADCIN7 A I VINTANA2.OUT

MICBIAS1.OUT A Power VINTANA2.OUT

VMIC1.OUT A Power VINTANA2.OUT

MICBIAS2.OUT A Power VINTANA2.OUT

VMIC2.OUT A Power VINTANA2.OUT

AVSS1 A Power GND GND

GPIO8 D I IO_1P8 4.7 7.4 10 5.9 7 8.3

UART1.RXD D I IO_1P8

RTSO/

CLK64K.OUT/ D OD VUSB.3P1 2

BERCLK.OUT

ADCIN5 A I VINTANA2.OUT

CTSI/

BERDATA.OUT

ADCIN3 A I VINTANA2.OUT

TXAF A I VUSB.3P1

ADCIN4 A I VINTANA2.OUT

RXAF A O VUSB.3P1

ADCIN6 A I VINTANA2.OUT

STP D I IO_1P8 16

GPIO9 D I/O IO_1P8 2

DIR D O IO_1P8 16

GPIO10 D I/O IO_1P8 2

D OD/CMOS/I/O VUSB.3P1 4.7 7.4 10 2

PU[6] (kΩ) PD[6] (kΩ) Buffer

Min[7] Typ[8] Max[9] Min Typ Max

(mA)[10]

Copyright © 2008–2011, Texas Instruments Incorporated Terminal Description 17

Submit Documentation Feedback

Product Folder Link(s): TPS65950

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

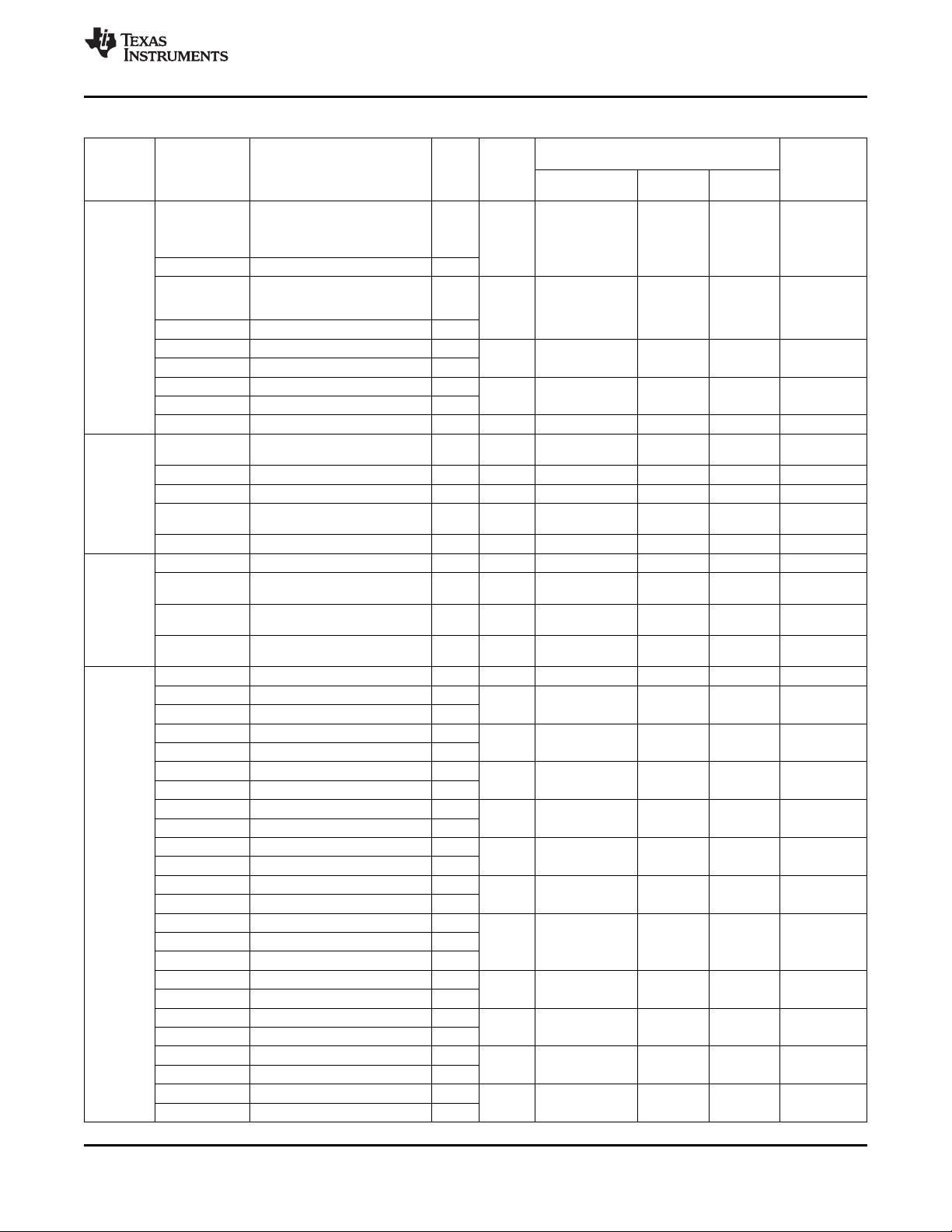

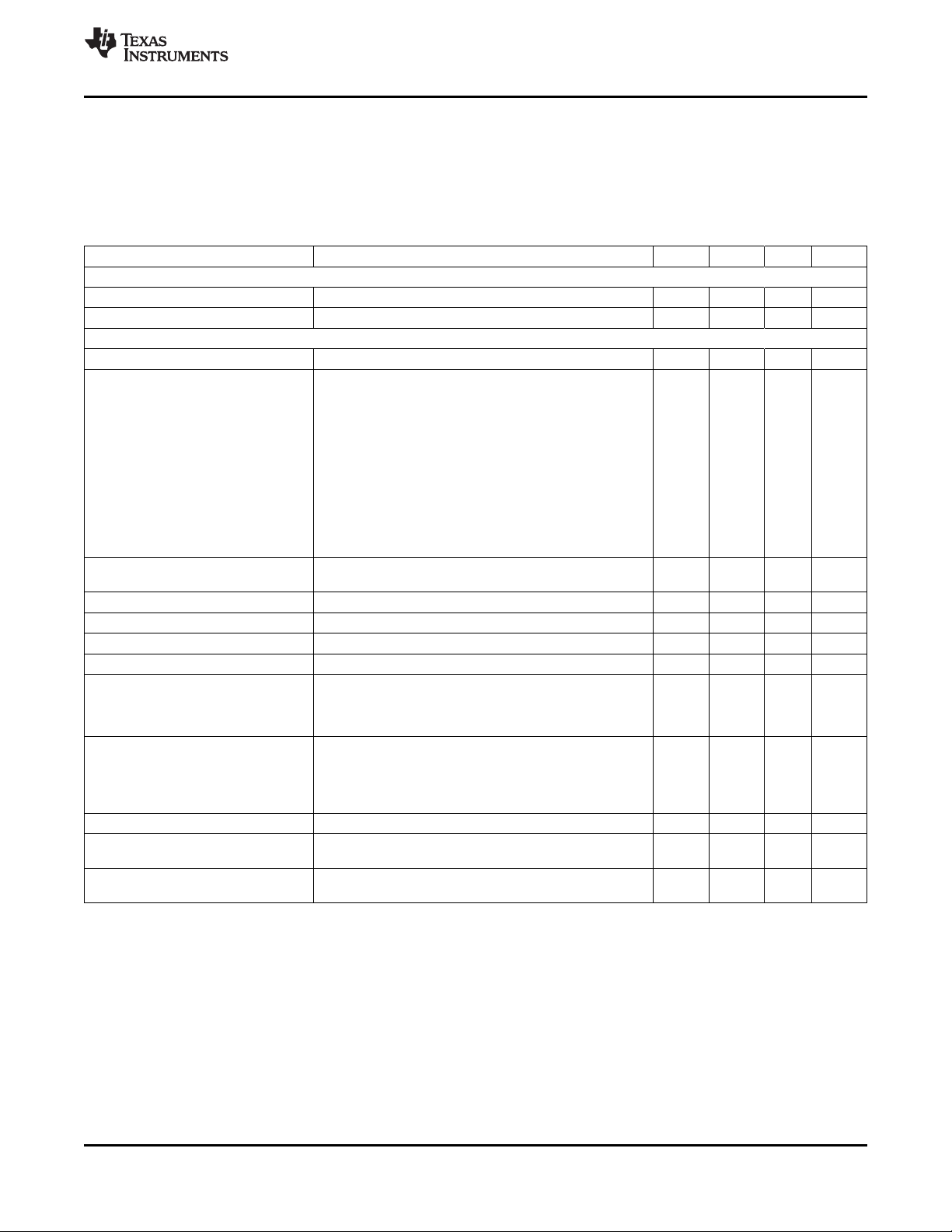

Table 2-1. Ball Characteristics (continued)

Ball[1] Type[4] Strength

M13 75 100 202 59 100 144

K14

K13

J14

J13 UART4.CTSO D O IO_1P8 16

G14 75 100 202 59 100 144

G13 75 100 202 59 100 144

F14 75 100 202 59 100 144

F13 75 100 202 59 100 144

T16 TEST.RESET A/D I VBAT 30 50 70

T1 TESTV1 A I/O VBAT

A16 TESTV2 A I/O VINTANA2.OUT

A1 TEST D I IO_1P8 60 100 146

A15 D I IO_1P8

B16 D I IO_1P8

R7 CP.IN A Power VBAT/VBUS

T7 CP.CAPP A O CP.CAPP

T6 CP.CAPM A O CP.CAPM

R6 CP.GND A Power GND GND

R9 VBAT.USB A Power VBAT

P9 VUSB.3P1 A Power VUSB.3P1

L1 VAUX12S.IN A Power VBAT

M2 VAUX1.OUT A Power VAUX1.OUT

M3 VAUX2.OUT A Power VAUX2.OUT

H15 VPLLA3R.IN A Power VBAT

K16 VRTC.OUT A Power VRTC.OUT

H14 VPLL1.OUT A Power VPLL1.OUT

J15 VSDI.CSI.OUT A Power VSDI.CSI.OUT

G16 VAUX3.OUT A Power VAUX3.OUT

B2 VAUX4.IN A Power VBAT

B3 VAUX4.OUT A Power VAUX4.OUT

C1 VMMC1.IN A Power VBAT

C2 VMMC1.OUT A Power VMMC1.OUT

A3 VMMC2.IN A Power VBAT

A4 VMMC2.OUT A Power VMMC2.OUT

K2 VSIM.OUT A Power VSIM.OUT

P8 A Power VINTUSB1P5.OUT

P10 A Power VINTUSB1P8.OUT

K1 VDAC.IN A Power VBAT

L2 VDAC.OUT A Power VDAC.OUT

K15 VINT.IN A Power VBAT

H3 VINTANA1.OUT A Power VINTANA1.OUT

Pin A/D Reference Level

Name[2] [3] RL[5]

NXT D O IO_1P8 16

GPIO11 D I/O IO_1P8 2

DATA0 D I/O IO_1P8 16

UART4.TXD D I IO_1P8

DATA1 D I/O IO_1P8 16

UART4.RXD D O IO_1P8 2

DATA2 D I/O IO_1P8 16

UART4.RTSI D I IO_1P8

DATA3 D I/O IO_1P8 16

GPIO12 D I/O IO_1P8 75 100 202 59 100 144 16

DATA4 D I/O IO_1P8 16

GPIO14 D I/O IO_1P8 2

DATA5 D I/O IO_1P8 16

GPIO3 D I/O IO_1P8 2

DATA6 D I/O IO_1P8 16

GPIO4 D I/O IO_1P8 2

DATA7 D I/O IO_1P8 16

GPIO5 D I/O IO_1P8 2

JTAG.TDI/

BERDATA

JTAG.TCK/

BERCLK

VINTUSB1P5.

OUT

VINTUSB1P8.

OUT

PU[6] (kΩ) PD[6] (kΩ) Buffer

Min[7] Typ[8] Max[9] Min Typ Max

60 100 140 60 100 140

(mA)[10]

www.ti.com

18 Terminal Description Copyright © 2008–2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65950

TPS65950

www.ti.com

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

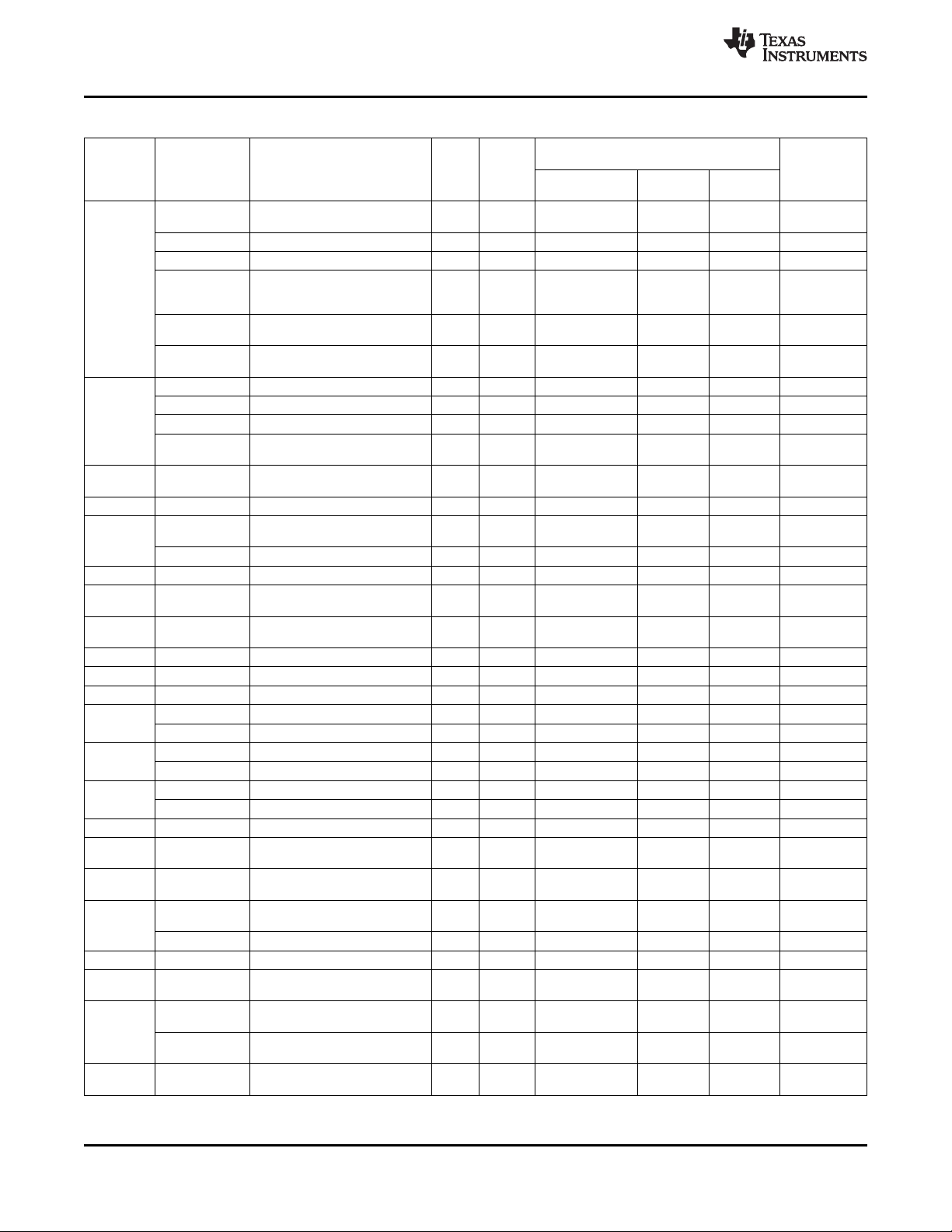

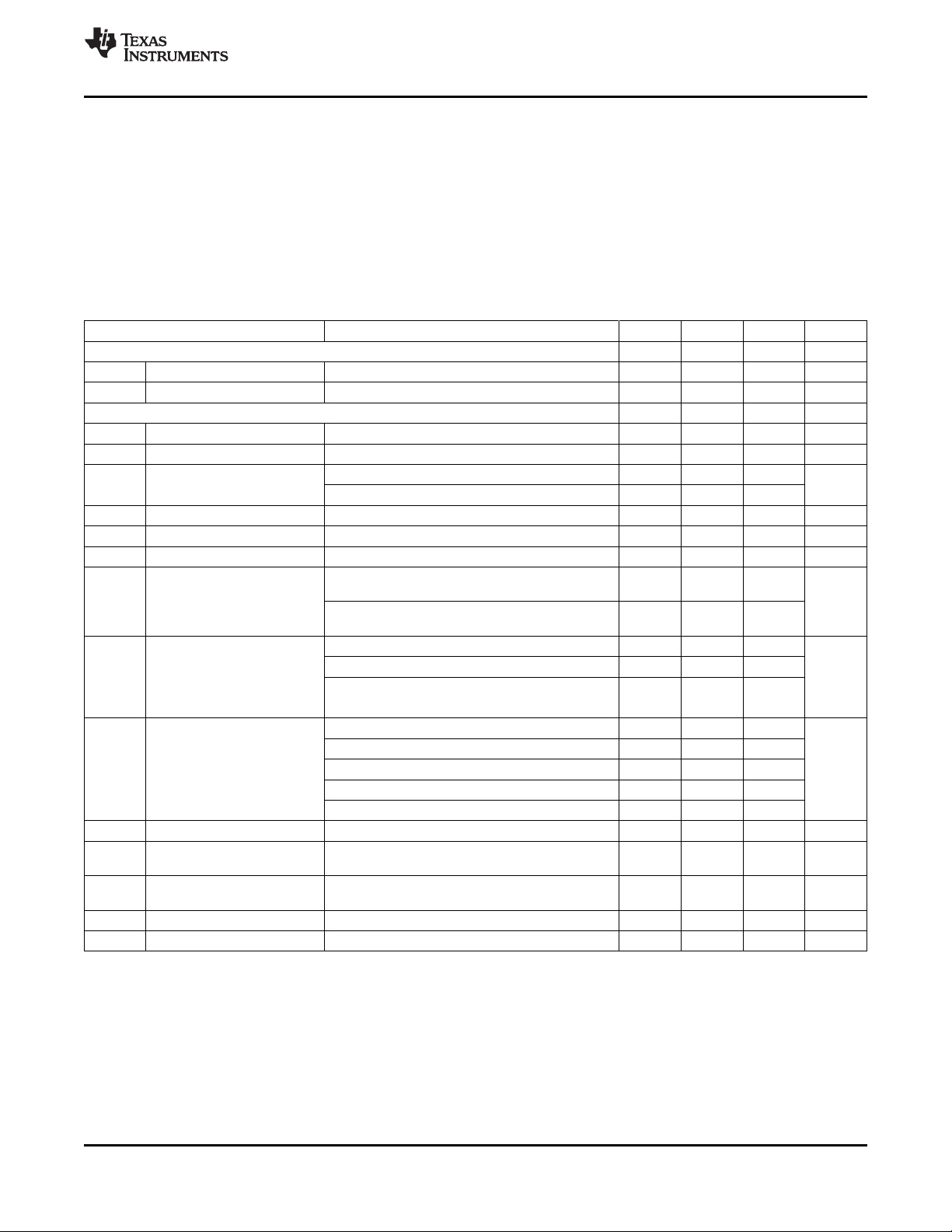

Table 2-1. Ball Characteristics (continued)

Ball[1] Type[4] Strength

J2 VINTANA2.OUT A Power VINTANA2.OUT

B6 VINTANA2.OUT A Power VINTANA2.OUT

L16 VINTDIG.OUT A Power VINTDIG.OUT

E15 VDD1.IN A Power VBAT

E14 VDD1.IN A Power VBAT

D14 VDD1.IN A Power VBAT

D16 VDD1.SW A O VBAT

D15 VDD1.SW A O VBAT

C14 VDD1.SW A O VBAT

E13 VDD1.FB A I

C16 VDD1.GND A Power GND GND

C15 VDD1.GND A Power GND GND

B15 VDD1.GND A Power GND GND

R13 VDD2.IN A Power VBAT

P14 VDD2.IN A Power VBAT

N13 VDD2.FB A I

T13 VDD2.SW A O VBAT

R14 VDD2.SW A O VBAT

T14 VDD2.GND A Power GND GND

R15 VDD2.GND A Power GND GND

P3 VIO.IN A Power VBAT

R4 VIO.IN A Power VBAT

N3 VIO.FB A I

R3 VIO.SW A O VBAT

T4 VIO.SW A O VBAT

R2 VIO.GND A Power GND GND

T3 VIO.GND A Power GND GND

M14 BKBAT A Power VBACK

C8 IO.1P8 A Power IO_1P8

H13 / H9 /

H10 / H11

F16 LEDGND A Power GND GND

G11 75 100 202 59 100 144

F15

G15

G8 KPD.C0 D OD IO_1P8

H7 KPD.C1 D OD IO_1P8

G6 KPD.C2 D OD IO_1P8

F7 KPD.C3 D OD IO_1P8

G7 KPD.C4 D OD IO_1P8

F4 KPD.C5 D OD IO_1P8

H6 KPD.C6 D OD IO_1P8

G4 KPD.C7 D OD IO_1P8

K9 KPD.R0 D I IO_1P8 8 10 12

K8 KPD.R1 D I IO_1P8 8 10 12

L8 KPD.R2 D I IO_1P8 8 10 12

K7 KPD.R3 D I IO_1P8 8 10 12

L9 KPD.R4 D I IO_1P8 8 10 12

J10 KPD.R5 D I IO_1P8 8 10 12

K10 KPD.R6 D I IO_1P8 8 10 12

L7 KPD.R7 D I IO_1P8 8 10 12

Pin A/D Reference Level

Name[2] [3] RL[5]

DGND A Power GND GND

GPIO13 D I/O IO_1P8

LEDSYNC D I IO_1P8

LEDA A OD VBAT

VIBRA.P A OD VBAT

LEDB A OD VBAT

VIBRA.M A OD VBAT

PU[6] (kΩ) PD[6] (kΩ) Buffer

Min[7] Typ[8] Max[9] Min Typ Max

(mA)[10]

Copyright © 2008–2011, Texas Instruments Incorporated Terminal Description 19

Submit Documentation Feedback

Product Folder Link(s): TPS65950

TPS65950

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

www.ti.com

Table 2-1. Ball Characteristics (continued)

Ball[1] Type[4] Strength

C3 BT.PCM.VDR D I/O IO_1P8 75 100 202 59 100 144

C5 BT.PCM.VDX D I/O IO_1P8 75 100 202 59 100 144

A2 RFID.EN D O VMMC2.OUT

Pin A/D Reference Level

Name[2] [3] RL[5]

GPIO16 D I/O IO_1P8

DIG.MIC.CLK0 D O IO_1P8

GPIO17 D I/O IO_1P8

DIG.MIC.CLK1 D O IO_1P8

PU[6] (kΩ) PD[6] (kΩ) Buffer

Min[7] Typ[8] Max[9] Min Typ Max

(mA)[10]

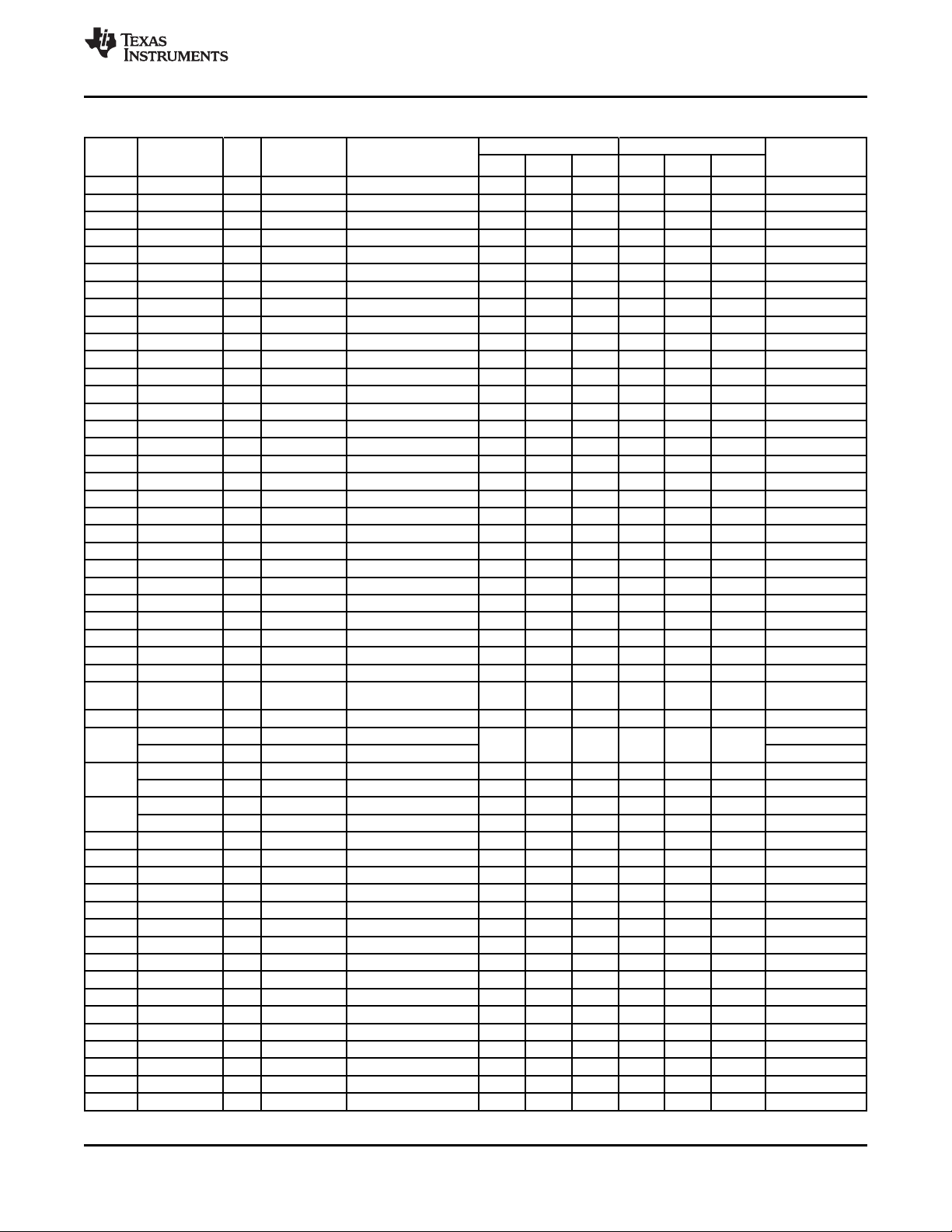

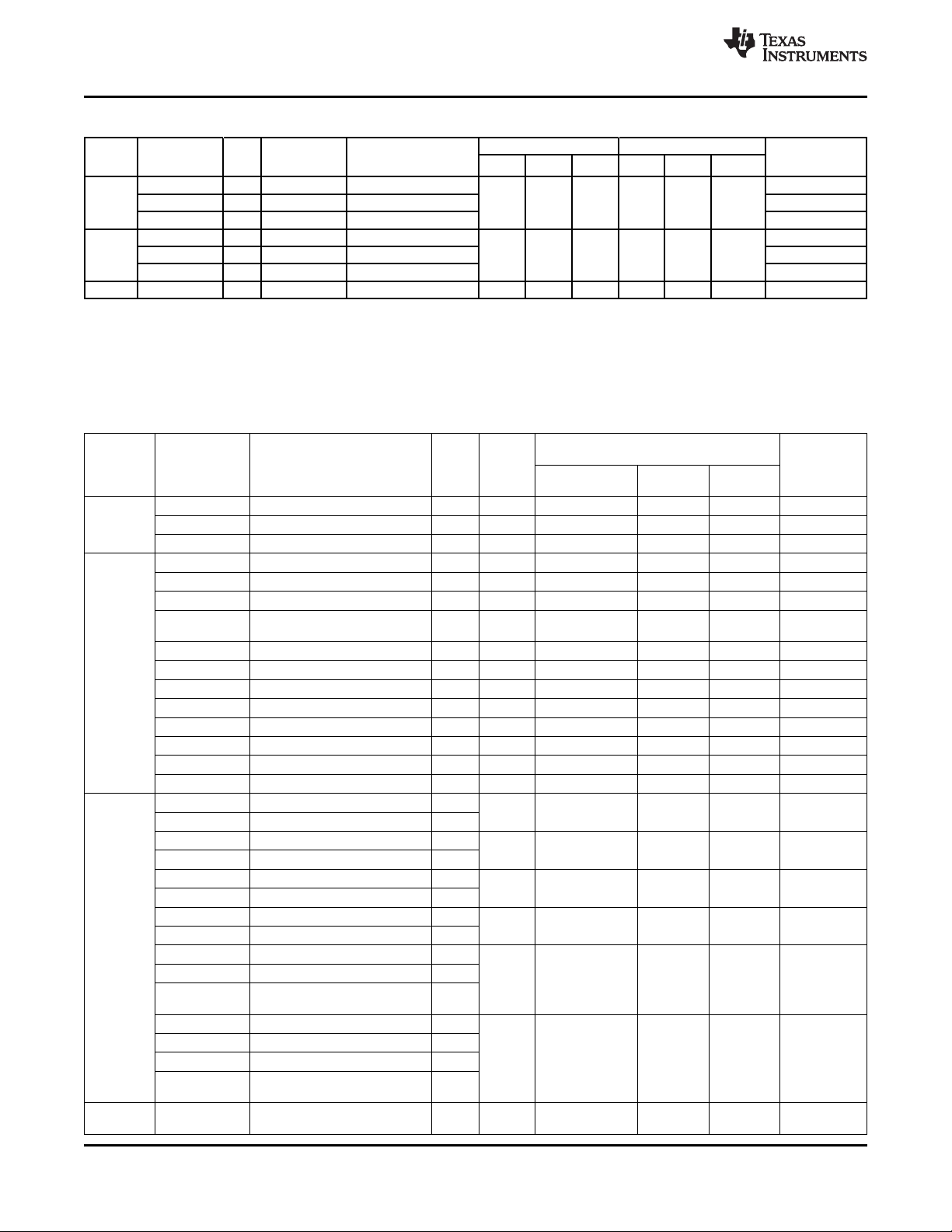

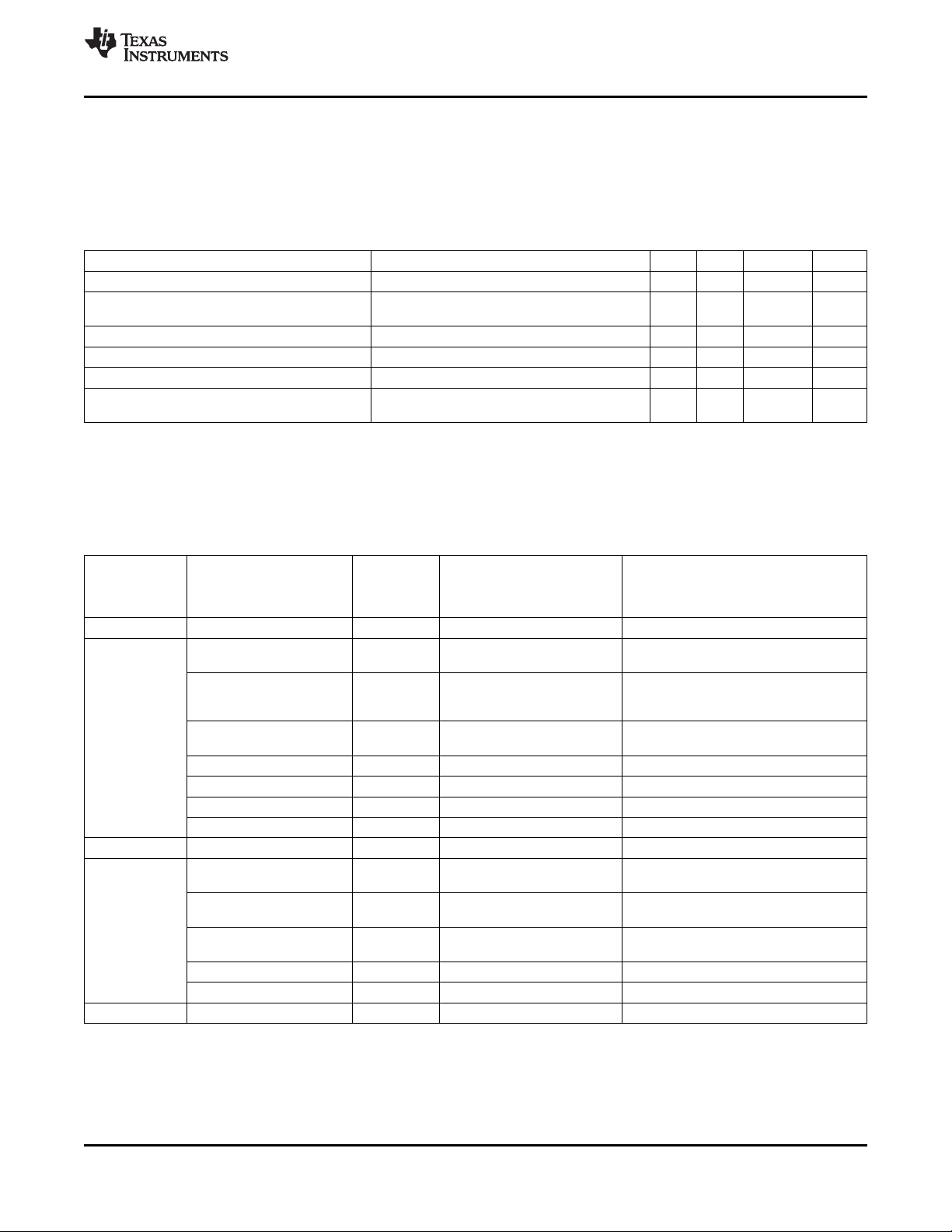

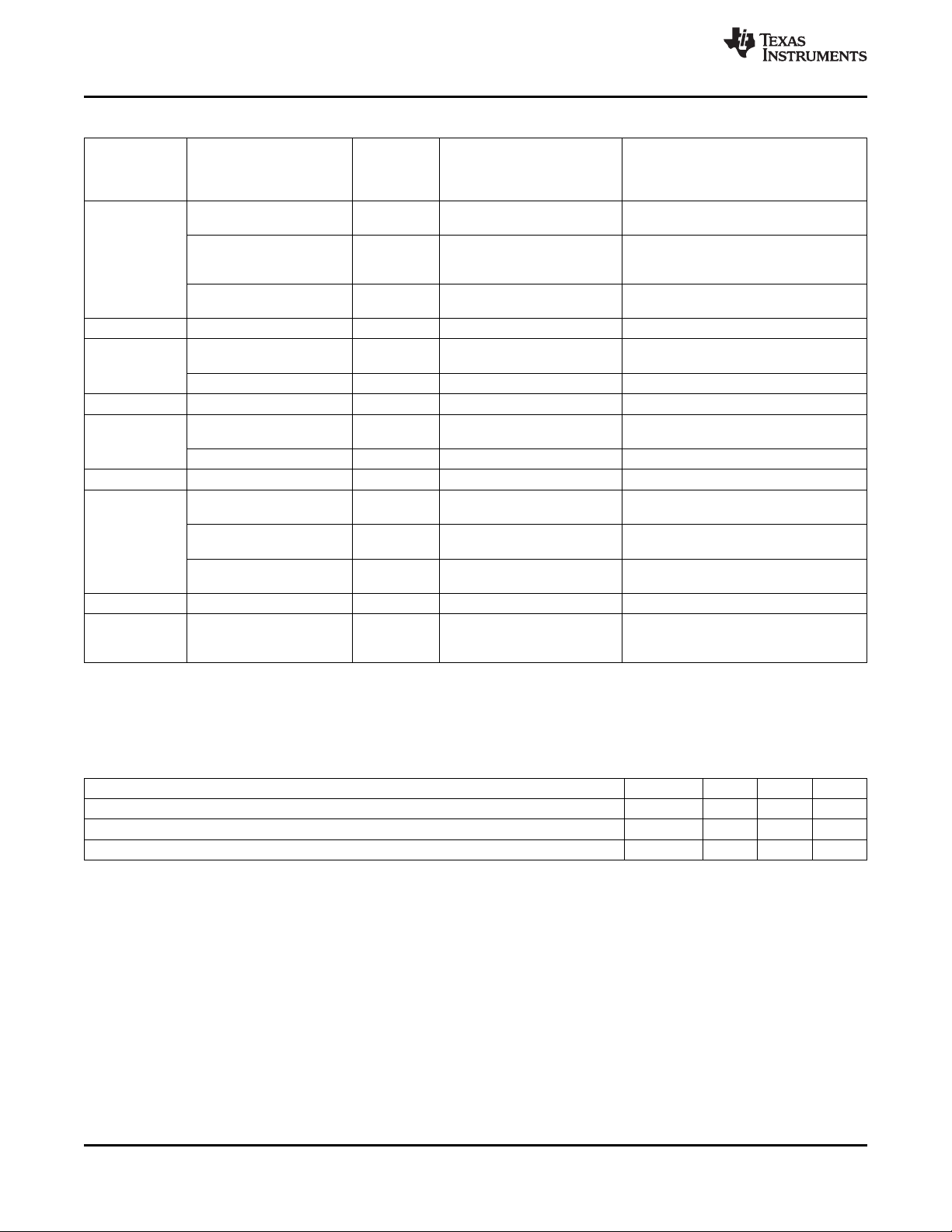

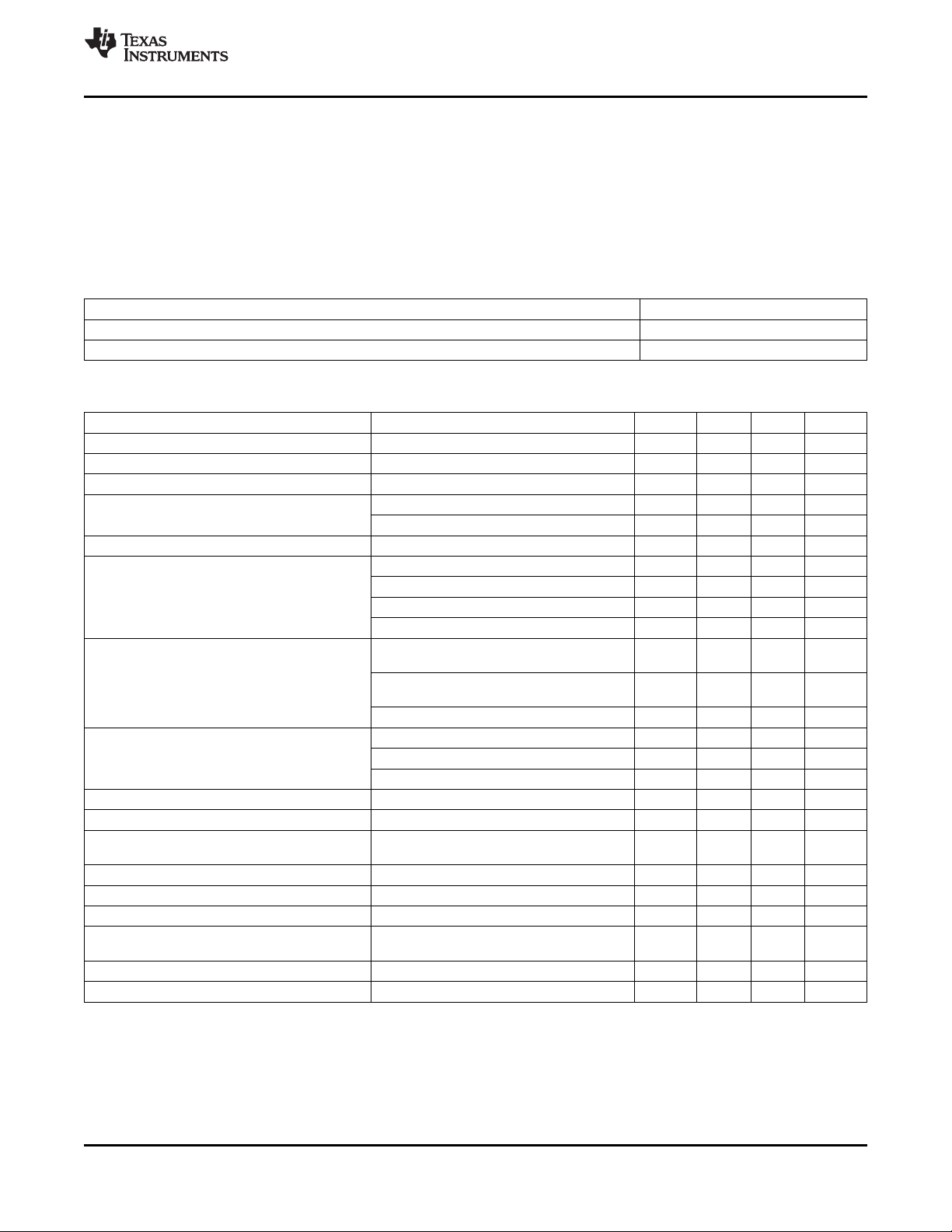

2.3 Signal Description

Table 2-2 lists the signals on the TPS65950; some signals are available on multiple pins.

Table 2-2. Signal Description

Configuration By Default After Reset

Module Description Type

Signal Unused

Name Features

(1)

Ball

Signal Type

ADCIN0 Battery type I/O H4 ADCIN0 I GND

ADC ADCIN1 Battery temperature I/O J3 ADCIN1 I GND

ADCIN2 General-purpose (GP) ADC input I G3 ADCIN2 I GND

VCCS Charge current sensing I P5 VCCS I Cap to GND

VAC Charge device input voltage Power N5 VAC Power GND

VBATS Charge current sensing I P4 VBATS I Cap to GND

PCHGAC I N4 PCHGAC I GND

ac precharge sense signal. Used

also for EEPROM

PCHGUSB USB precharge sense signal I N6 PCHGUSB I GND

Charger

VPRECH Precharge regulator output O N2 VPRECH O Cap to GND

BCIAUTO Linear charge specific boot mode I N1 BCIAUTO I GND

ICTLUSB1 USB power device control O P6 ICTLUSB1 O Floating

ICTLUSB2 USB power device control O P1 ICTLUSB2 O Floating

ICTLAC1 ac power device control O N7 ICTLAC1 O Floating

ICTLAC2 ac power device control O P2 ICTLAC2 O Floating

VBAT Battery voltage sensing Power R5 VBAT Power VBAT

GPIOs/

JTAG

GPIO0/CD1 GPIO0/card detection 1 I/O

JTAG.TDO JTAG test data output I/O

GPIO1/CD2 GPIO1/card detection 2 I/O

JTAG.TMS JTAG test mode state I

GPIO2 GPIO2 I/O

Test1 Test1 pin used in test mode only I/O

GPIO15 GPIO15 I/O

Test2 Test2 pin used in test mode only I/O

GPIO6 GPIO6 I/O

PWM0 Pulse width driver 0 O

Test3 I/O

Test3 pin used in test mode only

(controlled by JTAG)

P12 GPIO0 I PD Floating

N12 GPIO1 I PD Floating

L4 GPIO2 I PD Floating

P13 GPIO15 I PD Floating

M4 GPIO6 I PD Floating

GPIO7 GPIO7 I/O

VIBRA.SYNC Vibrator on-off synchronization I

N14 GPIO7 I PD Floating

START.

ADC

PWM1 Pulse width driver O

Test4 I/O

Test4 pin used in test mode only

(controlled by JTAG)

START.ADC ADC conversion request I J9 START.ADC I GND

Released

(1)

Internal

Pull or Not

(2)

(3)

(3)

(3)

20 Terminal Description Copyright © 2008–2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS65950

TPS65950

www.ti.com

SWCS032E–OCTOBER 2008–REVISED JANUARY 2011

Table 2-2. Signal Description (continued)

Configuration By Default After Reset

Module Description Type

CONTROL

VREF

I2C

SmartReflex

I2C

PCM

TDM

ANA.MIC G2 MIC.SUB.P I Cap to GND

Headset

microphone

Signal Unused

Name Features

SYSEN System enable output OD/I C13 SYSEN OD PU Floating

CLKEN Clock enable O C6 CLKEN O Floating

CLKEN2 Clock enable 2 O D7 CLKEN2 O Floating

CLKREQ Clock request I G10 CLKREQ I PD GND

INT1 Output interrupt line 1 O F10 INT1 O Floating

INT2 Output interrupt line 2 O F9 INT2 O Floating

NRESPWRON O A13 NRESPWRON O Floating

NRESWARM I B13 NRESWARM I GND

PWRON I A11 PWRON I VBAT

NC Not connected B14 NC Floating

NSLEEP1 Sleep request from device 1 I P7 NSLEEP1 I GND

NSLEEP2 Sleep request from device 2 I G9 NSLEEP2 I GND

CLK256FS Control for 256 × FSCLK output O D13 CLK256FS O Floating

VMODE1 I F8 VMODE1 I GND

BOOT0 Boot pin 0 I K11 BOOT0 I PD N/A

BOOT1 Boot pin 1 I J11 BOOT1 I PD N/A

REGEN Enable signal for external LDO OD A10 REGEN OD PU Floating

MSECURE I H8 MSECURE I N/A

VREF Reference voltage Power N16 VREF Power N/A

AGND N15 AGND Power GND GND

NC Not connected

I2C.SR.SDA I/O

VMODE2 I

I2C.SR.SCL I/O

I2C.CNTL.SDA I/O D4 I2C.CNTL.SDA I/O PU N/A

I2C.CNTL.SCL I/O D5 I2C.CNTL.SCL I/O PU N/A

PCM.VCK Data clock (voice port) I/O R1 PCM.VCK I/O Floating

PCM.VDR Data receive (voice port) I/O T2 PCM.VDR I/O GND

PCM.VDX Data transmit (voice port) I/O T15 PCM.VDX I/O Floating

PCM.VFS Frame synchronization (voice port) I/O R16 PCM.VFS I/O Floating