Temperature (qC)

Accuracy (%)

-50 -25 0 25 50 75 100 125

-0.5

-0.3

-0.1

0.1

0.3

0.5

Unit 1

Unit 2

Unit 3

Unit 4

Unit 5

Average

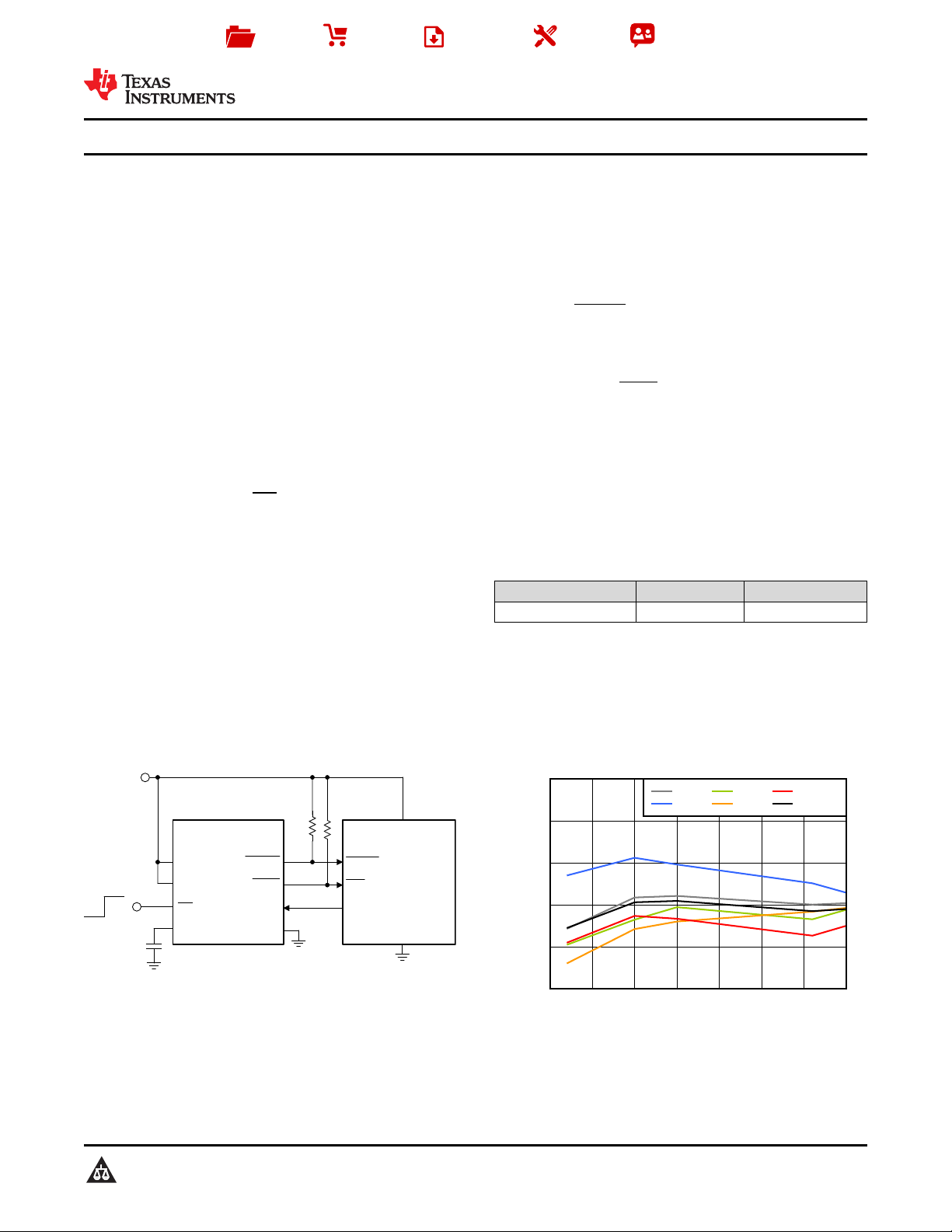

RESET

VDD

GND

TPS3851

1.8 V

Microcontroller

SET1

V

DD

RESET

GND

WDO

NMI

CWD

MR

WDI GPIO

Copyright © 2016, Texas Instruments Incorporated

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

SBVS300 –NOVEMBER 2016

TPS3851 Precision Voltage Supervisor with Integrated Watchdog Timer

TPS3851

1 Features

1

• 0.8% Voltage Threshold Accuracy

• Precision Undervoltage Monitoring:

– Supports Common Rails from 1.8 V to 5.0 V

– 4% and 7% Undervoltage Thresholds

Available

– 0.5% Hysteresis

• Factory-Programmed Precision Watchdog and

Reset Timers:

– ±15% Accurate WDT and RST Delays

• Watchdog Disable Feature

• User-Programmable Watchdog Timeout

• Input Voltage Range: VDD= 1.6 V to 6.5 V

• Low Quiescent Current: IDD= 10 µA (typ)

• Open-Drain Outputs

• Manual Reset Input (MR)

• Available in a Small 3-mm × 3-mm, 8-Pin VSON

Package

• Junction Operating Temperature Range:

–40°C to +125°C

2 Applications

• Safety-Critical Applications

• Telematics Control Units

• FPGAs and ASICs

• Microcontrollers and DSPs

3 Description

The TPS3851 combines a precision voltage

supervisor with a programmable watchdog timer. The

TPS3851 comparator achieves a 0.8% accuracy

(–40°C to +125°C) for the undervoltage (V

threshold. The TPS3851 also includes accurate

hysteresis on the undervoltage threshold making the

device ideal for use with tight tolerance systems. The

supervisor RESET delay features a 15% accuracy,

high-precision delay timing.

The TPS3851 includes a programmable watchdog

timer for a wide variety of applications. The dedicated

watchdog output (WDO) enables increased resolution

to help determine the nature of fault conditions. The

watchdog timeouts can be programmed either by an

external capacitor, or by factory-programmed default

delay settings. The watchdog can be disabled via

logic pins to avoid undesired watchdog timeouts

during the development process.

The TPS3851 is available in a small 3.00-mm ×

3.00-mm, 8-pin VSON package.

Device Information

PART NUMBER PACKAGE BODY SIZE (NOM)

TPS3851 VSON (8) 3.00 mm × 3.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

(1)

ITN

)

Fully Integrated Microcontroller Supervisory

Circuit

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Undervoltage Threshold (V

Temperature

) Accuracy vs

ITN

TPS3851

SBVS300 –NOVEMBER 2016

www.ti.com

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 4

6.1 Absolute Maximum Ratings ...................................... 4

6.2 ESD Ratings.............................................................. 4

6.3 Recommended Operating Conditions....................... 4

6.4 Thermal Information.................................................. 5

6.5 Electrical Characteristics........................................... 5

6.6 Timing Requirements................................................ 6

6.7 Typical Characteristics.............................................. 8

7 Detailed Description............................................ 11

7.1 Overview................................................................. 11

7.2 Functional Block Diagram ....................................... 11

7.3 Device Functional Modes........................................ 14

4 Revision History

DATE REVISION NOTES

November 2016 * Initial release.

8 Application and Implementation ........................ 15

8.1 Application Information............................................ 15

8.2 Typical Application ................................................. 18

9 Power Supply Recommendations...................... 21

10 Layout................................................................... 21

10.1 Layout Guidelines ................................................. 21

10.2 Layout Example .................................................... 21

11 Device and Documentation Support ................. 22

11.1 Device Support .................................................... 22

11.2 Documentation Support ........................................ 22

11.3 Receiving Notification of Documentation Updates 22

11.4 Community Resources.......................................... 22

11.5 Trademarks........................................................... 22

11.6 Electrostatic Discharge Caution............................ 22

11.7 Glossary................................................................ 23

12 Mechanical, Packaging, and Orderable

Information........................................................... 23

2

Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated

Product Folder Links: TPS3851

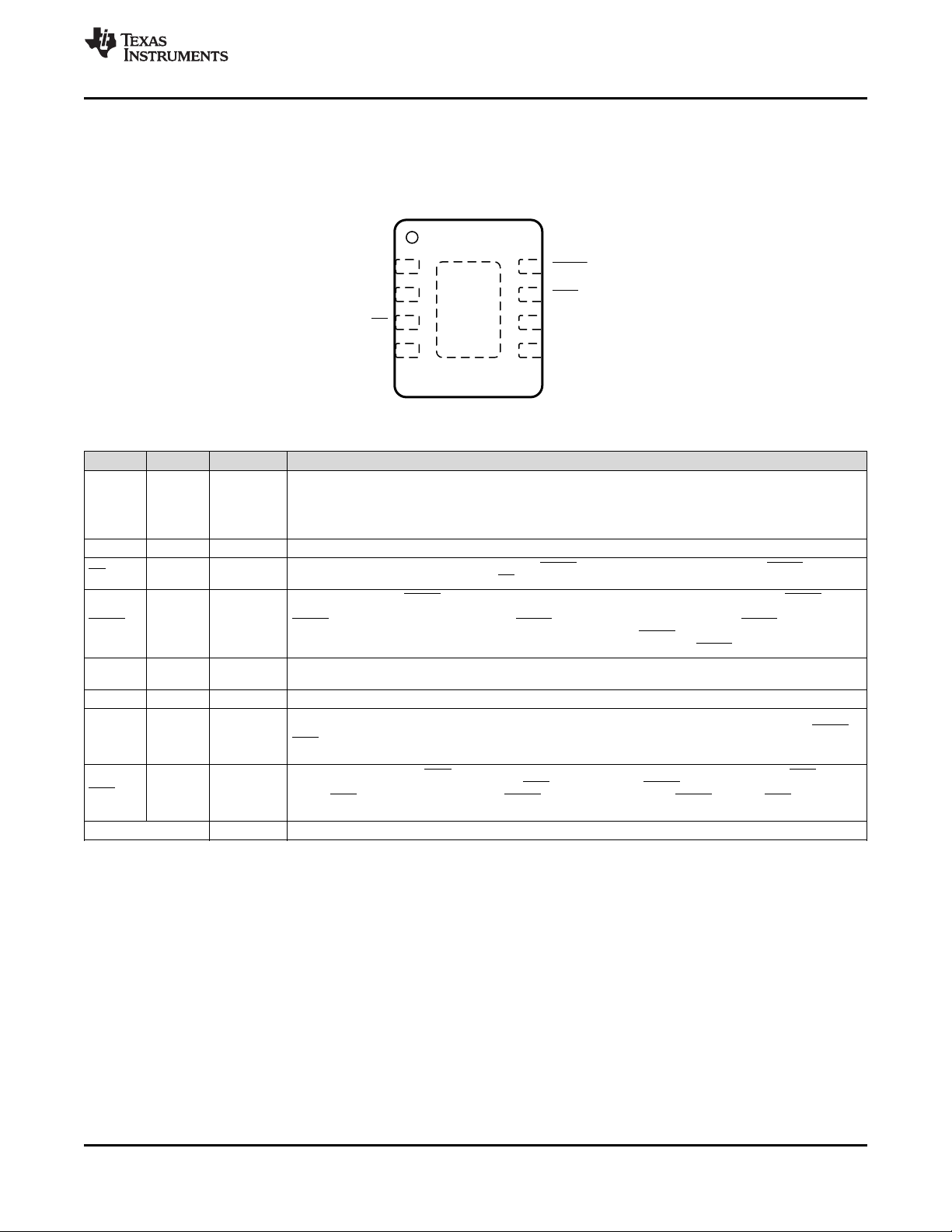

1VDD 8 RESET

2CWD 7 WDO

3MR 6 WDI

4GND 5 SET1

Not to scale

Thermal

Pad

www.ti.com

SBVS300 –NOVEMBER 2016

5 Pin Configuration and Functions

DRB Package: TPS3851

3-mm × 3-mm VSON-8

Top View

Pin Functions

NAME NO. I/O DESCRIPTION

Programmable watchdog timeout input. The watchdog timeout is set by connecting a capacitor between this pin and

CWD 2 I

GND 4 — Ground pin

MR 3 I

RESET 8 O

SET1 5 I

VDD 1 I Supply voltage pin. For noisy systems, connecting a 0.1-μF bypass capacitor is recommended.

WDI 6 I

WDO 7 O

Thermal pad — Connect the thermal pad to a large-area ground plane. The thermal pad is internally connected to GND.

ground. Connecting via a 10-kΩ resistor to VDDor leaving unconnected further enables the selection of the preset

watchdog timeouts; see the CWD Functionality section.

The TPS3851 determines the watchdog timeout using either Equation 1 or Equation 2 with standard or extended

timing, respectively.

Manual reset pin. A logical low on this pin issues a RESET. This pin is internally pulled up to VDD. RESET remains

low for a fixed reset delay (t

Reset output. Connect RESET using a 1-kΩ to 100-kΩ resistor to the correct pullup voltage rail (VPU). RESET goes

low when VDDgoes below the undervoltage threshold (V

RESET timeout-counter starts. At completion, RESET goes high. During startup, the state of RESET is undefined

below the specified power-on-reset (POR) voltage (V

monitored voltage is within the correct operating range (above V

Logic input. Grounding the SET1 pin disables the watchdog timer. SET1 and CWD select the watchdog timeouts; see

the SET1 section.

Watchdog input. A falling edge must occur at WDI before the timeout (tWD) expires.

When the watchdog is not in use, the SET1 pin can be used to disable the watchdog. WDI is ignored when RESET or

WDO are low (asserted) and when the watchdog is disabled. If the watchdog is disabled, WDI cannot be left

unconnected and must be driven to either VDD or GND.

Watchdog output. Connect WDO with a 1-kΩ to 100-kΩ resistor to the correct pullup voltage rail (VPU). WDO goes

low (asserts) when a watchdog timeout occurs. WDO only asserts when RESET is high. When a watchdog timeout

occurs, WDO goes low (asserts) for the set RESET timeout delay (t

impedance state.

) time after MR is deasserted (high).

RST

ITN

). Above POR, RESET goes low and remains low until the

POR

). When VDDis within the normal operating range, the

ITN+VHYST

) and the RESET timeout is complete.

). When RESET goes low, WDO is in a high-

RST

TPS3851

Product Folder Links: TPS3851

Submit Documentation FeedbackCopyright © 2016, Texas Instruments Incorporated

3

TPS3851

SBVS300 –NOVEMBER 2016

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

Supply voltage range VDD –0.3 7 V

Output voltage range RESET, WDO –0.3 7 V

Voltage ranges

Output pin current RESET, WDO ±20 mA

Input current (all pins) ±20 mA

Continuous total power dissipation See Thermal Information

Temperature

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The absolute maximum rating is VDD+ 0.3 V or 7.0 V, whichever is smaller.

(3) Assume that TJ= TAas a result of the low dissipated power in this device.

SET1, WDI, MR –0.3 7

CWD –0.3 VDD+ 0.3

Operating junction, T

Storage, T

stg

(1)

MIN MAX UNIT

(2)

(3)

J

(3)

A

–40 150

–40 150

V

°COperating free-air, T

–65 150

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001

Charged-device model (CDM), per JEDEC specification JESD22-C101

(1)

±1000

(2)

±500

V

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with

less than 500-V HBM is possible with the necessary precautions.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with

less than 250-V CDM is possible with the necessary precautions.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN TYP MAX UNIT

V

DD

V

SET1

C

CWD

CWD Pullup resistor to VDD 9 10 11 kΩ

R

PU

I

RESET

I

WDO

T

J

(1) Using standard timing with a C

(2) Using extended timing with a C

Supply pin voltage 1.6 6.5 V

SET1 pin voltage 0 6.5 V

Watchdog timing capacitor 0.1

(1)(2)

1000

(1)(2)

nF

Pullup resistor, RESET and WDO 1 10 100 kΩ

RESET pin current 10 mA

Watchdog output current 10 mA

Junction temperature –40 125 °C

capacitor of 0.1 nF or 1000 nF gives a t

CWD

capacitor of 0.1 nF or 1000 nF gives a t

CWD

of 0.704 ms or 3.23 seconds, respectively.

WD(typ)

of 62.74 ms or 77.45 seconds, respectively.

WD(typ)

4

Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated

Product Folder Links: TPS3851

www.ti.com

SBVS300 –NOVEMBER 2016

6.4 Thermal Information

TPS3851

THERMAL METRIC

(1)

8 PINS

R

θJA

R

θJC(top)

R

θJB

ψ

JT

ψ

JB

R

θJC(bot)

Junction-to-ambient thermal resistance 50.7 °C/W

Junction-to-case (top) thermal resistance 51.6 °C/W

Junction-to-board thermal resistance 25.8 °C/W

Junction-to-top characterization parameter 1.3 °C/W

Junction-to-board characterization parameter 25.8 °C/W

Junction-to-case (bottom) thermal resistance 7.1 °C/W

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report.

6.5 Electrical Characteristics

at V

+ V

ITN

open-drain pullup resistors are 10 kΩ for each output; typical values are at TJ= 25°C

GENERAL CHARACTERISTICS

(1)(2) (3)

V

DD

I

DD

RESET FUNCTION

(2)

V

POR

(1)

V

UVLO

V

ITN

V

HYST

I

MR

WATCHDOG FUNCTION

I

CWD

V

CWD

V

OL

I

D

V

IL

V

IH

V

IL(WDI)

V

IH(WDI)

(1) When VDDfalls below V

(2) When VDDfalls below V

(3) During power-on, VDDmust be a minimum 1.6 V for at least 300 µs before RESET correlates with VDD.

≤ VDD≤ 6.5 V over the operating temperature range of –40°C ≤ TA, TJ≤ 125°C (unless otherwise noted); the

HYST

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Supply voltage 1.6 6.5 V

Supply current 10 19 µA

Power-on reset voltage I

RESET

= 15 µA, V

= 0.25 V 0.8 V

OL(MAX)

Undervoltage lockout voltage 1.35 V

Undervoltage threshold accuracy,

entering RESET

VDDfalling V

– 0.8% V

ITN

ITN

+ 0.8%

Hysteresis voltage VDDrising 0.2% 0.5% 0.8%

MR pin internal pullup current VMR= 0 V 500 620 700 nA

CWD pin charge current CWD = 0.5 V 337 375 413 nA

CWD pin threshold voltage 1.192 1.21 1.228 V

RESET, WDO output low VDD = 5 V, I

RESET, WDO output leakage current,

open-drain

VDD = V

V

RESET

= V

= 3 mA 0.4 V

SINK

+ V

WDO

,

HYST

= 6.5 V

ITN

Low-level input voltage (MR, SET1) 0.25 V

High-level input voltage (MR, SET1) 0.8 V

Low-level input voltage (WDI) 0.3 × V

High-level input voltage (WDI) 0.8 × V

, RESET is driven low.

UVLO

, RESET and WDO are undefined.

POR

DD

TPS3851

UNITDRB (VSON)

1 µA

DD

V

V

Product Folder Links: TPS3851

Submit Documentation FeedbackCopyright © 2016, Texas Instruments Incorporated

5

VDD

RESET

WDI

WDO

t

RST

t

RST

t

RST

V

POR

V

ITN

t < t

WD

t = t

WD

(1)

X

V

ITN

+ V

HYST

V

ITN

X

t

RST-DEL

t < t

WD

TPS3851

SBVS300 –NOVEMBER 2016

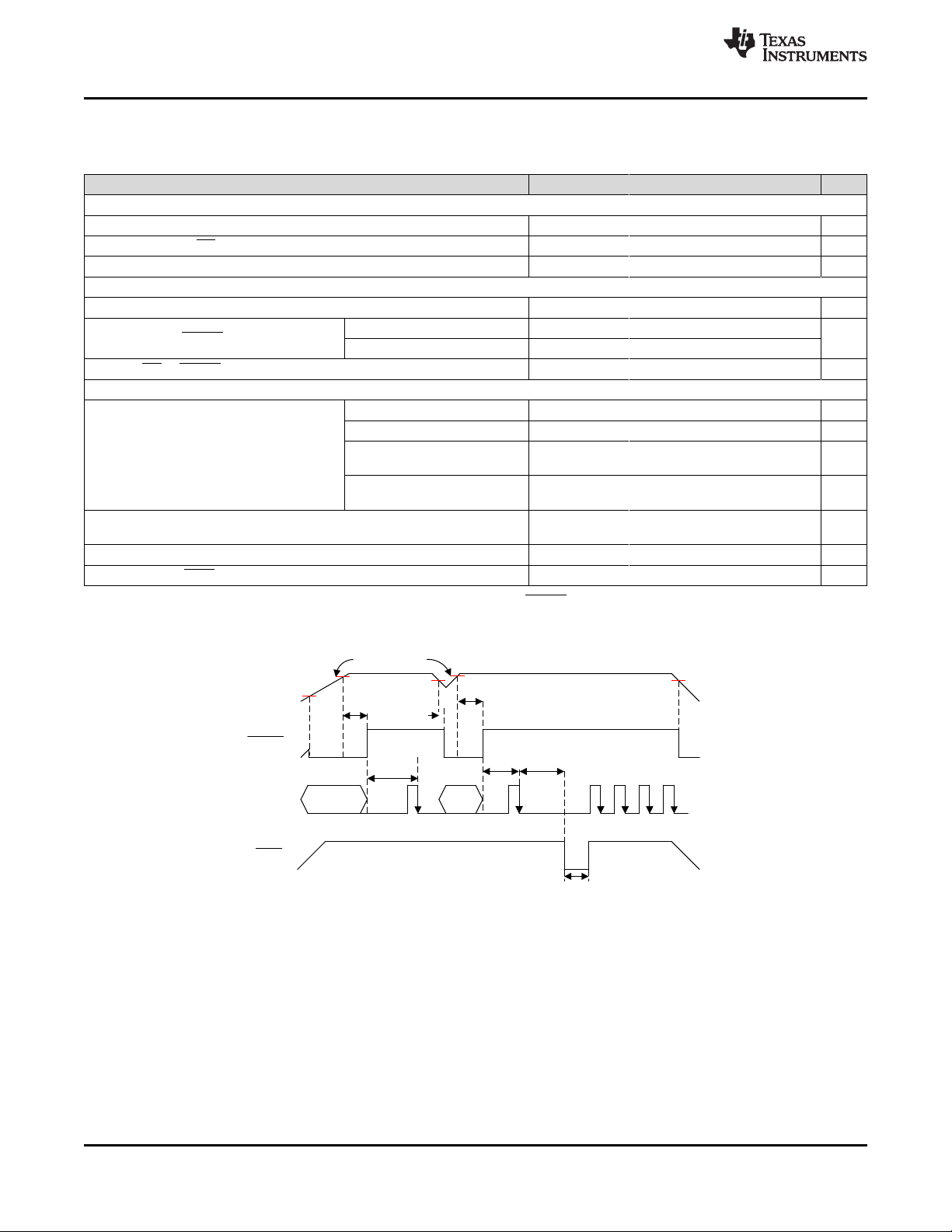

6.6 Timing Requirements

at V

+ V

ITN

open-drain pullup resistors are 10 kΩ for each output; typical values are at TJ= 25°C

GENERAL

t

INIT

RESET FUNCTION

t

RST

t

RST-DELVDD

t

MR-DEL

WATCHDOG FUNCTION

t

WD

t

WD-

setup

t

WD-del

(1) During power-on, VDDmust be a minimum 1.6 V for at least 300 µs before RESET correlates with VDD.

(2) The fixed watchdog timing covers both standard and extended versions.

(3) SET1 = 0 means V

≤ VDD≤ 6.5 V over the operating temperature range of –40°C ≤ TA, TJ≤ 125°C (unless otherwise noted); the

HYST

MIN NOM MAX UNIT

CWD pin evaluation period 381 µs

Minimum MR, SET1 pin pulse duration 1 µs

Startup delay

(1)

Reset timeout period 170 200 230 ms

to RESET delay

VDD= V

VDD= V

+ V

ITN

– 2.5% 17

ITN

+ 2.5% 35

HYST

MR to RESET delay 200 ns

(3)

(3)

Watchdog disabled

1360 1600 1840 ms

Watchdog disabled

170 200 230 ms

Watchdog timeout

CWD = NC, SET1 = 0

CWD = NC, SET1 = 1

(2)

CWD = 10 kΩ to VDD,

SET1 = 0

CWD = 10 kΩ to VDD,

SET1 = 1

(3)

(3)

Setup time required for device to respond to changes on WDI after

being enabled

Minimum WDI pulse duration 50 ns

WDI to WDO delay 50 ns

< VIL; SET1 = 1 means V

SET1

SET1

> VIH.

www.ti.com

300 µs

µs

150 µs

(1) See Figure 2 for WDI timing requirements.

Figure 1. Timing Diagram

6

Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated

Product Folder Links: TPS3851

Timing

WDI

t

WD(MIN)

t

WD(TYP)

t

WD(MAX)

WDO

= Tolerance Window

Correct

Operation

WDO

Late Fault

WDI

Valid

Region

www.ti.com

TPS3851

SBVS300 –NOVEMBER 2016

Figure 2. Watchdog Timing Diagram

Product Folder Links: TPS3851

Submit Documentation FeedbackCopyright © 2016, Texas Instruments Incorporated

7

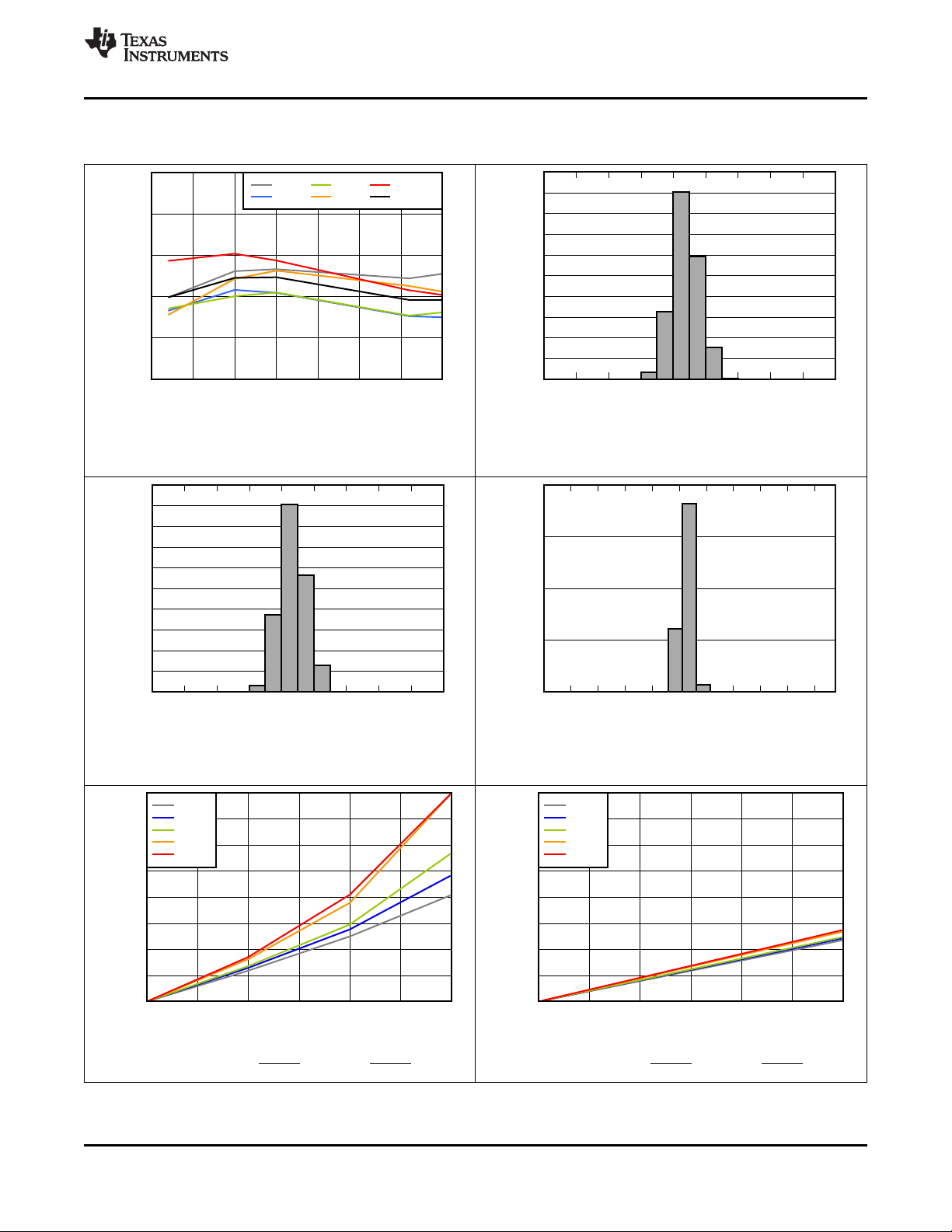

Temperature (qC)

Accuracy (%)

-50 -25 0 25 50 75 100 125

-0.5

-0.3

-0.1

0.1

0.3

0.5

Unit 1

Unit 2

Unit 3

Unit 4

Unit 5

Average

Temperature (qC)

Accuracy (%)

-50 -25 0 25 50 75 100 125

-0.5

-0.3

-0.1

0.1

0.3

0.5

Unit 1

Unit 2

Unit 3

Unit 4

Unit 5

Average

Temperature (qC)

CWD Charging Current (nA)

-50 -25 0 25 50 75 100 125

364

368

372

376

380

1.6 V

6.5 V

Temperature (qC)

Accuracy (%)

-50 -25 0 25 50 75 100 125

-0.5

-0.3

-0.1

0.1

0.3

0.5

Unit 1

Unit 2

Unit 3

Unit 4

Unit 5

Average

VDD (V)

Supply Current (PA)

0 1 2 3 4 5 6 7

0

4

8

12

16

-40qC

0qC

25qC

105qC

125qC

Temperature (qC)

Manual Reset Threshold (V)

-50 -25 0 25 50 75 100 125

0.3

0.4

0.5

0.6

0.7

V

IL

V

IH

TPS3851

SBVS300 –NOVEMBER 2016

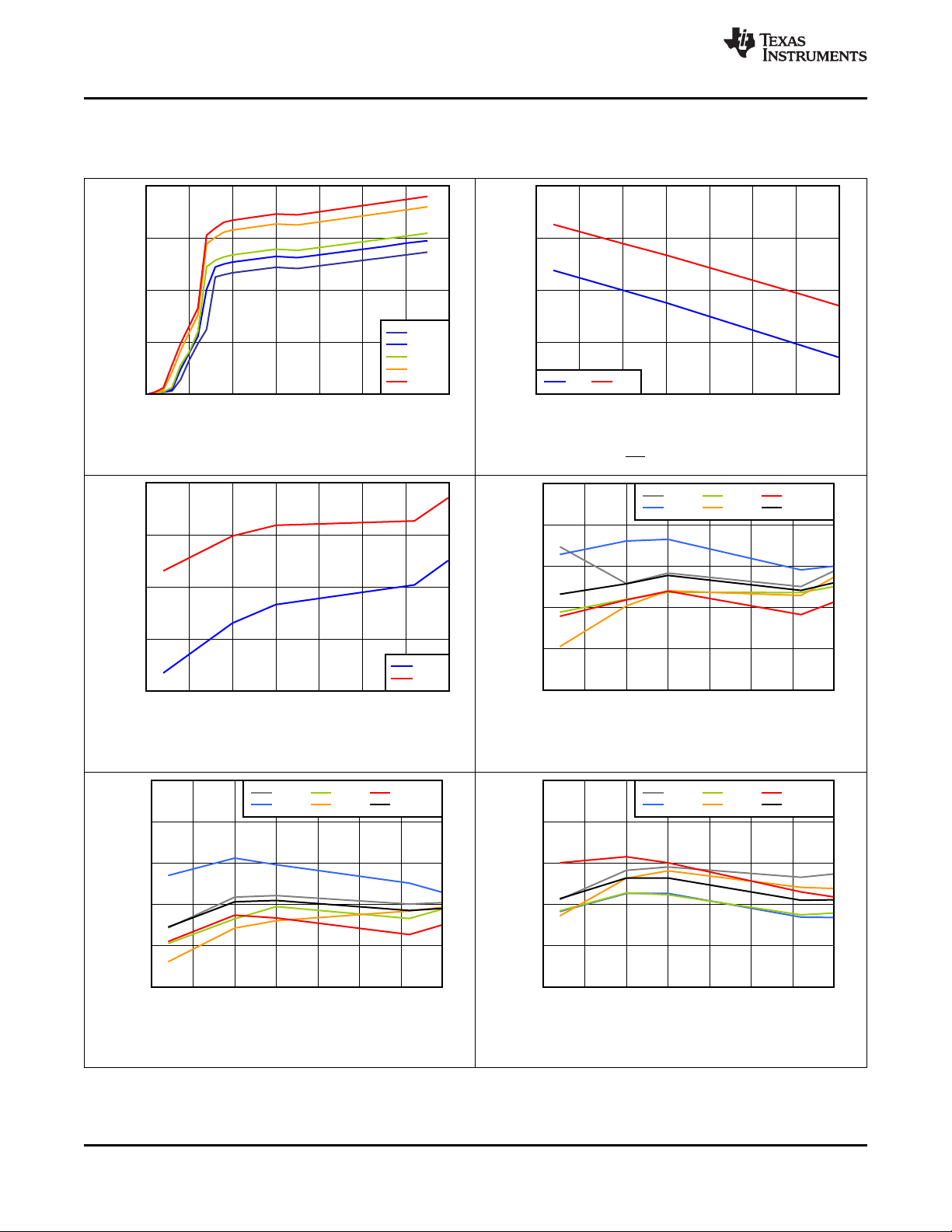

6.7 Typical Characteristics

all typical characteristics curves are taken at 25°C with 1.6 V ≤ VDD ≤ 6.5 V (unless other wise noted)

VDD = 1.6 V

www.ti.com

Figure 3. Supply Current vs V

DD

Figure 5. CWD Charging Current vs Temperature

Figure 4. MR Threshold vs Temperature

TPS3851G18, V

Figure 6. V

ITN

+ V

HYST

= 1.728 V

ITN

Accuracy vs Temperature

8

Figure 7. V

TPS3851G18, V

Accuracy vs Temperature

ITN

ITN

Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated

= 1.728 V

Figure 8. V

Product Folder Links: TPS3851

TPS3851G50, V

+ V

ITN

Accuracy vs Temperature

HYST

ITN

= 4.8 V

I

RESET

(mA)

V

OL

(V)

0 1 2 3 4 5 6

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

-40qC

0qC

25qC

105qC

125qC

I

RESET

(mA)

V

OL

(V)

0 1 2 3 4 5 6

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

-40qC

0qC

25qC

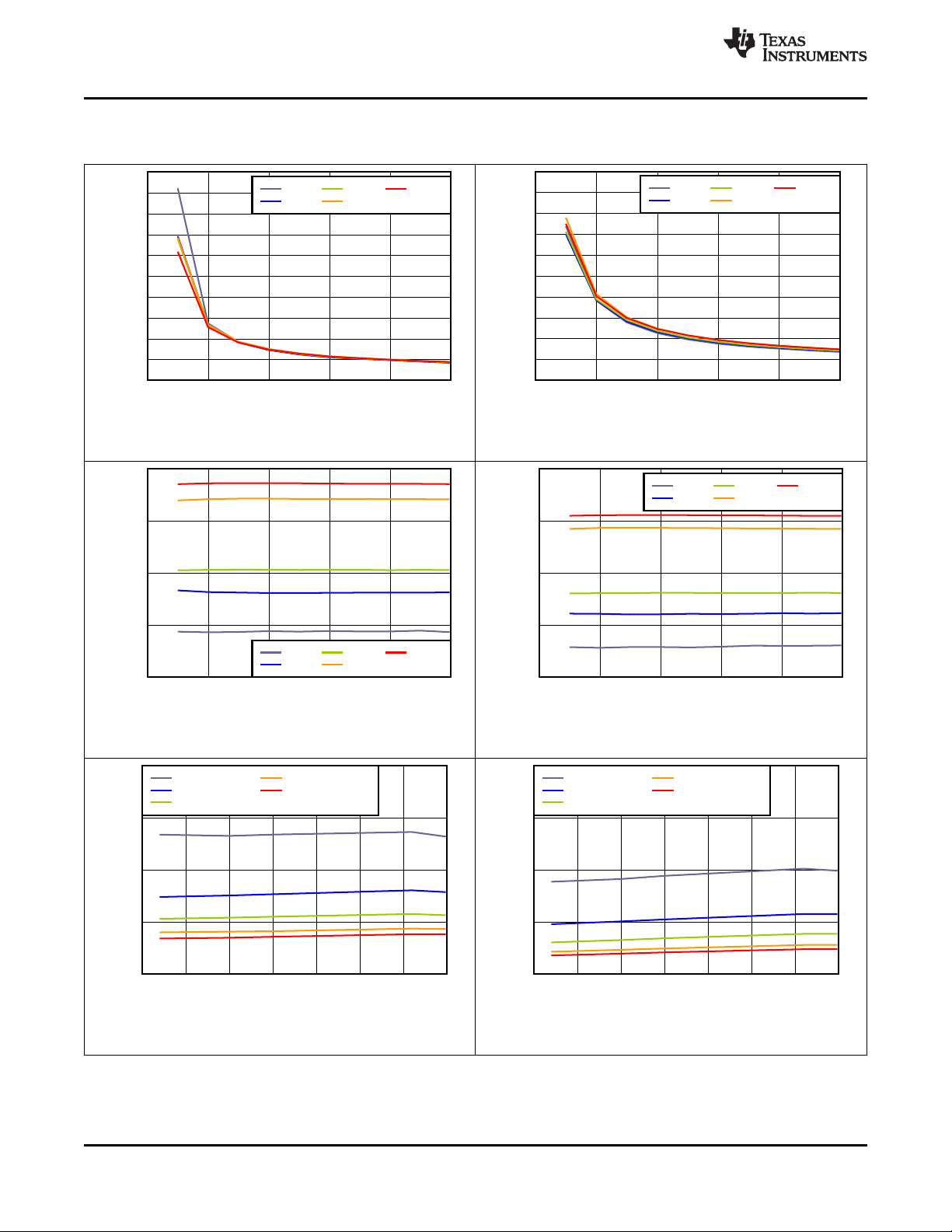

105qC

125qC

V

ITN

Accuracy (%)

Frequency (%)

0

5

10

15

20

25

30

35

40

45

50

-0.8 -0.6 -0.4 -0.2 0 0.2 0.4 0.6 0.8

Hysteresis (%)

Frequency (%)

0

20

40

60

80

0.2 0.35 0.5 0.8

Temperature (qC)

Accuracy (%)

-50 -25 0 25 50 75 100 125

-0.5

-0.3

-0.1

0.1

0.3

0.5

Unit 1

Unit 2

Unit 3

Unit 4

Unit 5

Average

V

ITN

+ V

HYST

Accuracy (%)

Frequency (%)

0

5

10

15

20

25

30

35

40

45

50

-0.8 -0.6 -0.4 -0.2 0 0.2 0.4 0.6 0.8

www.ti.com

Typical Characteristics (continued)

all typical characteristics curves are taken at 25°C with 1.6 V ≤ VDD ≤ 6.5 V (unless other wise noted)

TPS3851

SBVS300 –NOVEMBER 2016

TPS3851G50, V

Figure 9. V

Accuracy vs Temperature

ITN

ITN

= 4.8 V

Includes G and H versions; 1.8-V, 2.5-V, 3.0-V, 3.3-V, and 5-V

thresholds; total units = 36,627

Figure 11. V

Accuracy Histogram

ITN

Includes G and H versions; 1.8-V, 2.5-V, 3.0-V, 3.3-V, and 5-V

thresholds; total units = 36,627

Figure 10. V

ITN

+ V

Accuracy Histogram

HYST

Includes G and H versions; 1.8-V, 2.5-V, 3.0-V, 3.3-V, and 5-V

thresholds; total units = 36,627

Figure 12. Hysteresis Histogram

VDD = 1.6 V

Figure 13. Low-Level RESET Voltage vs RESET Current

Figure 14. Low-Level RESET Voltage vs RESET Current

Product Folder Links: TPS3851

VDD = 6.5 V

Submit Documentation FeedbackCopyright © 2016, Texas Instruments Incorporated

9

Temperature (qC)

Glitch Immunity (Ps)

-50 -25 0 25 50 75 100 125

5

10

15

20

25

Overdrive = 3%

Overdrive = 5%

Overdrive = 7%

Overdrive = 9%

Overdrive = 10%

Temperature (qC)

Glitch Immunity (Ps)

-50 -25 0 25 50 75 100 125

5

10

15

20

25

Overdrive = 3%

Overdrive = 5%

Overdrive = 7%

Overdrive = 9%

Overdrive = 10%

Overdrive (%)

Propagation Delay (ms)

0 2 4 6 8 10

190

195

200

205

210

-40qC

0qC

25qC

105qC

125qC

Overdrive (%)

Propagation Delay (ms)

0 2 4 6 8 10

190

195

200

205

210

-40qC

0qC

25qC

105qC

125qC

Overdrive (%)

Propagation Delay (Ps)

0 2 4 6 8 10

0

10

20

30

40

50

60

70

80

90

100

-40qC

0qC

25qC

105qC

125qC

Overdrive (%)

Propagation Delay (Ps)

0 2 4 6 8 10

0

5

10

15

20

25

30

35

40

45

50

-40qC

0qC

25qC

105qC

125qC

TPS3851

SBVS300 –NOVEMBER 2016

Typical Characteristics (continued)

all typical characteristics curves are taken at 25°C with 1.6 V ≤ VDD ≤ 6.5 V (unless other wise noted)

www.ti.com

TPS3851G18 entering undervoltage

Figure 15. Propagation Delay vs Overdrive

TPS3851G18 exiting undervoltage

Figure 17. Propagation Delay (t

) vs Overdrive

RST

TPS3851G50 entering undervoltage

Figure 16. Propagation Delay vs Overdrive

TPS3851G50 exiting undervoltage

Figure 18. Propagation Delay (t

) vs Overdrive

RST

V

ITN

= 1.728 V

Figure 19. High-to-Low Glitch Immunity vs Temperature

10

Submit Documentation Feedback Copyright © 2016, Texas Instruments Incorporated

Figure 20. High-to-Low Glitch Immunity vs Temperature

Product Folder Links: TPS3851

V

ITN

= 4.8 V

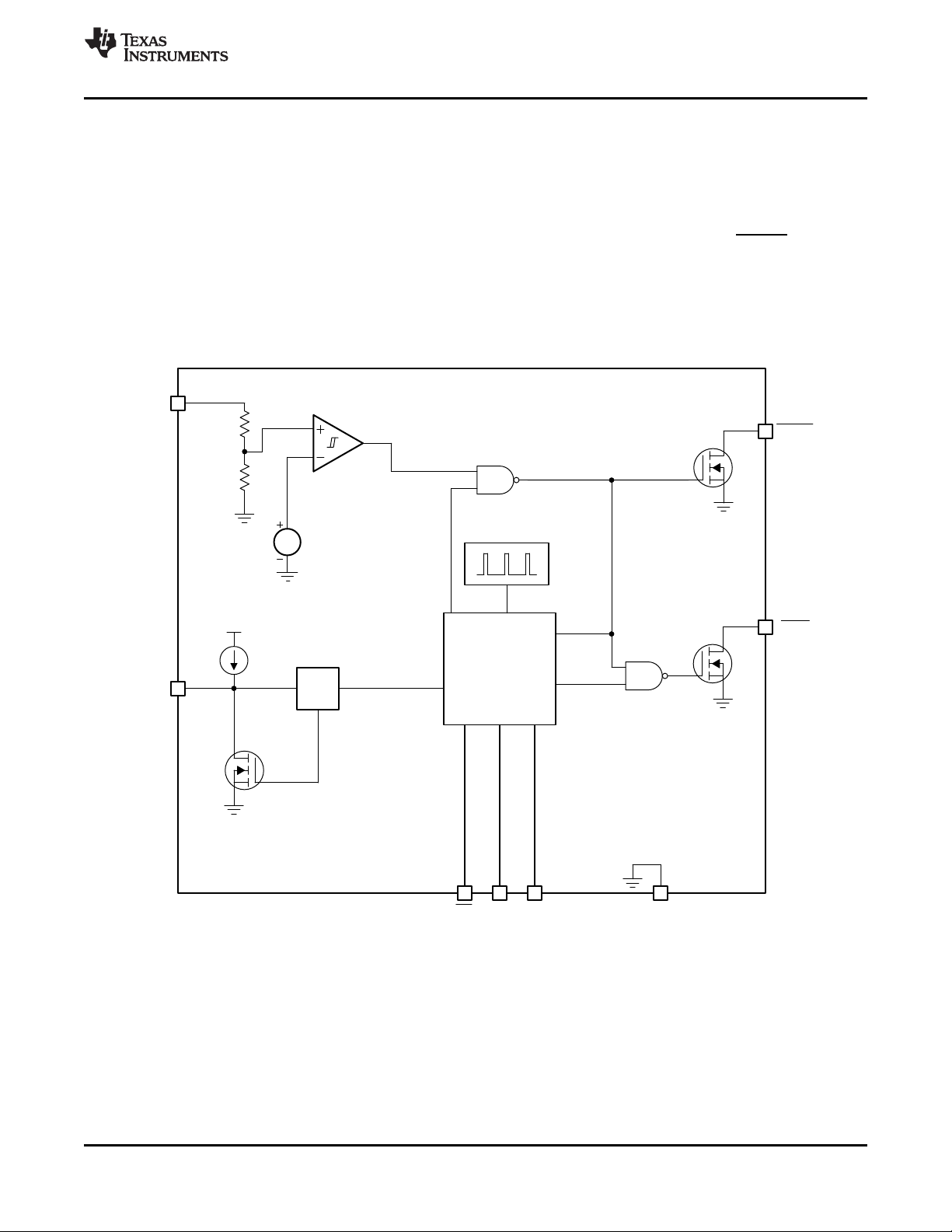

VDD

Precision

Clock

State

Machine

Cap

Control

CWD

GND

VDD

WDI

MR SET1

WDO

RESET

Reference

R

1

R

2

TPS3851

www.ti.com

SBVS300 –NOVEMBER 2016

7 Detailed Description

7.1 Overview

The TPS3851 is a high-accuracy voltage supervisor with an integrated watchdog timer. This device includes a

precision undervoltage supervisor with a threshold that achieves 0.8% accuracy over the specified temperature

range of –40°C to +125°C. In addition, the TPS3851 includes accurate hysteresis on the threshold, making the

device ideal for use with tight tolerance systems where voltage supervisors must ensure a RESET before the

minimum supply tolerance of the microprocessor or system-on-a-chip (SoC) is reached. There are two options

for the watchdog timing standard and extended timing. To get standard timing use the TPS3851Xyy(y)S, for

extended timing use the TPS3851Xyy(y)E.

7.2 Functional Block Diagram

(1) Note: R1+ R2= 4.5 MΩ.

Product Folder Links: TPS3851

Submit Documentation FeedbackCopyright © 2016, Texas Instruments Incorporated

11

Loading...

Loading...