SPRU011

~

~

~

Family

Developtnent

Support

Reference

S320

.

Guide

."

TEXAS

INSTRUMENTS

TMS320 Fatnily

Developtnent

Support

Reference

Guide

TEXAS

•

INSI:'RUMENTS

IMPORTANT

Texas

Instruments (TI)

reserves

the right

device specifications identified in this publication

its customers to obtain the latest version

NOTICE

to

make

changes in the devices or the

without

of

device specifications

notice. TI advises

to

verify,

before placing orders, that the information being relied upon by the customer

is

current.

In the absence

of

written agreement

to

the contrary,

TI

assumes no liability for

TI applications assistance, customer's product design, or infringement

ents or copyrights

devices described herein. Nor does

either express or

intellectual property right

chine, or process in which such semiconductor devices might

of

third parties by or arising from use

TI warrant or represent that any license,

implied,

Copyright © 1986, Texas Instruments Incorporated

is

granted under any patent right, copyright, or other

of

TI

covering or relating

to

any combination, ma-

of

semiconductor

be

or are used.

of

pat-

Quick

Reference

for

This

Document

TITLE

Introduction

The

TMS320

ROM Codes

Quality and Reliability

TMS320

Software Support Products

Hardware Development Tools

RTCTMS320

TMS320

TMS320

TMS320

Digital Signal Processor Family

Development Support Products

Seminar and Workshops

Documentation Support

University Program

Third-Party Support

TITLE

SECTION

1

2

3

4

5

6

7

8

9

10

11

APPENDIX

TMS320

TI Factory Repair and Exchange Policy

TI Program License Agreement

Product Order Information

A

B

C

v

vi

Contents

Section

1

Introduction

1.1

How

to

Use

This Manual

2

The

TMS320

2.1

First-Generation Devices

2.2 Second-Generation Devices

Typical Applications

2.3

3

ROM

Codes

4

Quality

4.1

Reliability Stress Tests

5

TMS320

6

Software

6.1

TMS320 Macro Assembler/Linker

TMS320 Simulator

6.2

6.3 SoftWare

Digital Filter Design Package (DFDP)

6.4

Digital Signal Processing Software Library

6.5

TMS320 Bell 212A Modem Software

6.6

Digital

and

Reliability

Development

Support

Development System (SWDS)

Signal

Support

Products

......

Processor

Products

.

Family

Page

1-1

1-3

2-1

2-4

2-9

2-12

3-1

4-1

4-2

5-1

6-1

6-2

6-5

6-7

6-10

6-13

6-15

7

Hardware

7.1

TMS320 Evaluation Module (EVM)

7.1

.1

System Configuration

7.1.2 Communication

7.1.3 Debugging

7.1.4 Equipment List

TMS320 Emulator (XDS)

7.2

7.2.1

7.2.2 Communication

7.2.3 Debugging

7.2.4 Equipment List

7.3

7.3.1

7.3.2 Customer Upgrade

7.4

7.4.1

7.4.2 Equipment List

7.5

System Configurations

TMS320 XDS Upgrade Program

TI

TMS320 Analog Interface Board

System Configuration

TMS320 DSP Design Kit

Development

.....

.....

Factory Upgrade

Tools

.

(AlB)

7-1

7-2

7-5

7-6

7-7

7-8

7-9

7-13

7-15

7-15

7-16

7-17

7-19

7-20

7-21

7-22

7-23

7-25

vii

8 RTC

8.1

8.2

8.3

TMS320

TMS320 Product Seminar

DSP

Design Workshops

RTC

locations . . . . .

Seminar

and

Workshops

8-1

./.

8-2

8-3

8-4

9TMS320

9.1

Produtt Descriptions and Product Bulletins

9.2 User's Guides

9.3

Data

9.4

DSP

9.4.1

9.4.2

9.4.3 Companding Routines for the

9.4.4 Floating-Point Arithmetic

9.4.5

Documentation

Support

...............

Sheets

Applications Book

Implementation

Fast

Fourier Transform Algorithms with the TMS32020 9-7

................

of

............

FIR/IIR Filters with the TMS32010/TMS32020

..........

TMS3201 0/TMS32020

with

the TMS3201 0 9-7

Floating-Point Arithmetic with the TMS32020

9-1

9-2

9-3

9-4

9-5

9-6

9-7

9-7

9.4.6 Precision Digital Sine-Wave Generation with the TMS3201 0 9-S

9.4.7 Matrix Multiplication with the TMS3201 0

9.4.8 Interfacing to Asynchronous Inputs with the TMS3201 0

9.4.9 Interfacing External Memory to the TMS3201 0

9.4.10 Hardware Interfacing to the TMS32020

9.4.11 TMS32020 and MC6S000 Interface

9.4.12 Telecommunications Interfacing to the TMS3201 0

9.4.13 Digital Voice

9.4.14 Implementation

Echo

Canceller with a TMS32020

of

Data

Encryption Standard Using TMS3201 0 9-

9.4.15 32-kbit/s ADPCM with the TMS3201 0

9.4.16 A Graphics

9.4.17

Control

9.5 University Textbooks

9.5.1

9.5.2

9.5.3

DFT/FFT and Convolution Algorithms 9-13

Digital Filter Design

Practical Approaches to Speech Coding

Implementation Using the TMS32020 lind TMS34061 9-11

System

Compensation

and

...........

..........

9.5.4 A Practical Guide to Adaptive Filter Design

9.5.5 A

9.6 Technical Articles

9.7

9.S

9.8.1

9.9 TMS320

Digital Signal Processing laboratory Using the TMS3201 0 9-

......................

TMS320 Quarterly Newsletter

TMS320

DSP

Bulletin Board Service

How to Access the TMS320

DSP

Hotline

............

...............

DSP

Bulletin Board Service

and

TMS32020

9-8

9-8

9-9

9-9

......

9-9

9-

.......

............

9~

9-11

Implementation with TMS3201 0 9-12

9" 13

9-14

9-14

....

9-14

9-16

9-23

............

9-24

9-24

'.

. . . . . . . 9-27

10

10

10

15

10

TMS320

10.1

TMS320' Hardware/Software Available to Universities

10.2

DSP

11

TMS320

11.1

Allen Ashley

11.2

Atlanta Signal Processors, Inc. (ASPI)

Avocet

11.3

11.4

Bedford

Burr Brown Corp.

11.5

11.6

Computalker

11.7

Crowell, Inc.

Cybernetic Micro

11.8

11.9

Daisy Systems Corp.

University

Program

Station Recommendations . . . . . .

Third-Party

.........

Systems,

Support

.

Inc.

Research

. . . .

Systems

viii

10-1

10-2

10-2

11-1

11-2

11-3

11-5

11-5

11-6

11-S

11-9

11-10

11-10

11

.10 Dalanco Spry

11.11 Digital Audio Corp. .

11.12 Digital

11.13 Digital Sound Corp.

11.14

DSP Technology Corp.

11

.15 Forth, Inc.

11.16

Gas

11.17 Hewlett-Packard

11

.18 Hyperception

11.19 Kontron Electronics

11.20 Loughborough Sound Images Ltd.

11.21 Microcraft Corp.

11.22 Microstuf,

11.23

PH

11.24 Pacific Microcircuits Ltd.

11.25 Pratica

11.26

Racal

11.27 Sentry Test

11.28 Signal Technology, Inc. (STI)

11.29 Signix Corp.

11.30 SIGnology, Inc. •

11.31

SKY Computers, Inc.

11.32 TelePhoto Communications

11.33 Televic

11.34

Texas

11.35 Thorn EMI Electronics

11.36

TIAC Manufacturing, Inc.

11.37 Valid Logic Systems

11

;38 Votan

11

.39 Whitman Engineering, Inc.

11.40 Third-Party Address, Phone, and Product Support List

11.41 Third-Party Consultants

11

.42 Trademarks

Signal Processing Software, Inc. (DSPS)

Light Software

Associates

SRL

Microelectronics Systems Ltd.

........

Instruments, Inc.

........

..............

Inc.

....

....

..........

Systems

......

.....................

.....

...

..........

.

.

.

.

.

.

............

.

.

.

.

11-11

11-12

11-12

11-13

11-14

11-15

11-15

11-16

11-18

11-19

11-19

11-20

11-21

11-21

11-22

11-25

11-25

.

11-26

11-26

11-27

11-28

11-29

11-33

11-34

11-35

11-36

11-37

11-38

11-38

.

.

11-39

11-41

11-47

11-49

A

B

C

Product

Texas

Texas

Instruments

Instruments

Order

Information

Factory

Program

Repair

License

and

Exchange

Agreement

Policy

A-1

8-1

C-1

ix

III

ustrations

Figure Page

1-1. TMS320 Family Development Support . . . . . . . . . . . . . . . . . . . . . . . . .

2-1. The TMS320 Family Roadmap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-2. TMS32010, TMS3201 0-14, TMS3201 0-25, TMS320C1 0, TMS320C1

2-3. TMS320C15/E15, TMS320C15-25 Block Diagram

2-4. TMS32011 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-5. TMS320C17 /E17, TMS320C17 -25 Block Diagram . . . . . . . . . . . . . . .

2-6. TMS32020 Block Diagram . . . . . . . . . . . . . . . . . . . . .

2-7.

3-1.

5-1. TMS320 Development Product Integration . . . . . . . . . . . . . . . . . . . . .

5-2. Typical TMS320 Application Development Flow . . . . . . . . . . . . . . . . .

6-1.

6-2. Linked Assembly

6-3. Simulator Screen Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6-4. SoftWare Development System (SWDS)

6-5. SWDS Screen Example .

6-6. Digital Filter Design Package (DFDP) . . . . . . . . . . . . . . . . . . . . . . . . .

6-7. DFDP Plot Examples

7-L

7-2. TMS32020/C25 Evaluation Module (EVM) . . . . . . . . . . . . . . . . . . . . .

7-3. TMS320

7-4. TMS320 EVM/Single-User System . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-5. TMS32010

7 -6. TMS320C10 Emulator (XDS/22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7-7. TMS320C25 Emulator (XDS/22) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 -8.

7-9.

7-10. TMS320 XDS/Single-User System

7-11

7-12. TMS320C10 XDS/22 Display Example

7 -13. XDS Upgrade Configurations . . . . . . . . . . . . . . . . . .

7-14.

7-15.

7 -16.

7-17.

11-1.

11-2. Burr Brown's VMEdsp

11-3. Burr Brown's VMEdsp MPV960 Analog Input

11-4. Dalanco Spry's Model 1 0 Digital Signal Processor . . . . . . . . . . . . . . . .

11-5. HP

11-6. Pacific Microcircuits' PD32HC01 Interface IC . . . . . . . . . . . . . . . . . . .

11-7. Pacific Microcircuits' SuPPort 320

11-8. SIGnology's SP-20 DSP Development/Measurement System . . . . . . .

11-9. SKY320-PC

11-10.SKY320-Q

11-11. SKY Challenger VMEbus DSP Board . . . . . . . . . . . . . . . . . . . . . . . . . .

'1-12.

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TMS320C25 Block Diagram

TMS320 ROM Code Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Assembly

TMS32010 Evaluation Module (EVM)

TMS320C25 Emulator Target Connector . . . . . . . . . . . . . . . . . . . . . . .

TMS320 XDS Host Computer Mode

..

TMS320 XDS Multiprocessor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . .

TMS320 Analog Interface Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TMS320

TMS320 AI B Adaptor Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TMS320

ASPI's Algorithm Development Package (ADP) . . . . . . . . . . . . . . . . . .

TI-Speech Development System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

with

a Single-Source Module . . . . . . . . . . . . . . . . . . . . . . . .

with

Multiple-Source Modules . . . . . . . . . . . . . . . . .

.........................................

EVM

Host Computer Mode .

EVM

with

Audio Cassette Interface . . . . . . . . . . . . . . . . . .

AlB

System Configuration

DSP

Design Kit

SPV1

64285S Emulation Subsystem . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSP

Board . . . . . . . . . . . . . . . . . . . . . . .

DSP

Board

...................................

.......................................

.....................................

00

Board . . . . . . . . . . . . . . . . . . . . . . . . .

DB01

.......................................

.......................

...........................

..

. . . . . . . . . . . . . . . . . . . . . . .

............................

..............................

...........................

.............................

and

Development Board . . . . . . .

...............

...

. . . . . . . . . . .

..

. . . . . . . . . . . .

DSP

Board . . . . . .

..

. . . . . . . . . . .

0-25

..

..

..

"

..

..

..

..

..

..

..

..

..

"

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

..

1-2

2-2.

2-6

2-6

2-8

2-8

2-11

2-11

3-2

5-2

5-3

6-3

6-4

6-6

6-8

6-9

6-10

6-12

7-3

7-4

7-5

7-5

7-6

7 -10

7-11

7 -12

7-13

7-14

7-14

7-15

7 -18

7-21

7-22

7 -'23

7-26

11-4

11-7

11-8

11-11

11-17

11-23

11-24

11-29

11-31

11-32

11-33

11-36

x

A-1. TMS320 Device Nomenclature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A-2. TMS320 Development Tool Nomenclature . . . . . . . . . . . . . . . . . . . . . .

Tables

..

..

A-5

A-6

Table

2-1.

TMS320 Family Overview

2-2.

Typical Applications

2-3.

TMS320

2-4.

TMS320

4-1.

5-1.

6-1.

7-1.

7-2.

9-1.

9-2.

9-3.

9-4.

9-5.

11-1.

11-2.

11-3.

11-4.

A-1.

A-2.

A-3.

B-1.

Microprocessor

Feature Matrix

Software Library Contents

XDS Upgrade

TMS320 XDS Upgrade Kit Contents

TMS320 Product Bulletins and Product Descriptions

TMS320 User's Guides

TMS320

Application Reports in the

DSP

Third-Party Address/Phone/Product Support List

Third-Party Reference List

Third-Party

Trademark List

TMS320 Digital Signal Processor

TMS320 Support Tool Part Numbers

Development Tool Connections

Repair

DSP

DSP

Data

Textbooks

Consultant List

and

Replacement Charges

of

Family Benchmarks

System Benchmarks

and

Microcontroller Tests

of

TMS320 Development Tools

Process

Sheets

............................................

.............................................

....................................

the TMS320 Family

............•........................

.......................................

......................................

.......................................

DSP

Applications Book

....................................

.......................

Part

to

a Target System

.............................

.............................

............................

Numbers

...........•...................

......................

.......................

...................

...............

................

.................

...................

...........................

................

,

...........

Page

2-3

.

.

2-12

.

2-13

.

2-13

.

4-5

.

5-4

6-14

.

7-17

.

7-19

.

9-2

.

9-3

.

9-4

.

9-6

.

9-13

.

11-41

.

11-45

.

11-47

.

11-49

.

A-1

.

A-2

A-3

.

B-4

.

xi

1.

Introduction

Texas

Instruments, long recognized

has

electronics,

group

The

of

architecture have made this high-performance, cost-effective processor the

and military applications.

of

Processors.

TMS32010, the first digital signal processor in the TMS320 family, was

introduced in 1983. During that year, the

the Year" by the magazine, Electronic Products. Its powerful instruction set,

inherent flexibility, high-speed number-crunching capabilities,and innovative

ideal solution

strengthened its position

VLSI microprocessors - the TMS320 family of Digital Signal

to

many telecommunications, computer, commercial, industrial,

as

a market leader in the

with

the emergence

TMS32010 was named "Product

area

of

of

a powerful

digital

Since that time,

to

cation

tions through extensive development support and expansion

family. The members

•

•

Plans

ing generations

processors.

the advancement

First-Generation Devices:

Second-Generation Devices:

for expansion

Texas

Instruments

of

digital signal processing (DSP) and its applica-

of

the

two

TMS32010, the first

TMS3201 0-14, a

TMS3201 0-25,

TMS32011,

TMS320C10, a CMOS

TMS320C10-25,

TMS320C15,

TMS320E15,

TMS320C15-25,

TMS320C17,

TMS320E17,

TMS320C17-25,

TMS32020,

formance

TMS320C25, a

twice the performance

as

a TMS3201 0

an

of

the first-generation devices

of

the TMS320 family include more

well

as

20-MHz

14-M Hz

a 25- M

a

25-MHz

a TMS320C1 0

an

EPROM version

a

25-MHz

a TMS320C15

an

EPROM version

a

25-MHz

NMOS

40-MHz

more powerful future generations

has

demonstrated

generations

digital signal processor

version

Hz

version

with

serial interface

20-MHz

version

with

version

with

version

20-MHz

CMOS version

of

the TMS32020.

an

unsurpassed dedi-

of

the TMS320 family include:

of

the TMS3201 0

of

the TMS3201 0

version

device capable

of

the TMS32010

of

the TMS320C10

expanded ROM and RAM

of

the TMS320C15

of

the TMS320C15

serial interface

of

the TMS320C17

of

the TMS320C17.

of

the TMS32020

spinoffsof

of

the TMS320

of

twice the per-

the exist-

of

digital signal

with

TMS320 family combines the high performance and specialized features

The

necessary in

support,

documentation, textbooks, newsletters,

of

application reports. Figure 1-1 shows the wide range

available.

DSP applications

including hardware and software development products, product

with

an

extensive program

DSP design workshops, and a variety

of

development

of

development tools

1-1

Introduction

1-2

Figure

1-1.

TMS320

Family

Development

Support

Introduction

1.1

How

to

Use

This

Manual

The TMS320 Family Development Support Reference Guide details the vast

development support available for the TMS320 family

cessors.

ment making

necessary

that

Information concerning all aspects

it

an

tools for design and development

TMS320 refers

effective reference guide

to

both the first and second generations

is

consolidated into this docu-

to

assist the user in selecting the

of

of

digital signal pro-

TMS320 applications. Note

of

DSP

devices.

Sections 1 and 2 provide

ties for the user unfamiliar

for the first time. Sections 5, 6, and 7 describe the software and hardware

development products and Section 9 the extensive documentation available

to

support the wide range

Sections

each

assist in selecting which product(s}

and workshops that provide hands-on experience using the

tools.

Section

Section

Section

Section

Section

5,

6,

phase

Appendix A gives ordering information.

and 7 describe the development products available to support

of

DSP design. These sections also provide information that

2.

The TMS320 Digital Signal Processor Family. Description,

key features, and

List

3.

4.

5.

6.

ROM

the procedure for

Quality

quality

TMS320 Development Support Products. Discussion

TMS320 software and hardware development flow.

Software Support'

opment and the following products:

• TMS320 Macro Assembler/Linker

• TMS320 Simulator

, • SoftWare Development System (SWDS)

• Digital Filter

• Digital Signal Processing Software Library

• TMS320 Bell 212A Modem Software.

an

overview

with

of

applications using the TMS320 family.

of

possible applications.

Codes. Discussion

and Reliabilitv. Discussion

and reliability criteria for evaluating performance.

of

digital signal processing and investigating

the TMS320 family and its capabili-

to

use.

Section 8 describes the seminar

development

block diagram

implementation.

Products. Information on software devel-

Design Package (DFDP)

of

TMS320 family members.

of

ROM codes (mask options) and

of

Texas Instruments

can

of

it

Section

7.

Hardware Development Tools. Information on hardware de-

velopment and the following tools:

• TMS320 Evaluation Module

• TMS320 Emulator (XDS)

• TMS320 XDS

• TMS320 Analog Interface Board

• TMS320 DSP Design Kit.

Upgrade Program

(EVM)

(AlB)

1-3

Introduction

Section

Section

Section

Section

Appendix

Appendix

Appendix

8.

RTC

TMS320 Seminar

and

Workshops. Description

half-day technical seminar and three-day workshops

of

the

sponsored by the TI Regional Technology Centers (RTC). Address list

9. TMS320 Documentation Support. Discussion

of

the worldwide

RTCs.

of

TMS320

documentation available, including data sheets, user's

guides, application reports, textbooks, technical articles,

newsletters, bulletin board, and hotline.

10. TMS320 University Program. Information about the

TMS320 hardware

count

to

universities. List

professors on

TMS320 devices. Recommendations on establishing

workstations and

11. TMS320 Third-Party Support. Description

nufactured by other companies, which

development. Address list

and

software products offered at a dis-

of

DSP

theories and applications using the

research

textbooks written by university

stations in universities.

of

of

can

third parties. List

products ma-

assist

DSP

in

TMS320

of

lab

digital

signal processing consultants. '

A.

TMS320 Product Order Information. Device packaging ,information and product part numbers. Explanation of TMS320

device and development support prefixes and nomenclature.

B.

Texas

Outline

Instruments Factory Repair and Exchange Policy.

of

policies and procedures for repairing or exchang-

ing a damaged system.

C.

Texas

Instruments

Pr<jlgram

License Agreement.

1-4

2. The

TMS320

Digital Signal Processor Family

The TMS320 family

bines the

an

multichip bit-slice processors .

. The combination

data buses separated) and its

tion set provide speed and

capable

TMS320 family optimizes speed by implementing functions in hardware that

other processors

proach provides the design engineer

single chip.

The

The first generation contains the

TMS32010-25, TMS32011, TMS320C10, TMS320C10-25,

TMS320C15/E15, TMS320C15-25, TMS320C17 /E17,

The

Many features

TMS320 is used,

devices.) Some specific features

ferent cost/performance tradeoffs. Software compatibility is maintained

throughout the

processor

This section describes

key features, and provides functional block diagrams. Typical applications

also suggested.

some

major topics:

flexibility

array processor, offering

of

executing ten MIPS (million instructions per second). The

TMS320 family consists

TMS32020 and TMS320C25

has

fundamental DSP operations. Included in this section

of

16/32-bit

of

a high-speed controller

of

the TMS320's Harvard-type architecture (program and

flexibility to produce a MOS microprocessor family

implement through software. This hardware-intensive ap-

are

common among the TMS320 processors. (Note that when

it

refers

to

family

software and hardware tools

to

protect the user's investment in architecture.

each

Two

tables provide comparisons

single-chip digital signal processors com-

with

the numerical capability

an

inexpensive alternative to custom VLSI and

special digital signal processing (DSP) instruc-

with

power previously unavailable on a

of

two

generations

TMS3201 0 and its spinoffs: TMS3201 0-14,

are

the second-generation processors.

both the first and second generations

are

added in

member

of

the first and second generations, lists

of

digital signal processors.

and TMS320C17 -25.

each

processor

to

facilitate rapid design.

of

device performance for

are

to

provide

the following

of

DSP

Each

of

dif-

are

• First-Generation Devices (Section

• Second-Generation Devices (Section 2.2 on page

• Typical Applications (Section 2.3 on page

Figure 2-1 shows the generations

plotted

provides

of

on a hypothetical performance versus technology scale. Table 2-1

an

overview

memory, I/O, cycle timing, package type, technology, and military support.

of

the TMS320 family

2.1

on page

of

processors on a TMS320 family road map,

of

2-4)

2-9)

2-12)

processors

with

comparisons

2-1

The

:

P:

:

E:

:R:

: F:

,0:

:

R:

:M:

:A

:N:

c:

:

E:

TMS320

Digital

Signal Processor Family

<€:"

GENERA"§!>

1;g;;,H;;t;;;;;:;;;;;;;;"tt;;;";;;,,,,;;;;;(:

Figure 2-1. The

2-2

.~.O<:.;.~.~.~.

~~~~?:,iXiy.

TMS320

Family Roadmap

:

.tt?;;;;;;;;;;;;;;';;;;;;;;;";;;;;";;";;;;;;;;;;;·

The

TMS320

Digital

Signal

Table

Processor

2-1.

TMS320

Family

Family

Overview

DEVICE

TMS32010-14

(NMOS)

TMS32010t

(NMOS)

TMS32010-25

(NMOS)

TMS32011

(NMOS)

TMS320C10:l:

(CMOS)

TMS320C10-25

(CMOS)

TMS320C15

(CMOS)

TMS320C15-25

(CMOS)

TMS320E15

(CMOS)

TMS320C17

(CMOS)

TMS320C17

(CMOS)

TMS320E17

(CMOS)

TMS32020:l:

(NMOS)

TMS320C25:1:

(CMOS)

= serial;

'SER

··On-chip

tMilitary version available.

:l:Military versions planned; contact nearest

EPROM.

ON-CHIP

RAM

144 1.5K

144 1.5K

144 1.5K

144

144

144 1.5K

256

256 4K

256 4K"

256 4K

-25 256 4K

256 4K"

544

544

PAR

= parallel.

MEMORY

ROM

PROG

1.5K

1.5K

4K

4K

OFF-CHIP

4K

4K

4K

4K

4K

4K

4K

4K

64K

64K

DATA

sales

SER

2 6x16

2 6x16

2 6x16

2 6x16

64K

64K

1

1 16x16

office for availability.

I/O'

PAR

8x16

8x16

8x16

8x16

8x16

8x16

8x16

8x16

16x16

CYCLE

TIME

(ns)

280

200

160

200

200

160

200

160

200

200

160

200

200

100

PACKAGE

TYPE

DIP

PLCC PGA

40

40

40

40

40

40

40

40 44

40

40

40 44

40

44

44

44,

44

68

68 68

2-3

The

TMS320

2.1

First-Generation

The first generation

TMS32010-14, TMS32010-25,

2.4-lJm NMOS technology,

TMS320C15/E15, TMS320C15-25, TMS320C17/E17,

processed

member

The

of

memory

of off-chip program memory

a microcomputer version,

to 2.5K words

ROM-code version

prototyping, code update, and field upgradeability.

The

alternative

quency

well suited include servo control, high-speed controllers, low-end modems,

audio processing, data encryption, and vibration

ecute 3.5

in 280

cycle

system

compatible

ment tools.

The

TMS32010,

program memory

million instructions per second) than the TMS32010. Existing TMS32010

designs

the input

Family -First-Generation

Devices

Devices

of

the TMS320 family includes the TMS32010,

and

and

in

2.0-lJm CMOS technology. This section briefly desoribes

of

the first generation, lists key features,

TMS32010,

achieving a 16 x

of

TMS32010-14, a 14-MHz

of

million imstructions per second

ns.

program memory

development and modification. The device

TMS32010~25,

can

clock cycle time

the first TMS320 family member,

144 words

for

the TMS32010. Some applications for which the TMS32010-14

The TMS32010-14 provides a direct

with

is

take advantage

16-bit

of

off-chip program memory for a total

can

DSP

applications not requiring the maximum .operating fre-

the higher-frequency,

intended for higher-performance applications that

and

multiply in a single 200-ns cycle. On-chip data

is

available. Full-speed execution from up to 4K words

is

possible. The TMS32010

with

1.5K words

also operate entirely from off-chip ROM for

version

access,

a 160-ns instruction cycle time version

require 25 percent greater processor throughput (6.25

thereby offering a cost-effective method for

of

the enhanced throughput simply by increasing

to

25 MHz without rewriting software.

TMS32011, which

the TMS320C10, TMS320C10-25,

and

is

a microprocessor capable

of

program ROM on.-chip

of

the TMS3201 0, provides a low-cost

analysis. The device

and

perform a 16 x

EPROM

20-MHz

is

TMS32010 and its develop-

are

processed

and

TMS320C17-25,

provides block diagrams.

is

also available

of

4K words. This

16-bit

interface for single-

pin-for-pin

and

use

in

each

in

and

up

ease

of

can

ex-

multiply

software

of

the

off-chip

is

2-4

The

TMS320C10

pin-for-pin compatible

2.0-lJm CMOS technology, achieving a power dissipation

that

of

the

phony and portable consumer products. A

the

The

instruction cycle time. Its lower power

for high-performance

The

compatible with the TMS3201.0

words and on-chip program

of

TMS320C15

the NMOS device. Because

TMS320C1 0

TMS320C1

TMS320C10-25, a 25-MHz

TMS320C15

4K words. The devices

has

a 200-ns instruction cycle time and

with

the TMS3201

is

ideal for power-sensitive applications such

O.

The TMS320C1 0

of

its low-power dissipation (165 mW),

masked

O.

version of the TMS320C10,

and

DSP

applications. '

and

TMS320E15

is

also

available in a 160-ns version, the

and

ROM (TMS320C15)

are

processed

higher speed make

are

fully object-code and pin-for-pin

offer expanded on-chip RAM

in

2.0-lJm CMOS technology. The

ROM option

or,

EPROM (TMS320E15)

TMS320C15-25.

is

object-code

is

processed in

less

than one-sixth

as

digital tele.

is

available for

has

it

well suited

and

a 160-ns

of

256

The

TMS320

Family -First-Generation

Some

of

the key features

TMS320C10, TMS320C10-25, TMS320C15/E15,

of

Devices

the TMS32010, TMS3201 0-14, TMS32010-25,

and

TMS320C15-25

are:

• Instruction cycle timing:

• On-chip

• On-chip

•

•

• External memory expansion up

•

• On-chip clock generator

• Single 5-V supply

• Device packaging

• Technology:

160 ns (TMS3201 0-25, TMS320C1 0-25, TMS320C15-25)

200

ns

(TMS3201 0/C1

280

ns

(TMS32010-14)

data RAM:

144 words

256 words

program ROM:

1.5K words (optional)

4K words

4K words

16 x

16-bit

Barrel

shifter

40-pin DIP

44-lead

2.4-lJm NMOS: TMS32010, TMS32010-14, TMS32010-25

2.0-lJm CMOS: TMS320C1

(TMS320C15/E15, TMS320C15-25)

(TMS320C15, TMS320C15-25)

of

on-chip program

parallel multiplier

(see

Table

PLCC

0,

TMS320C15/E15)

EPROM

with

to

2-1):

(TMS320E15)

32-bit

result

4K words at full

0/C1 0-25,

speed

TMS320C15/E15/C15-25.

2-5

The

TMS320

Family - First-Generation Devices

+5

V GND

t t

INTERRUPT

144-WORD RAM

..

1.5K-WORD ROM

32-BIT ALUIACC

r

CJ

L

MULTIPLIER

SHIFTERS

DATA

~

ADDRESS

(16) •

(12).

.

Figure

INTERRUPT

----

Figure

2-2.

TMS32010,

......

-1

2-3.

TMS320C15/E15,

TMS32010·14,

TMS320C10-25

+5

V

256-WORD RAM

.4K-WORD

ROM/EPROM

. MULTIPLIER

32-BIT

ALU/ACC

SHIFTERS

TMS320C15-25

TMS32010~25,

Block Diagram

GND

DATA

ADDRESS (12)

Block Diagram

TMS320C10,

(16)

2-6

The

TMS320

Family -First-Generation

Devices

The TMS32011

program

applications. The device

includes a dual-channel serial interface, on-chip companding hardware

(1J-law/A-law), serial port timer, and a peripheral mode for prototyping.

The

words

dual-channel serial interface, on-chip companding hardware

and a serial port timer. The devices

TMS32010,

also available in a 160-ns version, the TMS320C17-25.

Many key features

tures

• Instruction cycle timing:

•

•

•

• Dual-channel

• Direct interface to combo-codec .

• Serial

• On-chip companding hardware for IJ-Iaw

• Object-code compatible

• Compatible with TMS3201 0 development support tools

• Peripheral

• Device packaging

• Technology:

ROM (and no external memory expansion) intended for high-volume

TMS320C17

of

on-chip program ROM (TMS320C17) or

of

the TMS32011, TMS320C17/E17,

On-chip data RAM:

On-chip program ROM:

4K words

(TMS32011 )

is

a dedicated microcomputer

is

object-code compatible with the TMS3201 0, and

and

TMS320E17

and

processed

are

160

ns

(TMS320C17-25)

200

ns

(TMS32011, TMS320C17/E17)

144 words

256 words (TMS320C17/E17, TMS320C17-25)

1.5K words (TMS32011)

4K words (TMS320C17, TMS32017-25)

of

on-chip program

serial port for fu"-duplex serial communication

port timer for standalone serial communications

mode to TMS32010 for application development

40-pin DIP

44-lead

2.4-lJm NMOS: TMS32011

2.0-lJm CMOS: TMS320C17

PLCC

in

2.0-lJm CMOS technology. The TMS320C17

common

(TMS32011)

with

(see

Table 2-1):

are

are

to

a" first-generation devices. Some key fea-

EPROM

the TMS3201 0 instruction set

IE17, TMS320C17 -25.

with

1.5K words

dedicated microcomputers

EPROM

object-code compatible

and

TMS320C17-25

(TMS320E17)

and

A-law PCM conversions

(TMS320E17), a

of

on-chip

with

4K

(1J-law/A-law),

with

the

are:

is

2-7

The

TMS320

Family - First-Generation Devices

+5

V

GND

DATA

(16)

INTERRUPT

r

CJ

INTERRUPT

DUAL-

CHANNEL

SERIAL

TMS32010

Figure 2-4. TMS32011 Block Diagram

+5

V

t

..

TMS320C15

OR

TMS320E15

PORT

p.-LAW/A-LAW

HARDWARE

TIMER

GND

t

DUAL-

CHANNEL

SERIAL

PORT

SERIAL

INTERFACE

ADDRESS

DATA

A.

SERIAL

INTERFACE

--

(3)

(16)

-"

2-8

r

CJ

L

Figure 2-5. TMS320C17/E17.

p.-LAW/A-LAW

HARDWARE

TIMER

TMS320C17-26

ADDRESS (3) "

Block Diagram

The

TMS320

Family - Second-Generation Devices

2.2 Second-Generation Devices

The second generation

cludes

two

of

these devices

TMS320

tures, and provides a

The

compatible

times the throughput

(109 instructions), large

set

spaces,

erful addition

Some key features

• 200-ns instruction cycle time

• 544 words

• 128K words

• Wait states for communication

•

• Single-cycle multiply/accumulate

• Repeat instructions

• Global data memory interface

• Block moves for data/program management

• Five auxiliary registers

• Serial port for multiprocessing or interfacing

• On-chip clock gE!nerator

• Single

•

members, the

family. This section briefly describes each device, lists its key fea-

TMS32020, processed in

with

on-chip

to

TMS32010

to-digital

2.4-l..Im

converters, etc.

5-V

NMOS technology,

of

the

is

the

serial port, and hardware timer make the

the

of

of

software compatibility

supply

TMS32020

based upon that

block diagram.

TMS32010

of

the first-generation devices. Its enhanced instruction

on-chip

TMS320

of

the

TMS32020

on-chip

total data and program memory space

data RAM

with

TMS320

family.

family

of

and the TMS320C25. The architecture

of

the TMS3201 0, the first member

2.4-l..Im

and in many applications

dedicated arithmetic

68-pin

NMOS technology,

data memory

are:

to

slower

instructions

grid array (PGA) package.

digital signal processors

(544

off-chip

is

source-code

is

capable

words), large memory

TMS32020 a pow-

memories

unit

to

codecs, serial analog-

of

of

in-

the

two

2-9

The

TMS320

Family -Second-Generation

The

TMS320C25

It

is

processed in 1.8-l.Im CMOS technology and

cycle time

creases

include 24 additional instructions, eight auxiliary registers,

hardware stack, 4K words

addressing mode,

cess.

pin-for-pin and object-code compatibility

Some

• 100-ns instruction cycle time

• 4K words

• 544 words

• 128K words

• Wait states for communication

• Object-code compatible

•

• Block moves for data/program management

• Single-cycle multiply/accumulate instructions

• Eight auxiliary registers

• Bit-reversed indexed-addressing mode for radix-2

• Double-buffered serial port

• On-chip clock generator

• Synchronization capability between multiple processors

• Single 5-V supply

• 1.8-l.Im CMOS technology: 68-pin grid array (PGA) package

of

the functionality

All

of

key features

24 additional instructions to support adaptive filtering,

tended-precision arithmetic

68-lead chip carrier (PLCC) package.

is

the newest member

100

ns.

The TMS320C25's enhanced feature

of

the device over the TMS32020. Enhancements

of

and

these improvements have

ofthe

of

on-chip program ROM (microcomputer version)

of

on-chip RAM

of

total program

on-chip program ROM, a bit-reversed indexed-

the low-power dissipation inherent

TMS320C25

with

with

Devices

of

the TMS320 second generation.

is

capable

been

achieved while maintaining

with

the TMS32020.

are:

and

data memory space

to

slower off-chip memories

the TMS32020

dedicated arithmetic unit

FFTs

of

an

instruction

set

greatly in-

an

eight-level

to

the CMOS pro-

FFTs,

and

ex-

and

2-10

The

TMS320

Family - Second-Generation Devices

+5

V GND

INTERRUPTS

D

INTERRUPTS

256-WORD I 288-WORD

DATA/PROGI

Figure

+5

RAM

MULTIPLIER

32-BIT ALU/ACC

SHIFTERS

2-6.

TMS32020

V

I

I

TIMER

DATA

RAM

T 1

256-WORD I 288-WORD

DATA/PROG

RAM

I

I

DATA

I

RAM

I

4K-WORDS ROM

DATA (16)

MULTIPROCESSOR

INTERFACE

SERIAL INTERFACE

ADDRESS (16)

Block Diagram

GND

DATA

..

.

MULTIPROCESSOR

INTERFACE

(16)

..

MULTIPLIER

32-BIT ALU/ACC

r

D SHIFTERS

L

Figure

2-7.

TIMER

TMS320C25

SERIAL INTERFACE

ADDRESS (16)

Block Diagram

2-11

The

2.3

TMS320

Typical

Family -Typical

Applications

Applications

The

TMS320 family's unique versatility

design approaches

can

simultaneously provide the multiple functions often required in those

in

a variety

of

complex applications. For example, a single TMS32020

hance the capabilities

speech

well

recognition, speech synthesis,

as

internal modem functions. Table

of

a professional computer by providing text-to-speech,

plications.

Table

2-2.

Typical

Applications

and

realtime performance offer flexible

applications.

and

DTMF encoding

2-2

of

the

TMS320

In

addition, TMS320 devices

can

be

used

and

decoding,

lists typical TMS320 family ap-

Family

to en-

as

GENERAL-PURPOSE DSP

Digital Filtering

Convolution Robot Vision Function Generation

Correlation Image Transmission/ Pattern Matching

Hilbert Transforms Compression

Fast

Fourier Transforms Pattern Recognition Transient Analysis

Adaptive Filtering Image Enhancement Digital Filtering

Windowing Homomorphic Processing

Waveform Generation

VOICE/SPEECH

Voice Mail Disk Control Secure Communications

Speech Vocoding Servo Control

Speech Recognition Robot Control Sonar Processing

Speaker Verification

Speech Enhancement Engine Control Navigation

Speech Synthesis

Text-to-Speech Radio Frequency Modems

TELECOMMUNICATIONS

Echo Cancellation FAX Engine Control

ADPCM Transcoders Cellular Telephones Vibration Analysis

Digital

PBXs

Line Repeaters Digital Speech Adaptive Ride Control

Channel Multiplexing Interpolation (DSI) Global Positioning

1200

to

Adaptive

DTMF Encoding/Decoding Spread Spectrum

Data Encryption

Radar

Power

Digital Audio/TV

Music Synthesizer Power Line Monitors Diagnostic Tools

Educational Toys Prosthetics

19200-bps Modems

Equalizers Video Conferencing

CONSUMER

Detectors Robotics Hearing Aids

Tools Numeric Control Patient Monitoring

GRAPHICS/IMAGING

3-

0 Rotation Spectrum Analysis

Workstations

Animation/Digital Map

CONTROL

Laser

Printer Control Image Processing

Motor Control

Speaker Phones Antiskid

X.25 Packet Switching Navigation

Communications

INDUSTRIAL

Security Access

INSTRUMENTATION

Seismic Processing

Phase-Locked Loops

MILITARY

Radar

Processing

Missile Guidance

AUTOMOTIVE

Brakes

Voice Commands

Radio

Digital

Cellular Telephones

MEDICAL

Ultrasound Equipment

Fetal Monitors

2-12

Table 2-3 provides a comparison

DSP

operations when using either a TMS32010, a TMS32020, or a

TMS320C25. Table

2-4

shows the benchmarks for the

providing cost-effective solutions to a wide range

of

performance for some

of

the fundamental

same

of

applications.

three devices

in

These

The

TMS320

Family - Typical Applications

performance figures can be further improved by additional optimization

algorithms for specific design

goals, such

as

CPU

loading and program space

requirements.

Table

2-3.

TMS320

FUNCTION TMS32010 TMS32020 TMS320C25 UNIT

Sample Time:

FI

R filter tap

Biquad II R filter tap 2 2 1

adaptive filter tap 1.4 1.2 0.4

LMS

(filter

and

update)

Sample

Rate:

256-tap

256-tap adaptive

Fast

64

256 complex-point:

1024 complex-point:

Matrix multiplication 5.4 5.4 2.7

[1 x 3]

FIR

straightline

straightline

[3 x 1]

filter:

I/O

FI

R filter:

I/O

I/O

I/O

Without companded

With companded

Without companded

With companded

Fourier Transforms:

complex-point 555 434 217

Radix-4

Radix-2 looped

Radix-4

Radix-2 looped 69.4 45 22.5

DSP Family Benchmarks

0.4 0.2

9.6 18.5 37 kHz

9.1

2.7 3.2 9.5

2.7

N/A

N/A

N/A

15.75

3.1

2.44 1.5

6.88 3.44

14.18

0.1

31.5

9.1

7.1

of

lis

lis

liS

kHz

kHz

kHz

liS

ms

ms

ms

ms

liS

the

Table

2-4.

TMS320

DSP System Benchmarks

PERFORMANCE

APPLICATION STANDARD TMS32010

Echo cancellation

(CCITI

G.165) (16

Data

encryption

(ANSI X3.92-1981 ) (42 kbps)

Split-band modem

(CCITI

V.22/212A) (full-duplex)

32-kbps ADPCM

(CCITI

G.721) (half-duplex)

2400-bps LPC-10

~O:l:

(DOD 45) (half-duplex)

16-kbps subband

coder

tRequires external program memory.

:l:Requires

external data memory.

Echo length

ms)

Data

rate

(full-duplex)

CPU

CPU

CPU

CPU

TMS32020t

N/A

100

loading

loading 100

loading

loading 80

TMS320C25

100 50

84 42

80

95

60 30

90 50

t:l:

:I:

70 3

75

2-13

2-14

3.

ROM

Codes

Board space

reduce chip count and provide the customer

Instruments offers microcomputer versions for many

members. The on-chip

customer's

al-purpose features

customizing the processor

To facilitate design, all prototype

microprocessor. (Note that TMS320 refers to both the first and second generations

test and refine algorithms for immediate results. When the algorithm

finalized, t!le customer

into the

MC/MP

The

TMS320 family members (excluding the TMS32011, TMS320C17/E17, and

TMS320C17-25), often shortens design and field upgrade cycle times,

thereby reducing expense. This mode permits the customer

as

a standard device operating

TMS320 code

processing

of

inventory obsolescence when the code is altered

An entire algorithm or

ROM space

ing external memory. With a reduced chip count and this program memory

flexibilty, multiple functions can

ware device, thus enhancing a product's capabilities.

is

often a critical concern in many

ROM

of

these processors

own

code. This allows the user to take advantage

of

TI's digital signal processors while at the

to

suit a specific application.

work

is performed using a standard TMS320

of

DSP

devices.) TMS320 development tools permit a designer

can

submit the code to

on-Chip ROM

(microcomputer/microprocessor) mode, offered on maskable

is

are

avoided. Field upgrade cycle times and the associated expense

of

a TMS320 DSP. TMS320 programs can also

of

the device.

out

of

altered during design, the delays associated

an

often-used routine may

be

more easily implemented in a single hard-

DSP

applications.

with

a single-chip solution, Texas

of

the TMS320 family

can

be

masked

Texas

Instruments to

to

use

external program memory. When

with

are

also avoided.

be

masked into the on-chip

be

In

order to

with

the

of

the gener-

same

time

to

has

been

be

masked

the TMS320

new silicon

expanded us-

The first-generation

TMS320C10,

TMS320C15 and TMS320C17

ond-generation

as

dered

ROM size

Figure 3-1 illustrates the procedure

parts. With any masked device order, there

mask tooling which includes 25 prototypes. A non-cancellable minimum

production order per year

TMS320C10, TMS320C15,

high-volume usage

The masked

a masked device. The customer's code must

of

the chosen processor.

TMS320C25

TMS320 DSPs

and TMS32011

TMS320C25

of

and TMS320C17. The TMS32011

with

a minimum production order per year

will

with

mask

with

1.5K words

with

4K words

with

4K words

flow

5000 units

be

available in 1987.

option include the TMS3201 0,

of

on-chip ROM, and the

of

on-chip ROM. The sec-

of

on-chip ROM

fit

for implementing TMS320 masked

is

a one-time charge

is

required for the TMS32010,

can

also

be

or-

within the specified

of

$5500 for

is

intended for

of

10,000 units.

3-1

ROM

Codes

CUSTOMER

CUSTOMER SUBMITS:

-

TMS320

- PRINT EVALUATION AND ACCEPTANCE FORM (PEAF)

- PURCHASE

-

TMS320

TEXAS INSTRUMENTS RESPONDS:

- CUSTOMER

-

CODE

NEW

CODE

ORDER

CODE

CODE

SENT BACK TO CUSTOMER

NO

TI PRODUCES

TMS320

RELEASE

FOR

MASK CHARGE/25 PROTOTYPES

INPUT INTO TI SYSTEM

25

DESIGN

FORM

FOR

VERIFICATION

PROTOTYPES

3-2

,Figure

NO

3-1.

TMS320

TMS320

PROOUCTION

ROM

Code

Flowchart

ROM

Codes

Leadtimes for the first 25 prototype units begin when the customer

mally verified that TI

production order begin once the customer

totypes. The typical leadtime for masked

for masked

TMS320

stantly strives

changes at any time.

has

recorded his code correctly. Leadtimes for the first

formally approves the masked pro-

production

to

improve these leadtimes and reserves the right

Please

10

to

12

contact the nearest TI Sales Office

TMS320

prototypes is 8 weeks and

weeks. Texas Instruments con-

leadtimes, further information on these procedures, and confirmation

to

for

has

for-

make

current

of

the

mask/production requirements.

TMS320

A

preferred media

PROM:

EPROM:

FLOPPY:

When a code

is

reformatted

verification

been reformatted,

user and

made involve deletion

and addition

ROM code may be submitted in one

is 5 1/4"

floppies):.

I

TBP28S166, TBP28S86

TMS2764,

TMS2508, TMS2516, TMS2532, TMS2564

TI Cross-Assembler Format

is

submitted

to

accommodate the TI mask generation system. System level

by

the customer

it

not

affect the execution

of

data in the reserved locations

to

Texas Instruments

is

is

important that the changes remain transparent

of

all address tags (unnecessary in a ROM code device)

therefore necessary. Although the code has

of

the algorithm. The formatting changes

of

the

following

for

a masked device, the code

of

the ROM for device ROM test.

formats (the

to

the

Note that because these changes have been made, a checksum comparison

not

a valid means

ROM code algorithms may also

a modem. Contact the nearest

of

verification.

be

submitted by secure electronic transfer via

TI sales office for further information.

With each masked device order, the customer must sign a disclaimer stating:

is

to

"The units

be shipped against this order were assembled, for ex-

pediency purposes, on a prototype (i.e., non-production qualified)

of

which

is

not

manufacturing line, the reliability

Therefore, the anticipated inherent reliability

fully characterized.

of

these prototype units

cannot be expressly defined."

and a release stating:

"Any

masked ROM device may be resymbolized

uct and resold

as

device at the convenience

ROM codes

will

be deleted from the TI system after one year from the last

though

it

were

an

of

Texas Instruments."

unprogrammed version

as

TI standard prod-

delivery.

of

the

3-3

3-4

4.

Quality

and

Reliability

The quality and reliability performance

Microcontroller Products,

and

signal processors, relies on feedback from:

• Our customers

• Our total manufacturing operation from front-end wafer fabrication

final shipping inspection

• Product quality and reliability monitoring.

Our customer's perception

judging performance. This concept

rate Quality Policy,

"For every product or service

ments that solve the customer's problems, and

those requirements

Quality and reliability programs at

and internal information

ability.

Texas

Instruments offers a leadership reliability qualification system, based

years

of

research into customer requirements. This system provides more than

liable products; feedback

continuing improvements in TI products. Data generated by the system

ways available

last input received

formance is the most important quality and reliability measurement.

experience

which

without

with

to

aid customers in qualifying TI products. Although

for

any product delivery cycle, customer-perceived per-

which

of

quality must be the governing criterion

is

as

follows:

exception."

to

achieve constant improvement in quality and reli-

leading-edge memory technology

of

results

of

Texas Instruments Microprocessor

includes the

is

the basis

we

offer,

TI

are

therefore based on customer

to

manufacturing and design leads

TMS320

for

Texas Instruments Corpo-

we

shall define the require-

we

shall conform

as

family

well

as

of

years

just

it

digital

to

input

is

is the

to

for

on

of

re-

to

al-

4-1

Quality

4.1

and

Reliability

Reliability Stress Tests

Accelerated stress tests

process changes

vironments used

• High-temperature operating life

Storage life

•

•

Temperature cycling

Biased humidity

•

• Autoclave

• Electrostatic discharge

• Package integrity

• Elec::tromigration

• Channel-hot electrons

Typical events or changes that require internal requalification

clude:

•

New die design, shrink, or layout

•

Wafer process (baseline/control systems, flow,

dopants, passivation, or metal systems)

• Packaging assembly (baseline control systems or critical assembly

equipment)

• Piece parts (such

wire, or

Manufacturing site.

•

TI

r~liability

controls

duct

serve

sites; enhancing

than

built-in product excellence.

and management include product ramp monitor

release

as

the leading indicator in wafer-process integrity at TI MOS fabrication

200,000 MOS devices per month on reliability test

to

lead finish)

control systems extend beyond qualification. Total reliability

controls. MOS memories, utilizing high-density active elements,

all MOS logic device yields and reliability.

are

to

ensure product reliability excellence. The typical test en-

qualify new products or major changes in processing

performed on new semiconductor products and

(performed on geometries

as

lead frame, mold compound, mount material, bond

less

than 2.0

of

mask,

chemicals,

as

well

as

TI

to

ensure and sustain

11m).

product

final pro-

places more

are:

in-

gases,

4-2

Table

4-1 lists the microprocessor and microcontroller reliability tests, the du-

ration

of

the test, and sample

tests in the

table.

AOQ (Average Outgoing Quality) Amount

. ulation, usually expressed in terms of

FIT (Failure In Time)

Operating

lifetest

size.

The following defines and describes those

I

parts per million (PPM).

Estimated field failure rate in number

of

hours;

fail per

Device

ambient temperature

to

of

defective product in a pop-

failures per billion power-on device

1000

FITS

1000 device hours.

dynamically exercised at a high

simulate field usuage that would

equals

(usually 125°C)

0.1

percent

Quality

and

Reliability

expose the device to a much lower

ambient temperature (such

Using a derived high temperature, a

55·C ambient failure rate

culated.

can

as

be cal-

55·C).

High-temperature

Biased

Autoclave

Temperature

humidity

(pressure

cycle

storage

cooker)

Device exposed to

condition. Bond integrity

this environment.

Moisture and bias used

corrosion-type failures

packages.

ambient temperature

relative humidity (RH). Typical bias

voltage

nating pins.

Plastic-packaged devices exposed to

moisture at

one atmosphere above normal pressure. The pressure forces moisture

permeation

erates corrosion mechanisms

ent) on the device. External package

contaminates can also be activated

and caused

rent leakage paths.

Device exposed

extremes in

(-65·C

15

minutes per cycle) for at least

cycles. Package strength, bond quality, and consistency

cess

Conditions include 85·C

is

+5

121·C using a pressure

of

to

an

for

15

are

stressed in this environment.

150·C unbiased

is

stressed in

to

accelerate

in

plastic

with

85-percent

V and ground on alter-

the package and accel-

generate

to

severe temperature

alternating fashion

minutes and 150·C for

of

(if

pres-

inter~pin

assembly pro-

cur-

1000

of

Thermal

PIND

Mechanical

shock

Sequence:

Fine and gross leak

Mechanical shock

PI

N D (optional)

Vibration, variable frequency

Constant acceleration

Fine and gross leak

Test similar

test, but involving a liquid-to-liquid

transfer, per

1011.

Particle Impact Noise Detection test.

A non-destructive test.to detect loose

particles inside a device cavity.

Per

M I L-STD-883C, Method 1014.5

Per

MIL-STD-883C, Method 2002.3,

1500

Per

MIL-STD-883C, Method 2020.4

Per

MIL-STD-883C, Method 2007.1,

20 g, Condition

Per MIL-STD-883C, Method 2001.2,

20

kg, Condition

Per

MIL-STD-883C, Method 1014.5

g,

to

the temperature cycle

MIL-STD-883C, Method

0.5

ms,

Condition B

A .

D,

Y1

Plane min

4-3

Quality and Reiiability

Electrical test

Thermal Sequence:

Fine and gross leak

Solder heat (optional)

Temperature cycle

(10 cycles minimum)

Thermal shock

cycles minimum)

(10

Moisture

Fine and gross

Electrical test

resistance

leak

Thermal/Mechanical Sequence:

Fine

and

gross leak

Temperature cycle

(10 cycles minimum)

Constant acceleration

Fine and gross leak

Electrical test

Electrostatic discharge

Solderability

Solder heat

Salt atmosphere

Lead

pull

Lead

integrity

Electromigration

Resistance to solvents

To data

Per

Per

Per

-65

Per

-55

Per

Per

To data sheet limits

Per

Per

-65 to +150·C, Condition C

Per

30 kg,

Per

To data sheet limits

Per

Per

Per

10sec

Per

Condition

Per

Condition A

Per

Condition

Accelerated stress testing

ductor patterns

lifetime

Per

sheet limits

MIL-STD-883C, Method 1014.5

MIL-STD-750C, Method i 014.5

MIL-STD-883C, Method 1010.5,

to

+150·C, Condition C

MIL-STD-883C, Method 1011.4,

to

+125·C, Condition B

MIL-STD-883C, Method 1004.4

MIL-STD-883C, Method 1014.5

MIL-STD-883C, Method 1014.5

MIL-STD-883C, Method 1010.5,

MIL-STD-883C, Method 20()1.2,

Y1

Plane

MIL-STD-883C, Method 1014.5 .

MIL-STD-883C, Method 3015

MIL-STO-883C, Method 2003.3

MIL-STD-750C, Method 2031,

MIL-STD-883C, Method 1009.4,

A,

24,

hrs

min

MIL-STD-883C, Method 2004.4,

MIL-STD-883C, Method 2004.4,

B1

of

to

ensure acc,eptable

of

power-on operation

MIL-STD-883C, Method 2015.4

con-

4-4

Quality

and

Reliability

Table

4-1.

Microprocessor

and

MicrocontrollerTests

TEST

Operating life, 125·C, 5.0 V 1000 hrs 195

Op~rating

Storage life, 1 50·C

Biased

Autoclave,

Temperature cycle, -65

Thermal shock,

Electrostatic discharge,

Latch-up

Mechanical sequence

Thermal sequence

Thermal/mechanical sequence

PIND

Internal water vapor

Solderability 22 22

Solder heat 22 22

Resistance

Lead

Lead

Lead

Salt atmosphere

Flammability

Thermal impedance 5 5

·If

TI

Qualification test updates

life, 150·C, 5.0 V

85·C/85 percent

121

·C, 1 ATM

-65

(CMOS devices only)

to

integrity 15 15

pull

finish adhesion

junction temperature does not

solvents 12 12

(UL94-VO) 3

RH,

5.0 V 1000 hrs 129

to

150·C 1000 cyc

to

150·C 500 cyc 129 129

± 2

kV

exceed

are

available upon request at no charge.

consider performing any additional reliability test(s),

TI

information on

sales

office.

quality and reliability programs, contact the nearest n field

DURATION

1000 hrs

1000

240

plasticity

hrs

hrs

of

package.

SAMPLE

PLASTIC

SIZE

CERAMIC

77·

129 129

105

129 129

12 12

5 5

-

-

-

-

-

15

15

15 15

if

requested. For more

195

77

-

-

38

38

38

15

5

-

15

-

TI

will

Note:

Texas

Instruments reserves the right

ductor test

limits, procedures, or processing

arrangements for notification have

to

make changes in MOS Semicon-

been

without

made, TI advises all customers

notice. Unless prior

reverify current test and manufacturing conditions prior

published data.

to

relying on

to

4-5

4-6

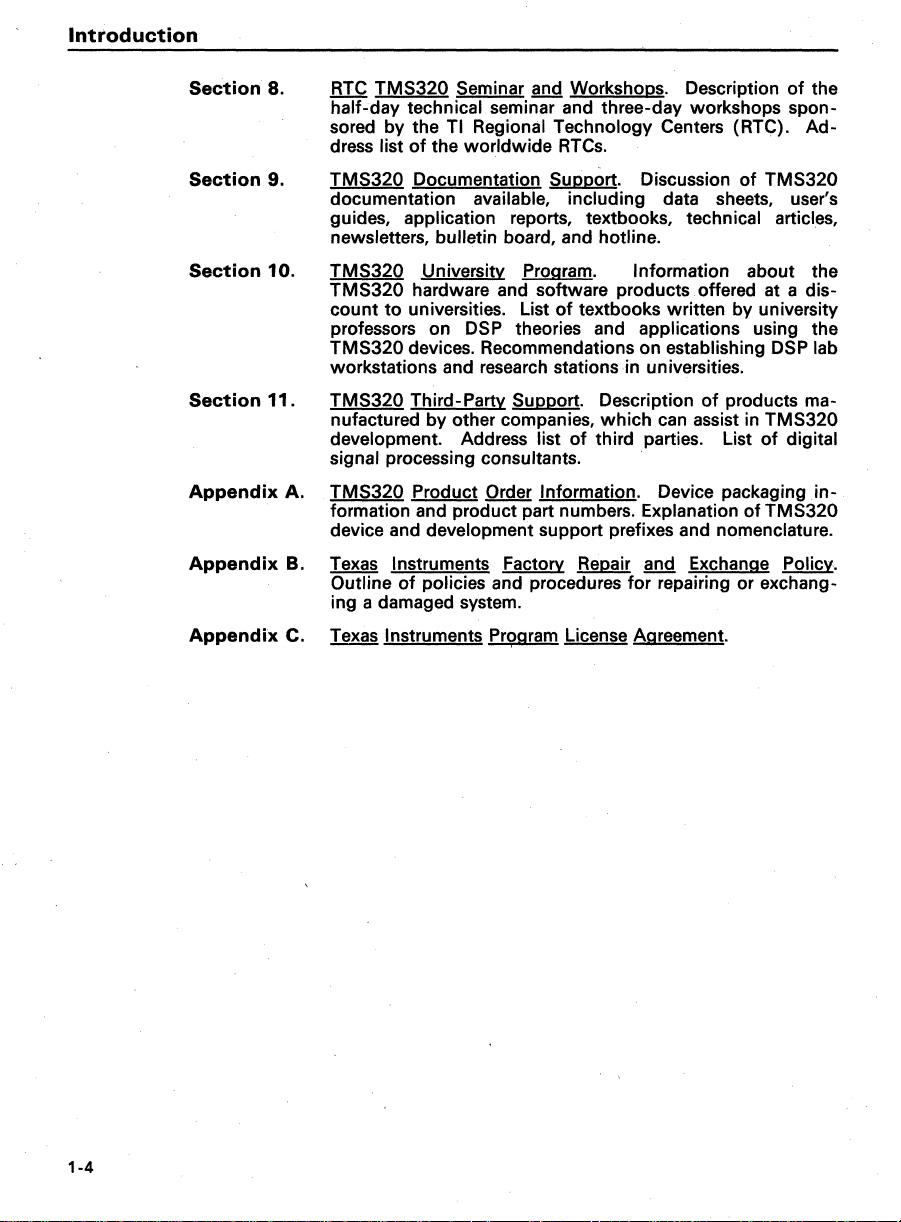

5.

TMS320

Development

Texas

Instruments offers

to assist the user in

products range from development and

ware development and integration systems such

Support

an

extensive line

a"

aspects

Products

of

of

TMS320 design and development. These

application software to complete hard-

development support products

as

the XDS/22.

System

(EVM) or Emulator

the processor's performance, benchmark time-critical code, and determine the

feasibility

tensive documentation provides information concerning device specifications

and capabilities. The

DSP design workshops that provide hands-on experience

velopment

Software and hardware can

assembler/linker and simulator for software development and the

hardware development. The

source program into

XDS, or

erful tool for debugging and integrating software and hardware modules.

Figure 5-1 shows development product integration, and Figure

typical application development. The appropriate

is indicated for

of

ment purpose, software and hardware features,

development begins

(XDS). These support tools allow the designer

of

using a TMS320 device to implement a specific algorithm.

tools (see Section 8.2).

an

EVM.

The XDS provides realtime in-circuit emulation

each

stage

the TMS320 development tools, comparing capabilities such

with

the

use

of

the TMS320 Evaluation Module

to

evaluate

TI

Regional Technology Centers (RTCs) offer three-day

with

TMS320 de-

be

developed in para"el by using the macro

XDS for

assembler/linker translates the system's assembly

object module that can

of

development. Table 5-1 provides a feature matrix

be

executed by the simulator,

and

is a pow-

5-2

TMS320 support product

as

develop-

and

amount

of

memory.

Ex-

shows

5-1

TM$320

Development Support Products

APPLICATIONS

LIBRARY

MACRO

ASSEMBLER

LINKER

DFDP

Figure 5-1.

TMS320

Development Product Integration

TMS320

Development

Support

Products

CONCEPTUAL

STAGE

TMS320

EVALUATION

HARDWARE/

SOFTWARE

DESIGN

HARDWARE/

SOFTWARE

INTEGRATION

HARDWARE

XDS

DSP APPLICATIONS

ASSEMBLER/LINKER

DESIGN

SYSTEM DEBUG

XDS

SOFTWARE DESIGN

ASSEMBLER/LINKER,

SIMULATOR

SWDS

(TMS32020/C25)

Figure 5-2. Typical

TMS320

Application

Development

Flow

5-3

TMS320

Development

Support

Products

Table 5-1. Feature

FEATURES

Development Purpose:

Evaluation/benchmarking

Software development

Hardware design No

Line-by-line assembler/reverse assembler

Modify/display memory and registers

Single-stepping

Breakpoint on address

Breakpoint on memory access/read/write No

Time-stamping/clock counter No

Real-time trace samples No No No

Full-speed in-circuit emulation:

From on-board memory

From target memory

Multi-user system No

Built-in

Files associated

Amount

system interface No No

to

I/O

ports

of

On-board program/data

memory:

On-board program/data (TMS32020/C25)

Program/data expansion (TMS320C25) 6K/16K

" Memory expansion board allows

program and data memory. configurable in 1 K blocks.

(TMS3201 0/C1 0)

Matrix

for

of

TMS320

EVM

Yes

No

Yes

Yes

Yes Yes Yes

Yes

Yes

No

No

4K/-

4K/4K

memory expansion

Development Tools

SIMULATOR SWDS

Yes Yes

Yes

No No

No

Yes

Yes

Yes

Yes

N/A

N/A

Yes

Yes

N/A

N/A

N/A

to

64K words total

.

Yes

Yes

Yes.

Yes

No

Yes

Yes

No

No

Yes

Yes

N/A

N/A

24K

XDS

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

No

No

No

4K/-

4K/4K

64K"

of

5-4

6.

Software

Support

Products

Many support products

processors. This section discusses the software support products, which include a macro assembler/linker, simulator, SoftWare Development System

(SWDS), Digital

TMS320 Bell

sections listed

• TMS320

• TMS320 Simulator (Section 6.2 on page

• SoftWare Development System (SWDS) (Section 6.3 on page

• Digital Filter Design Package (DFDP) (Section 6.4 on page 6-10)

• Digital Signal

• TMS320 Bell 212A Modem Software (Section 6.6 on page

Filter Design Package (DFDP), DSP Software Library, and

212A

below.

Macro Assembler/Linker (Section

are

offered for the TMS320 family of digital signal

Modem Software. These products

6.1

6-5)

Processing Software Library (Section 6.5 on page

are

on page

described in the

6-2)

6-15)

6-7)

6-13)