Page 1

TMS320C6474

www.ti.com

SPRS552F–OCTOBER 2008–REVISED JULY 2010

TMS320C6474 Multicore Digital Signal Processor

1 Features

12

• Key Features

– High-Performance Multicore DSP (C6474)

– Instruction Cycle Time: 0.83 ns (1.2-GHz

• 1.2-GHz Device: -40°C to 95°C

• 1-GHz Device: -40°C to 100°C

• 3 TMS320C64x+™ DSP Cores

Device); 1 ns (1-GHz Device); 1.18 ns – Dedicated SPLOOP Instructions

(850-MHz Device)

– Clock Rate: 1 GHz to 1.2 GHz (1.2-GHz

Device); 1 GHz (1-GHz Device); 850 MHz

(850-MHz Device)

– Commercial Temperature and Extended

Temperature

– 3 TMS320C64x+™ DSP Cores; Six RSAs for

CDMA Processing (2 per core)

– Enhanced VCP2/TCP2

– Frame Synchronization Interface

– 16-/32-Bit DDR2-667 Memory Controller

– EDMA3 Controller

– Antenna Interface

– Two 1x Serial RapidIO® Links, v1.2

Compliant

– One 1.8-V Inter-Integrated Circuit (I2C) Bus

– Two 1.8-V McBSPs

– 1000 Mbps Ethernet MAC (EMAC)

– Six 64-Bit General-Purpose Timers

– 16 General-Purpose I/O (GPIO) Pins

– Compact Instructions (16-Bit)

– Exception Handling

• TMS320C64x+ Megamodule L1 Memory

Architecture

– 256 K-Bit (32 K-Byte) L1P Program Cache

[Direct Mapped]

– 256 K-Bit (32 K-Byte) L1D Data Cache

[2-Way Set-Associative]

– 512 K-Bit (64 K-Byte) L3 ROM

• Enhanced VCP2

– Supports Over 694 7.95-Kbps AMR

• Enhanced Turbo Decoder Coprocessor (TCP2)

– Supports up to Eight 2-Mbps 3 GPP

(6 Iterations)

• Endianness: Little Endian, Big Endian

• Frame Synchronization Interface

– Time Alignment Between Internal

Subsystems, External Devices/System

– OBSAI RP1 Compliant for Frame Burst Data

– Alternate Interfaces for non-RP1 and

– Internal Semaphore Module non-UMTS Systems

– System PLL and PLL Controller/DDR PLL • 16-/32-Bit DDR2-667 Memory Controller

and PLL Controller, Dedicated to DDR2

Memory Controller

• High-Performance Multicore DSP (C6474)

– Instruction Cycle Time:

• 1.2-GHz Device: 0.83-ns

• 1-GHz Device: 1-ns

• EDMA3 Controller (64 Independent Channels)

• Antenna Interface

– 6 Configurable Links (Full Duplex)

– Supports OBSAI RP3 Protocol, v1.0:

768-Mbps, 1.536-, 3.072-Gbps Link Rates

– Supports CPRI Protocol V2.0: 614.4-Mbps,

• 850-MHz Device: 1.18 ns 1.2288-, 2.4576-Gbps Link Rates

– Clock Rate: – Clock Input Independent or Shared with CPU

• 1.2-GHz Device: 1 GHz to 1.2 GHz

• 1-GHz Device: 1 GHz

• 850-MHz Device: 850 MHz

– Eight 32-Bit Instructions/Cycle

– Commercial Temperature:

• 1.2-GHz Device: 0°C to 95°C

• 850-MHZ and 1-GHz Device: 0°C to 100°C

– Extended Temperature:

(Selectable at Boot-Time)

• Two 1x Serial RapidIO® Links, v1.2 Compliant

– 1.25-, 2.5-, 3.125-Gbps Link Rates

– Message Passing and DirectIO Support

– Error Management Extensions and

Congestion Control

• One 1.8-V Inter-Integrated Circuit (I2C) Bus

• Two 1.8-V McBSPs

(1)

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testingof all parameters.

(1)

Note: Advance Information is presented in this document for

the C6474 1.2-GHz extended temperature device.

Copyright © 2008–2010, Texas Instruments Incorporated

Page 2

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

AG

2

1 3456789101112131415161718192021222324252627

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

• 1000 Mbps Ethernet MAC (EMAC) – 32 General Purpose Semaphore Resources

– IEEE 802.3 Compliant • System PLL and PLL Controller

– Supports SGMII, v1.8 Compliant • DDR PLL and PLL Controller, Dedicated to

– 8 Independent Transmit (TX) and 8

DDR2 Memory Controller

Independent Receive (RX) Channels • IEEE-1149.1 and IEEE-1149.6 (JTAG™)

• Six 64-Bit General-Purpose Timers

– Configurable up to Twelve 32-Bit Timers

– Configurable in a Watchdog Timer mode

• 16 General-Purpose I/O (GPIO) Pins

• Internal Semaphore Module

– Software Method to Control Access to

Shared Resources

Boundary-Scan-Compatible

• 561-Pin Ball Grid Array (BGA) Packages (CUN,

GUN, or ZUN Suffix), 0.8-mm Ball Pitch

• 0.065-mm/7-Level Cu Metal Process (CMOS)

• SmartReflex™ Class 0 - 0.9-V to 1.2-V Adaptive

Core Voltage

• 1.8-V, 1.1-V I/Os

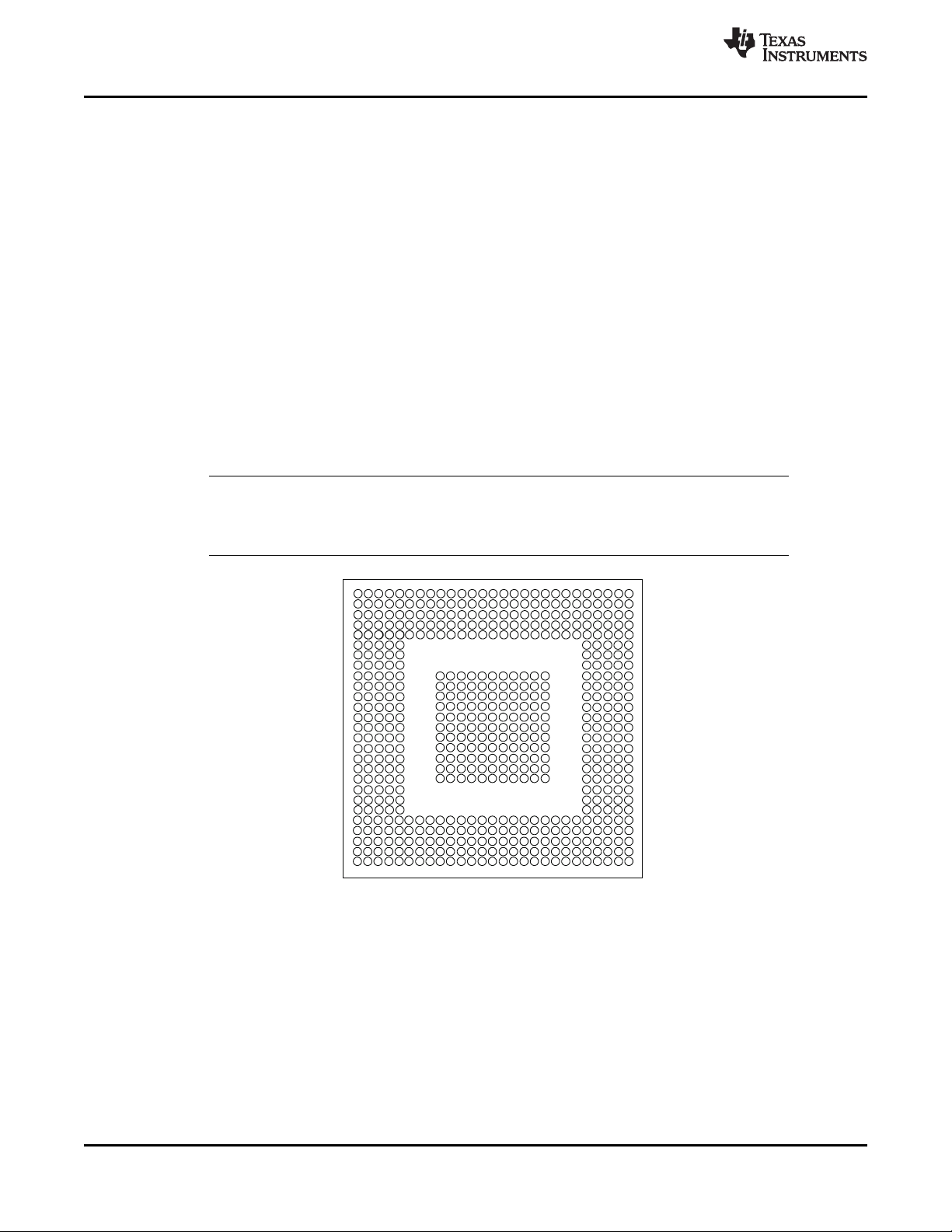

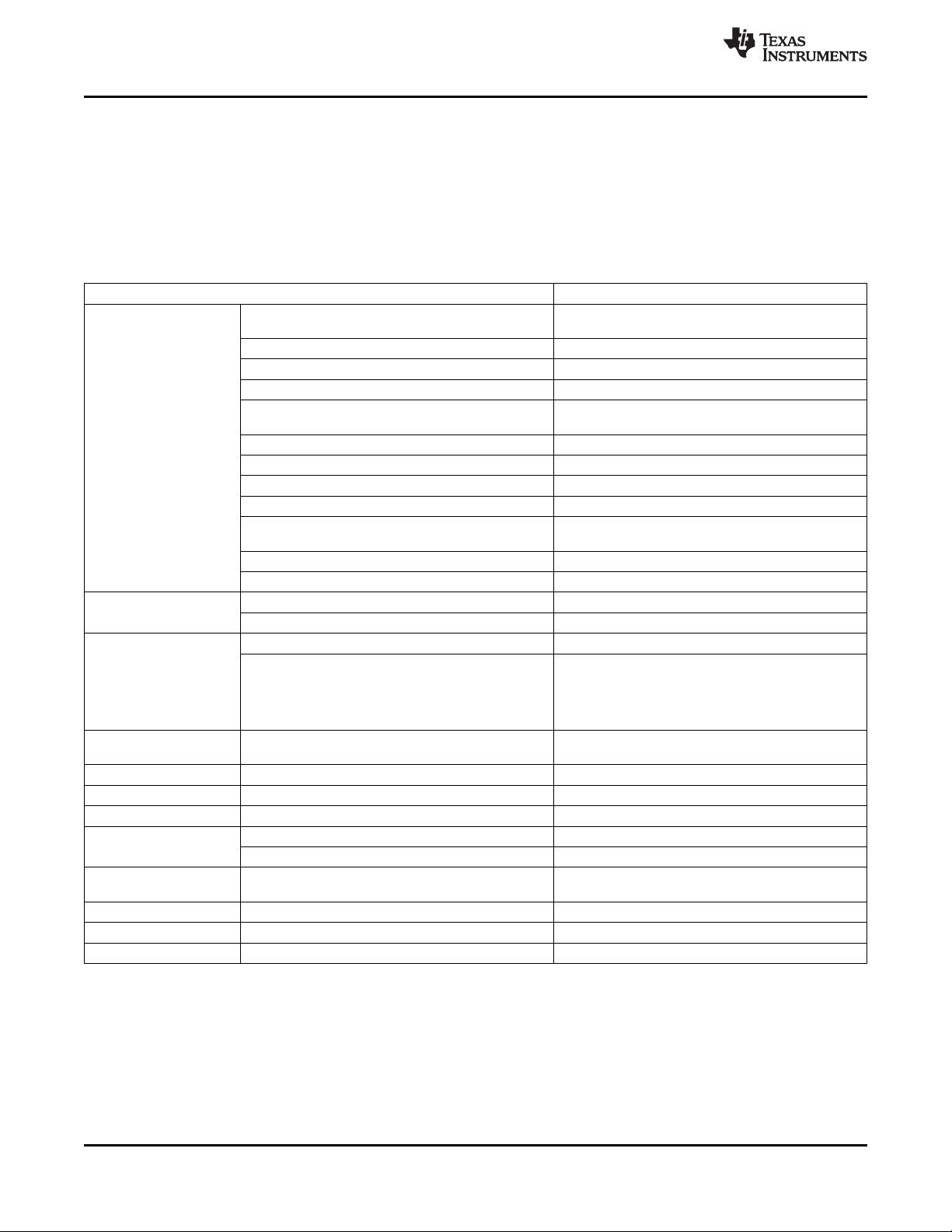

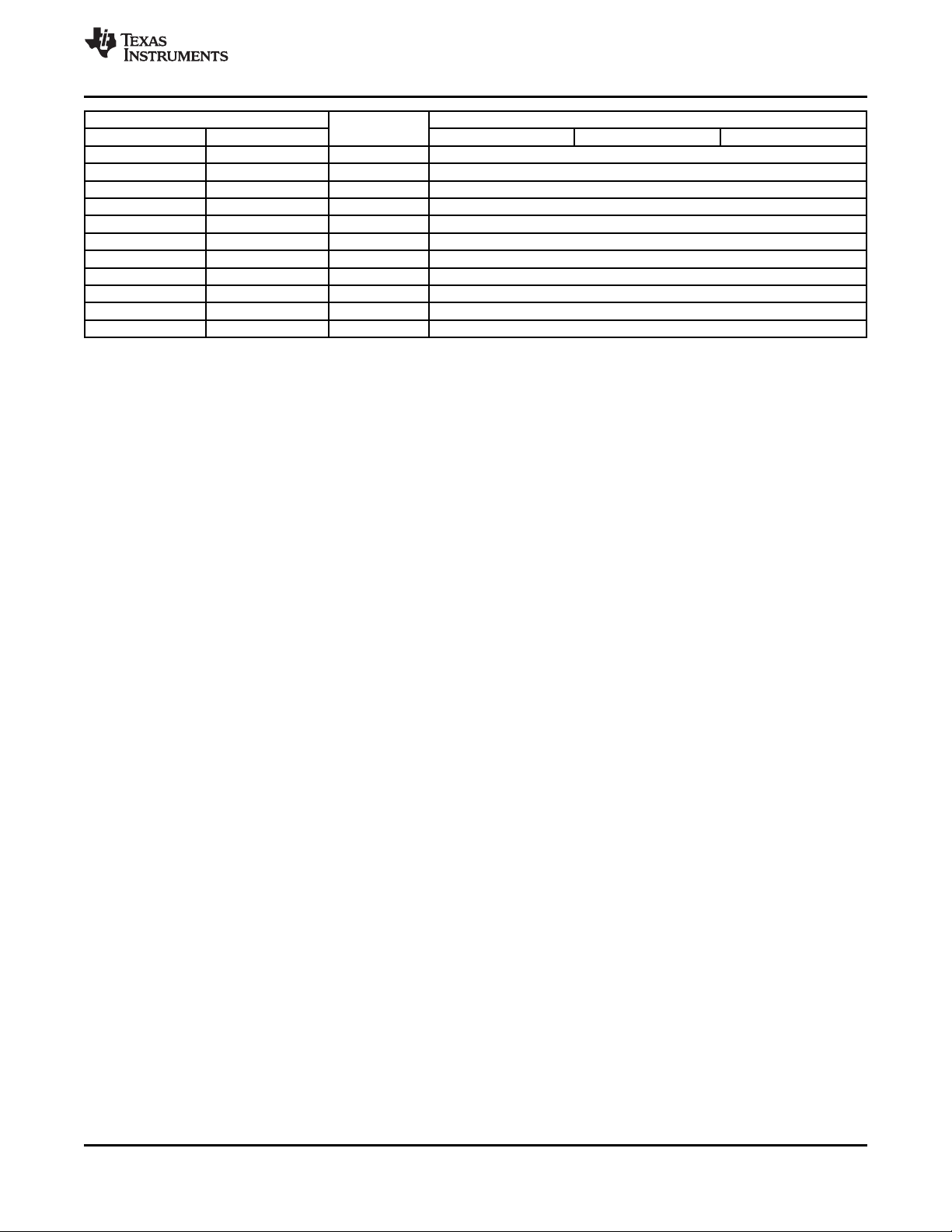

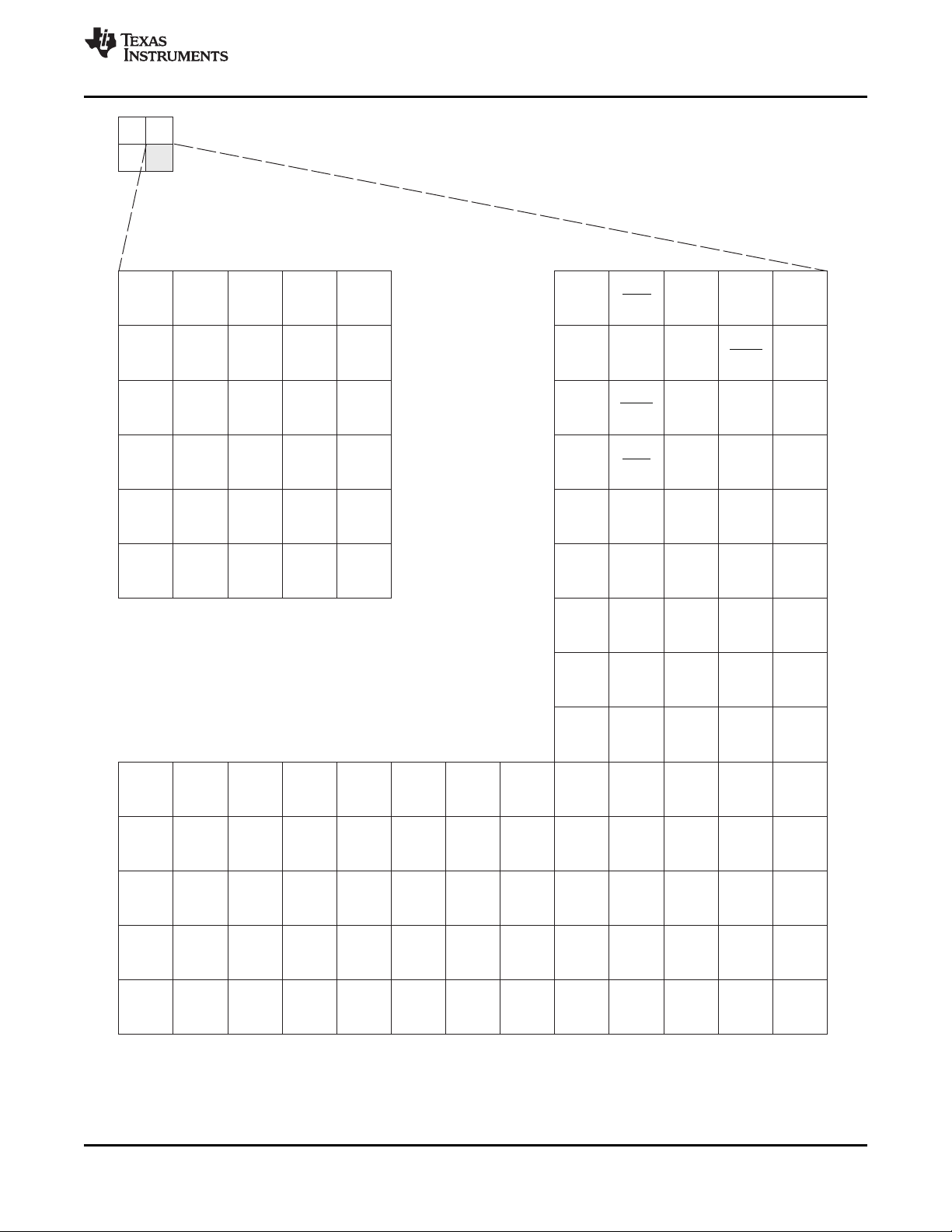

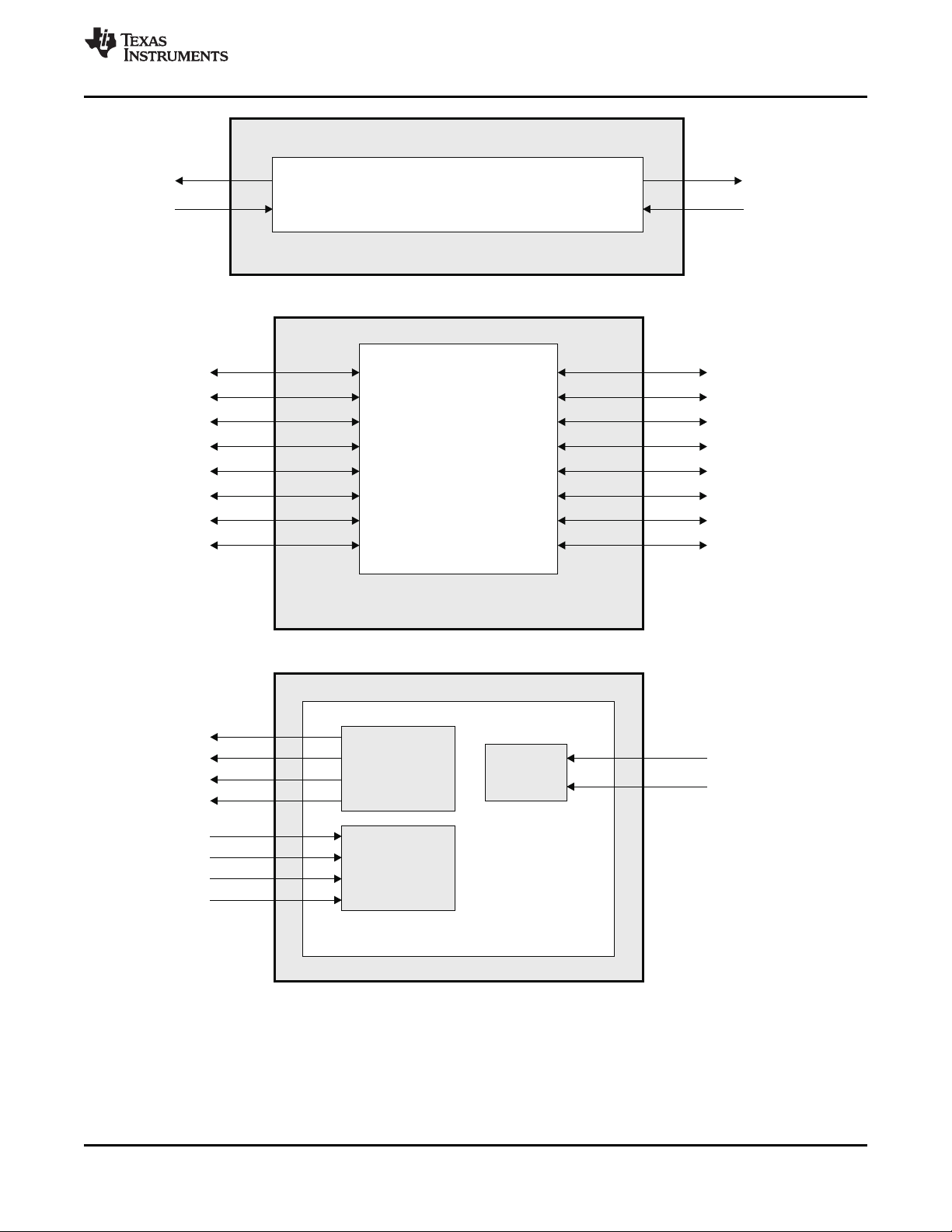

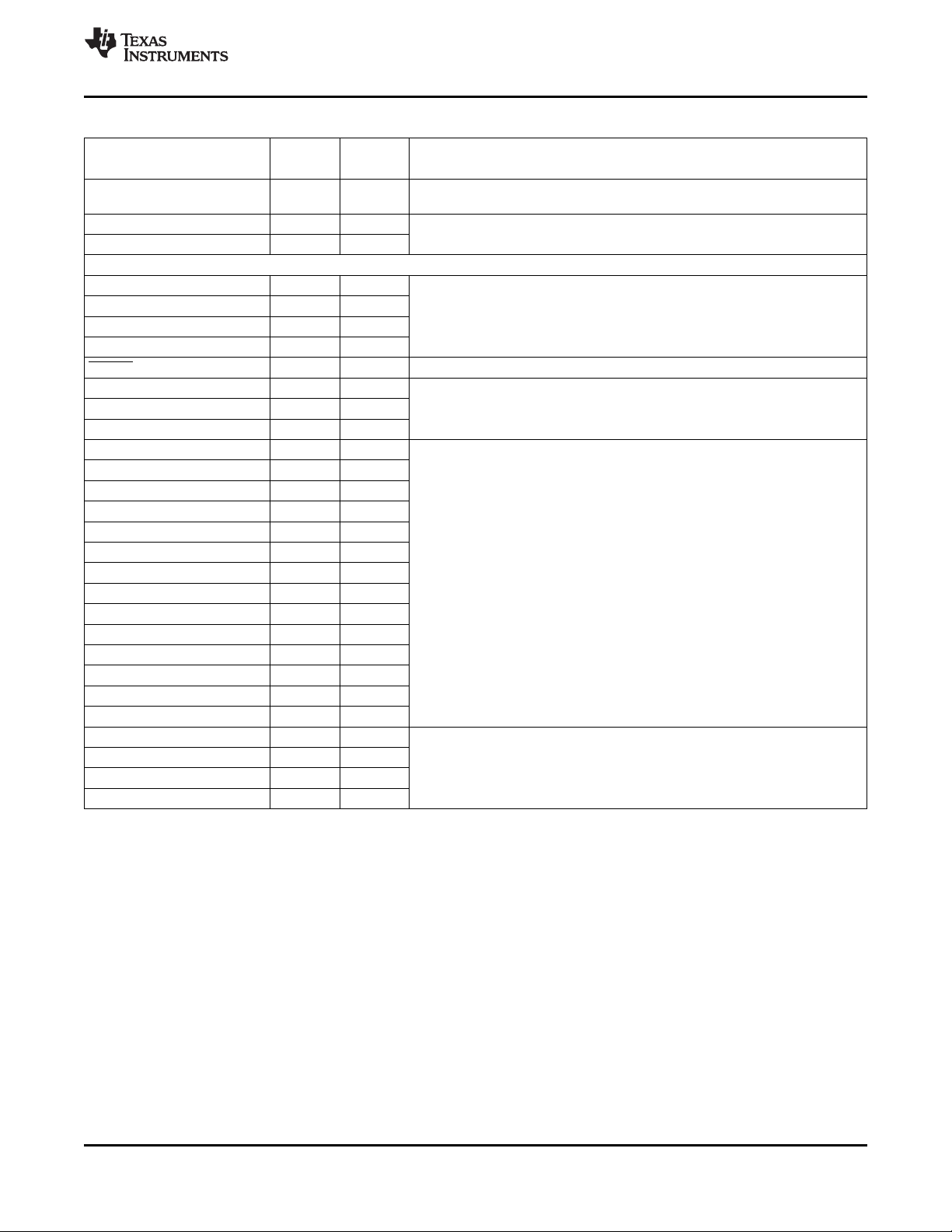

1.1 CUN/GUN/ZUN BGA Package (Bottom View)

The devices are designed for a package temperature range of 0°C to 100°C (commercial temperature

range; 1-GHz device), -40°C to 100°C (extended temperature range; 1-GHz device), 0°C to 95°C

(commercial temperature range; 850-MHz and 1.2-GHz device), and -40°C to 95°C (extended temperature

range; 1.2-GHz device). A heatsink is required so that this range is not exceeded.

NOTE

Advance Information is presented in this document for the C6474 1.2-GHz extended

temperature device.

www.ti.com

2 Features Copyright © 2008–2010, Texas Instruments Incorporated

Figure 1-1. CUN/GUN/ZUN 561-Pin BGA Package (Bottom View)

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 3

TMS320C6474

www.ti.com

1.2 Description

The TMS320C64x+ DSPs (including the TMS320C6474 device) are the highest-performance multicore

DSP generation in the TMS320C6000™ DSP platform.

The C6474 device is based on the third-generation high-performance, advanced VelociTI™

very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI).

The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™

DSP platform.

1.2.1 Core Processor

Based on 65-nm process technology and 3.6 GHz of total raw DSP processing power with performance of

up to 28,800 million instructions per second (MIPS) [or 28,800 16-bit MMACs per cycle], the C6474 device

offers cost-effective solutions to high-performance DSP programming challenges with three independent

DSP subsystems. The DSP possesses the operational flexibility of high-speed controllers and numerical

capability of array processors.

The C64x+ DSP core employs eight functional units, two register files, and two data paths. Like the earlier

C6000 devices, two of these functional units are multipliers or .M units. Each C64x+ .M unit doubles the

multiply throughput versus the C64x core by performing four 16-bit x 16-bit multiply-accumulates (MACs)

every clock cycle. Thus, eight 16-bit x 16-bit MACs can be executed every cycle on the C64x+ core. At

a1.2-GHz rate, this means 9600 16-bit MMACs can occur every microsecond. Moreover, each multiplier

on the C64x+ core can compute one 32-bit x 32-bit MAC or four 8-bit x 8-bit MACs every clock cycle.

SPRS552F–OCTOBER 2008–REVISED JULY 2010

The C6474 DSP integrates a large amount of on-chip memory organized as a three-level memory system.

The level-1 data memories on the device are 32 KB each. This memory can be configured as mapped

RAM, cache, or some combination of the two. When configured as cache, L1 program (L1P) is a

direct-mapped cache where as L1 data (L1D) is a two-way set associative cache. The level-3 (L3) ROM is

64 KB in the device. The C64x+ megamodule also has a 32-bit peripheral configuration (CFG) port, an

internal DMA (IDMA) controller, a system component with reset/boot control, and a free-running 32-bit

timer for time stamp.

The C64x+ DSP core has a complete set of development tools which includes: a new C compiler, an

assembly optimizer to simplify programming and scheduling, and a Windows® debugger interface for

visibility into source code execution.

The DMA switch fabric provides enhanced on-chip connectivity between the DSP cores and the

peripherals and accelerators.

1.2.2 Peripherals

The peripheral set includes: an inter-integrated circuit bus module (I2C); two multichannel buffered serial

ports (McBSPs) each at 100 Mbps; six 64-bit general-purpose timers (also configurable as twelve 32-bit

timers); 16 general-purpose input/output ports (GPIO) with programmable interrupt/event generation

modes; a 1000-Mbps Ethernet media access controller (EMAC), which provides an efficient interface

between the C6474 DSP core processor and the network; a management data input/output (MDIO)

module (also part of EMAC), which controls PHY configuration and status monitoring; a frame

synchronization (FSYNC) module, which synchronizes DMA transactions; a semaphore hardware block

(Semaphore), which allows access to shared resources with unique interrupts to each of the cores to

identify when that core has acquired the resource; and a 16-/32-bit DDR2 SDRAM interface.

The I2C port allows the DSP to easily control peripheral devices and communicate with a host processor.

Copyright © 2008–2010, Texas Instruments Incorporated Features 3

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 4

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

The device includes two Serial RapidIO® (SRIO) with link rates of 1.25 Gbps, 2.5 Gbps or 3.125 Gbps.

This high-bandwidth peripheral is used for point-to-point inter-device communication and may connect the

TCI6487/8 device to other DSPs, ASICs, or switches on the same board or across the backplane. This

dramatically improves system performance and reduces system cost for applications that include multiple

DSPs on a board such as video and telecom infrastructures and medical/imaging. The SRIO also provides

alarm, interrupt, and messaging events.

The device includes the SerDes-based antenna interface (AIF) capable of up to 3.072 Gbps operation per

link. The AIF comprises six high-speed serial links, compliant to OBSAI RP3 and CPRI standards. The

antenna interface is used to connect the backplane for antenna data transmission and reception. Each link

of the AIF includes a differential receive and transmit signal pair.

1.2.3 Accelerators

The device has two high-performance embedded coprocessors [enhanced Viterbi Decoder Coprocessor

(VCP2) and enhanced turbo decoder coprocessor (TCP2)] that significantly speed up channel-decoding

operations on-chip. The VCP2 operating at CPU clock divided-by-3 can decode over 694 7.95-Kbps

adaptive multi-rate (AMR) [K=9, R=1/3] voice channels. The VCP2 supports constraint lengths K = 5, 6, 7,

8, and 9, rates R = 3/4, 1/2, 1/3, and 1/5, and flexible polynomials, while generating hard decisions or soft

decisions. The TCP2 operating at CPU clock divided-by-3 can decode up to fifty 384-Kbps or eight

2-Mbps turbo encoded channels (assuming 6 iterations). The TCP2 implements the max*log-map

algorithm and is designed to support all polynomials and rates required by third-generation partnership

projects (3 GPP and 3 GPP2), with fully programmable frame length and turbo interleaver. Decoding

parameters such as the number of iterations and stopping criteria are also programmable.

Communications between the VCP2/TCP2 and the CPU are carried out through the EDMA3 controller.

www.ti.com

4 Features Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 5

DSP Subsystem 2

C64x+ Megamodule

Power Control

System

L1P Memory Controller (Memory Protect/Bandwidth Mgmt)

Instruction Fetch

EDMA 3.0

A Register File

A31 - A16

A15 - A0

B Register File

B31 - B16

B15 - B0

.L1

.S1

.M1

xx

xx

.D1

C64x+ DSP Core

Interrupt Exception Controller

L2 Memory Controller

(Memory Protect/

Bandwidth Mgmt)

Internal DMA

(DMA)

32K Bytes

L1P SRAM/Cache

Direct-Mapped

32K Bytes Total

L1D SRAM/Cache 2-Way

Set Associative

PLL1 and

PLL1 Controller

Semaphore

Power-Down and Device

Configuration Logic

L3 ROM

Boot Configuration

Sw itc he d C entra l R es ou rce ( SC R)

DDR2 Memory

Controller

PLL2

Serial RapidIO

(2x)

TCP2

VCP2

McBSP0

EMAC

10/100/1000

SGMII

MDIO

Timer [0-5]

I2C

GPIO16

FSYNC

Antenna

Interface

32

DDR2 SDRAM

L1 Data Memory Controller (Memory Protect/Bandwidth Mgmt)

DSP Subsystem 1

DSP Subsystem 0

2

McBSP1

16

.D2

.M2

xx

xx

.S2

.L2

16-/32-bit

Instruction Dispatch

Instruction Decode

Control Registers

SPLOOP Buffer

In-Circuit Emulation

www.ti.com

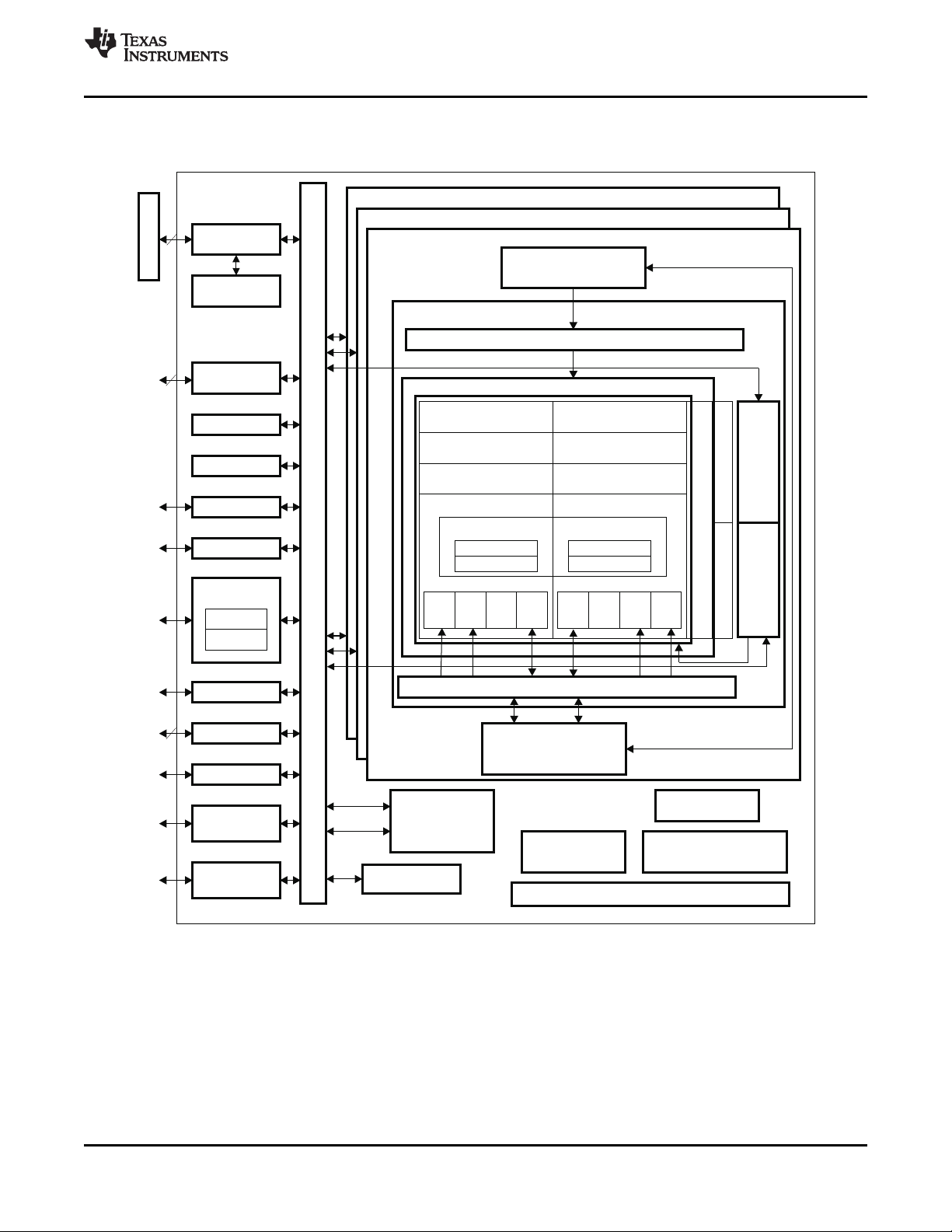

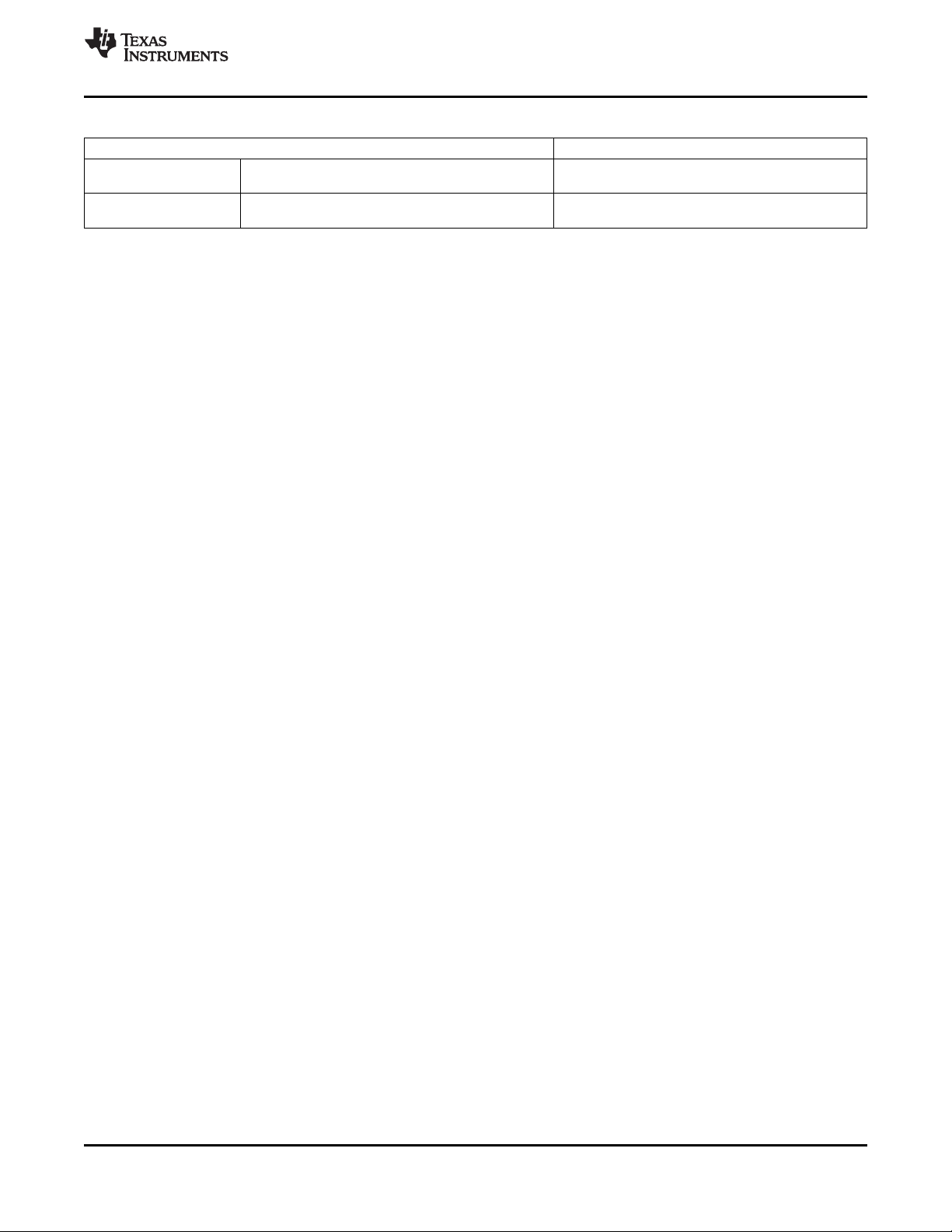

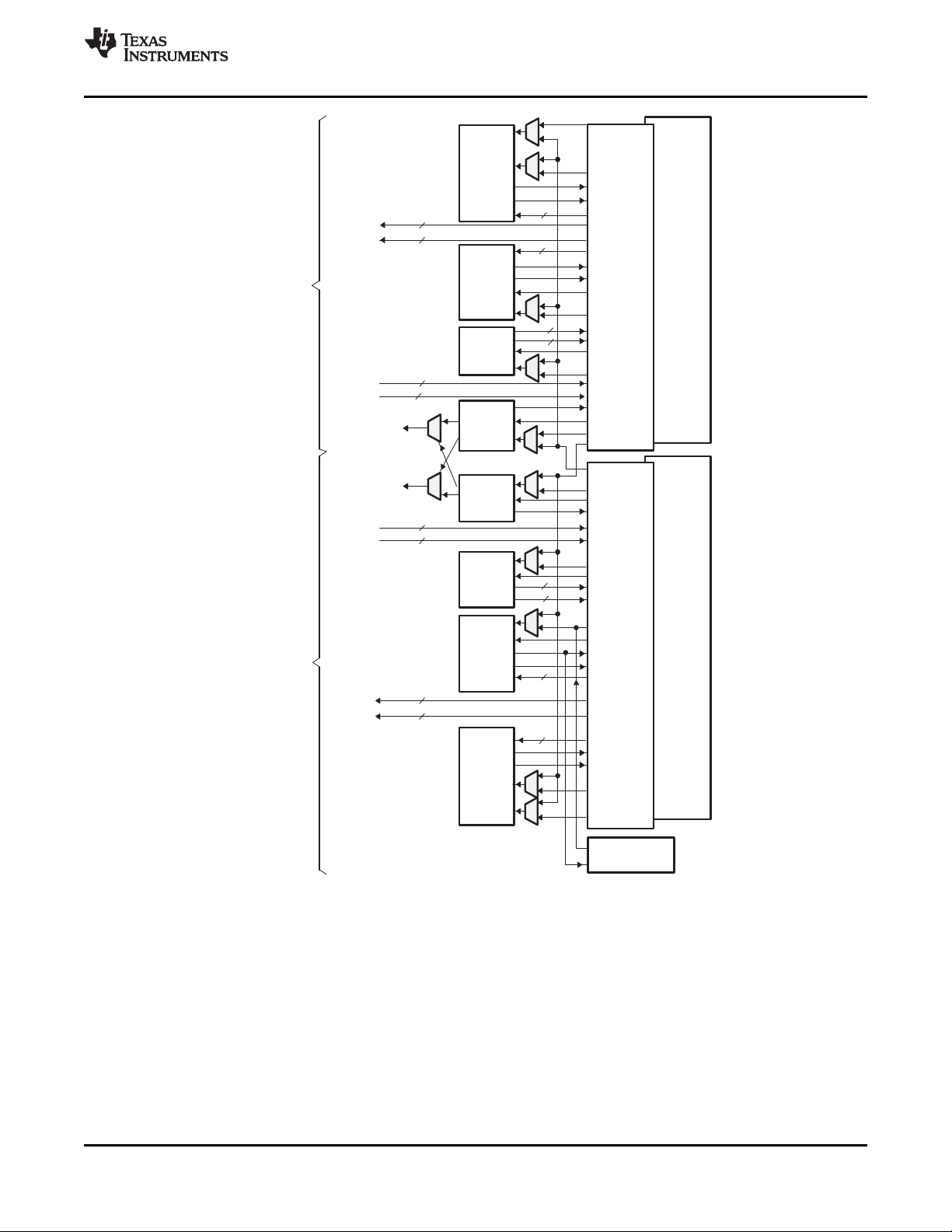

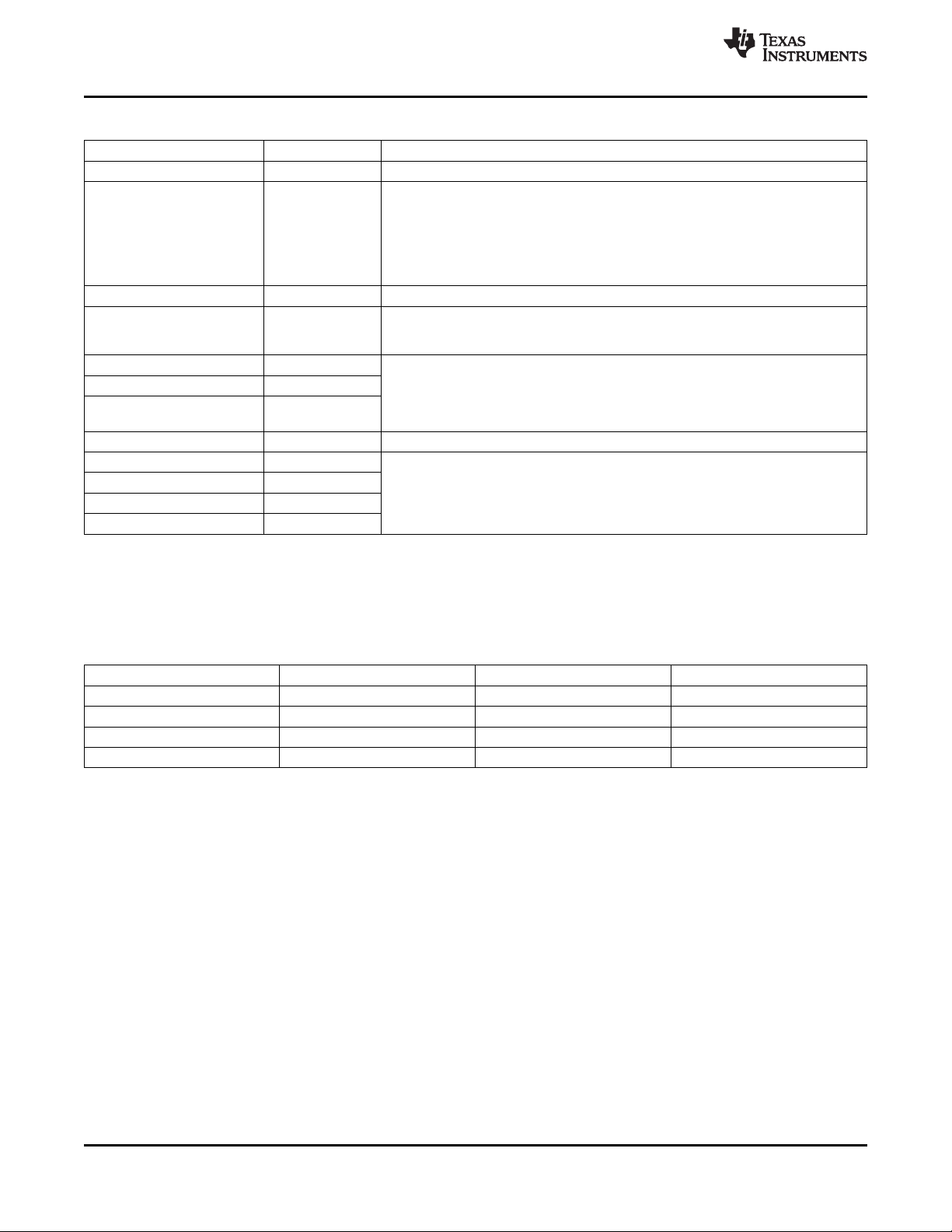

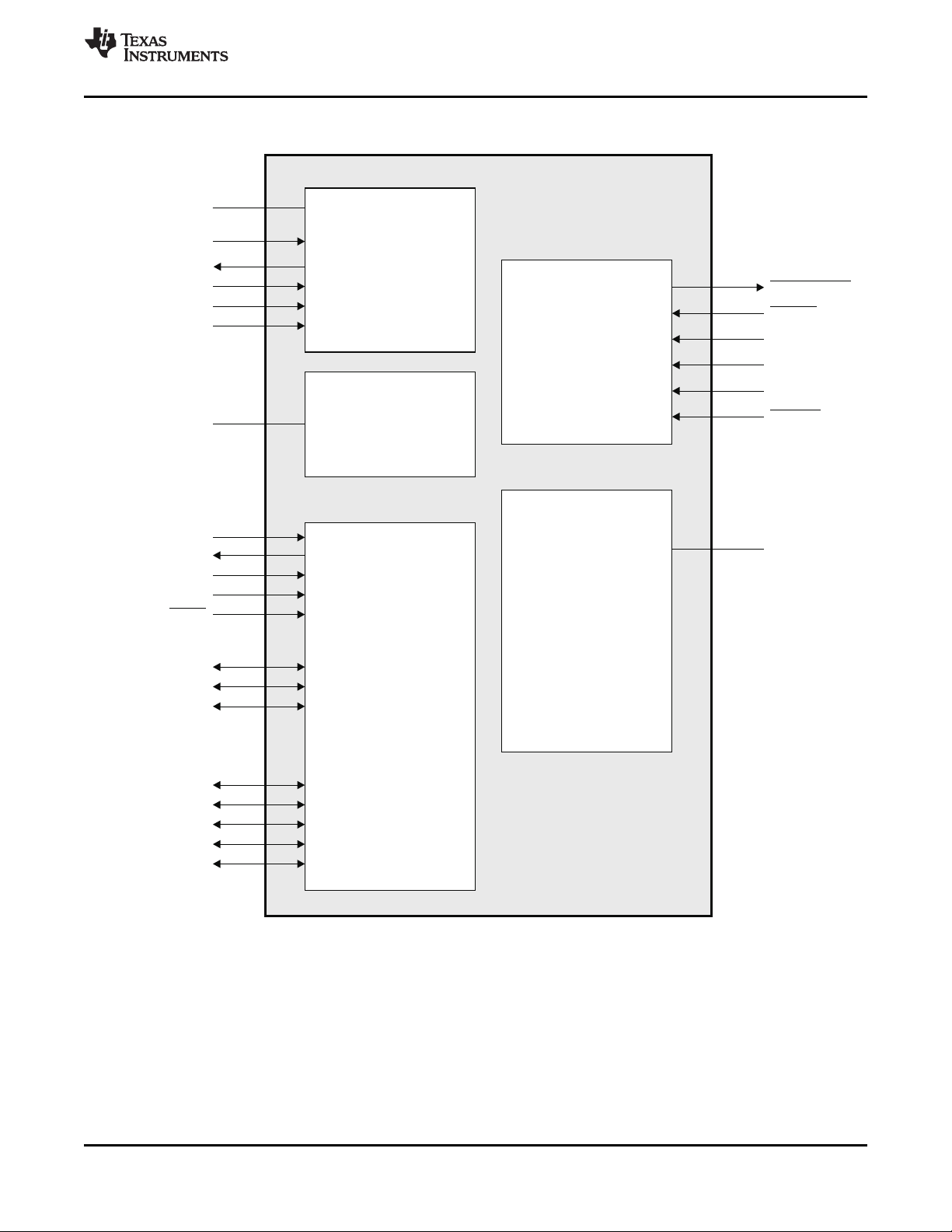

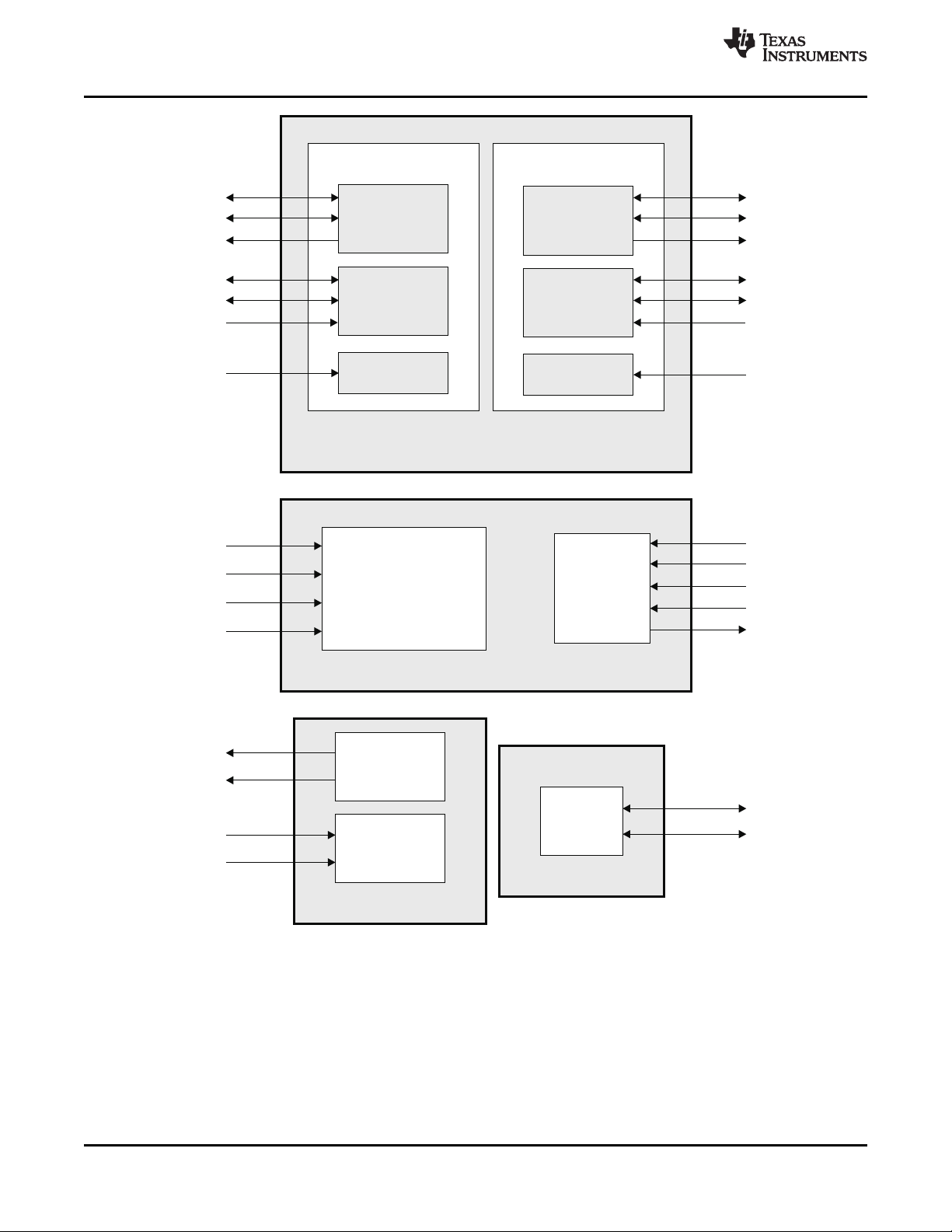

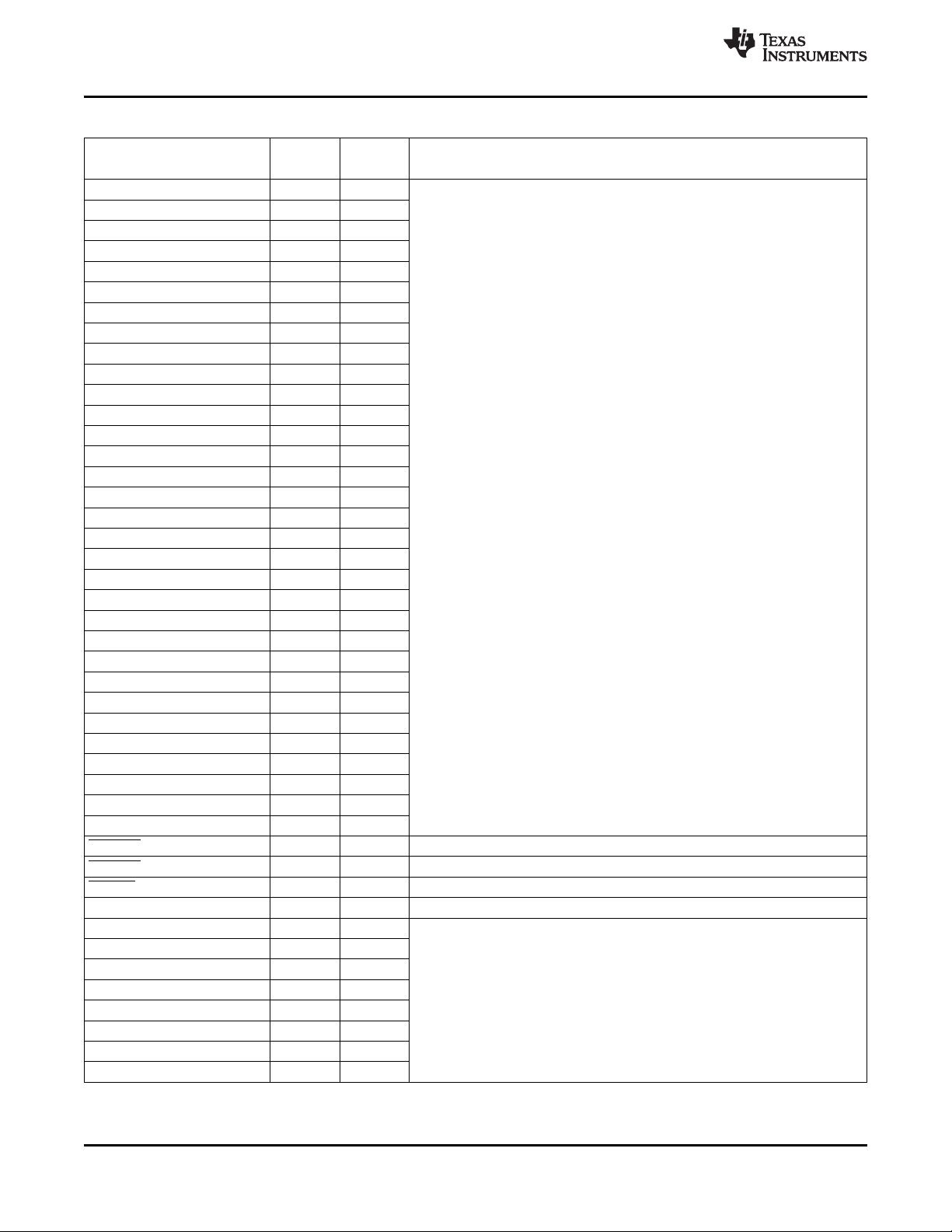

1.3 C6474 Functional Block Diagram

Figure 1-2 shows the functional block diagram of the C6474 device.

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Figure 1-2. Functional Block Diagram

Copyright © 2008–2010, Texas Instruments Incorporated Features 5

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 6

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

www.ti.com

1 Features ................................................... 1

1.1 CUN/GUN/ZUN BGA Package (Bottom View) ....... 2

1.2 Description ........................................... 3

1.3 C6474 Functional Block Diagram .................... 5

Revision History .............................................. 7

2 Device Overview ........................................ 8

2.1 Device Characteristics ............................... 8

2.2 CPU (DSP Core) Description ........................ 9

2.3 Memory Map Summary ............................. 12

2.4 Boot Sequence ..................................... 15

2.5 Pin Assignments .................................... 17

2.6 Signal Groups Description .......................... 21

2.7 Terminal Functions ................................. 26

2.8 Development ........................................ 41

3 Device Configuration ................................. 45

3.1 Device Configuration at Device Reset .............. 45

3.2 Peripheral Selection After Device Reset ........... 45

3.3 Device State Control Registers ..................... 46

3.4 Device Status Register Descriptions ............... 47

3.5 Inter-DSP Interrupt Registers (IPCGR0-IPCGR2

and IPCAR0-IPCAR2) .............................. 49

3.6 JTAG ID (JTAGID) Register Description ........... 50

3.7 Debugging Considerations ......................... 50

4 System Interconnect .................................. 51

4.1 Internal Buses, Switch Fabrics, and

Bridges/Gaskets .................................... 51

4.2 Data Switch Fabric Connections ................... 52

4.3 Configuration Switch Fabric ........................ 55

4.4 Priority Allocation ................................... 57

5 C64x+ Megamodule ................................... 58

5.1 Megamodule Diagram .............................. 58

5.2 Memory Architecture ............................... 59

5.3 Memory Protection ................................. 61

5.4 Bandwidth Management ............................ 62

5.5 Power-Down Control ............................... 63

5.6 Megamodule Resets ................................ 63

5.7 Megamodule Revision .............................. 63

5.8 C64X+ Megamodule Register Description(s) ....... 64

6 Device Operating Conditions ....................... 72

6.1 Absolute Maximum Ratings Over Operating Case

Temperature Range (Unless Otherwise Noted) .... 72

6.2 Recommended Operating Conditions .............. 73

6.3 Electrical Characteristics Over Recommended

Ranges of Supply Voltage and Operating Case

Temperature (Unless Otherwise Noted) ............ 74

7 Peripheral Information and Electrical

Specifications .......................................... 75

7.1 Parameter Information .............................. 75

7.2 Recommended Clock and Control Signal Transition

Behavior ............................................ 76

7.3 Power Supplies ..................................... 76

7.4 Peripheral IDs (PIDs) ............................... 79

7.5 Enhanced Direct Memory Access (EDMA3)

Controller ........................................... 80

7.6 Interrupts .......................................... 104

7.7 Reset Controller ................................... 112

7.8 PLL1 and PLL1 Controller ......................... 117

7.9 PLL2 and PLL2 Controller ......................... 130

7.10 DDR2 Memory Controller ......................... 132

7.11 I2C Peripheral ..................................... 135

7.12 Multichannel Buffered Serial Port (McBSP) ....... 140

7.13 Ethernet MAC (EMAC) ............................ 149

7.14 Management Data Input/Output (MDIO) .......... 156

7.15 Timers ............................................. 158

7.16 Enhanced Viterbi-Decoder Coprocessor (VCP2)

..................................................... 167

7.17 Enhanced Turbo Decoder Coprocessor (TCP2)

..................................................... 169

7.18 Serial RapidIO (SRIO) Port ....................... 171

7.19 General Purpose Input/Output (GPIO) ............ 183

7.20 Emulation Features and Capability ............... 184

7.21 Semaphore ........................................ 188

7.22 Antenna Interface Subsystem ..................... 191

7.23 Frame Synchronization ............................ 203

8 Mechanical Data ...................................... 207

8.1 Thermal Data ...................................... 207

8.2 Packaging Information ............................ 207

6 Contents Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 7

TMS320C6474

www.ti.com

Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

This data manual revision history highlights the technical changes made to the data manual in this

revision.

Scope: Applicable updates to the C64x device family, specifically relating to the TMS320C6474 device,

have been incorporated.

C6474 Revision History

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Section 7.3.1 Power-Supply Sequencing:

Added Footnote (1) to Table 7-1, Timing Requirements for Power Supply Ramping

Modified Figure 7-4, Power-Supply Timing

Section 7.7.2 Warm Reset:

Added last paragraph

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Copyright © 2008–2010, Texas Instruments Incorporated Contents 7

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 8

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

2 Device Overview

2.1 Device Characteristics

Table 2-1 provides an overview of the C6474 DSP. The tables show significant features of the C6474

device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type

with pin count.

Table 2-1. Characteristics of the C6474 Processor

HARDWARE FEATURES C6474

Peripherals DDR2 Memory Controller (32-bit bus width) [1.8 V I/O]

Not all peripherals pins (clock memory = DDRREFCLK(N|P)

are available at the same

time.

(For more detail, see

Section 3, Device

Configuration)

Decoder Coprocessors VCP2 (clock source = CPU/3 clock frequency) 1

On-Chip Memory Size (Bytes) 3200 KB

CPU Megamodule Revision ID Register

Revision ID (MM_REVID. [15:0]) 0x0181 2000)

JTAG Device_ID JTAG Register (address location: 0x0288 0814) For details, see Section 3.6

Frequency MHz 850 - 1200 (850 MHz to 1.2 GHz)

Cycle Time ns 1.18 ns - 0.83 ns (850 MHz to 1.2 GHz CPU)

Voltage Core (V) 0.9-V to 1.2-V SmartReflex

PLL1 and PLL1 Controller CLKIN1 Frequency Multiplier

Options

PLL2 DDR Clock X10

BGA Package 23 X 23 mm 561-Pin Flip-Chip with BGA CUN/GUN/ZUN

Process Technology mm 0.065 mm

(1) A heatsink and implementation of the SmartReflex solution is required for proper device operation. For more details on SmartReflex, see

Section 7.3.4.

EDMA3 (64 independent channels [CPU/3 clock rate] 1

High-speed 1x Serial RapidIO Port (2 lanes) 1

I2C 1

McBSPs

(internal or external clock source up to 100 Mbps)

1000 Ethernet MAC (EMAC) 1

Management Data Input/Output (MDIO) 1

Antenna Interface (AIF) 1

Frame Synchronization (FSYNC) 1

64-bit Timers (Configurable)

(internal clock source CPU/6 clock frequency)

SYSCLKOUT 1

General Purpose Input/Output Port (GPIO) 16

TCP2 (clock source = CPU/3 clock frequency) 1

Organization 32KB L1P Program Cache (SRAM/Cache)

32KB L1D Data Cache (SRAM/Cache)

3072KB Total L2 Unified Memory SRAM/Cache

I/O (V) 1.8 V, 1.1 V

6 64-bit or 12 32-bit

32KB Data Memory Controller

Bypass (x1), (x4 to x32)

1

2

64KB L3 ROM

0x0

(1)

www.ti.com

1.1 V

8 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 9

TMS320C6474

www.ti.com

Table 2-1. Characteristics of the C6474 Processor (continued)

HARDWARE FEATURES C6474

Product Status

Device Part Numbers (For more details on C64x+ DSP part numbering, see

(1) PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas

Instruments standard warranty. Production processing does not necessarily include testing of all parameters. Note: Advance Information

is presented in this document for the C6474 1.2-GHz extended temperature device.

(1)

Product Preview (PP), Advance Information (AI), or

Production Data (PD)

Figure 2-11)

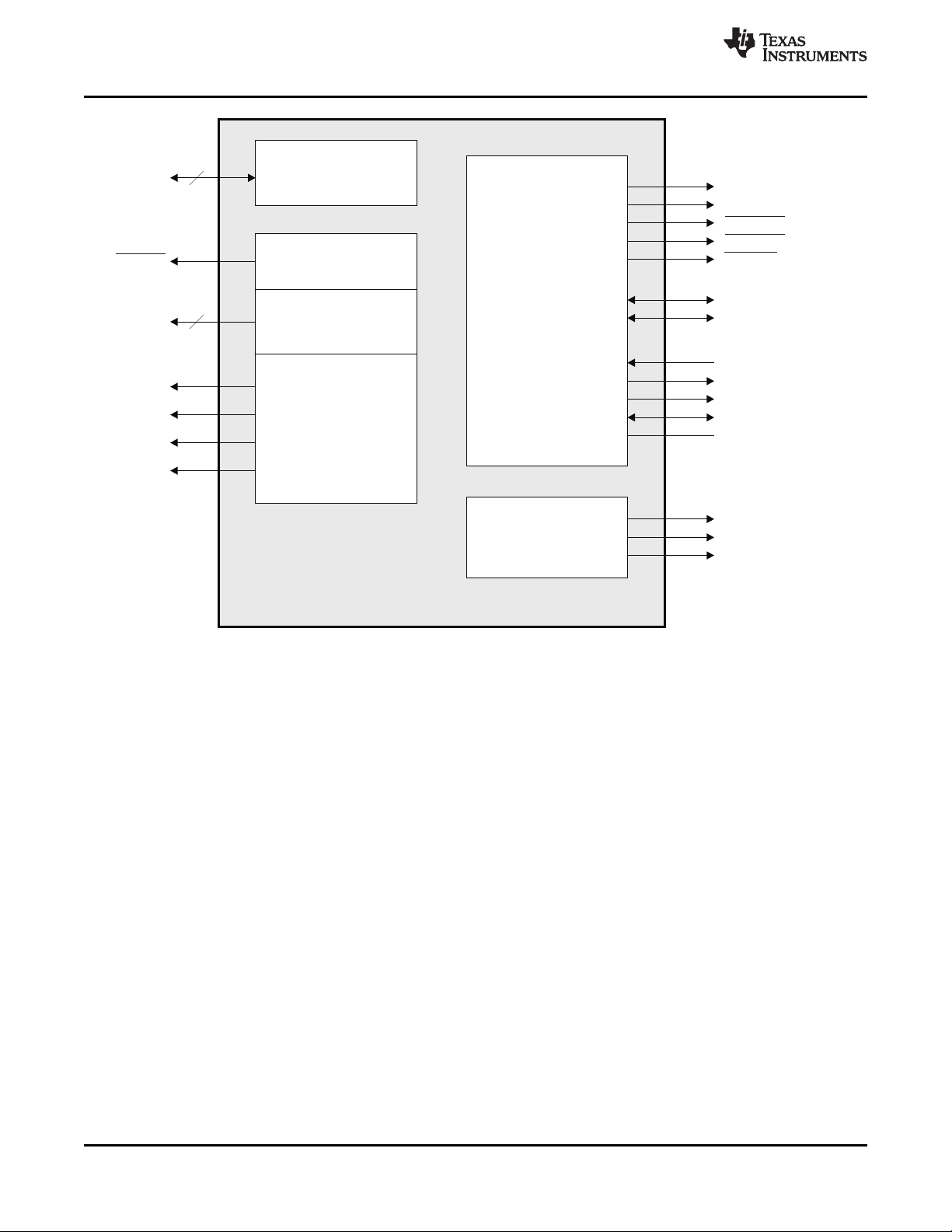

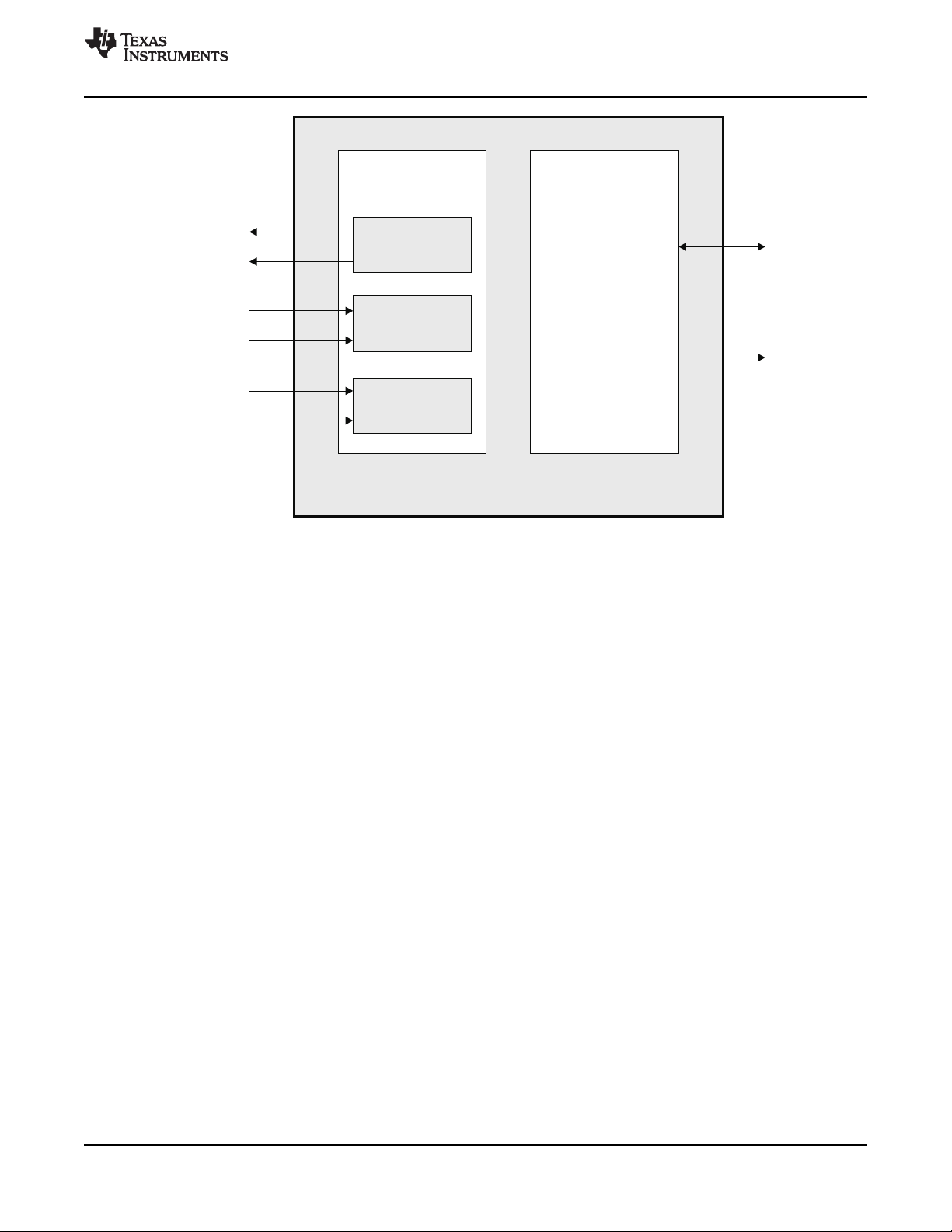

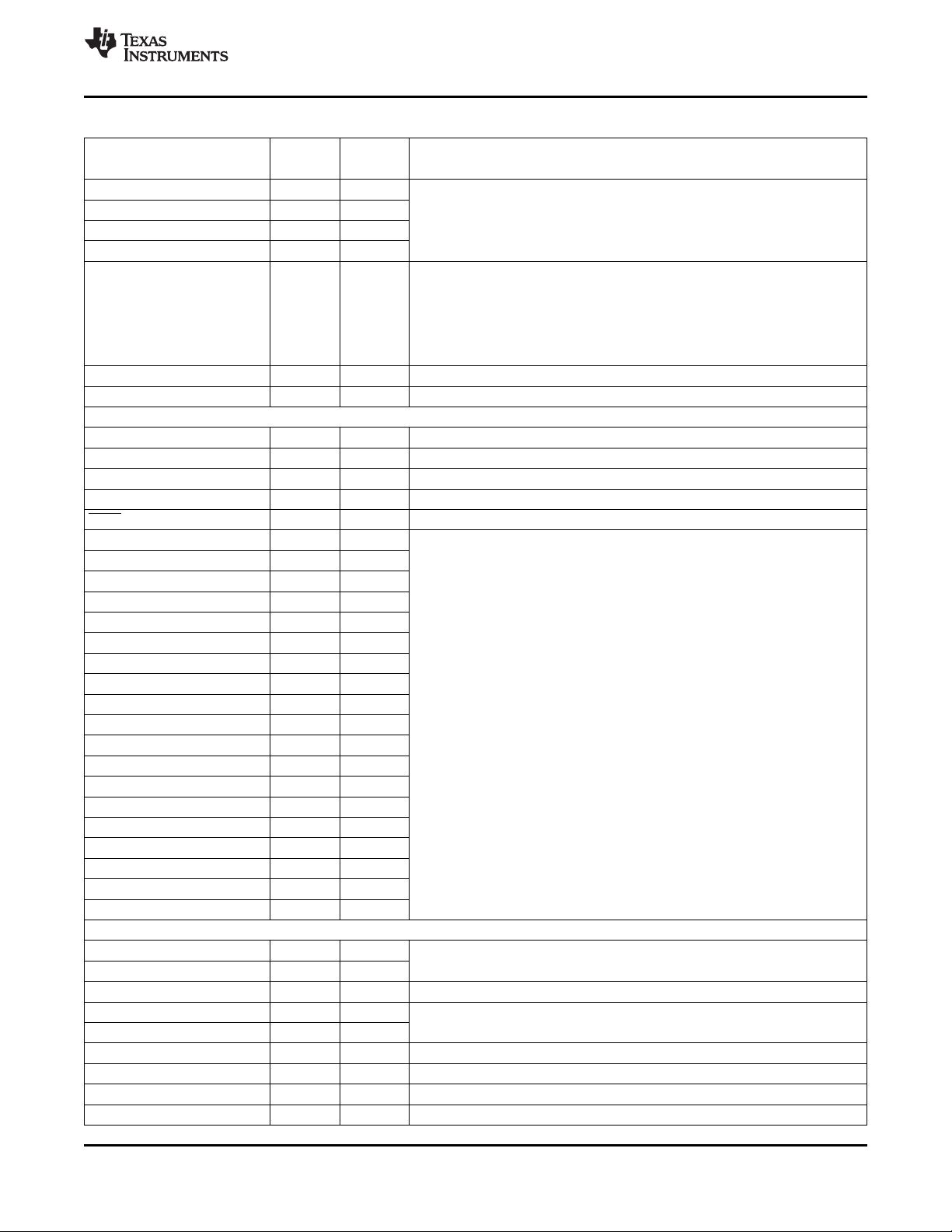

2.2 CPU (DSP Core) Description

The C64x+ central processing unit (CPU) consists of eight functional units, two register files, and two data

paths as shown in Figure 2-1. The two general-purpose register files (A and B) each contain 32 (thirty-two)

32-bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be

data address pointers. The data types supported include packed 8-bit data, 32-bit data, 40-bit data, and

64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are stored in register

pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or 32 MSBs in the next

upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

SPRS552F–OCTOBER 2008–REVISED JULY 2010

PD

TMS320C6474CUN/GUN/ZUN

The C64x+ CPU extends the performance of the C64x core through enhancements and new features.

Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, two 16 x

16 bit multiplies, two 16 x 32 bit multiplies, four 8 x 8 bit multiplies, four 8 x 8 multiplies with add

operations and four 16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There

is also support for Galois filed multiplication for 8-bit and 32-bit data. Many communications algorithms

such FFTs and modems require complex multiplication. The complex multiply (CMPY) instruction takes

four 16-bit inputs and produces a 32-bit real and a 32-bit imaginary output. There are also complex

multiplies with rounding capability that produces one 32-bit packed output that contain 16-bit real and

16-bit imaginary values. The 32 x 32 bit multiply instructions provide the extended precision necessary for

audio and other high-precision algorithms on a variety of signed and unsigned 32-bit data types.

The .L or arithmetic logic unit now incorporates the ability to do parallel add/subtract operations on a pair

of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2

comparisons were only available on the .L units. On the C64X+ core, they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Other new features include:

• SPLOOP - a small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

• Compact Instructions - The native instruction size of the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 9

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 10

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

• Instruction Set Enhancements - As noted above, there are new instructions such as 32-bit

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

• Exception Handling - Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to

detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and

from system events (such as watchdog time expiration).

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

• Time-Stamp Counter - Primarily targeted for real-time operating system (RTOS) robustness, a

free-running time-stamp counter is implemented in the CPU that is not sensitive to system stalls.

For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732)

• TMS320C64x+ DSP Cache User's Guide (literature number SPRU862)

• TMS320C64x+ Megamodule Reference Guide (literature number SPRU871)

• TMS320C64X to TMS320C64x+ CPU Migration Guide (literature number SPRAA84)

www.ti.com

10 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 11

src2

src2

.D1

.M1

.S1

.L1

longsrc

odddst

src2

src1

src1

src1

src1

evendst

evendst

odddst

dst1

dst

src2

src2

src2

longsrc

DA1

ST1b

LD1b

LD1a

ST1a

Datapath A

Odd

register

fileA

(A1, A3,

A5...A31)

Odd

register

fileB

(B1,B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

evendst

longsrc

odddst

ST2a

ST2b

longsrc

.L2

evendst

odddst

src1

Data pathB

Control Register

32MSB

32LSB

dst2

(A)

32MSB

32LSB

2x

1x

32LSB

32MSB

32LSB

32MSB

dst2

(B)

(B)

(A)

8

8

8

8

32

32

32

32

(C)

(C)

Even

register

file A

(A0, A2,

A4...A30)

Even

register

fileB

(B0,B2,

B4...B30)

(D)

(D)

(D)

(D)

www.ti.com

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

A. On .M unit, dst2 is 32 MB.

B. On .M unit, dst1 is 32 LSB.

C. On 64x+ CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 11

Figure 2-1. TMS320C64x+TM CPU (DSP Core) Data Path

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 12

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

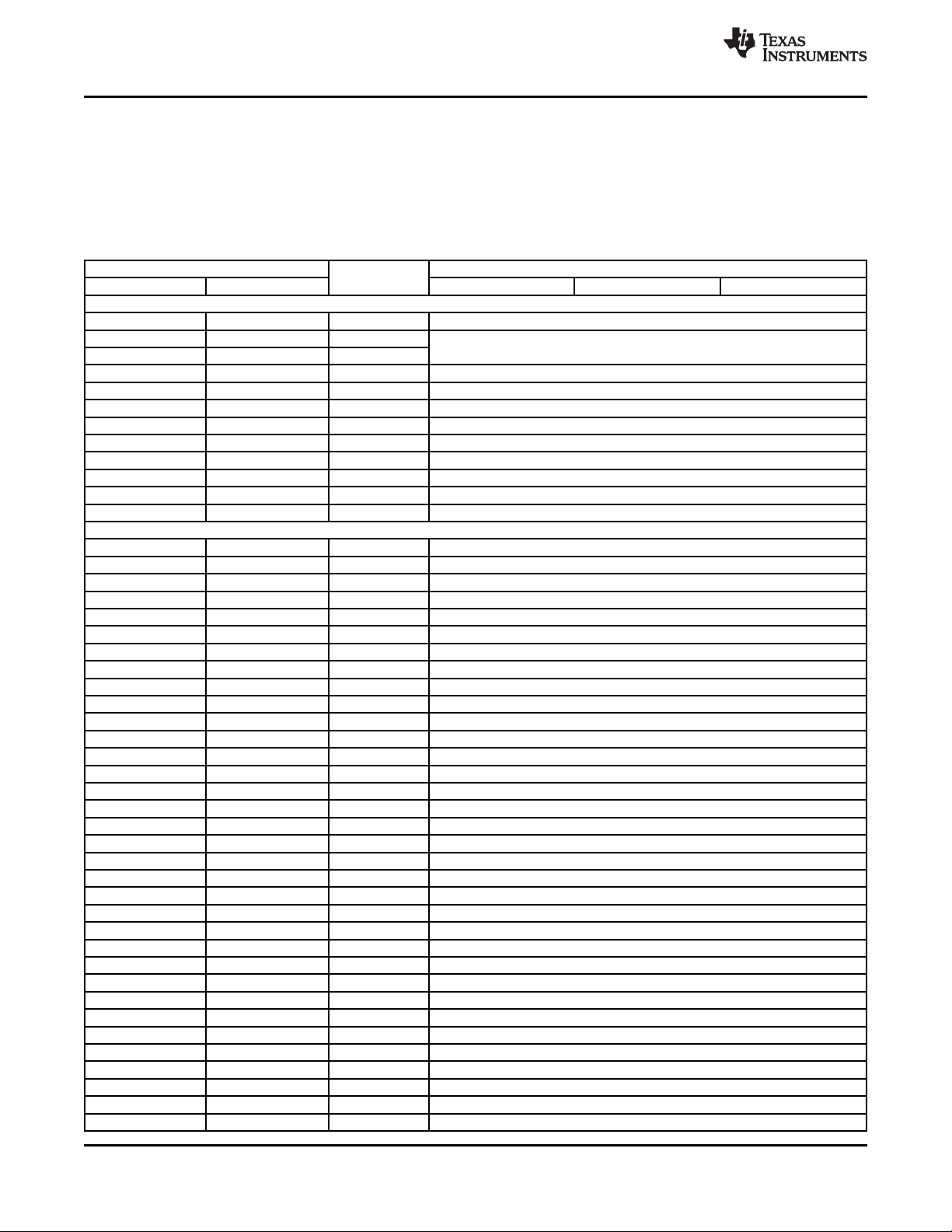

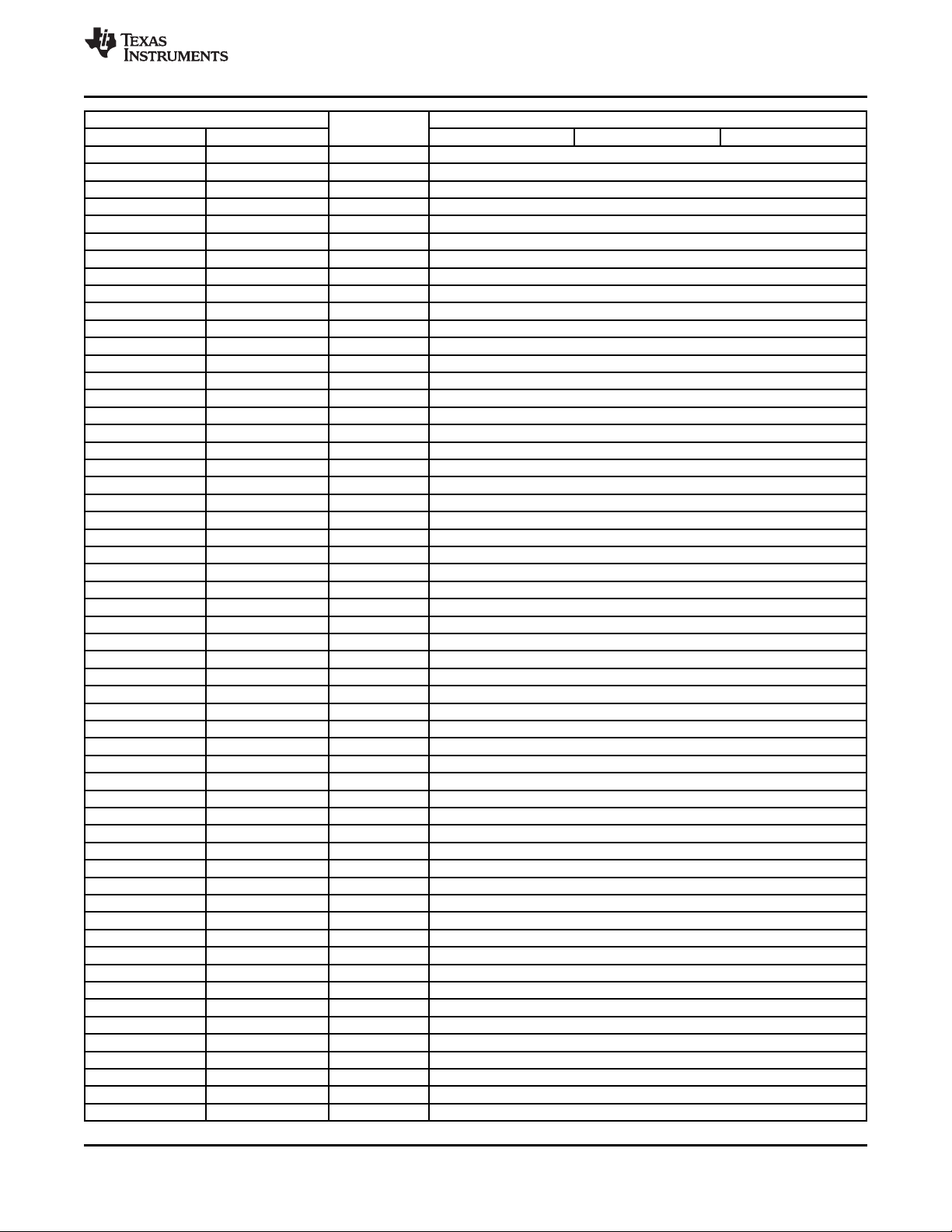

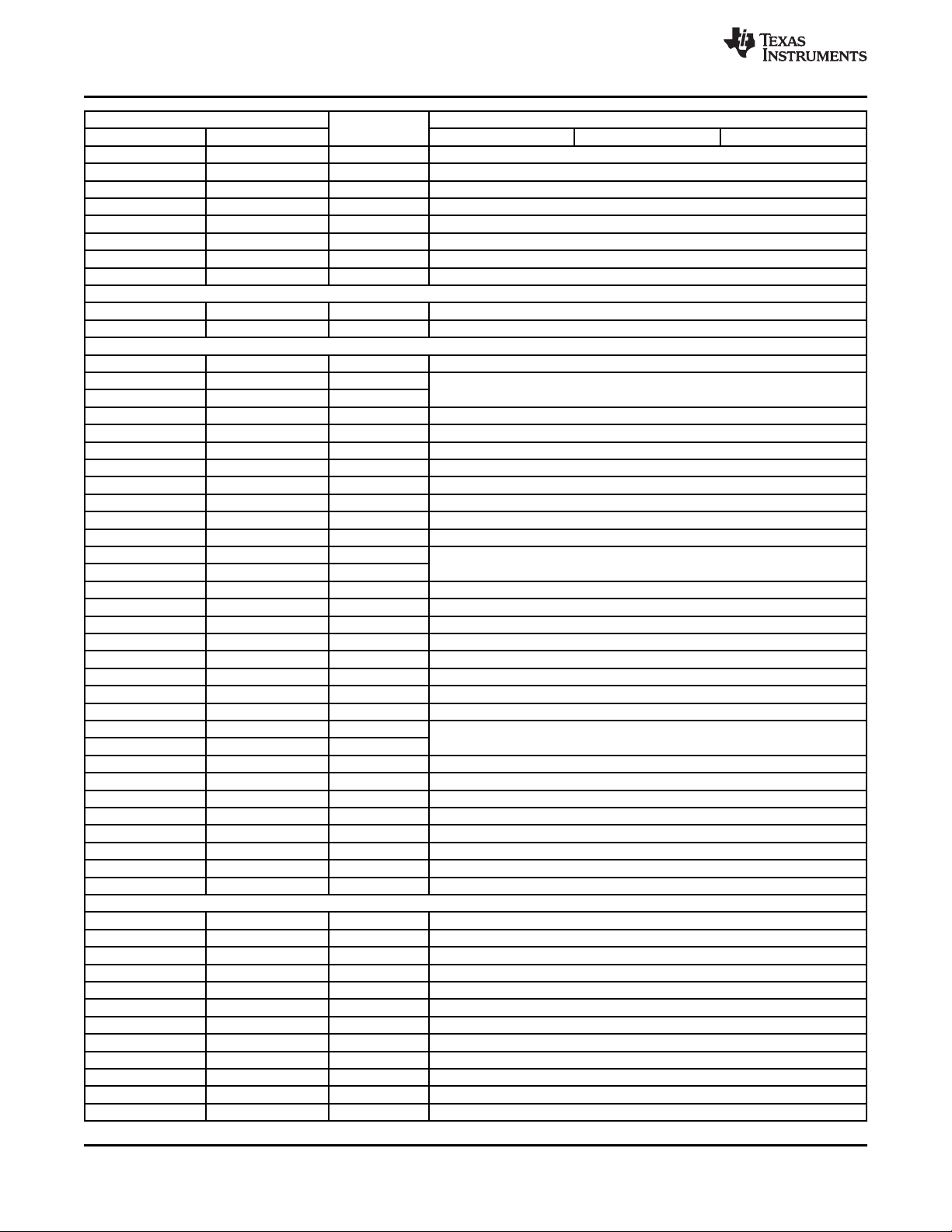

2.3 Memory Map Summary

Table 2-2 shows the memory map address of the C6474 device. For more information about the registers

in these address ranges, click on the links in the table. The external memory configuration register

address ranges in the C6474 device begin at the hex address location 0x7000 for DDR2 Memory

Controller.

Table 2-2. Memory Map Summary

HEX ADDRESS RANGE MEMORY BLOCK DESCRIPTION

START END C64x+ MEGAMODULE CORE0 C64x+ MEGAMODULE CORE1 C64x+ MEGAMODULE CORE 2

0000 0000 007F FFFF 8M Reserved

0080 0000 0087 FFFF 512K

0088 0000 008F FFFF 512K

009 00000 0097 FFFF 512K Reserved

0098 0000 009F FFFF 512K Reserved

00A0 0000 00DF FFFF 4M Reserved

00E0 0000 00E0 7FFF 32K L1PSRAM

00E0 8000 00EF FFFF 1M - 32K Reserved

00F0 0000 00F0 7FFF 32K L1D SRAM

00F0 8000 00FF FFFF 1M - 32K Reserved

0100 0000 01BF FFFF 4M C64x+ Megamodule Registers

01C0 0000 027F FFFF 12.5M Reserved

0280 0000 0280 03FF 1K Frame Synchronization (FSYNC)

0280 0400 0287 FFFF 511K Reserved

0288 0000 0288 00FF 256 Chip Interrupt Controller0 (CIC0)

0288 0100 0288 01FF 256 Chip Interrupt Controller1 (CIC1)

0288 0200 0288 02FF 256 Chip Interrupt Controller2 (CIC2)

0288 0300 0288 03FF 256 Chip Interrupt Controller3 (CIC3)

0288 0400 0288 0403 4 DSP Trace Formatter1 (DTF1)

0288 0404 0288 0407 4 DSP Trace Formatter2 (DTF2)

0288 0408 0288 040B 4 DSP Trace Formatter3 (DTF3)

0288 040C 0288 07FF 1K- 6 Reserved

0288 0800 0288 0BFF 1K CFGC

0288 0900 0288 0903 4B IPCGR0

0288 0904 0288 0907 4B IPCGR1

0288 0908 0288 090B 4B IPCGR2

0288 090C 0288 093F 52B Reserved

0288 0940 0288 0943 4B IPCAR0

0288 0944 0288 0947 4B IPCAR1

0288 0948 0288 094B 4B IPCAR2

0288 0C00 028B FFFF 253K Reserved

028C 0000 028C 00FF 256 McBSP0

028C 0100 028C FFFF 64K - 256 Reserved

028D 0000 208D 00FF 256 McBSP1

028D 0100 028D FFFF 64K - 256 Reserved

028E 0000 028F FFFF 128K Reserved

0290 0000 0290003F 64 Timer Pin Manager (TPMGR)

0290 0040 0290 FFFF 64K - 64 Reserved

0291 0000 0291003F 64 Timer0

0291 0040 0291 FFFF 64K - 64 Reserved

0292 0000 0292003F 64 Timer1

0292 0040 0292 FFFF 64K - 64 Reserved

0293 0000 0293003F 64 Timer2

0293 0040 0293 FFFF 64K - 64 Reserved

0294 0000 0294003F 64 Timer3

0294 0040 0294 FFFF 64K - 64 Reserved

SIZE

Internal RAM

L2 SRAM

Control Registers onCFG SCR

www.ti.com

12 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 13

www.ti.com

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

HEX ADDRESS RANGE MEMORY BLOCK DESCRIPTION

START END C64x+ MEGAMODULE CORE0 C64x+ MEGAMODULE CORE1 C64x+ MEGAMODULE CORE 2

0295 0000 0295003F 64 Timer4

0295 0040 0295 FFFF 64K - 64 Reserved

0296 0000 0296003F 64 Timer5

0296 0040 0296 FFFF 256K - 64 Reserved

029A 0000 029A 01FF 512 PLLController 1 (Main)

029A 0200 029B FFFF 128K - 512 Reserved

029C 0000 029C 01FF 512 Reserved

029C 0200 029C 02FF 256K - 512 Reserved

02A0 0000 02A0 7FFF 32K EDMA3 Channel Controller(TPCC)

02A0 8000 02A1 FFFF 96K Reserved

02A2 0000 02A2 7FFF 32K EDMA3 Transfer Controller0 (TPTC0)

02A2 8000 02A2 FFFF 32K EDMA3 Transfer Controller 1 (TPTC1)

02A3 0000 02A3 7FFF 32K EDMA3 Transfer Controller2 (TPTC2)

02A3 8000 02A3 FFFF 32K EDMA3 Transfer Controller 3 (TPTC3)

02A4 0000 02A4 7FFF 32K EDMA3 Transfer Controller4 (TPTC4)

02A4 8000 02A4 FFFF 32K EDMA3 Transfer Controller 5 (TPTC5)

02A5 0000 02A7 FFFF 192K Reserved

02A8 0000 02A8 00FF 256 Reserved

02A8 0100 02AB FFFF 256K -256 Reserved

02AC 0000 02AC 0FFF 4K Power/Sleep Controller (PSC)

02AC 1000 02AC 3FFF 12K Reserved

02AC 4000 02AC 40FF 256 Reserved

02AC 4100 02AC FFFF 48K - 256 Reserved

02AD 0000 02AD 7FFF 32K Embedded Trace Buffer0 (ETB0)

02AD 8000 02AD FFFF 32K Embedded TraceBuffer 1 (ETB1)

02AE 0000 02AE 7FFF 32K Embedded Trace Buffer 2 (ETB2)

02AE 8000 02AF FFFF 96K Reserved

02B0 0000 02B0 00FF 256 GPIO

02B0 0100 02B0 1FFF 8K - 256 Reserved

02B0 2000 02B0 23FF 1K Reserved

02B0 2400 02B0 3FFF 7K Reserved

02B0 4000 02B0 407F 128 I2C Data andControl

02B0 4080 02B3 FFFF 256K - 128 Reserved

02B4 0000 02B4 07FF 2K Semaphore

02B4 0800 02B7 FFFF 254K Reserved

02B8 0000 02B8 00FF 256 VCP2 Control

02B8 0100 02B8 FFFF 128K - 256 Reserved

02BA 0000 02BA 00FF 256 TCP2 Control

02BA 0100 02BB FFFF 128K - 256 Reserved

02BC 0000 02BF FFFF 256K Antenna Interface Control

02C0 0000 02C0 03FF 1K Reserved

02C0 0400 02C3 FFFF 255K Reserved

02C4 0000 02C4 00FF 256 SMGII Control

02C4 0100 02C7 FFFF 256K - 256 Reserved

02C8 0000 02C8 07FF 2K EMAC Control

02C8 0800 02C8 0FFF 2K Reserved

02C8 1000 02C8 10FF 256 EMAC Interrupt Controller

02C8 1100 02C8 17FF 2K - 256 Reserved

02C8 1800 02C8 18FF 256 MDIO

02C8 1900 02C8 FFFF 2K- 256 Reserved

02C8 2000 02C8 3FFF 8K EMAC Descriptor Memory

02C8 4000 02CF FFFF 496K Reserved

02D0 0000 02D2 0FFF 132K RapidIO

02D2 1000 02D3 FFFF 124K Reserved

02D4 0000 02D7 FFFF 256K Reserved

02D8 0000 02DB FFFF 256K Reserved

SIZE

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 13

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 14

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

www.ti.com

HEX ADDRESS RANGE MEMORY BLOCK DESCRIPTION

START END C64x+ MEGAMODULE CORE0 C64x+ MEGAMODULE CORE1 C64x+ MEGAMODULE CORE 2

02DC 0000 02DF FFFF 256K Reserved

02E0 0000 02E0 3FFF 16K RapidIO Descriptor Memory

02E0 4000 02EF FFFF 1M - 16K Reserved

02F0 0000 02F0 FFFF 64K Reserved

02F1 0000 02F1 FFFF 64K Reserved

02F2 0000 02F3 FFFF 128K Reserved

02F4 0000 02F5 FFFF 128K Reserved

02F6 0000 02FF FFFF 576K Reserved

0300 0000 03FF FFFF 16M Reserved

0400 0000 0FFF FFFF 192M Reserved

1000 0000 107F FFFF 8M Reserved

1080 0000 1087 FFFF 512K

1088 0000 108F FFFF 512K

1090 0000 1097 FFFF 512K Reserved

1098 0000 109F FFFF 512K Reserved

10A0 0000 10DF FFFF 4M Reserved

10E0 0000 10E0 7FFF 32K C64x+ Megamodule Core0 L1P SRAM

10E0 8000 10EF FFFF 1M - 32K Reserved

10F0 0000 10F0 7FFF 32K C64x+ Megamodule Core 0 L1D SRAM

10F0 8000 10FF FFFF 1M - 32K Reserved

1100 0000 117F FFFF 8M Reserved

1180 0000 1187 FFFF 512K

1188 0000 118F FFFF 512K

1190 0000 1197 FFFF 512K Reserved

1198 0000 119F FFFF 512K Reserved

11A0 0000 11DF FFFF 4M Reserved

11E0 0000 11E0 7FFF 32K C64x+ Megamodule Core1 L1P SRAM

11E0 8000 11EF FFFF 1M - 32K Reserved

11F0 0000 11F0 7FFF 32K C64x+ Megamodule Core 1 L1D SRAM

11F0 8000 11FF FFFF 1M - 32K Reserved

1200 0000 127F FFFF 8M Reserved

1280 0000 1287 FFFF 512K

1288 0000 128F FFFF 512K

1290 0000 1297 FFFF 512K Reserved

1298 0000 129F FFFF 512K Reserved

12A0 0000 12DF FFFF 4M Reserved

12E0 0000 12E0 7FFF 32K C64x+ Megamodule Core2 L1P SRAM

12E0 8000 12EF FFFF 1M - 32K Reserved

12F0 0000 12F0 7FFF 32K C64x+ Megamodule Core 2 L1D SRAM

12F0 8000 12FF FFFF 1M - 32K Reserved

1300 0000 1FFF FFFF 208M Reserved

2000 0000 2FFF FFFF 256M Reserved

3000 0000 3000 00FF 256 McBSP0 Data

3000 0100 33FF FFFF 64M - 256 Reserved

3400 0000 3400 00FF 256 McBSP1 Data

3400 0100 3BFF FFFF 128M - 256 Reserved

3C00 0000 3C00 FFFF 64K L3 ROM

3C01 0000 3FFF FFFF 64M - 64K Reserved

4000 0000 4FFF FFFF 256M Reserved

5000 0000 500F FFFF 1M TCP2 Data

5010 0000 57FF FFFF 127M Reserved

5800 0000 5800 FFFF 64K VCP2 Data

5801 0000 5FFF FFFF 128M 64K Reserved

SIZE

Reserved

Global Ram

C64x+ Megamodule Core0 L2 RAM

C64x+ Megamodule Core1 L2 SRAM

C64x+ Megamodule Core2 L2 SRAM

Data Space onEDMA SCR

14 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 15

www.ti.com

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

HEX ADDRESS RANGE MEMORY BLOCK DESCRIPTION

START END C64x+ MEGAMODULE CORE0 C64x+ MEGAMODULE CORE1 C64x+ MEGAMODULE CORE 2

6000 0000 603F FFFF 4M Reserved

6040 0000 6FFF FFFF 252M Reserved

7000 0000 7000 00FF 256 DDR2 EMIF Configuration

7000 0100 7FFF FFFF 256M - 256 Reserved

8000 0000 9FFF FFFF 512M DDR2EMIF Data

A000 0000 AFFF FFFF 256M AIF Data

B000 0000 BFFF FFFF 256m Reserved

C000 0000 CFFF FFFF 256m Reserved

D000 0000 DFFF FFFF 256m Reserved

E000 0000 EFFF FFFF 256m Reserved

F000 0000 FFFF FFFF 256m Reserved

SIZE

2.4 Boot Sequence

The boot sequence is a process by which the DSP's internal memory is loaded with program and data

sections. The DSP's internal registers are programmed with predetermined values. The boot sequence is

started automatically after each power-on reset, warm reset, and system reset. A local reset to an

individual C64x+ Megamodule should not affect the state of the hardware boot controller on the device.

For more details on the initiators of the resets, see Section 7.7, Reset Controller.

The C6474 device supports several boot processes begins execution at the ROM base address, which

contains the bootloader code necessary to support various device boot modes. The boot processes are

software driven; using the BOOTMODE[3:0] device configuration inputs to determine the software

configuration that must be completed.

2.4.1 Boot Modes Supported

The device supports several boot processes, which leverage the internal boot ROM. Most boot processes

are software driven, using the BOOTMODE[3:0] device configuration inputs to determine the software

configuration that must be completed. From a hardware perspective, there are three possible boot modes:

• No Boot (BOOTMODE[3:0] = 0000b)

With no boot, the CPU executes directly from the internal L2 RAM located at address 0x80 0000.

Note: Device operations are undefined if invalid code is located at address 0x80 0000. This boot mode

is a hardware boot mode.

• Public ROM Boot

The C64x+ Megamodule Core 0 is released from reset and begins executing from the L3 ROM base

address. C64x+ Megamodule Core 0 is responsible for performing the boot process (e.g., from I2C

ROM, Ethernet, or RapidIO), after which C64x+ Megamodule Core 0 brings the other C64x+

megamodule cores out of reset by setting to 1 the EVTPULSE4 bit (bit 4) of the C64x+ Megamodule

Core 0's EVTASRT register. This process is valid only once: writing 1, then writing 1 again will not

bring Core 1 and 2 out of reset again. Then, the C64x+ Megamodule Core 0 begins execution from the

entry address defined in the boot table. The C64x+ Megamodule Core 1 and 2 begin execution from

their L2 RAMs' base address.

The boot process performed by C64x+ Megamodule Core 0 in public ROM boot is determined by the

BOOTMODE[3:0] value in the DEVSTAT register. C64x+ Megamodule Core 0 reads this value, and then

executes the associated boot process in software.

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 15

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 16

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Table 2-3. C6474 Supported Boot Modes

MODE NAME BOOTMODE[3:0] DESCRIPTION

No Boot 0000b No Boot (BOOTMODE[3:0] = 0000b)

I2C Master Boot A 0001b Slave I2C address is 0x50. C64x+ Megamodule Core 0 configures I2C, acts as a

I2C Master Boot B 0010b Similar to I2C boot A except the slave I2C address is 0x51.

I2C Slave Boot 0011 The C64x+ Megamodule Core 0 configures I2C and acts as a slave and will accept

EMAC Master Boot 0100b TI Ethernet Boot, C64x+ Megamodule Core 0 configures EMAC0 and EDMA, if

EMAC Slave Boot 0101b

EMAC Forced-Mode Boot 0110b

Reserved 0111b Reserved

Serial RapidIO Boot (Config 0) 1000b The C64x+ Megamodule Core 0 configures the SRIO and an external host loads the

Serial RapidIO Boot (Config 1) 1001b

Serial RapidIO Boot (Config 2) 1010b

Serial RapidIO Boot (Config 3) 1011b

master to the I2C bus and copies data from an I2C EEPROM or a device acting as an

I2C slave to the DSP using a predefined boot table format. The destination address

and length are contained within the boot table. After boot table copy is complete, the

C64x+ Megamodule Core 0 brings the other C64x+ Megamodule Cores out of reset

by setting to 1 the EVTPULSE4 bit (bit 4) of the C64x+ Megamodule Core EVTASRT

register.

data and code section packets through the I2C interface. It is required that an I2C

master in present in the system.

required, and brings the code image into the internal on-chip memory via the protocol

defined by the boot method (EMAC bootloader). After initializing the on-chip memory

to the known state, C64x+ Megamodule Core 0 brings the other C64x+ Megamodule

Cores out of reset.

application via SRIO peripheral, using directIO protocol. A doorbell interrupt is used to

indicate that the code has been loaded. For more details on the Serial RapidIO

configurations, see Table 2-4.

www.ti.com

C64x+ Megamodule Core 0 configures Serial RapidIO and EDMA, if required, and brings the code image

into the internal on-chip memory via the protocol defined by the boot method (SRIO bootloader) and then

C64x+ Megamodule Core 0 brings the other C64x+ Megamodule Cores out of reset. Note that SRIO boot

modes are only supported on port 0.

Table 2-4. Serial RapidIO (SRIO) Supported Boot Modes

SRIO BOOT MODE SERDES CLOCK LINK RATE BOOTMODE[3:0]

Bootmode 8 - Config 0 125 MHz 1.25 Gbps 1000b

Bootmode 9 - Config 1 125 MHz 3.125 Gbps 1001b

Bootmode 10 - Config 2 156.25 MHz 1.25 Gbps 1010b

Bootmode 11 - Config 3 156.25 MHz 3.125 Gbps 1011b

All the other BOOTMODE[3:0] modes are reserved.

2.4.2 Second-Level Bootloaders

Any of the boot modes can be used to download a second-level bootloader. A second-level bootloader

allows for any level of customization to current boot methods as well as the definition of a completely

customized boot.

16 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 17

AE

AD

AC

AB

AA

Y

W

V

U

T

R

13121110987654321

131211109876

5

4321

AF

AG

14

14

AE

AD

AC

AB

AA

Y

W

V

U

T

R

AF

AG

RSV04

AIF_V

DDT11

V

SS

AIFTXN4

AIFTXP4

ALTCORE

CLKN

V

SS

AIFRXN5

AIFRXP5

V

SS

V

SS

AIF_V

DDT11

AIF_V

DDA11

V

SS

AIF_V

DDT11

SYSCLKN

V

SS

V

SS

AIFRXP4

AIFRXN4

FRAME

BURSTN

V

SS

AIFTXP5

AIFTXN5

RSV02

DV

DD18

V

SS

V

SS

V

SS

V

SS

CV

DDMON

DV

DD18MON

ALTFSYNC

CLK

CORECLK

SEL

ALTFSYNC

PULSE

RSV06

SYSCLK

OUT

FSYNC

CLKP

V

SS

DV

DD18

DV

DD18

AV

DD118

V

SS

ALTCORE

CLKP

RSV07 SYSCLKP

V

SS

V

SS

V

SS

RESETSTAT

DV

DD18

V

SS

V

SS

V

SS

RSV23

POR

V

SS

V

SS

TRT

SMFRAME

CLK

XWRST

DV

DD18

V

SS

GP15 TRTCLK

DV

DD18

GP12 GP11

V

SS

GP13

V

SS

V

SS

GP14

GP10

DV

DD18

V

SS

V

SS

GP08

GP07DV

DD18

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

FSYNC

CLKN

FRAME

BURSTP

V

SS

DV

DD18

TMS

GP02

TRST

TDO

TCK

DV

DD18

GP05

GP06

TDI V

SS

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

EMU10

DV

DD18

EMU15

V

SS

GP03

GP01

DV

DD18

DV

DD18

GP04

EMU00

V

SS

EMU01 EMU07

EMU11

GP00

GP09

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

www.ti.com

SPRS552F–OCTOBER 2008–REVISED JULY 2010

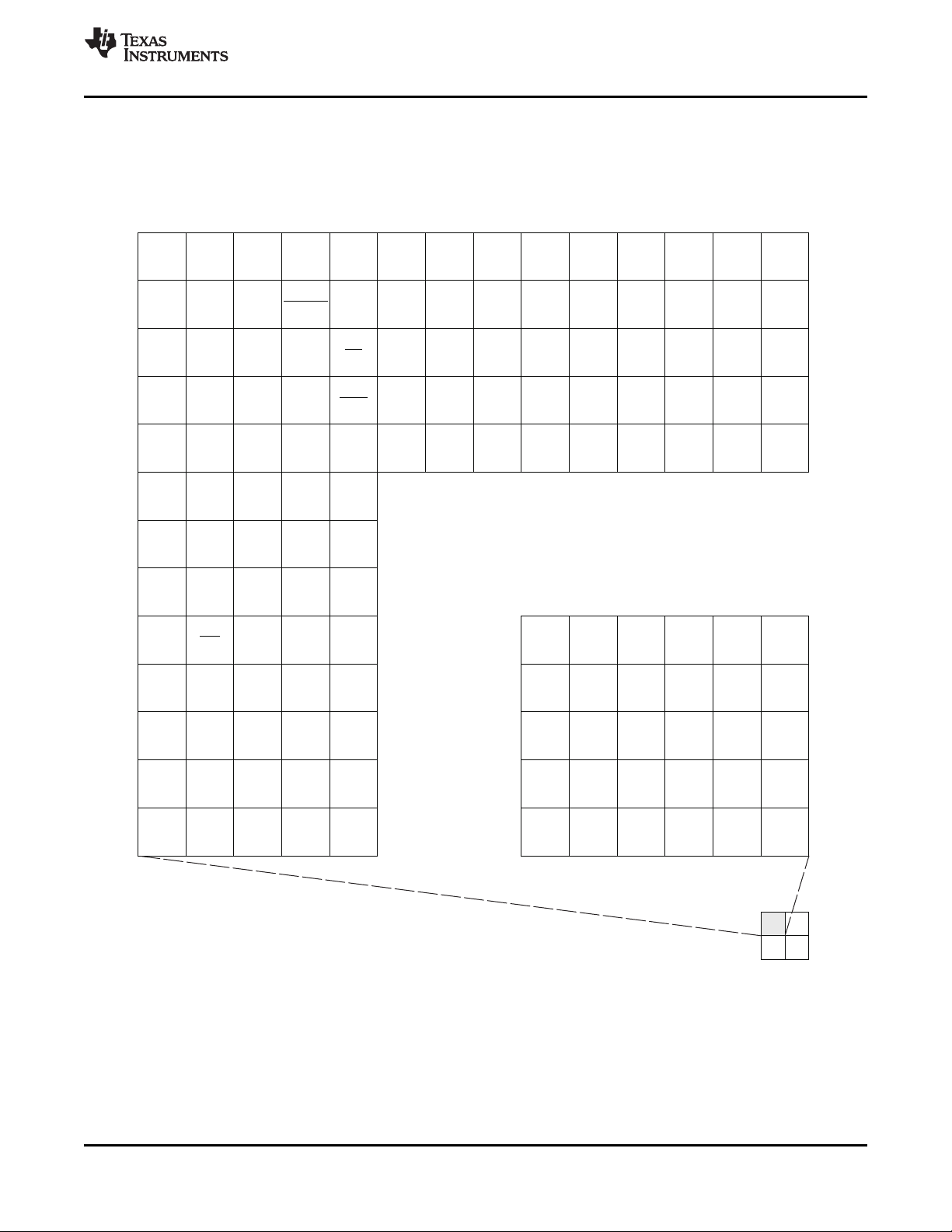

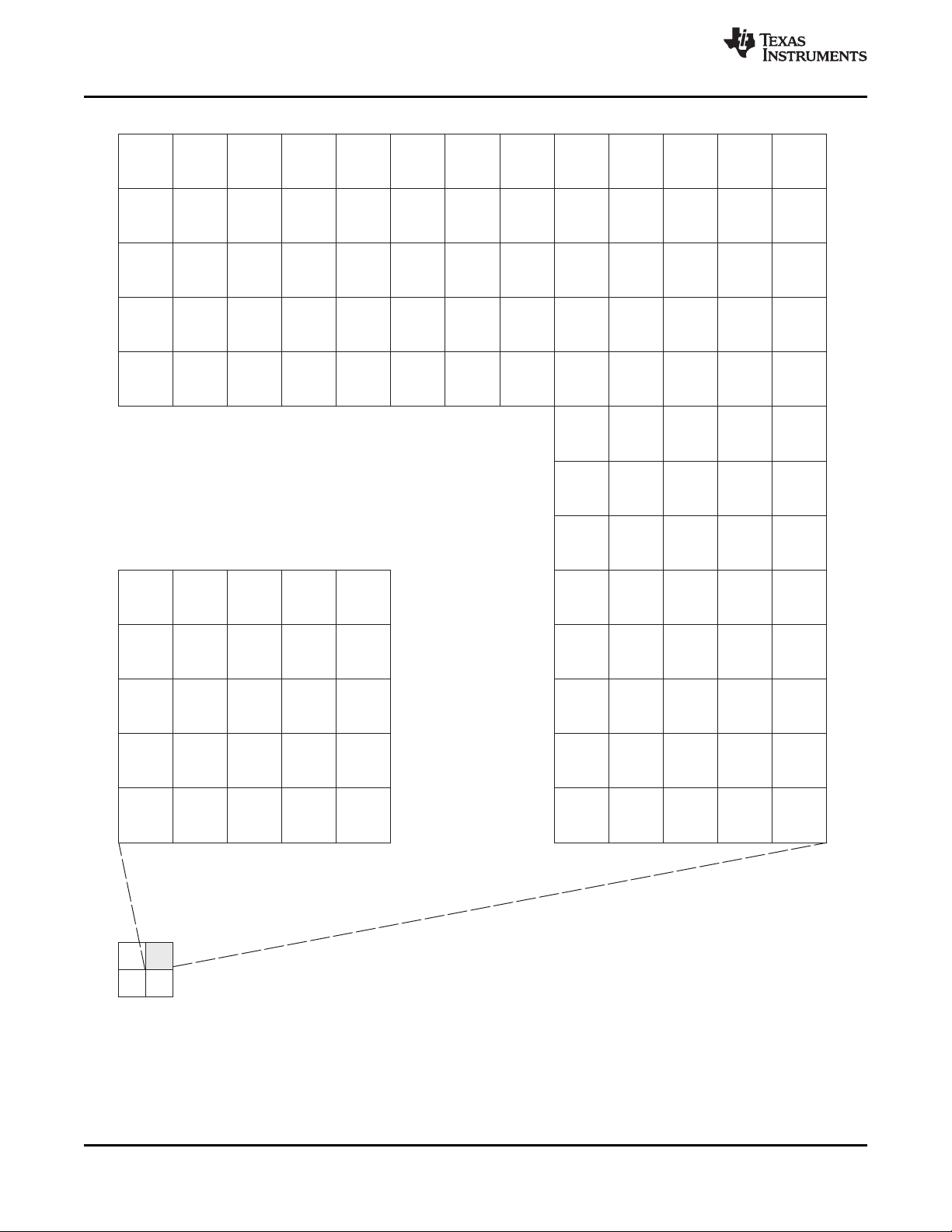

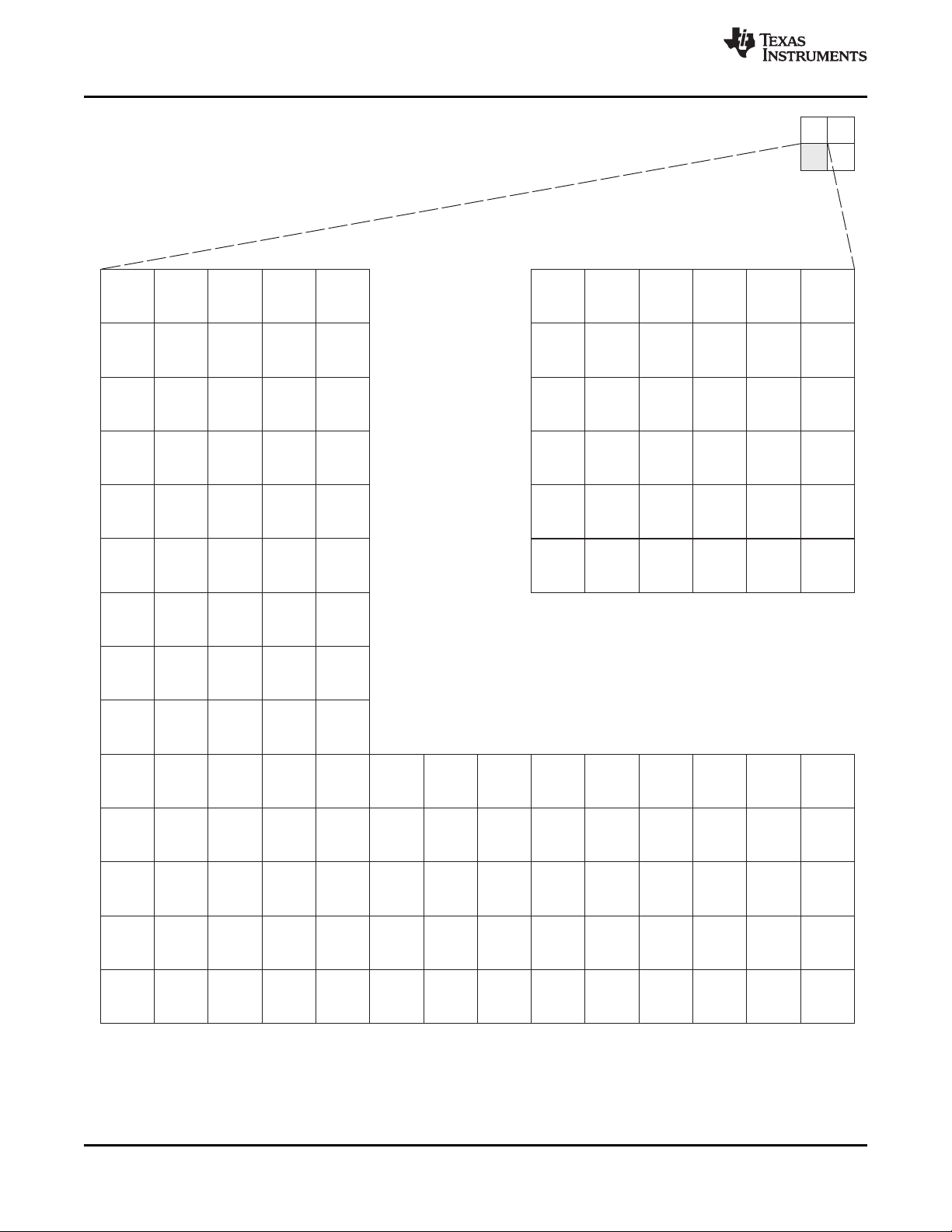

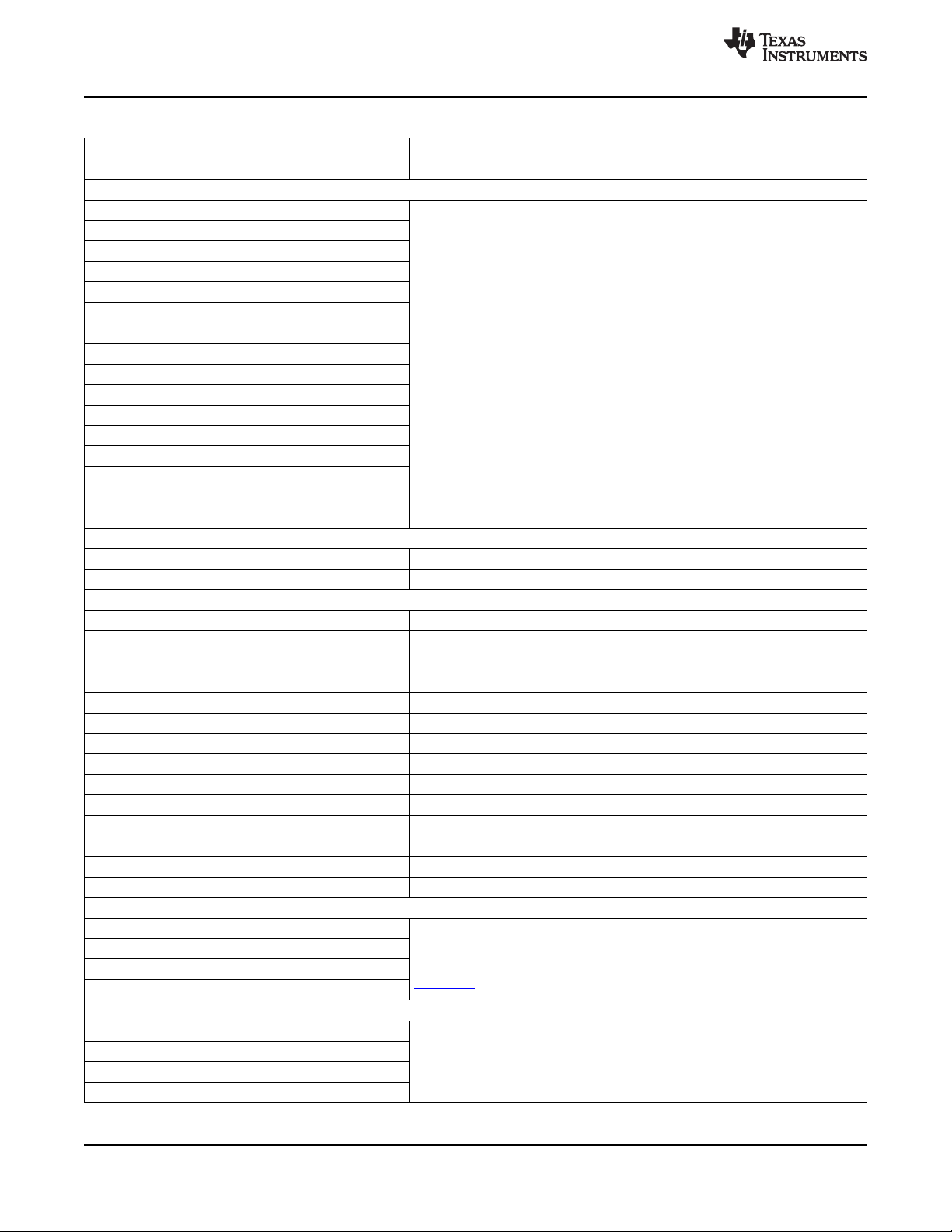

2.5 Pin Assignments

2.5.1 Pin Map

Figure 2-2 through Figure 2-5 show the C6474 pin assignments in four quadrants (A, B, C, and D).

TMS320C6474

Figure 2-2. C6474 Pin Map (Bottom View) [Quadrant A]

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 17

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 18

AE

AD

AC

AB

AA

Y

W

V

U

T

R

26252423222120

19

18171615

26

2524

2322212019

18

17

1615

AF

AG

27

27

AE

AD

AC

AB

AA

Y

W

V

U

T

R

AF

AG

AV

DD218

RSV05

RSV24

AIF_V

DDD11

DV

DD18

V

SS

RSV08

RSV09 V

SS

V

SS

DV

DD18

DDRD12

DDRD10

DDRD08

DDRSLRATE

DDRDQM1 DDRD15

DDRD13 DDRD14

DDRREF

CLKN

DDRREF

CLKP

DDRDQS1N DDRDQS1P

DDRD11

V

SS

V

SS

AIFRXP2 AIFRXN2

V

SS

AIFRXN1

AIF_V

DDT11

AIFRXP0

RSV01 V

SS

AIFTXP1

V

SS

AIF_V

DDT11

AIFRXP1 V

SS

V

SS

AIFRXN0

AIFTXN0 AIFTXP0

AIF_V

DDT11

AIFTXN2 AIFTXP2

V

SS

V

SS

V

SS

AIFRXN3

AIFRXP3

AIF_V

DDR18

AIFTXP3

AIFTXN3

V

SS

AIF_V

DDA11

V

SS

AIF_V

DDT11

AIF_V

DDA11

DDRRCV

ENIN0

DV

DD18

V

SS

DDRRCV

ENOUT0

V

SS

DV

DD18

DDRD05DDRD06

DDRD04

DDRD02

V

SS

DDRDQS0PDDRDQS0N

DV

DD18

DV

DD18

DDRDQM0

DDRD01

DDRD03

DDRD00

AIFTXN1

V

SS

AIF_V

DDA11

V

SS

AIF_V

DDD11

V

SS

V

SS

AIF_V

DDD11

V

SS

AIF_V

DDD11

AIF_V

DDD11

V

SS

AIF_V

DDD11

V

SS

V

SS

DDRCLK

OUTN0

DDRCLK

OUTP0

DV

DD18

V

SS

CV

DD

CV

DD

V

SS

V

SS

AIF_V

DDD11

V

SS

CV

DD

CV

DD

CV

DD

V

SS

V

SS

V

SS

CV

DD

CV

DD

V

SS

DDRD07

DV

DD18

V

SS

DDRBA2

DDRA07

DDRA12

V

SS

DDRCKE

DDRBA0

V

REFSSTL

V

SS

DV

DD18

V

SS

DDRBA1

DDRA03

DDRA09

DDRD09

AIF_V

DDR18

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

www.ti.com

Figure 2-3. C6474 Pin Map (Bottom View) [Quadrant B]

18 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 19

M

L

K

J

H

G

F

E

D

C

B

26252423222120

19

18171615

N

P

27

M

L

K

J

H

G

F

E

D

C

B

N

PV

SS

DDRWE

DDRA10

DV

DD18

V

SS

DV

DD18

RSV03

DDRA01

DDRCAS

DDRA05

V

SS

DDRODT

DDRA00

DDRA13

V

SS

DDRRAS

DDRA02

DV

DD18

V

SS

DV

DD18

DDRCE

DDRA04

DDRA06

DDRA11

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

V

SS

SGR_V

DDD11

V

SS

CV

DD

DDRCLK

OUTP1

V

SS

DV

DD18

DDRCLK

OUTN1

DV

DD18

V

SS

DDRD30DDRD29

DDRD31

DDRD28

DV

DD18

DDRDQS3NDDRDQS3P

V

SS

V

SS

DDRD24

DDRD25

DDRD26

DDRD27

V

SS

SGR_V

DDA11

DV

DD18

V

SS

V

SS

SGR_V

DDT11

V

SS

DV

DD18

DV

DD18

DDRRCV

ENIN1

DDRRCV

ENOUT1

V

SS

DV

DD18

V

SS

V

SS

V

SS

V

SS

V

SS

SGR_V

DDA11

DX0

MDIO

V

SS

RSV18

MDCLK

V

SS

SGR_V

DDT11

SGMIIRXN

SGMIIRXP

DDRDQM3

V

SS

DDRD19

DDRD17

DDRD21

DDRD22

RSV26

V

SS

DDRDQS2N

DDRDQS2P

DDRD23

V

SS

DDRDQM2

DDRD16

DDRD18

DDRD20

DDRA08

CV

DD

SGR_V

DDD11

V

SS

CV

DD

V

SS

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

CV

DD

V

SS

CV

DD

V

SS

A

26

2524

2322212019

18

17

1615

27

A

SGMIITXP

DV

DD18

SGR_V

DDR18

SGMIITXN V

SS

DV

DD18

CLKR1

CLKS1

V

SS

DV

DD18

CLKS0

DR1

RSV25

DX1

FSR1

FSR0

CLKX1

CLKR0

CLKX0

FSX1

FSX0

DR0

www.ti.com

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Figure 2-4. C6474 Pin Map (Bottom View) [Quadrant C]

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 19

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 20

M

L

K

J

H

G

F

E

D

C

B

121110987

6

5

4321

N

P

13

H

G

F

E

D

C

B

V

SS

DV

DD18

EMU16 EMU13

V

SS

DV

DD18

V

SS

EMU03 EMU09 EMU02

EMU06

RSV12

EMU14

RSV11 RSV10

V

SS

VCNTL2

VCNTL3

V

SS

DV

DD18

V

SS

RSV13VCNTL0

VCNTL1

V

SS

TIMO0

RSV14 TIMO1

V

SS

RSV21

DV

DD18

RSV22

V

SS

V

SS

TIMI0 SCL

DV

DD18

SGR_V

DDT11

V

SS

SGR_V

DDA11

V

SS

SGR_V

DDT11

V

SS

V

SS

V

SS

V

SS

V

SS

SDA RSV27

V

SS

TIMI1

V

SS

RSV28

V

SS

V

SS

V

SS

V

SS

DV

DD18

RIOSGMII

CLKN

V

SS

V

SS

SGR_V

DDA11

V

SS

RIOSGMII

CLKP

RIOTXP0 RIOTXN0

SGR_V

DDR18

RIOTXN1

V

SS

V

SS

V

SS

RSV17

SGR_V

DDT11

DV

DD18

NMI2

NMI1

RSV29

NMI0

EMU05

EMU04

EMU18

EMU08

V

SS

DV

DD18

DV

DD18

V

SS

EMU12

EMU17

A

12

1110

9

8

765

4

3

21

13

A

DV

DD18

DV

DD18

V

SS

V

SS

V

SS

RIORXN0

RIORXP0

V

SS

RIORXP1

RIORXN1

RSV19

RSV15

V

SS

SGR_V

DDT11

RSV16

V

SS

V

SS

V

SS

RSV20

V

SS

V

SS

V

SS

14

M

L

K

N

P

J

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

V

SS

V

SS

CV

DD

V

SS

SGR_V

DDD11

SGR_V

DDD11

V

SS

CV

DD

V

SS

V

SS

CV

DD

V

SS

CV

DD

V

SS

CV

DD

CV

DD

V

SS

CV

DD

V

SS

CV

DD

CV

DD

V

SS

SGR_V

DDD11

V

SS

CV

DD

V

SS

V

SS

V

SS

RIOTXP1

V

SS

14

V

SS

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

www.ti.com

Figure 2-5. C6474 Pin Map (Bottom View) [Quadrant D]

20 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 21

Resetand

Interrupts

IEEEStandard

1149.1

(JTAG)

Emulation

Reserved

AV

DD218

TMS

RESETSTAT

RSV

Control/Status

SYSCLKP

SYSCLKN

SYSCLKOUT

CORECLKSEL

ALTCORECLKP

ALTCORECLKN

Clock/PLL1

and

PLL Controller

Clock/PLL2

TDO

TDI

TCK

TRST

·

EMU00

EMU01

EMU02

·

·

EMU14

EMU15

EMU16

EMU17

EMU18

RESET

NMI0

NMI1

NMI2

XWRST

AV

DD118

www.ti.com

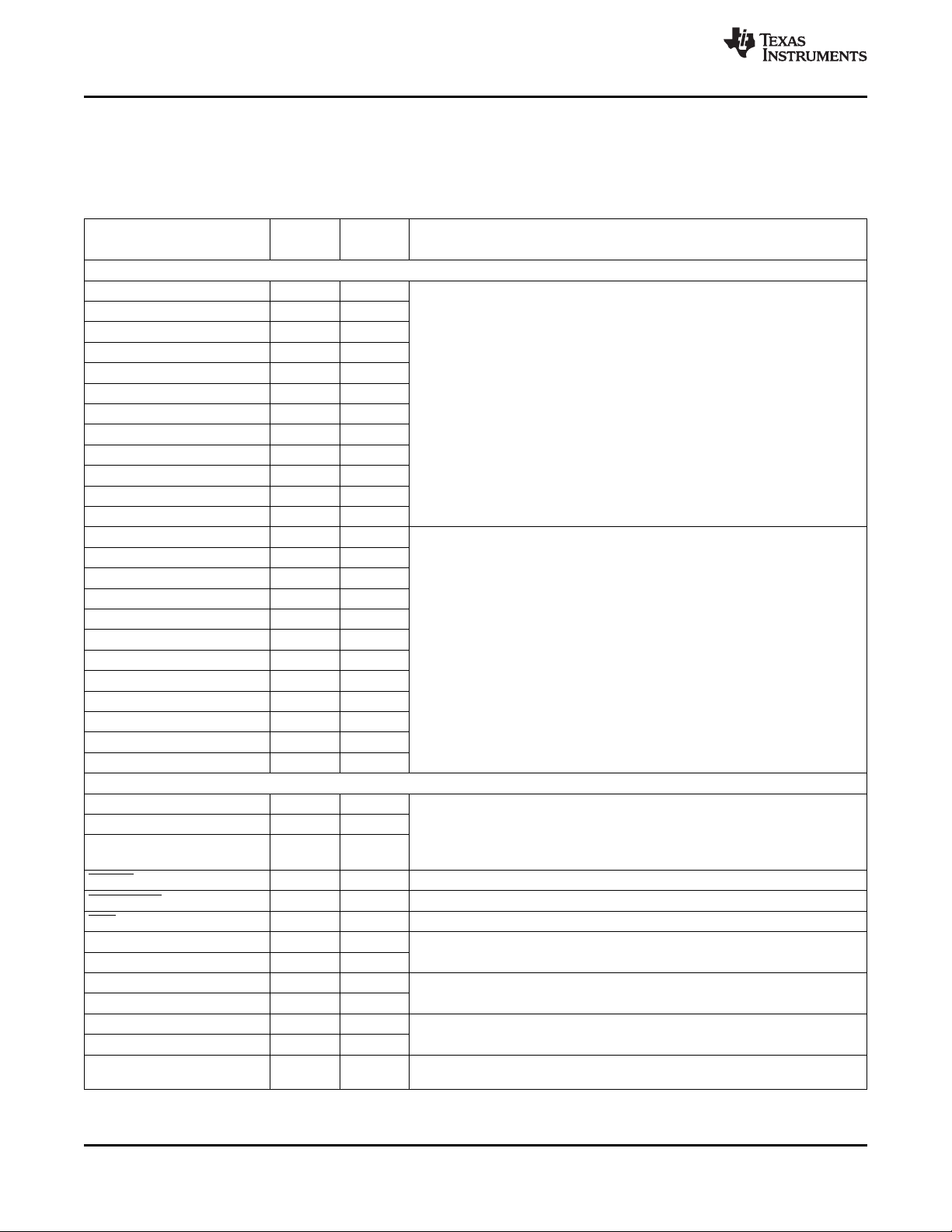

2.6 Signal Groups Description

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Figure 2-6. CPU and Peripheral Signals

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 21

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 22

DDRD[31:0]

DDRCE

DDRA[13:0]

14

DDRDQM0

DDRDQM1

DDRDQM2

DDRDQM3

Data

MemoryMap

Address

ByteEnables

DDRCLKOUTP

DDRCLKOUTN

DDRCAS

DDRRAS

DDRWE

DDRDQSP[3:0]

DDRDQSN[3:0]

DDRRCVENIN[2:0]

DDRRCVENOUT[2:0]

DDRODT

DDRSLRATE

V

REFSSTL

DDRBA0

DDRBA1

DDRBA2

External

Memory

Controller

Bank Address

DDRMemoryController(32-bitDataBus)

32

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

www.ti.com

Figure 2-7. DDR Memory Controller Peripheral Signals

22 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 23

TIMI0

TIMO0

GP00

GP01

GP02

GP03

GP04

GP05

GP06

GP07

RIOTXN0

RIOTXP0

RIOTXN1

RIOTXP1

RIORXN0

RIORXP0

RIORXN1

RIORXP1

Transmit

Receive

Clock

RapidIO

RIOSGMIICLKP

(A)

RIOSGMIICLKN

(A)

GP08

GP09

GP10

GP11

GP12

GP13

GP14

GP15

GPIO

General-PurposeInput/Output0(GPIO)Port

TIMO1

TIMI1

TimerPinManager

Timers(64-Bit)

www.ti.com

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

A. Reference Clock to drive RapidIO and SGMII.

Figure 2-8. Timers/GPIO/RapidIO Peripheral Signals

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 23

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 24

CLKX1

FSX1

DX1

CLKR1

FSR1

DR1

CLKS1

CLKX0

FSX0

DX0

CLKR0

FSR0

DR0

CLKS0

McBSP1

Clock

Receive

Transmit

McBSP0

Clock

Receive

Transmit

MultichannelBufferedSerialPorts

(McBSPs)

FRAMEBURSTN

FRAMEBURSTP

ALTFSYNCPULSE

TRT

FSYNCCLKN

FSYNCCLKP

ALTFSYNCCLK

TRTCLK

SMFRAMECLK

FSYNC Clock

FrameSynchroniztion(FSYNC)

AIFTXN[5:0]

AIFTXP[5:0]

AIFRXN[5:0]

AIFRXP[5:0]

SCL

SDA

Transmit

SCL

Receive

AntennaInterface(AIF)

I2C

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

www.ti.com

Figure 2-9. McBSP/FSYNC/AIF/I2C Peripheral Signals

24 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 25

SGMIITXN

SGMIITXP

SGMIIRXN

SGMIIRXP

RIOSGMIICLKN

(A)

RIOSGMIICLKP

(A)

EthernetMAC

(EMAC)

SGMII

Transmit

SGMII

Receive

SGMII

Clock

MDIO

EthernetMAC(EMAC)andMDIO

MDIO

MDCLK

www.ti.com

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

A. Reference Clock to drive RapidIO and SGMII.

Figure 2-10. EMAC/MDIO [SGMII] Peripheral Signals

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 25

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 26

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

2.7 Terminal Functions

The terminal functions table (Table 2-5) identifies the external signal names, the pin type (I, O, O/Z, or

I/O/Z), whether the pin has any internal pullup/pulldown resistors, and the signal function description.

Table 2-5. Terminal Functions

SIGNAL

NAME NO.

AIFRXN0 AF22 I

AIFRXP0 AF21 I

AIFRXN1 AG20 I

AIFRXP1 AG21 I

AIFRXN2 AG18 I

AIFRXP2 AG17 I

AIFRXN3 AE17 I

AIFRXP3 AE18 I

AIFRXN4 AE14 I

AIFRXP4 AE13 I

AIFRXN5 AF12 I

AIFRXP5 AF13 I

AIFTXN0 AE21 O

AIFTXP0 AE22 O

AIFTXN1 AD21 O

AIFTXP1 AD20 O

AIFTXN2 AF16 O

AIFTXP2 AF17 O

AIFTXN3 AD17 O

AIFTXP3 AD16 O

AIFTXN4 AG13 O

AIFTXP4 AG14 O

AIFTXN5 AD13 O

AIFTXP5 AD12 O

NMI0 J4 I IPD Non-maskable interrupts. NMI0, NMI1, and NMI2 pins are mapped to C64x+

NMI1 J2 I IPD

NMI2 J1 I IPD

XWRST AD5 I Warm Reset

RESETSTAT AF4 O Reset Status Output

POR AE5 I Power-on Reset

SYSCLKP AE9 I

SYSCLKN AE10 I

ALTCORECLKN AF10 I

ALTCORECLKP AF9 I

DDRREFCLKN AD23 I

DDRREFCLKP AD24 I

SYSCLKOUT AD6 O/Z IPD

TYPE

(1)

IPD/IPU

(2)

ANTENNA INTERFACE

Antenna Interface Receive Data (6 links)

Antenna Interface Transmit Data (6 links)

CLOCK/RESETS

Megamodule Core 0, C64x+ Megamodule Core 1, and C64x+ Megamodule Core

2, respectively. NMIs are edge-driven (rising edge). Any noise on the NMI pin

may trigger an NMI interrupt; therefore, if the NMI pin is not used, it is

recommended that the NMI pin be grounded rather than relying on the IPD.

System Clock Input to Antenna Interface and main PLL (Main PLL optional vs

ALTCORECLK)

Alternate Core Clock Input to main PLL (vs SYSCLK)

DDR Reference Clock Input to DDR PLL

System Clock Output to be used as a general purpose output clock for debug

purposes

SIGNAL DESCRIPTION

www.ti.com

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal

(2) IPD = internal pulldown, IPU = internal pullup. All internal pullups and pulldowns are 100 mA.

26 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 27

www.ti.com

Table 2-5. Terminal Functions (continued)

SIGNAL

NAME NO.

CORECLKSEL AF7 I

RIOSGMIICLKN D9 I

RIOSGMIICLKP C9 I

DDRDQM0 W24 O/Z

DDRDQM1 AE24 O/Z

DDRDQM2 B24 O/Z

DDRDQM3 H24 O/Z

DDRCE L24 O/Z DDR2 EMIF Chip Enable

DDRBA0 T25 O/Z

DDRBA1 R25 O/Z DDR Bank Address

DDRBA2 U25 O/Z

DDRA00 K25 O/Z

DDRA01 N25 O/Z

DDRA02 M25 O/Z

DDRA03 R26 O/Z

DDRA04 L25 O/Z

DDRA05 N27 O/Z

DDRA06 L26 O/Z

DDRA07 U26 O/Z

DDRA08 K26 O/Z

DDRA09 R27 O/Z

DDRA10 P25 O/Z

DDRA11 L27 O/Z

DDRA12 U27 O/Z

DDRA13 K27 O/Z

DDRCLKOUTP0 V25 O/Z

DDRCLKOUTN0 V24 O/Z

DDRCLKOUTP1 J25 O/Z

DDRCLKOUTN1 J24 O/Z

TYPE

(1)

(2)

IPD/IPU

Core Clock Select to select between SYSCLK(N|P) and ALTCORECCLK to the

main PLL

RapidIO/SGMII Reference Clock to drive the RapidIO and SGMII SERDES

DDR MEMORY CONTROLLER

DDR2 EMIF Data Masks

DDR2 EMIF Address Bus

DDR2 EMIF Output Clocks to drive SDRAMs (one clock pair per SDRAM)

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

SIGNAL DESCRIPTION

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 27

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 28

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Table 2-5. Terminal Functions (continued)

SIGNAL

NAME NO.

DDRD00 W27 I/O/Z

DDRD01 W25 I/O/Z

DDRD02 Y27 I/O/Z

DDRD03 W26 I/O/Z

DDRD04 AA27 I/O/Z

DDRD05 AA26 I/O/Z

DDRD06 AA25 I/O/Z

DDRD07 AA24 I/O/Z

DDRD08 AC27 I/O/Z

DDRD09 AC26 I/O/Z

DDRD10 AC25 I/O/Z

DDRD11 AD27 I/O/Z

DDRD12 AC24 I/O/Z

DDRD13 AE26 I/O/Z

DDRD14 AE27 I/O/Z

DDRD15 AE25 I/O/Z

DDRD16 B25 I/O/Z

DDRD17 D25 I/O/Z

DDRD18 B26 I/O/Z

DDRD19 D24 I/O/Z

DDRD20 B27 I/O/Z

DDRD21 D26 I/O/Z

DDRD22 D27 I/O/Z

DDRD23 C27 I/O/Z

DDRD24 F24 I/O/Z

DDRD25 F25 I/O/Z

DDRD26 F26 I/O/Z

DDRD27 F27 I/O/Z

DDRD28 G27 I/O/Z

DDRD29 H25 I/O/Z

DDRD30 H26 I/O/Z

DDRD31 H27 I/O/Z

DDRCAS N26 O/Z DDR2 EMIF Column Address Strobe

DDRRAS M24 O/Z DDR2 Row Address Strobe

DDRWE P24 O/Z DDR2 EMIF Write Enable

DDRCKE T24 O/Z DDR2 EMIF Clock Enable

DDRDQS0P Y26 I/O/Z

DDRDQS0N Y25 I/O/Z

DDRDQS1P AD26 I/O/Z

DDRDQS1N AD25 I/O/Z

DDRDQS2P C26 I/O/Z

DDRDQS2N C25 I/O/Z

DDRDQS3P G25 I/O/Z

DDRDQS3N G26 I/O/Z

TYPE

(1)

IPD/IPU

(2)

DDR2 EMIF Data Bus

DDR2 EMIF Data Strobe

SIGNAL DESCRIPTION

www.ti.com

28 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 29

TMS320C6474

www.ti.com

Table 2-5. Terminal Functions (continued)

SIGNAL

NAME NO.

DDRRCVENIN0 AB25 I

DDRRCVENOUT0 AB24 O/Z

DDRRCVENIN1 E24 I

DDRRCVENOUT1 E25 O/Z

DDRODT K24 O/Z Bits 1:0 are the ODT status, these bits are Read/Write:

DDRSLRATE AE23 I DDR2 Slew rate control

V

REFSSTL

T26 A Reference Voltage Input for SSTL18 buffers used by DDR2 EMIF (V

TCK W4 I IPU JTAG Clock Input

TDI V4 I IPU JTAG Data Input

TDO W3 O/Z JTAG Data Output

TMS W1 I IPU JTAG Test Mode Input

TRST W2 I IPD JTAG Reset

EMU00 R4 I/O/Z IPU

EMU01 R2 I/O/Z IPU

EMU02 N3 I/O/Z IPU

EMU03 N1 I/O/Z IPU

EMU04 M2 I/O/Z IPU

EMU05 M1 I/O/Z IPU

EMU06 N4 I/O/Z IPU

EMU07 R3 I/O/Z IPU

EMU08 M4 I/O/Z IPU

EMU09 N2 I/O/Z IPU Emulation and Trace Port

EMU10 R1 I/O/Z IPU

EMU11 T2 I/O/Z IPU

EMU12 L3 I/O/Z IPU

EMU13 P4 I/O/Z IPU

EMU14 K2 I/O/Z IPU

EMU15 T1 I/O/Z IPU

EMU16 P3 I/O/Z IPU

EMU17 L4 I/O/Z IPU

EMU18 M3 I/O/Z IPU

FSYNCCLKN AD8 I Frame Sync Interface Clock used to drive the frame synchronization interface

FSYNCCLKP AD7 I

SMFRAMECLK AD4 O/Z IPD Frame Sync Clock Output

FRAMEBURSTN AD10 I

FRAMEBURSTP AD9 I

ALTFSYNCCLK AF6 I IPD Alternate Frame Sync Clock Input (vs FSYNCCLK(N|P)

ALTFSYNCPULSE AE6 I IPD Alternate Frame Sync Input (vs FRAMEBURST (N|P)

TRT AD3 I IPD Multi-standard Frame Synchronization Tick

TRTCLK AC4 I IPD Multi-standard Frame Synchronization Clock

TYPE

(1)

(2)

IPD/IPU

DDR2 EMIF Data Strobe Gate Input/Outputs to help meet DDR Timing

DDR2 EMIF On-Die Termination Outputs used to set termination on the

SDRAMs

The DDR2 ODT control register is found at 0x7000 00F0

00 - no termination

01- half termination

11 - full termination

JTAG EMULATION

FRAME SYNCHRONIZATION (FSYNC)

(OBSAI RP1 clock)

Frame Burst to drive frame indicators to the frame synchronization module

(OBSAI RP1)

SPRS552F–OCTOBER 2008–REVISED JULY 2010

SIGNAL DESCRIPTION

DDS18/2

)

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 29

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 30

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Table 2-5. Terminal Functions (continued)

SIGNAL

NAME NO.

GP00 T3 I/O/Z IPD

GP01 U4 I/O/Z IPD

GP02 V1 I/O/Z IPD

GP03 U3 I/O/Z IPD

GP04 T4 I/O/Z IPU

GP05 V2 I/O/Z IPD

GP06 V3 I/O/Z IPD

GP07 Y3 I/O/Z IPD

GP08 Y4 I/O/Z IPD

GP09 AA2 I/O/Z IPD

GP10 AA3 I/O/Z IPD

GP11 AB4 I/O/Z IPD

GP12 AB3 I/O/Z IPD

GP13 AB2 I/O/Z IPD

GP14 AA4 I/O/Z IPD

GP15 AC3 I/O/Z IPD

SCL E4 I/O/Z I2C Clock (open drain)

SDA D4 I/O/Z I2C Data (open drain)

CLKS0 D20 I IPD McBSP0 Module Clock

CLKR0 B20 I/O/Z IPD McBSP0 Receive Clock

CLKX0 C20 I/O/Z IPD McBSP0 Transmit Clock

DR0 A20 I IPD McBSP0 Receive Data

DX0 D19 O/Z IPD McBSP0 Transmit Data

FSR0 B21 I/O/Z IPD McBSP0 Receive Frame Sync

FSX0 A21 I/O/Z IPD McBSP0 Transmit Frame Sync

CLKS1 A25 I IPD McBSP1 Module Clock

CLKR1 A24 I/O/Z IPD McBSP1 Receive Clock

CLKX1 C22 I/O/Z IPD McBSP1 Transmit Clock

DR1 D21 I IPD McBSP1 Receive Data

DX1 B22 O/Z IPD McBSP1 Transmit Data

FSR1 C21 I/O/Z IPD McBSP1 Receive Frame Sync

FSX1 A22 I/O/Z IPD McBSP1 Transmit Frame Sync

VCNTL0 G3 O

VCNTL1 G2 O

VCNTL2 H4 O

VCNTL3 H3 O

RIORXN0 A9 I

RIORXP0 A10 I

RIORXN1 A13 I

RIORXP1 A12 I

(1)

TYPE

GENERAL PURPOSE INPUT/OUTPUT (GPIO)

MULTICHANNEL BUFFERED SERIAL PORT (McBSP)

IPD/IPU

(2)

General Purpose Input/Output

GPIO[3:0] are mapped to BOOTMODE[3:0]

(see Section 2.4.1, Boot Modes Supported)

GPIO4 is mapped to LENDIAN

0 = Big Endian

1 = Little Endian (default)

GPIO5 is mapped to L2_CONFIG is a reserved bootstrap pin and should be

pulled up to DV

during bootstrap

GPIO[7:6] are not multiplexed

GPIO[11:8] are mapped to DEVNUM[3:0]

(see Section 2.4.1, Boot Modes Supported)

GPIO[15:12] are not multiplexed

MISCELLANEOUS

Voltage Control Outputs to variable core power supply (open-drain buffers)

Note: These pins must be externally pulled up. For more infomation, see the

TMS320C6474 Hardware Design Guide application report (literature number

SPRAAW7).

SERIAL RAPIDIO (SRIO)

Serial RapidIO Receive Data (2 links)

DD18

I2C

www.ti.com

SIGNAL DESCRIPTION

30 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 31

www.ti.com

Table 2-5. Terminal Functions (continued)

SIGNAL

NAME NO.

RIOTXN0 C11 O

RIOTXP0 C10 O

RIOTXN1 C13 O

RIOTXP1 C14 O

SGMIIRXN C16 I

SGMIIRXP C17 I

SGMIITXN A16 O

SGMIITXP A15 O

MDIO B19 I/O/Z IPU MDIO Data

MDCLK C19 O IPD MDIO Clock

TIMI0 E3 I IPD

TIMI1 C4 I IPD

TIMO0 F2 O/Z IPD

TIMO1 F4 O/Z IPD

RSV01 AE19 A Reserved, unconnected

RSV02 AD14 A Reserved, unconnected

RSV03 N24 A Reserved, 45.3-Ω 1% resistor to GND

RSV04 AG10 A Reserved, unconnected

RSV05 AG24 A Reserved, unconnected

RSV06 AE7 O Reserved, unconnected

RSV07 AE8 O Reserved, unconnected

RSV08 AF24 O Reserved, unconnected

RSV09 AF25 O Reserved, unconnected

RSV10 K4 I/O/Z IPU Reserved, unconnected

RSV11 K3 I/O/Z IPU Reserved, unconnected

RSV12 K1 I/O/Z IPU Reserved, unconnected

RSV13 G4 O/Z IPD Reserved, unconnected

RSV14 F3 O/Z IPD Reserved, unconnected

RSV15 D7 A Reserved, GND connection

RSV16 C7 A Reserved, unconnected

RSV17 B12 A Reserved, unconnected

RSV18 B18 A Reserved, unconnected

RSV19 D6 I/O/Z IPU Reserved, unconnected

RSV20 C6 I/O/Z IPU Reserved, unconnected

RSV21 E6 Reserved, CVDDconnection

RSV22 E7 Reserved, CVDDconnection

RSV23 AE4 O/Z IPD Reserved, unconnected

RSV24 AG25 O/Z IPD Reserved, unconnected

RSV25 D22 A Reserved, GND connection

RSV26 C23 A Reserved, GND connection

RSV27 D5 A Reserved, unconnected

RSV28 C5 A Reserved, unconnected

TYPE

(1)

MANAGEMENT DATA INPUT/OUTPUT (MDIO)

(2)

IPD/IPU

Serial RapidIO Transmit data (2 links)

ETHERNET MAC (EMAC) AND SGMII

Ethernet MAC SGMII Receive Data

Ethernet MAC SGMII Transmit Data

TIMERS

Timer Inputs

Timer Outputs

RESERVED

SIGNAL DESCRIPTION

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 31

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 32

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Table 2-5. Terminal Functions (continued)

SIGNAL

NAME NO.

RSV29 J3 Reserved, DV

J11 S

J17 S

J19 S

J9 S

K10 S

K18 S

L11 S

L13 S

L15 S

L17 S

L19 S

L9 S

M10 S

M12 S

M14 S

M16 S

M18 S

N11 S

CV

DD

N13 S 0.9 - 1.2-V Core Supply Voltage

N15 S

N17 S

N19 S

N9 S

P10 S

P12 S

P14 S

P16 S

P18 S

R11 S

R13 S

R15 S

R17 S

R19 S

R9 S

T10 S

T12 S

T14 S

TYPE

(1)

IPD/IPU

(2)

SUPPLY VOLTAGE PINS

DD18

www.ti.com

SIGNAL DESCRIPTION

connection

32 Device Overview Copyright © 2008–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 33

www.ti.com

SIGNAL

NAME NO.

CV

DD

AIF_V

DDA11

SGR_V

DDA11

AV

DD218

AV

DD118

AIF _V

DDD11

SGR_V

DDD11

CV

DDMON

AIF_V

DDR18

SGR_V

DDR18

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Table 2-5. Terminal Functions (continued)

(1)

TYPE

T16 S

T18 S

U11 S

U13 S

U15 S

U19 S

U9 S 0.9 - 1.2-V Core Supply Voltage

V10 S

V12 S

V14 S

W11 S

W13 S

W9 S

AC12 A

AC15 A

AC18 A

AC21 A

D12 A

D18 A

E11 A

E15 A

AG23 A

AG9 A

AG26 S

U17 S

V16 S

V18 S 1.1-V AIF Serdes Digital Supply

W15 S

W17 S

W19 S

J13 S

J15 S

K12 S 1.1-V SRIO/SGMII Serdes Digital Supply

K14 S

K16 S

AG6 S 0.9 - 1.2-V CVDDSupply Monitor

AD19 S

AD15 S

C12 S

A18 S

IPD/IPU

(2)

SIGNAL DESCRIPTION

1.1-V AIF Serdes Analog Supply

1.1-V SRIO/SGMII Serdes Analog Supply

1.8-V PLL Supply

1.8-V AIF Serdes Regulator Supply

1.8-V SRIO/SGMII Serdes Regulator Supply

TMS320C6474

Copyright © 2008–2010, Texas Instruments Incorporated Device Overview 33

Submit Documentation Feedback

Product Folder Link(s) :TMS320C6474

Page 34

TMS320C6474

SPRS552F–OCTOBER 2008–REVISED JULY 2010

Table 2-5. Terminal Functions (continued)

SIGNAL

NAME NO.

DV

DD18

A1 S

A19 S

A23 S

A27 S

A5 S

AA23 S

AA5 S

AB26 S