Page 1

TMS320C28x Assembly Language Tools

v20.12.0.STS

User’s Guide

Literature Number: SPRU513V

JULY 2001 – REVISED DECEMBER 2020

Page 2

Page 3

www.ti.com Table of Contents

Table of Contents

Read This First......................................................................................................................................................................... 11

About This Manual..................................................................................................................................................................11

How to Use This Manual........................................................................................................................................................ 11

Notational Conventions.......................................................................................................................................................... 12

Related Documentation From Texas Instruments.................................................................................................................. 13

Trademarks............................................................................................................................................................................ 13

1 Introduction to the Software Development Tools.............................................................................................................. 15

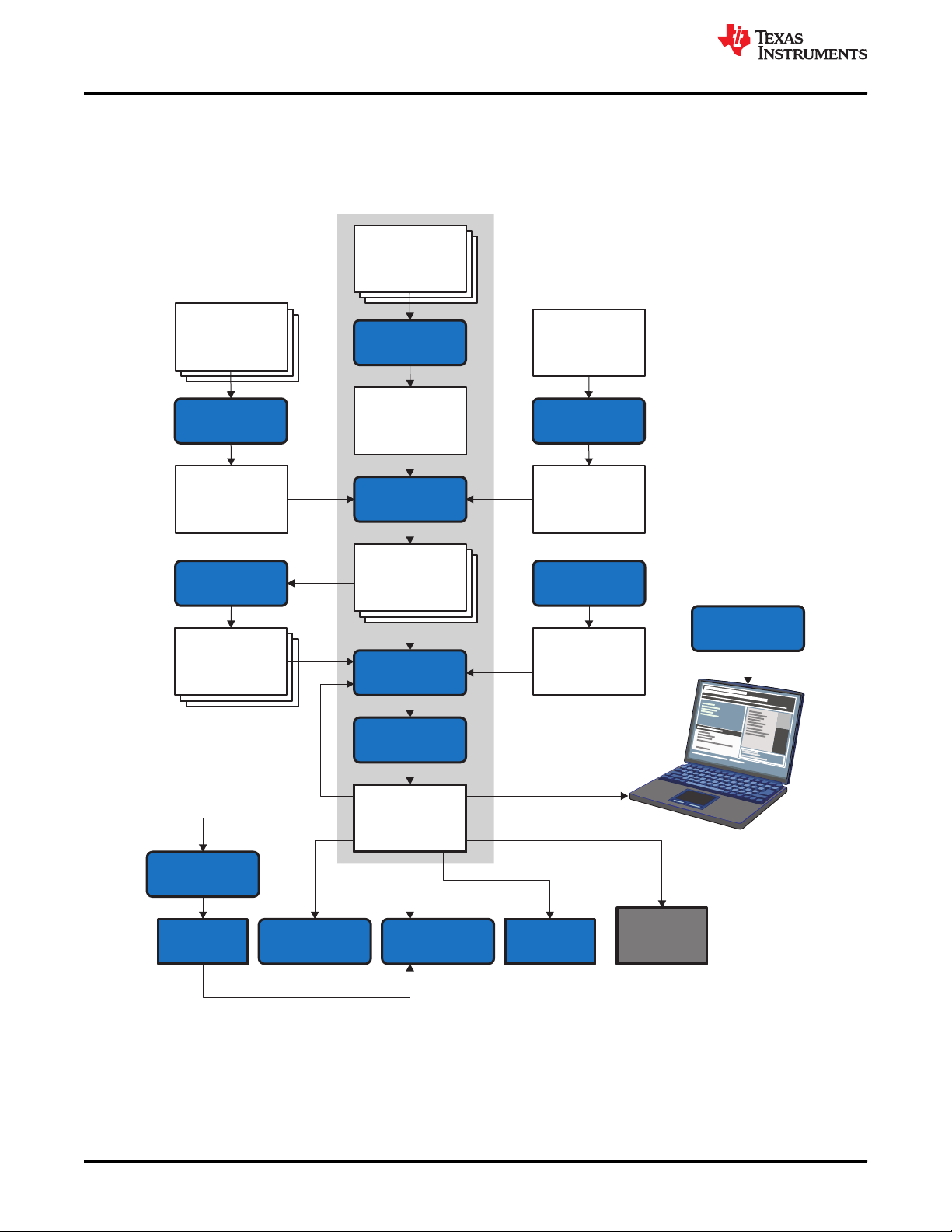

1.1 Software Development Tools Overview........................................................................................................................... 16

1.2 Tools Descriptions............................................................................................................................................................17

2 Introduction to Object Modules...........................................................................................................................................19

2.1 Object File Format Specifications.................................................................................................................................... 20

2.2 Executable Object Files................................................................................................................................................... 20

2.3 Introduction to Sections....................................................................................................................................................20

2.3.1 Special Section Names............................................................................................................................................. 21

2.4 How the Assembler Handles Sections............................................................................................................................. 21

2.4.1 Uninitialized Sections................................................................................................................................................ 22

2.4.2 Initialized Sections.....................................................................................................................................................22

2.4.3 User-Named Sections............................................................................................................................................... 23

2.4.4 Current Section..........................................................................................................................................................23

2.4.5 Section Program Counters........................................................................................................................................ 24

2.4.6 Subsections............................................................................................................................................................... 24

2.4.7 Using Sections Directives..........................................................................................................................................25

2.5 How the Linker Handles Sections.................................................................................................................................... 27

2.5.1 Combining Input Sections..........................................................................................................................................28

2.5.2 Placing Sections........................................................................................................................................................ 29

2.6 Symbols........................................................................................................................................................................... 29

2.6.1 Global (External) Symbols.........................................................................................................................................30

2.6.2 Local Symbols........................................................................................................................................................... 30

2.6.3 Weak Symbols...........................................................................................................................................................30

2.6.4 The Symbol Table......................................................................................................................................................31

2.7 Symbolic Relocations.......................................................................................................................................................32

2.7.1 Expressions With Multiple Relocatable Symbols (COFF Only)................................................................................. 32

2.8 Loading a Program...........................................................................................................................................................33

3 Program Loading and Running........................................................................................................................................... 35

3.1 Loading............................................................................................................................................................................ 36

3.1.1 Load and Run Addresses.......................................................................................................................................... 36

3.1.2 Bootstrap Loading..................................................................................................................................................... 37

3.2 Entry Point........................................................................................................................................................................40

3.3 Run-Time Initialization......................................................................................................................................................41

3.3.1 The _c_int00 Function............................................................................................................................................... 41

3.3.2 RAM Model vs. ROM Model...................................................................................................................................... 41

3.3.3 About Linker-Generated Copy Tables....................................................................................................................... 43

3.4 Arguments to main........................................................................................................................................................... 44

3.5 Run-Time Relocation........................................................................................................................................................44

3.6 Additional Information...................................................................................................................................................... 44

4 Assembler Description.........................................................................................................................................................45

4.1 Assembler Overview........................................................................................................................................................ 46

4.2 The Assembler's Role in the Software Development Flow.............................................................................................. 47

4.3 Invoking the Assembler....................................................................................................................................................48

4.4 Controlling Application Binary Interface........................................................................................................................... 49

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

TMS320C28x Assembly Language Tools

v20.12.0.STS

3

Page 4

Table of Contents

www.ti.com

4.5 Naming Alternate Directories for Assembler Input........................................................................................................... 49

4.5.1 Using the --include_path Assembler Option.............................................................................................................. 50

4.5.2 Using the C2000_A_DIR Environment Variable........................................................................................................51

4.6 Source Statement Format................................................................................................................................................ 52

4.6.1 Label Field................................................................................................................................................................. 53

4.6.2 Mnemonic Field......................................................................................................................................................... 53

4.6.3 Operand Field............................................................................................................................................................54

4.6.4 Comment Field.......................................................................................................................................................... 54

4.7 Literal Constants.............................................................................................................................................................. 54

4.7.1 Integer Literals...........................................................................................................................................................54

4.7.2 Character String Literals............................................................................................................................................56

4.7.3 Floating-Point Literals................................................................................................................................................57

4.8 Assembler Symbols......................................................................................................................................................... 57

4.8.1 Identifiers................................................................................................................................................................... 57

4.8.2 Labels........................................................................................................................................................................ 57

4.8.3 Local Labels.............................................................................................................................................................. 58

4.8.4 Symbolic Constants...................................................................................................................................................59

4.8.5 Defining Symbolic Constants (--asm_define Option).................................................................................................60

Example 4-3. Using Symbolic Constants Defined on Command Line................................................................................61

4.8.6 Predefined Symbolic Constants................................................................................................................................ 61

4.8.7 Registers................................................................................................................................................................... 61

4.8.8 Substitution Symbols................................................................................................................................................. 63

4.9 Expressions......................................................................................................................................................................63

4.9.1 Mathematical and Logical Operators.........................................................................................................................64

4.9.2 Relational Operators and Conditional Expressions................................................................................................... 65

4.9.3 Well-Defined Expressions..........................................................................................................................................65

4.9.4 Legal Expressions..................................................................................................................................................... 65

4.10 Built-in Functions and Operators....................................................................................................................................66

4.10.1 Built-In Math and Trigonometric Functions..............................................................................................................66

4.11 TMS320C28x Assembler Extensions.............................................................................................................................67

4.11.1 C28x Support...........................................................................................................................................................67

4.11.2 C28x FPU32 and FPU64 Extensions.......................................................................................................................68

4.11.3 C28x CLA Extensions..............................................................................................................................................68

4.12 Source Listings...............................................................................................................................................................69

4.13 Debugging Assembly Source.........................................................................................................................................71

4.14 Cross-Reference Listings...............................................................................................................................................72

4.15 Smart Encoding..............................................................................................................................................................73

4.16 Pipeline Conflict Detection............................................................................................................................................. 74

4.16.1 Protected and Unprotected Pipeline Instructions.................................................................................................... 74

4.16.2 Pipeline Conflict Prevention and Detection............................................................................................................. 74

4.16.3 Pipeline Conflicts Detected......................................................................................................................................74

5 Assembler Directives........................................................................................................................................................... 77

5.1 Directives Summary......................................................................................................................................................... 78

5.2 Directives that Define Sections........................................................................................................................................ 82

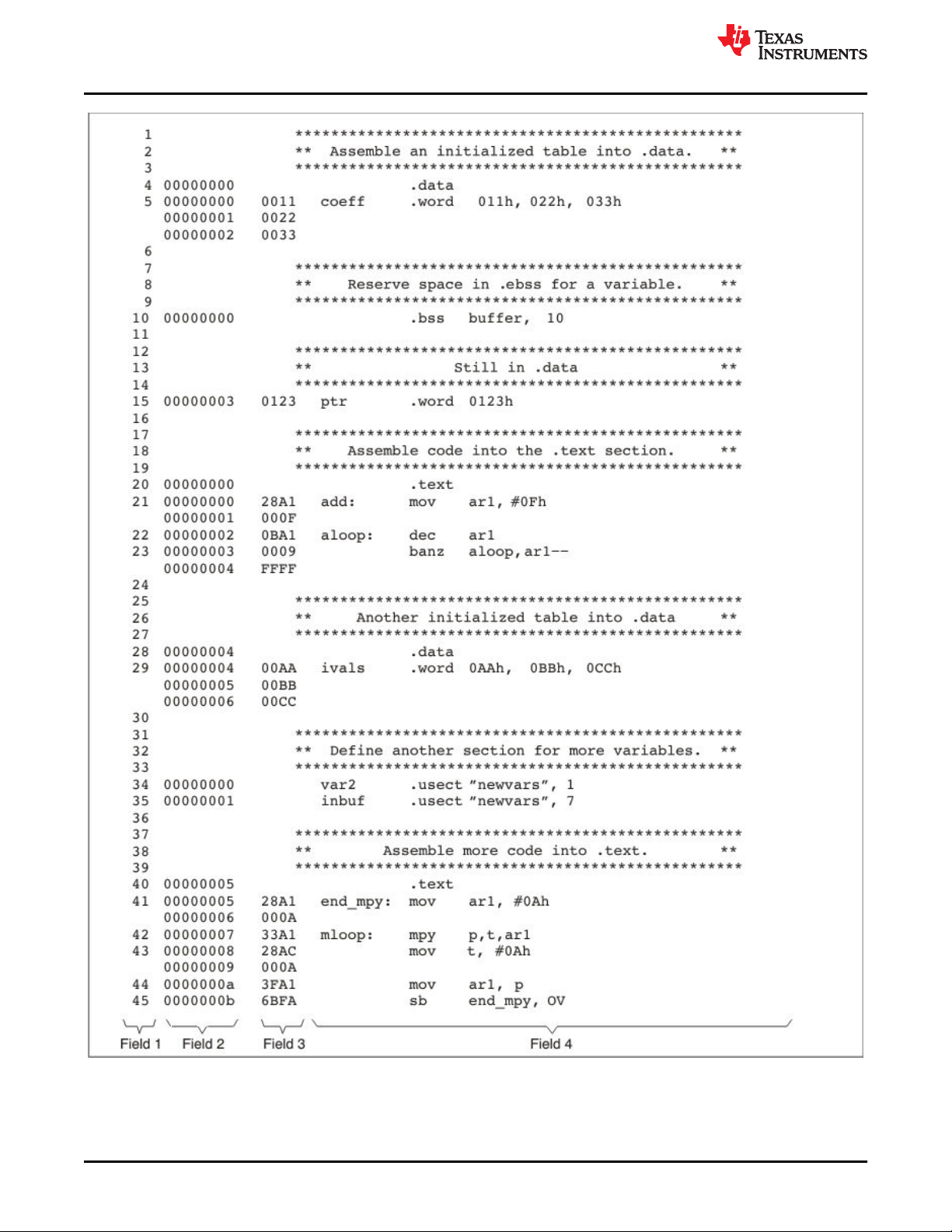

Example 5-1. Sections Directives.......................................................................................................................................83

5.3 Directives that Initialize Values.........................................................................................................................................83

5.4 Directives that Perform Alignment and Reserve Space................................................................................................... 86

5.5 Directives that Format the Output Listings....................................................................................................................... 87

5.6 Directives that Reference Other Files.............................................................................................................................. 88

5.7 Directives that Enable Conditional Assembly...................................................................................................................89

5.8 Directives that Define Union or Structure Types.............................................................................................................. 89

5.9 Directives that Define Enumerated Types........................................................................................................................89

5.10 Directives that Define Symbols at Assembly Time.........................................................................................................89

5.11 Miscellaneous Directives................................................................................................................................................90

5.12 Directives Reference......................................................................................................................................................91

6 Macro Language Description.............................................................................................................................................155

6.1 Using Macros................................................................................................................................................................. 156

6.2 Defining Macros............................................................................................................................................................. 157

6.3 Macro Parameters/Substitution Symbols....................................................................................................................... 158

6.3.1 Directives That Define Substitution Symbols...........................................................................................................159

6.3.2 Built-In Substitution Symbol Functions.................................................................................................................... 160

4 TMS320C28x Assembly Language Tools

v20.12.0.STS

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Page 5

www.ti.com

Table of Contents

6.3.3 Recursive Substitution Symbols.............................................................................................................................. 161

6.3.4 Forced Substitution..................................................................................................................................................161

6.3.5 Accessing Individual Characters of Subscripted Substitution Symbols...................................................................161

6.3.6 Substitution Symbols as Local Variables in Macros................................................................................................ 162

6.4 Macro Libraries.............................................................................................................................................................. 163

6.5 Using Conditional Assembly in Macros..........................................................................................................................163

6.6 Using Labels in Macros..................................................................................................................................................165

6.7 Producing Messages in Macros..................................................................................................................................... 166

6.8 Using Directives to Format the Output Listing................................................................................................................166

6.9 Using Recursive and Nested Macros.............................................................................................................................168

6.10 Macro Directives Summary.......................................................................................................................................... 169

7 Archiver Description.......................................................................................................................................................... 171

7.1 Archiver Overview.......................................................................................................................................................... 172

7.2 The Archiver's Role in the Software Development Flow................................................................................................ 172

7.3 Invoking the Archiver......................................................................................................................................................173

7.4 Archiver Examples......................................................................................................................................................... 173

7.5 Library Information Archiver Description........................................................................................................................ 175

7.5.1 Invoking the Library Information Archiver................................................................................................................ 175

7.5.2 Library Information Archiver Example..................................................................................................................... 176

7.5.3 Listing the Contents of an Index Library.................................................................................................................. 176

7.5.4 Requirements.......................................................................................................................................................... 176

8 Linker Description.............................................................................................................................................................. 177

8.1 Linker Overview............................................................................................................................................................. 178

8.2 The Linker's Role in the Software Development Flow....................................................................................................178

8.3 Invoking the Linker......................................................................................................................................................... 179

8.4 Linker Options................................................................................................................................................................ 180

8.4.1 Wildcards in File, Section, and Symbol Patterns.....................................................................................................182

8.4.2 Specifying C/C++ Symbols with Linker Options...................................................................................................... 182

8.4.3 Relocation Capabilities (--absolute_exe and --relocatable Options)....................................................................... 182

8.4.4 Allocate Memory for Use by the Loader to Pass Arguments (--arg_size Option)....................................................183

8.4.5 Compression (--cinit_compression and --copy_compression Option).....................................................................184

8.4.6 Compress DWARF Information (--compress_dwarf Option)................................................................................... 184

8.4.7 Control Linker Diagnostics.......................................................................................................................................184

8.4.8 Automatic Library Selection (--disable_auto_rts Option)......................................................................................... 185

8.4.9 Disable Conditional Linking (--disable_clink Option)............................................................................................... 185

8.4.10 Do Not Remove Unused Sections (--unused_section_elimination Option)........................................................... 185

8.4.11 Linker Command File Preprocessing (--disable_pp, --define and --undefine Options)..........................................185

8.4.12 Error Correcting Code Testing (--ecc Options)...................................................................................................... 187

8.4.13 Define an Entry Point (--entry_point Option)......................................................................................................... 188

8.4.14 Set Default Fill Value (--fill_value Option)..............................................................................................................188

8.4.15 Define Heap Size (--heap_size Option).................................................................................................................189

8.4.16 Hiding Symbols......................................................................................................................................................189

8.4.17 Alter the Library Search Algorithm (--library, --search_path, and C2000_C_DIR )................................................189

8.4.18 Change Symbol Localization................................................................................................................................. 192

8.4.19 Create a Map File (--map_file Option)................................................................................................................... 193

8.4.20 Managing Map File Contents (--mapfile_contents Option).................................................................................... 194

8.4.21 Disable Name Demangling (--no_demangle)........................................................................................................ 195

8.4.22 Disable Merging of Symbolic Debugging Information (--no_sym_merge Option) ................................................ 196

8.4.23 Strip Symbolic Information (--no_symtable Option)...............................................................................................196

8.4.24 Name an Output Module (--output_file Option)..................................................................................................... 196

8.4.25 Prioritizing Function Placement (--preferred_order Option)...................................................................................197

8.4.26 C Language Options (--ram_model and --rom_model Options)............................................................................ 197

8.4.27 Retain Discarded Sections (--retain Option)..........................................................................................................197

8.4.28 Create an Absolute Listing File (--run_abs Option)............................................................................................... 198

8.4.29 Scan All Libraries for Duplicate Symbol Definitions (--scan_libraries)...................................................................198

8.4.30 Define Stack Size (--stack_size Option)................................................................................................................ 198

8.4.31 Enforce Strict Compatibility (--strict_compatibility Option).....................................................................................198

8.4.32 Mapping of Symbols (--symbol_map Option)........................................................................................................ 198

8.4.33 Introduce an Unresolved Symbol (--undef_sym Option)....................................................................................... 199

8.4.34 Display a Message When an Undefined Output Section Is Created (--warn_sections)........................................ 199

8.4.35 Generate XML Link Information File (--xml_link_info Option)................................................................................199

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

TMS320C28x Assembly Language Tools

v20.12.0.STS

5

Page 6

Table of Contents

www.ti.com

8.4.36 Zero Initialization (--zero_init Option).................................................................................................................... 199

8.5 Linker Command Files................................................................................................................................................... 200

8.5.1 Reserved Names in Linker Command Files............................................................................................................ 201

8.5.2 Constants in Linker Command Files........................................................................................................................201

8.5.3 Accessing Files and Libraries from a Linker Command File................................................................................... 201

8.5.4 The MEMORY Directive.......................................................................................................................................... 203

8.5.5 The SECTIONS Directive........................................................................................................................................ 206

8.5.6 Placing a Section at Different Load and Run Addresses.........................................................................................219

8.5.7 Using GROUP and UNION Statements.................................................................................................................. 222

8.5.8 Overlaying Pages.................................................................................................................................................... 227

8.5.9 Special Section Types (DSECT, COPY, NOLOAD, and NOINIT)............................................................................ 229

8.5.10 Configuring Error Correcting Code (ECC) with the Linker.....................................................................................230

8.5.11 Assigning Symbols at Link Time............................................................................................................................ 232

8.5.12 Creating and Filling Holes..................................................................................................................................... 238

8.6 Linker Symbols...............................................................................................................................................................242

8.6.1 Using Linker Symbols in C/C++ Applications.......................................................................................................... 242

8.6.2 Declaring Weak Symbols.........................................................................................................................................243

8.6.3 Resolving Symbols with Object Libraries................................................................................................................ 243

8.7 Default Placement Algorithm..........................................................................................................................................244

8.7.1 How the Allocation Algorithm Creates Output Sections.......................................................................................... 245

8.7.2 Reducing Memory Fragmentation........................................................................................................................... 245

8.8 Using Linker-Generated Copy Tables............................................................................................................................ 245

8.8.1 Using Copy Tables for Boot Loading....................................................................................................................... 246

8.8.2 Using Built-in Link Operators in Copy Tables.......................................................................................................... 246

8.8.3 Overlay Management Example............................................................................................................................... 247

8.8.4 Generating Copy Tables With the table() Operator................................................................................................. 247

8.8.5 Compression........................................................................................................................................................... 251

8.8.6 Copy Table Contents............................................................................................................................................... 255

8.8.7 General Purpose Copy Routine...............................................................................................................................256

8.9 Linker-Generated CRC Tables and CRC Over Memory Ranges................................................................................... 257

8.9.1 Using the crc_table() Operator in the SECTIONS Directive.................................................................................... 257

8.9.2 Using the crc() Operator in the MEMORY Directive................................................................................................ 262

8.9.3 A Special Note Regarding 16-Bit char.....................................................................................................................266

8.10 Partial (Incremental) Linking........................................................................................................................................ 267

8.11 Linking C/C++ Code.....................................................................................................................................................268

8.11.1 Run-Time Initialization........................................................................................................................................... 268

8.11.2 Object Libraries and Run-Time Support................................................................................................................ 268

8.11.3 Setting the Size of the Stack and Heap Sections.................................................................................................. 268

8.11.4 Initializing and AutoInitialzing Variables at Run Time.............................................................................................269

8.12 Linker Example............................................................................................................................................................ 269

9 Absolute Lister Description...............................................................................................................................................273

9.1 Producing an Absolute Listing........................................................................................................................................274

9.2 Invoking the Absolute Lister........................................................................................................................................... 275

9.3 Absolute Lister Example................................................................................................................................................ 276

10 Cross-Reference Lister Description............................................................................................................................... 279

10.1 Producing a Cross-Reference Listing.......................................................................................................................... 280

10.2 Invoking the Cross-Reference Lister............................................................................................................................281

10.3 Cross-Reference Listing Example................................................................................................................................282

11 Object File Utilities............................................................................................................................................................283

11.1 Invoking the Object File Display Utility......................................................................................................................... 284

11.2 Invoking the Disassembler........................................................................................................................................... 285

11.3 Invoking the Name Utility..............................................................................................................................................285

11.4 Invoking the Strip Utility................................................................................................................................................286

12 Hex Conversion Utility Description.................................................................................................................................287

12.1 The Hex Conversion Utility's Role in the Software Development Flow........................................................................ 288

12.2 Invoking the Hex Conversion Utility............................................................................................................................. 289

12.2.1 Invoking the Hex Conversion Utility From the Command Line.............................................................................. 289

12.2.2 Invoking the Hex Conversion Utility With a Command File................................................................................... 292

12.3 Understanding Memory Widths....................................................................................................................................293

12.3.1 Target Width.......................................................................................................................................................... 293

12.3.2 Specifying the Memory Width................................................................................................................................293

6 TMS320C28x Assembly Language Tools

v20.12.0.STS

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Page 7

www.ti.com

Table of Contents

12.3.3 Partitioning Data Into Output Files.........................................................................................................................294

12.3.4 Specifying Word Order for Output Words..............................................................................................................297

12.4 The ROMS Directive.................................................................................................................................................... 297

12.4.1 When to Use the ROMS Directive......................................................................................................................... 298

12.4.2 An Example of the ROMS Directive...................................................................................................................... 299

12.5 The SECTIONS Directive.............................................................................................................................................300

12.6 The Load Image Format (--load_image Option)...........................................................................................................302

12.6.1 Load Image Section Formation............................................................................................................................. 302

12.6.2 Load Image Characteristics...................................................................................................................................302

12.7 Excluding a Specified Section......................................................................................................................................303

12.8 Assigning Output Filenames........................................................................................................................................ 303

12.9 Image Mode and the --fill Option..................................................................................................................................304

12.9.1 Generating a Memory Image.................................................................................................................................304

12.9.2 Specifying a Fill Value............................................................................................................................................304

12.9.3 Steps to Follow in Using Image Mode................................................................................................................... 305

12.10 Array Output Format.................................................................................................................................................. 305

12.11 Building a Table for an On-Chip Boot Loader.............................................................................................................305

12.11.1 Description of the Boot Table...............................................................................................................................305

12.11.2 The Boot Table Format........................................................................................................................................ 305

12.11.3 How to Build the Boot Table.................................................................................................................................306

12.11.4 Booting From a Device Peripheral.......................................................................................................................306

12.11.5 Setting the Entry Point for the Boot Table............................................................................................................307

12.11.6 Using the C28x Boot Loader................................................................................................................................307

12.12 Using Secure Flash Boot on TMS320F2838x Devices.............................................................................................. 312

12.13 Controlling the ROM Device Address........................................................................................................................ 313

12.14 Control Hex Conversion Utility Diagnostics................................................................................................................314

12.15 Description of the Object Formats..............................................................................................................................315

12.15.1 ASCII-Hex Object Format (--ascii Option)........................................................................................................... 315

12.15.2 Intel MCS-86 Object Format (--intel Option)........................................................................................................316

12.15.3 Motorola Exorciser Object Format (--motorola Option)....................................................................................... 317

12.15.4 Extended Tektronix Object Format (--tektronix Option)....................................................................................... 318

12.15.5 Texas Instruments SDSMAC (TI-Tagged) Object Format (--ti_tagged Option)................................................... 319

12.15.6 TI-TXT Hex Format (--ti_txt Option).....................................................................................................................320

12.16 Hex Conversion Utility Error Messages..................................................................................................................... 321

13 Sharing C/C++ Header Files With Assembly Source.....................................................................................................323

13.1 Overview of the .cdecls Directive................................................................................................................................. 324

13.2 Notes on C/C++ Conversions...................................................................................................................................... 324

13.2.1 Comments............................................................................................................................................................. 324

13.2.2 Conditional Compilation (#if/#else/#ifdef/etc.)....................................................................................................... 325

13.2.3 Pragmas................................................................................................................................................................ 325

13.2.4 The #error and #warning Directives...................................................................................................................... 325

13.2.5 Predefined symbol __ASM_HEADER__............................................................................................................... 325

13.2.6 Usage Within C/C++ asm( ) Statements............................................................................................................... 325

13.2.7 The #include Directive........................................................................................................................................... 325

13.2.8 Conversion of #define Macros...............................................................................................................................325

13.2.9 The #undef Directive............................................................................................................................................. 326

13.2.10 Enumerations...................................................................................................................................................... 326

13.2.11 C Strings..............................................................................................................................................................326

13.2.12 C/C++ Built-In Functions..................................................................................................................................... 327

13.2.13 Structures and Unions......................................................................................................................................... 327

13.2.14 Function/Variable Prototypes...............................................................................................................................328

13.2.15 C Constant Suffixes.............................................................................................................................................328

13.2.16 Basic C/C++ Types..............................................................................................................................................328

13.3 Notes on C++ Specific Conversions............................................................................................................................ 328

13.3.1 Name Mangling..................................................................................................................................................... 328

13.3.2 Derived Classes.................................................................................................................................................... 329

13.3.3 Templates.............................................................................................................................................................. 329

13.3.4 Virtual Functions....................................................................................................................................................329

13.4 Special Assembler Support..........................................................................................................................................329

13.4.1 Enumerations (.enum/.emember/.endenum).........................................................................................................329

13.4.2 The .define Directive..............................................................................................................................................330

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

TMS320C28x Assembly Language Tools

v20.12.0.STS

7

Page 8

Table of Contents

www.ti.com

13.4.3 The .undefine/.unasg Directives............................................................................................................................ 330

13.4.4 The $defined( ) Built-In Function........................................................................................................................... 330

13.4.5 The $sizeof Built-In Function................................................................................................................................. 330

13.4.6 Structure/Union Alignment and $alignof( ).............................................................................................................331

13.4.7 The .cstring Directive.............................................................................................................................................331

A Symbolic Debugging Directives....................................................................................................................................... 333

A.1 DWARF Debugging Format...........................................................................................................................................334

A.2 Debug Directive Syntax................................................................................................................................................. 334

B XML Link Information File Description.............................................................................................................................335

B.1 XML Information File Element Types.............................................................................................................................336

B.2 Document Elements...................................................................................................................................................... 336

B.2.1 Header Elements.................................................................................................................................................... 336

B.2.2 Input File List...........................................................................................................................................................337

B.2.3 Object Component List............................................................................................................................................338

B.2.4 Logical Group List................................................................................................................................................... 339

B.2.5 Placement Map....................................................................................................................................................... 341

B.2.6 Symbol Table...........................................................................................................................................................342

C CRC Reference Implementation........................................................................................................................................343

C.1 Compilation Instructions................................................................................................................................................ 344

C.2 Reference CRC Calculation Routine............................................................................................................................. 344

Example C-1. Reference Implementation of a CRC Calculation Function: ref_crc.c....................................................... 344

C.3 Linker-Generated Copy Tables and CRC Tables...........................................................................................................347

Example C-2. Main Routine for Example Application: main.c.......................................................................................... 347

Example C-3. Checking CRC Values: check_crc.c.......................................................................................................... 348

Example C-4. Task1 Routine: task1.c...............................................................................................................................348

Example C-5. Task2 Routine: task2.c...............................................................................................................................348

Example C-6. Task3 Routine: task3.c...............................................................................................................................349

Example C-7. Example 1 Command File: ex1.cmd (for COFF)....................................................................................... 349

D Glossary..............................................................................................................................................................................351

D.1 Terminology................................................................................................................................................................... 351

Revision History.................................................................................................................................................................... 358

List of Figures

Figure 1-1. TMS320C28x Software Development Flow............................................................................................................ 16

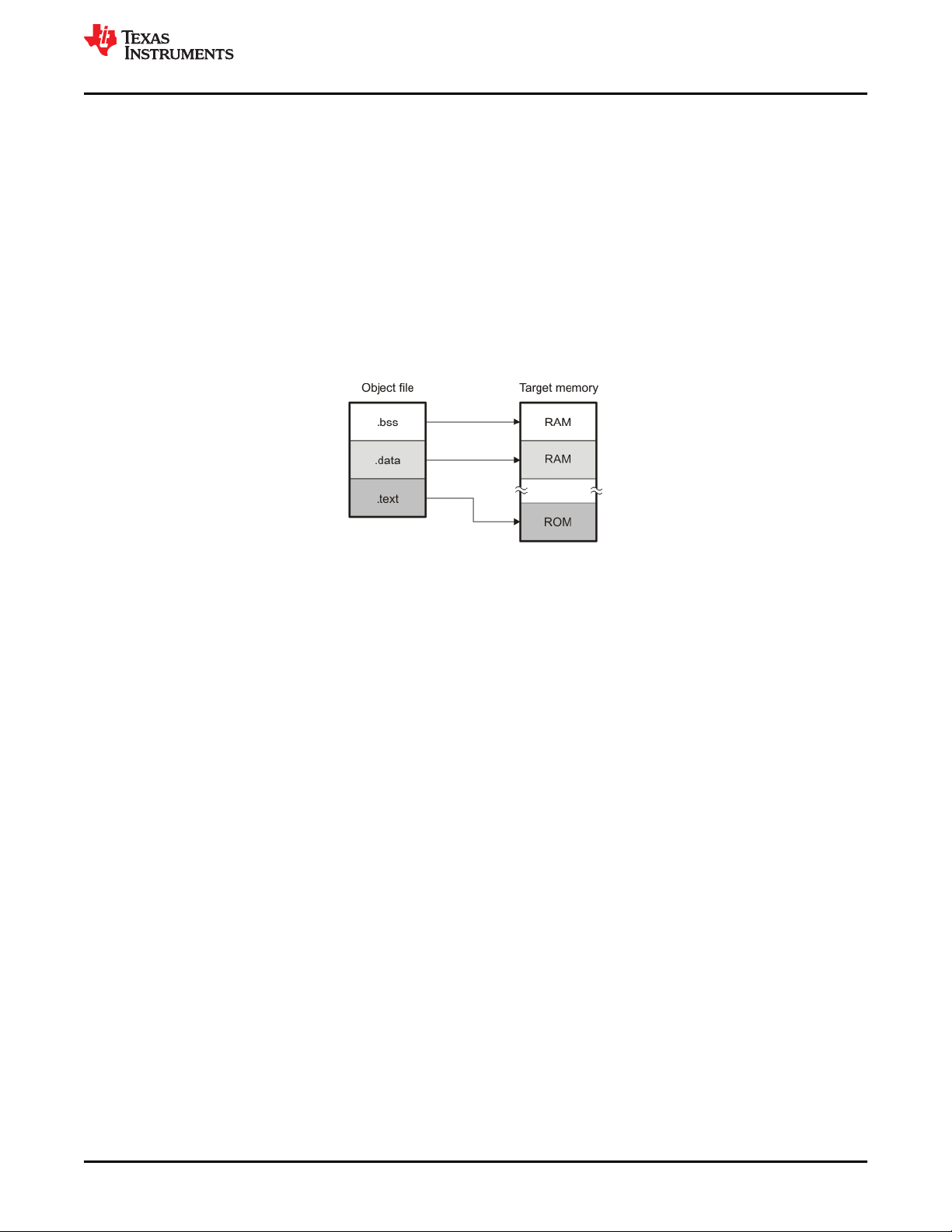

Figure 2-1. Partitioning Memory Into Logical Blocks................................................................................................................. 21

Figure 2-2. Using Sections Directives Example.........................................................................................................................26

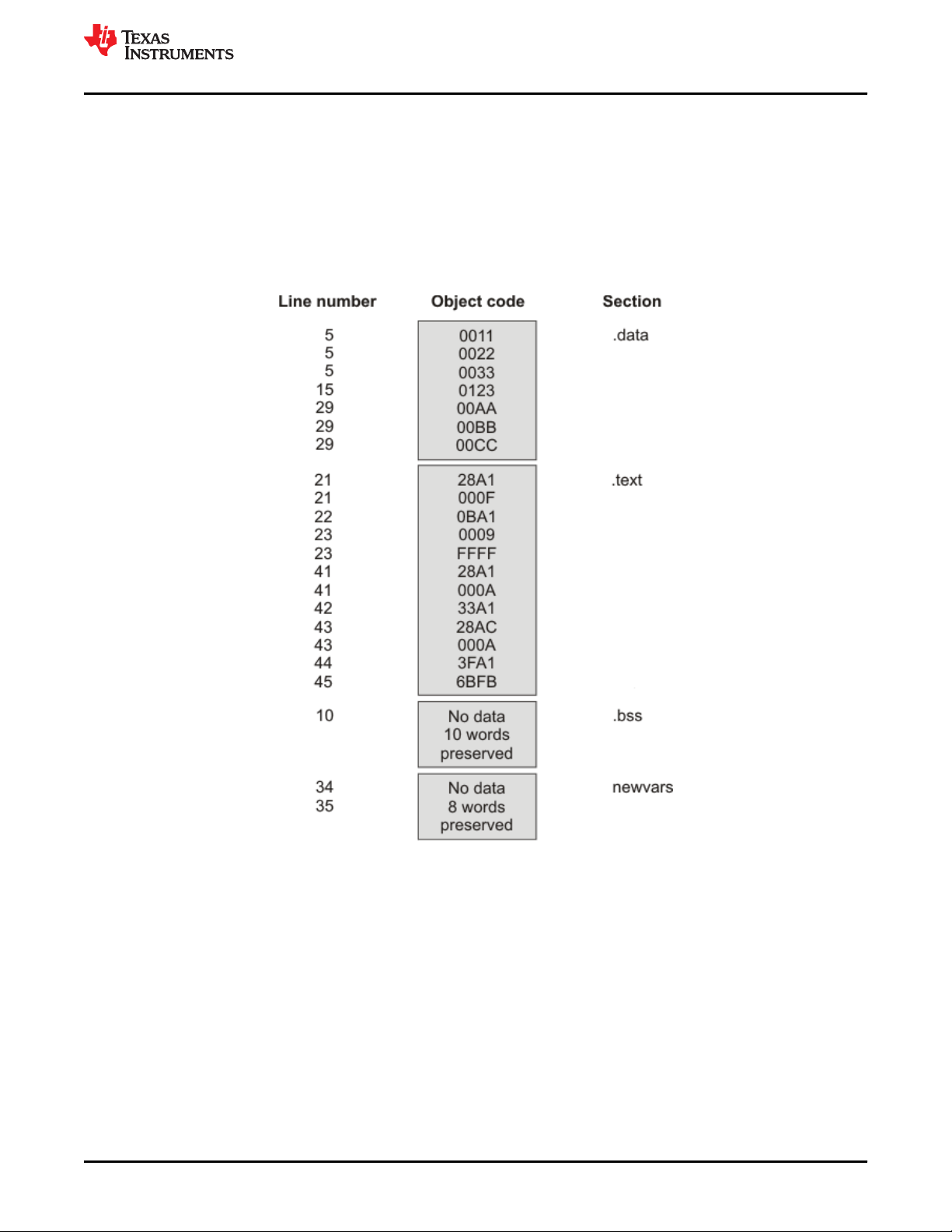

Figure 2-3. Object Code Generated by the File in Figure 2-2 ...................................................................................................27

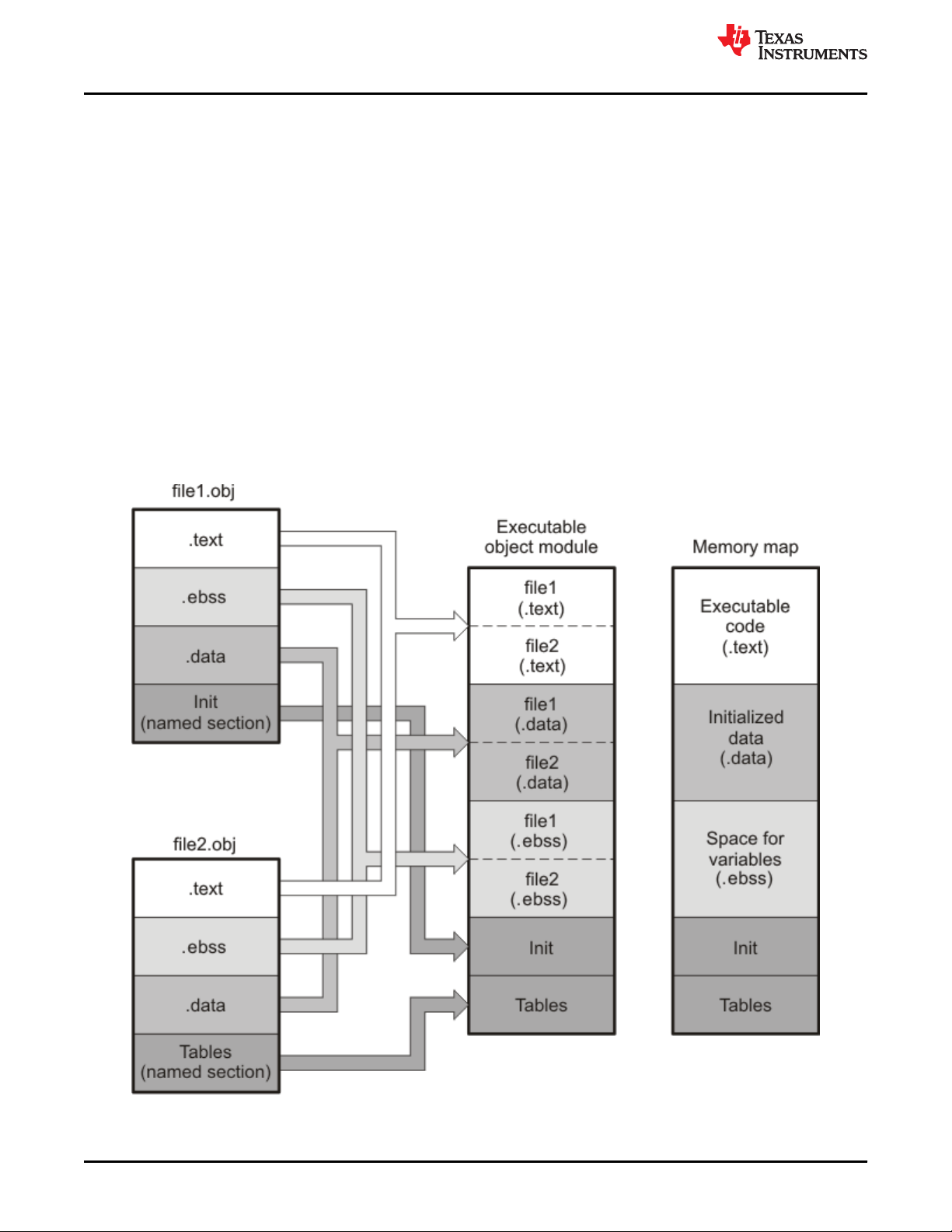

Figure 2-4. Combining Input Sections to Form an Executable Object Module.......................................................................... 28

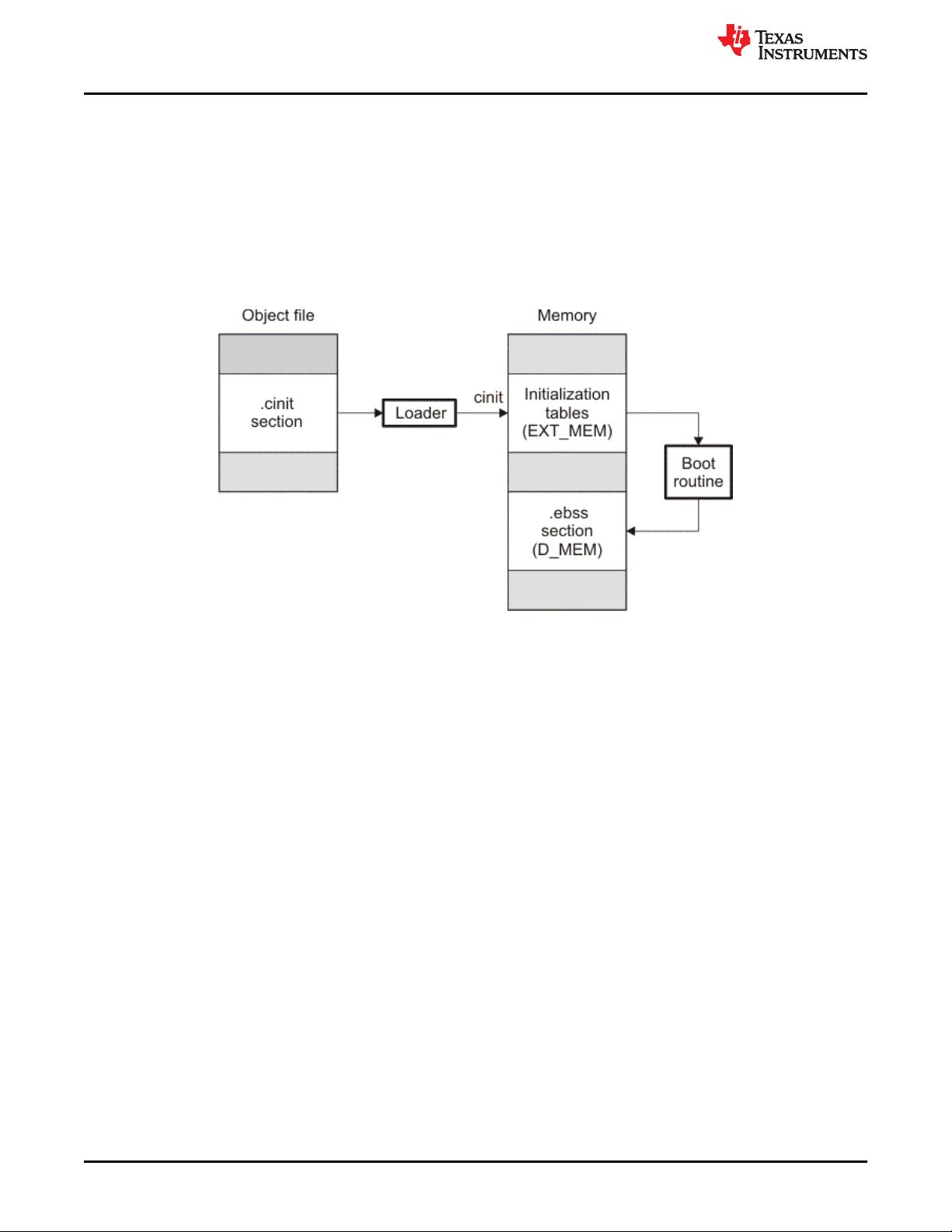

Figure 3-1. Bootloading Sequence (Simplified)......................................................................................................................... 37

Figure 3-2. Bootloading Sequence with Secondary Bootloader................................................................................................ 38

Figure 3-3. Autoinitialization at Run Time..................................................................................................................................42

Figure 3-4. Initialization at Load Time........................................................................................................................................43

Figure 4-1. The Assembler in the TMS320C28x Software Development Flow......................................................................... 47

Figure 4-2. Example Assembler Listing..................................................................................................................................... 70

Figure 5-1. The .field Directive...................................................................................................................................................84

Figure 5-2. Initialization Directives.............................................................................................................................................85

Figure 5-3. The .align Directive..................................................................................................................................................86

Figure 5-4. The .space and .bes Directives............................................................................................................................... 87

Figure 5-5. The .field Directive.................................................................................................................................................114

Figure 5-6. Single-Precision Floating-Point Format................................................................................................................. 115

Figure 5-7. The .usect Directive...............................................................................................................................................153

Figure 7-1. The Archiver in the TMS320C28x Software Development Flow........................................................................... 172

Figure 8-1. The Linker in the TMS320C28x Software Development Flow...............................................................................178

Figure 8-2. Memory Map Defined in The MEMORY Directive ................................................................................................205

Figure 8-3. Section Placement Defined by The SECTIONS Directive ....................................................................................208

Figure 8-4. Run-Time Execution of Moving a Function from Slow to Fast Memory at Run Time ...........................................222

Figure 8-5. Memory Allocation Shown in The UNION Statement and Separate Load Addresses for UNION Sections .........224

Figure 8-6. Overlay Pages Defined in Example 8-5 and Example 8-6 ................................................................................... 229

Figure 8-7. Compressed Copy Table....................................................................................................................................... 251

Figure 8-8. Handler Table........................................................................................................................................................ 252

Figure 8-9. CRC_TABLE Conceptual Model............................................................................................................................260

8 TMS320C28x Assembly Language Tools

v20.12.0.STS

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Page 9

www.ti.com

Table of Contents

Figure 8-10. CRC Storage Format for Memory Ranges.......................................................................................................... 265

Figure 8-11. CRC Data Flow Example.....................................................................................................................................266

Figure 9-1. Absolute Lister Development Flow........................................................................................................................274

Figure 10-1. The Cross-Reference Lister Development Flow................................................................................................. 280

Figure 12-1. The Hex Conversion Utility in the TMS320C28x Software Development Flow................................................... 288

Figure 12-2. Hex Conversion Utility Process Flow.................................................................................................................. 293

Figure 12-3. Object File Data and Memory Widths..................................................................................................................294

Figure 12-4. Data, Memory, and ROM Widths.........................................................................................................................296

Figure 12-5. The infile.out File Partitioned Into Four Output Files........................................................................................... 299

Figure 12-6. Sample Hex Converter Out File for Booting From 8-Bit SPI Boot....................................................................... 309

Figure 12-7. Sample Hex Converter Out File for C28x 16-Bit Parallel Boot GP I/O................................................................ 310

Figure 12-8. Sample Hex Converter Out File for Booting From 8-Bit SCI Boot....................................................................... 311

Figure 12-9. ASCII-Hex Object Format....................................................................................................................................315

Figure 12-10. Intel Hexadecimal Object Format...................................................................................................................... 316

Figure 12-11. Motorola-S Format.............................................................................................................................................317

Figure 12-12. Extended Tektronix Object Format.................................................................................................................... 318

Figure 12-13. TI-Tagged Object Format.................................................................................................................................. 319

Figure 12-14. TI-TXT Object Format....................................................................................................................................... 321

List of Tables

Table 4-1. TMS320C28x Assembler Options.............................................................................................................................48

Table 4-2. C28x Processor Symbolic Constants........................................................................................................................61

Table 4-3. CPU and CPU Control Registers.............................................................................................................................. 62

Table 4-4. FPU and FPU Control Registers............................................................................................................................... 62

Table 4-5. VCU Registers.......................................................................................................................................................... 62

Table 4-6. Operators Used in Expressions (Precedence)..........................................................................................................64

Table 4-7. Built-In Mathematical Functions................................................................................................................................ 66

Table 4-8. Symbol Attributes...................................................................................................................................................... 72

Table 4-9. Smart Encoding for Efficiency................................................................................................................................... 73

Table 4-10. Smart Encoding Intuitively...................................................................................................................................... 73

Table 4-11. Instructions That Avoid Smart Encoding................................................................................................................. 74

Table 5-1. Directives that Control Section Use.......................................................................................................................... 78

Table 5-2. Directives that Gather Sections into Common Groups............................................................................................. 78

Table 5-3. Directives that Affect Unused Section Elimination.................................................................................................... 78

Table 5-4. Directives that Initialize Values (Data and Memory)..................................................................................................78

Table 5-5. Directives that Perform Alignment and Reserve Space............................................................................................ 79

Table 5-6. Directives that Format the Output Listing..................................................................................................................79

Table 5-7. Directives that Reference Other Files....................................................................................................................... 80

Table 5-8. Directives that Affect Symbol Linkage and Visibility..................................................................................................80

Table 5-9. Directives that Define Symbols at Assembly Time ...................................................................................................80

Table 5-10. Directives that Enable Conditional Assembly......................................................................................................... 80

Table 5-11. Directives that Define Union or Structure Types..................................................................................................... 81

Table 5-12. Directives that Create or Affect Macros.................................................................................................................. 81

Table 5-13. Directives that Control Diagnostics......................................................................................................................... 81

Table 5-14. Directives that Perform Assembly Source Debug................................................................................................... 81

Table 5-15. Directives that Are Used by the Absolute Lister......................................................................................................81

Table 5-16. Directives that Perform Miscellaneous Functions................................................................................................... 81

Table 6-1. Substitution Symbol Functions and Return Values................................................................................................. 160

Table 6-2. Creating Macros......................................................................................................................................................169

Table 6-3. Manipulating Substitution Symbols......................................................................................................................... 169

Table 6-4. Conditional Assembly............................................................................................................................................. 169

Table 6-5. Producing Assembly-Time Messages.....................................................................................................................169

Table 6-6. Formatting the Listing............................................................................................................................................. 169

Table 8-1. Basic Options Summary......................................................................................................................................... 180

Table 8-2. File Search Path Options Summary........................................................................................................................180

Table 8-3. Command File Preprocessing Options Summary................................................................................................... 180

Table 8-4. Diagnostic Options Summary................................................................................................................................. 180

Table 8-5. Linker Output Options Summary.............................................................................................................................181

Table 8-6. Symbol Management Options Summary................................................................................................................ 181

Table 8-7. Run-Time Environment Options Summary............................................................................................................. 181

Table 8-8. Link-Time Optimization Options Summary..............................................................................................................181

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

TMS320C28x Assembly Language Tools

v20.12.0.STS

9

Page 10

Table of Contents www.ti.com

Table 8-9. Miscellaneous Options Summary........................................................................................................................... 182

Table 8-10. Predefined C28x Macro Names............................................................................................................................ 186

Table 8-11. Groups of Operators Used in Expressions (Precedence)..................................................................................... 234

Table 10-1. Symbol Attributes in Cross-Reference Listing...................................................................................................... 282

Table 12-1. Basic Hex Conversion Utility Options................................................................................................................... 289

Table 12-2. Boot-Loader Options............................................................................................................................................. 306

Table 12-3. Boot Table Source Formats.................................................................................................................................. 307

Table 12-4. Boot Table Format.................................................................................................................................................307

Table 12-5. Options for Specifying Hex Conversion Formats.................................................................................................. 315

Table A-1. Symbolic Debugging Directives.............................................................................................................................. 334

10 TMS320C28x Assembly Language Tools

v20.12.0.STS

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

Page 11

www.ti.com Read This First

Preface

Read This First

About This Manual

The TMS320C28x Assembly Language Tools User's Guide explains how to use the following Texas Instruments

Code Generation object file tools:

• Assembler

• Archiver

• Linker

• Library information archiver

• Absolute lister

• Cross-reference lister

• Disassembler

• Object file display utility

• Name utility

• Strip utility

• Hex conversion utility

How to Use This Manual

This book helps you learn how to use the Texas Instruments object file and assembly language tools designed

specifically for the TMS320C28x™ 16-bit devices. This book consists of four parts:

• Introductory information, consisting of Chapter 1 through Chapter 3, gives you an overview of the object

file and assembly language development tools. Chapter 2, in particular, explains object modules and how

they can be managed to help your TMS320C28x application load and run. It is highly recommended that

developers become familiar with what object modules are and how they are used before using the assembler

and linker.

• Assembler description, consisting of Chapter 4 through Chapter 6, contains detailed information about

using the assembler. Chapter 4 and Chapter 5 explain how to invoke the assembler and discuss source

statement format, valid constants and expressions, assembler output, and assembler directives. Chapter 6

focuses on the macro language.

• Linker and other object file tools description, consisting of Chapter 7 through Chapter 12, describes in

detail each of the tools provided with the assembler to help you create executable object files. Chapter 7

provides details about using the archiver to create object libraries. Chapter 8 explains how to invoke the

linker, how the linker operates, and how to use linker directives. Chapter 11 provides a brief overview of some

of the object file utilities that can be useful in examining the content of object files as well as removing symbol

and debug information to reduce the size of a given object file. Chapter 12 explains how to use the hex

conversion utility.

• Additional Reference material, consisting of Appendix A through Appendix D, provides supplementary

information including symbolic debugging directives used by the TMS320C28x C/C++ compiler. A description

of the XML link information file and a glossary are also provided.

SPRU513V – JULY 2001 – REVISED DECEMBER 2020

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

TMS320C28x Assembly Language Tools

v20.12.0.STS

11

Page 12

Read This First www.ti.com

Notational Conventions

This document uses the following conventions:

• Program listings, program examples, and interactive displays are shown in a special typeface .

Interactive displays use a bold version of the special typeface to distinguish commands that you enter from

items that the system displays (such as prompts, command output, error messages, etc.).

Here is a sample of C code:

#include <stdio.h>

main()

{ printf("hello world\n");

}

• In syntax descriptions, the instruction, command, or directive is in a bold typeface and parameters are in an

italic typeface. Portions of a syntax that are in bold should be entered as shown; portions of a syntax that are

in italics describe the type of information that should be entered.

• Square brackets ( [ and ] ) identify an optional parameter. If you use an optional parameter, you specify the

information within the brackets. Unless the square brackets are in the bold typeface, do not enter the

brackets themselves. The following is an example of a command that has an optional parameter:

cl2000 [options] [filenames] [--run_linker [link_options] [object files]]

• Braces ( { and } ) indicate that you must choose one of the parameters within the braces; you do not enter the

braces themselves. This is an example of a command with braces that are not included in the actual syntax

but indicate that you must specify either the --rom_model or --ram_model option:

cl2000 --run_linker

[--output_file= name.out] --library= libraryname

{--rom_model | --ram_model} filenames

• In assembler syntax statements, The leftmost character position, column 1, is reserved for the first character