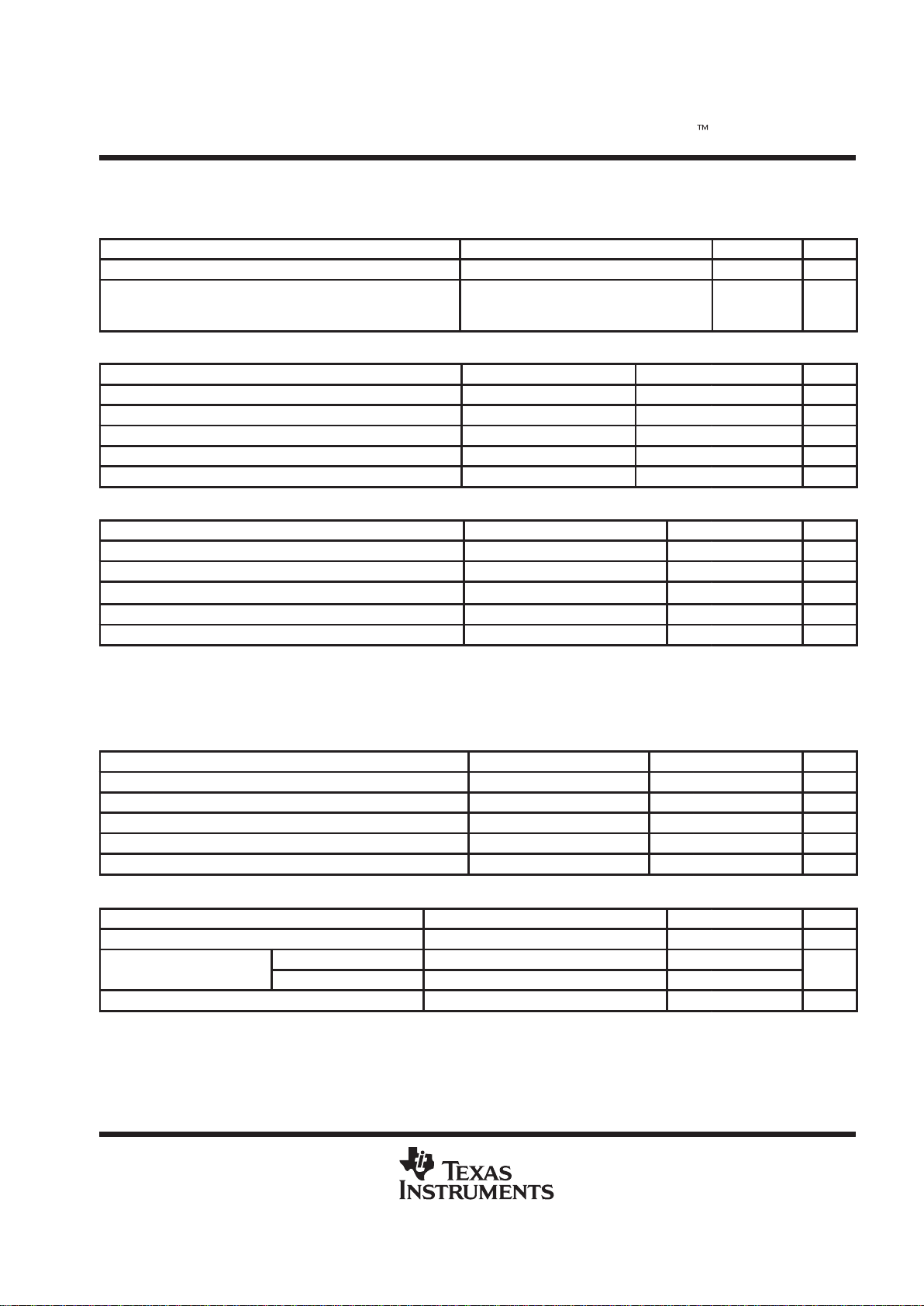

1

2

3

4

5

6

7

14

13

12

11

10

9

8

DV

DD

AV

DD

SIG

DC OFFSET

MID

GND

BW

CLK

TEST

TRACKINH

EXTS0

EXTS1

CON2

CON1

D PACKAGE

(TOP VIEW)

TLV5592

2-BIT ANALOG-TO-DIGITAL CONVERTER

FOR FLEXt PAGER CHIPSET

SLAS145A – JUNE1996 – REVISED DECEMBER 1997

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Supports FLEXt Protocol Messaging Systems

With The TLV559X FLEX Decoder

D

3-Pole Butterworth Low-Pass Selectable

Dual-Bandwidth Audio Filter

– BW 1 = 1 kHz ±5% (– 3 dB)

– BW 2 = 2 kHz ±5% (– 3 dB)

D

Both Peak and Valley Detectors Available

D

2-Bit Analog-to-Digital Converter

D

Operating Temperature Range –20°C to 65°C

D

Four Modes of Operation:

– Fast Track

– Slow Track

– Hold

– Standby

D

1.8-V to 2.5-V Single Power Supply

Operation

applications

D

FLEX Protocol Numeric and

Alphanumeric Messaging Systems

D

One-Way or Two-Way

description

The T exas Instruments (TI) TLV5592 analog-todigital converter (ADC) is a system level solution

to interface a 4-level baseband audio signal to a

digital decoder. The TLV5592 is a direct interface

to the TL V559X FLEX decoder . Designed primarily for messaging applications, the TL V5592 incorporates signal conditioning, both peak and valley

detection along with analog-to-digital conversion.

A selectable third-order Butterworth filter with

cutoff frequencies of 1 kHz and 2 kHz is included.

The peak and valley detectors are implemented

with a unique design that does not require external

capacitors. Two 8-bit digital-to-analog converters

(DACs) are used in a feedback loop to

automatically adjust to the peak and valley levels.

The DAC outputs are used to set V

ref+

and V

ref–

for

the 2-bit ADC. Modes of operation include fast

track, slow track, hold, and standby . The standby

mode maximizes battery life. The TLV5592

operates on a single power supply from 1.8 V to

2.5 V.

AVAILABLE OPTIONS

PACKAGE

T

A

SMALL OUTLINE

(D)

–25°C to 65°C TLV5592ED

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

FLEX is a trademark of Motorola Inc.

TI is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright 1997, Texas Instruments Incorporated

TLV5592

2-BIT ANALOG-TO-DIGITAL CONVERTER

FOR FLEXt PAGER CHIPSET

SLAS145A – JUNE1996 – REVISED DECEMBER 1997

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

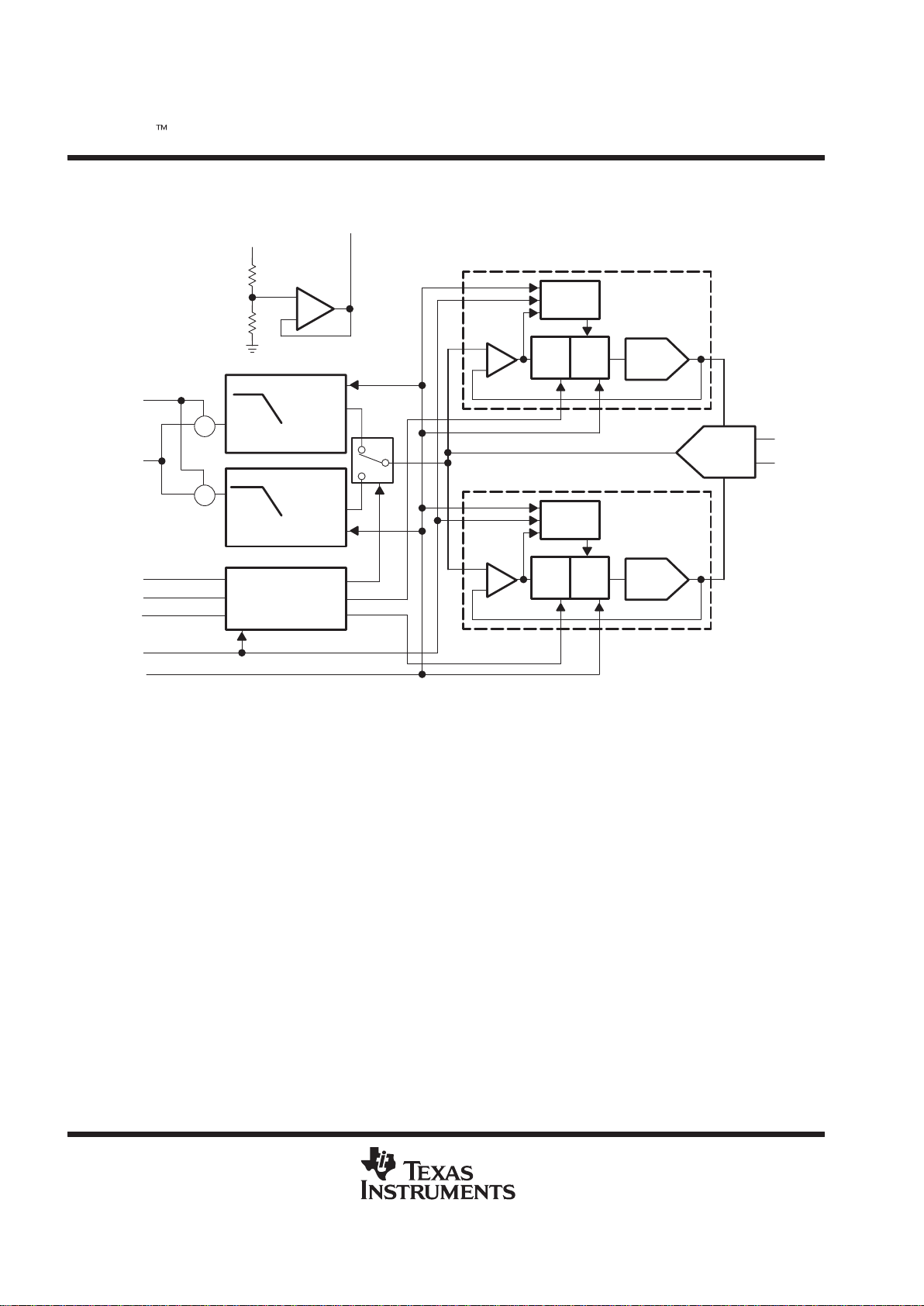

functional block diagram

_

+

8-Bit

DAC

CTR

2-Bit

ADC

fs = 1 kHz

Gain = 6 dB

nominal

3rd-Order Butterworth

3rd-Order Butterworth

Mode Control

and Enable

AV

DD

MID

Peak Detector

Valley Detector

REF +

REF –

EXTS0

EXTS1

DC OFFSET

SIG

CON1

CON2

BW

TRACKINH

11

10

5

2

4

3

8

9

7

12

Up/

Down

CLK

14

fs = 2 kHz

Gain = 6 dB

nominal

FILOUT

Σ

Σ

–

–

Decay

Counter

8-Bit

DAC

CTR

Up/

Down

Decay

Counter

TLV5592

2-BIT ANALOG-TO-DIGITAL CONVERTER

FOR FLEXt PAGER CHIPSET

SLAS145A – JUNE1996 – REVISED DECEMBER 1997

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

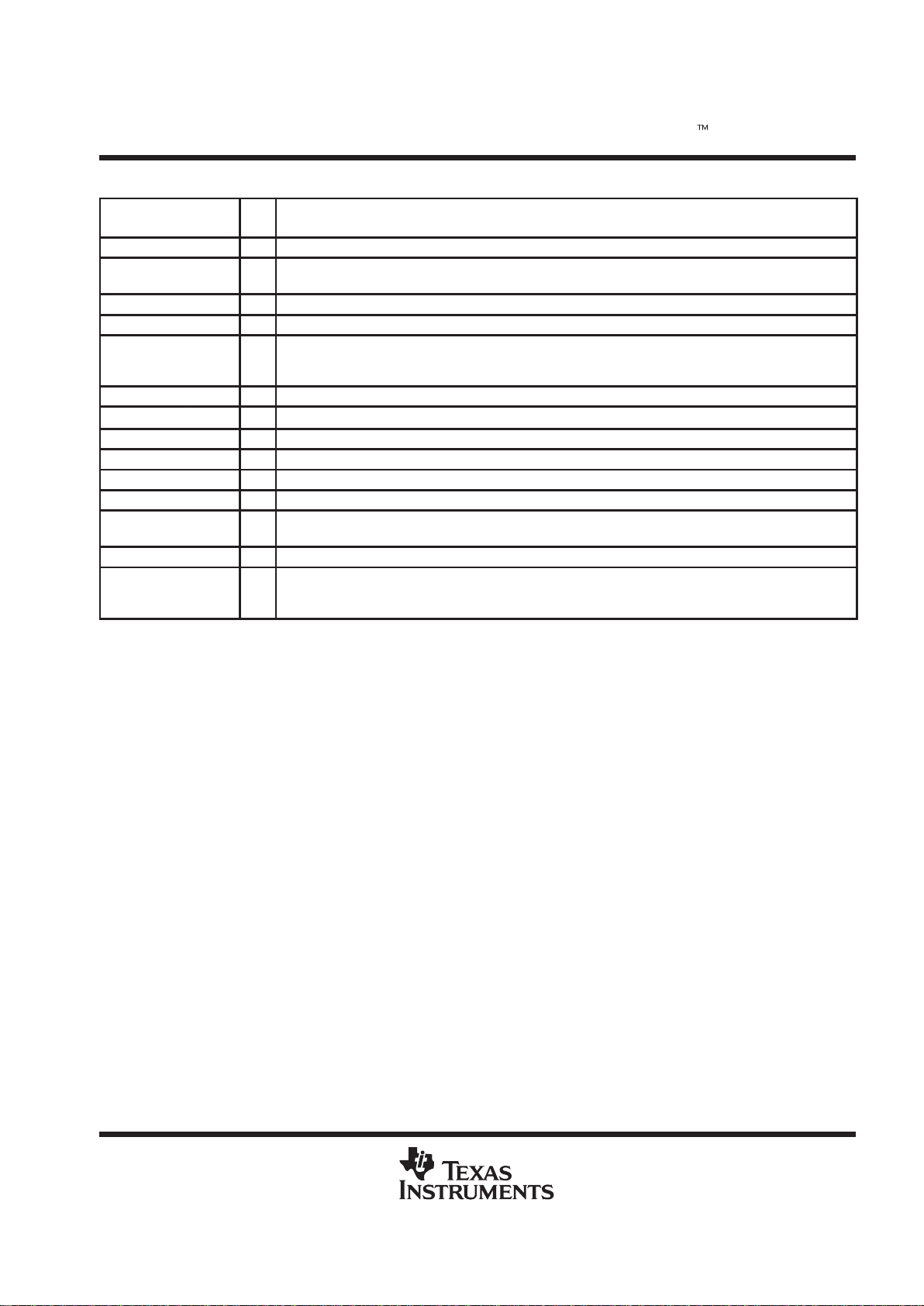

Terminal Functions

TERMINAL

I/O

NAME NO.

DESCRIPTION

AV

DD

2 I Analog supply voltage

BW 7 I Digital bandwidth select. A high level on BW selects the 2-kHz filter cutoff and a low level selects the 1-kHz

filter cutoff.

CON1 8 I Digital control 1 input. In conjunction with CON2, CON1 selects fast track, slow track, hold, or standby mode.

CON2 9 I Digital control 2 input. In conjunction with CON1, CON2 selects fast track, slow track, hold, or standby mode.

CLK 14 I Digital clock input. CLK input is a 50% duty cycle transistor-transistor logic (TTL)-level clock input with nominal

frequency of 38.4 kHz. The CLK input is edge sensitive in all non-test modes. For all test modes, the CLK input

is level sensitive.

DC OFFSET 4 I Analog dc offset correction input. The dc component of the audio signal should be applied to DC OFFSET.

DV

DD

1 I Digital supply voltage

EXTS0 11 O Digital output 0 of the ADC. Data bit 0 is the least significant bit (LSB).

EXTS1 10 O Digital output 1 of the ADC. Data bit 1 is the most significant bit (MSB).

GND 6 Return terminal for the IC current

MID 5 O Analog midpoint output. MID is a buffered output of AVDD/2.

SIG 3 I Analog audio signal input. An appropriate resistance capacitance (RC) low-pass filter (antialiasing filter)

should be connected to SIG.

TEST 13 I Digital test input enable. TEST should be connected to ground in normal operation.

TRACKINH 12 I Digital track inhibit logic input. A high level on TRACKINH disables the peak and valley detector counters; a

low level enables the peak and valley detector counters. The counters continue to decay at the decay rate while

TRACKINH is a low level.

TLV5592

2-BIT ANALOG-TO-DIGITAL CONVERTER

FOR FLEXt PAGER CHIPSET

SLAS145A – JUNE1996 – REVISED DECEMBER 1997

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage range, AV

DD

, DVDD –0.5 V to 6.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, V

I

–0.3 V to AV

DD

+ 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, EXTS0, EXTS1 –0.3 V to DV

DD

+ 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Offset input voltage, V

IO

–0.3 V to AV

DD

+ 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peak input current (any input) ±20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

–20°C to 65° C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

–65°C to 150° C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

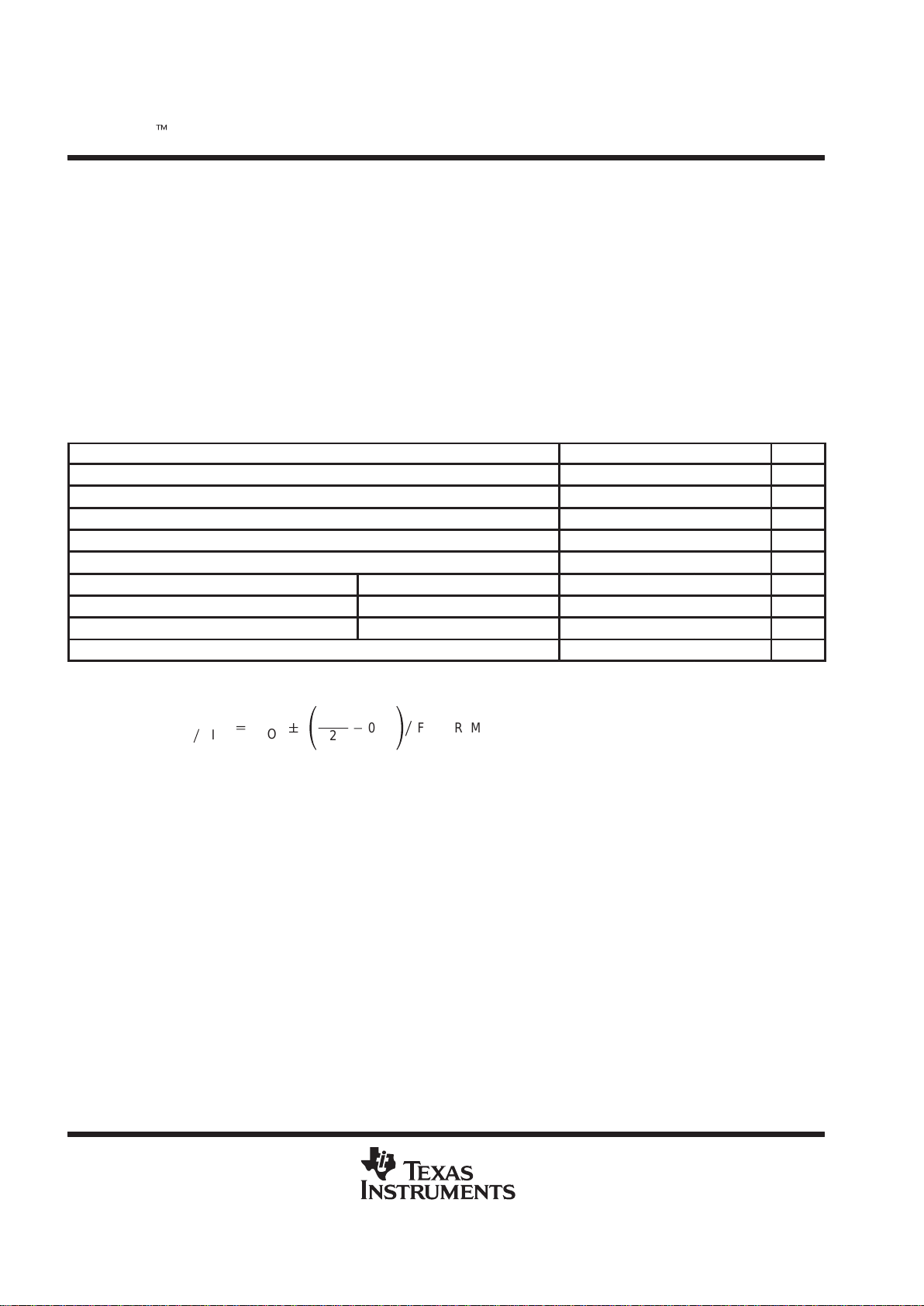

recommended operating conditions

MIN NOM MAX UNIT

Supply voltage, AVDD, DV

DD

1.8 2.5 V

Power supply ripple 0.001 V

pp

Input clock frequency, f

(CLK)

38.4 kHz

Input clock duty cycle 45 50 55 %

Voltage of fset applied at DC OFFSET, V

I(DC OFFSET)

(see Note 2) 0.25 VDD–0.25 V

Analog input voltage, V

I(pp)

(See Note 1 ) VDD = 2.0 V VIO–0.355 VIO+0.355 V

pp

High-level control input voltage, V

IH

VDD = 1.8 V to 2.4 V 0.2 DV

DD

V

Low-level control input voltage, V

IL

VDD = 1.8 V to 2.4 V 0.8 DV

DD

V

Operating free-air temperature, T

A

–25 65 °C

NOTES: 1. The TLV5592 functions and operates down to 1.8 V. Full electrical specifications are ensured from 1.8 to 2.5 V, unless otherwise

noted.

2.

V

I(MAXńMIN)

+

VIO"

ǒ

V

DD

2

*

0.25

Ǔ

ń

(FILTER MAX GAIN)

This equation is valid for input sinusoids of less than 800 Hz.

TLV5592

2-BIT ANALOG-TO-DIGITAL CONVERTER

FOR FLEXt PAGER CHIPSET

SLAS145A – JUNE1996 – REVISED DECEMBER 1997

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range,

AV

DD

= DV

DD

= 1.8 V to 2.5 V, f

(CLK)

= 38.4 kHz (unless otherwise noted)

power

PARAMETER TEST CONDITIONS MIN MAX UNIT

I

DD

Operating supply current Fast track, slow track, or hold mode 250 µA

I

DD(standby)

Standby supply current

V

I(DC OFFSET)

= 0.8 V, V

I(SIG)

= 0.8 V

For all digital inputs,

0 < VI < 0.5 V or VI > DVDD –0.5 V.

1 µA

digital

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

OH

High-level output voltage IOH = –100 µA DVDD –0.5 V

V

OL

Low-level output voltage IOL = 100 µA 0.5 V

I

IH

High-level input current VI = DV

DD

1 2.5 µA

I

IL

Low-level input current VI = 0 –1 –2.5 µA

C

i

Input capacitance, digital input 10 pF

analog

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Voltage accuracy at MID VDD = 2 V, C

L(MID)

= 220 nF 1.42 1.0 1.05 V

Z

i

Input impedance at SIG (see Note 3) f

(IN)

= 1.0 kHz 1 MΩ

Z

i(offset)

Input impedance at DC OFFSET (see Note 3) 1 3 MΩ

I

I(SIG)

Average input current into SIG GND < VI < AV

DD

100 nA

C

i

Input capacitance, all inputs 10 pF

NOTE 3: The input is capacitive and, therefore, is dynamic. Impedance specifications are based on f

(CLK)

= 38.4 kHz.

operating characteristics over recommended operating free-air temperature range,

AV

DD

=DVDD=3 V, f

(CLK)

= 38.4 kHz (unless otherwise noted)

peak-and-valley DACs

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Step size, LSB VDD/255 V

E

FS

Full-scale error 1 LSB

E

ZS

Zero-code error 3 LSB

Voltage output drift Hold mode 0 mV/ms

E

D

Differential nonlinearity (DNL) error 1 LSB

low-pass filter

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

G Pass-band filter gain V

I(DC OFFSET)

= 0.8 V, VI = ± 125 mV 5.75 6 6.25 dB

1-kHz filter VI = ± 500 mV f

I(SIG)

= 1 kHz 2 3 4

Filter attenuation

2-kHz filter VI = ± 500 mV f

I(SIG)

= 2 kHz 2 3 4

dB

t

s

Stabilization time Off mode to hold mode (see Table 1) 5 ms

Loading...

Loading...