Page 1

T

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

D

8-Bit Resolution, 35 MSPS Sampling

Analog-to-Digital Converter (ADC)

D

Low Power Consumption: 90 mW Typ

Using External References

D

Wide Analog Input Bandwidth: 600 MHz Typ

D

3.3-V Single-Supply Operation

D

3.3-V TTL/CMOS-Compatible Digital I/O

D

Internal Bottom and Top Reference

Voltages

D

Adjustable Reference Input Range

D

Power-Down (Standby) Mode

D

Separate Power Down for Internal Voltage

References

D

Three-State Outputs

D

28-Pin Thin Shrink SOP (TSSOP) Packages

D

Applications

– Digital Communications (IF Sampling)

– High-Speed DSP Front-End

(TMS320C6000)

– Medical Imaging

– Video Processing (Scan Rate/Format

Conversion)

– DVD Read Channel Digitization

description

DRV

DRV

DV

DV

PW PACKAGE

(TOP VIEW)

DD

D0

D1

D2

D3

D4

D5

D6

D7

SS

SS

CLK

OE

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

AV

28

AV

27

AIN

26

CML

25

PWDN_REF

24

AV

23

REFBO

22

REFBI

21

REFTI

20

REFTO

19

AV

18

BG

17

AV

16

15

STBY

SS

DD

SS

SS

DD

The TLV5535 is an 8-bit, 35 MSPS, high-speed A/D converter. It converts the analog input signal into 8-bit

binary-coded digital words up to a sampling rate of 35 MHz. All digital inputs and outputs are 3.3 V

TTL/CMOS-compatible.

The device consumes very little power due to the 3.3-V supply and an innovative single-pipeline architecture

implemented in a CMOS process. The user obtains maximum flexibility by setting both bottom and top voltage

references from user-supplied voltages. If no external references are available, on-chip references are

available for internal and external use. The full-scale range is 1 V

up to 1.6 Vpp, depending on the analog

pp

supply voltage. If external references are available, the internal references can be disabled independently from

the rest of the chip, resulting in an even greater power saving.

While usable in a wide variety of applications, the device is specifically suited for the digitizing of high-speed

graphics and for interfacing to LCD panels or LCD/DMD projection modules . Other applications include DVD

read channel digitization, medical imaging, and communications. This device is suitable for IF sampling of

communication systems using sub-Nyquist sampling methods because of its high analog input bandwidth.

AVAILABLE OPTIONS

A

–40°C to 85°C TLV5535IPW

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PACKAGED DEVICES

TSSOP-28

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1999, Texas Instruments Incorporated

1

Page 2

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

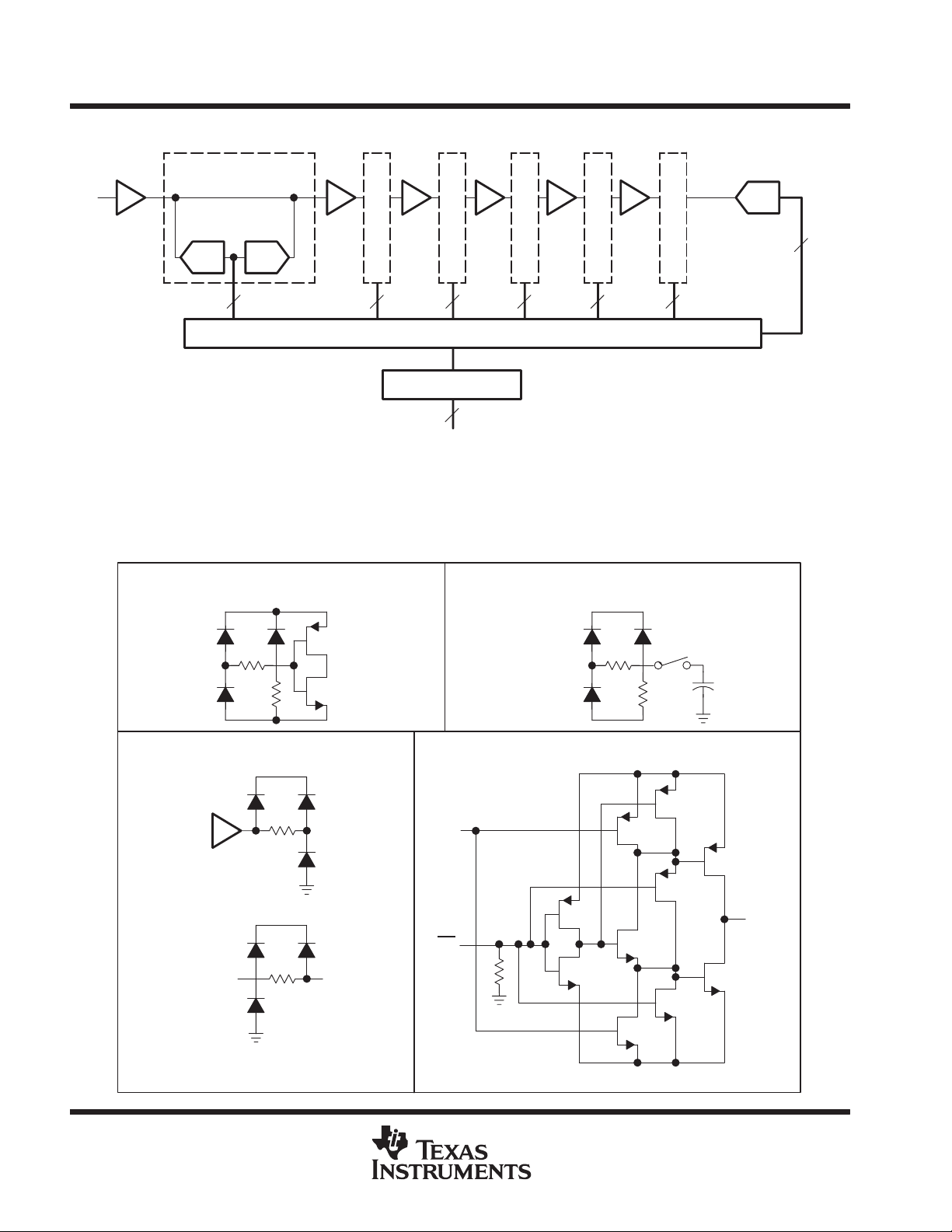

functional block diagram

SHA

+

–

SHA SHA SHA SHA SHA

DACADC

2222 2

Correction Logic

Output Buffers

D0(LSB)–D7(MSB)

2

ADC

The single-pipeline architecture uses 6 ADC/DAC stages and one final flash ADC. Each stage produces a

resolution of 2 bits. The correction logic generates its result using the 2-bit result from the first stage, 1 bit from

each of the 5 succeeding stages, and 1 bit from the final stage in order to arrive at an 8-bit result. The correction

logic ensures no missing codes over the full operating temperature range.

circuit diagrams of inputs and outputs

ALL DIGITAL INPUT CIRCUITS AIN INPUT CIRCUIT

DV

DD

AV

DD

2

REFERENCE INPUT CIRCUIT D0–D7 OUTPUT CIRCUIT

AV

DD

Internal

Reference

Generator

AV

REFBI

or

REFTI

DD

REFTO

or

REFBO

D

OE

0.5 pF

DRV

DRV

DD

D_Out

SS

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 3

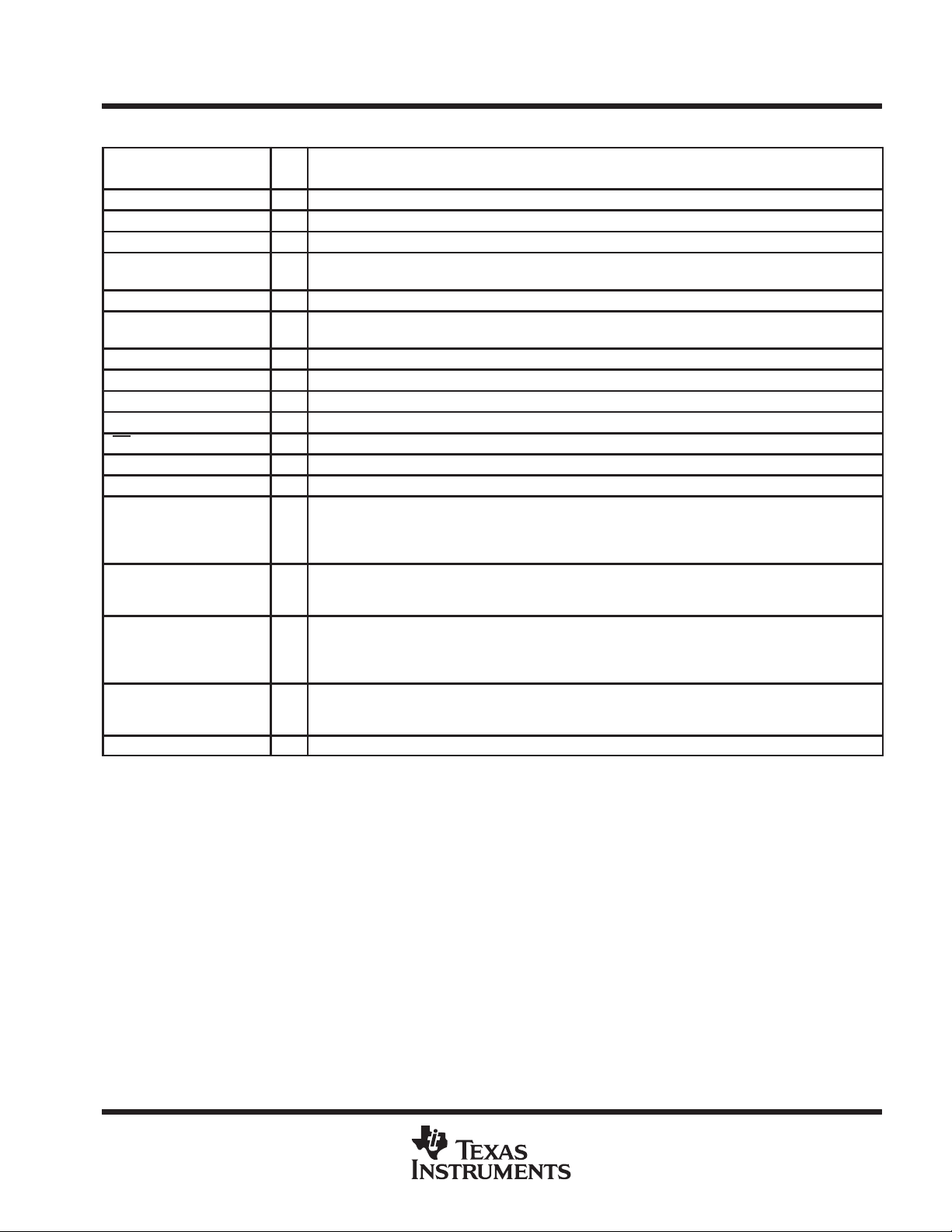

I/O

DESCRIPTION

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

Terminal Functions

TERMINAL

NAME NO.

AIN 26 I Analog input

AV

DD

AV

SS

BG 17 O Band gap reference voltage. A 1-µF capacitor (with an optional 0.1-µF capacitor in parallel) should be

CLK 12 I Clock input. The input is sampled on each rising edge of CLK.

CML 25 O Common mode level. This voltage is equal to (A VDD – AVSS) ÷ 2. An external 0.1-µF capacitor should be

D0 – D7 2 – 9 O Data outputs. D7 is the MSB.

DRV

DD

DRV

SS

DV

DD

OE 13 I Output enable. When high, the D0 – D7 outputs go in high-impedance mode.

DV

SS

PWDN_REF 24 I Power down for internal reference voltages. A high on this terminal disables the internal reference circuit.

REFBI 21 I Reference voltage bottom input. The voltage at this terminal defines the bottom reference voltage for the

REFBO 22 O Reference voltage bottom output. An internally generated reference is available at this terminal. It can be

REFTI 20 I Reference voltage top input. The voltage at this terminal defines the top reference voltage for the ADC.

REFTO 19 O Reference voltage top output. An internally generated reference is available at this terminal. It can be

STBY 15 I Standby input. A high level on this input enables power-down mode.

16, 27 I Analog supply voltage

18, 23, 28 I Analog ground

connected between this terminal and A VSS for external filtering.

connected between this terminal and A VSS.

1 I Supply voltage for digital output drivers

10 I Ground for digital output drivers

14 I Digital supply voltage

11 I Digital ground

ADC. It can be connected to REFBO or to an externally generated reference level. Sufficient filtering

should be applied to this input. The use of a 0.1-µF capacitor connected between REFBI and AVSS is

recommended. Additionaly, a 0.1-µF capacitor can be connected between REFTI and REFBI.

connected to REFBI or left unconnected. A 1-µF capacitor between REFBO and A VSS provides sufficient

decoupling required for this output.

It can be connected to REFTO or to an externally generated reference level. Sufficient filtering should be

applied to this input. The use of a 0.1-µF capacitor between REFTI and AVSS is recommended.

Additionaly, a 0.1-µF capacitor can be connected between REFTI and REFBI.

connected to REFTI or left unconnected. A 1-µF capacitor between REFTO and A VSS provides sufficient

decoupling required for this output.

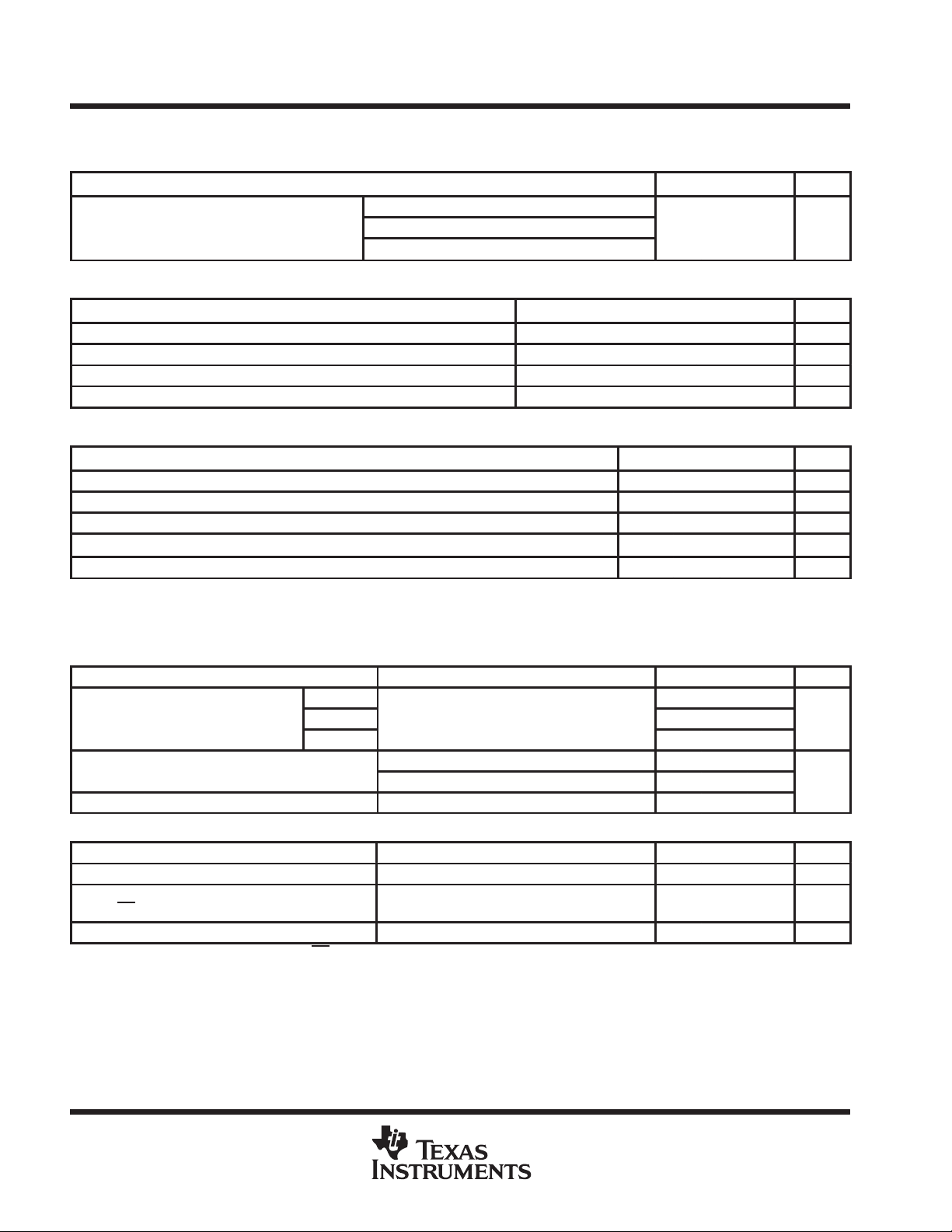

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage range:AVDD to AVSS, DVDD to DVSS –0.5 V to 4.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AVDD to DVDD, AVSS to DVSS –0.5 V to 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital input voltage range to DVSS –0.5 V to DVDD + 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Analog input voltage range to AVSS –0.5 V to AVDD + 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital output voltage range applied from external source to DGND –0.5 V to DV

Reference voltage input range to AGND: V

(REFTI)

, V

(REFTO)

, V

(REFBI)

, V

(REFBO)

–0.5 V to AVDD + 0.5 V

DD

+ 0.5 V. . . . . . . . . . . . . .

Operating free-air temperature range, TA: TLV5535I –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

–55°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

stg

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

Page 4

TLV5535

C

L

V

I

MHz

FS

PDPower dissipation

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

recommended operating conditions over operating free-temperature range

power supply

Supply voltage

analog and reference inputs

Reference input voltage (top), V

Reference input voltage (bottom), V

Reference voltage differential, V

Analog input voltage, V

(AIN)

(REFTI)

(REFTI)

digital inputs

High-level input voltage, V

Low-level input voltage, V

Clock period, t

Pulse duration, clock high, t

Pulse duration, clock low, t

c

IH

IL

w(CLKH)

w(CLKL)

(REFBI)

– V

AVDD – AV

DVDD – DV

DRVDD – DRV

(REFBI)

SS

SS

SS

MIN NOM MAX UNIT

(NOM) – 0.2 2 + (AVDD – 3) (NOM) + 0.2 V

0.8 1 1.2 V

V

(REFBI)

MIN NOM MAX UNIT

2.0 DV

DGND 0.2xDV

28.6 ns

13 ns

13 ns

MIN NOM MAX UNIT

3 3.3 3.6 V

1 + (AVDD – 3) V

V

(REFTI)

DD

DD

V

V

V

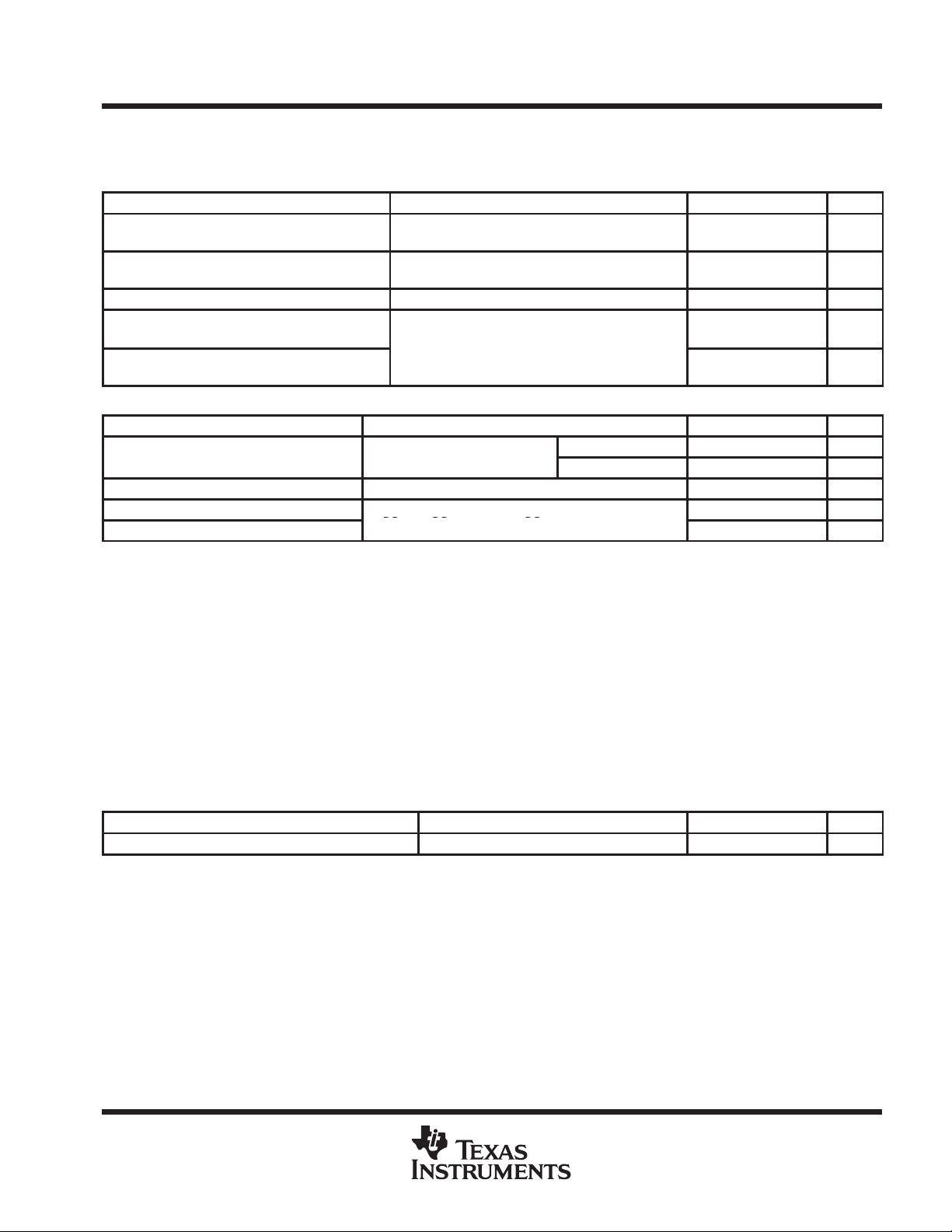

electrical characteristics over recommended operating conditions, f

= 35 MSPS, external

CLK

voltage references (unless otherwise noted)

power supply

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

AV

I

DD

P

D(STBY)

DD

Operating supply current

p

Standby power STBY = H, CLK held high or low 11 15

DV

DRV

DD

DD

AVDD = DVDD = 3.3 V, DRVDD = 3 V,

= 15 F,

PWDN_REF = L 106 139

PWDN_REF = H 90 113

= 1

p

, –1-dB

–

-

digital logic inputs

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

I

High-level input current on CLK

IH

Low-level input current on digital inputs

I

IL

(OE

, STDBY, PWDN_REF, CLK)

CIInput capacitance 5 pF

†

IIH leakage current on other digital inputs (OE, STDBY , PWDN_REF) is not measured since these inputs have an internal pull-down resistor of

4 KΩ to DGND.

†

AVDD = DVDD = DRVDD = CLK = 3.6 V 10 µA

AVDD = DVDD = DRVDD = 3.6 V,

Digital inputs at 0 V

27 34

1.5 2.6

4 6

10 µA

mA

mW

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 5

AV

DD

DV

DD

DRV

DD

V

Integral nonlinearity (INL), best-fit

Internal references (see Note 1)

DD DD DD

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

electrical characteristics over recommended operating conditions, f

= 35 MSPS, external

CLK

voltage references (unless otherwise noted) (continued)

logic outputs

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

High-level output voltage

OH

V

Low-level output voltage

OL

C

Output capacitance 5 pF

O

High-impedance state output current to

I

OZH

high level

High-impedance state output current to

I

OZL

low level

dc accuracy

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Differential nonlinearity (DNL) Internal references (see Note 2), TA = –40°C to 85°C –1 ±0.6 1.3 LSB

Zero error

Full-scale error

NOTES: 1. Integral nonlinearity refers to the deviation of each individual code from a line drawn from zero to full scale. The point used as zero

occurs 1/2 LSB before the first code transition. The full-scale point is defined as a level 1/2 LSB beyond the last code transition. The

deviation is measured from the center of each particular code to the true straight line between these two endpoints.

2. An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Therefore this measure

indicates how uniform the transfer function step sizes are. The ideal step size is defined here as the step size for the device under

test [i.e., (last transition level – first transition level) ÷ (2n – 2)]. Using this definition for DNL separates the effects of gain and offset

error. A minimum DNL better than –1 LSB ensures no missing codes.

3. Zero error is defined as the difference in analog input voltage – between the ideal voltage and the actual voltage – that switches

the ADC output from code 0 to code 1. The ideal voltage level is determined by adding the voltage corresponding to 1/2 LSB to the

bottom reference level. The voltage corresponding to 1 LSB is found from the difference of top and bottom references divided by

the number of ADC output levels (256).

Full-scale error is defined as the difference in analog input voltage – between the ideal voltage and the actual voltage – that switches

the ADC output from code 254 to code 255. The ideal voltage level is determined by subtracting the voltage corresponding to 1.5

LSB from the top reference level. The voltage corresponding to 1 LSB is found from the difference of top and bottom references

divided by the number of ADC output levels (256).

AVDD = DVDD = DRVDD = 3 V at IOH = 50 µA,

Digital output forced high

AVDD = DVDD = DRVDD = 3.6 V at IOL = 50 µA,

Digital output forced low

=

AVDD = DVDD = 3.3 V, DRVDD = 3 V,

Internal references (see Note 3)

=

= 3.6

TA = 25°C –1.5 ±0.7 1.5 LSB

TA = –40°C to 85°C –2.4 ±0.7 2.4 LSB

2.8 V

0.1 V

10 µA

10 µA

5 %FS

5 %FS

analog input

C

Input capacitance 4 pF

I

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

5

Page 6

TLV5535

Differential phase, DP

0.6

CLK in

Differential gain, DG

20 IRE am litude vs full scale of 140 IRE

0.2%

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

electrical characteristics over recommended operating conditions, f

= 35 MSPS, external

CLK

voltage references (unless otherwise noted) (continued)

reference input (AVDD = DVDD = DRVDD = 3.6 V)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

R

Reference input resistance 400 Ω

ref

I

Reference input current 2.5 mA

ref

reference outputs

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

(REFTO)

V

(REFBO)

dynamic performance

Effective number of bits (ENOB)

Signal-to-noise ratio + distortion (SNRD)

Total harmonic distortion (THD)

Spurious free dynamic range (SFDR)

Analog input full-power bandwidth, BW See Note 4 600 MHz

†

Based on analog input voltage of – 1-dB FS referenced to a 1.3 Vpp full-scale input range and using the external voltage references at

f

= 35 MSPS with AVDD = DVDD = 3.3 V and DRVDD = 3 V at 25°C.

CLK

NOTE 4: The analog input bandwidth is defined as the maximum frequency of a –1-dB FS input sine that can be applied to the device for which

Reference top offset voltage

Reference bottom offset voltage

Absolute min/max values valid

and tested for AVDD = 3.3 V

†

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

fin = 1 MHz 6.6 7.4

fin = 4.2 MHz 6.6 7.4

fin = 15 MHz 7

fin = 1 MHz 41.5 46

fin = 4.2 MHz 41.5 46

fin = 15 MHz 43

fin = 1 MHz –46 –55

fin = 4.2 MHz –45.5 –54

fin = 15 MHz –50

fin = 1 MHz 48 58

fin = 4.2 MHz 48 58

fin = 15 MHz 52

p

an extra 3-dB attenuation is observed in the reconstructed output signal.

f

= 35 MHz, fin = 4.2 MHz,

CLK

20 IRE amplitude vs full-scale of 140 IRE

2.07 2 + [(AVDD – 3) ÷ 2] 2.21 V

1.09 1 + [(AVDD – 3) ÷ 2] 1.21 V

Bits

dB

dB

dB

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 7

f

See Note 5

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

electrical characteristics over recommended operating conditions, f

voltage references (unless otherwise noted) (continued)

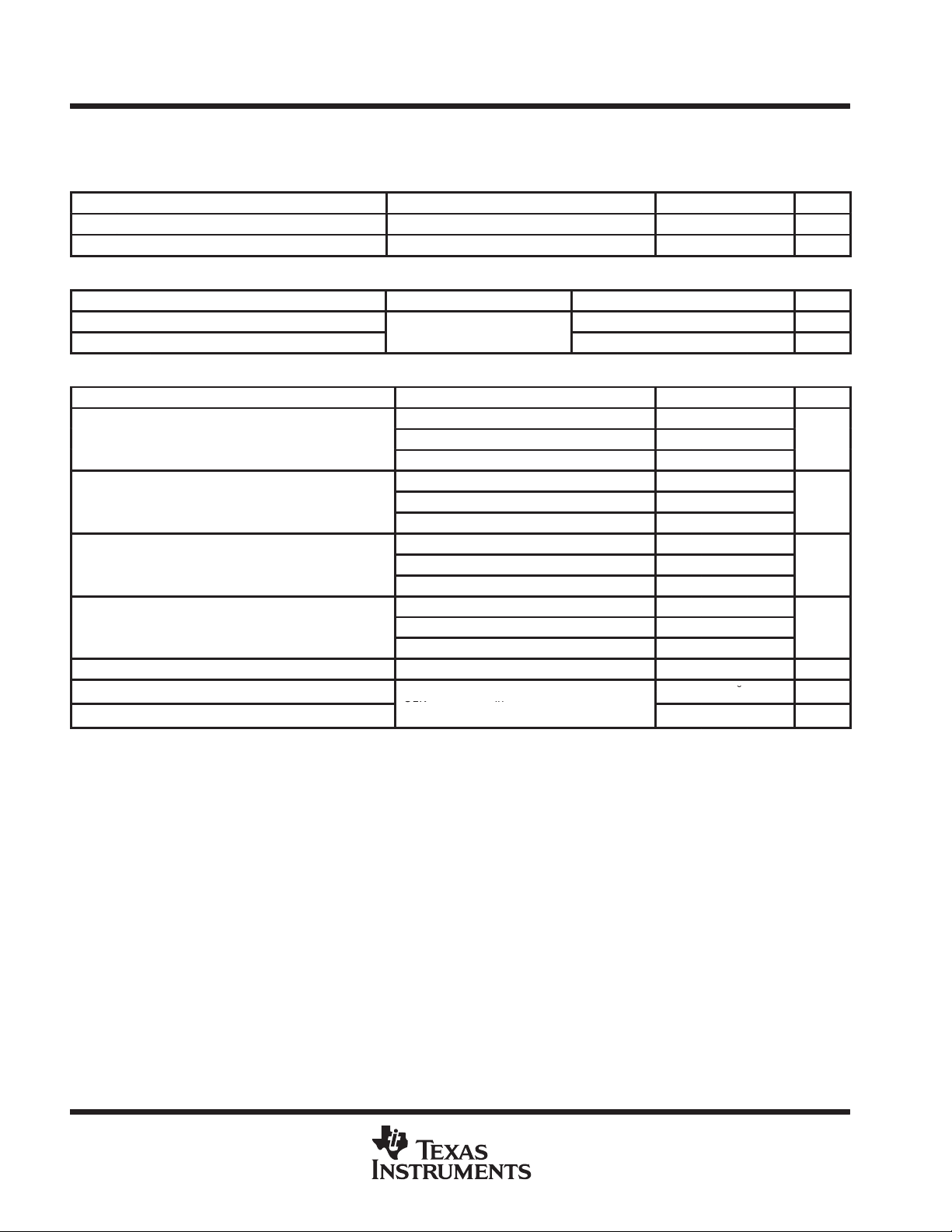

timing requirements

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

CLK

t

d(o)

t

h(o)

t

d(pipe)

t

d(a)

t

j(a)

t

dis

t

en

NOTES: 5. Output timing t

Maximum conversion rate 35 MHz

Minimum conversion rate 10 kHz

Output delay time (see Figure 1) CL = 10 pF, See Notes 5 and 6 9 ns

Output hold time CL = 2 pF, See Note 5 2 ns

Pipeline delay time (latency) See Note 6 4.5 4.5 4.5

Aperture delay time 3 ns

Aperture jitter

Disable time, OE rising to Hi-Z

Enable time, OE falling to valid data 5 8 ns

is measured from the 1.5 V level of the CLK input falling edge to the 10%/90% level of the digital output. The digital

output load is not higher than 10 pF.

Output hold time t

digital output is load is not less than 2 pF.

Aperture delay t

The OE signal is asynchronous.

OE timing t

not higher than 10 pF.

OE timing ten is measured from the V

levels. The digital output load is not higher than 10 pF.

6. The number of clock cycles between conversion initiation on an input sample and the corresponding output data being made

available from the ADC pipeline. Once the data pipeline is full, new valid output data is provided on every clock cycle. In order to

know when data is stable on the output pins, the output delay time t

to be added to the pipeline latency. Note that since the max t

clocked in on a rising edge of CLK at this speed. The falling edge should be used.

d(o)

is measured from the 1.5 V level of the CLK input falling edge to the 10%/90% level of the digital output. The

h(o)

is measured from the 1.5 V level of the CLK input to the actual sampling instant.

d(A)

is measured from the V

dis

level of OE to the high-impedance state of the output data. The digital output load is

IH(MIN)

level of OE to the instant when the output data reaches V

IL(MAX)

(i.e., the delay time through the digital output buffers) needs

d(o)

is more than 1/2 clock period at 35 MHz, data cannot be reliably

d(o)

= 35 MSPS, external

CLK

1.5 ps, rms

5 8 ns

OH(min)

or V

OL(max)

CLK

cycles

output

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

Page 8

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

PARAMETER MEASUREMENT INFORMATION

N+3

N

N+1

90%

10%

V

IH(min)

N+5

V

t

en

IL(max)

CLK

N+2

t

d(pipe)

t

j(a)

t

t

h(o)

d(a)

1.5 V

1/f

V

V

CLK

t

w(CLKH)

D0–D7 N–4 N–3 N–2 N–1 N N+1

OE

IH

(min)

t

w(CLKL)

IL

(max)

N+4

1.5 V

t

d(o)

t

dis

Figure 1. Timing Diagram

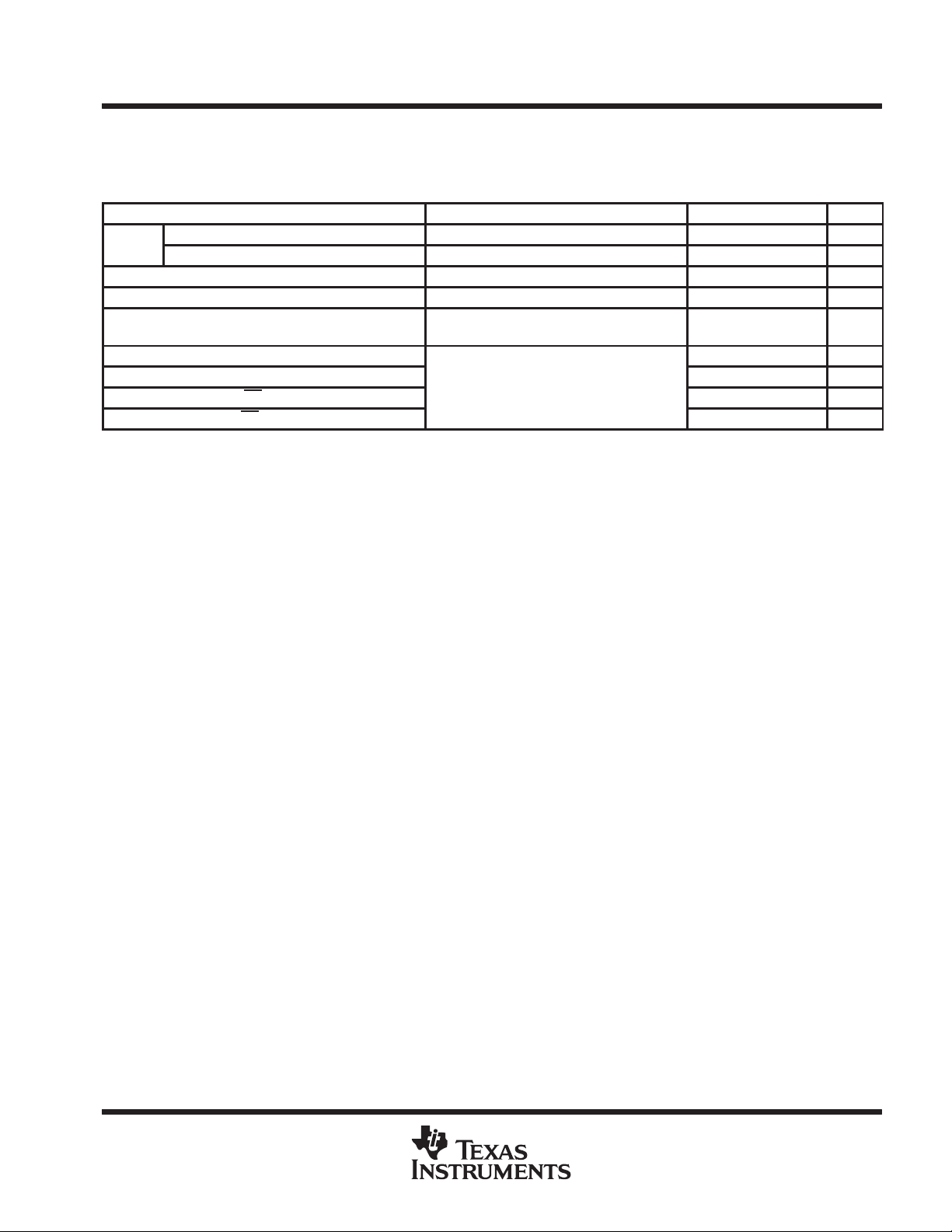

TYPICAL CHARACTERISTICS

performance plots at 25°C

V

OH(min)

V

OL(max)

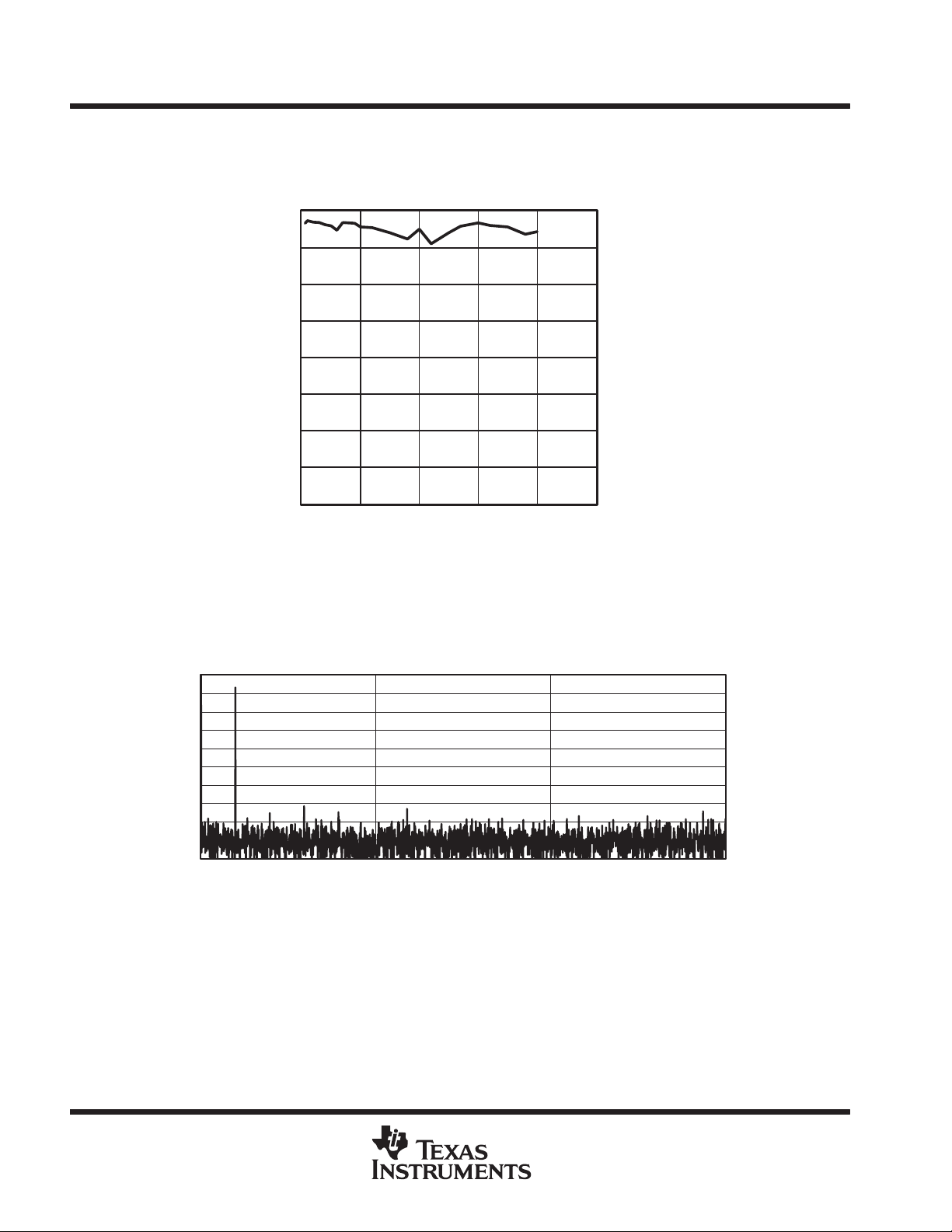

0.2

0.1

0.0

DNL – LSB

–0.1

–0.2

0 50 100 150 200 250

ADC Code

Figure 2. DNL vs Input Code at 35 MSPS (with external reference, PW Package)

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

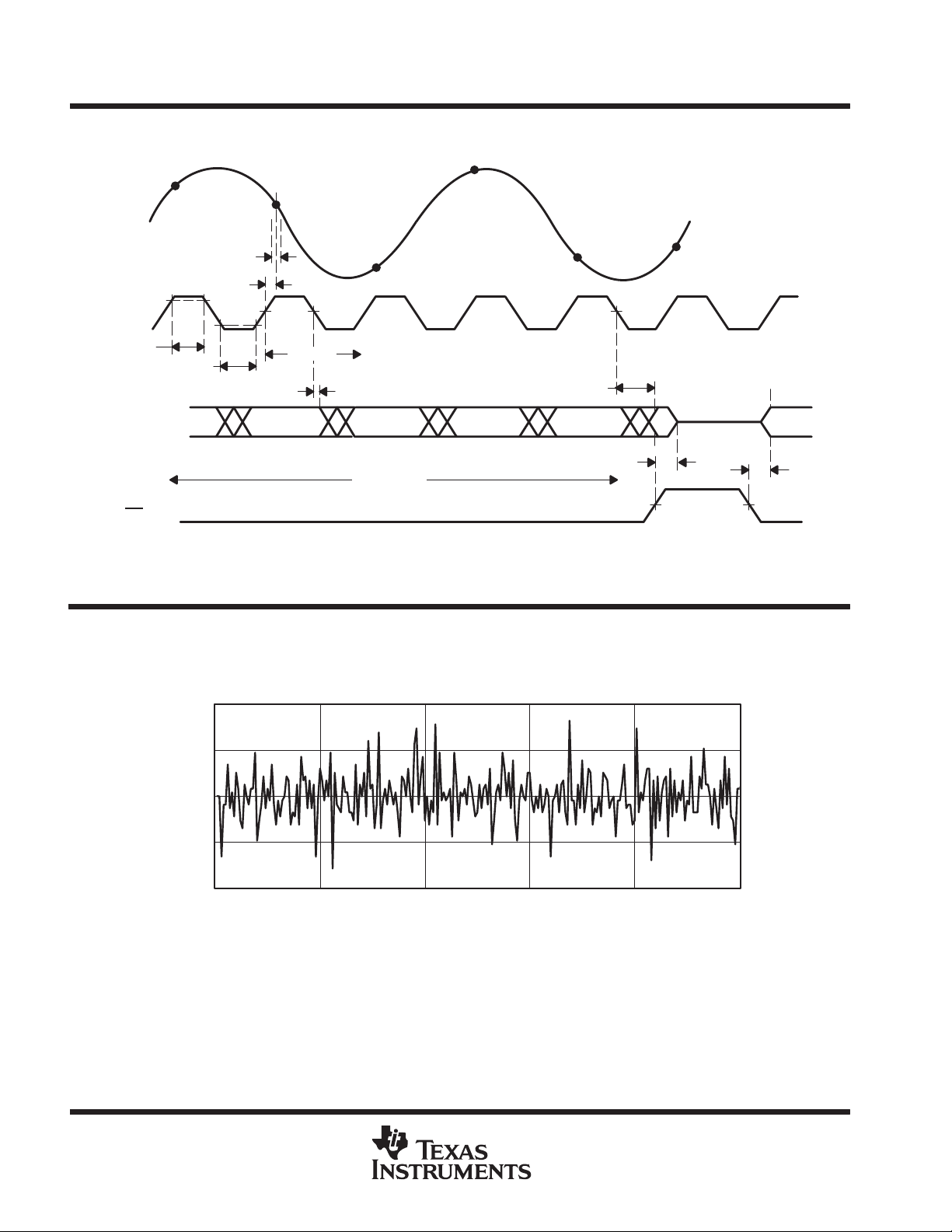

Page 9

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

TYPICAL CHARACTERISTICS

performance plots at 25°C (continued)

0.4

0.3

0.2

0.1

–0.0

–0.1

INL – LSB

–0.2

–0.3

–0.4

0 50 100 150 200 250

Figure 3. INL vs Input Code at 35 MSPS (with external reference, PW package)

TLV5535

SLAS221 – JUNE 1999

ADC Code

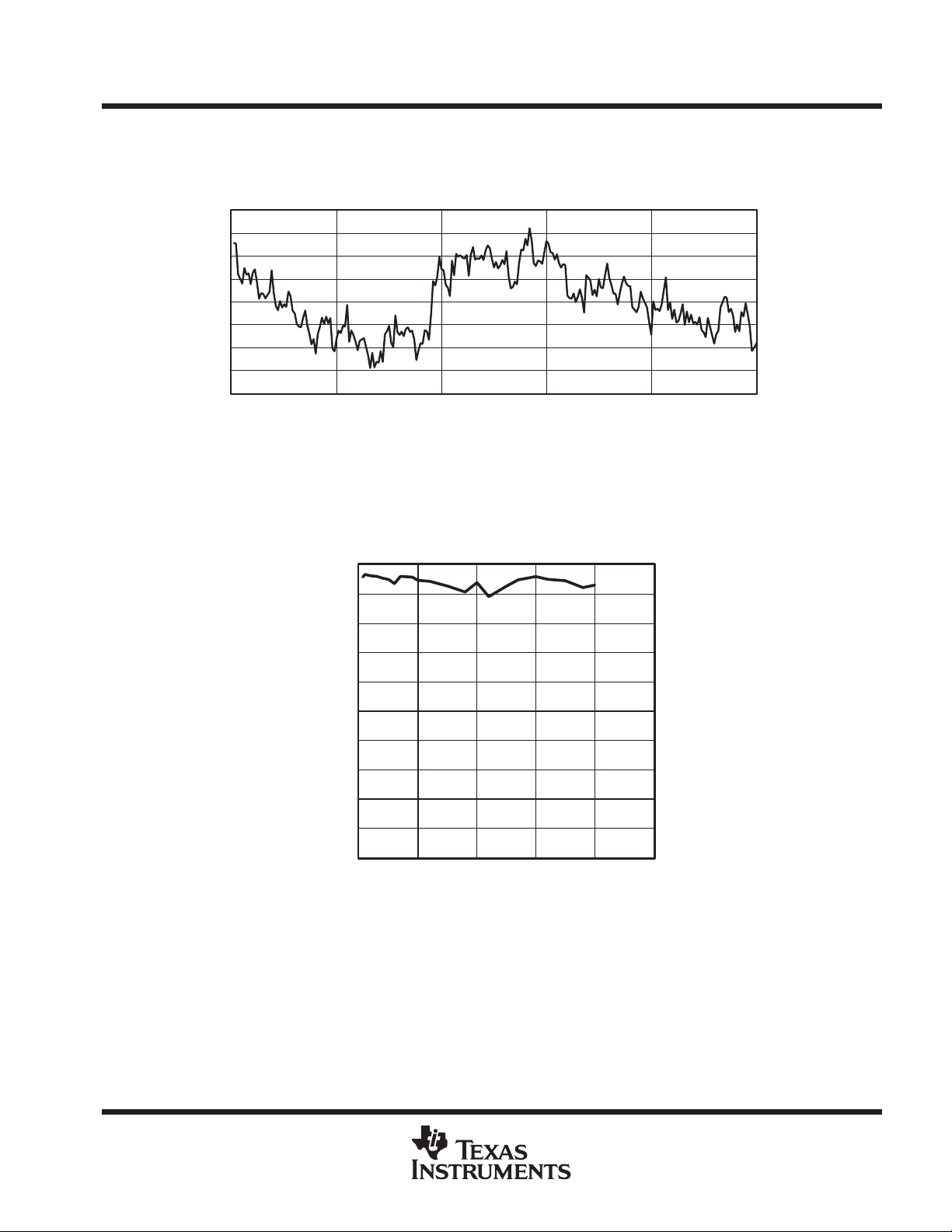

50

45

40

35

30

25

SNRD – dB

20

15

10

5

0

0 1020304050

Analog Input Frequency – MHz

Figure 4. SNRD vs fin at 35 MSPS (external reference)

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

9

Page 10

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TYPICAL CHARACTERISTICS

performance plots at 25°C (continued)

8

7

6

5

4

ENOB

3

2

1

0

0 1020304050

Analog Input Frequency – MHz

Figure 5. ENOB vs FIN, 35 MSPS (external reference)

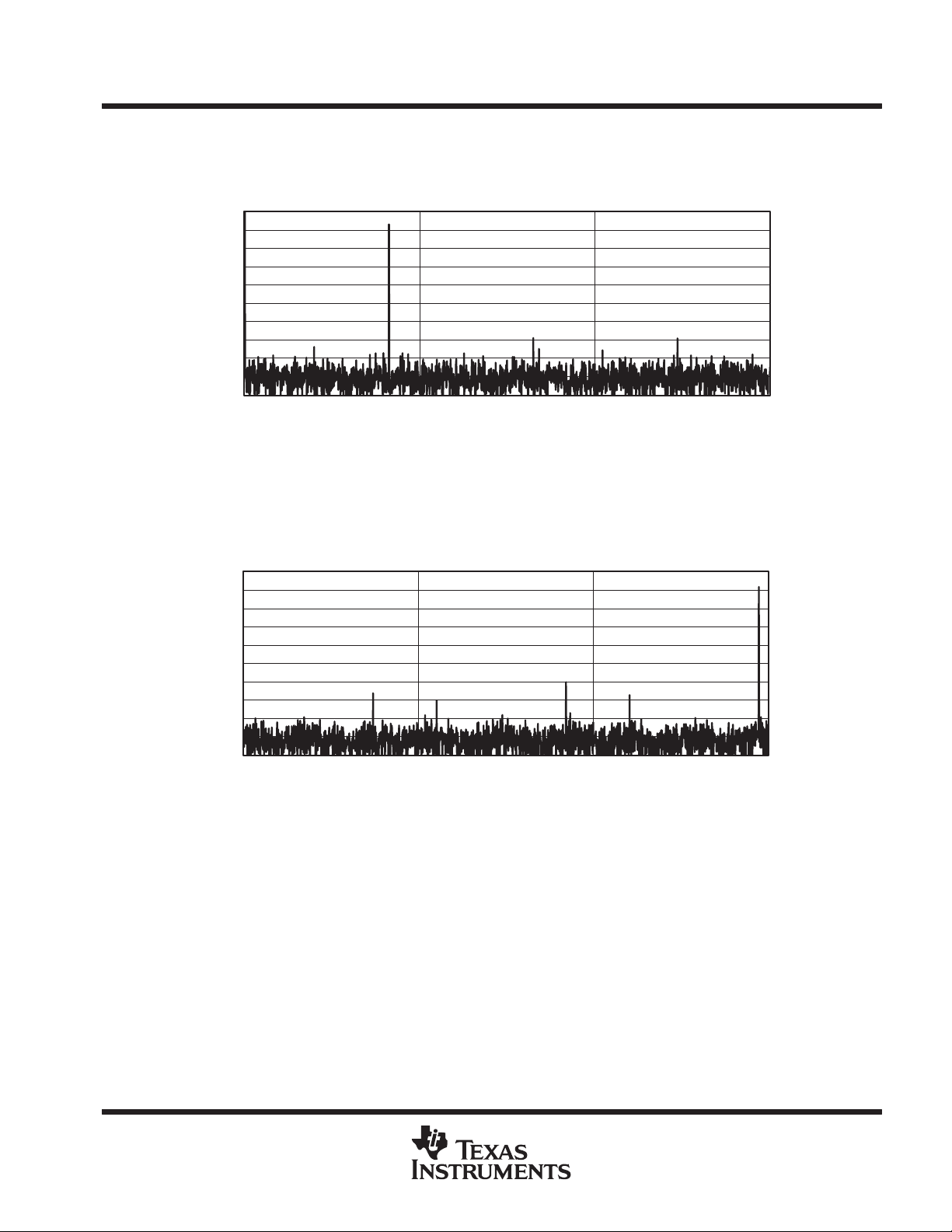

0

–10

–20

–30

–40

–50

–60

–70

Power – dBFS

–80

–90

–100

0 5 10 15

f – Frequency – MHz

Figure 6. Spectral Plot fin = 1.0 MHz at 35 MSPS

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 11

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

TYPICAL CHARACTERISTICS

performance plots at 25°C (continued)

0

–10

–20

–30

–40

–50

–60

Power – dB

–70

–80

–90

–100

0 5 10 15

Figure 7. Spectral Plot fin = 4.2 MHz at 35 MSPS

TLV5535

SLAS221 – JUNE 1999

f – Frequency – MHz

0

–10

–20

–30

–40

–50

–60

Power – dB

–70

–80

–90

–100

0 5 10 15

f – Frequency – MHz

Figure 8. Spectral Plot fin = 15.527 MHz at 35 MSPS

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

11

Page 12

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TYPICAL CHARACTERISTICS

performance plots at 25°C (continued)

120

100

80

60

Power – mV

40

20

0

0 1020304050

Input Clock Frequency – MHz

Figure 9. Power vs f

CLK

at fin = 1 MHz, –1-dB FS

2.5

2.0

1.5

1.0

Supply Current – mA

0.5

0

0 1020304050

Input Frequency – MHz

Figure 10. DRVDD Supply Current vs f

at fin = 1 MHz, –1-dB FS

CLK

0.00

–1.00

–2.00

–3.00

–4.00

Fundamental – dB

–5.00

–6.00

–7.00

1 10 100 1000

Input Frequency – MHz

Figure 11. ADC Output Power With Respect to –1-dB FS V

(internal reference, PW package)

IN

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 13

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

PRINCIPLES OF OPERATION

The TL V5535 implements a high-speed 35 MSPS converter in a cost-effective CMOS process. Powered from

3.3 V , the single-pipeline design architecture ensures low-power operation and 8-bit accuracy . Signal input and

clock signals are all single-ended. The digital inputs are 3.3-V TTL/CMOS compatible. Internal voltage

references are included for both bottom and top voltages. Therefore the converter forms a self-contained

solution. Alternatively , the user may apply externally generated reference voltages. In doing so, both input offset

and input range can be modified to suit the application.

A high-speed sampling-and-hold captures the analog input signal. Multiple stages generate the output code with

a pipeline delay of 4.5 CLK cycles. Correction logic combines the multistage data and aligns the 8-bit output

word. All digital logic operates at the rising edge of CLK.

analog input

A first-order approximation for the equivalent analog input circuit of the TLV5535 is shown in Figure 12. The

equivalent input capacitance C

sample period of one half clock cycle. When a full-scale voltage step is applied, the input source provides the

charging current through the switch resistance RSW (200 Ω) of S1 and quickly settles. In this case, the input

impedance is low. Alternatively, when the source voltage equals the value previously stored on CI, the hold

capacitor requires no input current and the equivalent input impedance is very high.

is 4 pF typical. The input must charge/discharge this capacitance within the

I

TLV5535

To maintain the frequency performance outlined in the specifications, the total source impedance should be

limited to about 80 Ω, as follows from the equation with f

RStƪ1 ÷ǒ2f

CLK

CI

In(256)Ǔ–R

ƫ

The source impedance is approximatly 450 Ω.

SW

= 35 MHz, CI = 4 pF, RSW = 200 Ω:

CLK

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

13

Page 14

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

PRINCIPLE OF OPERATION

analog input (continued)

So, for applications running at a lower f

R

V

S

, the total source resistance will increase proportionally.

CLK

TLV5535

S

AIN

S1

R

SW

C

I

Figure 12. Simplified Equivalent Input Circuit

dc coupled input

For dc-coupled systems an op amp can level-shift a ground-referenced input signal. A circuit as shown in

Figure 13(a) is acceptable. Alternatively , the user might want a bipolar shift together with the bottom reference

voltage as seen in Figure 13(b). In this case the AIN voltage is given by:

AIN+2 R2÷ǒR1)

V

IN

+

_

AV

DD

Ǔ

R

2

REFTI

REFTO

TLV5535

AIN

REFBI

REFBO

V

REF

–V

IN

V

V

IN

REF

R

IN

R

IN

_

R

+

1

R

2

REFTI

REFTO

TLV5535

AIN

REFBI

REFBO

(a)

(b)

Figure 13. DC-Coupled Input Circuit

ac coupled input

For many applications, especially in single supply operation, ac coupling offers a convenient way for biasing

the analog input signal at the proper signal range. Figure 14 shows a typical configuration. To maintain the

outlined specifications, the component values need to be carefully selected. The most important issue is the

positioning of the 3-dB high-pass corner point f

, which is a function of R2 and the parallel combination of

–3 dB

C1 and C2, called Ceq. This is given by the following equation:

f

–3 dB

+

1 ÷ǒ2π xR2xC

eq

Ǔ

where Ceq is the parallel combination of C1 and C2.

Since C1 is typically a large electrolytic or tantalum capacitor, the impedance becomes inductive at higher

frequencies. Adding a small ceramic or polystyrene capacitor, C2 of approximately 0.01 µF, which is not

inductive within the frequency range of interest, maintains low impedance. If the minimum expected input signal

frequency is 20 kHz, and R2 equals 1 kΩ and R1 equals 50 Ω, the parallel capacitance of C1 and C2 must be

a minimum of 8 nF to avoid attenuating signals close to 20 kHz.

14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 15

ac coupled input (continued)

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

PRINCIPLE OF OPERATION

C1

V

IN

C2

+

–

R2

R1

V

BIAS

TLV5535

AIN

Figure 14. AC-Coupled Input Circuit

reference terminals

The voltages on terminals REFBI and REFTI determine the TLV5535 input range. Since the device has an

internal voltage reference generator with outputs available on REFBO and REFTO respectively , corresponding

terminals can be directly connected externally to provide a contained ADC solution. Especially at higher

sampling rates, it is advantageous to have a wider analog input range. The wider analog input range is

achievable by using external voltage references (e.g., at AV

from 1 Vpp (internal reference) to 1.3 Vpp (external reference) as shown in T able 1). These voltages should not

be derived via a voltage divider from a power supply source. Instead, a bandgap-derived voltage reference

should be used to derive both references via an op amp circuit. Refer to the schematic of the TL V5535 evaluation

module for an example circuit.

When using external references, the full-scale ADC input range and its dc position can be adjusted. The

full-scale ADC range is always equal to V

REFT

– V

. The maximum full-scale range is dependent on A V

REFB

as shown in the specification section. In addition to the limitation on their difference, V

have limits on their useful range. These limits are also dependent on AVDD.

= 3.3 V, the full-scale range can be extended

DD

and V

REFT

REFB

DD

each also

Table 1 summarizes these limits for 3 cases.

Table 1. Recommended Operating Modes

AV

DD

3 V 0.8 V 1.2 V 1.8 V 2.2 V 1 V

3.3 V 0.8 V 1.2 V 2.1 V 2.5 V 1.3 V

3.6 V 0.8 V 1.2 V 2.4 V 2.8 V 1.6 V

V

REFB(min)

V

REFB(max)VREFT(min)

V

REFT(max)

(V

REFT–VREFB)max

digital inputs

The digital inputs are CLK, STDBY, PWDN_REF, and OE. All of these signals, except CLK, have an internal

pulldown resistor to connect to digital ground. This provides a default active operation mode using internal

references when left unconnected.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

15

Page 16

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

PRINCIPLE OF OPERATION

digital inputs (continued)

The CLK signal at high frequencies should be considered as an analog input. Overshoot/undershoot should be

minimized by proper termination of the signal close to the TLV5535. An important cause of performance

degradation for a high-speed ADC is clock jitter. Clock jitter causes uncertainty in the sampling instant of the

ADC, in addition to the inherent uncertainty on the sampling instant caused by the part itself, as specified by

its aperture jitter. There is a theoretical relationship between the frequency (f) and resolution (2

that needs to be sampled and the maximum amount of aperture error dt

formula shows the relation:

ǒ

Ǔ

N)1

dt

+1Bƪp

max

As an example, for an 8-bit converter with a 15-MHz input, the jitter needs to be kept < 41 pF in order not to have

changes in the LSB of the ADC output due to the total aperture error.

f2

ƫ

that is tolerable. The following

max

digital outputs

The output of the TL V5535 is standard binary code. Capacitive loading on the output should be kept as low as

possible (a maximum loading of 10 pF is recommended) to provide the best performance. Higher output loading

causes higher dynamic output currents and can increase noise coupling into the analog front end of the device.

To drive higher loads, the use of an output buffer is recommended.

N

) of a signal

When clocking output data from the TL V5535, it is important to observe its timing relation to CLK. The pipeline

ADC delay is 4.5 clock cycles to which the maximum output propagation delay is added. See Note 6 in the

specification section for more details.

layout, decoupling and grounding rules

It is necessary for any PCB using the TLV5535 to have proper grounding and layout to achieve the stated

performance. Separate analog and digital ground planes that are spliced underneath the device are advisable.

The TLV5535 has digital and analog terminals on opposite sides of the package to make proper grounding

easier. Since there is no internal connection between the analog and digital grounds, they have to be joined on

the PCB. Joining the digital and analog grounds at a point in close proximity to the TLV5535 is advised.

As for power supplies, separate analog and digital supply terminals are provided on the device (A V

The supply to the digital output drivers is kept separate also (DRVDD). Lowering the voltage on this supply from

the nominal 3.3 V to 3 V improves performance because of the lower switching noise caused by the output

buffers.

Due to the high sampling rate and switched-capacitor architecture, the TLV5535 generates transients on the

supply and reference lines. Proper decoupling of these lines is essential. Decoupling as shown in the schematic

of the TLV5535 EVM is recommended.

/DVDD).

DD

16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 17

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

TLV5535 evaluation module

TI provides an evaluation module (EVM) for TL V5535. The EVM also includes a 10b 80 MSPS DAC so that the

user can convert the digitized signal back to the analog domain for functional testing. Performance

measurements can be done by capturing the ADC’s output data.

The EVM provides the following additional features:

D

Provision of footprint for the connection of an onboard crystal oscillator, instead of using an external clock

input.

D

Use of TLV5535 internal or external voltage references. In the case of external references, an onboard

circuit is used that derives adjustable bottom and top reference voltages from a bandgap reference. Two

potentiometers allow for the independent adjustments of both references. The full scale ADC range can be

adjusted to the input signal amplitude.

D

All digital output, control signal I/O (output enable, standby, reference powerdown) and clock I/O are

provided on a single connector. The EVM can thus be part of a larger (DSP) system for prototyping.

D

Onboard prototyping area with analog and digital supply and ground connections.

TLV5535

Figure 15 shows the EVM schematic.

The EVM is factory shipped for use in the following configuration:

D

Use of external (onboard) voltage references

D

External clock input

analog input

A signal in the range between V

J10. This signal is onboard terminated with 50Ω. There is no onboard biasing of the signal. When using external

(onboard) references, these levels can be adjusted with R7 (V

both references to shift. R6 only impacts the bottom reference. The range of these signals for which the device

is specified depends on AV

Internally generated reference levels are also dependent on AV

section.

(REFBI)

and is shown in the

DD

and V

(REFTI)

should be applied to avoid overflow/underflow on connector

(REFTI)

Recommended Operating Conditions

) and R6 (V

as shown in the electrical characteristics

DD

(REFBI)

). Adjusting R7 causes

.

clock input

A clock signal should be applied with amplitudes ranging from 0 to A VDD with a frequency equal to the desired

sampling frequency on connector J9. This signal is onboard terminated with 50 Ω. Both ADC and DAC run of f

the same clock signal. Alternatively the clock can be applied from terminal 1 on connector J11. A third option

is using a crystal oscillator. The EVM board provides the footprint for a crystal oscillator that can be populated

by the end-user, depending on the desired frequency. The footprint is compatible with the Epson EG-8002DC

series of programmable high-frequency crystal oscillators. Refer to the TLV5535 EVM Settings for selecting

between the different clock modes.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

17

Page 18

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

power supplies

The board provides seven power supply connectors (see T able 2). For optimum performance, analog and digital

supplies should be kept separate. Using separate supplies for the digital logic portion of TL V5535 (DVDD) and

its output drivers (DRVDD) benefits dynamic performance, especially when DRVDD is put at the minimum

required voltage (3 V), while DVDD might be higher (up to 3.6 V). This lowers the switching noise on the die

caused by the output drivers.

Table 2. Power Supplies

SIGNAL

NAME

DRV3 J1 3DRV 3.3 V digital supply for TLV5535 (digital output drivers)

DV3 J2 3VD 3.3 V digital supply for TLV5535 (digital logic) and peripherals

DV5 J3 5VD 5 V digital supply for D/A converter and peripherals

AV3 J4 3VA 3.3 V analog supply for TLV5535

AV5 J5 5VA 5 V analog supply for onboard reference circuit and D/A converter. Can be left unconnected if

AV+12 J6 12VA 12 V analog supply for onboard reference circuit. Can be left unconnected if internal references

AV–12 J7 –12VA –12 V analog supply for onboard reference circuit. Can be left unconnected if internal

CONNECTOR

BOARD

LABEL

DESCRIPTION

internal references are used and no D/A conversion is required.

are used.

references are used.

voltage references

SW1 and SW2 switch between internal and external top and bottom references respectively. The external

references are onboard generated from a stable bandgap-derived 3.3 V signal (using TI’s TPS7133 and

quad-opamp TLE2144). They can be adjusted via potentiometers R6 (V

(REFBI)

) and R7 (V

(REFTI)

). It is advised

to power down the internal voltage references by asserting PWN_REF when onboard references are used.

The references are measured at test points TP3 (V

(REFB)

) and TP4 (V

(REFT)

).

DAC output

The onboard DAC is a 10-bit 80 MSPS converter. It is connected back-to-back to the TLV5535. While the user

could use its analog output for measurements, the DAC output is directly connected to connector J8 and does

not pass through an analog reconstruction filter. So mirror spectra from aliased signal components feed through

into the analog output.

For this reason and to separate ADC and DAC contributions, performance measurements should be made by

capturing the ADC output data available on connector J11 and not by evaluating the DAC output.

18

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 19

TLV5535 EVM settings

clock input settings

REFERENCE

DESIGNATOR

W1 Clock selection switch

W2 Clock source switch

W3 Clock output switch

reference settings

REFERENCE

DESIGNATOR

SW1 REFT external/internal switch

SW2 REFB external/internal switch

1–2 J11: clock from pin1 on J11 connector

2–3 J9: clock from J9 SMA connector

J

XTL: clock from onboard crystal oscillator

j

CLK: clock from pin 1 on J11 connector (if W1/1–2) or J9 SMA connector (if W1/2–3)

NOTE: If set to XTL and a XTL oscillator is populated, no clock signal should be applied to J9 or J1 1, depending on the W1

setting.

1–2 Rising: clock output on J1 1 connector is the same phase as the clock to the digital output buffer . Data changes on rising

CLK edge.

2–3 Falling: clock output on J1 1 connector is the opposite phase as the digital output buffer. Data changes on falling CLK edge.

Jj

REFT internal: REFT from TLV5535 internal reference

jJ

REFT external: REFT from onboard voltage reference circuit

Jj

REFB internal: REFB from TLV5535 internal reference

jJ

REFB external: REFB from onboard voltage reference circuit

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

FUNCTION

FUNCTION

control settings

REFERENCE

DESIGNATOR

W4 TL V5535 and digital output buf fer output enable control (1)

W5 TL V5535 and digital output buf fer output enable control (2)

W6 TL V5535 STDBY control

J

5535-574 OE

board-external OE

j

5535-574 OE

buffer needs to be pulled low from pin 5 on J1 1 connector to enable. The OE

pin 7 on J11 connector (W5 open) or is permanently enabled if W5 is closed.

J

5535 OE

-connected.

OE

j

5535 OE

the output can be disabled.

J

Stdby: STDBY is active (high).

j

Active: STDBY is low, via internal pulldown. STDBY can be taken high from pin 9 on J11 connector to enable standby

mode.

-connected: Connects OEs of TLV5535 and digital output buffer (574 buffer). Use this when no

is used. In addition, close W5 to have both OEs permanently enabled.

-disconnected: Disconnects OEs of TL V5535 and digital output buffer (574 buffer). The OE for the output

to GND: Connects OEs of TL V5535 to GND. Additionally connects OE of 74ALS574 to GND if W4 is 5535-574

external: Enables control of OE of TL V5535 via pin 7 on J1 1 connector . When taken high (internal pulldown)

FUNCTION

for TLV5535 is independently controlled from

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

19

Page 20

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

control settings (continued)

REFERENCE

DESIGNATOR

W7 TL V5535 PWDN REF control

W8 DAC enable

J

Pwdn_ref: PWDN_REF is active (high).

j

Active: PWDN_REF is low , via internal pulldown. PWDN_REF can be taken high from pin 10 on J11 connector to enable

pwdn_ref mode.

J

Active: D/A on

j

Standby: D/A off

FUNCTION

20

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 21

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

.1 µF

C33

STDBY

DV3

.1 µF

GND

OUT

2OUT

–

6

2IN

R15

.1 µF

TLV5535PW

C35

.1 µF

W2

J9

7

U4B

+

5

2IN

1 kΩ

AV +12

W5

U2D

R28

TLE2144CDW

C31

.1 µF

4

W7

W6

20

R13

11

12

13

W1

321

49.9

R29

SN74ALVC00

EXT_REFB

R26

1OUT

U4A

–

2

3

1IN

1IIN

R5

REF3V

DV3

20

U2C

10

1

+

R6 5 kΩ

2.1 kΩ

R17

8

9

C32

.1 µF

AV –12

13

R9

1 kΩ

R10

Q(0–7)

Q7Q6Q5Q4Q3Q2Q1

6

U2B

4

20

SN74ALVC00

10

EXT_REFT

10

R27

4OUT

16

TLE2144CDW

U4D

R16

1 kΩ

–

+

15

14

4IN

4IN

R12

1 kΩ

3OUT

10

U4C

1 kΩ

–

+

11

12

3IN

3IN

1 kΩ

R7

R8

1 kΩ

REF3V

Q0

CLK_OUT

20

R37

SN74ALVC00

5

W3

3

U2A

1

CLK_IN

SN74ALVC00

2

TP3 TP4

REFTI

REFBI

SW2 SW1

EXT_REFB EXT_REFT

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

TP1 TP2

REFTO

C40

REFBO

J11

R2

C44

10µ F

+

C43

.01 µF

.1 µF

C37

.1 µF

C38

10µ F

+

C39

.1 µF

C36

.01 µF

0

C23

REF3V

10µ F

+

8

6

5

7

PG

OUT

OUT

SENSE

ININEN

U1

342

C27

AV5

J10

DRV3

DV5

R11

10 kΩ

W8

C29

C41

DV5

.1 µF

R14

10 kΩ

9

NC

NC

BLK

CLK

8

D9

7

D8

6

D7

5

D6

4

D5

3

D4

2

D3

1

32

.1 µF

.1 µF

C28

DV5

11161514131210

U3

R4

3.24 kΩ

.1 µF

C26

C25

.1 µF

AV5

17

18

19

20

21

22

23

24

R3

200

J8

VB

CE

NC

IREF

DVSS

SREF

VREF

AVDD

AVDD

VG

IO

IO

AVSSNCDVSS

DVDDNCD0D1D2

25262728293031

DV5

DVDD

C30

R1

.1 µF

C22

10µ F

+

R34

ANALOG IN

AV3

C45

R40

10 kΩ

U5

.1 µF

20

DV3

CXD2306Q

R18

R19

R20

R21

R22

R23

R25

20

R24

10 k Ω

49.9

.1 µF

GND

TPS7133QD

1

C42

C46

.1 µF

28

27262524232221201918171615

AIN

CML

AVSS

DRVDD

U6

1

W4

1123456789

1

OC

CLK

DV3

20

20

20

20

20

20

20

AVSS

AVDD

PWDN_REF

D0D1D2D3D4D5D6D7DRVSS

2345678

20202020202020

R39

R38

R36

R35

R33

R32

1D2D3D4D5D6D7D

1Q2Q3Q4Q5Q6Q7Q

19181716151413

10 kΩ

10 kΩ

10 kΩ

10 kΩ

10 kΩ

10 kΩ

R48

R47

R46

R45

R44

R43

.1 µF

REFBI

REFBO

9

R31

12

10 kΩ

R42

AVSS

REFTI

REFTO

DVSS

1011121314

20

R30

8D

SN74LVT574DW

DGND

10

8Q

DV5DV5

X1

10 kΩ

R41

C34

AV3

BG

AVDD

CLKOEDVDD

C24

VCC

OE

DAC_OUT

DV5

CLOCK IN

Figure 15. EVM Schematic

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

21

Page 22

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Analog +12 V

J6

1

C11

1 µF

2

Analog –12 V

J7

1

C13

1 µF

2

Analog +5 V

J5

1

C9

1 µF

2

Analog +3.3 V

J4

1

C7

1 µF

2

+

4.7 µH

+

C12

10 µF

4.7 µH

C14

10 µF

4.7 µH

+

C10

10 µF

4.7 µH

+

C8

10 µF

L6

L7

L5

L4

+

+

C20

10 µF

C21

10 µF

+

C19

10 µF

+

C18

10 µF

AV +12 V

AV –12 V

AV5

AV3

Digital +5 V

J3

1

C5

1 µF

2

Digital +3.3 V (DVDD)

J2

1

C3

1 µF

2

Digital +3.3 V (DRVDD)

J1

1

C1

1 µF

2

+

10 µF

+

10 µF

+

10 µF

L3

4.7 µH

C6

L2

4.7 µH

C4

L1

4.7 µH

C2

+

C17

10 µF

+

C16

10 µF

+

C15

10 µF

DV5

DV3

DRV3

Figure 15. EVM Schematic (continued)

22

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 23

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Figure 16. EVM Board Layout, Top Overlay

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

23

Page 24

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Figure 17. EVM Board Layout, Top Layer

24

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 25

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Figure 18. EVM Board Layout, Internal Plane 1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

25

Page 26

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Figure 19. EVM Board Layout, Internal Plane 2

26

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 27

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

3350 (mil)

4200 (mil)

Figure 20. EVM Board Layout, Drill Drawing for Through Hole

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

27

Page 28

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Figure 21. EVM Board Layout, Bottom Layer

28

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 29

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Table 3. TLV5535EVM Bill of Material

QTY. REFERENCE DESIGNATOR VALUE SIZE DESCRIPTION

7 C1, C11, C13, C3, C5, C7, C9 1 µF 1206 ceramic multilayer capacitor Any

18 C10, C12, C14, C15, C16,

C17, C18, C19, C2, C20, C21,

C22, C23, C4, C6, C8, C38,

C44

2 C36, C43 0.01 µF 805 Ceramic multilayer Any

19 C24, C25, C26, C27, C28,

C29, C30, C31, C32, C33,

C34, C35, C37, C39, C40,

C41, C42, C45, C46

7 J1, J2, J3, J4, J5, J6, J7 Screw Con 2 terminal screw connector Lumberg

3 J10, J8, J9 SMA PCM mount, SMA Jack Johnson Components

1 J11 IDC26 13I × 2.025I square pin header Samtec

7 L1, L2, L3, L4, L5, L6, L7 4.7 µH 4.7 µH DO1608C-472-Coil Craft Coil Craft

1 R2 0 1206 Chip resistor Any

2 R26, R27 10 1206 Chip resistor Any

12 R1, R11, R14, R40, R41, R42,

R43, R44, R45, R46, R47, R48

6 R10, R12, R15, R16, R8, R9 1 K 1206 Chip resistor Any

1 R5 2.1 K 1206 Chip resistor Any

20 R13, R17, R18, R19, R20,

R21, R22, R23, R24, R25,

R29, R30, R31, R32, R33,

R35, R36, R37, R38, R39

1 R3 200 1206 Chip resistor Any

1 R4 3.24 K 1206 Chip resistor Any

2 R28, R34 49.9 1206 Chip resistor Any

1 R6 5 K 4 mm SM pot-top adjust Bourns

1 R7 1 K 4 mm SM pot-top adjust Bourns

2 SW1, SW2 SPDT C&K tiny series–slide switch C&K

4 TP1, TP2, TP3, TP4 TP Test point, single 0.025I pin Samtec

1 U3 CXD2306Q Sony

1 U2 SN74ALVC00D 14-SOIC (D) Quad 2-input positive NAND Texas Instruments

1 U5 SN74LVT574DW 20-SOP (DW) Texas Instruments

†

Manufacturer and part number data for reference only. Equivalent parts might be substituted on the EVM.

10 µF 3216 16 V, 10 µF, tantalum capacitor Any

0.1 µF 805 Ceramic multilayer capacitor Any

10 K 1206 Chip resistor Any

20 1206 Chip resistor Any

MANUFACTURER/

PART NUMBER

KRMZ2

142-0701-206

TSW-113-07-L-D

DO1608-472

3214W-5K

3214W-1K

TS01CLE

TSW-101-07-L-S

or equivalent

CXD2306Q

SN74ALVC00D

SN74LVT574DW

†

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

29

Page 30

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

TLV5535 EVALUA TION MODULE

Table 3. TLV5535EVM Bill of Material (Continued)

QTY. REFERENCE DESIGNATOR VALUE SIZE DESCRIPTION

1 U4 TLE2144CDW 16-SOP(D) Quad op amp Texas Instruments

1 U6 TLV5535PW 28-TSSOP (PW) Texas Instruments

1 U1 TPS7133 8-SOP(D) Low-dropout voltage regulator Texas Instruments

6 W2, W4, W5, W6, W7, W8 SPST 2 position jumper , 0.1I spacing Samtec

2 W1, W3 DPFT 3 position jumper, 0.1I spacing Samtec

1 X1 NA Crystal oscillator Epson

†

Manufacturer and part number data for reference only. Equivalent parts might be substituted on the EVM.

MANUFACTURER/

PART NUMBER

TLE2144CDW/

TLE2144IDW

TLV5535PW

TPS7133QD

TSW-102-07-L-S

or equivalent

TSW-103-07-L-S

or equivalent

SG-8002DC series

†

30

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Page 31

TLV5535

8-BIT, 35 MSPS, LOW -POWER ANALOG-TO-DIGITAL CONVERTER

SLAS221 – JUNE 1999

MECHANICAL DATA

PW (R-PDSO-G**) PLASTIC SMALL-OUTLINE PACKAGE

14 PIN SHOWN

0,65

14

1

1,20 MAX

0,30

0,19

8

4,50

4,30

7

A

0,15

0,05

6,60

6,20

M

0,10

Seating Plane

0,10

0,15 NOM

Gage Plane

0,25

0°–8°

0,75

0,50

PINS **

DIM

A MAX

A MIN

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

8

3,10

2,90

14

5,10

4,90

16

5,10

20

6,60

6,404,90

24

7,90

7,70

28

9,80

9,60

4040064/E 08/96

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

31

Page 32

PACKAGE OPTION ADDENDUM

www.ti.com

18-Jul-2006

PACKAGING INFORMATION

Orderable Device Status

(1)

Package

Type

Package

Drawing

Pins Package

Qty

Eco Plan

TLV5535IPW ACTIVE TSSOP PW 28 50 Green (RoHS &

no Sb/Br)

TLV5535IPWG4 ACTIVE TSSOP PW 28 50 Green (RoHS &

no Sb/Br)

TLV5535IPWR ACTIVE TSSOP PW 28 2000 Green (RoHS &

no Sb/Br)

TLV5535IPWRG4 ACTIVE TSSOP PW 28 2000 Green (RoHS &

no Sb/Br)

(1)

The marketing status values are defined asfollows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the devicewill be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in

a new design.

PREVIEW: Device has been announced but isnot in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production ofthe device.

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check

http://www.ti.com/productcontent for the latest availability information andadditional product content details.

TBD: The Pb-Free/Green conversion plan has notbeen defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements

for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered

at high temperatures, TI Pb-Free products aresuitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and

package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS

compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame

retardants (Br or Sb do not exceed0.1% by weight in homogeneous material)

(2)

Lead/Ball Finish MSL Peak Temp

CU NIPDAU Level-1-260C-UNLIM

CU NIPDAU Level-1-260C-UNLIM

CU NIPDAU Level-1-260C-UNLIM

CU NIPDAU Level-1-260C-UNLIM

(3)

(3)

MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder

temperature.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the

accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take

reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on

incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited

information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI

to Customer on an annual basis.

Addendum-Page 1

Page 33

PACKAGE MATERIALS INFORMATION

www.ti.com

TAPE AND REEL INFORMATION

11-Mar-2008

*All dimensions are nominal

Device Package

TLV5535IPWR TSSOP PW 28 2000 330.0 16.4 6.9 10.2 1.8 12.0 16.0 Q1

Type

Package

Drawing

Pins SPQ Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0 (mm) B0 (mm) K0 (mm) P1

(mm)W(mm)

Pin1

Quadrant

Pack Materials-Page 1

Page 34

PACKAGE MATERIALS INFORMATION

www.ti.com

11-Mar-2008

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

TLV5535IPWR TSSOP PW 28 2000 346.0 346.0 33.0

Pack Materials-Page 2

Page 35

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements,

and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should

obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are

sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard

warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where

mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not

responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing

such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products

and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be

provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in

such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at

the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are

designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated

products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Clocks and Timers www.ti.com/clocks Digital Control www.ti.com/digitalcontrol

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

RFID www.ti-rfid.com Telephony www.ti.com/telephony

RF/IF and ZigBee® Solutions www.ti.com/lprf Video & Imaging www.ti.com/video

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2008, Texas Instruments Incorporated

Wireless www.ti.com/wireless

Loading...

Loading...