TEXAS INSTRUMENTS TLV320AIC20, TLV320AIC21, TLV320AIC24, TLV320AIC25, TLV320AIC20K Technical data

...

www.ti.com

Low-Power, Highly-Integrated, Programmable

16-Bit, 26-KSPS, Dual-Channel CODEC

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

FEATURES

• Stereo 16-Bit Oversampling Sigma-Delta A/D

• Differential and Single-Ended Analog

Input/Output

Converter • Built-In Analog Functions:

• Stereo 16-Bit Oversampling Sigma-Delta D/A – Analog and Digital Sidetone

Converter

• Support Maximum Master Clock of 100 MHz to

Allow DSPs Output Clock to be Used as a

Master Clock

• Selectable FIR/IIR Filter With Bypassing

Option

• Programmable Sampling Rate up to:

– Max 26 Ksps With On-Chip IIR/FIR Filter

– Max 104 Ksps With IIR/FIR Bypassed

– Antialiasing Filter (AAF)

– Programmable Input and Output Gain

Control (PGA)

– Microphone/Handset/Headset Amplifiers

– AIC20/21/20K Have a Built-In 8- Ω Speaker

Driver

– Power Management With Hardware/Software

Power-Down Modes 30 µW

• Separate Software Control for ADC and DAC

• On-Chip FIR Produced 84-dB SNR for ADC Power Down

and 92-dB SNR for DAC over 13-Khz BW

• Smart Time Division Multiplexed ( SMARTDM

Serial Port

– Glueless 4-Wire Interface to DSP

– Automatic Cascade Detection (ACD)

Self-Generates Master/Slave Device

Addresses

– Programming Mode to Allow On-The-Fly

Reconfiguration

– Continuous Data Transfer Mode to Minimize

Bit Clock Speed

– Support Different Sampling Rate for Each

Device

– Turbo Mode to Maximize Bit Clock For

Faster Data Transfer and Allow Multiple

Serial Devices to Share the Same Bus

– Allows up to Eight Devices to be Connected

®

• Fully Compatible With Common TMS320

) Family and Microcontroller Power Supplies

– 1.65-V - 1.95-V Digital Core Power

– 1.1-V - 3.6-V Digital I/O

– 2.7-V - 3.6-V Analog

• Internal Reference Voltage (V

• 2s Complement Data Format

• Test Mode Which Includes Digital Loopback

and Analog Loopback

APPLICATIONS

• Wireless Accessories

• Hands-Free Car Kits

• VOIP

• Cable Modem

• Speech Processing

to a Single Serial Port

• Host port

– 2-Wire Interface

– Selectable I2C or S2C

®

DSP

)

ref

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SMARTDM, TMS320, TMS320C5000, TMS320C6000 are registered trademarks of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2002–2005, Texas Instruments Incorporated

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

These devices have limited built-in ESD protection. The leads should be shorted together or the device

placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

DESCRIPTION

The TLV320AIC2x is a low-cost, low-power, highly-integrated, high-performance, dual-voice codec. It features

two 16-bit analog-to-digital (A/D) channels and two 16-bit digital-to-analog (D/A) channels, which can be

connected to a handset, headset, speaker, microphone, or a subscriber line via a programmable analog

crosspoint.

The TLV320AIC2x provides high resolution signal conversion from digital-to-analog (D/A) and from

analog-to-digital (A/D) using oversampling sigma-delta technology with programmable sampling rate.

The TLV320AIC2x implements the smart time division multiplexed serial port (SMARTDM™) . The SMARTDM

port is a synchronous 4-wire serial port in TDM format for glue-free interface to TI DSPs (i.e., TMS320C5000

TMS320C6000

mode and on-the-fly reconfiguration programming mode. The TLV320AIC2x can be gluelessly cascaded to any

SMARTDM-based device to form a multichannel codec, and up to eight TLV320AIC2x codecs can be cascaded

to a single serial port.

The TLV320AIC2x provides a flexible host port. The host port interface is a two-wire serial interface that can be

programmed to be either an industrial standard I2C or a simple S2C (start-stop communication protocol).

The TLV320AIC2x integrates all of the critical functions needed for most voice-band applications including MIC

preamplifier, handset amplifier headset amplifier, 8- Ω speaker driver, sidetone control, antialiasing filter (AAF),

input/output programmable gain amplifier (PGA), and selectable low-pass IIR/FIR filters.

The TLV320AIC2x implements an extensive power management; including device power-down, independent

software control for turning off ADC, DAC, operational-amplifiers, and IIR/FIR filter (bypassable) to maximize

system power conservation. The TLV320AIC2x consumes only 14.9 mW per channel at 3 V.

The TLV320AIC2x low power operation from 2.7-V to 3.6-V power supplies along with extensive power

management make it ideal for portable applications including wireless accessories, hands-free car kits, VOIP,

cable modem, and speech processing. Its low group delay characteristic makes it suitable for single or

multichannel active control applications.

The TLV320AIC2x is characterized for commercial operation from 0°C to 70°C, and industrial operation from

-40°C to 85°C. The TLV320AIC2xk is characterized for industrial operation from -40°C to 85°C.

®

DSP platforms) and microcontrollers. The SMARTDM™ supports both continuous data transfer

®

,

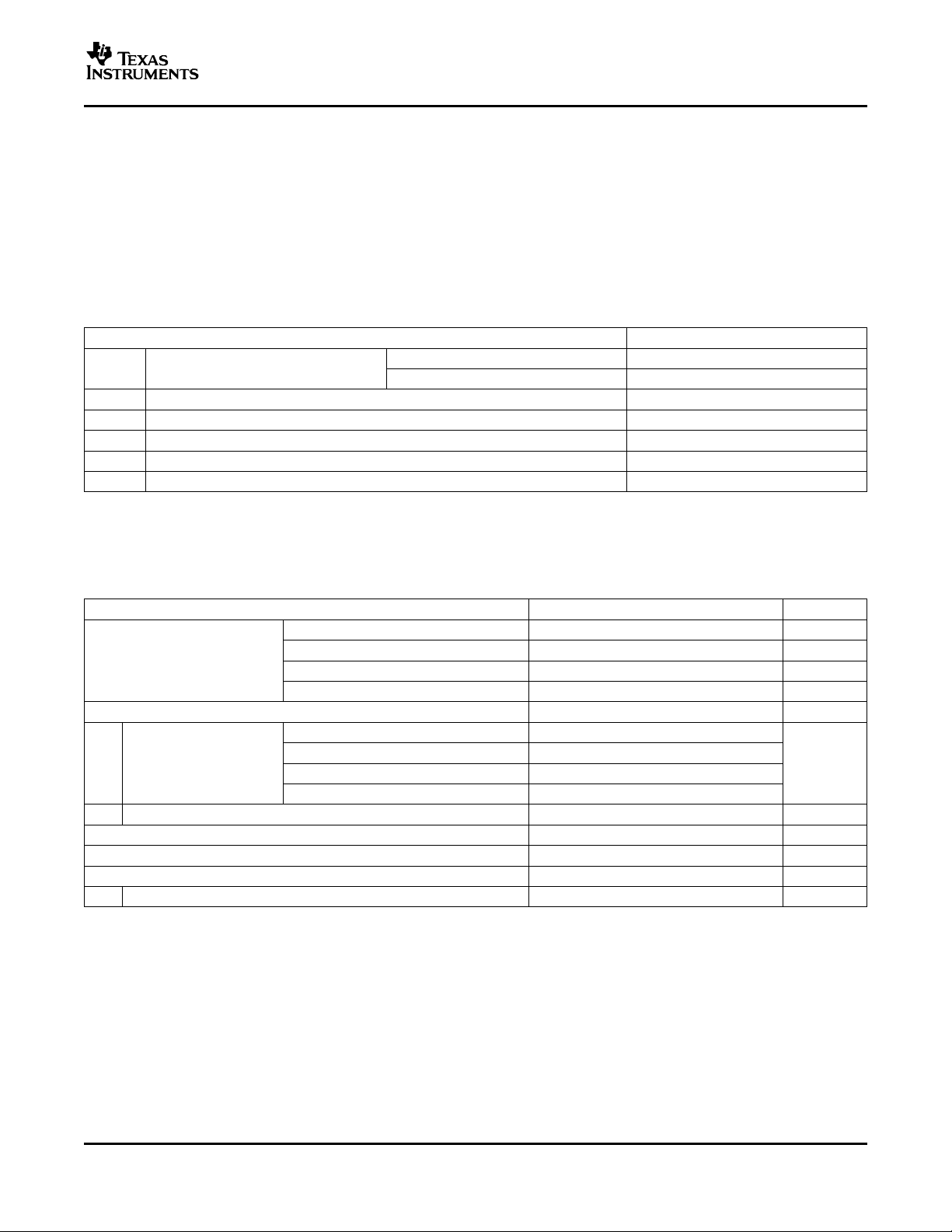

ORDERING INFORMATION

T

A

0°C to 70°C TLV320AIC2xC

-40°C to 85°C TLV320AIC2xI

(1) For the most current package and ordering information, see the Package Option Addendum at the

end of this document, or see the TI website at www.ti.com .

2

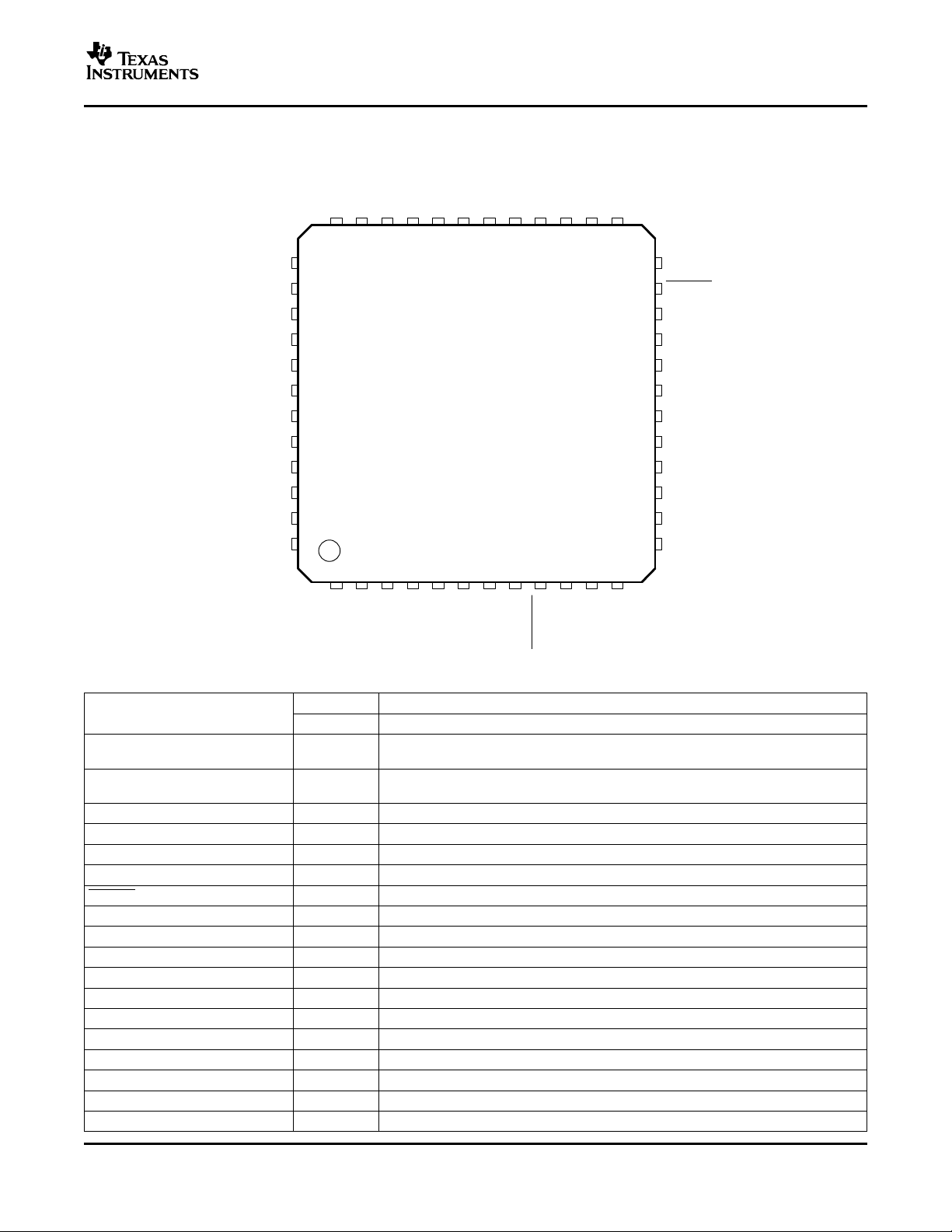

48-TQFP PFB PACKAGE

(1)

www.ti.com

PFB

TOP VIEW

1

2 3 4 5 6 7 8 9 10 11 12

13

14

15

16

17

18

19

20

21

22

23

24

36 35 34 33 32 31 30 29 28 27 26 25

37

38

39

40

41

42

43

44

45

46

47

48

MICBIAS

MICI+

MICI-

AVDD1

AVSS1

CIDI+

CIDI-

DRVSS2

SPKO-

DRVDD

SPKO+

DRVSS1

VSS

RESET

MCLK

M/S

SCLK

FS

DIN

DOUT

DVSS

DVDD

FSD

IOVSS

LCDAC

HNSO-

HNSO+

HNSI-

HNSI+

AVDD

AVSS

LINEI+

LINEI-

LINEO-

LINEO+

NC

HDSI-

HDSI+

HDSO-

HDSO+

AVDD2

AVSS2

TESTP

NC

PWRDN

SDA

SCL

IOVDD

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

Terminal Functions

TERMINAL

NAME NO. I/O DESCRIPTION

HDSI- 1

HDSI+ 2

HDSO- 3

HDSO+ 4

AVDD2 5 I Analog power supply

AVSS2 6 I Analog ground

TESTP 7 I Test pin. Should be connected to digital ground.

NC 8, 48 Not connected

PWRDN 9 I Power down

SDA 10 I/O I2C/S

SCL 11 I I2C/S

IOVDD 12 I I/O power supply

IOVSS 13 I I/O ground

FSD 14 O Frame sync delayed

DVDD 15 I Digital supply (1.8 V)

DVSS 16 I Digital ground

DOUT 17 O Data OUT

DIN 18 I Data IN

FS 19 I/O Frame sync

SCLK 20 I/O Serial clock

I Head-set input. The Head-set input can be treated similar to the Line-input pins

O 150- Ω output

2

C data

2

C clock

3

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

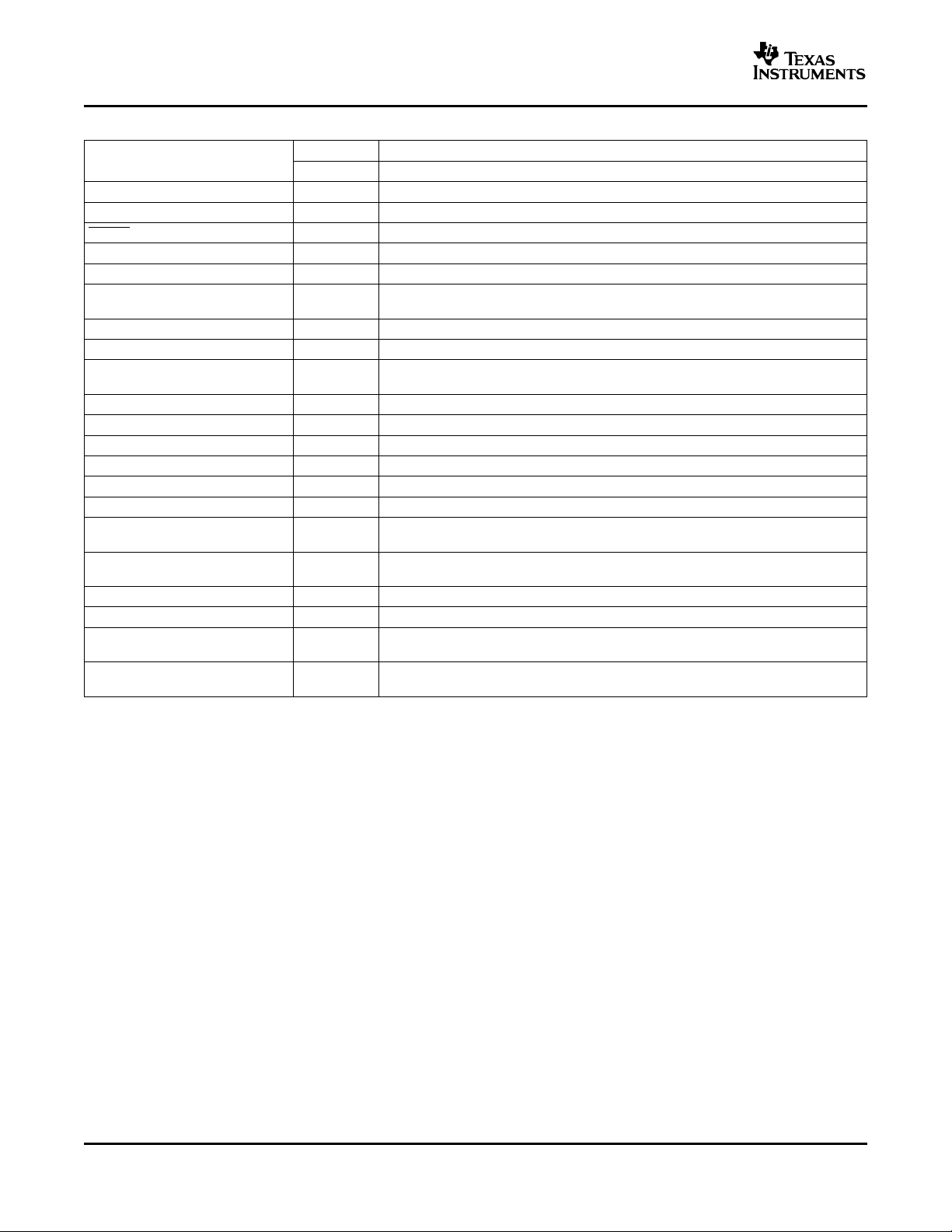

Terminal Functions (continued)

TERMINAL

NAME NO. I/O DESCRIPTION

M/S 21 I Master slave select applied to CODEC1 only. CODEC2 is always a slave.

MCLK 22 I Master clock

RESET 23 I Reset

VSS 24 I Device ground. Typically this should be connected to the Analog Ground.

DRVSS1 25 I Driver ground

SPKO+ 26

SPKO- 28

DRVDD 27 I Driver supply

DRVSS2 29 I Driver ground

CIDI- 30

CIDI+ 31

AVDD1 33 I Analog supply

AVSS1 32 I Analog ground

MICI- 34 I Microphone input

MICI+ 35 I Microphone input

MICBIAS 36 I Microphone bias

LCDAC 37 O 6-Bit DAC output may be used to drive LCDAC

HNSO- 38

HNSO+ 39

HNSI- 40

HNSI+ 41

AVDD 42 I Analog supply

AVSS 43 I Analog ground

LINEI+ 44

LINEI- 45

LINEO- 46

LINEO+ 47

O 8- Ω output

I Caller-ID input. The Caller-ID input can be treated similar to the Line-input pins

O 150- Ω output

I Hand-set input. The Hand-set input can be treated similar to the Line-input pins

I Line input

O 600- Ω output

4

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

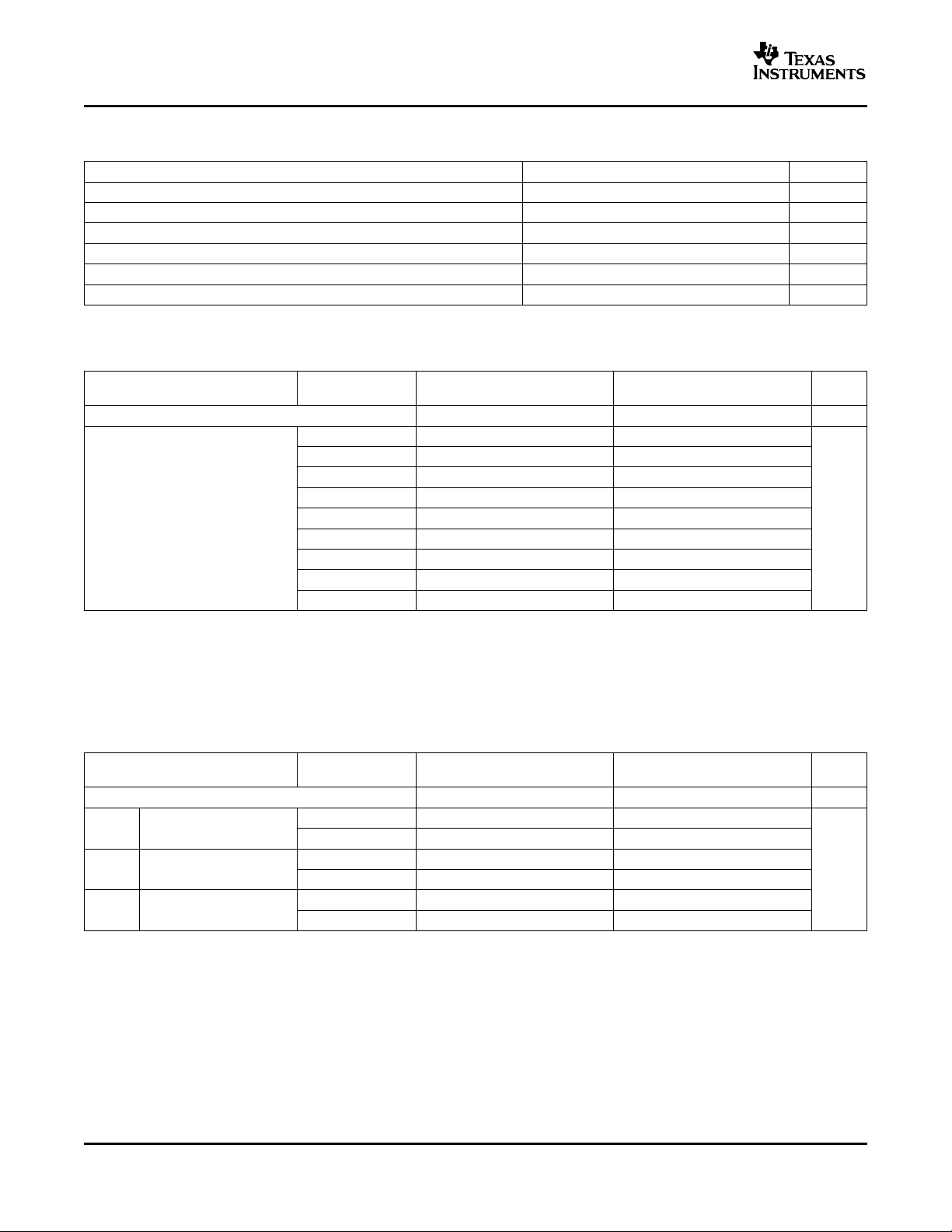

Electrical Characteristics

All specifications are common across the AIC20, AIC21, AIC24, AIC25, AIC20K, and AIC24K except where

explicitly stated.

AIC20/21/24/25: Over Recommended Operating Free-Air Temperature Range, AVDD = 3.3 V, DVDD = 1.8 V,

IOVDD = 3.3 V (Unless Otherwise Noted)

AIC20K/24K: Over Recommended Operating Free-Air Temperature Range, AVDD = 3.3 V, DVDD = 1.8 V,

IOVDD = 3.3 V (Unless Otherwise Noted)

Absolute Maximum Ratings

(1)

over Operating Free-Air Temperature Range (Unless Otherwise Noted)

TLV320AIC2x

AVDD, IOVDD, DRVDD

(2)

(2)

-0.3 V to 2.25 V

-0.3 V to 4 V

V

CC

V

O

V

I

T

A

T

stg

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

(2) All voltage values are with respect to VSS.

Supply voltage range: DVDD

Output voltage range, all digital output signals -0.3 V to IOVDD + 0.3 V

Input voltage range, all digital input signals -0.3 V to IOVDD + 0.3 V

Operating free-air temperature range -40°C to 85°C

Storage temperature range -65°C to 150°C

Case temperature for 10 seconds: package 260°C

only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Recommended Operating Conditions

MIN NOM MAX UNIT

Analog, AVDD 2.7 3.3 3.6 V

V

Supply voltage

CC

Analog single-ended peak-to-peak input voltage, V

R

Output load resistance, Ω

L

C

Analog output load capacitance 20 pF

L

Digital output capacitance 20 pF

Master clock 100 MHz

ADC or DAC conversion rate 26 kHz

T

Operating free-air temperature, -40 85 °C

A

(1) DRVDD should be kept at the same voltage as AVDD.

Analog output driver, DRVDD

Digital core, DVDD 1.65 1.8 1.95 V

Digital I/O, IOVDD 1.1 3.3 3.6 V

Between LINEO+ and LINEO- (differential) 600

Between HDSO+ and HDSO- (differential) 150

Between HNSO+ and HDSO- (differential) 150

Between SPKO+ and SPKO- (differential) 8

(1)

I(analog)

2.7 3.3 3.6 V

2 V

5

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

Digital Inputs and Outputs

FS = 8 KHz, outputs not loaded

PARAMETER MIN TYP MAX UNIT

V

OH

V

OL

I

IH

I

IL

C

i

C

o

ADC PATH FILTER

FS = 8 KHz

PATH FILTER FIR FILTER IIR FILTER

(1) The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The analog input test signal is a sine wave with

0 dB = 4 V

band scales linearly with the sample rate.

(2) The filter characteristics are specified by design and are not tested in production. In places where more than one value is specified, the

first value is with the High Pass Filter on and the second value is with the HPF off

High-level output voltage, DOUT 0.8 IOVDD V

Low-level output voltage, DOUT 0.1 IOVDD V

High-level input current, any digital input 5 µA

Low-level input current, any digital input 5 µA

Input capacitance 3 pF

Output capacitance 5 pF

(1) (2)

PARAMETER MIN TYP MAX MIN TYP MAX UNIT

Filter gain relative to gain

at 1020 Hz

as the reference level for the analog input signal. The pass band is 0 to 3600 Hz for an 8-KHz sample rate. This pass

I(PP)

TEST

CONDITIONS

0 Hz to 60 Hz -27 / 0.07 -27 / 0.15

60 Hz to 200 Hz -1 / 0.07 -0.75 / 0.15

200 Hz to 300 Hz -0.03 / 0.05 0. 11 / 0.15

300 Hz to 2.4 KHz -0.1 0.15 -0.1 0.25

2.4 kHz to 3 kHz -0.05 0.15 -0.5 0.2 dB

3 kHz to 3.4 KHz -0.5 0.1 -0.5 0.2

3.4 kHz to 3.6 KHz -0.4 0.15

4 KHz -26 -42

4.5 KHz to 72 kHz -52 -52

ADC DYNAMIC PERFORMANCE

With FIR Filter, FS = 8 KHz

PARAMETER MIN TYP MAX MIN TYP MAX UNIT

Line In Driver AIC20/21/24/25 AIC20k/24k

SNR Signal-to-noise ratio

THD Total harmonic distortion dB

THD+N

(1) The test condition is a differential 1020-Hz input signal with an 8-KHz conversion rate. Input and output common mode is 1.35 V.

6

Signal-to-harmonic

distortion + noise

(1)

TEST

CONDITIONS

VI= -3 dB 81 84 70 84

VI= -9 dB 73 76 76

VI= -3 dB 83 90 70 90

VI= -9 dB 81 88 88

VI= -3 dB 80 83 83

VI= -9 dB 73 76 76

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

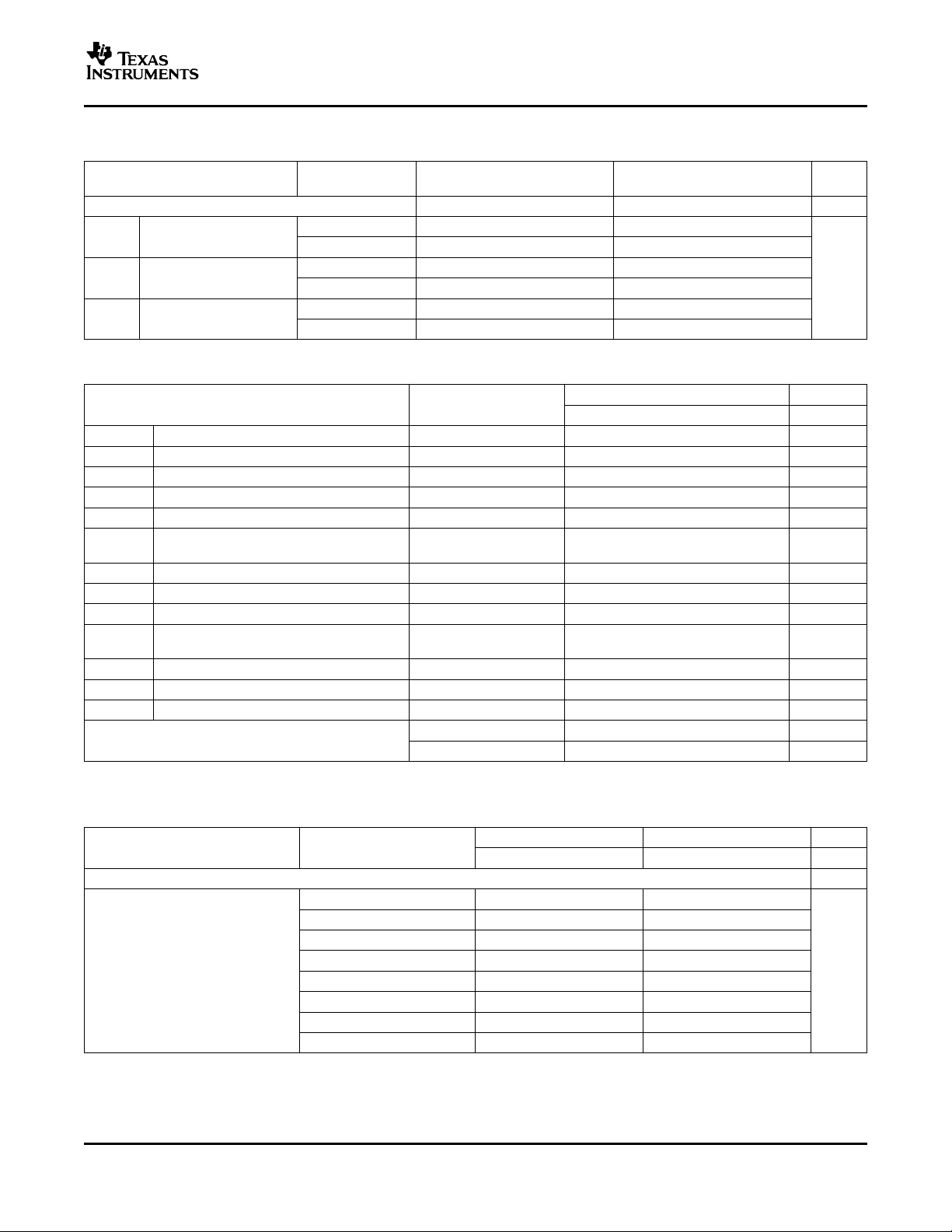

ADC DYNAMIC PERFORMANCE

With IIR Filter, FS = 8 KHz

PARAMETER MIN TYP MAX MIN TYP MAX UNIT

SNR Signal-to-noise ratio

THD Total harmonic distortion dB

THD+N

Signal-to-harmonic

distortion + noise

ADC CHANNEL CHARACTERISTICS

PARAMETER TEST CONDITIONS

V

I(pp)

V

IO

I

B

E

G

E

O(ADC)

CMRR VI= -100 mV at 1020 Hz 50 dB

R

i

C

i

Differential-ended input level PGA gain = 0 dB 4 V

Input offset voltage ±5 mV

Input bias current 125 µA

Common mode voltage 1.35 V

Dynamic range VI= -3 dB 87 dB

Mute attenuation PGA = MUTE dB

Intrachannel isolation 87 dB

Gain error VI= -3 dB at 1020 Hz -0.45 dB

ADC converter offset error ±15 mV

Common-mode rejection ratio at INMx and

INPx

Idle channel noise V

Input resistance TA= 25°C 10 k Ω

Input capacitance TA= 25°C 2 pF

Channel delay

TEST

CONDITIONS

AIC20/21/24/25 AIC20k/24k

VI= -3 dB 82 82

VI= -9 dB 76 76

VI= -3 dB 83 83

VI= -9 dB 77 77

VI= -3 dB 78 78

VI= -9 dB 70 70

AIC20/21/24/25/20k/24k

MIN TYP MAX UNIT

Zero Digital

(INP,INM,MICIN)

= 0 V 70 µVrms

IIR 5/f

FIR 17/f

Code

s

s

S

S

DAC PATH FILTER

FS = 8 KHz

PATH FILTER, FS = 8 KHz

(1) The filter gain outside of the passband is measured with respect to the gain at 1020 Hz. The input signal is the digital equivalent of a

sine wave (digital full scale = 0 dB). The nominal differential DAC channel output with this input condition is 4 V

0 to 3600 Hz for an 8-kHz sample rate. This pass band scales linearly with the conversion rate.

(2) The filter characteristics are specified by design and are not tested in production.

(1) (2)

PARAMETER TEST CONDITIONS

Filter gain relative to gain

at 1020 Hz

FIR FILTER IIR FILTER

MIN TYP MAX MIN TYP MAX UNIT

0 Hz to 200 Hz 0.1 0.05

200 Hz to 300 Hz -0.05 0.05

300 Hz to 2.4 KHz -0.25 0.15 -0.1 0.1

2.4 kHz to 3 kHz -0.3 0.1 -0.2 0.1

3 kHz to 3.4 KHz -0.55 0.05 -0.25 0.05

3.4 kHz to 3.6 KHz -30 0

4 KHz -28 -34

4.5 KHz to 72 KHZ -70 -70

. The pass band is

I(PP)

dB

7

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

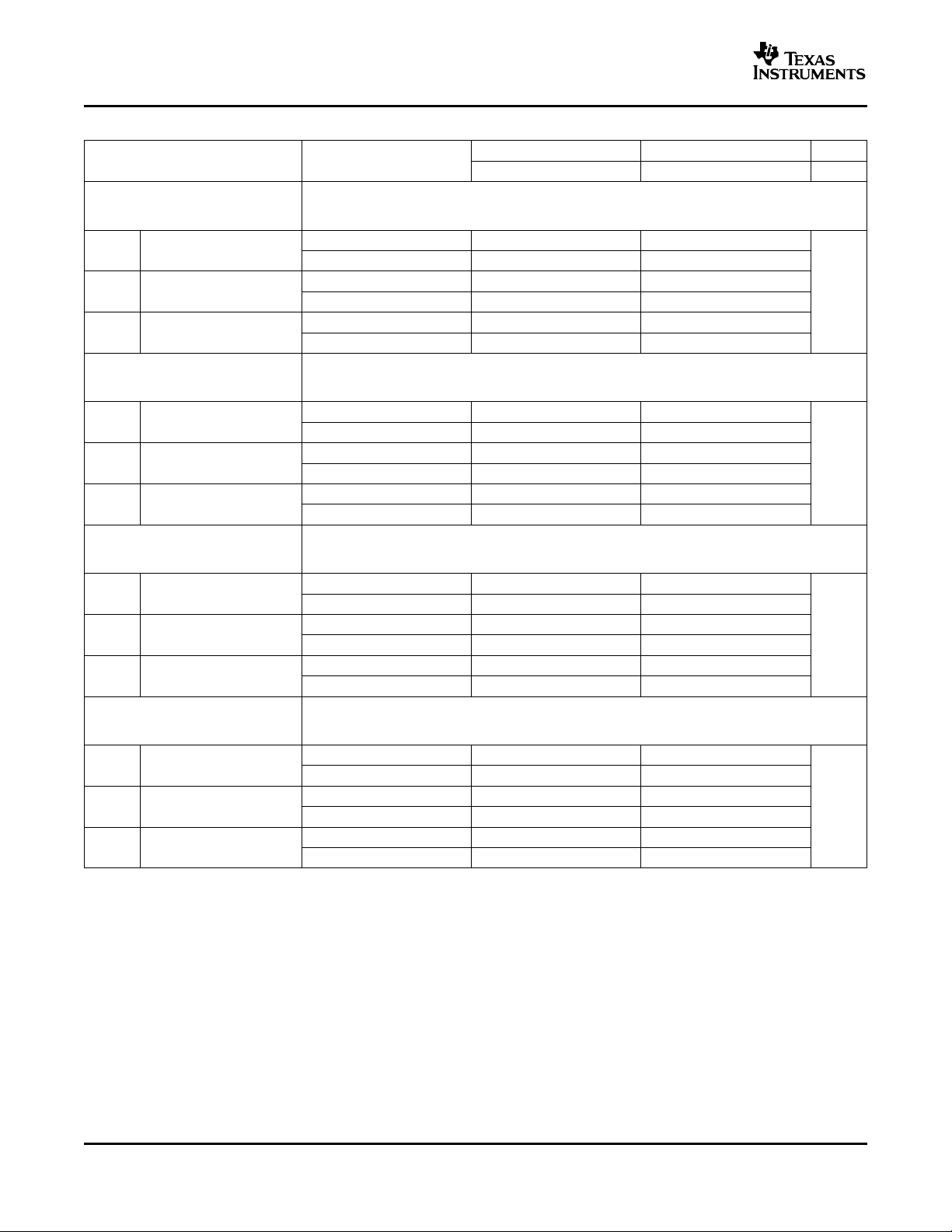

DAC DYNAMIC PERFORMANCE

PARAMETER TEST CONDITIONS

DAC Line Output (LINEO-, LINEO+)

SNR Signal-to-noise ratio

THD Total Harmonic Distortion dB

THD+N

DAC Line Output (LINEO-, LINEO+)

SNR Signal-to-noise ratio

THD Total Harmonic Distortion dB

THD+N

DAC Headphone Output (HDSO-,

SNR Signal-to-noise ratio

THD Total Harmonic Distortion dB

THD+N

SNR Signal-to-noise ratio

THD Total Harmonic Distortion dB

THD+N

(1) The conversion rate is 8 kHz.

(2) The speaker driver is valid only for the AIC20/21/20K.

Using FIR Filter

Signal-to-total Harmonic

Distortion + noise

Using IIR Filter

Signal-to-total Harmonic

Distortion + noise

HDSO+), (HNSO-, HNSO+)

Signal-to-total Harmonic

Distortion + noise

DAC Speaker Output (SPKO-,

SPKO+)

Signal-to-total Harmonic

Distortion + noise

(1) (2)

The test condition is the digital equivalent of a 1020-Hz input signal with an 8-kHz conversion rate.

The test is measured at output of the application schematic low-pass filter. The test is conducted in

16-bit mode.

VI= 0 dB 88 92 80 92

VI= -9 dB 81 83 83

VI= 0 dB 84 90 70 90

VI= -9 dB 77 84 84

VI= 0 dB 82 88 88

VI= -9 dB 76 80 80

The test condition is the digital equivalent of a 1020-Hz input signal with an 8-kHz conversion rate.

The test is measured at output of the application schematic low-pass filter. The test is conducted in

16-bit mode.

VI= 0 dB 83 83

VI= -9 dB 74 74

VI= 0 dB 85 85

VI= -9 dB 80 80

VI= 0 dB 80 80

VI= -9 dB 73 73

The test condition is the digital equivalent of a 1020-Hz input signal with an 8-kHz conversion rate.

The test is measured at output of the application schematic low-pass filter. The test is conducted in

(1)

16-bit mode.

VI= 0 dB 92 92

VI= -9 dB 83 83

VI= 0 dB 90 90

VI= -9 dB 89 89

VI= 0 dB 88 88

VI= -9 dB 82 82

The test condition is the digital equivalent of a 1020-Hz input signal with an 8-kHz conversion rate.

The test is measured at output of the application schematic low-pass filter. The test is conducted in

16-bit mode.

VI= 0 dB 91 91

VI= -9 dB 83 83

VI= 0 dB 91 91

VI= -9 dB 91 91

VI= 0 dB 88 88

VI= -9 dB 82 82

AIC20/21/24/25 AIC20k/24k

MIN TYP MAX MIN TYP MAX UNIT

8

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

DAC CHANNEL CHARACTERISTICS

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Dynamic range VI= 0 dB at 1020 Hz 92 dB

Interchannel isolation 90 dB

E

G

V

OO

V

O

(1) The conversion rate is 8 kHz.

OUTPUT AMPLIFIER CHARACTERISTICS

SPEAKER INTERFACE

HANDSET AND HEADSET INTERFACE

LINE INTERFACE

(1) The speaker driver is valid only for the AIC20/21/20k.

Gain error, 0 dB VO= 0 dB at 1020 Hz -0.7 dB

Mute attenuation PGA = Mute 90 dB

Common-mode voltage 1.35 V

Idle channel narrow band noise 0 - 4 kHz

Output offset voltage at OUTP1_150

(differential)

Analog output voltage, (3.3 V) HDSO+ 0.35 2.35 V

Channel delay

PARAMETER TEST CONDITIONS

(1)

Speaker output power 250 mW

Maximum output current 250 mA

Speaker output power 13 mW

Maximum output current 13 mA

Speaker output power 3.5 mW

Maximum output current 3.5 mA

DIN = All zeros ±8 V

V

= 3.3 V, fully

CC

differential, 8- Ω load

V

= 3.3 V, fully

CC

differential, 150- Ω load

V

= 3.3 V, fully

CC

differential, 600- Ω load

(1)

IIR 5/f

FIR 18/f

AIC20/21/24/25/20k/24k

MIN TYP MAX UNIT

40 V rms

s

s

s

s

BIAS AMPLIFIER CHARACTERISTICS

PARAMETER TEST CONDITIONS

V

Output voltage 1.35/2.35 V

O

Integrated noise 300 Hz – 13 KHz 20 µV

V

Offset voltage 10 mV

S

Current drive 5 mA

Unity gain bandwith 1 MHz

DC gain 90 dB

PSRR 70 dB

POWER-SUPPLY REJECTION

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

AV

DD

(1) Power supply rejection measurements are made with both the ADC and the DAC channels idle and a 200 mV peak-to-peak signal

Supply-voltage rejection ratio, analog supply

(fj = 0 to fs/2 )

applied to the appropriate supply.

(1)

Differential 75

AIC20/21/24/25/20k/24k

MIN TYP MAX UNIT

9

www.ti.com

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

POWER-CONSUMPTION

PARAMETER TEST CONDITIONS

ADC (single channel) 5.7

DAC (single channel) Without drivers 3.5

Speaker driver

Handset driver No signal 2

Headset driver No signal 2

Lineout driver No signal 2 mW

Reference 2.3

Digital PLL off 3.4

PLL

Total Analog with all sections on No signal, PLL off 35.8

POWER DOWN CURRENT

Hardware power-down (no clock) 1

Software power-down

(1) The speaker driver is valid only for the AIC20/21/20k.

(1)

No signal 9.3

Analog 4.6

Digital 1.8

Analog, PLL off 2 µA

Digital 650

AIC20/21/24/25/20k/24k

MIN TYP MAX UNIT

LCD DAC

PARAMETER

V

Output range 0.35 2.35 V

O

Sampling rate 104 kHz

INL ±0.5 LSB

DNL ±0.25 LSB

V

Offset voltage ±25 mV

S

E

Gain error ±0.02 dB

G

Typical ADC performance With PGA Gain Setting Using FIR

PGA GAIN SETTING SNR THD SINAD UNIT

9 dB 83 90 81

18 dB 83 97 83 dB

24 dB 78 95 77

36 dB 72 95 72

(1) Test condition is a 1020-Hz input differential signal with an 8-kHz conversion rate. Input amplitude is given such that output of PGA is at

-3 dB level.

AIC20/21/20k

MIN TYP MAX UNIT

(1)

10

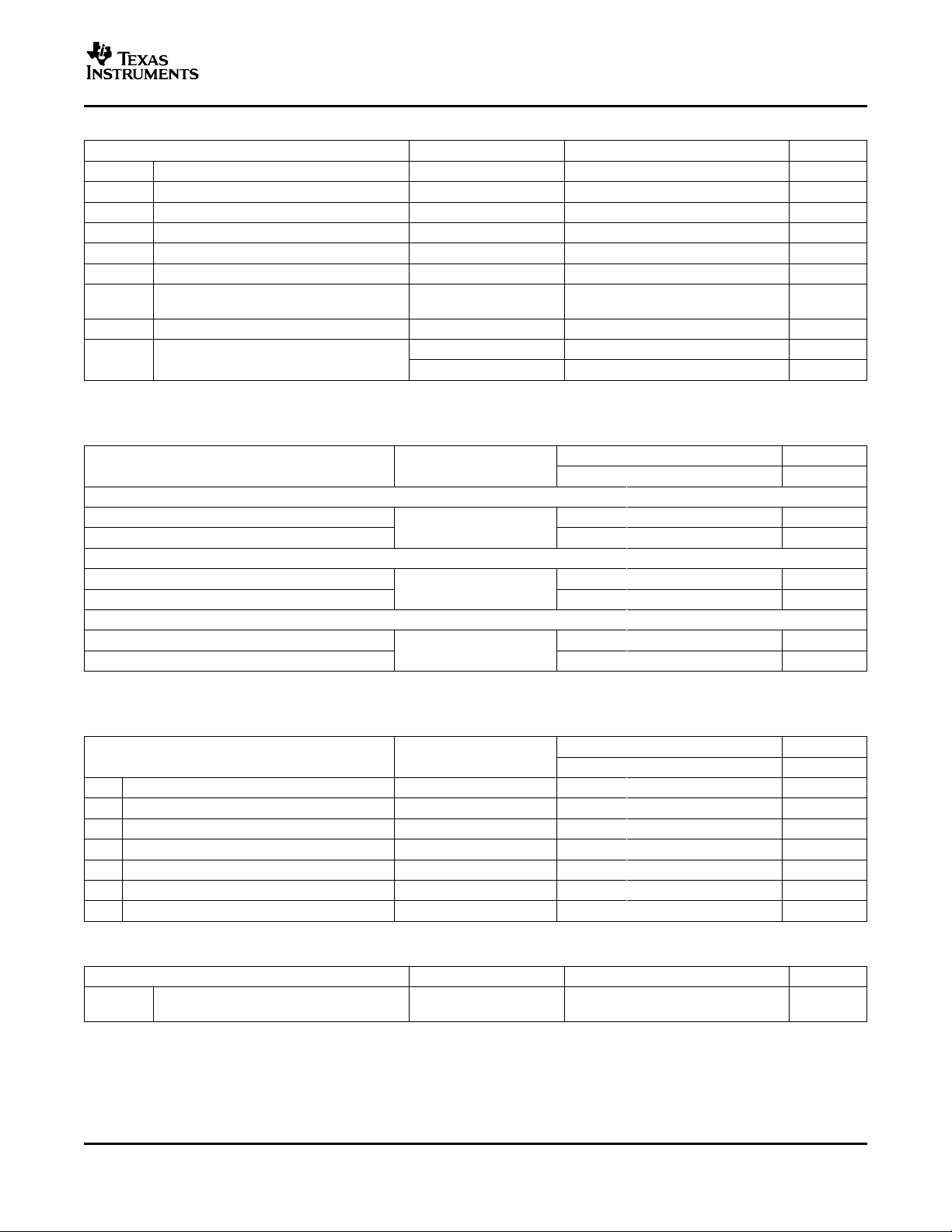

www.ti.com

DAC

+

+

Σ-∆

DAC

0dB to -42 dB

(1.5 dB Steps).

-48 dB, -54 dB

Analog Sidetone

-9 dB to -27 dB

Σ-∆

ADC

0dB to 42dB

(1.5 dB Steps).

48 dB, 54 dB

CODEC 1 (Channel 1)

Σ-∆

DAC

0dB to -42 dB

(1.5 dB Steps).

-48 dB, -54 dB

Σ-∆

ADC

0dB to 42dB

(1.5 dB Steps).

48 dB, 54 dB

CODEC 2 (Channel 2)

Analog Sidetone

-9 dB to -27 dB

1.35 V / 2.35

2 mA

SMARTDM

Serial Port

Internal Clock

Generator

Host Port

SPKO+

SPKO-

Speaker

8 Ω Output

LINE0+

LINEO-

Line Output

600 Ω

HNSO+

HNSO-

Handset

150 Ω Output

HNSI+

HNSI-

Handset

Input

HDSO+

HDSO-

Headset

150 Ω Output

HDSI+

HDSI-

Headset

Input

MICI+

MICI-

Microphone

Input

LINEI+

LINEI-

Line

Input

CIDI+

CIDI-

MICBIAS

LCDAC

MCLK FSD DOUT DIN SCLK FS M/S SDA SCL

Functional Block Diagram - AIC20/21/20K

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

11

www.ti.com

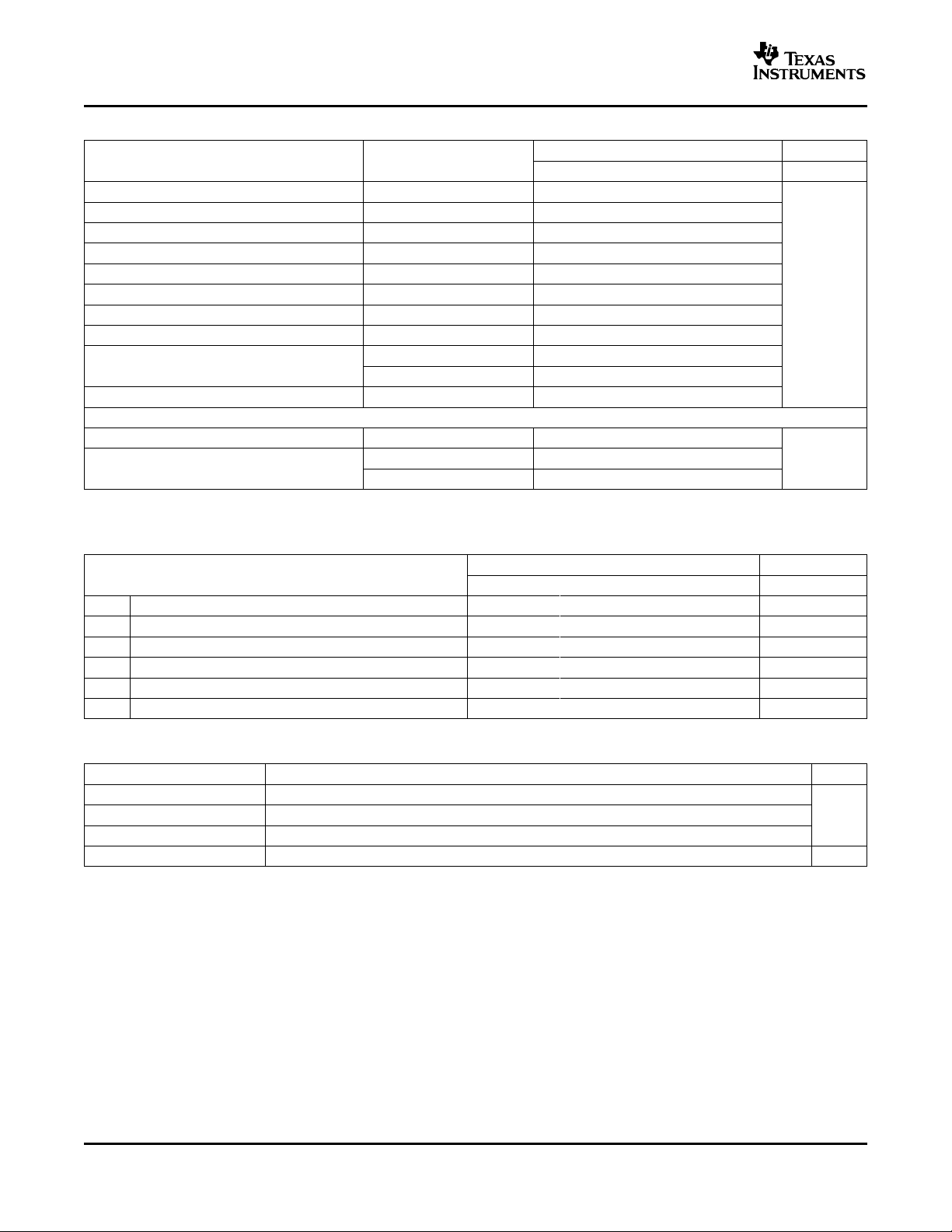

DAC

+

+

Σ−∆

DAC

0 dB to −42 dB

(1.5 dB Steps).

−48 dB, −54 dB

Analog Sidetone

−9 dB to −27 dB

Σ−∆

ADC

0 dB to 42 dB

(1.5 dB Steps).

48 dB, 54 dB

Σ−∆

DAC

0 dB to −42 dB

(1.5 dB Steps).

−48 dB, −54 dB

Σ−∆

ADC

0 dB to 42 dB

(1.5 dB Steps).

48 dB, 54 dB

Analog Sidetone

−9 dB to −27 dB

1.35 V / 2.35

2 mA

SMARTDM

Serial Port

Internal Clock

Generator

Host Port

OUTP1

OUTM1

Line Output

600 Ω

OUTP2

OUTM2

150 Ω Output

INP2

INM2

Input

OUTP3

OUTM3

150 Ω Output

INP3

INM3

Input

MICI+

MICI−

Microphone

Input

INP1

INM1

Input

INP4

INM4

MICBIAS

LCDAC

MCLK FSD DOUT DIN SCLK FS M/S SDA SCL

CODEC 1 (Channel 1)

CODEC 2 (Channel 2)

Input

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

Functional Block Diagram - AIC24/25/24K

12

www.ti.com

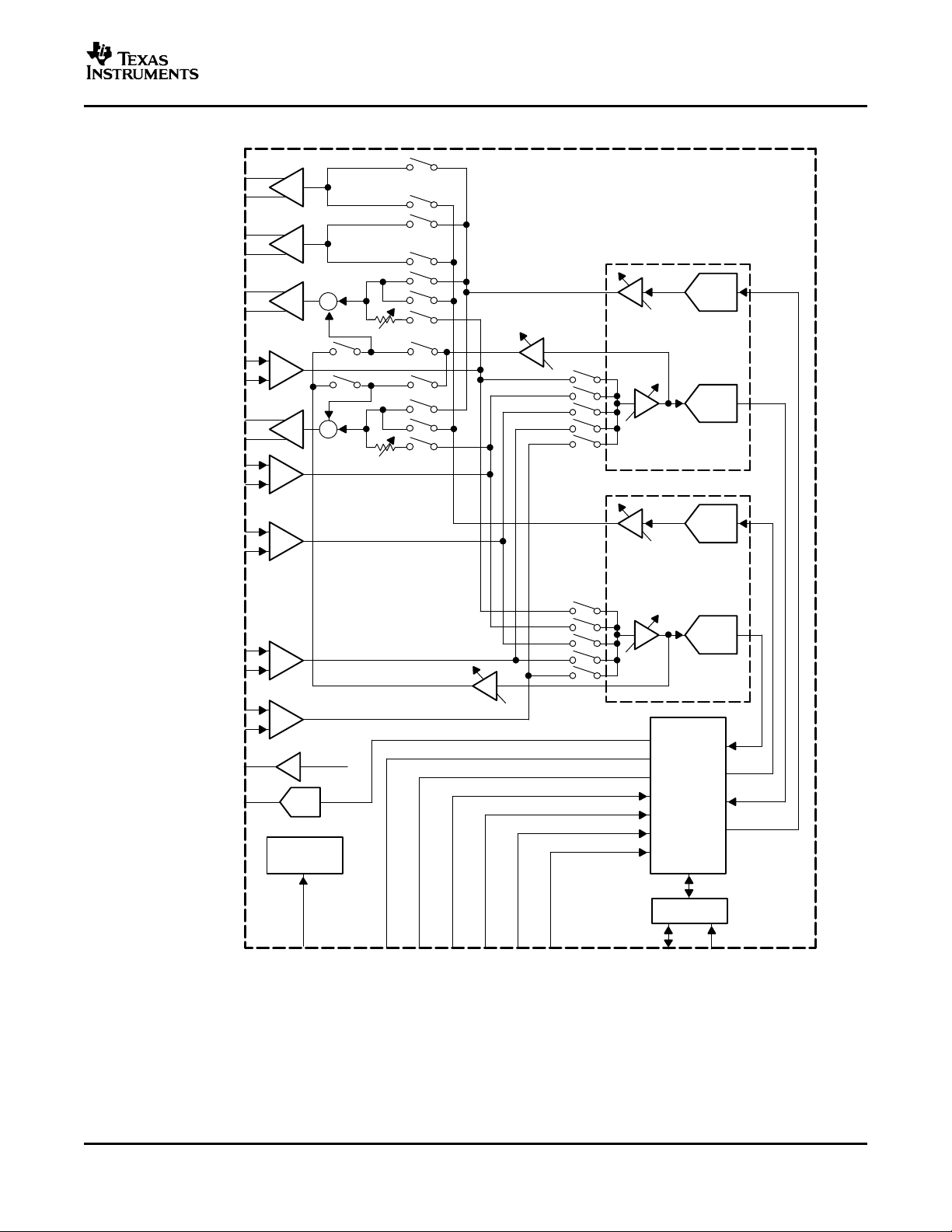

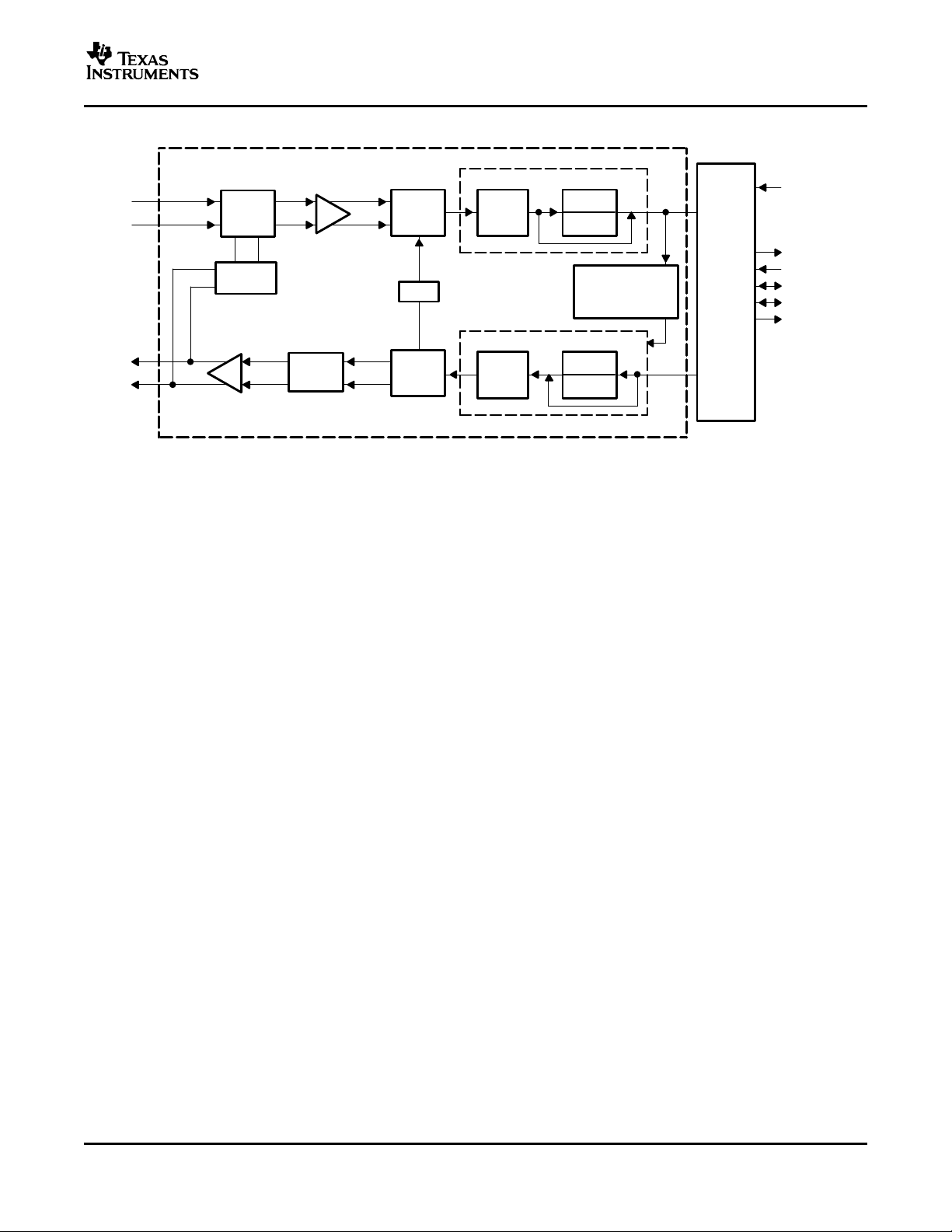

Analog

Loopback

PGA

Low Pass

Filter

Sigma-

Delta

DAC

Anti-

Aliasing

Filter

Sigma-

Delta

ADC

Sinc

Filter

FIR Filter

IIR Filter

Decimation Filter

Sinc

Filter

FIR Filter

IIR Filter

Interpolation Filter

Digital Loopback

w/ Sidetone Control

and Mute

M/S

DOUT

DIN

FS

SCLK

FSD

PGA

SMARTDM

-9 dB to -27 dB

Serial

Port

0 dB to 42 dB (1.5 dB Steps)

48 dB, 54 dB

V

ref

CODEC

0 dB to -42 dB (1.5 dB Steps)

-48 dB, -54 dB

Functional Block Diagram (One of Two Channels Shown)

Definitions and Terminology

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

Data Transfer The time during which data is transferred from DOUT and to DIN.

Interval The interval is 16 shift clocks, and the data transfer is initiated by

the falling edge of the FS signal.

Signal Data This refers to the input signal and all of the converted representations

through the ADC channel and the signal through the DAC channel to the

analog output. This is contrasted with the purely digital software control

data.

Frame Sync Frame sync refers only to the falling edge of the signal FS that initiates

the data transfer interval

Frame Sync and Sampling Period Frame sync and sampling period is the time between falling edges of

successive FS signals.

f

s

The sampling frequency

ADC Channel ADC channel refers to all signal processing circuits between the analog

input and the digital conversion result at DOUT.

DAC channel DAC channel refers to all signal processing circuits between the digital

data word applied to DIN and the differential output analog signal

available at OUTP and OUTM.

Dxx Bit position in the primary data word (xx is the bit number)

DSxx Bit position in the secondary data word (xx is the bit number)

d The alpha character d represents valid programmed or default data in the

control register format (see Section 3.2, Secondary Serial Communi-

PGA Programmable gain amplifier

IIR Infinite impulse response

FIR Finite impulse response

cation) when discussing other data bit portions of the register.

13

www.ti.com

t

h1

2.4 V

MCLK

RESET

2.4 V

t

su1

2.4 V

t

wL

t

wH

t

d1

t

d2

t

d1

t

d2

t

en

t

d3

t

dis

t

su2

t

h2

D15

D15

SCLK

FS

FSD

DOUT

DIN

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

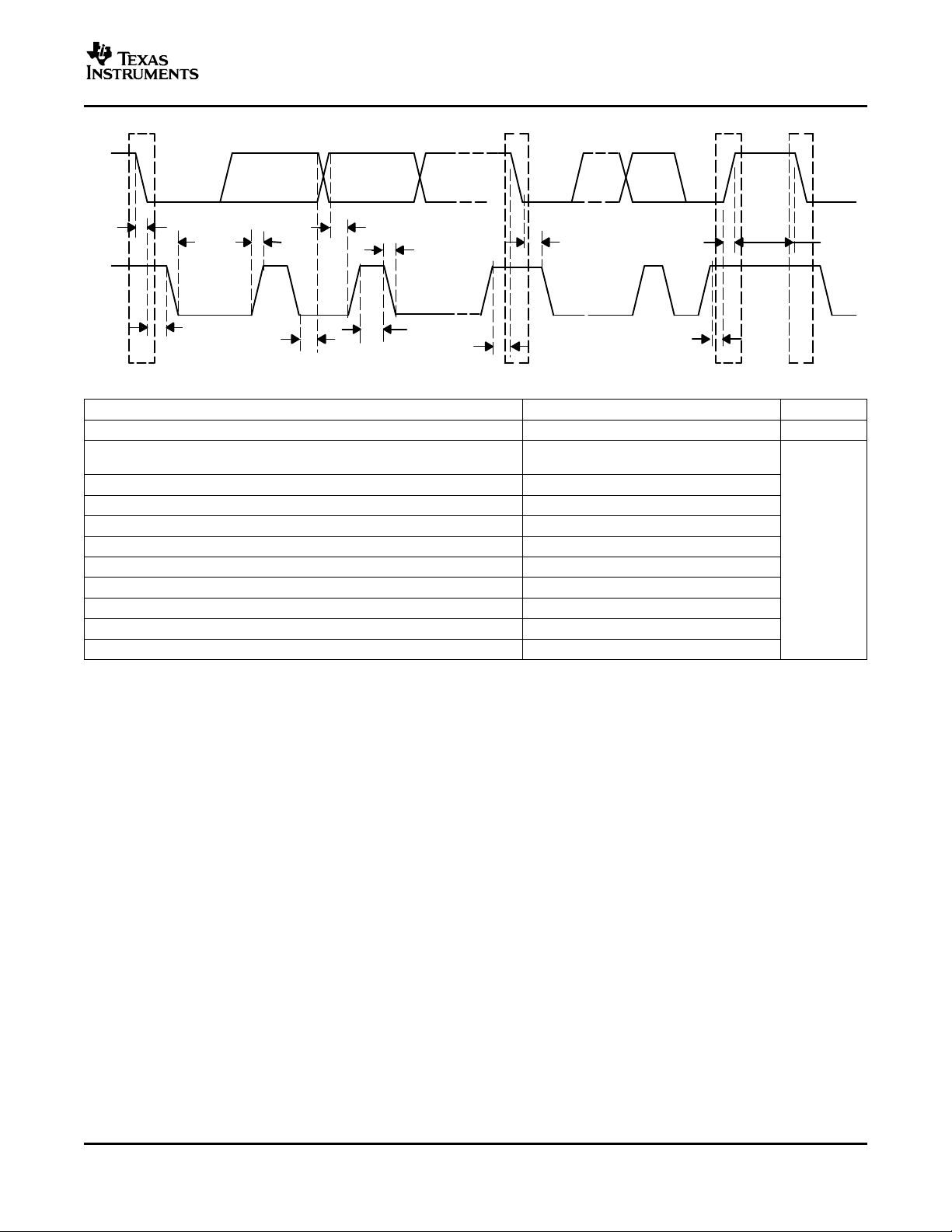

TIMING REQUIREMENTS

Figure 1. Hardware Reset Timing

Figure 2. Serial Communication Timing

TEST CONDITIONS MIN TYP MAX UNIT

t

wH

t

wL

t

su1

t

h1

t

d1

t

d2

t

d3

t

en

t

dis

t

su2

t

h2

14

Pulse duration, MCLK high 5

Pulse duration, MCLK low 5

Setup time, RESET, before MCLK high (see Figure 1 ) 3

Hold time, RESET, after MCLK high (see Figure 1 ) 2

Delay time, SCLK ↑ to FS/FSD ↓ CL= 20 pF 5 ns

Delay time, SCLK ↑ to FS/FSD ↑ 5

Delay time, SCLK ↑ to DOUT 15

Enable time, SCLK ↑ to DOUT 15

Disable time, SCLK ↑ to DOUT 15

Setup time, DIN, before SCLK ↓ 10

Hold time, DIN, after SCLK ↓ 10

www.ti.com

SDA

SCL

t

f

t

LOW

t

HD;STA

t

HD;DAT

t

HIGH

t

SU;STA

t

SU;STO

t

BUF

t

r

t

HD;STA

t

f

t

SU;DAT

t

r

Figure 3. I2C / S2C Timing Diagram

PARAMETER SYMBOL MIN MAX UNIT

SCL clock frequency t

Hold time (repeated START condition. After this period, the first clock pulse is t

generated.

Low period of the SCL clock t

High period of the SCL clock t

Set-up time for a repeated START condition t

Data hold time t

Data set-up time t

Rise time of both SDA and SCL signals t

Fall time of both SDA and SCL signals t

Set-up time for STOP condition t

Bus free time between a STOP and START condition t

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

SCL

HD;STA

LOW

HIGH

SU;STA

HD;DAT

SU;DAT

r

f

SU;STO

BUF

0 900 kHz

100

560

560

100

50

50

100

500

ns

300

100

15

www.ti.com

−140

−120

−100

−80

−60

−40

−20

0

0 500 1000 1500 2000 2500 3000 3500 4000

Amplitude − dB

f − Frequency − Hz

−140

−120

−100

−80

−60

−40

−20

0

0 500 1000 1500 2000 2500 3000 3500 4000

Amplitude − dB

f − Frequency − Hz

0 2000 4000 6000 8000 10000 12000 14000 16000 18000 20000

−140

−120

−100

−80

−60

−40

−20

0

Amplitude − dB

f − Frequency − Hz

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

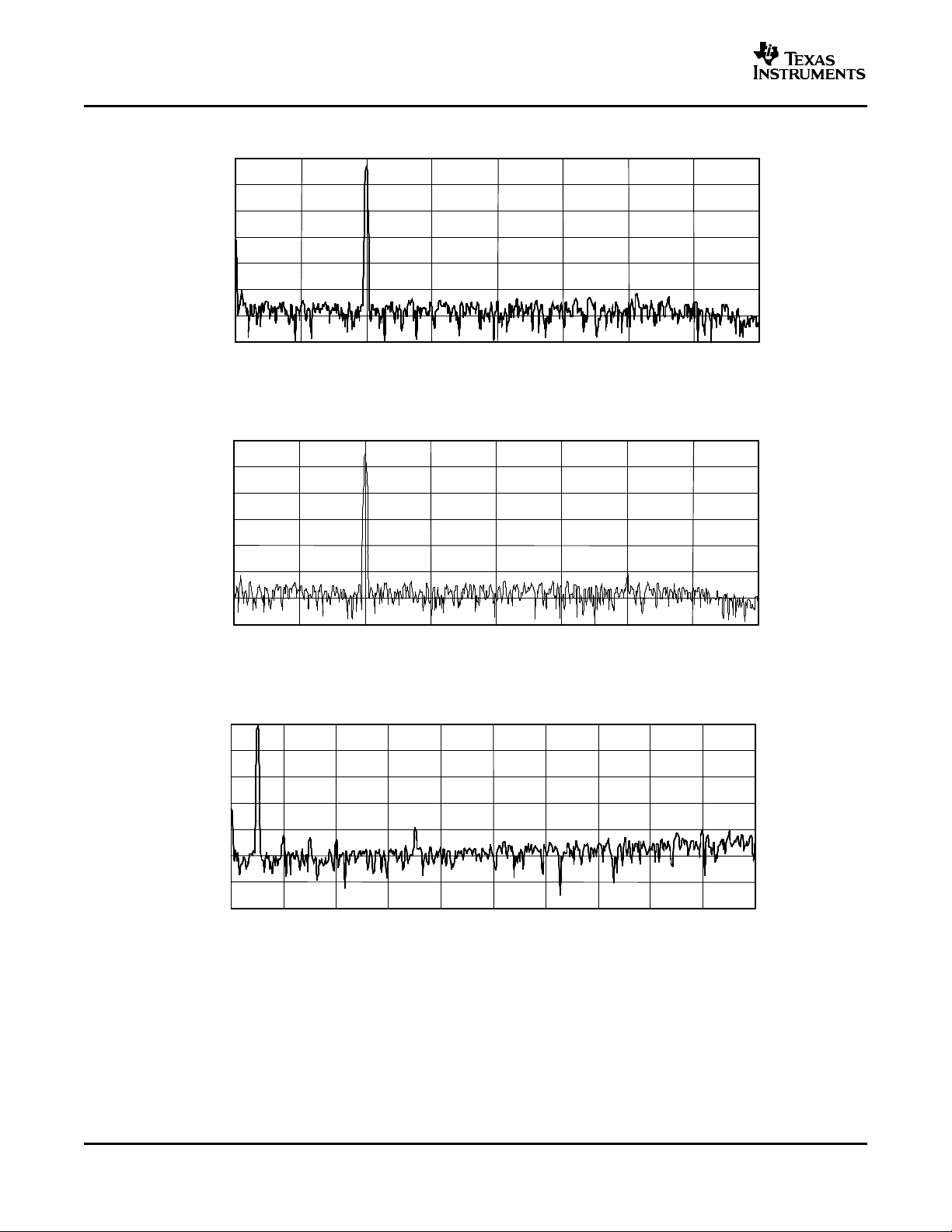

PARAMETER MEASUREMENT INFORMATION

Figure 4. FFT—ADC Channel (-3 dB input)

Figure 5. FFT—ADC Channel (-9 dB input)

Figure 6. FFT—DAC Channel (0 dB input)

16

www.ti.com

0 2000 4000 6000 8000 10000 12000 14000 16000 18000 20000

−140

−120

−100

−80

−60

−40

−20

0

Amplitude − dB

f − Frequency − Hz

0 2000 4000 6000 8000 10000 12000 14000 16000

−140

−120

−100

−80

−60

−40

−20

0

Amplitude − dB

f − Frequency − Hz

0 2000 4000 6000 8000 10000 12000 14000 16000 18000 20000

−140

−120

−100

−80

−60

−40

−20

0

Amplitude − dB

f − Frequency − Hz

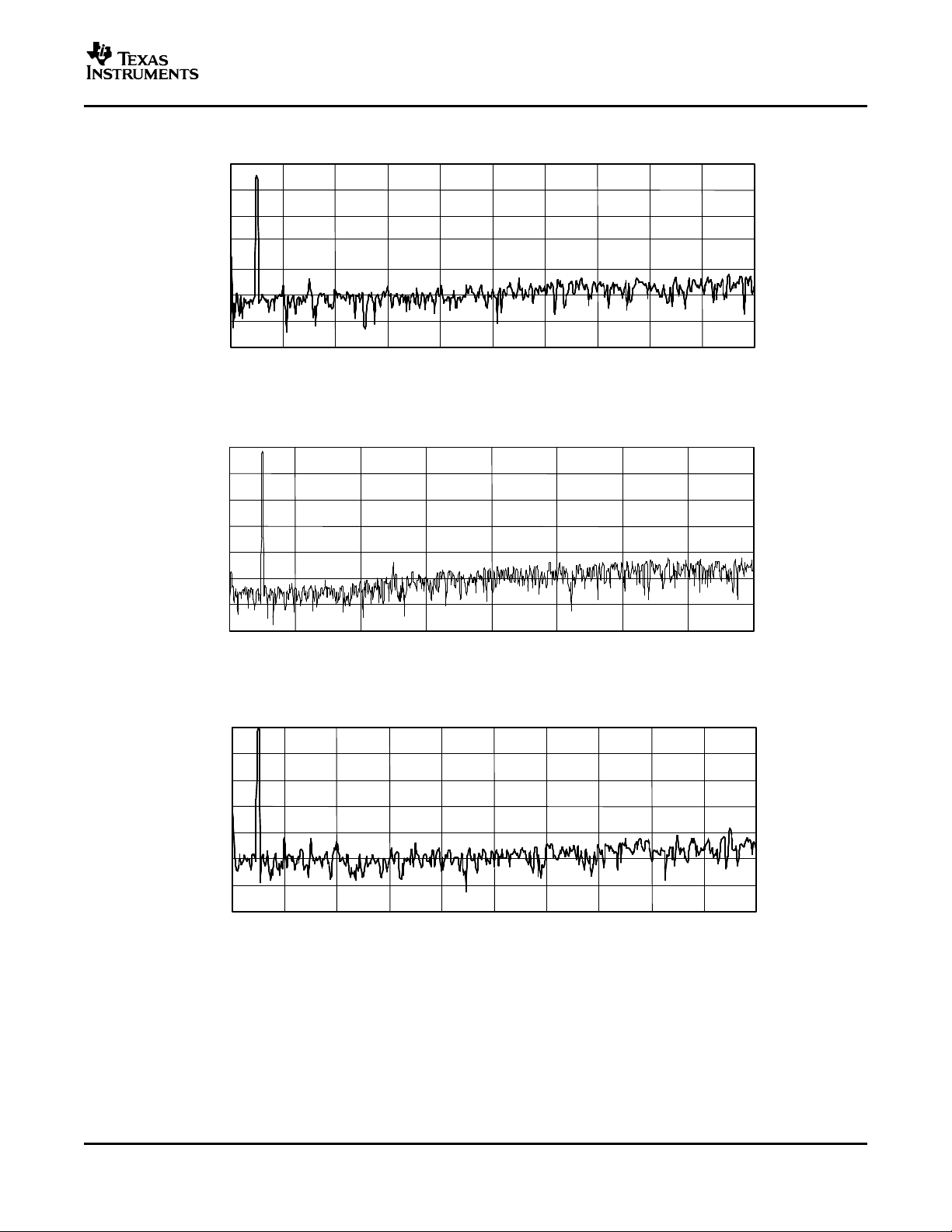

PARAMETER MEASUREMENT INFORMATION (continued)

Figure 7. FFT—DAC Channel (-9 dB input)

TLV320AIC20, TLV320AIC21

TLV320AIC24, TLV320AIC25

TLV320AIC20K, TLV320AIC24K

SLAS363D – MARCH 2002 – REVISED APRIL 2005

Figure 8. FFT—ADC Channel in FIR/IIR Bypass Mode (-3 dB input)

Figure 9. FFT—DAC Channel in FIR/IIR Bypass Mode (0 dB input)

17

Loading...

Loading...