TLV320AD11A

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

D

Complete Discrete Multitone (DMT)-Based

Asymmetric Digital Subscriber Line (ADSL)

Coder/Decoder (CODEC) Solution

D

Complies With ANSI T1.413 Issue II and ITU

G.992.1

D

Supports up to 8 MBPS Downstream and

800 KBPS Upstream Duplex

D

Integrated 14-Bit Converters for

Transmitter/Echo-Canceller/Receiver

(TX/EC/RX)

D

Integrated 12-Bit DAC for VCXO Control

D

Integrated TX/EC/RX Channel Filters

D

Integrated TX/EC/RX Attenuation/Gain

description

The TL V320AD1 1A is a high-speed codec for remote terminal-side (RT) modems that support the ANSI T1.413

[Issue 2 discrete multi-tone (DMT) asymmetric digital subscriber line (ADSL) access] and ITU G.992.1

standards. It is a low-power device that includes five major functional blocks: transmitter, receiver, clock,

reference, and host interface. It is designed to work with the T exas Instruments TL V320AD12 central office-side

(CO) codec.

D

Integrated Voltage Reference

D

High-Speed Parallel Interface

D

16-bit 2s Complement Data Format

D

Selectable 2.2 MSPS or 4.4 MSPS Parallel

Data Transfer Rate

D

Serial Configuration Port

D

Eight General-Purpose Output Pins

D

Single 3.3-V Supply

D

Hardware/Software Power Down

D

100-Pin PQFP (PZ) Package

D

–40°C to 85°C Operation

The device’s transmit channel consists of the following functional blocks: 138 kHz digital low-pass filter,

bypassable 25.875 kHz digital high-pass filter, 14-bit high speed DAC, 138 kHz analog low-pass filter , transmit

attenuator, and an echo cancellation channel. The receiver channel consists of two programmable-gain

amplifiers, a frequency equalizer, a 1.104-MHz low-pass analog filter, a 14-bit high speed ADC, and a

1.104-MHz low-pass digital filter. The clock circuit divides a 35.328-MHz frequency from an external VCXO

down to the necessary frequencies used throughout the device. The frequency of the external VCXO is

controlled by a 12-bit onboard voltage output DAC. An onboard reference circuit generates a 1.5-V reference for

the converters.

The device has a parallel port for data transfer and a serial port for control. The parallel port is 16 bits wide and is

reserved for moving data between the codec and a DSP such as the Texas Instruments TMS320C6XX.

Configuration is done via a serial port. The device can be powered down via a dedicated pin, or through software

control, to reduce heat dissipation. Additionally , there is a general-purpose (GP) port consisting of eight output

terminals for control of external circuitry.

The TL V320AD1 1A codec is available in a 100-pin PZ PQFP package and is characterized for operation in the

temperature range of –40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 2000, Texas Instruments Incorporated

1

TLV320AD11A

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

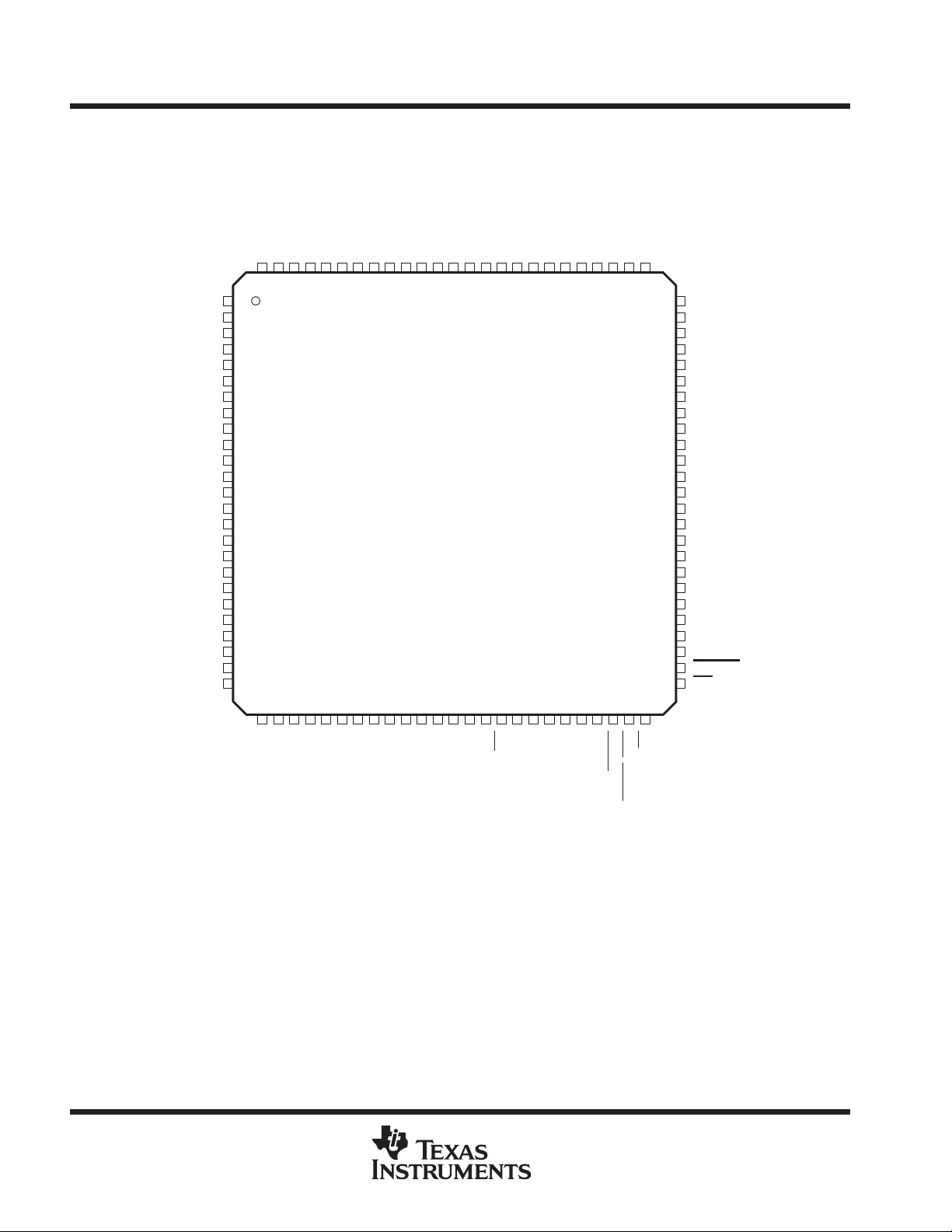

PZ PACKAGE

(TOP VIEW)

SS

NC

AVDD_FIL_RXVREFM

93

92

91

VMID_REF

89

90

TL V320AD11A

37

36

35

34

33

GP0

GP1

GP2

GP3

GP4

GP5

GP6

GP7

DVSS

NC

VMID_ADC

A VDD_ADC

A VSS_ADC

NC

DVDD_RX

DVSS_RX

D0

D1

D2

D3

D4

D5

D6

D7

D8

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

CONFIG2

OE_SYNC

ONE_WE

NC

97

98

99

100

29

28

27

26

RXM

RXP

AVSS_FIL_RX

94

95

96

32

31

30

REFPNCAVSS_FIL_TX

A VSS_REF

A VDD_REF

86

87

88

40

38

39

AVDD_FIL_TX

83

84

85

43

42

41

TXM

TXPNCECM

80

81

82

46

45

44

ECPNCNC

78

79

48

47

77

49

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

NC

NC

A VDD_FIL_EC

A VSS_FIL_EC

A VSS2_TX

A VDD2_TX

COMPB_TX

COMPA_TX

A VSS1_TX

A VDD1_TX

A VSS2_EC

A VDD2_EC

COMPA_EC

COMPB_EC

A VSS1_EC

A VDD1_EC

VCXOCNTL

DVSS

DVDD_DAC

DVSS_DAC

ADR1

ADR0

PWDN

RESET

CS

D9

D11

D10

DVSS_BF

DVDD_BF

NC – No connection (leave open)

2

D14

D12

D13

D15

SDO

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

FS

SDI

OSEN

SCLK/READY

INT

CLKIN

DVSS_CLK

CLKOUT/INT

SYNC

DVSS_LG

DVDD_CLK

DVDD_LG

OE

WETX

WEEC/CS2

3.3 V INTEGRATED ADSL OVER POTS CODEC

I/O

DESCRIPTION

SLWS087B – JUNE 1999 – REVISED MARCH 2000

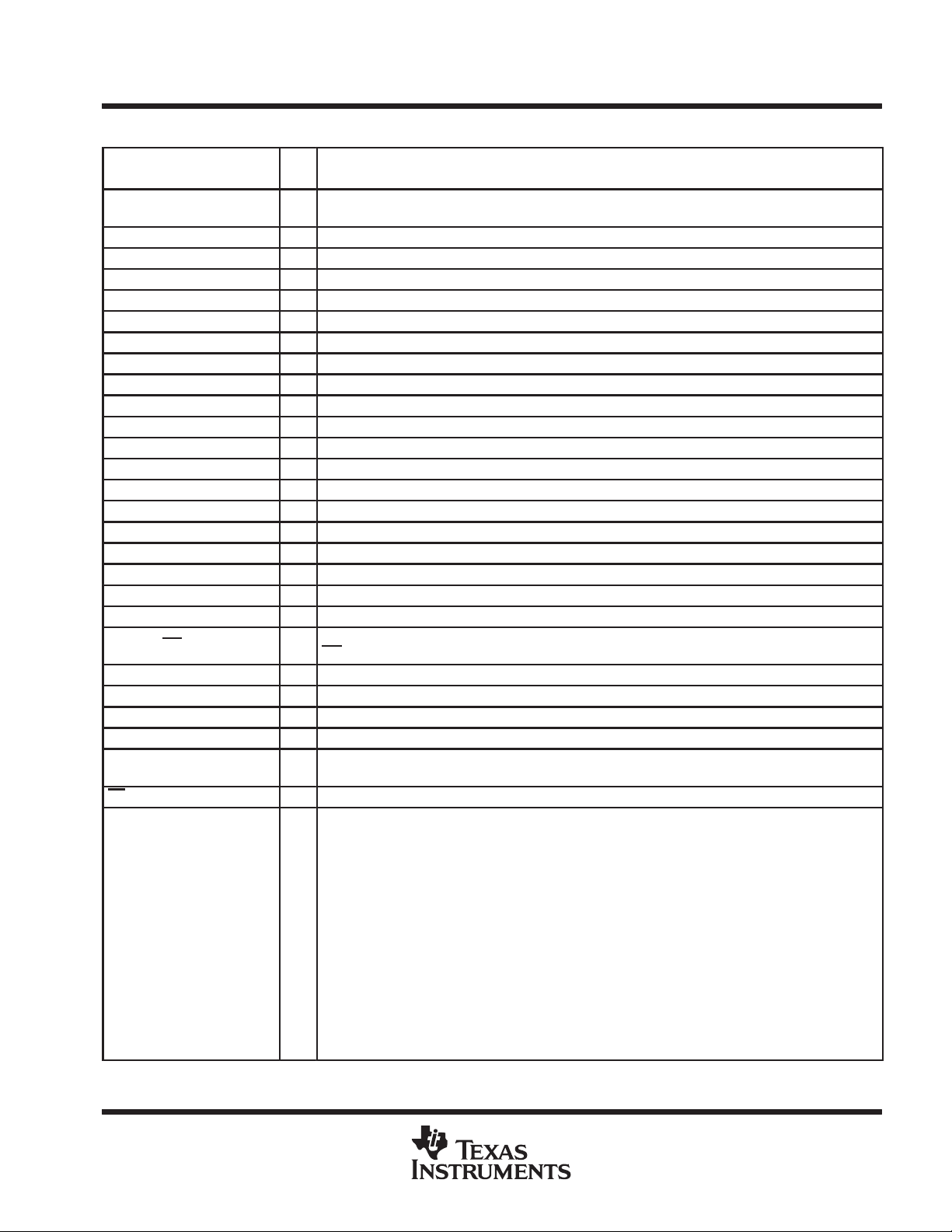

Terminal Functions

TERMINAL

NAME NO.

ADR0

ADR1

AVDD1_EC 60 I EC channel analog power supply #1

AVDD2_EC 64 I EC channel analog power supply #2

AVDD1_TX 66 I TX channel analog power supply #1

AVDD2_TX 70 I TX channel analog power supply #2

AVDD_ADC 12 I Receive channel analog power supply

AVDD_FIL_EC 73 I EC channel filter analog power supply

AVDD_FIL_RX 93 I Receive channel filter analog power supply

AVDD_FIL_TX 83 I Transmit channel filter analog power supply

AVDD_REF 86 I Reference analog power supply

AVSS1_EC 61 I EC channel analog ground # 1

AVSS2_EC 65 I EC channel analog ground #2

AVSS1_TX 67 I TX channel analog ground #1

AVSS2_TX 71 I TX channel analog ground #2

AVSS_ADC 13 I Receive channel analog ground

AVSS_FIL_EC 72 I EC channel filter analog ground

AVSS_FIL_RX 94 I Receive channel filter analog ground

AVSS_FIL_TX 84 I Transmit channel filter analog ground

AVSS_REF 87 I Reference analog ground

CLKIN 42 I 35.328 MHz VCXO clock input

CLKOUT/INT 41 O

COMPA_EC 63 O EC channel cap input A. Add 500 pF X7R ceramic capacitor to AVDD1_EC.

COMPB_EC 62 O EC channel cap input B. Add 1 µF X7R ceramic capacitor to AVDD1_EC.

COMPA_TX 68 O TX channel decoupling cap input A. Add 500 pF ceramic capacitor to AVDD1_TX.

COMPB_TX 69 O TX channel decoupling cap input B. Add 1 µF ceramic capacitor to AVDD1_TX.

CONFIG2 100 I

CS 51 I Parallel port chip select

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

54

55

34 (MSB)

33

32

31

30

29

28

25

24

23

22

21

20

19

18

17 (LSB)

I Serial port chip ID address bits, ADR0 is the least significant bit.

If CONFIG2 (pin 100) is low, this pin is 4.416 MHz clock output. If CONFIG2 is high, this pin functions as

.

INT

I/O configuration input pin. A high on this pin redefines the function of pins 37 and 41. The default state of

this pin is low. Refer to Figure 3 for details.

I/O Parallel port data bits D0=LSB

TLV320AD11A

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

3

TLV320AD11A

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

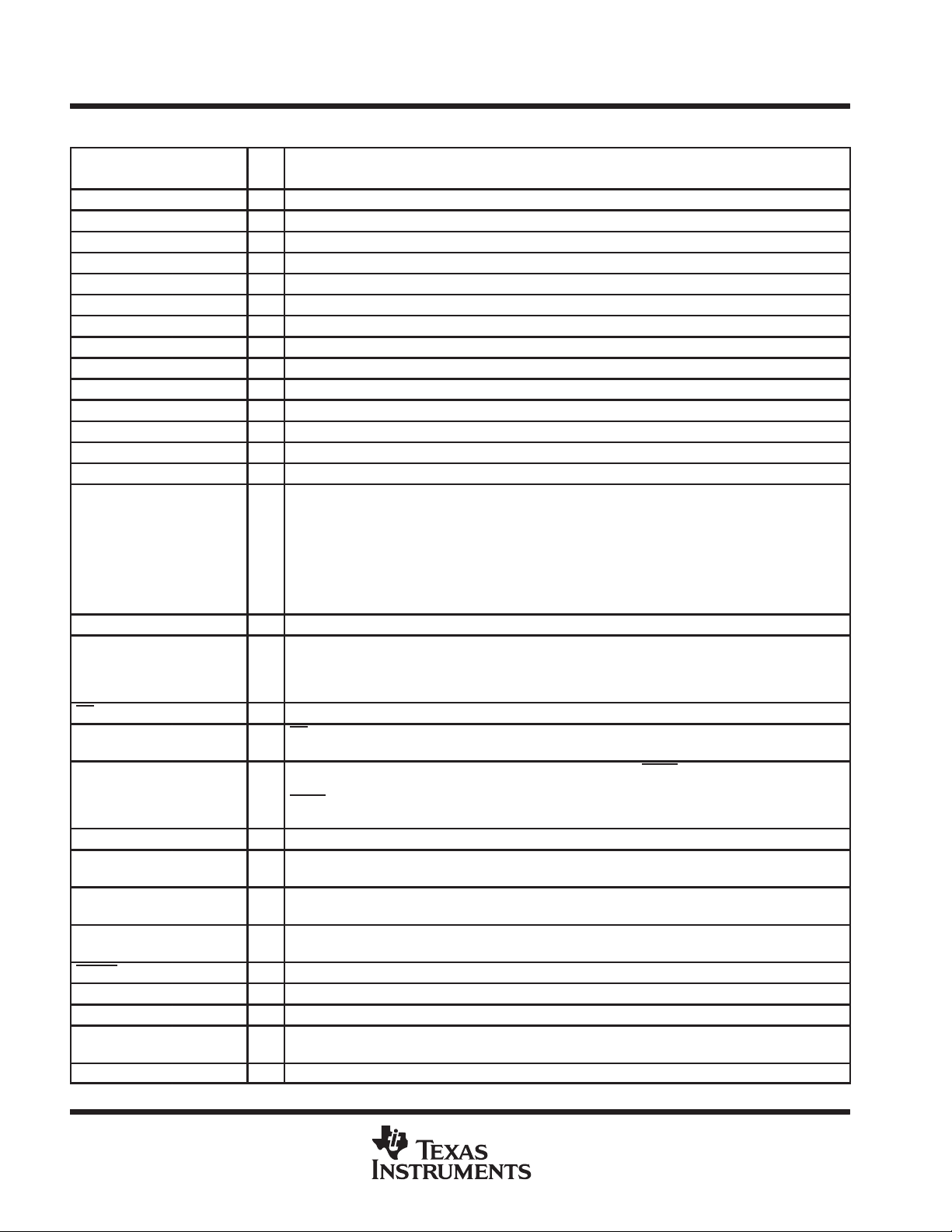

Terminal Functions(Continued)

TERMINAL

NAME NO.

DVDD_BF 26 I Digital I/O buffer supply

DVDD_CLK 44 I Digital clock supply

DVDD_LG 47 I Digital logic supply

DVDD_RX 15 I Receive channel digital power supply

DVDD_DAC 57 I Digital power supply for DAC

DVSS 9, 58 I Digital ground

DVSS_BF 27 I Digital I/O buffer ground

DVSS_CLK 43 I Digital clock ground

DVSS_LG 46 I Digital logic ground

DVSS_RX 16 I Receive channel ground

DVSS_DAC 56 I DAC ground

ECM 79 O EC output minus

ECP 78 O EC output plus

FS 38 I Frame sync input

GP7

GP6

GP5

GP4

GP3

GP2

GP1

GP0

INT 40 O Data rate clock (INT is 4.4 MHz when OSEN=1, 2.2 MHz when OSEN=0)

NC 10, 14, 74,

OE 50 I Parallel port output enable from host processor

OE_SYNC 99 I OE synchronized input. A high input will optimize the read operation from keep-out zone. The default

ONE_WE 98 I TX and EC write combined input. A high on this pin allows pin 48, WETX, to be used to write to both the

OSEN 39 I Over-sampling enable input. OSEN=1 enables over-sampling mode (INT = 4.4 MHz).

PWDN 53 I Power-down input. When PWDN=0, device is in normal operating mode. When PWDN=1, device is in

REFM 89 O Decoupling reference REF voltage minus. Add 10 µF tantalum and 0.1 µF ceramic capacitors to

REFP 88 O Decoupling reference REF voltage plus. Add 10 µF tantalum and 0.1 µF ceramic capacitors to

RESET 52 I H/W system reset. An low level will reset the device.

RXM 96 I Receive RX input minus. RXM is self-biased to AVDD_FIL_RX/2.

RXP 95 I Receive RX input plus. RXP is self-biased to AVDD_FIL_RX/2.

SCLK/READY 37 O If CONFIG2 (pin 100) is low, this pin is serial clock output. If CONFIG2 is high, it indicates the period in

SDI 36 I Serial data input

8

7

6

5

4

3

2

1

75, 76, 77,

80, 85, 91,

97

I/O DESCRIPTION

O General-purpose output port

No connection. All the NC pins should be left open.

state of this pin is low. See Figure 5 for details.

EC and TX channels. In this case, after a hardware reset or write to SCR14[0], the first low-going pulse of

will be a write to TX channel and the second one will be a write to EC channel. The default state of

WETX

this pin is low.

power-down mode.

AVSS_REFP. The nominal dc voltage at this terminal is 0.5 V . See figure 9 for detail.

AVSS_REFM. The nominal dc voltage at this terminal is 2.5 V.. See figure 9 for detail.

which parallel data can be transferred.

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV320AD11A

I/O

DESCRIPTION

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

Terminal Functions(Continued)

TERMINAL

NAME NO.

SDO 35 O Serial data output

SYNC 45 I SYNC pulse for clock synchronization. A high pulse to the pin synchronizes the clock operation. The

TXM 82 O Transmit output minus

TXP 81 O Transmit output plus

VCXOCNTL 59 O VCXO DAC output

VMID_ADC 11 O Decoupling 1.5 V for ADC. Add 10 µF tantalum and 0.1 µF ceramic capacitors to AVSS_ADC.

VMID_REF 90 O Decoupling 1.5 V reference voltage. Add 10 µF tantalum and 0.1 µF ceramic capacitors to A VSS_REF.

V

SS

92 I Substrate. VSS needs to connect to analog ground.

WEEC/CS2 49 I Write enable to EC channel from host processor, when ONE_WE (pin 98) is low . If ONE_WE is high, it

WETX 48 I Write enable for TX channel from host processor. If ONE_WE is high, it functions as write enable for both

default state of the pin is low. Refer to Figure 4 for detail.

functions as second chip select, CS2

, and both CS and CS2 need to be low in order to have WETX

access data on the parallel bus.

TX and EC after hardware reset or write to SCR14[0]. In this case, the first low-going pulse of WETX

be a write to TX channel, and the second one will be a write to EC channel

will

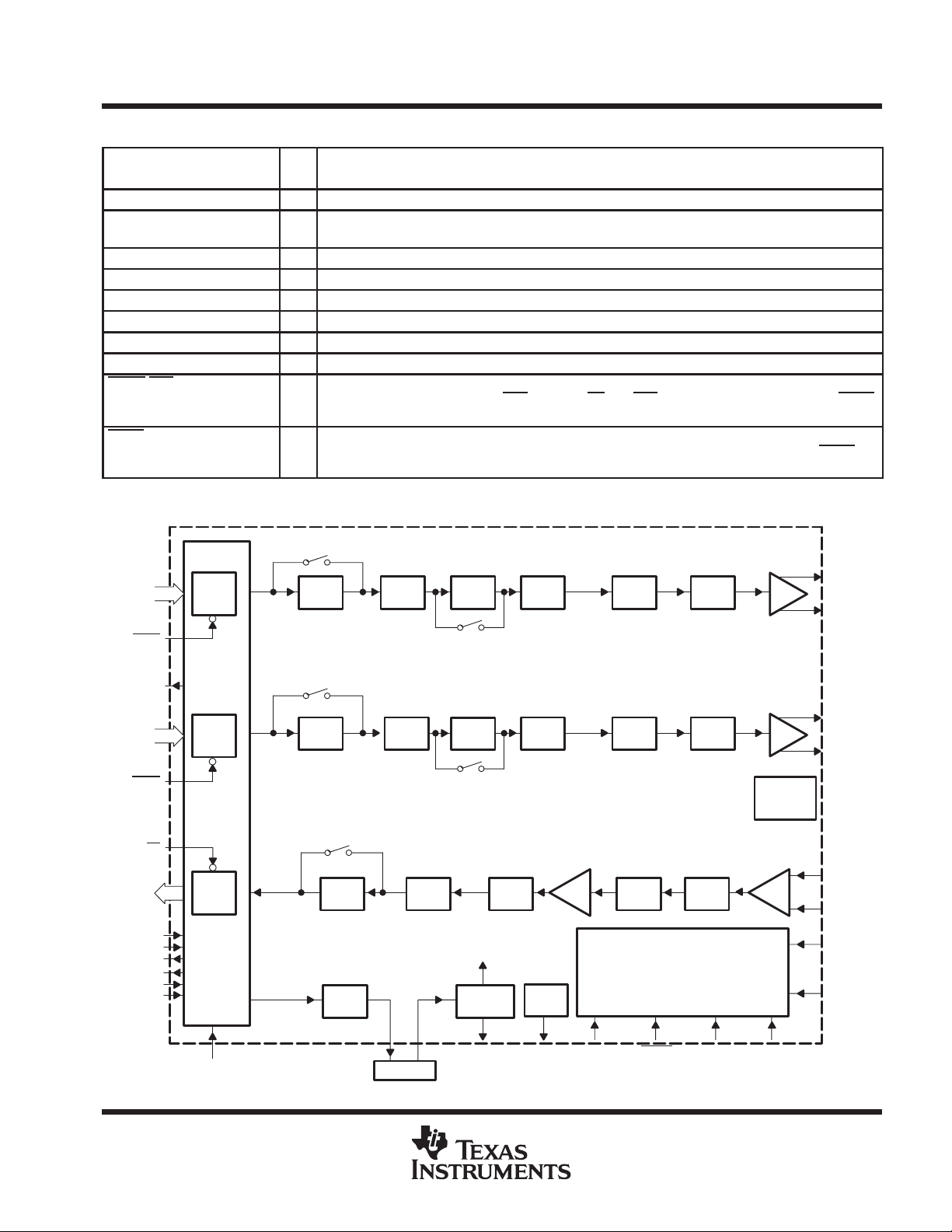

functional block diagram

D0–D15

WETX

D0–D15

WEEC

D0–D15

SCLK

ADR1

ADR0

INT

OE

SDI

SDO

FS

Input

Buffer

Parallel

Bus

Input

Buffer

CODEC

Interface

Output

Buffer

Serial

Interface

276 KSPS

276 KSPS

2208

KSPS

OSEN

INTRP

2×

OSEN

INTRP

2×

OSEN

DEC/2

VCXO

DAC

552

KSPS

552

KSPS

138 kHz

4416

KSPS

Digital

LPF

138 kHz

Digital

LPF

1.104 MHz

Digital

LPF

25.875 kHz

Digital

HPF

SCR7[0]

25.875 kHz

Digital

HPF

SCR14[2]

4416

KSPS

Clock

Generator

14 Bit

4.416 MSPS

RX

ADC

INTRP

8×

INTRP

8×

(0.25 dB/step)

4V

PP

GP0–7

4416

KSPS

4416

KSPS

0 to 11.5 dB

PGA2

4.416 MSPS

4.416 MSPS

1.104 MHz

3V

PP

14 Bit

TX

DAC

14 Bit

EC

DAC

RX

LPF

138 kHz

LPF

138 kHz

LPF

(25 dB Boost

5 dB/step)

RX

EQ

Control Block

TX

EC

0 to –24 dB

(–1 dB/step)

TX PAA

PAA

0 to –24 dB

(–1 dB/step)

EC PAA

PAA

Internal

Reference

0 to 6 dB

(1 dB/step)

PGA1

TXP

TXM

ECP

ECM

RXP

RXM

OE_SYNC

ONE_WE

OSEN

VCXOCNTL CLKIN

VCXO

35.328 MHz

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

CLKOUT

4.416 MHz

GP0–GP7

SYNC

RESET

PWDN CONFIG2

5

TLV320AD11A

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

PRINCIPLES OF OPERATION

communication channels

transmitter channel/echo-cancellation channel

The transmitter channel is powered by a high performance DAC. This is a 4.416-MHz, 14-bit DAC that provides a

16X over-sampling to reduce DAC noise. The input buffer is sampled at either 276 KSPS (pin OSEN = low,

default), or 552 KSPS (pin OSEN = high). A low-pass filter limits its output to 138 kHz. A programmable

attenuator, with a range between 0 and –24 dB in –1-dB steps, drives the output into the external ADSL line

driver.

A second transmitter is used to perform pre-echo cancellation. This analog echo cancellation helps reduce the

dynamic range requirements of the RT receiver . It has the same function as the first transmitter channel. It drives

a separate external line driver to perform the cancellation.

receiver channel

The receiver channel has two PGAs and an equalizer to match the loop loss and flatten the spectrum. This

results in a reduction in dynamic range requirement for the high resolution ADC. The receiver channel also has a

1.104-MHz low-pass filter with a 4.416 MSPS and a 14-bit ADC to provide a 2X over-sampling. The output buffer

is updated at either 2208 KSPS (pin OSEN = low, default), or 4416 KSPS (pin OSEN = high).

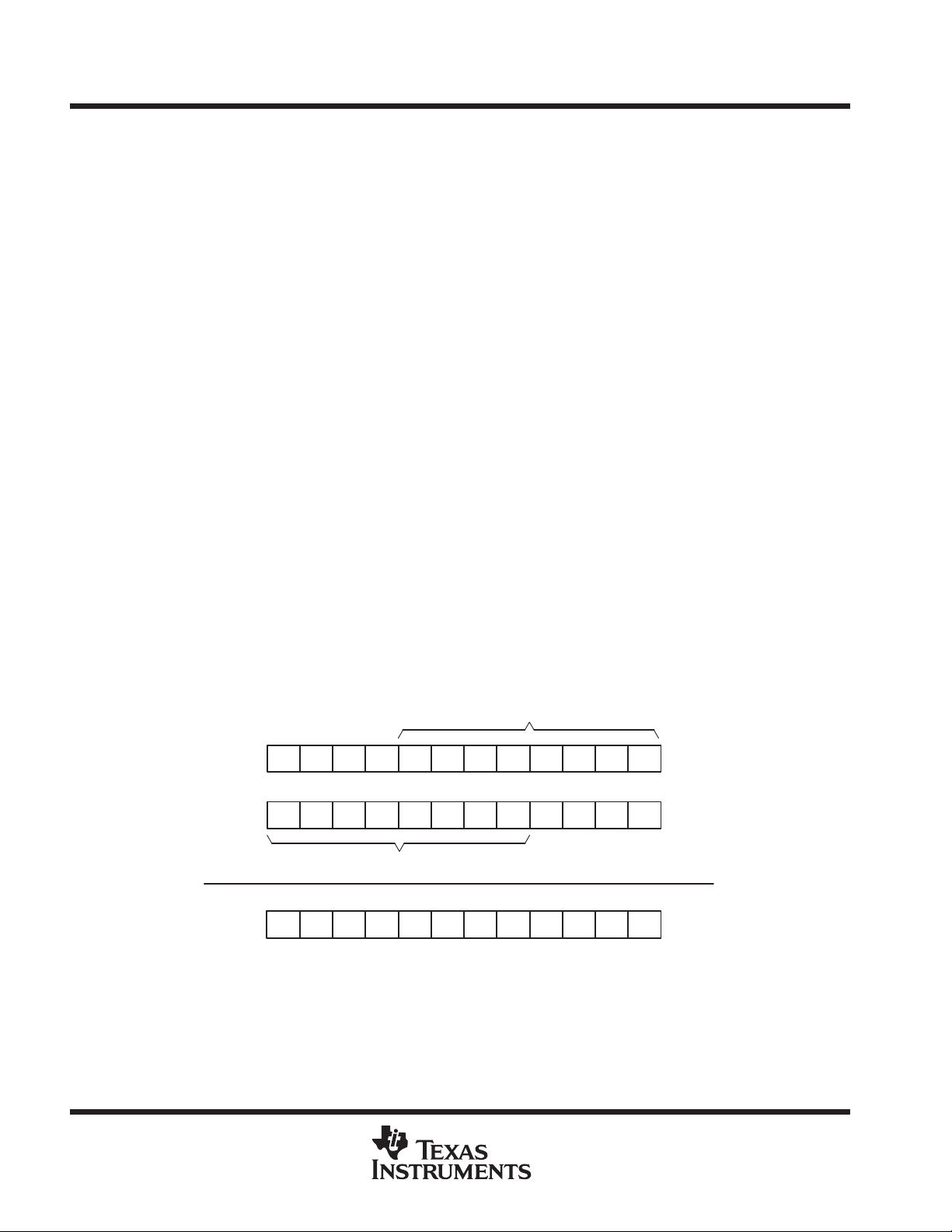

VCXO-control DAC

A 12-bit DAC is used to control the external 35.328-MHz VCXO (voltage control oscillator) that provides the

system clock to the codec. In a typical application, the typical update rate of the DAC is about 4 kHz, depending

on the ADSL frame rate. The host DSP initiates the update through the serial interface. The two 8-bit registers

SCR4 and SCR5 (each 2s complement) are used to generate the 12-bit code for the DAC. This requires the

use of 16 bits to obtain a 12-bit number. So the lower 4 bits of the MSB register (SCR5[3:0]) are added (2s

complement) to the higher 4 bits of the LSB register (SCR4[7:4]). Refer to Figure 1 for code generation. The

updated code is sent to the DAC two SCLKs after the SCR4 register is received. Notice that if SCR5 does not

need to be updated, only one write cycle to SCR4 is needed to update the VCXO DAC. In this case, the lower

8 bits of the 12-bit word will be updated.

SCR4

D7

D7 D7 D7 D7 D6 D5 D4 D3 D2 D1 D0

D7 D6 D5 D4 D3 D2 D1 D0 0 0 0 0

+

D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

SCR5

12-bit code for VCXO DAC

Figure 1. 12-Bit Code Generation for VCXO DAC

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV320AD11A

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

PRINCIPLES OF OPERATION

communication channels (continued)

clock generation

The clock generation block provides the necessary clock signals for the device, with minimum skew and jitter.

This is closely dependent on the performance of the external VCXO. The external VCXO specifications are:

D

3.3 V supply

D

35.328 MHz ± 50 PPM

D

Minimum duty cycle is 60/40 (50/50 is optimum)

The major clocks generated internally are shown in Table 1.

Table 1. Clock Description

FREQUENCY

CLOCK

INT 2.208 4.416

CLKOUT 4.416 4.416

SCLK 4.416 4.416

(MHz)

OSEN=0 OSEN=1

INT

The interrupt (INT) to the host processor is 4.416 MHz when OSEN = 1 and 2.208 MHz when OSEN = 0.

SCLK

The serial clock used in the serial codec interface has a fixed frequency of 4.416 MHz and is synchronous with

the master clock (35.328 MHz).

CLKOUT

CLKOUT is a 4.416-MHz clock output, and is synchronous with the master clock (35.328 MHz).

interface

parallel interface

The device has a 16-bit parallel interface for transmitter and receiver data. Strobes OE, WETX, and CS from

the host DSP are edge-triggered signals. An incoming signal is registered on the rising edge of WETX/WEEC.

When ONE_WE is enabled, only WETX

channel write operation. After D0 of register SCR14 is programmed, the data from the first pulse of WETX goes

to the transmit channel, while the data from the second pulse of WETX goes to the echo-cancellation channel.

Output data from the codec is enabled after the falling edge of the OE strobe, and disabled after the rising edge

of the OE strobe. The INT cycle time is hardware-configurable to 4.416 MHz (2X over-sampling mode,

OSEN=1), or to 2.208 MHz (1X over-sampling mode, OSEN=0). SYNC is used to synchronize the operation

between the codec and the host transceiver. SCLK/READY is used to indicate the parallel data transfer period

in configuration mode 2. See Figure 3 for details.

is needed for both the transmit channel and the echo-cancellation

OE_SYNC is used to synchronize the codec timing to OE

. See Figure 5 for details.

For the 16-bit parallel data, D0 is the LSB and D15 is the MSB. The parallel TX and RX data contains 16 valid

bits. All 16 bits are used in the digital filtering.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

7

TLV320AD11A

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

PRINCIPLES OF OPERATION

interface (continued)

keep-out zones

The last CLKIN cycle before a transition of CLKOUT is defined as a keep-out zone. These zones are reserved

for the sampling of analog signals. All digital I/O (except for CLKIN) should be quiet during these keep-out zones.

over-sampling mode

The OSEN pin selects 2X over-sampling mode (INT running at 4.416 MHz), or 1X over-sampling mode (INT

running at 2.208 MHz).

serial interface

The serial port is used for codec configuration and register reading. The word length is 16-bit. Two hardware

configuration terminals, ADR[1:0], are used to configure the device ID. Up to four codecs can be identified for

each common serial port. Refer to figure 6 for timing and format.

The master codec (ADR[1:0] = [0,0]) provides the SCLK to the host processor. The SCLK terminals on the other

codecs are left unconnected. All the codecs in a multi-codec system should be synchronized so that their SCLK

signals are in phase, even though the signals themselves are not being used. This ensures that, even though

the individual SCLK signals of each codec are not being used, the data is being latched into the codec properly .

The SCLK is a continuously running 4.416-MHz fixed-frequency clock, synchronized to the codec internal

events and CLKOUT (to the host) so that the keep-out zones may be monitored. A host DSP can drive the FS

(synchronized to the CLKOUT from the codec) into the codec to initiate a 16-bit serial I/O frame.

If SCR5 needs to be updated, the host controller (DSP) must first write the SCR5 of the VCXO DAC data, and

then the SCR4 of the VCXO DAC data. The VCXO DAC only gets updated after the SCR4 is written.

GP port

The general-purpose port provides eight outputs, each capable of delivering 0.5 mA, for control of external

circuitry such as LEDs, gain control, and power down.

voltage reference

The built-in reference provides the required reference voltage and current to individual analog blocks. It is also

brought out to external terminals for noise decoupling.

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TLV320AD11A

DEFAULT

SCR0

0000

3.3 V INTEGRATED ADSL OVER POTS CODEC

SLWS087B – JUNE 1999 – REVISED MARCH 2000

PRINCIPLES OF OPERATION

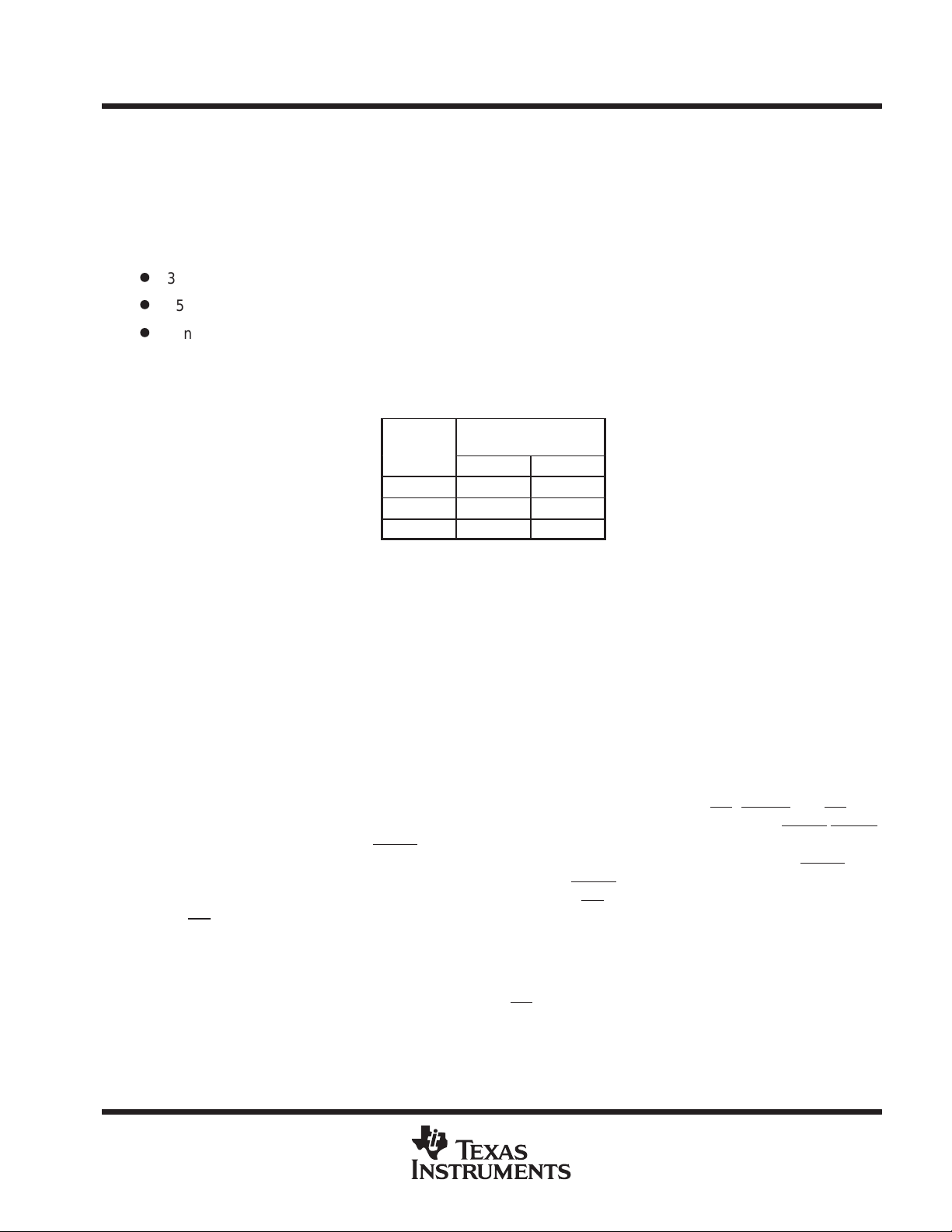

register programming (see Figure 6 for timing and format details)

Table 2. System Control Registers (SCR)

REGISTER

NAME

SCR1 0001 R/W 00000000

SCR2 0010 R/W 00000000 D[5:0]=RX PGA2. D[5:0]=000000 for 0 dB. D[5:0]=101110 for 11.5 dB.

SCR3 0011 R/W 00000000

SCR4 0100 R/W 00000000 D[7:0]=VCXODAC (low 8 bits of 12-bit DAC code)

SCR5 0101 R/W 00000000 D[7:0]=VCXODAC (high 8 bits of 12-bit DAC code)

SCR6 0110 R/W 00000000 D[7:0]=GP[7:0]

SCR7 0111 R/W 00000000

SCR8 1000 R/W 00000000

SCR9 1001 R/W 00000000 D[7:0]=RX offset low

SCR10 1010 R/W 00000000 D[7:0]=RX offset high

SCR11 1011 R/W 00000000

SCR12 1 100 R/W 00000000 D[2:0]=RX PGA1. D[2:0]=000 for 0 dB. D[2:0]=110 for 6 dB.

SCR13 1 101 R/W 00000000

SCR14 1110 R/W 00000000

NOTE 1: It is a two-stage FIFO buffer, and can store up to two write-samples if asynchronous write operation is required.

ADDRESS

S3, S2, S1, S0

MODE

R 00000000

W D0: S/W RESET (self clearing)

VALUE

D[4:0]=TX channel PAA gain select. D[4:0]=00000 for 0 dB

D[4:0]=1 1000 for –24 dB

D[2:0]= RX EQ slope select. D[2:0]=000 for 0dB/MHz, D[2:0]=001 for 5 dB/MHz,

D[2:0]=101 for 25 dB/MHz

MISC control (set to 1 to enable)

D0: bypass TX DHPF (25.875 kHz)

D1: S/W power-down RX channel

D2: S/W power-down TX channel

D3: analog loop-back (TX channel)

D4: digital loop-back (TX and EC channel)

D5: TX parallel interface (read-back) test mode enable

D6: EC channel power down

D7: EC analog loop-back

D[4:0]=EC channel PAA gain select. D[4:0]=00000 for 0 dB.

D[4:0]=1 1000 for –24 dB.

D[4:0]=TX digital gain select. The gain range is –1dB to 1dB in 0.1 dB-steps.

D[4:0]=00000 for 0 dB. D[4:0]=00001 for +0.1 dB. D[4:0]=01010 for +1 dB.

D[4:0]=10000 for –1 dB. D[4:0]=11001 for –0.1 dB.

D[4:0]=EC digital gain select. The gain range is –1dB to 1dB in 0.1-dB steps.

D[4:0]=00000 for 0 dB. D[4:0]=00001 for +0.1 dB. D[4:0]=01010 for +1 dB.

D[4:0]=10000 for –1 dB. D[4:0]=11001 for –0.1 dB.

D0: Sync the write operation when ONE_WE is selected. After D0 is set to 1, the first

pulse of WETX

The bit will be self-cleared to 0.

D1: enable FIFO (first-in, first-out). See Note 1.

D2: Bypass EC DHPF (25.875 kHz)

D3: ECNULL. When D3 is set to 1, ECP and ECM are connected to weakly driven

mid supply. It can only be used during EC power-down mode.

goes to TX channel, and the second pulse goes to EC channel.

FUNCTION

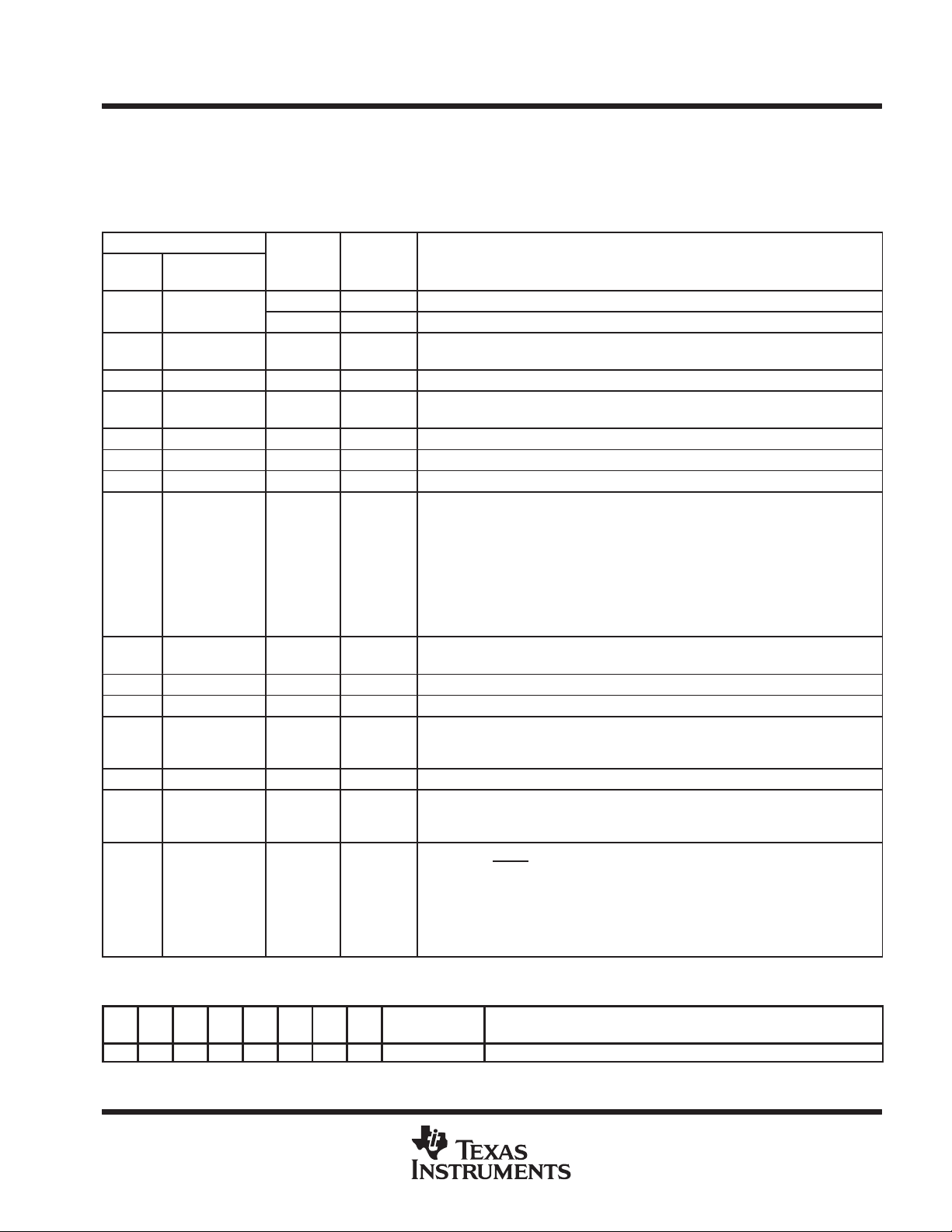

SCR0 – system control register Address:0000b Contents at reset: 00000000b

D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 0 0 0 0 1 01 S/W reset (self clearing). All control registers are set to reset content.

REGISTER

VALUE (HEX)

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

DESCRIPTION

9

Loading...

Loading...