RHBDAP

www.ti.com

On/Off

Input

Shift

Register

DCInput

Shift

Register

7−bitDCRegister

Delay

x0

ConstantCurrent

Driver

LOD

MODE

0 1

MODE

0

1

0

15

111

0

On/OffRegister

0

6

0

0

01

Temperature

ErrorFlag

(TEF)

LEDOpen

Detection

(LOD)

7−bitDCRegister

Delay

x1

ConstantCurrent

Driver

LOD

On/OffRegister

7

13

1

1

7−bitDCRegister

Delay

x15

ConstantCurrent

Driver

LOD

On/OffRegister

105

111

15

15

BLANK

0

Max.OUTn

Current

GNDVCC SINSCLK

SOUT

IREF

XERR

XLA

T

MODE

OUT0

OUT1

OUT15

PGND

BLANK

BLANK

BLANK

16

16

112

1

VUP

VUP

VUP

VUP

16-CHANNEL LED DRIVER WITH DOT CORRECTION AND PRE-CHARGE FET

FEATURES APPLICATIONS

• 16 Channels

• Drive Capability

– 0 to 80 mA (Constant-Current Sink)

• Constant Current Accuracy: ±1% (typical)

• Serial Data Interface

• Fast Switching Output: Tr/ Tf= 10ns (typical)

• CMOS Level Input/Output

• 30 MHz Data Transfer Rate

• V

• Operating Temperature = –40 ° C to 85 ° C

• LED Supply Voltage up to 17 V

• 32-pin HTSSOP( PowerPAD™) and QFN

• Dot Correction

• Controlled In-Rush Current

• Pre-Charge FET

• Error Information

= 3.0 V to 5.5 V

CC

Packages

– 7 bit (128 Steps)

– individual adjustable for each channel

– LOD: LED Open Detection

– TEF: Thermal Error Flag

TLC5924

SLVS626 – JUNE 2006

• Monocolor, Multicolor, Fullcolor LED Display

• Monocolor, Multicolor LED Signboard

• Display Backlighting

• Multicolor LED lighting applications

DESCRIPTION

The TLC5924 is a 16 channel constant-current sink

driver. Each channel has a On/Off state and a

128-step adjustable constant current sink (dot

correction). The dot correction adjusts the brightness

variations between LED, LED channels and other

LED drivers. Both dot correction and On/Off state are

accessible via a serial data interface. A single

external resistor sets the maximum current of all 16

channels.

Each constant-current output has a pre-charge FET

that enables an improvement in image quality of the

dynamic-drive LED display.

The TLC5924 features two error information circuits.

The LED open detection (LOD) indicates a broken or

disconnected LED at an output terminal. The thermal

error flag (TEF) indicates an over-temperature

condition.

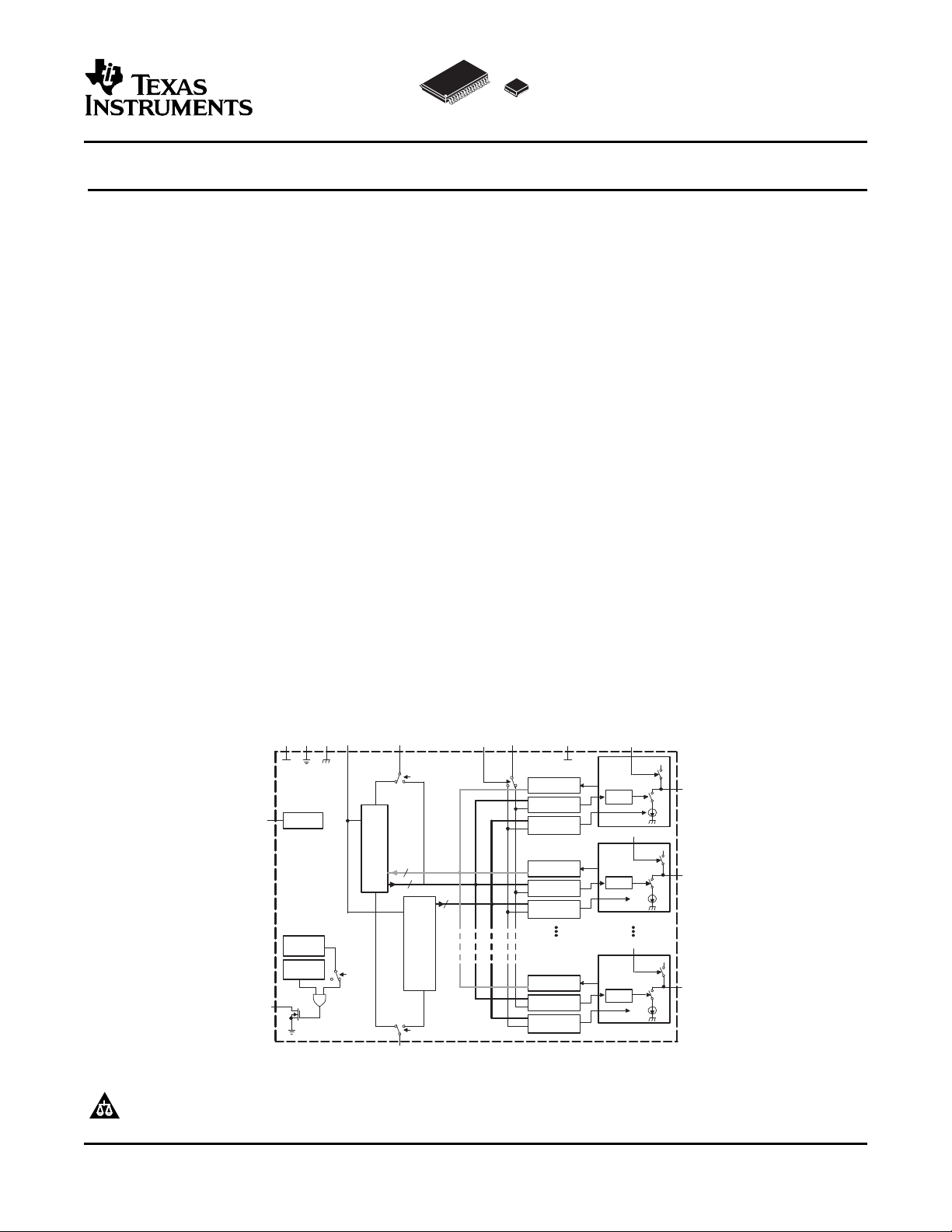

FUNCTIONAL BLOCK DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2006, Texas Instruments Incorporated

www.ti.com

TLC5924

SLVS626 – JUNE 2006

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

(1)

(1)

T

A

–40 ° C to 85 ° C

ORDERING INFORMATION

Package Part Number

32-pin, HTSSOP, PowerPAD™ TLC5924DAP

32-pin, 5 mm x 5 mm QFN TLC5924RHB

(1) For the most current package and ordering information, see the Package Option Addendum at the end

of this document, or see the TI website at www.ti.com .

ABSOLUTE MAXIMUM RATINGS

(1) (2)

TLC5924 UNIT

V

Supply voltage

CC

V

Pre-charge voltage –0.3 to 16 V

UP

I

Output current (dc) I

O

V

Input voltage range

I

V

Output voltage range

O

ESD rating

T

Storage temperature range –40 to 150 °C

stg

Power dissipation rating at (or

above) TA= 25 ° C

(2)

to I

(2)

(2)

(OUT0)

V

(BLANK)

V

(SOUT)

V

(OUT0)

(OUT15)

, V

, V

, V

(XLAT)

(SCLK)

, V

(XERR)

to V

(OUT15)

, V

(SIN)

, V

(MODE)

(IREF)

–0.3 to 6 V

90 mA

–0.3 to V

–0.3 to V

-0.3 to V

+ 0.3 V

CC

+ 0.3 V

CC

UP

HBM (JEDEC JESD22-A114, Human Body Model) 2 kV

CDM (JEDEC JESD22-C101, Charged Device Model) 500 V

HTSSOP (DAP) 42.54 mW/ ° C

(3)

QFN (RHB) 27.86 mW/ ° C

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

(3) See SLMA002 for more information about PowerPAD™

V

RECOMMENDED OPERATING CONDITIONS—DC Characteristics

V

Supply voltage 3 5.5 V

CC

V

Pre-charge voltage 3 15 V

UP

V

Voltage applied to output, (Out0 - Out15) V

O

V

High-level input voltage 0.8 VCC VCC V

IH

V

Low-level input voltage GND 0.2 VCC V

IL

I

High-level output current V

OH

I

Low-level output current V

OL

I

Constant output current OUT0 to OUT15 80 mA

OLC

T

Operating free-air temperature range -40 85 ° C

A

2

= 5 V at SOUT –1 mA

CC

= 5 V at SOUT, XERR 1 mA

CC

Submit Documentation Feedback

MIN NOM MAX UNIT

V

UP

www.ti.com

TLC5924

SLVS626 – JUNE 2006

RECOMMENDED OPERATING CONDITIONS—AC Characteristics

V

= 3 V to 5.5 V, TA= -40°C to 85°C (unless otherwise noted)

CC

MIN TYP MAX UNIT

f

SCLK

t

wh0

t

wh1

t

su0

t

su1

t

su1a

t

su2

t

su3

t

h0

t

h1

t

h1a

t

h2

t

h3

(1) " ↑ " and " ↓ " indicates a rising edge, and a falling edge respectively.

ELECTRICAL CHARACTERISTICS

V

CC

V

OH

V

OL

I

I

I

CC

I

OLC

I

LO0

I

LO1

∆ I

∆ I

∆ I

∆ I

R

(ON)

T

(TEF)

V

(LOD)

V

(IREF)

(1) Measured at device start-up temperature. Once the IC is operating (self heating), lower ICCvalues will be seen. See Figure 20 .

(2) Not tested. Specified by design.

Clock frequency SCLK 30 MHz

, t

CLK pulse duration SCLK=H/L 16 ns

wl0

XLAT pulse duration XLAT=H 20 ns

SIN to SCLK ↑

(1)

10

SLCK ↑ to XLAT ↓ (dot correction data) 10

Setup time SCLK ↑ to XLAT ↑ (ON/OFF data) 10 ns

MODE ↑ ↓ to SCLK ↑ 10

MODE ↑ ↓ to XLAT ↑ 10

SCLK ↑ to SIN 10

XLAT ↓ to SCLK ↑ (dot correction data) 10

Hold time XLAT ↑ to SCLK ↑ (ON/OFF data) 10 ns

SCLK ↑to MODE ↑ ↓ 10

XLAT ↓ to MODE ↑ ↓ 10

= 3 V to 5.5 V, TA= –40 ° C to 85 ° C (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

High-level output voltage IOH= –1 mA, SOUT VCC– 0.5 V

Low-level output voltage IOL= 1 mA, SOUT 0.5 V

Input current VI= V

No data transfer, All output OFF, VO= 1 V, R

k Ω

No data transfer, All output OFF, VO= 1 V, R

Supply current mA

k Ω

Data transfer 30 MHz, All output ON, VO= 1 V,

R

Data transfer 30 MHz, All output ON, VO= 1 V,

R

Constant sink current All output ON, VO= 1 V, R

All output OFF, VO= 15 V, R

Leakage output current

OUT15

V

Constant sink current error All output ON, VO= 1 V, R

OLC0

Constant sink current error ± 4% ± 8.5%

OLC1

Line regulation ± 1 ± 4 %/V

OLC2

Load regulation ± 2 ± 6 %/V

OLC3

device to device, averaged current from OUT0 to OUT15,

R

All output ON, VO= 1 V, R

OUT0 to OUT15, V

All output ON, VO= 1 V to 3 V, R

OUT0 to OUT15

Pre-charge FET on-resistance V

Thermal error flag threshold Junction temperature, rising temperature

LED open detection threshold 0.3 0.4 V

Reference voltage output R

or GND, BLANK, XLAT, SCLK, SIN, MODE –1 1 µ A

CC

= 10

(IREF)

= 1.3

(IREF)

= 1.3 k Ω

(IREF)

= 600 Ω

(IREF)

= 600 Ω 70 80 90 mA

(IREF)

= 600 Ω , OUT0 to

(IREF)

= 5.5 V, No TEF and LOD 10 µ A

XERR

= 600 Ω , OUT0 to OUT15 ± 1% ± 4%

(IREF)

= 600 Ω

(IREF)

= 600 Ω ,

(IREF)

= 3 V to 5.5 V

CC

= 600 Ω ,

(IREF)

= 3 V, VO= 0 V, OUT0 to OUT15 10 K Ω

UP

= 600 Ω 1.20 1.24 1.28 V

(IREF)

(2)

36 65

150 160 180 ° C

15

32

(1)

0.1 µ A

6

Submit Documentation Feedback

3

www.ti.com

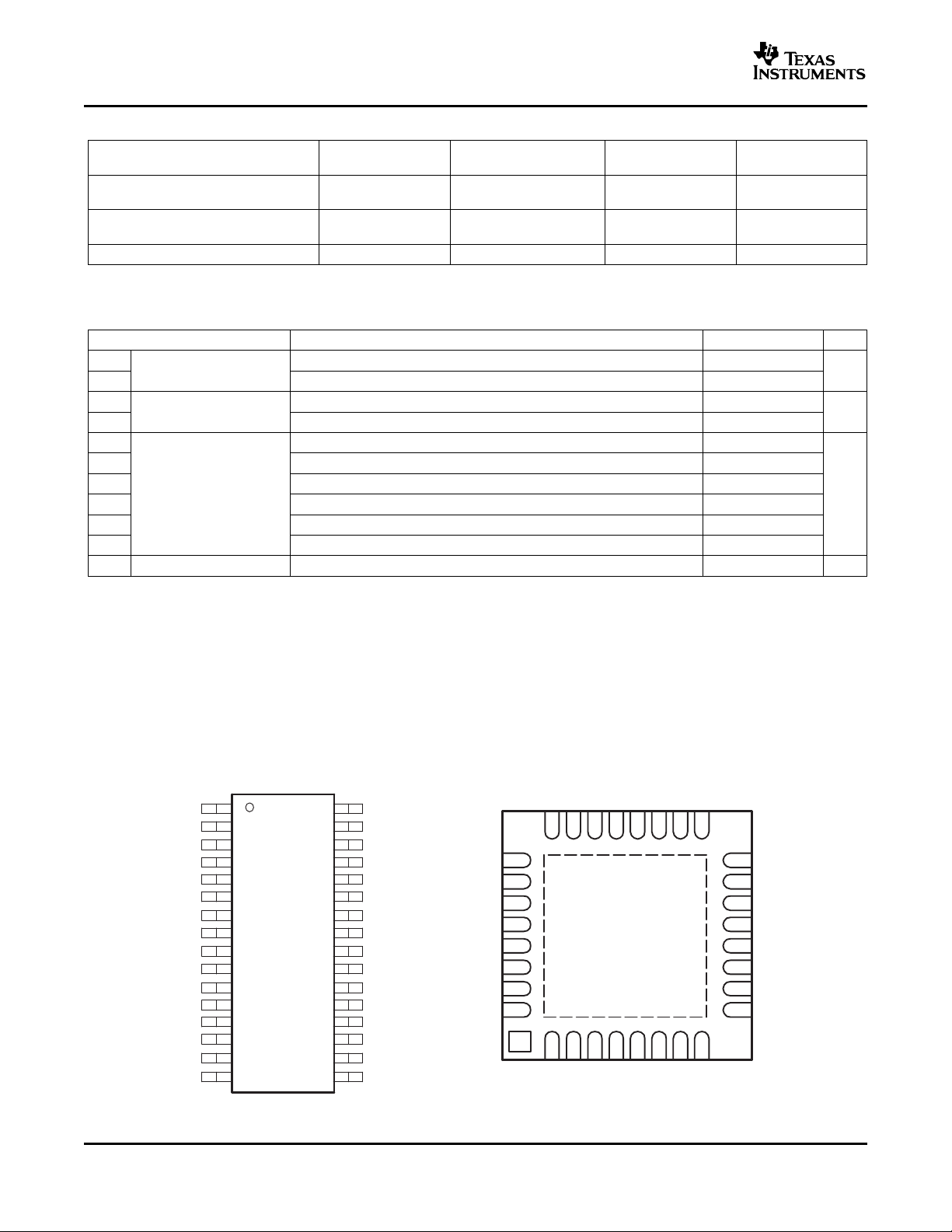

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

GND

BLANK

XLAT

SCLK

SIN

VUP

OUT0

OUT1

PGND

OUT2

OUT3

OUT4

OUT5

PGND

OUT6

OUT7

VCC

IREF

MODE

XERR

SOUT

VUP

OUT15

OUT14

PGND

OUT13

OUT12

OUT11

OUT10

PGND

OUT9

OUT8

THERMAL

PAD

SOUT24VUP23OUT1522OUT1421PGND20OUT1319OUT1218OUT1

1

17

OUT1016

PGND15

OUT914

OUT813

OUT712

OUT611

PGND10

OUT59

OUT4

8

OUT3

7

OUT2

6

PGND

5

OUT1

4

OUT0

3

VUP

2

SIN

1

XERR 25

MODE 26

IREF 27

VCC 28

GND 29

BLANK 30

XLAT 31

SCLK 32

RHBPACKAGE

(TOPVIEW)

(QFN)

DAPPACKAGE

(TOPVIEW)

TLC5924

SLVS626 – JUNE 2006

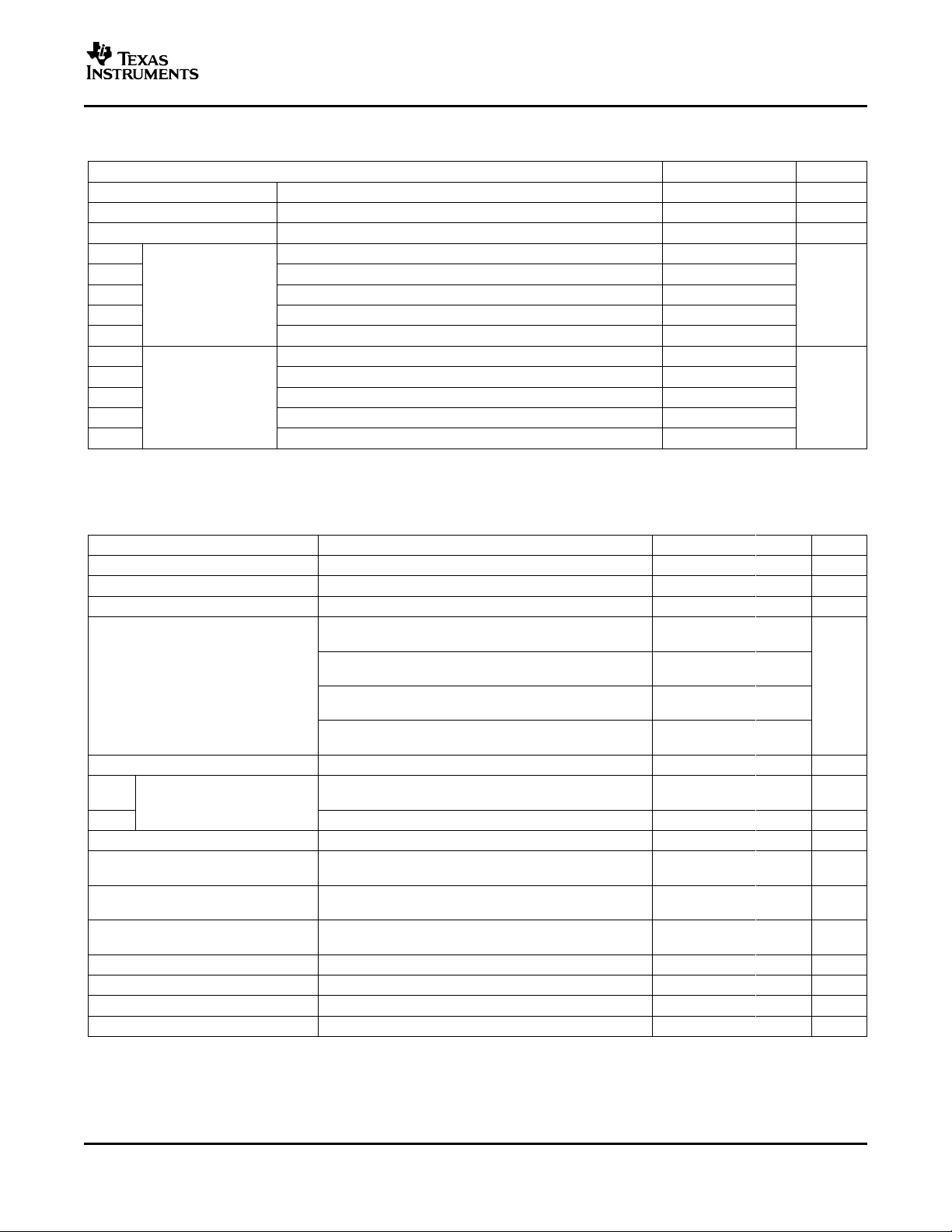

DISSIPATION RATINGS

PACKAGE

32-pin HTSSOP with PowerPAD

soldered

32-pin HTSSOP with PowerPAD

unsoldered

32-pin QFN 3482 mW 27.86 mW/ ° C 2228 mW 1811 mW

(1) The PowerPAD is soldered to the PCB with a 2 oz. copper trace. See SLMA002 for further information.

(1)

(1)

SWITCHING CHARACTERISTICS

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

t

r0

Rise time ns

t

r1

t

f0

Fall time ns

t

f1

t

pd0

t

pd1

t

pd2

Propagation delay time ns

t

pd3

t

pd4

t

pd5

t

Output delay time OUTn ↑ to OUT(n+1) ↑ , OUTn ↓ to OUT(n+1) ↓ (see

d

POWER RATING DERATING FACTOR POWER RATING POWER RATING

TA< 25 ° C ABOVE TA = 25 ° C TA= 70 ° C TA= 85 ° C

5318 mW 42.54 mW/ ° C 3403 mW 2765 mW

2820 mW 22.56 mW/ ° C 1805 mW 1466 mW

SOUT(see

OUTn, V

SOUT (see

OUTn, V

SCLK ↑ to SOUT ↑ ↓ (see

MODE ↑↓ to SOUT ↑ ↓ (see

BLANK ↑ ↓ to OUT0 ↑ ↓ (see

XLAT ↑ to OUT0 ↑ ↓ (see

OUTn ↑ ↓ to XERR ↑ ↓ (see

XLAT ↑ to I

(1)

) 16

= 5 V, TA= 60 ° C, DCx = 7F (see

CC

(1)

) 16

= 5 V, TA= 60 ° C, DCx = 7F (see

CC

OUT

(dot-correction) (see

(3) (4)

) 30

(3)

) 30

(5)

), Sink current On/Off 80

(5)

) 60

(6)

) 1000

(7)

) 1000

(2)

) 10 30

(2)

) 10 30

(5)

) 14 22 30 ns

(1) See Figure 4 . Defined as from 10% to 90%

(2) See Figure 5 . Defined as from 10% to 90%

(3) See Figure 4 , Figure 16

(4) " ↑ " and " ↓ " indicates a rising edge, and a falling edge respectively.

(5) See Figure 5 and Figure 16

(6) See Figure 5 , Figure 6 , and Figure 16

(7) See Figure 5

4

Submit Documentation Feedback

www.ti.com

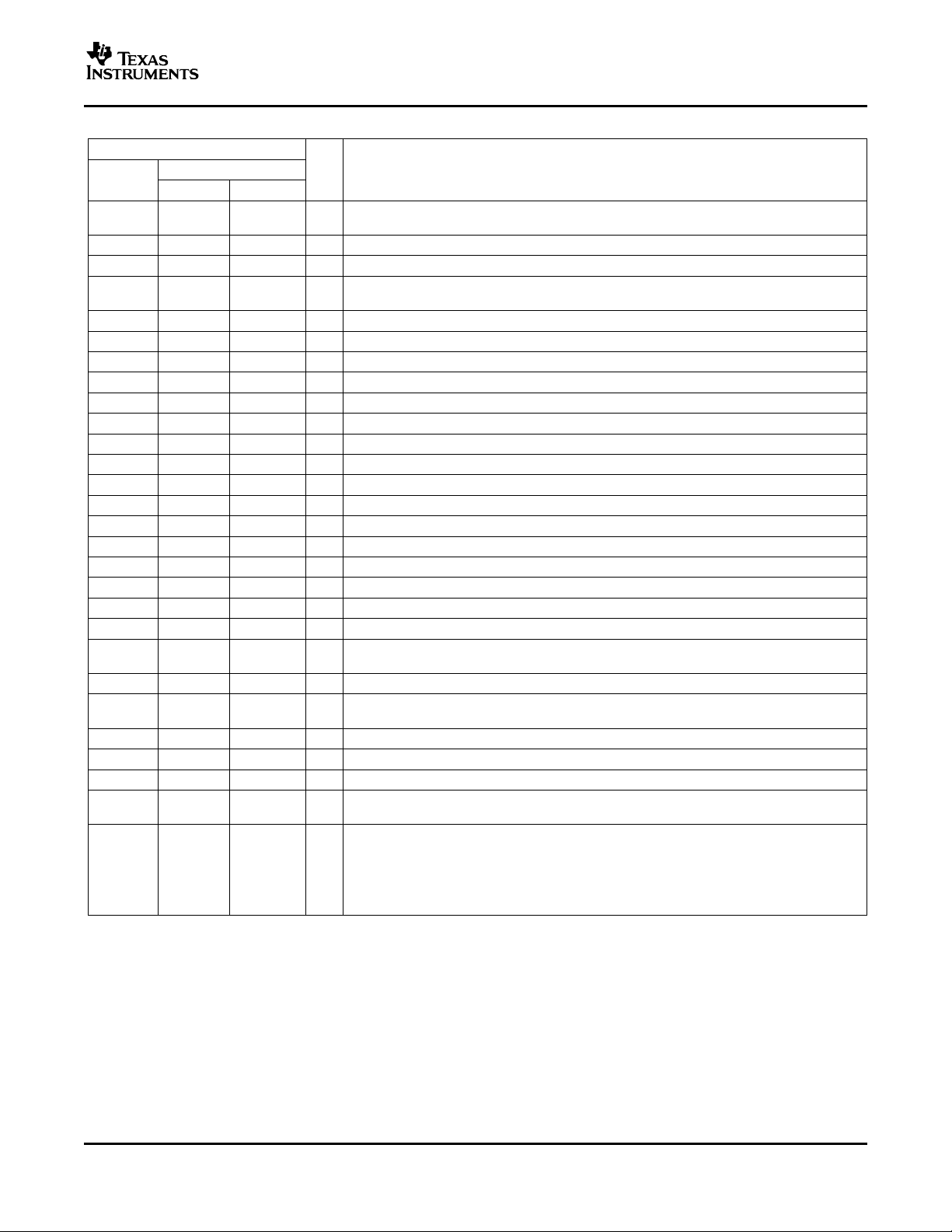

Terminal Functions

TERMINAL

NAME

BLANK 2 30 I

GND 1 29 Ground

IREF 31 27 I/O Reference current terminal

MODE 30 26 I

OUT0 7 3 O Constant current output

OUT1 8 4 O Constant current output

OUT2 10 6 O Constant current output

OUT3 11 7 O Constant current output

OUT4 12 8 O Constant current output

OUT5 13 9 O Constant current output

OUT6 15 11 O Constant current output

OUT7 16 12 O Constant current output

OUT8 17 13 O Constant current output

OUT9 18 14 O Constant current output

OUT10 20 16 O Constant current output

OUT11 21 17 O Constant current output

OUT12 22 18 O Constant current output

OUT13 23 19 O Constant current output

OUT14 25 21 O Constant current output

OUT15 26 22 O Constant current output

PGND Power ground

VUP 6, 27 2, 23 Pre-charge power supply voltage

SCLK 4 32 I

SIN 5 1 I Data input of serial I/F

SOUT 28 24 O Data output of serial I/F

VCC 32 28 Power supply voltage

XERR 29 25 O

XLAT 3 31 I

TSSOP QFN

NO. I/O DESCRIPTION

Blank (Light OFF). When BLANK=H, All OUTn outputs are forced to VUP level. When

BLANK=L, ON/OFF of OUTn outputs are controlled by input data.

Mode select. When MODE=L, SIN, SOUT, SCLK, XLAT are connected to ON/OFF control

logic. When MODE=H, SIN, SOUT, SCLK, XLAT are connected to dot-correction logic.

9, 14, 5, 10,

19, 24 15, 20

Data shift clock. Note that the internal connections are switched by MODE (pin #30). At

SCLK ↑ , the shift-registers selected by MODE shift the data.

Error output. XERR is open drain terminal. XERR transistions from H to L when LOD or TEF

detected.

Data latch signal. When MODE = L (ON/OFF data mode), XLAT is an edge-triggered latch

signal of ON/OFF registers. The serial data in ON/OFF input shift registers is latched into the

ON/OFF registers at the rising edge of XLAT. When MODE = H (DC data mode), XLAT is a

level-triggered latch signal of dot correction registers. The serial data in DC input shift

registers is written into dot correction registers when XLAT = H. The data in dot correction

registers is held constant when XLAT = L.

TLC5924

SLVS626 – JUNE 2006

Submit Documentation Feedback

5

www.ti.com

VCC

INPUT

GND

400 W

SOUT

GND

10 W

XERR

GND

20 W

SOUT

15 pF

OUTn

VUP

51 Ω

15pF

TLC5924

SLVS626 – JUNE 2006

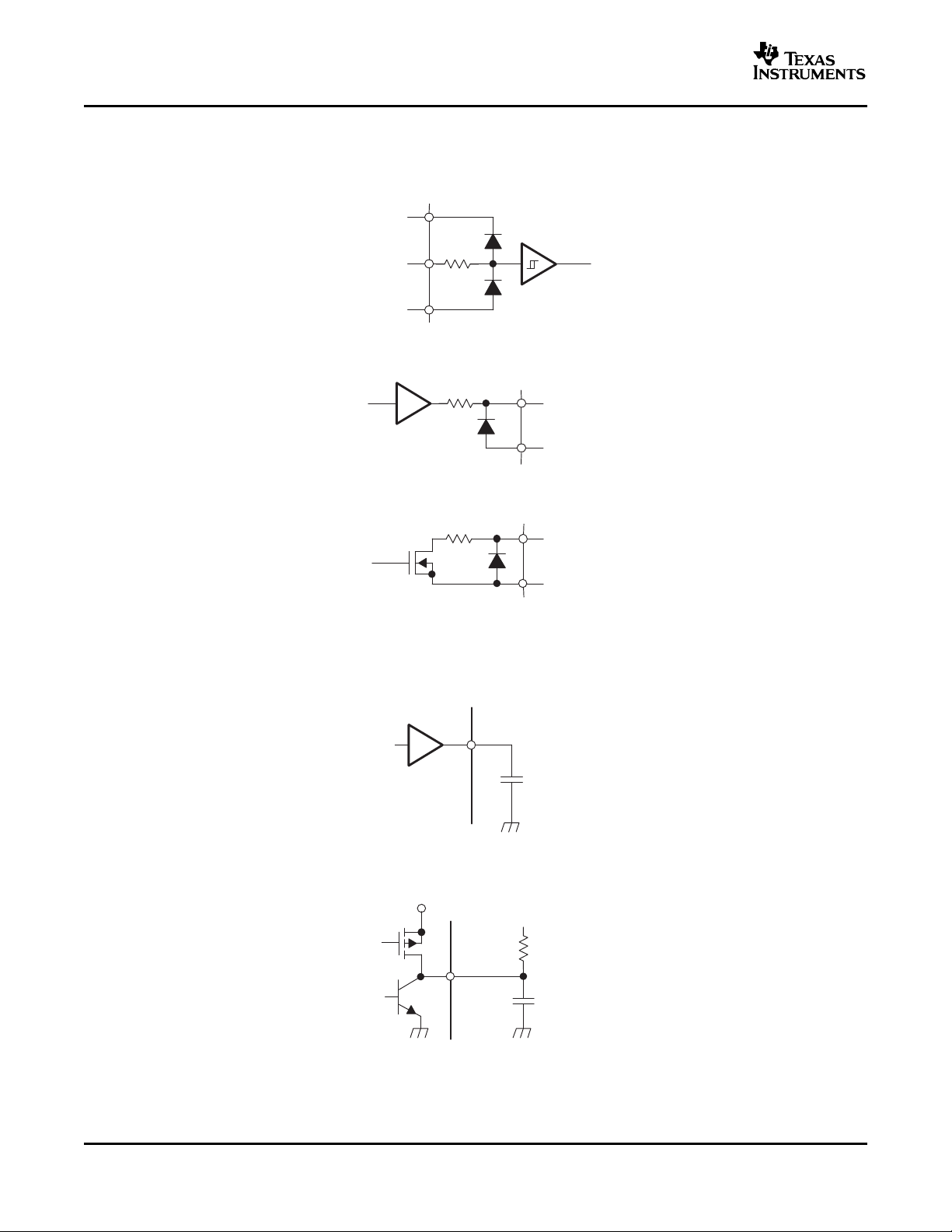

PIN EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

(Note: Resistor values are equivalent resistance and not tested).

Figure 1. Input Equivalent Circuit (BLANK, XLAT, SCLK, SIN, MODE)

Figure 2. Output Equivalent Circuit

Figure 3. Output Equivalent Circuit (XERR)

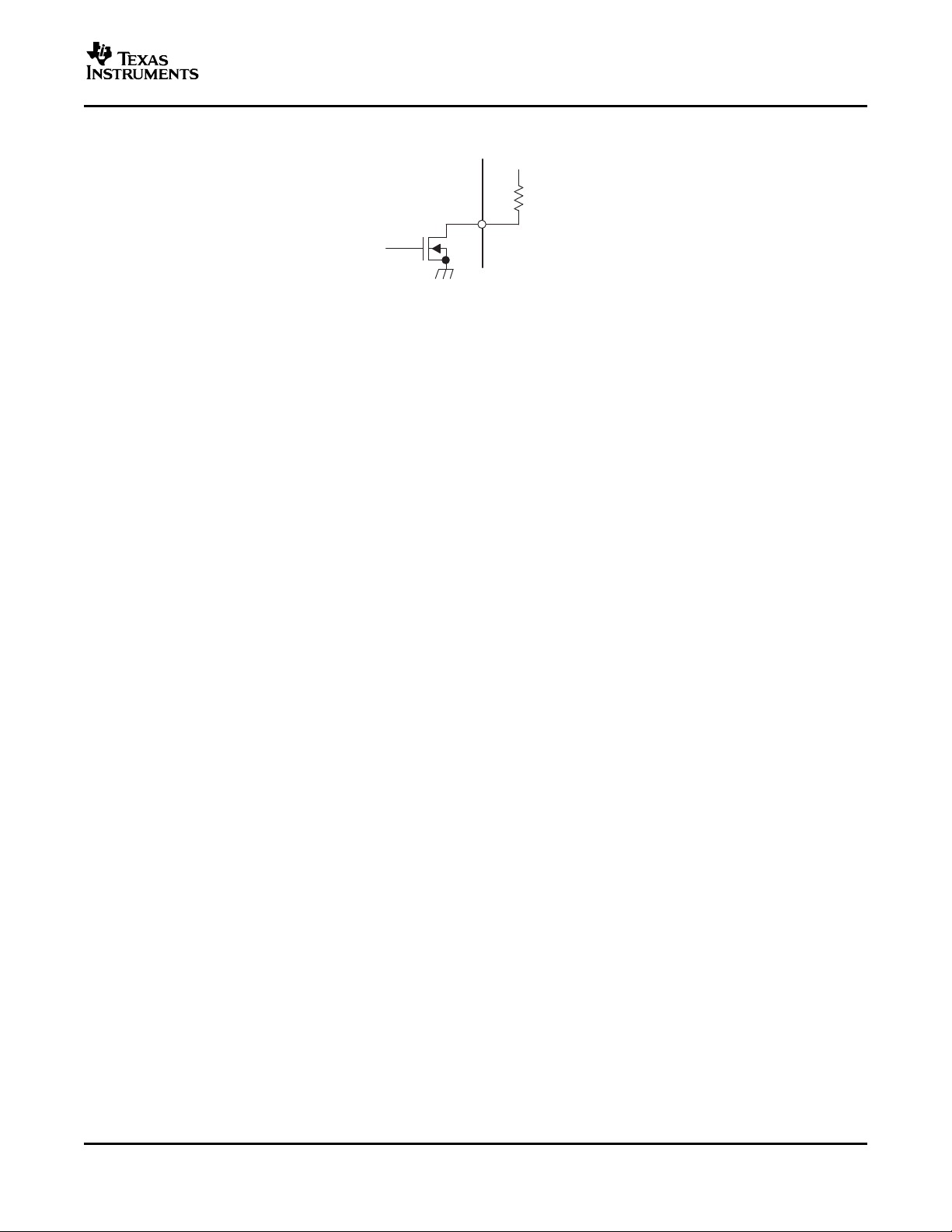

PARAMETER MEASUREMENT INFORMATION

Figure 4. Test Circuit for tr0, tf0, t

Figure 5. Test Circuit for tr1, tf1, t

, t

pd0

pd1

, t

, t

pd2

pd3

, t

pd5

td

6

Submit Documentation Feedback

www.ti.com

XERR

470 kΩ

PARAMETER MEASUREMENT INFORMATION (continued)

TLC5924

SLVS626 – JUNE 2006

Figure 6. Test Circuit for t

pd4

Submit Documentation Feedback

7

www.ti.com

I

MAX

+

V

IREF

R

IREF

40

I

Outn

+

I

MAX

DC

n

127

DC15.0

105

DC15.6

111

DC14.6

104

MSB

DCOUT15

DC0.0

0

DC1.07DC0.6

6

LSB

DCOUT0

DCOUT14 − DCOUT1

TLC5924

SLVS626 – JUNE 2006

PRINCIPLES OF OPERATION

Setting Maximum Channel Current

The maximum output current per channel is set by a single external resistor, R

IREF and GND. The voltage on IREF is set by an internal band gap V

maximum channel current is equivalent to the current flowing through R

with a typical value of 1.24V. The

(IREF)

(IREF)

maximum output current per channel can be calculated by Equation 1 :

where:

V

= 1.24V typ.

IREF

R

= User selected external resistor ®

IREF

Figure 17 shows the maximum output current, I

resistor between IREF terminal to ground, and I

should not be smaller than 600 Ω)

IREF

, versus R

OLC

is the constant output current of OUT0,.....OUT15. A variable

OLC

(IREF)

. In Figure 17 , R

power supply may be connected to the IREF pin through a resistor to change the maximum output current per

channel. The maximum output per channel is 40 times the current flowing out of the IREF pin. The maximum

current from IREF equals 1.24V/600 Ω .

, which is placed between

(IREF)

multiplied by a factor of 40. The

is the value of the

(IREF)

(1)

Setting Dot-Correction

The TLC5924 has the capability to fine adjust the current of each channel, OUT0 to OUT15 independently. This

is also called dot correction. This feature is used to adjust the brightness deviations of LED connected to the

output channels OUT0 to OUT15. Each of the 16 channels can be programmed with a 7-bit word. The channel

output can be adjusted in 128 steps from 0% to 100% of the maximum output current I

channels must be entered at the same time. Equation 2 determines the output current for each OUTn:

where:

I

= the maximum programmable current of each output

Max

DCn = the programmed dot-correction value for output n (DCn = 0, 1, 2 ...127)

n = 0, 1, 2 ... 15

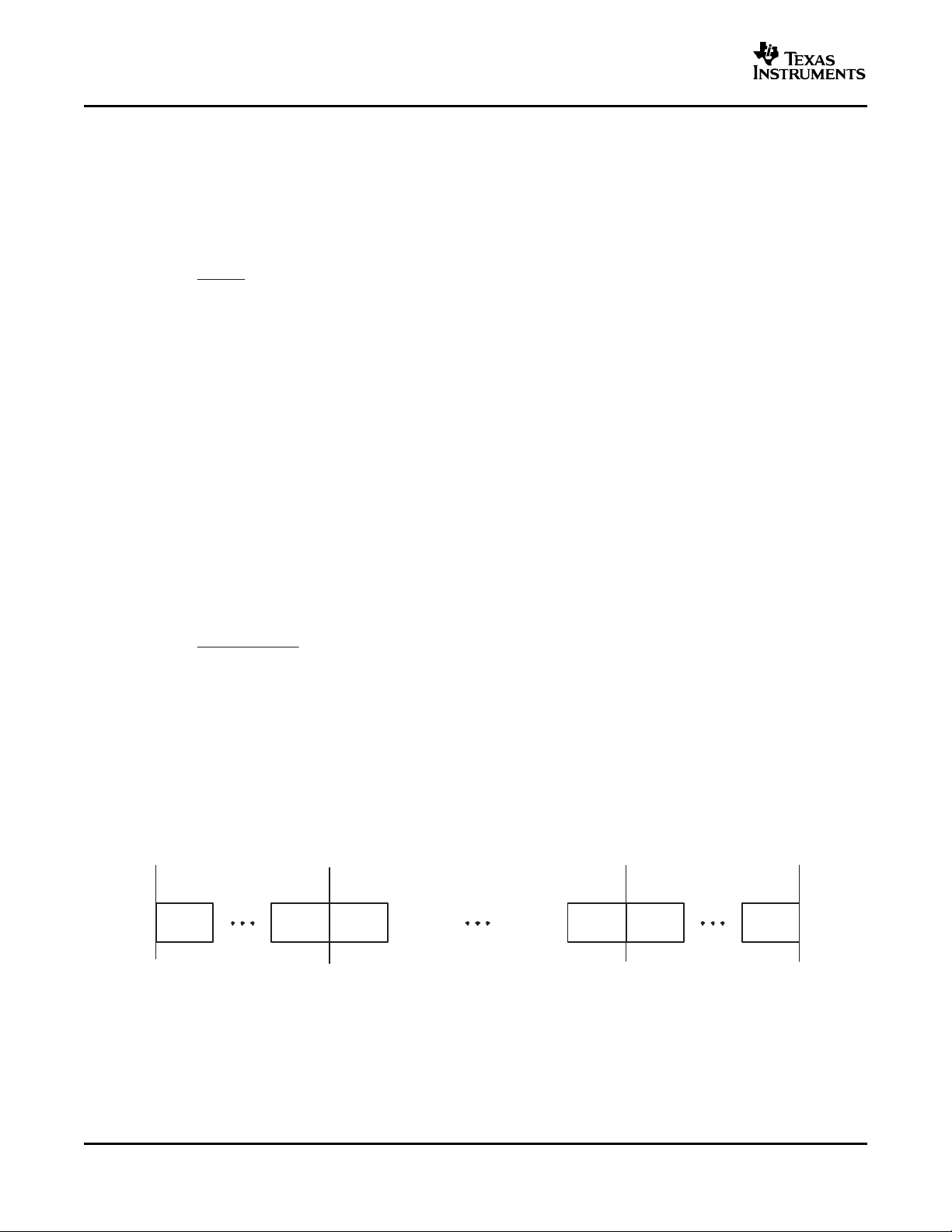

Dot correction data are entered for all channels at the same time. The complete dot correction data format

consists of 16 x 7-bit words, which forms a 112-bit wide serial data packet. The channel data is put one after

another. All data is clocked in with MSB first. Figure 7 shows the DC data format. The DC15.6 in Figure 7 stands

for the 6thmost significant bit for output 15.

. Dot correction for all

MAX

(2)

Figure 7. DC Data Format

To input data into dot correction register, MODE must be set to high. The internal input shift register is then set

to 112-bit width. After all serial data is clocked in, a high level pulse of XLAT signal connects the serial data to

the dot correction register. The dot correction registers are level-triggered latches of XLAT signal. The serial

data is latched into the dot correction registers when XLAT goes low. The data in dot correction registers is held

constant when XLAT is low. BLANK signal does not need to be high to latch in new data. Since XLAT is a

level-triggered signal when MODE is high, SCLK and SIN must not be changed while XLAT is high. (Figure 16 ).

8

Submit Documentation Feedback

www.ti.com

On/OffData

15

MSB

On/Off

OUT15

On/Off

OUT14

On/Off

OUT13

0

LSB

On/Off

OUT2

On/Off

OUT1

On/Off

OUT0

TLC5924

SLVS626 – JUNE 2006

PRINCIPLES OF OPERATION (continued)

Output Enable

When BLANK = H, TLC5924 switches off the sink current of all OUTn with each output delay, then switches on

the pre-charge FET of all OUTn. When BLANK = L, the TLC5924 switches off the pre-charge FETs, and enables

the sink current set by input data. See "Delay Between Outputs" section for more detail on the output delay.

Table 1. BLANK Signal Truth Table

BLANK OUT0 - OUT15

LOW Normal condition

HIGH VUP

Setting Channel On/Off Status

All OUTn channels of TLC5924 can be switched on or off independently. Each of the channels can be

programmed with a 1-bit word. On/Off data are entered for all channels at the same time. The complete On/Off

data format consists of 16 x 1-bit words, which form a 16-bit wide data packet. The channel data is put one after

another. All data is clocked in with MSB first. Figure 8 shows the On/Off data format.

Figure 8. On/Off Data Format

To input On/Off data into On/Off register MODE must be set to low. The internal input shift register is then set to

16 bit width. After all serial data is clocked in, a rising edge of XLAT is used to latch data into the On/Off

register. The ON/OFF register is an edge-triggered latch of XLAT signal. BLANK signal does not need to be high

to latch in new data. Figure 16 shows the On/Off data input timing chart.

Delay Between Outputs

The TLC5924 has graduated delay circuits between outputs. These delay circuits can be found in the constant

current block of the device (see Functional Block Diagram). The fixed delay time is 20 ns (typical), OUT0 has no

delay, OUT1 has 20 ns delay, OUT2 has 40 ns delay, etc. This delay prevents large inrush currents, which

reduce power supply bypass capacitor requirements when the outputs turn on. The delay works during switch on

and switch off of each output channel. LEDs that have not turned on before BLANK is pulled high will still turn on

and off at the determined delayed time regardless of the state of BLANK. Therefore, every LED will be

illuminated for the amount of time BLANK is low.

Pre-Charge FET On/Off Timing

The pre-charge FETs turn on at the same time; and, they turn on at the time the last output that is on turns off.

All pre-charge FETs turn off just after BLANK signal becomes low level, regardless of on/off data of each output.

Figure 9 shows the example of BLANK and OUTn timing.

Submit Documentation Feedback

9

www.ti.com

t

pd2

t

pd2

VUP

Pre-chargePeriod

ONCurrentON OFF

BLANK

OUT0

OUT14

OUT15

ONOFF

t x14

d

t x14

d

VUPVUP

TLC5924

Pre-ChargePowerSupply

TLC5924

SLVS626 – JUNE 2006

Figure 9. Timing Chart of BLANK and OUTn

(On/Off Data Condition: OUT0=H, OUT14=H, OUT15=L)

VUP: Pre-Charge Power Supply

VUP is a pre-charge power supply terminal. The pre-charge voltage should be supplied to this terminal for

normal operation. When VUP terminal is open, TLC5924 keeps OUT0-15 open. TLC5924 has two VUP pins as

shown in the Terminal Functions Table. Both VUP pins should be connected to the pre-charge power supply as

shown in Figure 10 .

Serial Interface Data Transfer Rate

The TLC5924 includes a flexible serial interface, which can be connected to a microcontroller or digital signal

processor. Only 3 pins are required to input data into the device. The rising edge of SCLK signal shifts the data

from SIN pin to internal shift register. After all data is clocked in, a rising edge of XLAT latches the serial data to

the internal registers. All data is clocked in with MSB first. Multiple TLC5924 devices can be cascaded by

connecting SOUT pin of one device with SIN pin of following device. The SOUT pin can also be connected to

controller to receive LOD information from TLC5924.

10

Figure 10. VUP Power Supply

Submit Documentation Feedback

www.ti.com

TLC5924

SIN SOUT

OUT0 OUT15

SCLK

MODE

XLAT

BLANK

IREF

XERR

TLC5924

SIN SOUT

OUT0 OUT15

SCLK

MODE

XLAT

BLANK

IREF

XERR

IC0 ICn

5

SIN

SCLK

MODE

XLAT

BLANK

XERR

Controller

SOUT

100k

100nF

V

(LED)

V

(LED)

V

(LED)

V

(LED)

V

CC

100nF

V

CC

V

CC

f_(SCLK) + 112 f_(update) n

TLC5924

SLVS626 – JUNE 2006

Figure 11. Cascading Devices

Figure 11 shows a example application with n cascaded TLC5924 devices connected to a controller. The

maximum number of cascaded TLC5924 devices depends on application system and data transfer rate.

Equation 3 calculates the minimum data input frequency needed.

where:

f_(SCLK): The minimum data input frequency for SCLK and SIN.

f_(update): The update rate of the whole cascaded system.

n: The number of cascaded TLC5924 devices.

Operating Modes

The TLC5924 has different operating modes depending on MODE signal. Table 2 shows the available operating

modes. The values in the input shift registers, DC register and On/Off register are unknown just after power on.

The DC and On/Off register values should be properly stored through the serial interface before starting the

operation.

Table 2. TLC5924 Operating Modes Truth Table

MODE SIGNAL INPUT SHIFT REGISTER MODE

LOW 16 bit On/Off Mode

HIGH 112 bit Dot Correction Data Input Mode

(3)

Submit Documentation Feedback

11

www.ti.com

LODData

0

LSB

OUT2 OUT1 OUT0

LOD LOD LOD

15

MSB

LOD

OUT15

OUT14 OUT13

LODLOD

TLC5924

SLVS626 – JUNE 2006

Error Information Output

The open-drain output XERR is used to report both of the TLC5924 error flags, TEF and LOD. During normal

operating conditions, the internal transistor connected to the XERR pin is turned off. The voltage on XERR is

pulled up to V

on, and XERR is pulled to GND. Since XERR is an open-drain output, multiple ICs can be OR'ed together and

pulled up to V

error.

To differentiate LOD and TEF signal from XERR pin, LOD can be masked out with BLANK = HIGH.

TEMPERATURE BLANK OUTn VOLTAGE TEF LODn

TJ< T

TJ> T

TJ< T

TJ> T

(1) Note: High-Z means high impedance

through a external pull-up resistor. If TEF or LOD is detected, the internal transistor is turned

CC

with a single pull-up resistor. This reduces the number of signals needed to report a system

CC

Table 3. XERR Truth Table

CONDITION ERROR INFORMATION XERR

(TEF)

(TEF)

(TEF)

(TEF)

H Don't Care L L High-Z

H L

L OUTn > V

OUTn < V

OUTn > V

OUTn < V

(LOD)

(LOD)

(LOD)

(LOD)

L L High-Z

H L

H L L

H L

(1)

TEF: Thermal Error Flag

The TLC5924 provides a temperature error flag (TEF) circuit to indicate an over-temperature condition of the IC.

If the junction temperature exceeds the threshold temperature T

(160°C typical), TEF becomes H and XERR

(TEF)

pin goes to low level. When the junction temperature becomes lower than the threshold temperature, TEF

becomes L and XERR pin becomes high impedance.

LOD: LED-Open Detection

The TLC5924 has an LED-open detector to detect broken or disconnected LEDs, which should be connected to

the output. The LED-open detector pulls the XERR pin down to GND when the LED open is detected. An open

LED is detected when the following three conditions are met:

1. BLANK is low

2. On/Off data is high

3. The voltage of OUTn is less than 0.3 V (typical)

The LOD status of each output can also be read out from the SOUT pin. Figure 12 shows the LOD data format.

Table 4 shows the LOD truth table.

Figure 12. LOD Data Format

12

Submit Documentation Feedback

www.ti.com

SLVS626 – JUNE 2006

Table 4. LOD Data Truth Table

LED ON/OFF LOD BIT

Good On 0

Good Off 0

Bad On 1

Bad Off 0

Key Timing Requirements to Reading LOD

• LOD status flag

The LOD status flag becomes active if the output voltage is <0.3 V (typical) when the output sink current

turns on. There is a 1-µs time delay from the time the output sink current turns on until the time the LOD

status flag becomes valid. The timing for each channel’s LOD status to become valid is shifted by the 30 ns

channel-to-channel turn-on time. After BLANK goes low, OUT0 LOD status is valid when tpd2 + tpd4 = 60

ns + 1 µs = 1.06 µs. OUT1 LOD status is valid when tpd2 + tpd4 + td = 60 ns + 1 µs + 30 ns = 1.09 µs.

OUT3 LOD status is valid when tpd2 + tpd4 + 2*td = 1.12 µs, and so on.

• LOD internal latch

The TLC5924 has an internal latch to hold each channel’s LOD status flag information, as shown in

Figure 13 . When MODE is low, the LOD status information is latched into this latch on the rising edge of

XLAT. This is an edge-triggered latch. To ensure that a valid LOD status flag is latched, BLANK must be low

when XLAT goes high. After the rising edge of XLAT, changes in the status flags do not affect the values in

the LOD latch.

• Loading LOD data to the input shift register

The LOD data must be transferred to the input shift register before it is available to be clocked out of SOUT.

The internal shift register has a set/reset function that is controlled by the LOD internal latch. While XLAT is

high, the LOD internal latch holds the input shift register in either set or reset, depending on the value in the

latch. This effectively puts the LOD data into the input shift register where it remains as long as XLAT is

high. The values in the input shift register are unaffected by any other signals, including SIN and SCLK while

XLAT is high. During this time, the status of OUT15 is present on SOUT.

• Latching LOD data into the internal shift register

While XLAT is high, the status of OUT15 is present on SOUT. When XLAT transitions low, all data is latched

into the Input shift register, and the LOD internal latch is disconnected from the internal shift register.

• Clocking LOD data out of SOUT

While XLAT is low and SCLK is low, the status of OUT15 is on SOUT. On the next rising edge of SCLK, the

status of OUT14 shifts to SOUT. Each subsequent rising edge of SCLK shifts the LOD data out of SOUT.

XLAT must stay low until all LOD data is clocked out of SOUT. See Shifting the LOD Data Out section for

more details.

TLC5924

Submit Documentation Feedback

13

www.ti.com

16bitLODStatusFlags

16bitLODInternalLatch

InputShiftRegister

GSRegister

SIN

SOUT

(FIFORegister)

XLAT

SCLK

SOUT

LOD

OUT15

LOD

OUT14

LOD

OUT12

LOD

OUT13

TLC5924

SLVS626 – JUNE 2006

Figure 13. LOD Flags and Latches

Shifting the LOD Data Out

SOUT outputs the LOD data as shown in Figure 14 , where:

• XLAT rising edge

Holds the LOD status flag. SOUT outputs LOD OUT15 data. BLANK must be low.

• XLAT = H

Sets or resets the input shift register depending on each LOD data.

Set/Reset function is higher priority than shifting the register value. If XLAT is high and the SCLK pin is

pulsed, all LOD data are kept in the shift register and SOUT keeps the LOD OUT15 data.

• XLAT = L

Ready to shift out LOD data by SCLK. SOUT contains LOD OUT15 data at this time. BLANK can be high or

low during this time.

• SCLK rising edge

SOUT outputs LOD OUT14 at the first SCLK rising edge. SOUT outputs LOD OUT13 at the second SCLK

rising edge, and continues to output the next LOD data at each SCLK rising edge.

14

Figure 14. The LOD Data of SOUT

Submit Documentation Feedback

www.ti.com

MODE

XLAT

SCLK

SIN

BLANK

OUT0

XERR

AttherisingedgeofXLAT whileBLANK=L,LODstatusislatched into

theinternaledge-triggeredregister.

tpd2:60nsmax

tdx15=450nsmax

tpd4:1000nsmax

1510nsmax

LEDopen

WhenXLAT=H,theinternaledge-triggeredregister

setsorresetstheinputshiftregister.

>1000ns

tpd2:60nsmax

tdx15=450nsmax

tpd4:1000nsmax

1510nsmax

>1000ns

OUT15

SOUT

Figure 15 shows the timing chart of reading LOD data.

TLC5924

SLVS626 – JUNE 2006

Figure 15. Timing Chart of Reading LOD Data

Submit Documentation Feedback

15

www.ti.com

SCLK

SOUT

SIN

MODE

XLAT

On/OffModeData

InputCycle

DCModeDataInputCycle

BL

ANK

XERR

OUT0

OUT1

DCModeDataInput

Cycle

On/OffModeData

InputCycle

On/OffModeData

InputCycle

t

wh1

f

SCLK

t

wl0

t

su1

t

wh0

t

h0

t

pd0

t

h2

t

su2

t

h1

t

h3

t

pd1

t

pd1

t

su3

t

h3

t

su3

t

pd2

t

pd4

t

d

t

pd5

t

pd2

t

pd5

t

pd3

On/Of

f

LSB

On/Of

f

MSB

DC

MSB

MSB

DC

LSB

DC

MSB

DC

MSB

DC

LSB

DC

MSB

On/Of

f

MSB

On/Of

f

MSB

LSB

On/Of

f

MSB

On/Of

f

MSB

On/Of

f

MSB

On/Off

DC

LSB

DC

LSB

On/Of

f

LSB

DC

On/Of

f

MSB−1

t

su0

(current)

(current)

t

d

t

su1a

t

h1a

TLC5924

SLVS626 – JUNE 2006

16

Figure 16. Timing Chart Example for ON/OFF Setting to Dot-Correction

Submit Documentation Feedback

www.ti.com

0

10

20

30

40

50

60

70

80

90

100

0 0.50 1 1.50 2 2.50 3

I

O

− OutputCurrent − mA

V − RequiredOutputVOoltage − V

I

MAX

=60mA

I

MAX

=40mA

I

MAX

=20mA

827

100

1 k

10 k

100 k

0.01 0.02 0.03 0.04 0.05 0.06 0.07 0.080

49.6 k

9.92 k

4.96 k

2.48 k

1.65 k

1.24 k

709

− Reference Resistor −

I

OLC

− Output Current − A

R

IREF

Ω

V

Outn

= 1 V

DC = 127

992

3k

2k

1k

0

−40 −20 0 20 40

4k

5k

6k

60 80 100

T

A

− Free-AirTemperature −°C

− PowerDissipation − mW

P

D

TLC5924DAP

PowerPADSoldered

TLC5924RHB

TLC5924DAP

PowerPADUnsoldered

0

10

20

30

40

50

60

70

−50 −30 −10 10 30 50 70 90 110 130 150

I

CC

− Supply Current − mA

TA − Free-Air Temperature − °C

TLC5924

SLVS626 – JUNE 2006

TYPICAL CHARACTERISTICS

REFERENCE RESISTOR OUTPUT CURRENT

vs vs

OUTPUT CURRENT REQUIRED OUTPUTn VOLTAGE

Figure 17. Figure 18.

POWER DISSIPATION SUPPLY CURRENT

vs vs

FREE-AIR TEMPERATURE FREE-AIR TEMPERATURE

(A)

Power Rating – Free-Air Temperature

Figure 19 shows total power dissipation. Figure 20 shows supply current versus free-air temperature.

Figure 19.

Submit Documentation Feedback

A. Data Transfer = 30 MHz / All Outputs,

ON/V

O

= 1 V / R

IREF

= 600 Ω / AV

Figure 20.

= 5 V

DD

17

PACKAGE OPTION ADDENDUM

www.ti.com

31-Mar-2008

PACKAGING INFORMATION

Orderable Device Status

(1)

Package

Type

Package

Drawing

Pins Package

Qty

Eco Plan

TLC5924DAP ACTIVE HTSSOP DAP 32 46 Green (RoHS &

no Sb/Br)

TLC5924DAPG4 ACTIVE HTSSOP DAP 32 46 Green (RoHS &

no Sb/Br)

TLC5924DAPR ACTIVE HTSSOP DAP 32 2000 Green (RoHS &

no Sb/Br)

TLC5924DAPRG4 ACTIVE HTSSOP DAP 32 2000 Green (RoHS &

no Sb/Br)

TLC5924RHBR ACTIVE QFN RHB 32 3000 Green (RoHS &

no Sb/Br)

TLC5924RHBRG4 ACTIVE QFN RHB 32 3000 Green (RoHS &

no Sb/Br)

TLC5924RHBT ACTIVE QFN RHB 32 250 Green (RoHS &

no Sb/Br)

TLC5924RHBTG4 ACTIVE QFN RHB 32 250 Green (RoHS &

no Sb/Br)

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in

a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

Lead/Ball Finish MSL Peak Temp

CU NIPDAU Level-3-260C-168 HR

CU NIPDAU Level-3-260C-168 HR

CU NIPDAU Level-3-260C-168 HR

CU NIPDAU Level-3-260C-168 HR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

CU NIPDAU Level-2-260C-1 YEAR

(3)

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check

http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements

for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered

at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and

package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS

compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame

retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3)

MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder

temperature.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the

accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take

reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on

incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited

information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI

to Customer on an annual basis.

Addendum-Page 1

PACKAGE MATERIALS INFORMATION

www.ti.com

TAPE AND REEL INFORMATION

19-Mar-2008

*All dimensions are nominal

Device Package

TLC5924DAPR HTSSOP DAP 32 2000 330.0 24.4 8.6 11.5 1.6 12.0 24.0 Q1

TLC5924RHBR QFN RHB 32 3000 330.0 12.4 5.3 5.3 1.5 8.0 12.0 Q2

TLC5924RHBT QFN RHB 32 250 180.0 12.4 5.3 5.3 1.5 8.0 12.0 Q2

Type

Package

Drawing

Pins SPQ Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0 (mm) B0 (mm) K0 (mm) P1

(mm)W(mm)

Pin1

Quadrant

Pack Materials-Page 1

PACKAGE MATERIALS INFORMATION

www.ti.com

19-Mar-2008

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

TLC5924DAPR HTSSOP DAP 32 2000 346.0 346.0 41.0

TLC5924RHBR QFN RHB 32 3000 346.0 346.0 29.0

TLC5924RHBT QFN RHB 32 250 190.5 212.7 31.8

Pack Materials-Page 2

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements,

and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should

obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are

sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard

warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where

mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not

responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing

such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products

and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be

provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in

such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at

the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are

designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated

products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DSP dsp.ti.com Broadband www.ti.com/broadband

Clocks and Timers www.ti.com/clocks Digital Control www.ti.com/digitalcontrol

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Military www.ti.com/military

Power Mgmt power.ti.com Optical Networking www.ti.com/opticalnetwork

Microcontrollers microcontroller.ti.com Security www.ti.com/security

RFID www.ti-rfid.com Telephony www.ti.com/telephony

RF/IF and ZigBee® Solutions www.ti.com/lprf Video & Imaging www.ti.com/video

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2008, Texas Instruments Incorporated

Wireless www.ti.com/wireless

Loading...

Loading...