TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Direct Upgrades for the TL06x Low-Power

BiFETs

D

Low Power Consumption . . .

6.5 mW/Channel Typ

D

On-Chip Offset-Voltage Trimming for

Improved DC Performance

(1.5 mV, TL031A)

D

Higher Slew Rate and Bandwidth Without

Increased Power Consumption

D

Available in TSSOP for Small Form-Factor

Designs

description

The TL03x series of JFET-input operational amplifiers of fer improved dc and ac characteristics over the TL06x

family of low-power BiFET operational amplifiers. On-chip zener trimming of offset voltage yields precision

grades as low as 1.5 mV (TL031A) for greater accuracy in dc-coupled applications. T exas Instruments improved

BiFET process and optimized designs also yield improved bandwidths and slew rates without increased power

consumption. The TL03x devices are pin-compatible with the TL06x and can be used to upgrade existing

circuits or for optimal performance in new designs.

BiFET operational amplifiers offer the inherently higher input impedance of the JFET -input transistors without

sacrificing the output drive associated with bipolar amplifiers. This higher input impedance makes the TL3x

amplifiers better suited for interfacing with high-impedance sensors or very low-level ac signals. These devices

also feature inherently better ac response than bipolar or CMOS devices having comparable power

consumption.

The TL03x family has been optimized for micropower operation, while improving on the performance of the

TL06x series. Designers requiring significantly faster ac response should consider the Excalibur TLE206x

family of low-power BiFET operational amplifiers.

Because BiFET operational amplifiers are designed for use with dual power supplies, care must be taken to

observe common-mode input-voltage limits and output swing when operating from a single supply . DC biasing

of the input signal is required and loads should be terminated to a virtual-ground node at midsupply. Texas

Instruments TLE2426 integrated virtual-ground generator is useful when operating BiFET amplifiers from single

supplies.

The TL03x devices are fully specified at ±15 V and ±5 V. For operation in low-voltage and/or single-supply

systems, T exas Instruments LinCMOS families of operational amplifiers (TLC-prefix) are recommended. When

moving from BiFET to CMOS amplifiers, particular attention should be paid to slew rate, bandwidth

requirements, and output loading.

The C-suffix devices are characterized for operation from 0°C to 70°C. The I-suffix devices are characterized

for operation from –40°C to 85°C. The M-suffix devices are characterized for operation over the full military

temperature range of –55°C to 125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright 1999, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

1

2

3

4

8

7

6

5

OFFSET N1

IN–

IN+

V

CC–

NC

V

CC+

OUT

OFFSET N2

3212019

910111213

4

5

6

7

8

18

17

16

15

14

NC

V

CC+

NC

OUT

NC

NC

IN–

NC

IN+

NC

NC

OFFSET N1

NC

NC

NC

NC

OFFSET N2

NC

NC

V

CC–

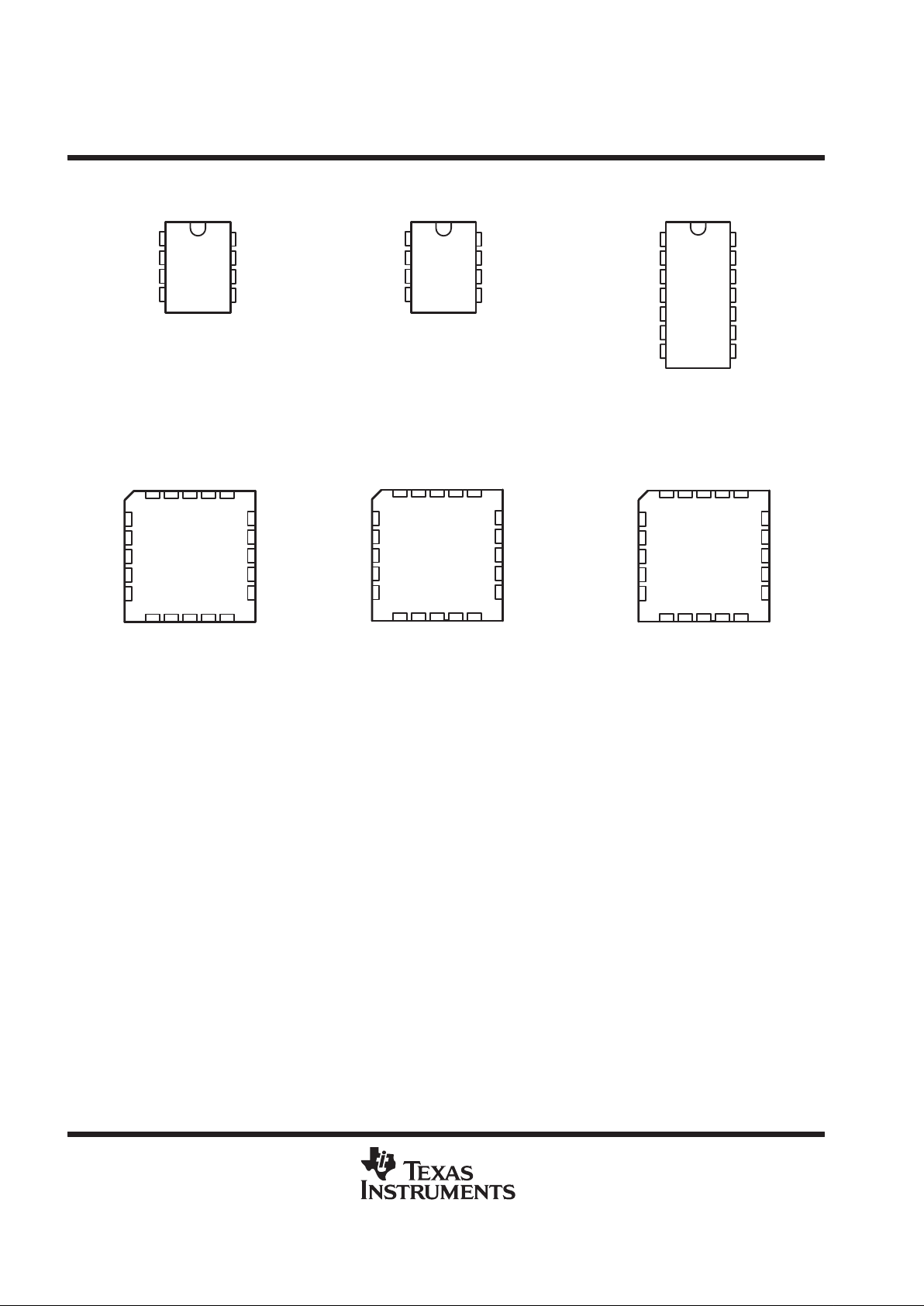

TL031x, TL031Ax

D, JG, OR P PACKAGE

(TOP VIEW)

1

2

3

4

8

7

6

5

1OUT

1IN–

1IN+

V

CC –

V

CC+

2OUT

2IN–

2IN+

3212019

910111213

4

5

6

7

8

18

17

16

15

14

NC

2OUT

NC

2IN–

NC

NC

1IN–

NC

1IN+

NC

NC

1OUT

NC

NC

NC

NC

2IN+

NC

CC–

V

CC+

V

TL031M, TL031AM

FK PACKAGE

(TOP VIEW)

TL032M, TL032AM

FK PACKAGE

(TOP VIEW)

TL032x, TL032Ax

D, JG, OR P PACKAGE

(TOP VIEW)

3212019

910111213

4

5

6

7

8

18

17

16

15

14

4IN+

NC

V

CC–

NC

3IN+

1IN+

NC

V

CC+

NC

2IN+

1IN–

1OUT

NC

3IN–

2IN–

NC

3OUT

4OUT

4IN–

2OUT

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1OUT

1IN–

1IN+

V

CC+

2IN+

2IN–

2OUT

4OUT

4IN–

4IN+

V

CC–

3IN+

3IN–

3OUT

TL034x, TL034Ax

D, J, N, OR PW PACKAGE

(TOP VIEW)

TL034M, TL034AM

FK PACKAGE

(TOP VIEW)

NC – No internal connection

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

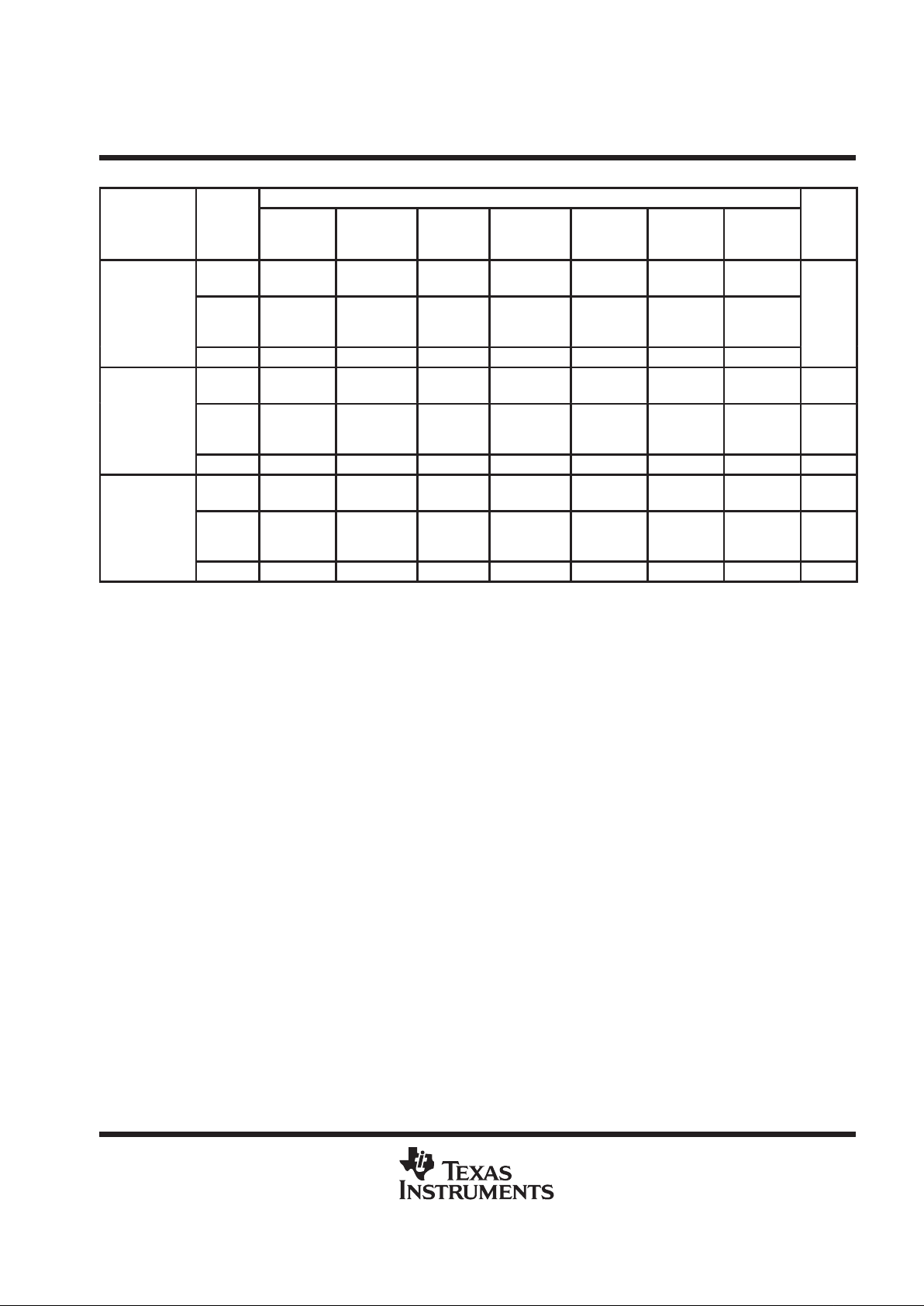

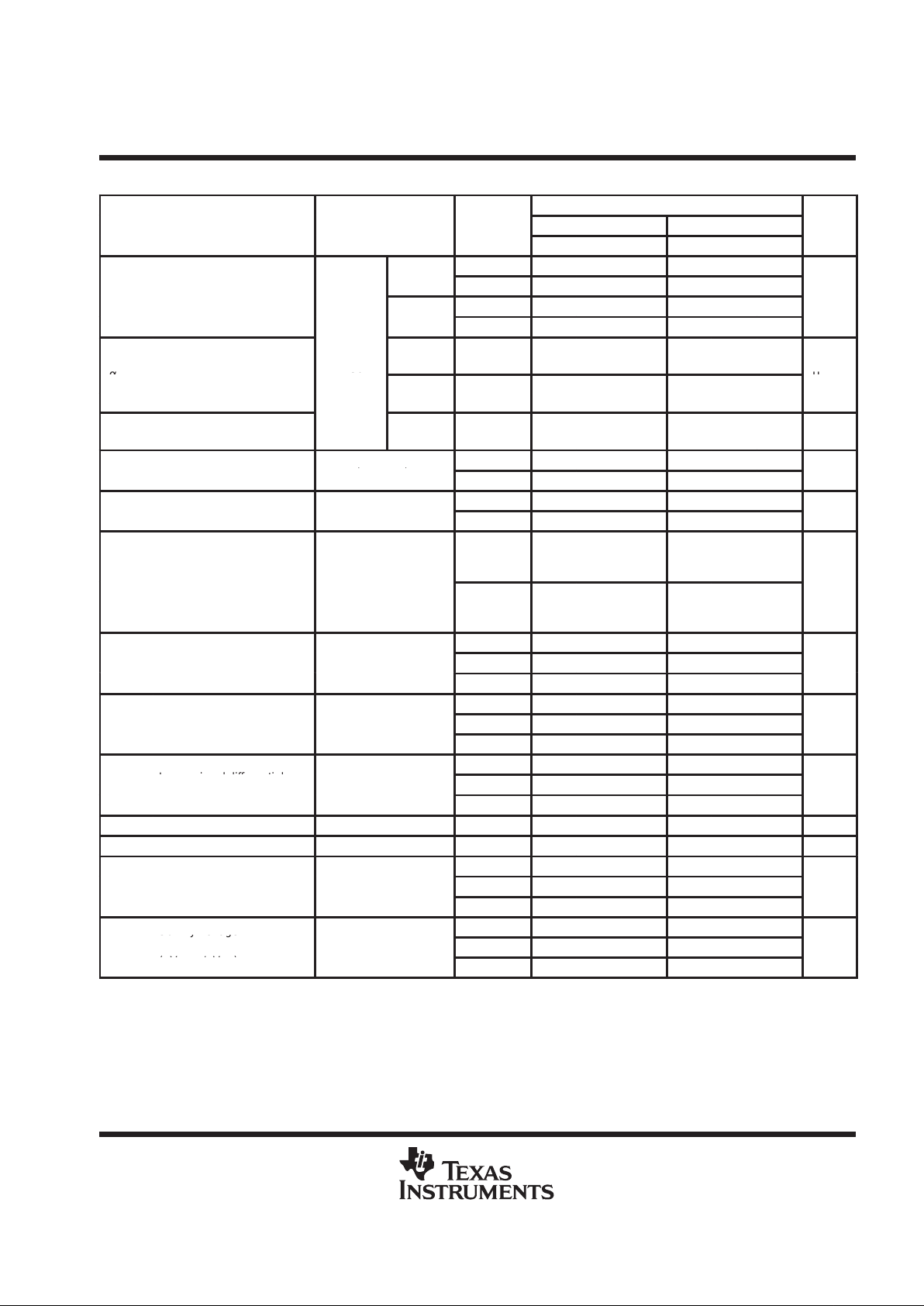

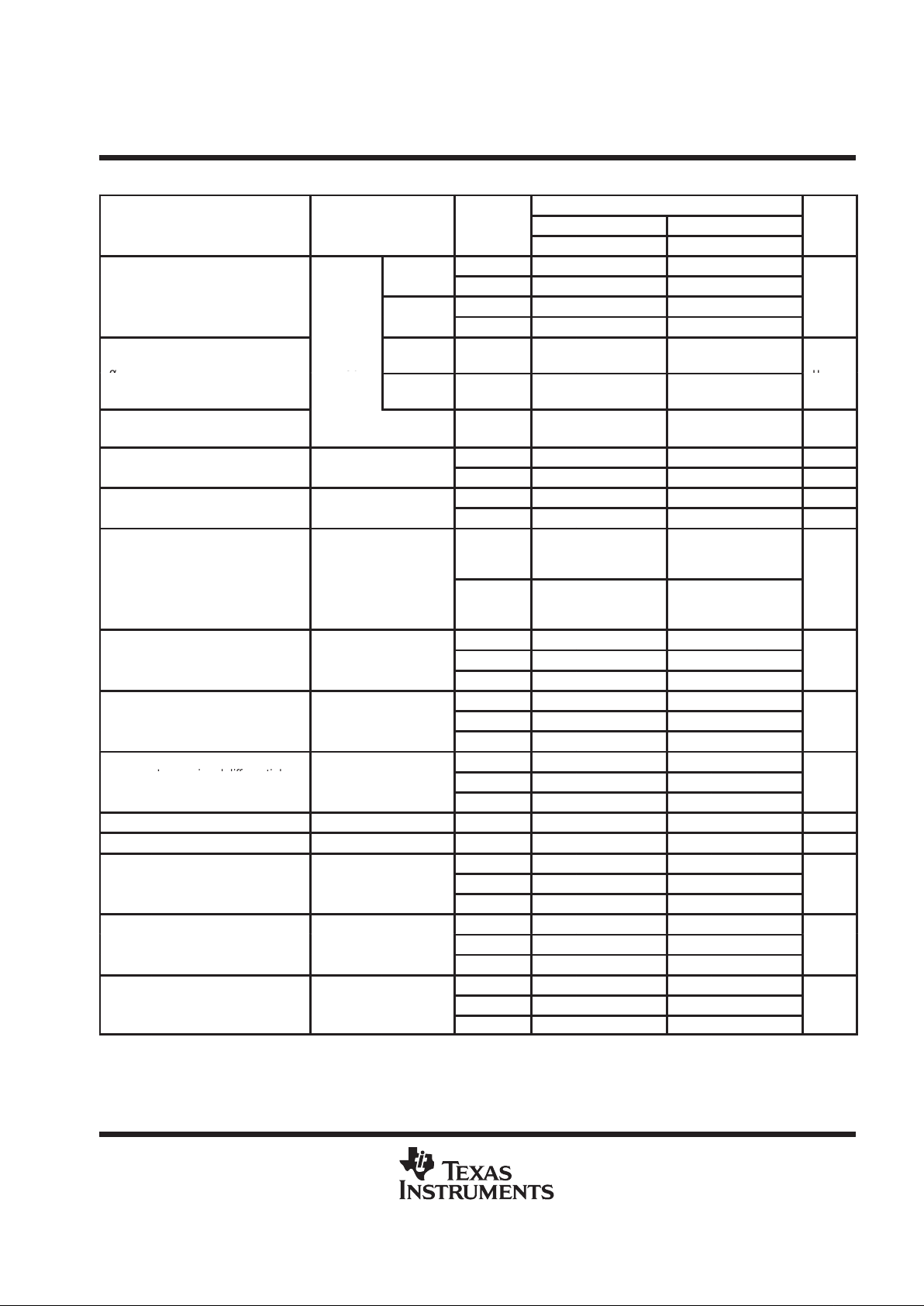

AVAILABLE OPTIONS

PACKAGED DEVICES

T

A

VIOMAX

AT 25°C

SMALL

OUTLINE

†

(D)

CHIP

CARRIER

(FK)

CERAMIC

DIP

(J)

CERAMIC

DIP

(JG)

PLASTIC

DIP

(N)

PLASTIC

DIP

(P)

TSSOP

†

(PW)

CHIP

FORM

‡

(Y)

0.8 mV

TL031ACD

TL032ACD

— — — —

TL031ACP

TL032ACP

—

0°C to 70°C

1.5 mV

TL031CD

TL032CD

TL034ACD

— — — TL034ACN

TL031CP

TL032CP

—

TL031Y

TL032Y

TL034Y

4 mV TL034CD — — — TL034CN TL034CPW

0.8 mV

TL031AID

TL032AID

— — — —

TL031AIP

TL032AIP

— —

–40°C to 85°C

1.5 mV

TL031ID

TL032ID

TL034AID

— — — TL034AIN

TL031IP

TL032IP

— —

4 mV TL034ID — — — TL034IN — — —

0.8 mV

TL031AMD

TL032AMD

TL031AMFK

TL032AMFK

—

TL031AMJG

TL032AMJG

—

TL031AMP

TL032AMP

— —

–55°C to 125°C

1.5 mV

TL031MD

TL032MD

TL034AMD

TL031MFK

TL032MFK

TL034AMFK

TL034AMJ

TL031MJG

TL032MJG

TL034AMN

TL031MP

TL032MP

— —

4 mV TL034MD TL034MFK TL034MJ — TL034MN — — —

†

The D and PW packages are available taped and reeled and are indicated by adding an R suffix to device type (e.g., TL034CDR or TL034CPWR).

‡

Chip forms are tested at 25°C.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

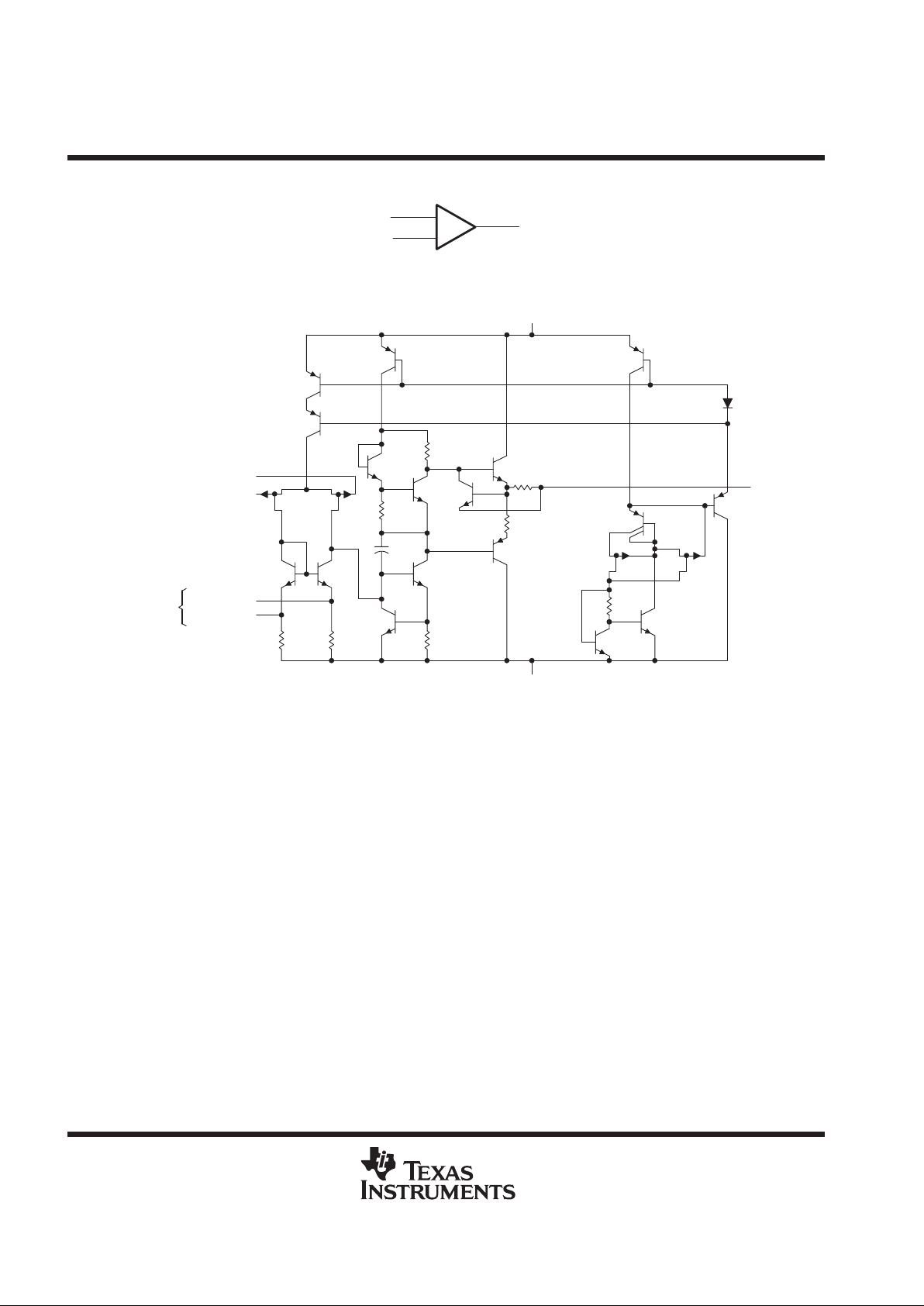

symbol (each amplifier)

–

+

OUT

IN–

IN+

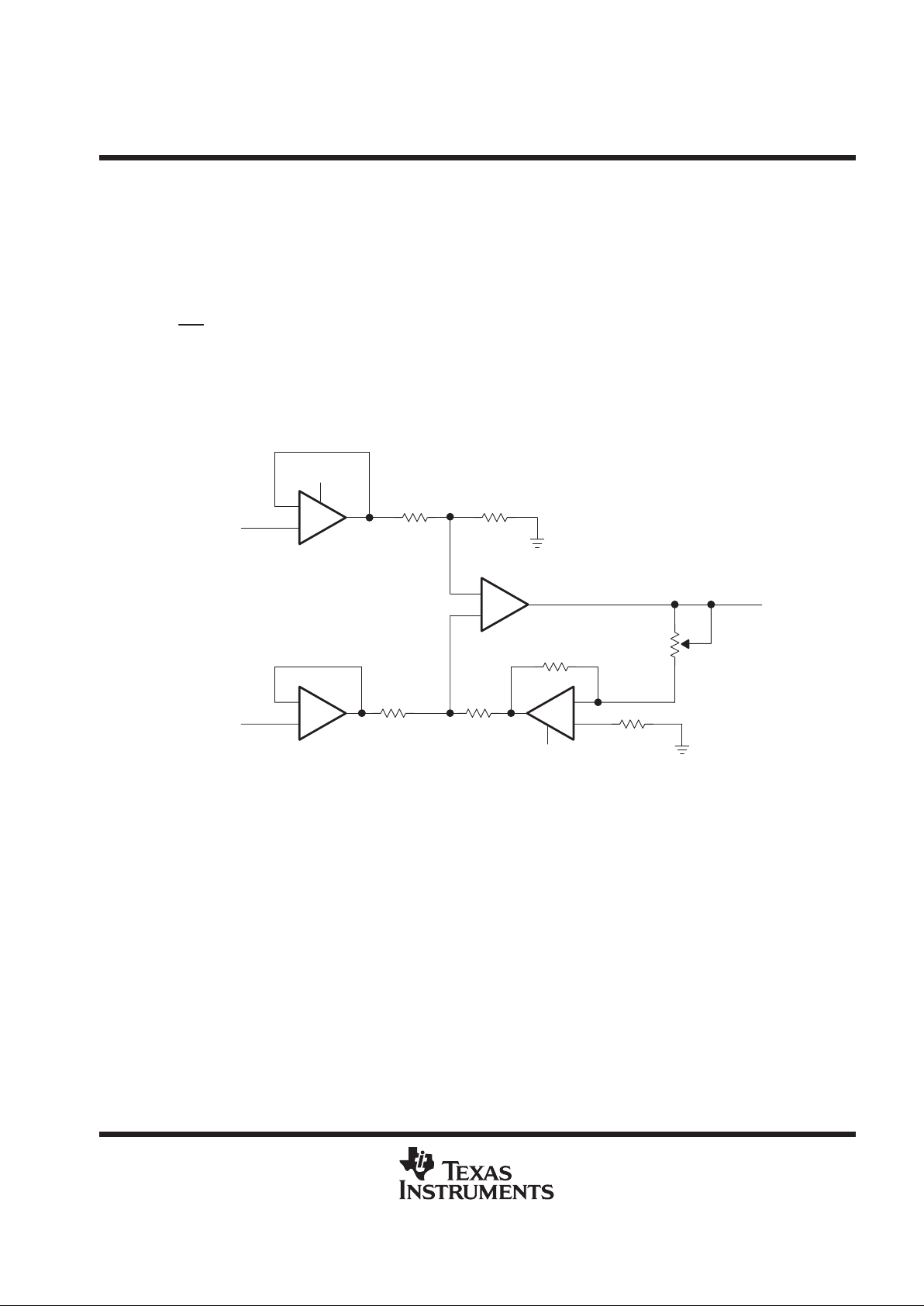

equivalent schematic (each amplifier)

R2

OFFSET N2

OFFSET N1

IN–

IN+

Q2

Q3

Q5

V

CC+

Q14

Q6

R4

Q8

Q10

R7

Q11

R6

Q12

R3

C1

Q9

Q7

Q4

R5R1

Q1

JF1 JF2

Q13

Q16

R8

JF3 JF4

Q15

Q17

OUT

D1

V

CC–

NOTE A: OFFSET N1 and OFFSET N2 are available only on the TL031.

(see Note A)

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

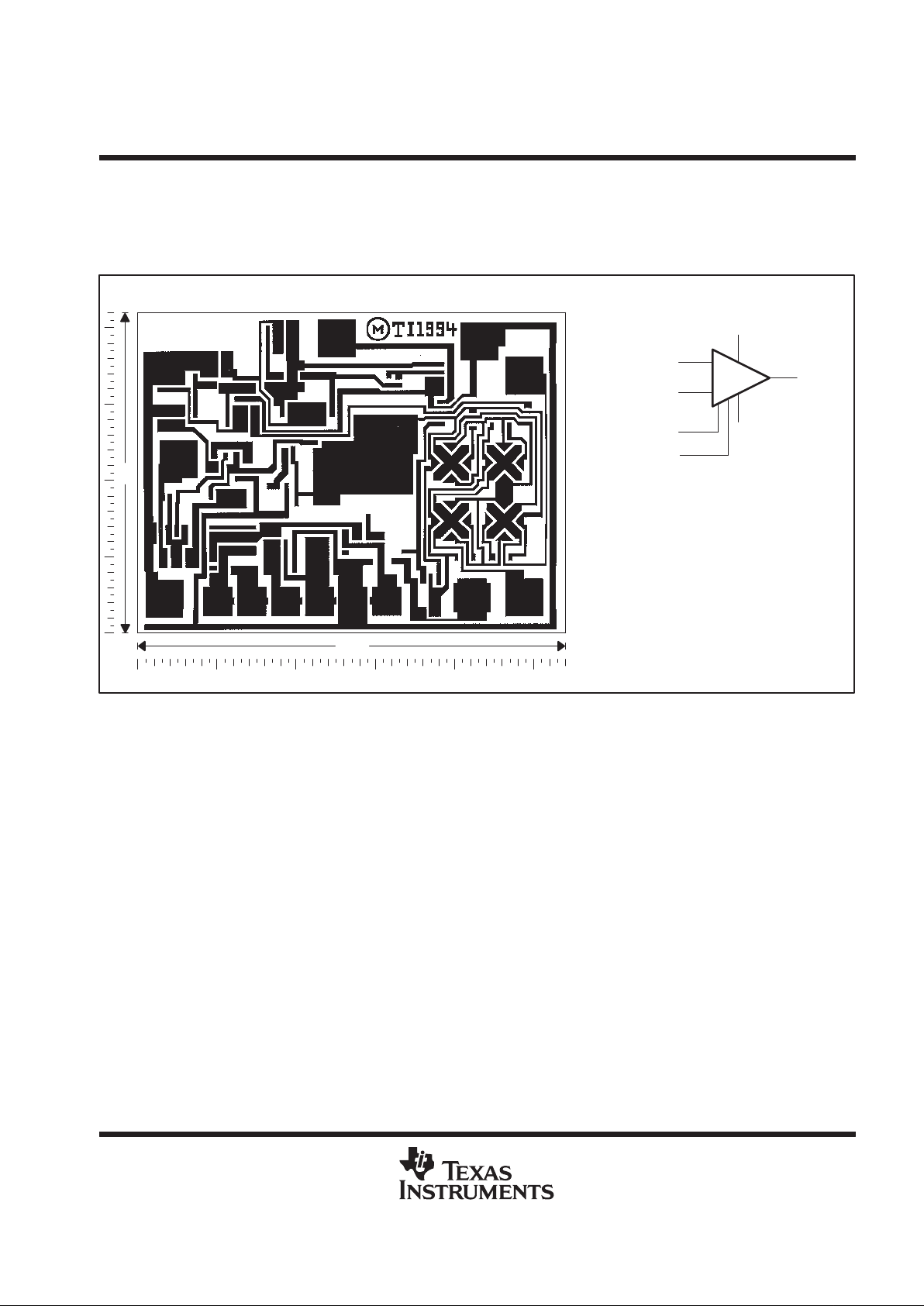

TL031Y chip information

This chip, when properly assembled, has characteristics similar to the TL031C. Thermal compression or

ultrasonic bonding can be used on the doped-aluminum bonding pads. These chips can be mounted with

conductive epoxy or a gold-silicon preform.

Bonding-Pad Assignments

54

42

Chip Thickness: 15 MIls Typical

Bonding Pads: 4 × 4 Mils Minimum

TJ(max) = 150°C

Tolerances Are ±10%.

All Dimensions Are in Mils.

Pin (4) is Internally Connected

to Backside of the Chip.

+

–

OUT

IN+

IN–

V

CC+

(7)

(3)

(2)

(6)

(1)

(4)

(5)

V

CC–

OFFSET N1

OFFSET N2

(1)

(2)

(3)

(4)

(6)

(7)

(8)

(5)

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

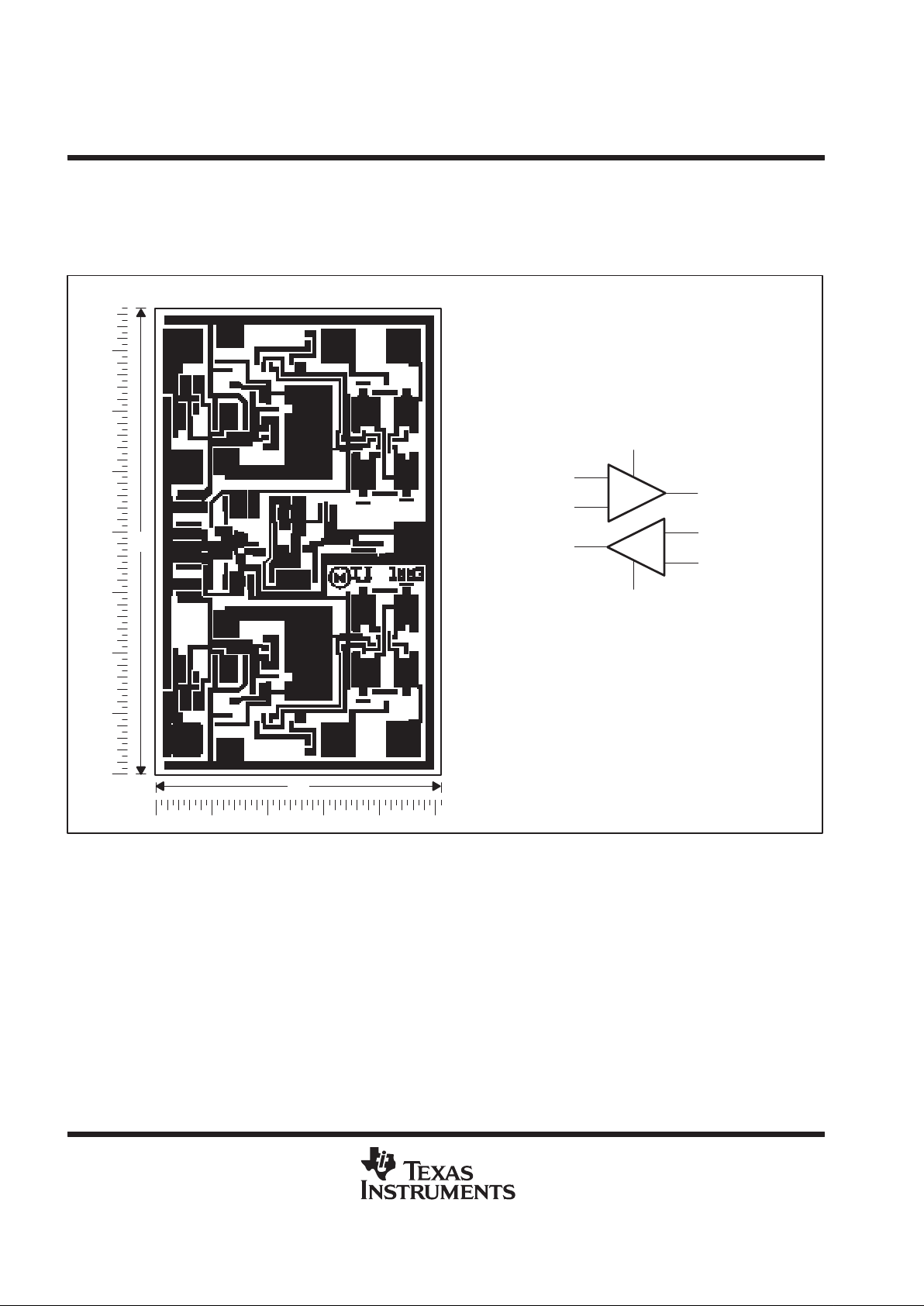

TL032Y chip information

This chip, when properly assembled, has characteristics similar to the TL032C. Thermal compression or

ultrasonic bonding can be used on the doped-aluminum bonding pads. These chips can be mounted with

conductive epoxy or a gold-silicon preform.

Bonding-Pad Assignments

Chip Thickness: 15 Mils Typical

Bonding Pads: 4 × 4 Mils Minimum

TJ(max) = 150°C

Tolerances Are ±10%.

All Dimensions Are in Mils.

Pin (4) is Internally Connected to Backside of Chip.

+

–

1OUT

1IN+

1IN–

V

CC+

(8)

(6)

(3)

(2)

(5)

(1)

–

+

(7)

2IN+

2IN–

2OUT

(4)

V

CC–

67

51

(6) (5)

(4)

(3)(2)(1)

(8)

(7)

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

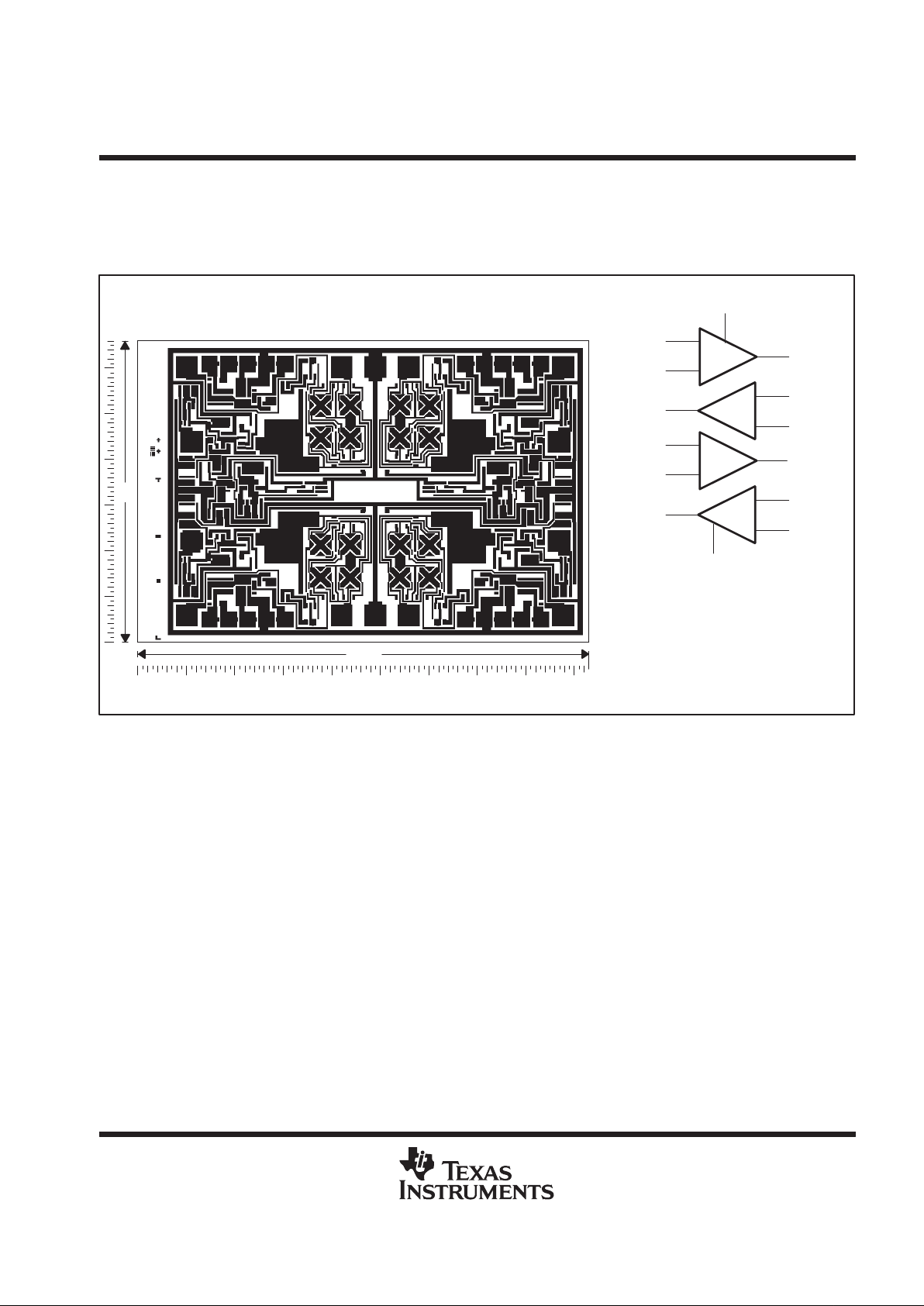

TL034Y chip information

This chip, when properly assembled, has characteristics similar to the TL034C. Thermal compression or

ultrasonic bonding can be used on the doped-aluminum bonding pads. These chips can be mounted with

conductive epoxy or a gold-silicon preform.

Bonding-Pad Assignments

+

–

1OUT

1IN+

1IN–

V

CC+

(4)

(6)

(3)

(2)

(5)

(1)

–

+

(7)

2IN+

2IN–

2OUT

(11)

V

CC–

+

–

3OUT

3IN+

3IN–

(13)

(10)

(9)

(12)

(8)

–

+

(14)

4OUT

4IN+

4IN–

(5)

(6)

(7)

(8)

(9)

(10)

93

66

(1)

(2) (3) (4) (5) (6)

(7)

(8)

(9)(10)(11)(12)(13)

(14)

Chip Thickness: 15 Mils Typical

Bonding Pads: 4 × 4 Mils Minimum

TJ(max) = 150°C

Tolerances Are ±10%.

All Dimensions Are in Mils.

Pin (11) is Internally Connected

to Backside of the Chip.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

†

Supply voltage, V

CC+

(see Note 1) 18 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply voltage, V

CC–

(see Note 1) –18 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Differential input voltage, V

ID

(see Note 2) ±30 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage, VI (any input) (see Notes 1 and 3) ±15 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input current, II (each input) ±1 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output current, IO (each output) ±40 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total current into V

CC+

160 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Total current out of V

CC–

160 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Duration of short-circuit current at (or below) 25°C (see Note 4) Unlimited. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous total power dissipation See Dissipation Rating Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range,T

stg

–65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Case temperature for 60 seconds: FK package 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1 /16 inch) from case for 10 seconds: D, N, P, or PW package 260°C. . . . . . . . .

Lead temperature 1,6 mm (1 /16 inch) from case for 60 seconds: J or JG package 300°C. . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to the midpoint between V

CC+

and V

CC–

.

2. Differential voltages are at IN+ with respect to IN–.

3. The magnitude of the input voltage must never exceed the magnitude of the supply voltage or 15 V, whichever is less.

4. The output may be shorted to either supply. Temperature and/or supply voltages must be limited to ensure that the maximum

dissipation rating is not exceeded.

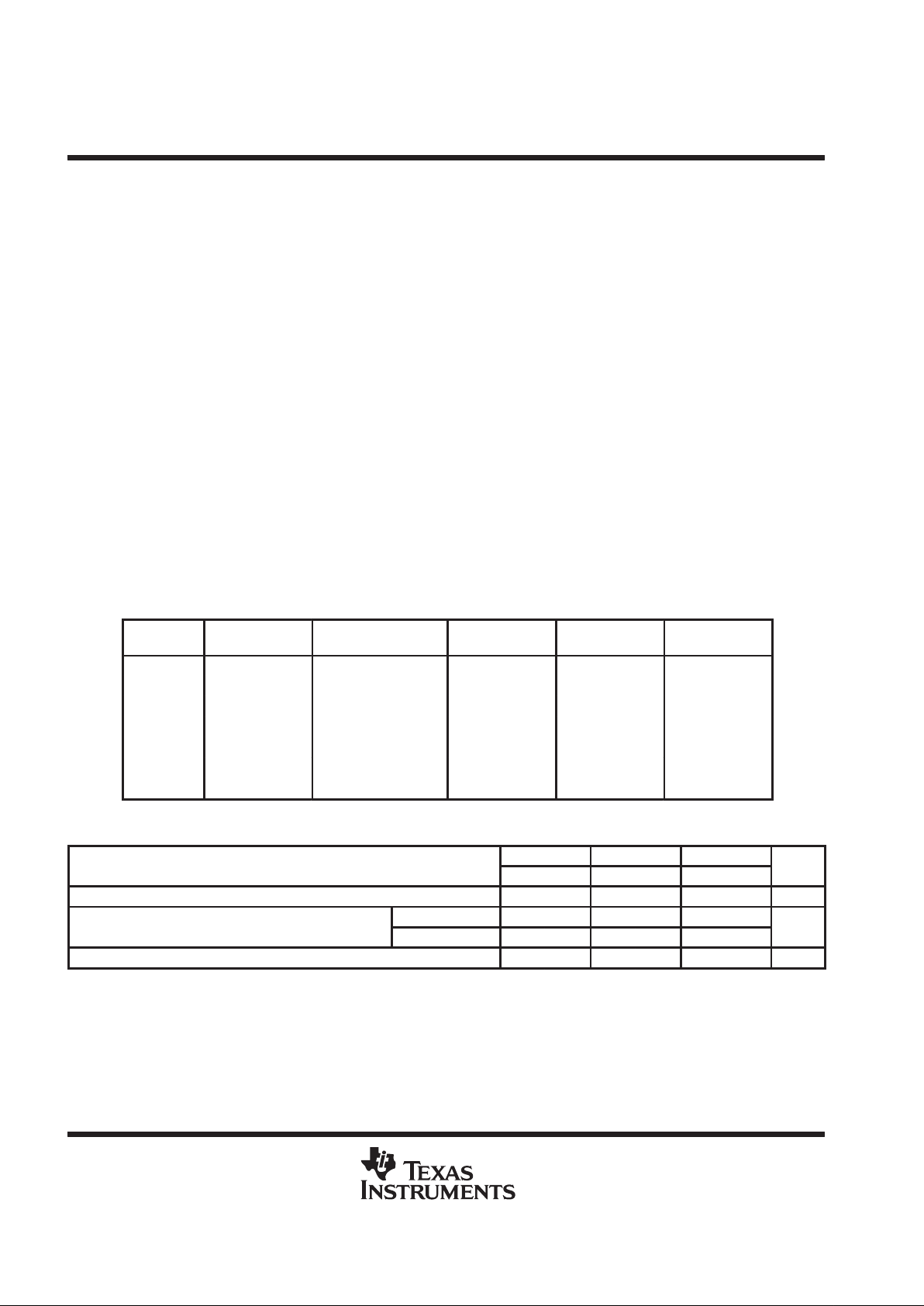

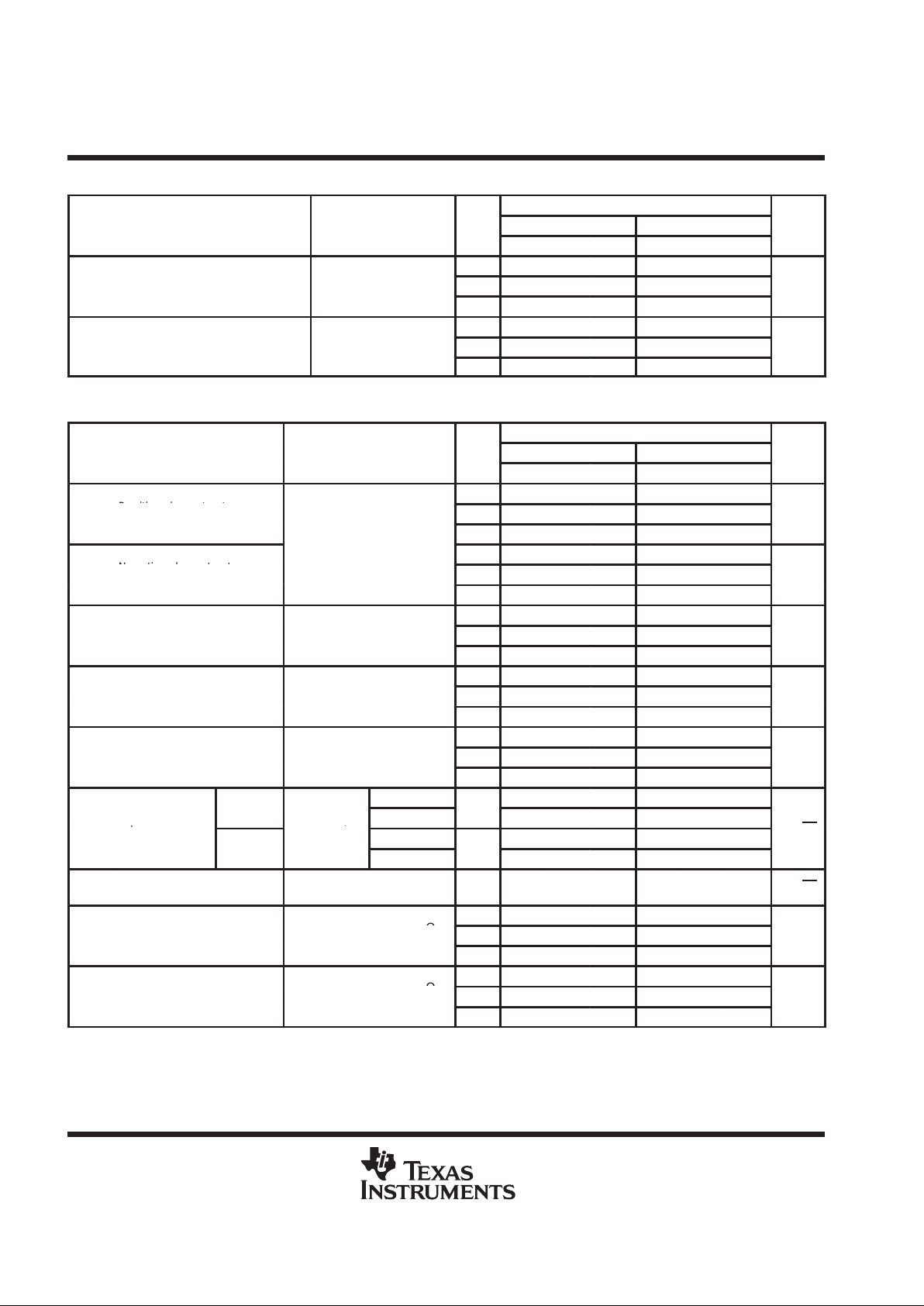

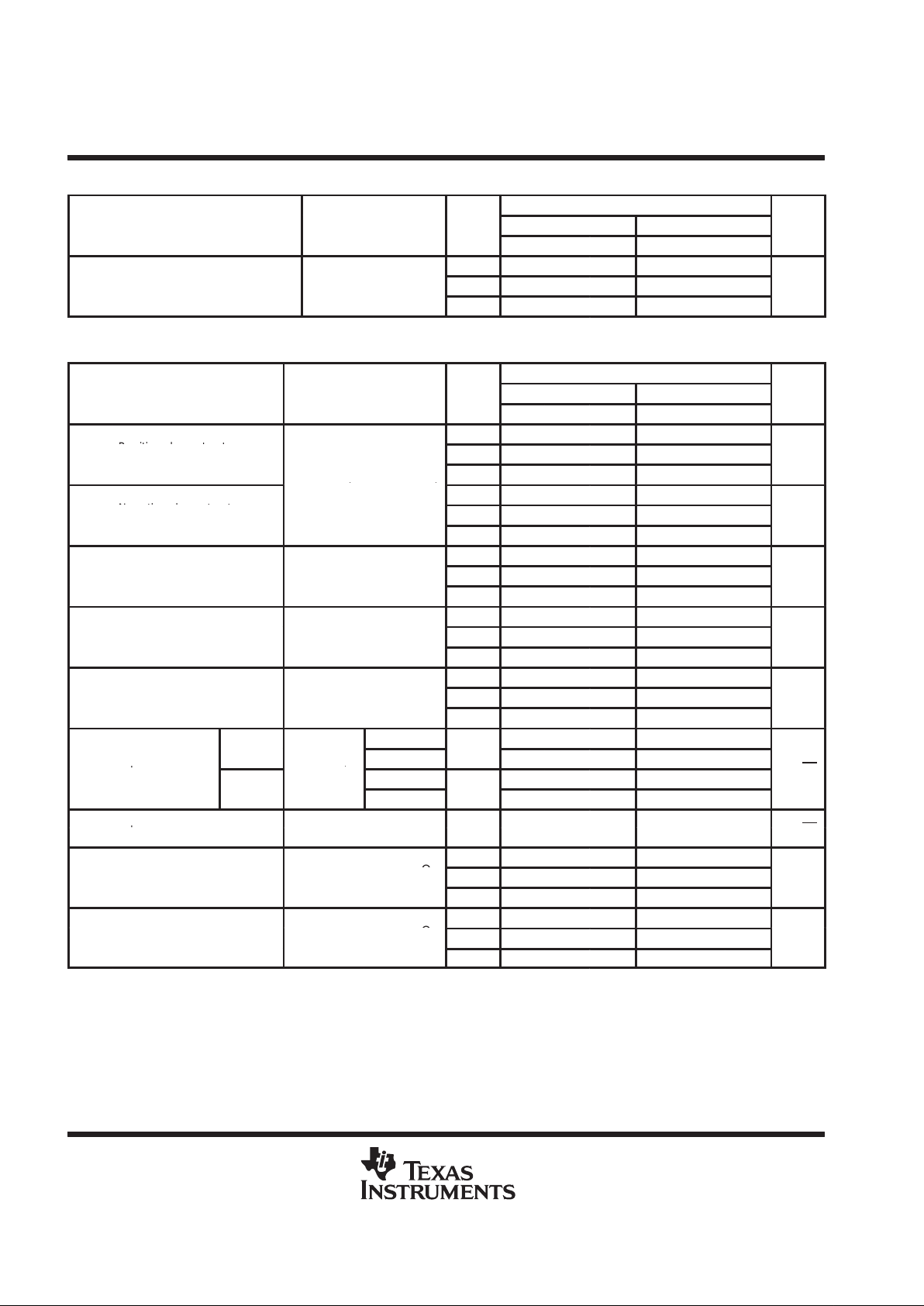

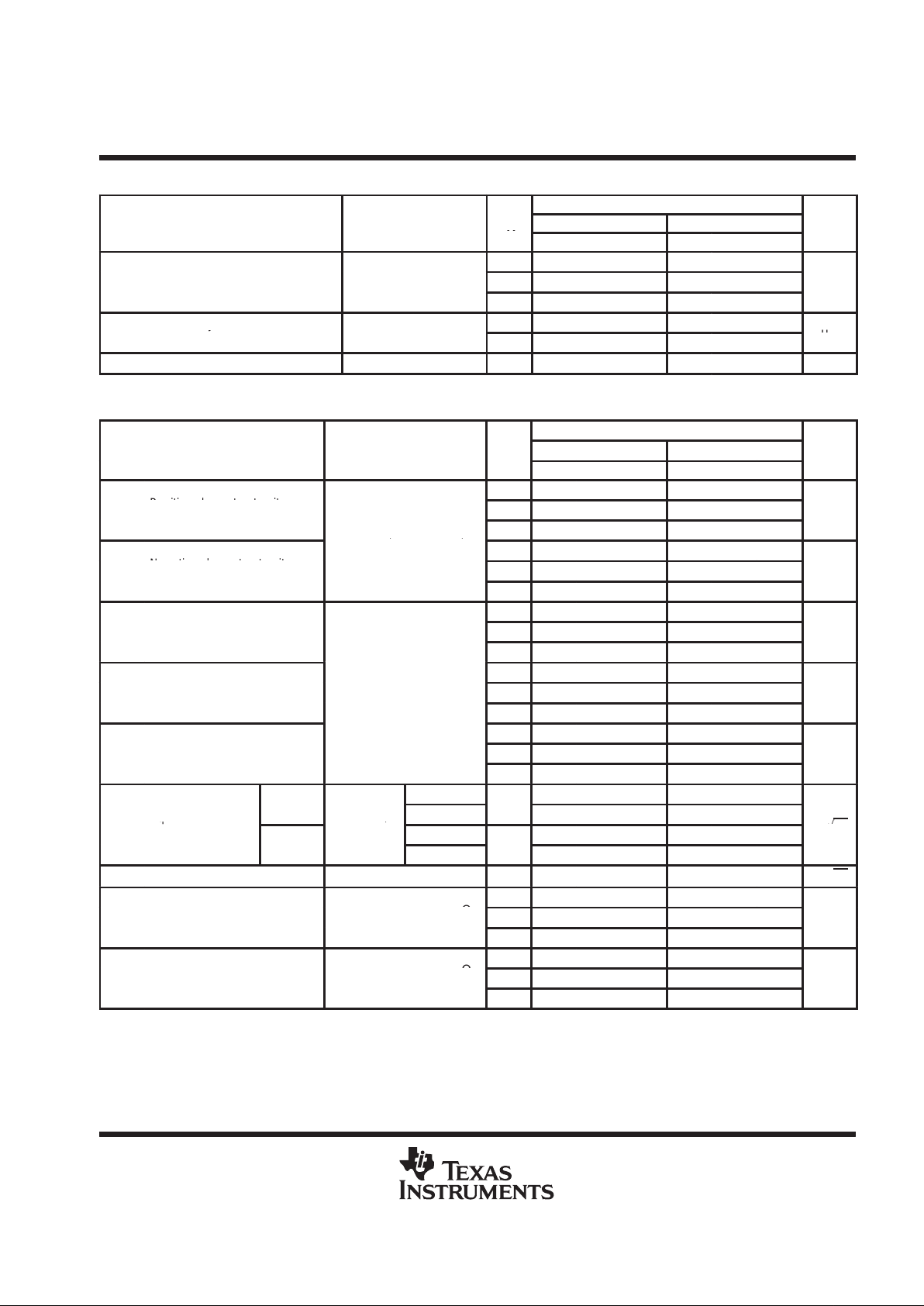

DISSIPATION RATING TABLE

PACKAGE

TA ≤ 25°C

POWER RATING

DERATING FACTOR

ABOVE TA = 25°C

TA = 70°C

POWER RATING

TA = 85°C

POWER RATING

TA = 125°C

POWER RATING

D 950 mW 7.6 mW/°C 608 mW 494 mW 190 mW

FK 1375 mW 11.0 mW/°C 880 mW 715 mW 275 mW

J 1375 mW 11.0 mW/°C 880 mW 715 mW 275 mW

JG 1050 mW 8.4 mW/°C 672 mW 546 mW 210 mW

N 1150 mW 9.2 mW/°C 736 mW 598 mW 230 mW

P 1100 mW 8.0 mW/°C 640 mW 520 mW 200 mW

PW 700 mW 5.6 mW/°C 448 mW N/A N/A

recommended operating conditions

C SUFFIX I SUFFIX M SUFFIX

MIN MAX MIN MAX MIN MAX

UNIT

Supply voltage, V

CC±

±5 ±15 ±5 ±15 ±5 ±15 V

p

V

CC±

= ±5 V –1.5 4 –1.5 4 –1.5 4

Common-mode input voltage, V

IC

V

CC±

= ±15 V –11.5 14 –11.5 14 –11.5 14

V

Operating free-air temperature, T

A

0 70 –40 85 –55 125 °C

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

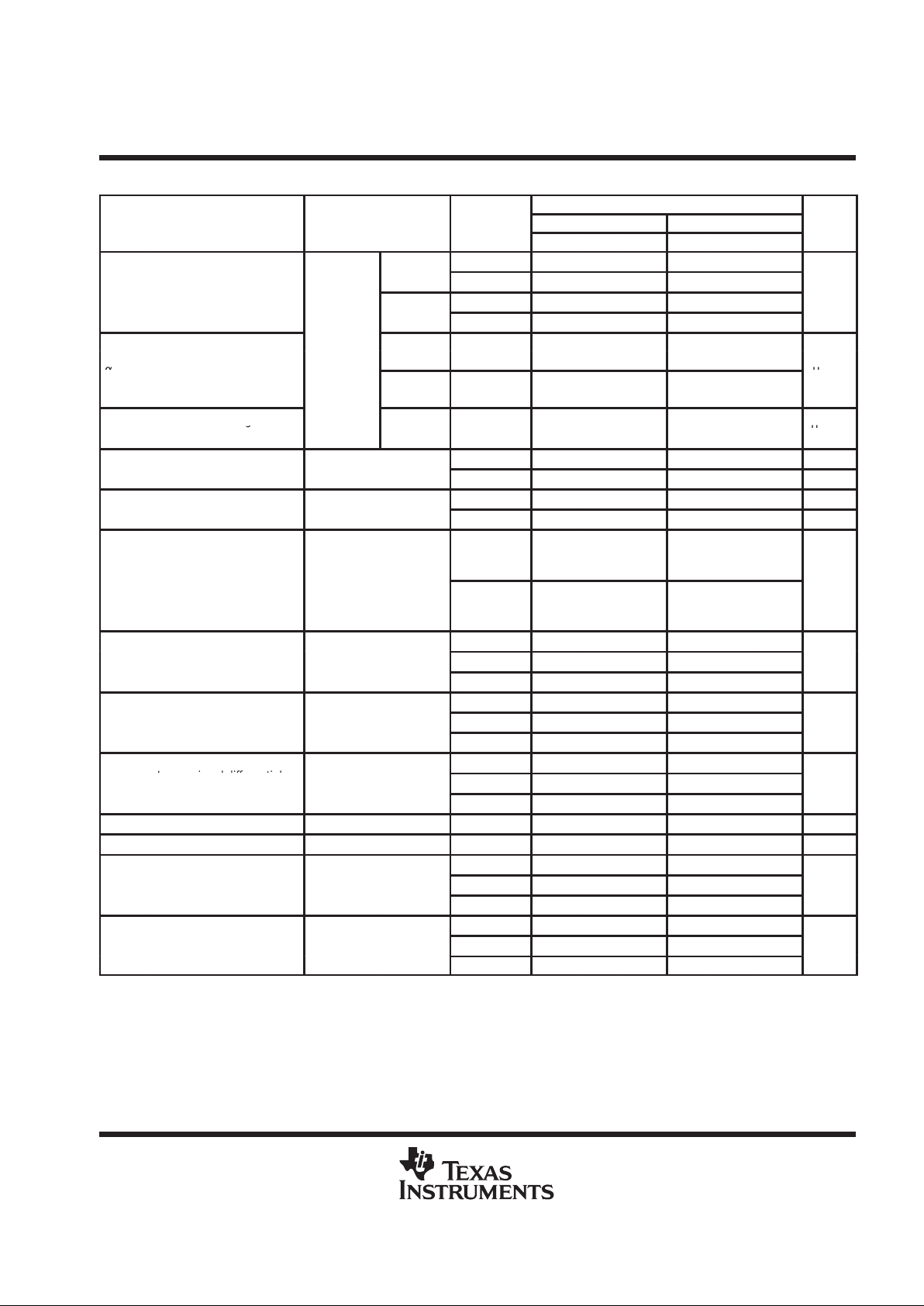

TL031C and TL031AC electrical characteristics at specified free-air temperature

TL031C, TL031AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.54 3.5 0.5 1.5

p

TL031C

Full range† 4.5 2.5

VIOInput offset voltage

25°C 0.41 2.8 0.34 0.8

mV

TL031AC

Full range† 3.8 1.8

V

O

= 0,

25°C to

T emperature coef ficient of

V

IC

= 0,

R

= 50 Ω

TL031C

70°C

7.1

5.9

°

α

VIO

input offset voltage

R

S

50

Ω

25°C to

µ

V/°C

TL031AC

70°C

7.1

5.9

25

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 1 100 1 100

p

IIOInput offset current

O

,

IC

,

See Figure 5

70°C 9 200 12 200

pA

p

V

= 0, V

= 0,

25°C 2 200 2 200

p

IIBInput bias current

O

,

IC

,

See Figure 5

70°C 50 400 80 400

pA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

.4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

0°C 3 4.2 13 14

V

out ut voltage swing

70°C 3 4.3 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative peak

p

RL = 10 kΩ

0°C –3 –4.1 –12.5 –13.9

V

out ut voltage swing

70°C –3 –4.2 –12.5 –14

25°C 4 12 5 14.3

A

VD

Large-signal differential

p

§

RL = 10 kΩ

0°C 3 11.1 4 13.5

V/mV

voltage am lification

§

70°C 4 13.3 5 15.2

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 4 pF

25°C 70 87 75 94

CMRR

Common-mode

VIC = V

ICR

min,

0°C 70 87 75 94

dB

rejection ratio

V

O

= 0,

R

S

= 50

Ω

70°C 70 87 75 94

Supply-voltage

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

VO = 0, RS = 50 Ω

0°C 75 96 75 96

dB

(∆V

CC±

/∆VIO)

70°C 75 96 75 96

†

Full range is 0°C to 70°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL031C and TL031AC electrical characteristics at specified free-air temperature (continued)

TL031C, TL031AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 1.9 2.5 6.5 8.4

P

D

Total power dissipation VO = 0, No load

0°C

1.8 2.5 6.3 8.4

mW

70°C 1.9 2.5 6.3 8.4

25°C 192 250 217 280

I

CC

Supply current VO = 0, No load

0°C

184 250 211 280

µA

70°C 189 250 210 280

TL031C and TL031AC operating characteristics at specified free-air temperature

TL031C, TL031AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 2 1.5 2.9

SR+

Positive slew rate at

†

0°C 1.8 1 2.6

V/µs

unity gain

†

R

= 10 kΩ, C

= 100 pF,

70°C

2.2 1.5 3.2

L

,

See Figure 1

L

,

25°C 3.9 1.5 5.1

SR–

Negative slew rate at

†

0°C 3.7 1.5 5

V/µs

unity gain

†

70°C 4 1.5 5

V

I(PP)

= ±10 mV , 25°C 138 132

t

r

Rise time

RL = 10 kΩ,

CL = 100 pF, 0°C 134 127

ns

See Figures 1 and 2 70°C 150 142

V

I(PP)

= ±10 mV , 25°C 138 132

t

f

Fall time

RL = 10 kΩ,

CL = 100 pF, 0°C 134 127

ns

See Figure 1 70°C 150 142

V

I(PP)

= ±10 mV , 25°C 11% 5%

Overshoot factor

CL = 100 pF,

CL = 100 pF, 0°C 10% 4%

See Figures 1 and 2 70°C 12% 6%

f = 10 Hz

°

61 61

Equivalent input

TL031C

R

= 20 Ω,

f = 1 kHz

25°C

41 41

V

n

q

noise voltage

S

,

See Figure 3

f = 10 Hz

°

61 61

n

V/√H

z

TL031AC

f = 1 kHz

25°C

41 41 60

I

n

Equivalent input noise

current

f = 1 kHz 25°C 0.003 0.003

pA/√Hz

25°C 1 1.1

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 10 kΩ,

0°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

70°C 1 1

25°C 61° 65°

φ

m

Phase margin at unity gain

V

I

= 10 mV,

=

p

R

L

= 10

kΩ

,

0°C 61° 65°

C

L

= 25 F,

See Figure 4

70°C 60° 64°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL031I and TL031AI electrical characteristics at specified free-air temperature

TL031I, TL031AI

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.54 3.5 0.5 1.5

p

TL031I

Full range

†

5.3 3.3

VIOInput offset voltage

25°C 0.41 2.8 0.34 0.8

mV

TL031AI

Full range

†

4.6 2.6

VO = 0,

25°C to

T emperature coef ficient of

V

IC

= 0,

R

= 50 Ω

TL031I

85°C

6.5

6.2

°

α

VIO

input offset voltage

R

S

= 50

Ω

25°C to

µ

V/°C

TL031AI

85°C

6.5

6.2

25

Input offset voltage

°

g

long-term drift

‡

25°C

0.04

0.04µV/mo

p

VO = 0, VIC = 0, 25°C 1 100 1 100 pA

IIOInput offset current

See Figure 5 85°C 0.02 0.45 0.02 0.45 nA

p

VO = 0, VIC = 0, 25°C 2 200 2 200 pA

IIBInput bias current

See Figure 5 85°C 0.2 0.9 0.2 0.9 nA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

–40°C 3 4.1 13 14

V

out ut voltage swing

85°C 3 4.4 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative peak

p

RL = 10 kΩ

–40°C –3 –4.1 –12.5 –13.8

V

out ut voltage swing

85°C –3 –4.2 –12.5 –14

25°C 4 12 5 14.3

A

VD

Large-signal differential

p

§

RL = 10 kΩ

–40°C 3 8.4 4 11.6

V/mV

voltage am lification

§

85°C 4 13.5 5 15.3

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 4 pF

25°C 70 87 75 94

CMRR

Common-mode

V

IC =

V

ICR

min

,

–40°C 70 87 75 94

dB

rejection ratio

VO = 0, RS = 50 Ω 85°C 70 87 75 94

pp

-

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

VO = 0,

RS = 50 Ω

–40°C

75 96 75 96

dB

(∆V

CC±

/∆VIO)

85°C 75 96 75 96

†

Full range is –40°C to 85°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL031I and TL031AI electrical characteristics at specified free-air temperature (continued)

TL031I, TL031AI

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 1.9 2.5 6.5 8.4

P

D

Total power dissipation VO = 0, No load

–40°C

1.4 2.5 5.4 8.4

mW

85°C 1.9 2.5 6.2 8.4

25°C 192 250 217 280

I

CC

Supply current VO = 0, No load

–40°C

144 250 181 280

µA

85°C 189 250 207 280

TL031I and TL031AI operating characteristics at specified free-air temperature

TL031I, TL031AI

PARAMETER TEST CONDITIONS T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 2 1.5 2.9

SR+

Positive slew rate at

†

–40°C 1.6 1 2.1

V/µs

unity gain

†

R

= 10 kΩ C

= 100 pF,

85°C

2.3 1.5 3.3

L

See Figure 1

L

,

25°C 3.9 1.5 5.1

SR–

Negative slew rate at unity

†

–40°C 3.3 1.5 4.8

V/µs

gain

†

85°C 4.1 1.5 4.9

V

I(PP)

= ±10 mV , 25°C 138 132

t

r

Rise time

RL = 10 kΩ,

CL = 100 pF, –40°C 132 123

ns

See Figures 1 and 2 85°C 154 146

V

I(PP)

= ±10 mV , 25°C 138 132

t

f

Fall time

RL = 10 kΩ,

CL = 100 pF, –40°C 132 123

ns

See Figure 1 85°C 154 146

V

I(PP)

= ±10 mV , 25°C 11% 5%

Overshoot factor

RL = 10 kΩ,

CL = 100 pF, –40°C 12% 5%

See Figures 1 and 2 85°C 13% 7%

f = 10 Hz

°

61 61

Equivalent

TL031I

R

= 20 Ω,

f = 1 kHz

25°C

41 41

V

n

i

npu

t

S

,

See Figure 3

f = 10 Hz

°

61 61

n

V/√H

z

noise voltage

TL031AI

f = 1 kHz

25°C

41 41 60

Equivalent input noise

°

I

n

q

current

f

= 1 kHz

25°C

0.003

0.003

p

A/√H

z

25°C 1 1.1

B

1

Unity-gain bandwidth

VI = 10 mV

p

RL = 10 kΩ,

–40°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

85°C 0.9 1

25°C 61° 65°

φ

m

Phase margin at unity gain

V

I

= 10 mV,

=

p

R

L

= 10 kΩ,

–40°C 60° 65°

C

L

= 25

F

See Figure 4

85°C 60° 64°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL031M and TL031AM electrical characteristics at specified free-air temperature

TL031M, TL031AM

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.54 3.5 0.5 1.5

p

TL031M

Full range

†

6.5 4.5

VIOInput offset voltage

25°C 0.41 2.8 0.34 0.8

mV

TL031AM

Full range

†

5.8 3.8

T emperature coef ficient of

V

O

=

0

,

VIC = 0,

R

= 50 Ω

TL031M

25°C to

125°C

5.1 4.3

°

α

VIO

input offset voltage

R

S

50

Ω

TL031AM

25°C to

125°C

5.1 4.3

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

VO = 0, VIC = 0, 25°C 1 100 1 100 pA

IIOInput offset current

See Figure 5 125°C 0.2 10 0.2 10 nA

p

VO = 0, VIC = 0, 25°C 2 200 2 200 pA

IIBInput bias current

See Figure 5 125°C 7 20 8 20 nA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

–55°C 3 4.1 13 14

V

out ut voltage swing

125°C 3 4.4 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative peak

p

RL = 10 kΩ

–55°C –3 –4 –12.5 –13.8

V

out ut voltage swing

125°C –3 –4.3 –12.5 –14

25°C 4 12 5 14.3

A

VD

Large-signal differential

p

§

RL = 10 kΩ

–55°C 3 7.1 4 10.4

V/mV

voltage am lification

§

125°C 3 12.9 4 15

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 4 pF

25°C 70 87 75 94

CMR

Common-mode

VIC = V

ICR

min,

–55°C 70 87 70 94

dB

R

rejection ratio

V

O

= 0,

R

S

= 50

Ω

125°C 70 87 70 94

pp

-

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

VO = 0,

RS = 50 Ω

–55°C

75 96 75 95

dB

(∆V

CC±

/∆VIO)

125°C 75 96 75 96

25°C 1.9 2.5 6.5 8.4

P

D

Total power dissipation VO = 0, No load

–55°C

1.1 2.5 4.7 8.4

mW

125°C 1.8 2.5 5.8 8.4

†

Full range is –55°C to 125°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

14

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL031M and TL031AM electrical characteristics at specified free-air temperature (continued)

TL031M, TL031AM

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 192 250 217 280

I

CC

Supply current VO = 0, No load

–55°C

114 250 156 280

µA

125°C 178 250 197 280

TL031M and TL031AM operating characteristics at specified free-air temperature

TL031M, TL031AM

PARAMETER TEST CONDITIONS T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 2 1.5 2.9

SR+

Positive slew rate at

†

–55°C 1.4 1 1.9

V/µs

unity gain

†

R

= 10 kΩ, C

= 100 pF,

125°C

2.4 1 3.5

L

,

See Figure 1

L

,

25°C 3.9 1.5 5.1

SR–

Negative slew rate at

†

–55°C 3.2 1 4.6

V/µs

unity gain

†

125°C 4.1 1 4.7

V

I(PP)

= ±10 mV , 25°C 138 132

t

r

Rise time

RL = 10 kΩ,

CL = 100 pF, –55°C 142 123

ns

See Figures 1 and 2 125°C 166 158

V

I(PP)

= ±10 mV , 25°C 138 132

t

f

Fall time

RL = 10 kΩ,

CL = 100 pF, –55°C 142 123

ns

See Figure 1 125°C 166 158

V

I(PP)

= ±10 mV , 25°C 11% 5%

Overshoot factor

RL = 10 kΩ,

CL = 100 pF, –55°C 16% 6%

See Figures 1 and 2 125°C 14% 8%

f = 10 Hz

°

61 61

Equivalent input

TL031M

R

= 20 Ω,

f = 1 kHz

25°C

41 41

V

n

q

noise voltage

S

,

See Figure 3

f = 10 Hz

°

61 61

n

V/√H

z

TL031AM

f = 1 kHz

25°C

41 41

Equivalent input noise

°

I

n

q

current

f

= 1 kHz

25°C

0.003

0.003

p

A/√H

z

25°C 1 1.1

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 10 kΩ,

–55°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

125°C 0.9 0.9

25°C 61° 65°

φ

m

Phase margin at unity gain

VI = 10 mV,

p

RL = 10 kΩ,

–55°C 57° 64°

C

L

= 25 F,

See Figure 4

125°C 59° 62°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

15

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

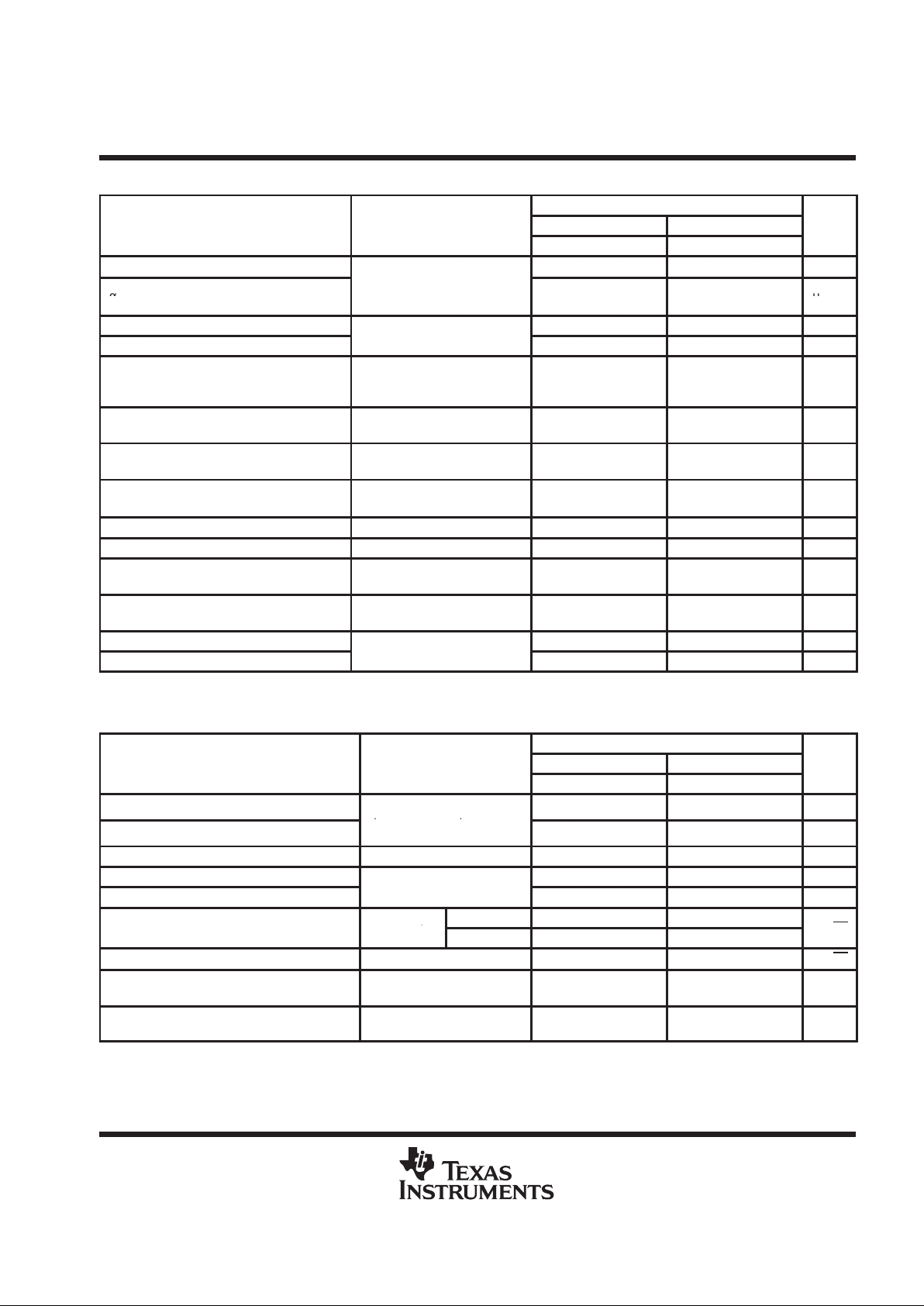

TL031Y electrical characteristics, TA = 25°C

TL031Y

PARAMETER TEST CONDITIONS

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

V

IO

Input offset voltage

0.54 0.5 mV

T emperature coef ficient of

V

O

= 0,

=

V

IC

= 0,

°

α

VIO

input offset voltage

R

S

= 50

Ω

7.1

5.9µV/°C

I

IO

Input offset current

V

= 0, V

= 0,

1 1 pA

I

IB

Input bias current

O

,

See Figure 5

IC

,

2 2 pA

V

ICR

Common-mode input voltage

range

–3.4

to

5.4

–13.4

to

15.4

V

V

OM+

Maximum positive peak

output voltage swing

RL = 10 kΩ 4.3 14 V

V

OM–

Maximum negative peak

output voltage swing

RL = 10 kΩ –4.2 –13.9 V

A

VD

Large-signal differential

voltage amplification

†

RL = 10 kΩ 12 14.3 V/mV

r

i

Input resistance 10

12

10

12

Ω

c

i

Input capacitance 5 4 pF

CMRR Common-mode rejection ratio

VIC = V

ICR

min,

RS = 50 Ω

VO = 0,

87 94 dB

k

SVR

Supply-voltage rejection ratio

(∆V

CC±

/∆VIO)

VO = 0, RS = 50 Ω 96 96 dB

P

D

Total power dissipation

1.9 6.5 mW

I

CC

Supply current

V

O

= 0,

No load

192 217 µA

†

At V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL031Y operating characteristics, TA = 25°C

TL031Y

PARAMETER TEST CONDITIONS

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

SR+

Positive slew rate at unity gain

‡

RL = 10 kΩ,pRL = 10 kΩ,

p

2 2.9 V/µs

SR–

Negative slew rate at unity gain

‡

C

L

=

100 pF

,

See Figure 1

C

L

=

100 pF

,

See Figure 1

3.9 5.1 V/µs

t

r

Rise time V

I(PP)

= ±10 mV , 138 132 ns

t

f

Fall time RL = 10 kΩ, CL = 100 pF, 138 132 ns

Overshoot factor See Figures 1 and 2 11% 5%

R

= 20 Ω,

f = 10 Hz 61 61

V

n

Equival

ent input noise voltage

S

,

See Figure 3

f = 1 kHz 41 41

n

V/√H

z

I

n

Equivalent input noise current f = 1 kHz 0.003 0.003

pA/√Hz

B

1

Unity-gain bandwidth

VI = 10 mV,

CL = 25 pF,

RL = 10 kΩ,

See Figure 4

1 1.1 MHz

φ

m

Phase margin at unity gain

VI = 10 mV,

CL = 25 pF,

RL = 10 kΩ,

See Figure 4

61° 65°

‡

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

16

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

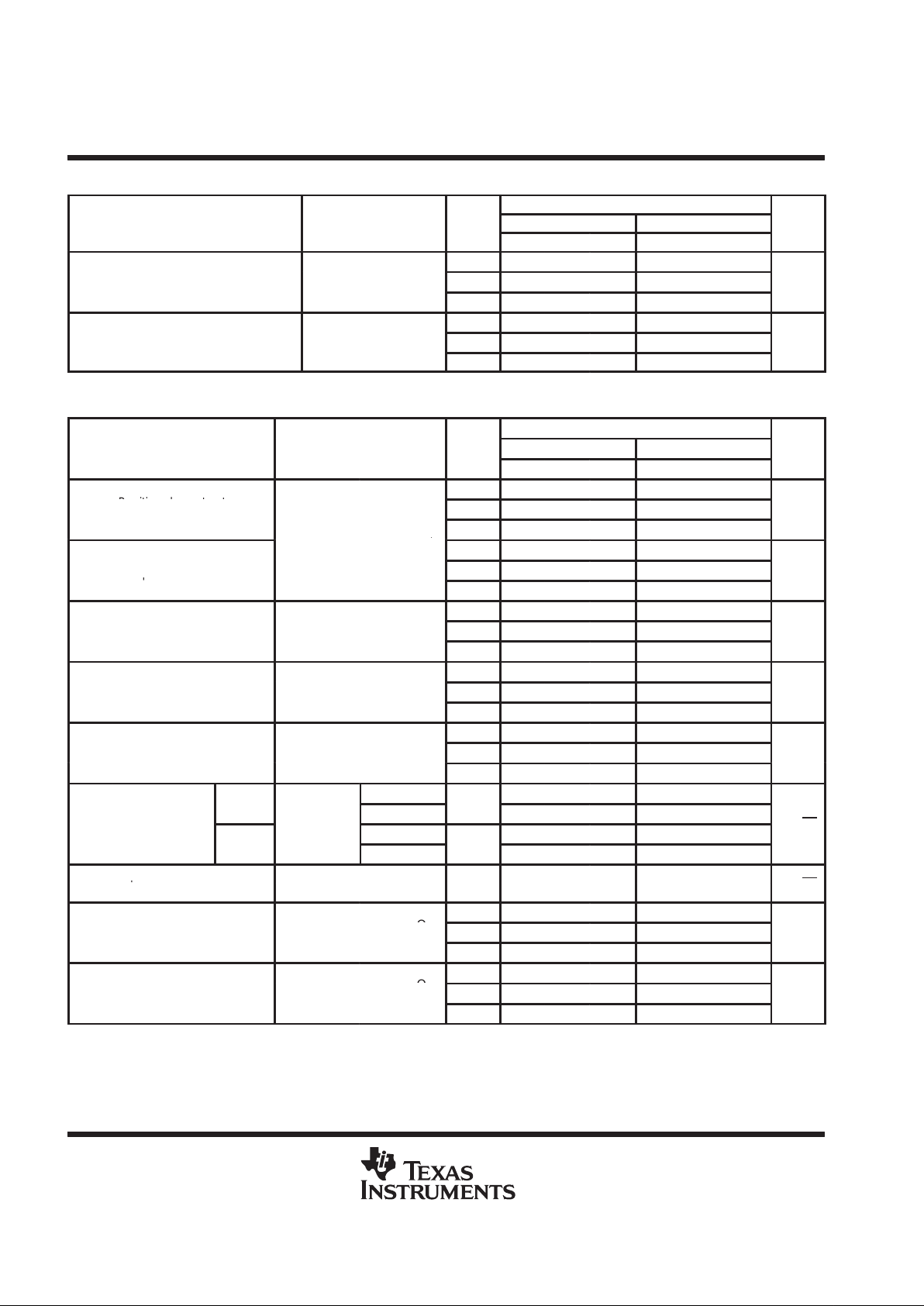

TL032C and TL032AC electrical characteristics at specified free-air temperature

TL032C, TL032AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V

UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.69 3.5 0.57 1.5

p

TL032C

Full range

†

4.5 2.5

VIOInput offset voltage

25°C 0.53 2.8 0.39 0.8

mV

TL032AC

Full range

†

3.8 1.8

T emperature coef ficient

V

O

=

0

,

VIC = 0,

R

= 50 Ω

TL032C

25°C to

70°C

11.5 10.8

°

α

VIO

of input offset voltage

R

S

50

Ω

TL032AC

25°C to

70°C

11.5 10.8 25

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 1 100 1 100

p

IIOInput offset current

O

,

See Figure 5

IC

,

70°C 9 200 12 200

pA

p

V

= 0, V

= 0,

25°C 2 200 2 200

p

IIBInput bias current

O

,

See Figure 5

IC

,

70°C 50 400 80 400

pA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

0°C 3 4.2 13 14

V

out ut voltage swing

70°C 3 4.3 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative

peak output voltage

RL = 10 kΩ

0°C –3 –4.1 –12.5 –13.9

V

swing

70°C –3 –4.2 –12.5 –14

25°C 4 12 5 14.3

A

VD

Large-signal differential

p

§

RL = 10 kΩ

0°C 3 11.1 4 13.5

V/mV

voltage am lification

§

70°C 4 13.3 5 15.2

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 14 pF

25°C 70 87 75 94

CMRR

Common-mode

VIC = V

ICR

min,

0°C 70 87 75 94

dB

rejection ratio

V

O

= 0,

R

S

= 50

Ω

70°C 70 87 75 94

Supply-voltage

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

V

CC±

= ±

5 V t

o ±15 V,

=

=

0°C 75 96 75 96

dB

(∆V

CC±

/∆VIO)

V

O

= 0,

R

S

= 50

Ω

70°C 75 96 75 96

†

Full range is 0°C to 70°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = 2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

17

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL032C and TL032AC electrical characteristics at specified free-air temperature (continued)

TL032C, TL032AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 3.8 5 13 17

P

D

Total power dissipation

p

VO = 0, No load

0°C

3.7 5 12.7 17

mW

(two am lifiers)

70°C 3.8 5 12.6 17

Supply current

0°C 368 500 422 560

I

CC

y

(two amplifiers)

V

O

= 0,

No load

70°C 378 500 420 560

µ

A

VO1/V

O2

Crosstalk attenuation AVD = 100 dB 25°C 120 120 dB

TL032C and TL032AC operating characteristics at specified free-air temperature

TL032C, TL032AC

PARAMETER TEST CONDITIONS T

A

V

CC±

= ±5 V V

CC

±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 12 1.5 2.9

SR+

Positive slew rate at unity

†

0°C 1.8 1 2.6

V/µs

gain

†

R

= 10 kΩ, C

= 100 pF,

70°C 2.2 1.5 3.2

L

,

L

,

See Figure 1

25°C 3.9 1.5 5.1

SR–

Negative slew rate at unity

†

0°C 3.7 1.5 5

V/µs

gain

†

70°C 4 1.5 5

25°C 138 132

t

r

Rise time

0°C 134 127

ns

70°C 150 142

=

25°C 138 132

t

f

Fall time

V

I(PP)

=

±10 V

,

RL = 10 kΩ, CL = 100 pF,

0°C 134 127

ns

See Figures 1 and 2

70°C 150 142

25°C 11% 5%

Overshoot factor

0°C 10% 4%

70°C 12% 6%

f = 10 Hz

°

49 49

Equivalent input

TL032C

R

= 20 Ω,

f = 1 kHz

25°C

41 41

V

n

q

noise voltage

S

,

See Figure 3

f = 10 Hz

°

49 49

n

V/√H

z

TL032AC

f = 1 kHz

25°C

41 41 60

I

n

Equivalent input noise current f = 1 kHz 25°C 0.003 0.003

pA/√Hz

25°C 1 1.1

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 10 kΩ,

0°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

70°C 1 1

25°C 61° 65°

φ

m

Phase margin at unity gain

V

I

= 10 mV,

=

p

R

L

= 10 kΩ,

0°C 61° 65°

C

L

= 25 F,

See Figure 4

70°C 60° 64°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

18

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL032I and TL032AI electrical characteristics at specified free-air temperature

TL032I, TL032AI

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.69 3.5 0.57 1.5

p

TL032I

Full range

†

5.3 3.3

VIOInput offset voltage

25°C 0.53 2.8 0.39 0.8

mV

TL032AI

Full range

†

4.6 2.6

T emperature coef ficient

V

O

= 0,

VIC = 0,

R

= 50 Ω

TL032I

25°C to

85°C

11.4 10.8

°

α

VIO

of input offset voltage

R

S

50

Ω

TL032AI

25°C to

85°C

11.4 10.8 25

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 1 100 1 100 pA

IIOInput offset current

O

,

See Figure 5

IC

,

85°C 0.02 0.45 0.02 0.45 nA

p

V

= 0, V

= 0,

25°C 2 200 2 200 pA

IIBInput bias current

O

,

See Figure 5

IC

,

85°C 0.2 0.9 0.3 0.9 nA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

–40°C 3 4.2 13 14

V

out ut voltage swing

85°C 3 4.4 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative

peak output voltage

RL = 10 kΩ

–40°C –3 –4.1 –12.5 –13.8

V

swing

85°C –3 –4.2 –12.5 –14

Large-signal differential

–40°C 3 8.4 4 11.6

A

VD

gg

voltage amplification

§

R

L

= 10

kΩ

85°C 4 13.5 5 15.3

V/mV

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 4 pF

25°C 70 87 75 94

CMRR

Common-mode

VIC = V

ICR

min,

–40°C 70 87 75 94

dB

rejection ratio

V

O

= 0,

R

S

= 50

Ω

85°C 70 87 75 94

Supply-voltage

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

V

CC±

= ±5 V to

±15 V

,

–40°C 75 96 75 96

dB

(∆V

CC±

/∆VIO)

VO = 0, RS = 50 Ω 85°C 75 96 75 96

†

Full range is –40°C to 85°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = 2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

19

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL032I and TL032AI electrical characteristics at specified free-air temperature (continued)

TL032I, TL032AI

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 3.8 5 13 17

P

D

Total power dissipation

p

VO = 0, No load

–40°C 2.9 5 10.9 17

mW

(two am lifiers)

85°C 3.7 5 12.4 17

25°C 384 500 434 560

I

CC

Supply current

p

VO = 0, No load

–40°C 288 500 362 560

µA

(two am lifiers)

85°C 372 500 414 560

VO1/V

O2

Crosstalk attenuation AVD = 100 dB 25°C 120 120 dB

TL032I and TL032AI operating characteristics at specified free-air temperature

TL032I, TL032AI

PARAMETER TEST CONDITIONS T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

MIN TYP MAX MIN TYP MAX

25°C 2 1.5 2.9

SR+

Positive slew rate at unity

†

–40°C 1.6 1 2.1

V/µs

gain

†

p

85°C 2.3 1.5 3.3

R

L

=

10 kΩ, C

L

=

100 pF

25°C 3.9 1.5 5.1

SR–

Negative slew rate at unity

†

–40°C 3.3 1.5 4.8

V/µs

gain

†

85°C 4.1 1.5 4.9

=

25°C 138 132

t

r

Rise time

V

I(PP)

=

±10 V

,

RL = 10 kΩ, CL = 100 pF,

–40°C 132 123

ns

See Figures 1 and 2

85°C 154 146

=

25°C 138 132

t

f

Fall time

V

I(PP)

=

±10 V

,

RL = 10 kΩ, CL = 100 pF,

–40°C 132 123

ns

See Figure 1

85°C 154 146

=

25°C 11% 5%

Overshoot factor

V

I(PP)

=

±10 V

,

RL = 10 kΩ, CL = 100 pF,

–40°C 12% 5%

See Figures 1 and 2

85°C 13% 7%

f = 10 Hz

°

49 49

Equivalent input

TL032I

R

= 20 Ω,

f = 1 kHz

25°C

41 41

V

n

q

noise voltage

S

,

See Figure 3

f = 10 Hz

°

49 49

n

V/√H

z

TL032AI

f = 1 kHz

25°C

41 41 60

I

n

Equivalent input noise

current

f = 1 kHz 25°C 0.003 0.003

pA/√Hz

25°C 1 1.1

B1Unity-gain bandwidth

VI = 10 mV,

p

RL = 10 kΩ,

–40°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

85°C 0.9 1

25°C 61° 65°

φmPhase margin at unity gain

V

I

= 10 mV,

=

p

R

L

= 10 kΩ,

–40°C 61° 65°

C

L

= 25 F,

See Figure 4

85°C 60° 64°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

20

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL032M and TL032AM electrical characteristics at specified free-air temperature

TL032M, TL032AM

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.69 3.5 0.57 1.5

p

TL032M

Full range

†

6.5 4.5

VIOInput offset voltage

25°C 0.53 2.8 0.39 0.8

mV

TL032AM

Full range

†

5.8 3.8

T emperature coef ficient

V

O

= 0,

VIC = 0,

R

= 50 Ω

TL032M

25°C to

125°C

9.7 9.7

°

α

VIO

of input offset voltage

R

S

50

Ω

TL032AM

25°C to

125°C

9.7 9.7

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 1 100 1 100 pA

IIOInput offset current

O

,

See Figure 5

IC

,

125°C 0.2 10 0.2 10 nA

p

V

= 0, V

= 0,

25°C 2 200 2 200 pA

IIBInput bias current

O

,

See Figure 5

IC

,

125°C 7 20 8 20 nA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

–55°C 3 4.1 13 14

V

out ut voltage swing

125°C 3 4.4 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative peak

p

RL = 10 kΩ

–55°C –3 –4 –12.5 –13.8

V

out ut voltage swing

125°C –3 –4.3 –12.5 –14

25°C 4 12 5 14.3

A

VD

Large-signal differential

p

§

RL = 10 kΩ

–55°C 3 7.1 4 10.4

V/mV

voltage am lification

§

125°C 3 12.9 4 15

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 4 pF

25°C 70 87 75 94

CMRR

Common-mode rejection

VIC = V

ICR

min,

–55°C 70 87 70 94

dB

ratio

V

O

= 0,

R

S

= 50

Ω

125°C 70 87 70 94

Supply-voltage

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

V

CC±

= ±5 V to ±15 V,

=

=

–55°C 75 95 75 95

dB

(∆V

CC±

/∆VIO)

V

O

= 0,

R

S

= 50

Ω

125°C 75 96 75 96

†

Full range is –55°C to 125°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = 2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

21

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL032M and TL032AM electrical characteristics at specified free-air temperature (continued)

TL032M, TL032AM

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 3.8 5 13 17

P

D

Total power dissipation

p

VO = 0, No load

–55°C

2.3 5 9.4 17

mW

(two am lifiers)

125°C 3.6 5 11.8 17

25°C 384 500 434 560

I

CC

Supply current

p

VO = 0, No load

–55°C

228 500 312 560

µA

(two am lifiers)

125°C 356 500 394 560

VO1/V

O2

Crosstalk attenuation AVD = 100 dB 25°C 120 120 dB

TL032M and TL032AM operating characteristics at specified free-air temperature

TL032M, TL032AM

PARAMETER TEST CONDITIONS T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

MIN TYP MAX MIN TYP MAX

25°C 2 1.5 2.9

SR+

Positive slew rate at unity

†

–55°C 1.4 1 1.9

V/µs

gain

†

RL = 10 kΩ,

p

125°C 2.4 1 3.5

C

L

=

100 pF

,

See and

Figure 1

25°C 3.9 1.5 5.1

SR–

Negative slew rate at unity

†

See and Figure 1

–55°C 3.2 1 4.6

V/µs

gain

†

125°C 4.1 1 4.7

V

I(PP)

= ±10 V ,

25°C 138 132

t

r

Rise time

()

RL = 10 kΩ,

=

p

–55°C 142 123

ns

C

L

=

100 F

,

See Figures 1 and 2

125°C 166 58

V

I(PP)

= ±10 V ,

25°C 138 132

t

f

Fall time

()

RL = 10 kΩ,

=

p

–55°C 142 123

ns

C

L

=

100 F

,

See Figure 1

125°C 166 158

V

I(PP)

= ±10 V ,

25°C 11% 5%

Overshoot factor

()

RL = 10 kΩ,

=

p

–55°C 16% 6%

C

L

=

100 F

,

See Figures 1 and 2

125°C 14% 8%

f = 10 Hz

°

49 49

Equivalent

p

TL032M

R

= 20 Ω,

f = 1 kHz

25°C

41 41

V

n

i

nput noise

volt

age

S

,

See Figure 3

f = 10 Hz

°

49 49

n

V/√H

z

voltage

TL032AM

f = 1 kHz

25°C

41 41

I

n

Equivalent input noise

current

f = 1 kHz 25°C 0.003 0.003

pA/√Hz

25°C 1 1.1

B1 Unity-gain bandwidth

VI = 10 mV,

p

RL = 10 kΩ,

–55°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

125°C 0.9 0.9

25°C 61° 65°

φ

m

Phase margin at unity gain

V

I

= 10 mV,

=

p

R

L

= 10 kΩ,

–55°C 57° 64°

C

L

= 25 F,

See Figure 4

125°C 59° 62°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

22

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL032Y electrical characteristics, TA = 25°C

TL032Y

PARAMETER TEST CONDITIONS V

CC±

= ±5 V V

CC±

= ±15 V UNIT

MIN TYP MAX MIN TYP MAX

V

IO

Input offset voltage

0.69 0.57 mV

α

VIO

T emperature coef ficient of

input offset voltage

V

O

= 0,

RS = 50 Ω

V

IC

= 0,

11.5 10.8 µV/°C

I

IO

Input offset current

VO = 0,

See Figure 5

VIC = 0,

1 1 pA

I

IB

Input bias current

VO = 0,

See Figure 5

VIC = 0,

2 2 pA

V

ICR

Common-mode input voltage range

–3.4

to

5.4

–13.4

to

15.4

V

V

OM+

Maximum positive peak

output voltage swing

RL = 10 kΩ 4.3 14 V

V

OM–

Maximum negative peak

output voltage swing

RL = 10 kΩ –4.2 –13.9 V

A

VD

Large-signal differential

voltage amplification

†

RL = 10 kΩ 12 14.3 V/mV

r

i

Input resistance 10

12

10

12

Ω

c

i

Input capacitance 5 14 pF

CMRR Common-mode rejection ratio

VIC = V

ICR

min,

VO = 0, RS = 50 Ω

87 94 dB

k

SVR

Supply-voltage rejection ratio

(∆V

CC±

/∆VIO)

V

CC±

= ±5 V to ±15 V,

VO = 0, RS = 50 Ω

96 96 dB

P

D

Total power dissipation

(two amplifiers)

VO = 0, No load 3.8 13 mW

VO1/V

O2

Crosstalk attenuation AVD = 100 dB 120 120 dB

†

At V

CC±

= ±5 V, VO = 2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL032Y operating characteristics, TA = 25°C

TL032Y

PARAMETER TEST CONDITIONS V

CC±

= ±5 V V

CC

±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

SR+

Positive slew rate at unity gain

†

RL = 10 kΩ, CL = 100 pF, 12 2.9 V/µs

SR–

Negative slew rate at unity gain

†

See Figure 1 and Note 8 3.9 5.1 V/µs

t

r

Rise time V

I(PP)

= ±10 V , 138 132 ns

t

f

Fall time RL = 10 kΩ,, CL = 100 pF, 138 132 ns

Overshoot factor See Figures 1 and 2 11% 5%

p

R

= 20 Ω,

f = 10 Hz 49 49

VnEquivalent input noise voltage

S

,

See Figure 3

f = 1 kHz 41 41

n

V/√H

z

I

n

Equivalent input noise current f = 1 kHz 0.003 0.003

pA/√Hz

B

1

Unity-gain bandwidth

VI = 10 mV,

CL = 25 pF,

RL = 10 kΩ,

See Figure 4

1 1.1 MHz

φ

m

Phase margin at unity gain

VI = 10 mV,

CL = 25 pF,

RL = 10 kΩ,

See Figure 4

61° 65°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

23

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

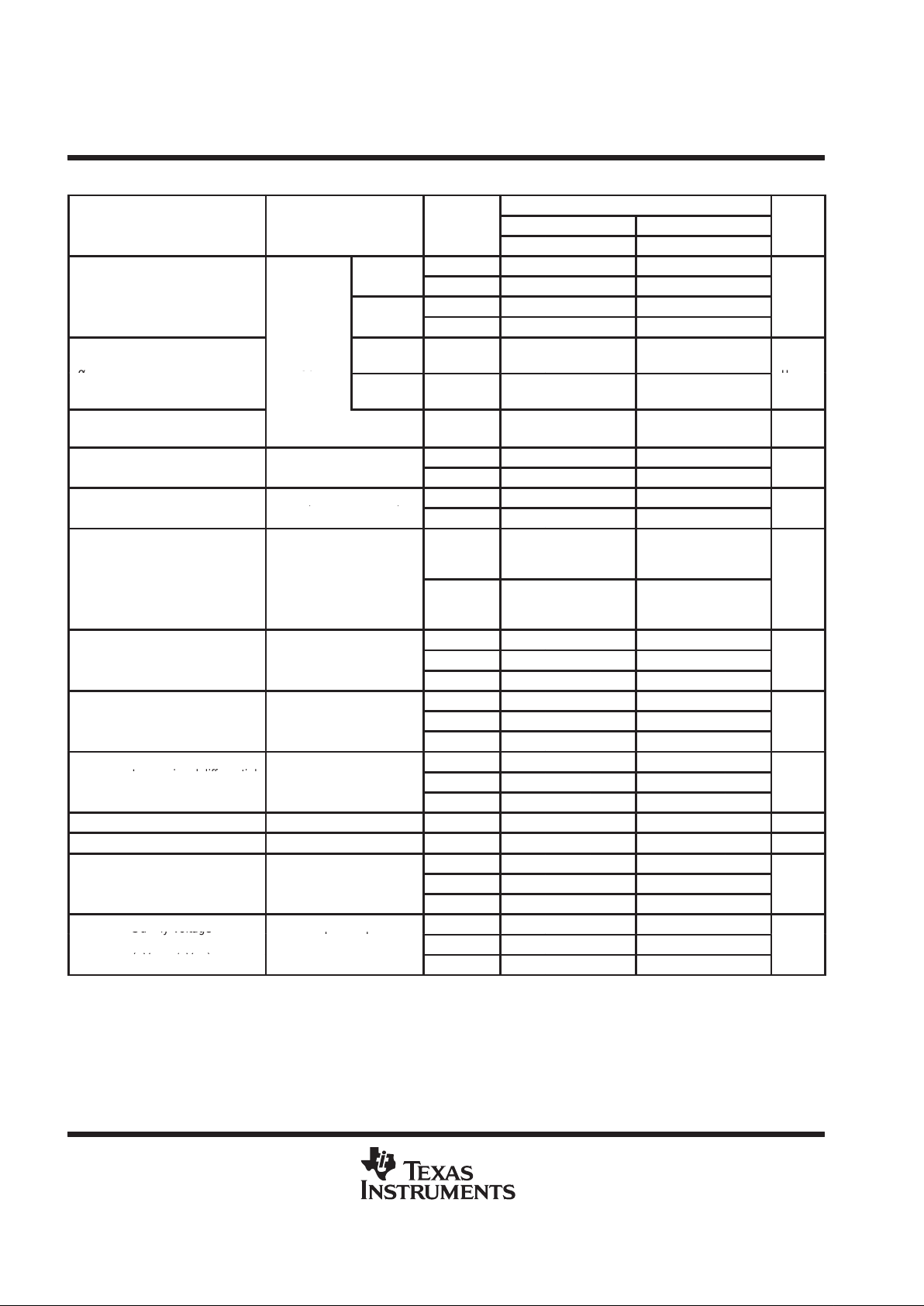

TL034C and TL034AC electrical characteristics at specified free-air temperature

TL034C, TL034AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.91 6 0.79 4

p

TL034C

Full range

†

8.2 6.2

VIOInput offset voltage

25°C 0.7 3.5 0.58 1.5

mV

V

O

= 0,

=

TL034AC

Full range

†

5.7 3.7

T emperature coef ficient of

V

IC

= 0,

RS = 50 Ω

TL034C

25°C to

70°C

11.6 12

°

α

VIO

input offset voltage

TL034AC

25°C to

70°C

11.6 12 25

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 1 100 1 100

p

IIOInput offset current

O

,

IC

,

See Figure 5

70°C 9 200 12 200

pA

p

V

= 0, V

= 0,

25°C 2 200 2 200

p

IIBInput bias current

O

,

IC

,

See Figure 5

70°C 50 400 80 400

pA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

0°C 3 4.2 13 14

V

out ut voltage swing

70°C 3 4.3 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative peak

p

RL = 10 kΩ

0°C –3 –4.1 –12.5 –13.9

V

out ut voltage swing

70°C –3 –4.2 –12.5 –14

25°C 4 12 5 14.3

A

VD

Large-signal differential

p

§

RL = 10 kΩ

0°C 3 11.1 4 13.5

V/mV

voltage am lification

§

70°C 4 13.3 5 15.2

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 14 pF

=

25°C 70 87 75 94

CMRR

Common-mode

V

IC

=

V

ICR

min

,

VO = 0,

0°C 70 87 75 94

dB

rejection ratio

RS = 50 Ω

70°C 70 87 75 94

pp

-

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

VO = 0, RS = 50 Ω

0°C 75 96 75 96

dB

(∆V

CC±

/∆VIO)

70°C 75 96 75 96

†

Full range is 0°C to 70°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

24

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL034C and TL034AC electrical characteristics at specified free-air temperature (continued)

TL034C, TL034AC

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 7.7 10 26 34

P

D

Total power dissipation

p

VO = 0, No load

0°C 7.4 10 25.3 34

mW

(two am lifiers)

70°C 7.6 10 25.2 34

25°C 0.77 1 0.87 1.12

I

CC

Supply current (four amplifiers) VO = 0, No load

0°C 0.74 1 0.85 1.12

mA

70°C 0.76 1 0.84 1.12

VO1/V

O2

Crosstalk attenuation AVD = 100 25°C 120 120 dB

TL034C and TL034AC operating characteristics at specified free-air temperature

TL034C, TL034AC

PARAMETER TEST CONDITIONS T

A

V

CC±

= ±5 V V

CC

±

= ±15 V

UNIT

MIN TYP MAX MIN TYP MAX

25°C 2 1.5 2.9

SR+

Positive slew rate at unity

†

0°C 1.8 1 2.6

V/µs

gain

†

RL = 10 kΩ,

p

70°C 2.2 1.5 3.2

C

L

=

100 pF

,

See

Figure 1

25°C 3.9 1.5 5.1

SR–

Negative slew rate at unity

†

See Figure 1

0°C 3.7 1.5 5

V/µs

gain

†

70°C 4 1.5 5

V

I(PP)

= ±10 V ,

25°C 138 132

t

r

Rise time

()

RL = 10 kΩ,

=

p

0°C 134 127

ns

C

L

=

100 F

,

See Figures 1 and 2

70°C 150 142

V

I(PP)

= ±10 V ,

25°C 138 132

t

f

Fall time

()

RL = 10 kΩ,

=

p

0°C 134 127

ns

C

L

=

100 F

,

See Figure 1

70°C 150 142

V

I(PP)

= ±10 V ,

25°C 11% 5%

Overshoot factor

()

RL = 10 kΩ,

=

p

0°C 10% 4%

C

L

=

100 F

,

See Figures 1 and 2

70°C 12% 6%

f = 10 Hz

°

83 83

Equivalent input

TL034C

R

= 20 Ω,

f = 1 kHz

25°C

43 43

V

n

q

noise voltage

S

,

See Figure 3

f = 10 Hz

°

83 83

n

V/√H

z

TL034AC

f = 1 kHz

25°C

43 43 60

I

n

Equivalent input noise current f = 1 kHz 25°C 0.003 0.003

pA/√Hz

25°C 1 1.1

B

1

Unity-gain bandwidth

VI = 10 mV, RL = 10 kΩ,

p

0°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

70°C 1 1

25°C 61° 65°

φ

m

Phase margin at unity gain

VI = 10 mV, RL = 10 kΩ,

p

0°C 61° 65°

C

L

= 25 F,

See Figure 4

70°C 60° 64°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

25

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL034I and TL034AI electrical characteristics at specified free-air temperature

TL034I, TL034AI

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.91 3.6 0.79 4

p

TL034I

Full range

†

9.3 7.3

VIOInput offset voltage

25°C 0.7 3.5 0.58 1.5

mV

V

O

= 0,

=

TL034AI

Full range

†

6.8 4.8

T emperature coef ficient

V

IC

= 0,

RS = 50 Ω

TL034I

25°C to

85°C

11.5 11.6

°

α

VIO

of input offset voltage

TL034AI

25°C to

85°C

11.5 11.6 25

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 1 100 1 100 pA

IIOInput offset current

O

,

IC

,

See Figure 5

85°C 0.02 0.45 0.02 0.45 nA

p

V

= 0, V

= 0,

25°C 2 200 2 200 pA

IIBInput bias current

O

,

IC

,

See Figure 5

85°C 0.2 0.9 0.3 0.9 nA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

–40°C 3 4.1 13 14

V

out ut voltage swing

85°C 3 4.4 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative peak

p

RL = 10 kΩ

–40°C –3 –4.1 –12.5 –13.8

V

out ut voltage swing

85°C –3 –4.2 –12.5 –14

Large-signal differential

–40°C 4 12 5 14.3

A

VD

gg

voltage amplification

§

R

L

= 10

kΩ

85°C 3 8.4 4 11.6

V/mV

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 4 pF

=

25°C 70 87 75 94

CMRR

Common-mode

V

IC

=

V

ICR

min

,

VO = 0,

–40°C 70 87 75 94

dB

rejection ratio

RS = 50 Ω

85°C 70 87 75 94

pp

-

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

VO = 0, RS = 50 Ω

–40°C 75 96 75 96

dB

(∆V

CC±

/ ∆VIO)

85°C 75 96 75 96

†

Full range is –40°C to 85°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to

TA = 25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV .

§

At V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

26

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL034I and TL034AI electrical characteristics at specified free-air temperature (continued)

TL034I, TL034AI

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 7.7 10 26 34

P

D

Total power dissipation

p

VO = 0, No load

–40°C 5.8 10 21.7 34

mW

(four am lifiers)

85°C 7.4 10 24.8 34

25°C 0.77 1 0.87 1.12

I

CC

Supply current (four amplifiers) VO = 0, No load

–40°C 0.58 1 0.72 1.12

mA

85°C 0.74 1 0.83 1.12

VO1/V

O2

Crosstalk attenuation AVD = 100 25°C 120 120 dB

TL034I and TL034AI operating characteristics

TL034I, TL034AI

PARAMETER TEST CONDITIONS T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

MIN TYP MAX MIN TYP MAX

25°C 2 1.5 2.9

SR+

Positive slew rate at unity

†

–40°C 1.6 1 2.1

V/µs

gain

†

R

= 10 kΩ, C

= 100 pF,

85°C

2.3 1.5 3.3

L

,

See Figure 1

L

,

25°C 3.9 1.5 5.1

SR–

Negative slew rate at unity

†

–40°C 3.3 1.5 4.8

V/µs

gain

†

85°C 4.1 1.5 4.9

25°C 138 132

t

r

Rise time

–40°C 132 123

ns

85°C 154 146

V

I(PP)

= ±10 V ,

25°C 138 132

t

f

Fall time

()

RL = 10 kΩ,

p

–40°C 132 123

ns

C

L

=

100 F

,

See Fi

g

ures 1 and 2

85°C 154 146

g

25°C 11% 5%

Overshoot factor

–40°C 12% 5%

85°C 13% 7%

f = 10 Hz

°

83 83

Equivalent input

TL034I

R

= 20 Ω,

f = 1 kHz

25°C

43 43

V

n

q

noise voltage

S

,

See Figure 3

f = 10 Hz

°

83 83

n

V/√H

z

TL034AI

f = 1 kHz

25°C

43 43 60

I

n

Equivalent input noise

current

f = 1 kHz 25°C 0.003 0.003

pA/√Hz

25°C 1 1.1

B

1

Unity-gain bandwidth

VI = 10 mV,

p

RL = 10 kΩ,

–40°C 1 1.1

MHz

C

L

= 25 F,

See Figure 4

85°C 0.9 1

25°C 61° 65°

φ

m

Phase margin at unity gain

VI = 10 mV,

p

RL = 10 kΩ,

–40°C 61° 65°

C

L

= 25 F,

See Figure 4

85°C 60° 64°

†

For V

CC±

= ±5 V, V

I(PP)

= ±1 V; for V

CC±

= ±15 V, V

I(PP)

= ±5 V.

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

27

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TL034M and TL034AM electrical characteristics at specified free-air temperature

TL034M, TL034AM

PARAMETER TEST CONDITIONS

T

A

V

CC±

= ±5 V V

CC±

= ±15 V UNIT

A

MIN TYP MAX MIN TYP MAX

25°C 0.91 3.6 0.78 4

p

TL034M

Full range

†

11 9

VIOInput offset voltage

25°C 0.7 3.5 0.58 1.5

mV

V

O

= 0,

=

TL034AM

Full range

†

8.5 6.5

T emperature coef ficient of

V

IC

= 0,

RS = 50 Ω

TL034M

25°C to

125°C

10.6 10.9

°

α

VIO

input offset voltage

TL034AM

25°C to

125°C

10.6 10.9

µ

V/°C

Input offset voltage

long-term drift

‡

25°C 0.04 0.04 µV/mo

p

V

= 0, V

= 0,

25°C 1 100 1 100 pA

IIOInput offset current

O

,

IC

,

See Figure 5

125°C 0.2 10 0.2 10 nA

p

V

= 0, V

= 0,

25°C 2 200 2 200 pA

IIBInput bias current

O

,

IC

,

See Figure 5

125°C 7 20 8 20 nA

Common-mode input

25°C

–1.5

to

4

–3.4

to

5.4

–11.5

to

14

–13.4

to

15.4

V

ICR

voltage range

Full range

†

–1.5

to

4

–11.5

to

14

V

25°C 3 4.3 13 14

V

OM+

Maximum positive peak

p

RL = 10 kΩ

–55°C 3 4.1 13 14

V

out ut voltage swing

125°C 3 4.4 13 14

25°C –3 –4.2 –12.5 –13.9

V

OM–

Maximum negative peak

p

RL = 10 kΩ

–55°C –3 –4 –12.5 –13.8

V

out ut voltage swing

125°C –3 –4.3 –12.5 –14

25°C 4 12 5 14.3

A

VD

Large-signal differential

p

§

RL = 10 kΩ

–55°C 3 7.1 4 10.4

V/mV

voltage am lification

§

125°C 3 12.9 4 15

r

i

Input resistance 25°C 10

12

10

12

Ω

c

i

Input capacitance 25°C 5 4 pF

25°C 70 87 75 94

CMRR

Common-mode

VIC = V

ICR

min,

–55°C 70 87 70 94

dB

rejection ratio

V

O

= 0,

R

S

= 50

Ω

125°C 70 87 70 94

pp

-

25°C 75 96 75 96

k

SVR

Su ly voltage

rejection ratio

VO = 0, RS = 50 Ω

–55°C 75 95 75 95

dB

(∆V

CC±

/∆VIO)

125°C 75 96 75 96

†

Full range is –55°C to 125°C.

‡

Typical values are based on the input offset voltage shift observed through 168 hours of operating life test at TA = 150°C extrapolated to TA =

25°C using the Arrhenius equation and assuming an activation energy of 0.96 eV.

§

At V

CC±

= ±5 V, VO = ±2.3 V; at V

CC±

= ±15 V, VO = ±10 V .

TL03x, TL03xA, TL03xY

ENHANCED-JFET LOW-POWER LOW-OFFSET

OPERATIONAL AMPLIFIERS

SLOS180B – FEBRUARY 1997 – REVISED FEBRUARY 1999

28