Page 1

PRODUCTPREVIEW

DM3730, DM3725

www.ti.com

1 DM3730, DM3725 Digital Media Processor

1.1 Features

12345

• DM3730/25 Digital Media Processor:

– Compatible with OMAP™ 3 Architecture

– ARM®microprocessor (MPU) Subsystem

• Up to 1-GHz ARM®Cortex™-A8 Core

See Processor Clocks OPP table.

• NEON SIMD Coprocessor

– High Performance Image, Video, Audio

(IVA2.2TM) Accelerator Subsystem

• Up to 800-MHz TMS320C64x+TMDSP Core

• Enhanced Direct Memory Access (EDMA)

Controller (128 Independent Channels)

• Video Hardware Accelerators

– POWERVR SGX™ Graphics Accelerator

(DM3730 only)

• Tile Based Architecture Delivering up to

20 MPoly/sec

• Universal Scalable Shader Engine:

Multi-threaded Engine Incorporating Pixel

and Vertex Shader Functionality • 8-Bit Overflow Protection

• Industry Standard API Support: • Bit-Field Extract, Set, Clear

OpenGLES 1.1 and 2.0, OpenVG1.0

• Fine Grained Task Switching, Load

Balancing, and Power Management

• Programmable High Quality Image

Anti-Aliasing

– Advanced Very-Long-Instruction-Word

(VLIW) TMS320C64x+TMDSP Core

• Eight Highly Independent Functional

Units

• Six ALUs (32-/40-Bit); Each Supports

Single 32- bit, Dual 16-bit, or Quad 8-bit,

Arithmetic per Clock Cycle

• Two Multipliers Support Four 16 x 16-Bit

Multiplies (32-Bit Results) per Clock

Cycle or Eight 8 x 8-Bit Multiplies (16-Bit

Results) per Clock Cycle

• Load-Store Architecture With

Non-Aligned Support

• 64 32-Bit General-Purpose Registers

• Instruction Packing Reduces Code Size

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2POWERVR SGX is a trademark of Imagination Technologies Ltd.

3OMAP is a trademark of Texas Instruments.

4Cortex is a trademark of ARM Limited.

5ARM is a registered trademark of ARM Ltd.

PRODUCT PREVIEW information concernsproducts in the formative

or design phase of development. Characteristic data and other

specifications are design goals. Texas Instruments reserves the right

to change ordiscontinue these products withoutnotice.

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

DM3730, DM3725

Digital Media Processor

Check for Samples: DM3730, DM3725

• All Instructions Conditional

• Additional C64x+TMEnhancements

– Protected Mode Operation

– Expectations Support for Error

Detection and Program Redirection

– Hardware Support for Modulo Loop

Operation

– C64x+TML1/L2 Memory Architecture

• 32K-Byte L1P Program RAM/Cache

(Direct Mapped)

• 80K-Byte L1D Data RAM/Cache (2-Way

Set- Associative)

• 64K-Byte L2 Unified Mapped RAM/Cache

(4- Way Set-Associative)

• 32K-Byte L2 Shared SRAM and 16K-Byte

L2 ROM

– C64x+TMInstruction Set Features

• Byte-Addressable (8-/16-/32-/64-Bit Data)

• Normalization, Saturation, Bit-Counting

• Compact 16-Bit Instructions

• Additional Instructions to Support

Complex Multiplies

– External Memory Interfaces:

• SDRAM Controller (SDRC)

– 16, 32-bit Memory Controller With

1G-Byte Total Address Space

– Interfaces to Low-Power SDRAM

– SDRAM Memory Scheduler (SMS) and

Rotation Engine

• General Purpose Memory Controller

(GPMC)

– 16-bit Wide Multiplexed Address/Data

Bus

– Up to 8 Chip Select Pins With

128M-Byte Address Space per Chip

Select Pin

– Glueless Interface to NOR Flash,

Copyright © 2010, Texas Instruments Incorporated

Page 2

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

NAND Flash (With ECC Hamming – System Direct Memory Access (SDMA)

Code Calculation), SRAM and Controller (32 Logical Channels With

Pseudo-SRAM Configurable Priority)

– Flexible Asynchronous Protocol – Comprehensive Power, Reset, and Clock

Control for Interface to Custom Logic Management

(FPGA, CPLD, ASICs, etc.)

– Nonmultiplexed Address/Data Mode

(Limited 2K-Byte Address Space)

– 1.8-V I/O and 3.0-V (MMC1 only),

0.9-V to 1.2-V Adaptive Processor Core

Voltage

0.9-V to 1.1-V Adaptive Core Logic Voltage

Note: These are default Operating

Performance Point (OPP) voltages and could

be optimized to lower values using

SmartReflex AVS.

– Commercial and Extended Temperature

Grades

– Serial Communication

• 5 Multichannel Buffered Serial Ports

(McBSPs)

– 512 Byte Transmit/Receive Buffer

(McBSP1/3/4/5)

– 5K-Byte Transmit/Receive Buffer

(McBSP2)

– SIDETONE Core Support (McBSP2 and

3 Only) For Filter, Gain, and Mix

Operations

– Direct Interface to I2S and PCM Device

and T Buses

– 128 Channel Transmit/Receive Mode

• Four Master/Slave Multichannel Serial

Port Interface (McSPI) Ports

• High-Speed/Full-Speed/Low-Speed USB

OTG Subsystem (12-/8-Pin ULPI Interface)

• High-Speed/Full-Speed/Low-Speed

Multiport USB Host Subsystem

– 12-/8-Pin ULPI Interface or 6-/4-/3-Pin

Serial Interface

• One HDQ/1-Wire Interface

• Four UARTs (One with Infrared Data

Association [IrDA] and Consumer Infrared

[CIR] Modes)

• Three Master/Slave High-Speed

Inter-Integrated Circuit (I2C) Controllers

– Camera Image Signal Processing (ISP)

• CCD and CMOS Imager Interface

• Memory Data Input

• BT.601/BT.656 Digital YCbCr 4:2:2

(8-/10-Bit) Interface

• Glueless Interface to Common Video

Decoders

• Resize Engine

– Resize Images From 1/4x to 4x

– Separate Horizontal/Vertical Control

www.ti.com

• SmartReflexTMTechnology

• Dynamic Voltage and Frequency Scaling

(DVFS)

– ARM®Cortex™-A8 Core

• ARMv7 Architecture

– Trust Zone

– Thumb®-2

– MMU Enhancements

• In-Order, Dual-Issue, Superscalar

Microprocessor Core

• NEON Multimedia Architecture

• Over 2x Performance of ARMv6 SIMD

• Supports Both Integer and Floating Point

SIMD

• Jazelle®RCT Execution Environment

Architecture

• Dynamic Branch Prediction with Branch

Target Address Cache, Global History

Buffer, and 8-Entry Return Stack

• Embedded Trace Macrocell (ETM)

Support for Non-Invasive Debug

– ARM Cortex-A8 Memory Architecture:

• 32K-Byte Instruction Cache (4-Way

Set-Associative)

• 32K-Byte Data Cache (4-Way

Set-Associative)

• 256K-Byte L2 Cache

– 32K-Byte ROM

– 64K-Byte Shared SRAM

– Endianess:

• ARM Instructions - Little Endian

• ARM Data – Configurable

• DSP Instructions/Data - Little Endian

• Removable Media Interfaces:

– Three Multimedia Card (MMC)/ Secure Digital

(SD) With Secure Data I/O (SDIO)

• Test Interfaces

– IEEE-1149.1 (JTAG) Boundary-Scan

Compatible

– Embedded Trace Macro Interface (ETM)

– Serial Data Transport Interface (SDTI)

• 12 32-bit General Purpose Timers

• 2 32-bit Watchdog Timers

• 1 32-bit Secure Watchdog Timer

• 1 32-bit 32-kHz Sync Timer

• Up to 188 General-Purpose I/O (GPIO) Pins

(Multiplexed With Other Device Functions)

• 45-nm CMOS Technology

2 DM3730, DM3725 Digital Media Processor Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 3

PRODUCTPREVIEW

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

• Package-On-Package (POP) Implementation for – 515-pin s-PBGA package (CBC Suffix),

Memory Stacking (Not Available in CUS .65mm Ball Pitch (Top), .5mm Ball Pitch

Package) (Bottom)

• Packages: – 423-pin s-PBGA package (CUS Suffix),

– 515-pin s-PBGA package (CBP Suffix), .5mm

.65mm Ball Pitch

Ball Pitch (Top), .4mm Ball Pitch (Bottom)

Copyright © 2010, Texas Instruments Incorporated DM3730, DM3725 Digital Media Processor 3

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 4

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

1.2 Description

The DM37x generation of high-performance, digital media processors are based on the enhanced device

architecture and are integrated on TI's advanced 45-nm process technology. This architecture is designed

to provide best in class ARM and Graphics performance while delivering low power consumption. This

balance of performance and power allow the device to support the following example applications:

• Portable Data Terminals

• Navigation

• Auto Infotainment

• Gaming

• Medical Imaging

• Home Automation

• Human Interface

• Industrial Control

• Test and Measurement

• Single board Computers

The device can support numerous HLOS and RTOS solutions including Linux and Windows Embedded

CE which are available directly from TI. Additionally, the device is fully backward compatible with previous

Cortex™-A8 processors and OMAP™ processors.

This DM3730/25 Digital Media Processor data manual presents the electrical and mechanical

specifications for the DM3730/25 Digital Media Processor. The information contained in this data manual

applies to both the commercial and extended temperature versions of the DM3730/25 Digital Media

Processor unless otherwise indicated. It consists of the following sections:

• A description of the DM3730/25 terminals: assignment, electrical characteristics, multiplexing, and

functional description

• A presentation of the electrical characteristics requirements: power domains, operating conditions,

power consumption, and dc characteristics

• The clock specifications: input and output clocks, DPLL and DLL

• A description of thermal characteristics, device nomenclature, and mechanical data about the available

packaging

www.ti.com

4 DM3730, DM3725 Digital Media Processor Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 5

PRODUCTPREVIEW

64

64

Async

64

64

L2$

256K

MPU

Subsystem

POWERVR

SGX

Graphics

Accelerator

TM

32

32

32

Channel

System

DMA

3232

Parallel

TV

Amp

LCD Panel

CVBS

or

S-Video

Dual Output 3-Layer

Display Processor

(1xGraphics, 2xVideo)

Temporal Dithering

SDTV QCIF Support®

32

Camera

ISP

Image

Capture

Hardware

Image

Pipeline

Camera

(Parallel)

64

HS USB

Host

HS

USB

OTG

32

L3 Interconnect Network-Hierarchial, Performance, and Power Driven

64KB

On-Chip

RAM

32

32KB

On-Chip

ROM

32

SMS:

SDRAM

Memory

Scheduler/

Rotation

64

SDRC:

SDRAM

Memory

Controller

L4 Interconnect

32

System

Controls

PRCM

2xSmartReflex

TM

Control

Module

External

Peripherals

Interfaces

Peripherals: 4xUART,

3xHigh-Speed I2C, 5xMcBSP

(2x with Sidetone/Audio Buffer)

4xMcSPI, 6xGPIO

3xHigh-Speed MMC/SDIO

HDQ/1 Wire, 6xMailboxes

12xGPTimers, 2xWDT,

32K Sync Timer

GPMC:

General

Purpose

Memory

Controller

NAND/

NOR

Flash,

SRAM

32

Emulation

Debug: SDTI, ETM, JTAG

External and

Stacked Memories

32

IVA 2.2 Subsystem

TMS320DM64x+ DSP

Imaging Video and

Audio Processor

32K/32K L1$

48K L1D RAM

64K L2$

32K L2 RAM

16K L2 ROM

Video Hardware

64

32

Async

64

32

ARM

Cortex™- A8

®

Core

TrustZone

32K/32K L1$

DM3730, DM3725

www.ti.com

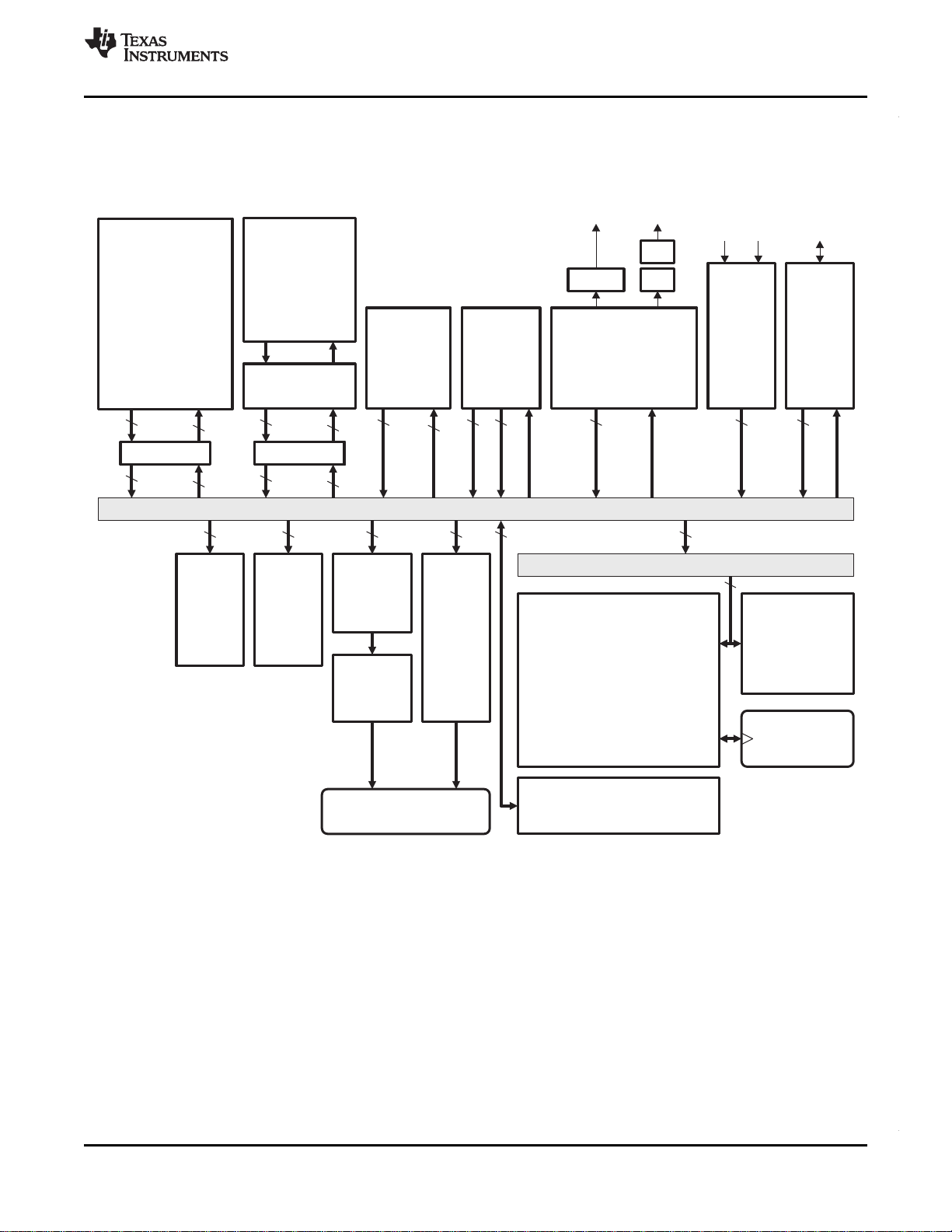

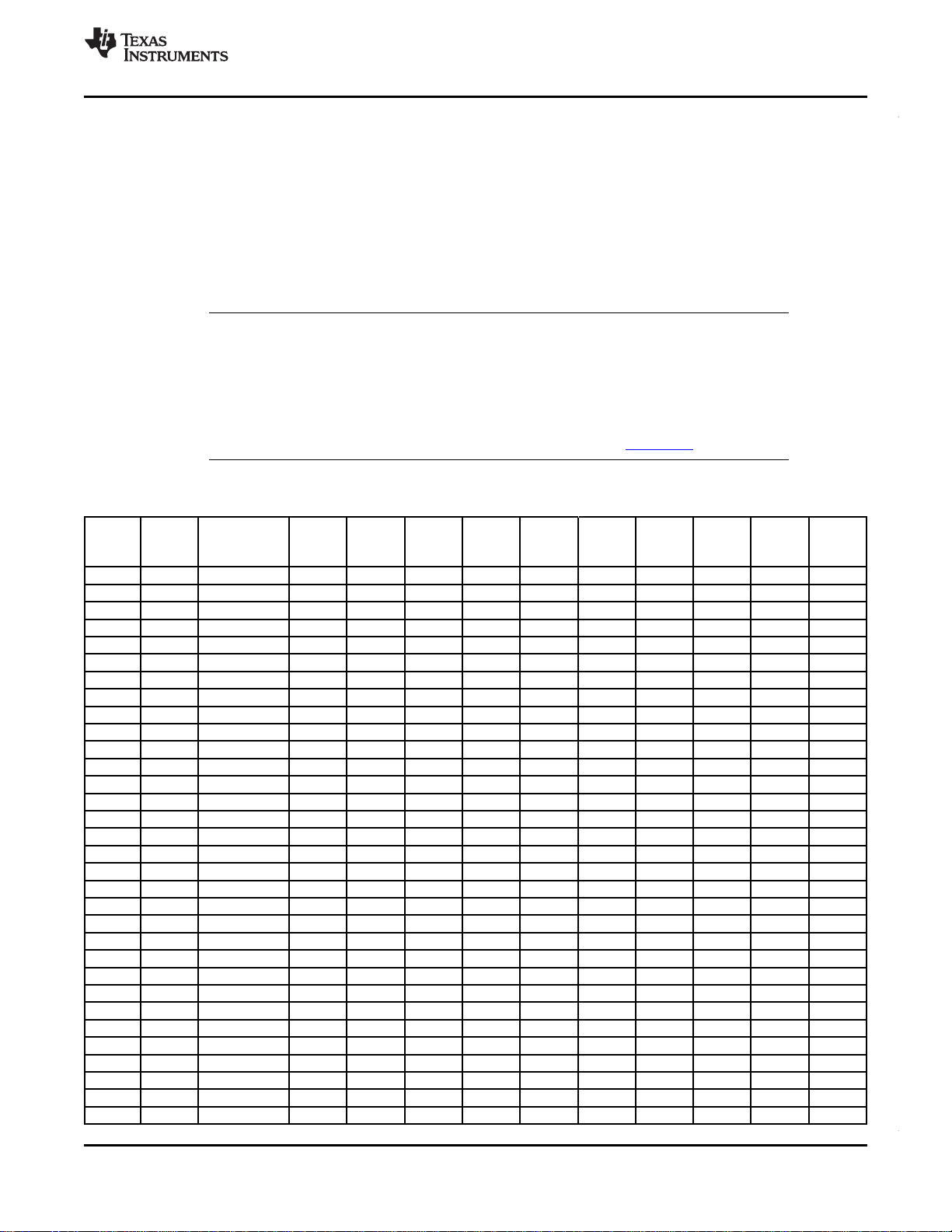

1.3 Functional Block Diagram

The functional block diagram of the DM3730/25 Digital Media Processor is shown below.

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Copyright © 2010, Texas Instruments Incorporated DM3730, DM3725 Digital Media Processor 5

Figure 1-1. DM3730/25 Functional Block Diagram

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 6

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

This data sheet revision history highlights the technical changes made from the previous to the current

revision.

SECTION ADDITIONS/CHANGES/DELETIONS

Terminal Description

Electrical Characteristics • Table 3-2 . Maximum Current Ratings at Ball Level

Clock Specifications

Timing Requirements and

Switching Characteristics

www.ti.com

Revision History

Revision History

Updated/changed:

• Table 2-1. Ball Characteristics (CBP Pkg.)

• Table 2-2. Ball Characteristics (CBC Pkg.)

• Table 2-3. Ball Characteristics (CUS Pkg.)

Updated/changed:

• Table 3-1. Absolute Maximum Rating over Junction Temperature Range

• Table 3-4. Recommended Operating Conditions

• Table 3-5. DC Electrical Characteristics

Added/updated:

• Section 4.3.3. DPLL and DLL Noise Isolation

• Section 4.3.6. SGX Clock

• Table 4-2. Crystal Electrical Characteristics

• Table 4-13. sys_clkout2 Output Clock Switch Characteristics

• Table 4-18. Processor Voltages Without SmartReflex

• Table 4-19. Processor Voltages With SmartReflex

• Figure 4-8. DPLL and DLL Noise Filter

Added/updated:

• Section 5.4.2.2. Placement

• Section 5.4.2.3. LPDDR Keep Out Region

• Section 5.4.2.4. Net Classes

• Section 5.4.2.5. LPDDR Signal Termination

• Section 5.4.2.6. LPDDR CK and ADDR_CTRL Routing

• Section 5.6.7.1. UART

• Table 5-22. ISP2P cam_xclka and cam_xclkb Output Clocks Switching Characteristics

TM

TM

6 DM3730, DM3725 Digital Media Processor Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 7

PRODUCTPREVIEW

2

3

4

5

6

7

8

9

10

11

121314

15

16

17

18

19

20

21

22

23

A

B

C

D

E

F

G

H

J

K

L

M

N

P

T

R

U

V

W

Y

AA

AB

AC

24

25

26

27

28

AD

AE

AF

AG

AH

1

030-001

DM3730, DM3725

www.ti.com

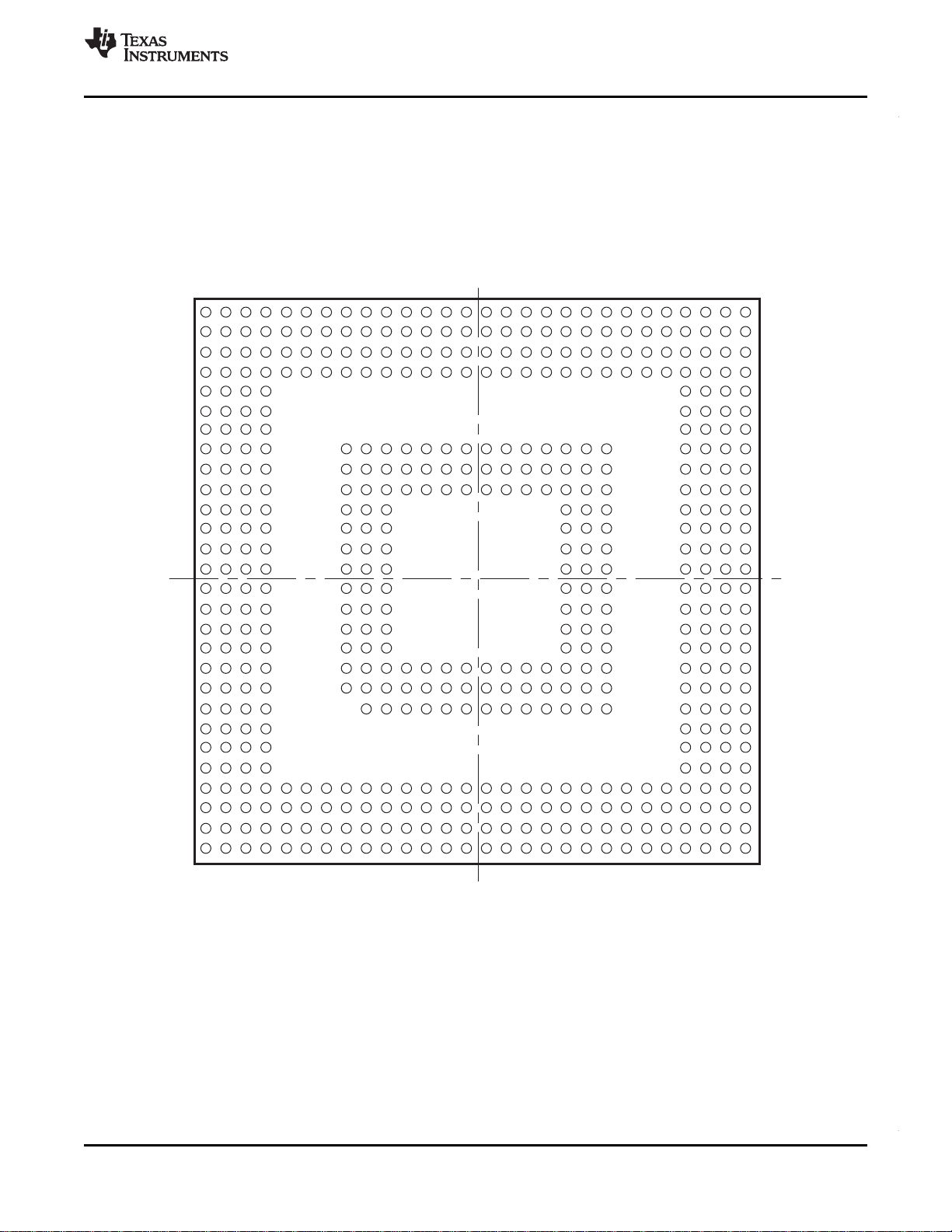

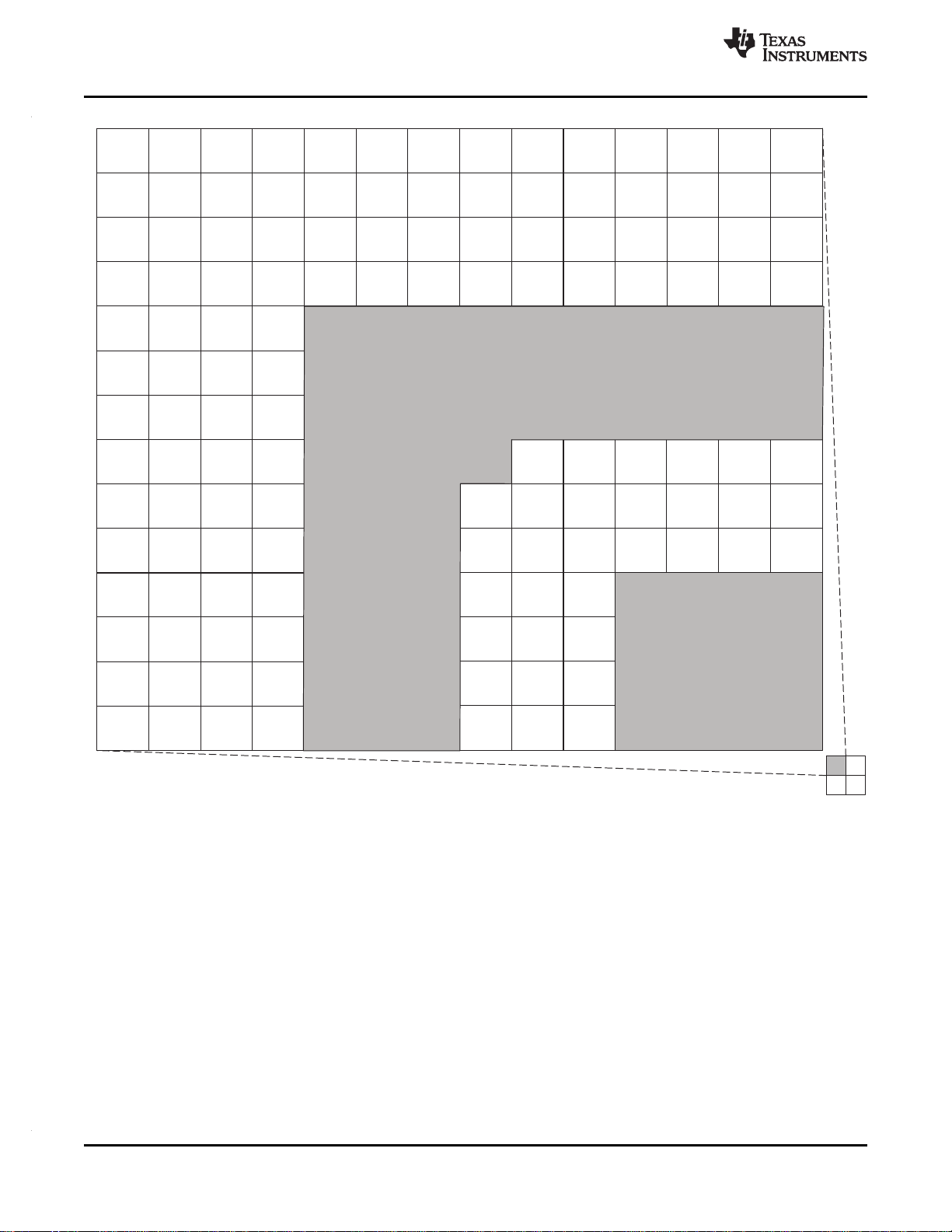

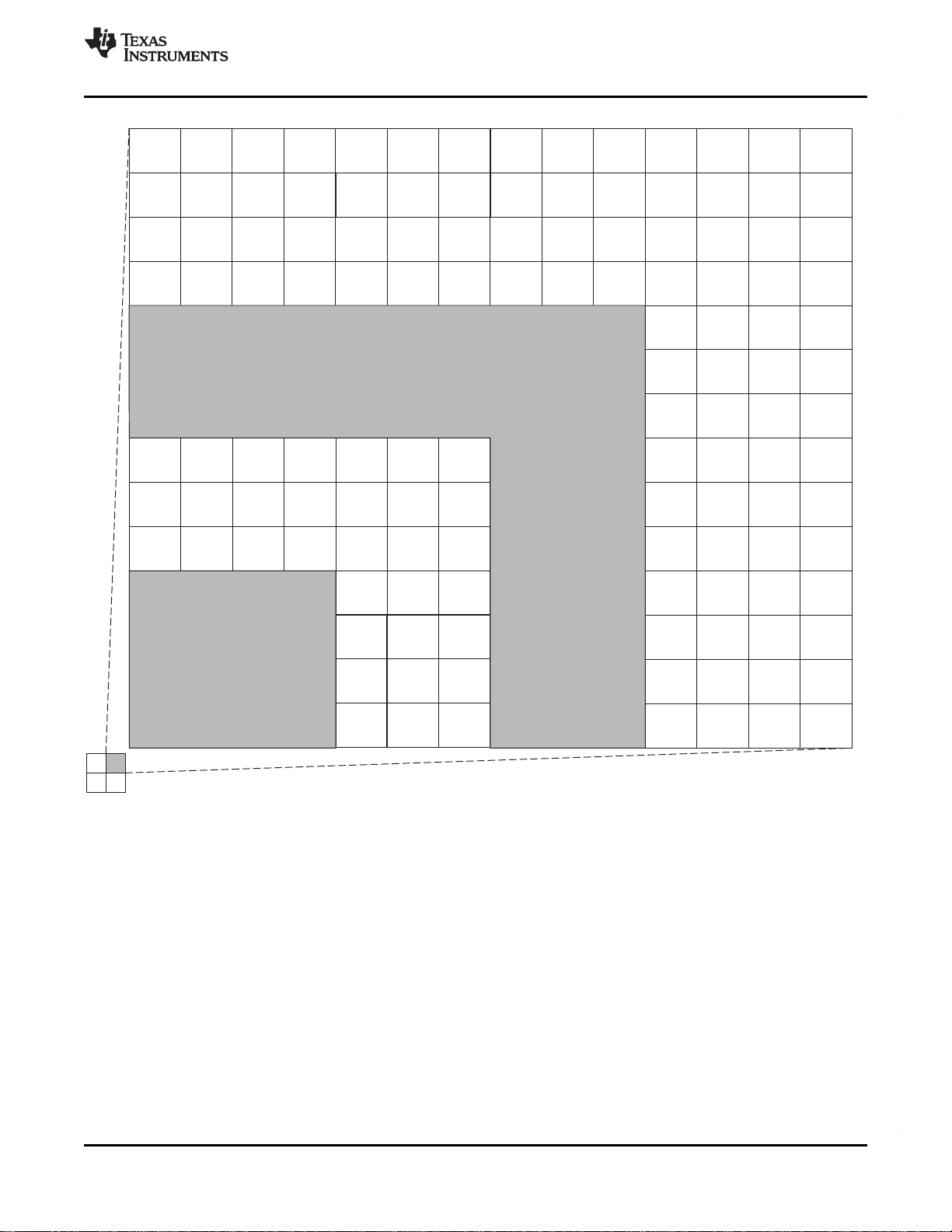

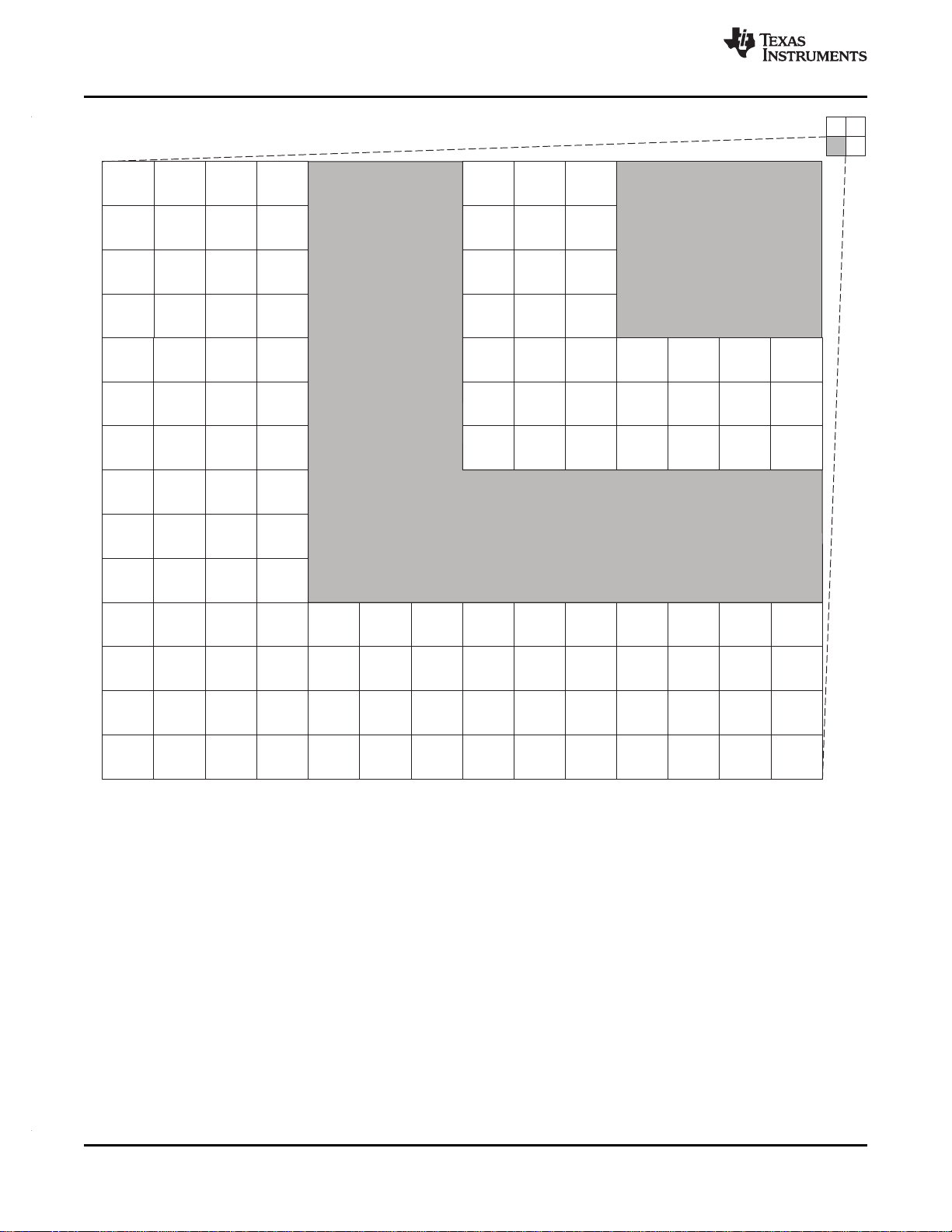

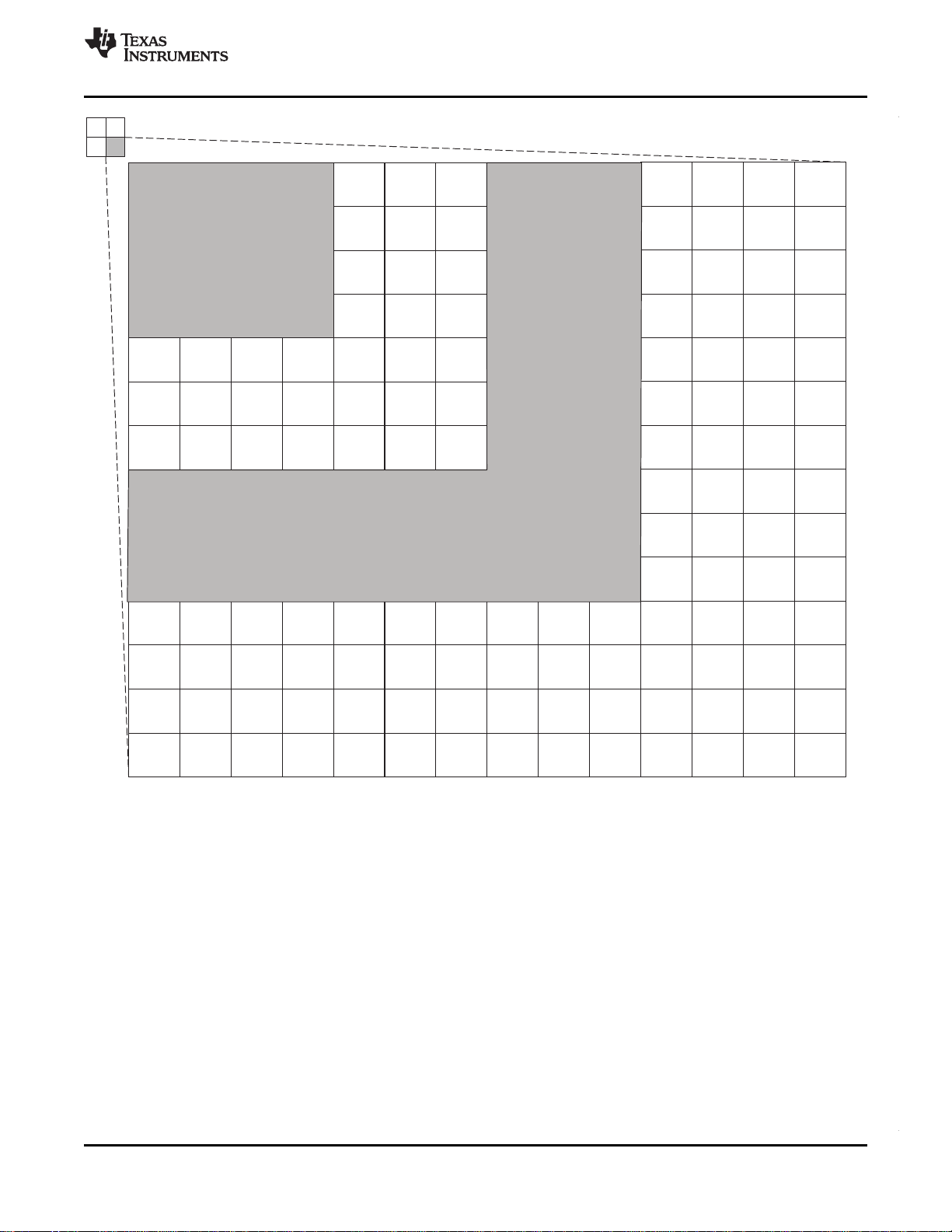

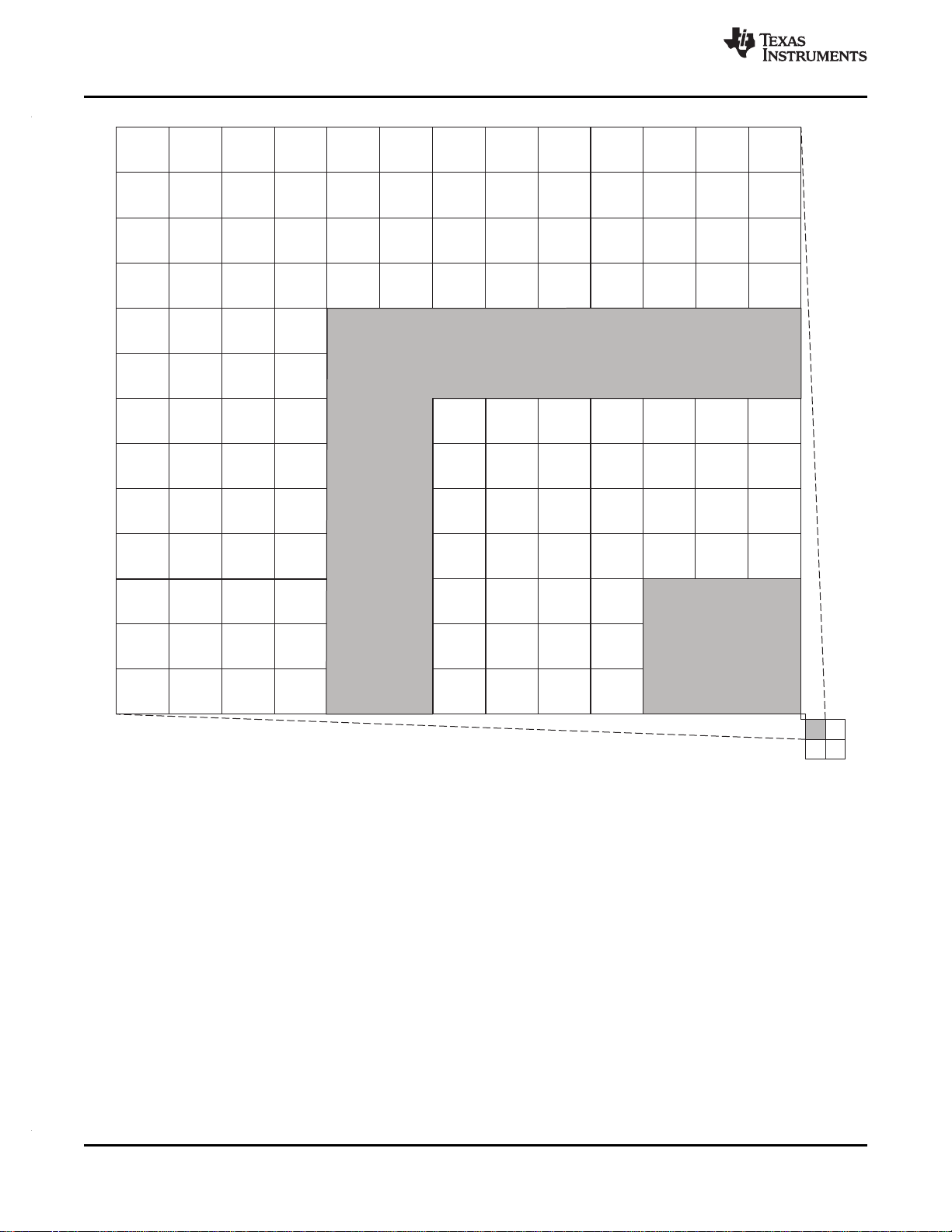

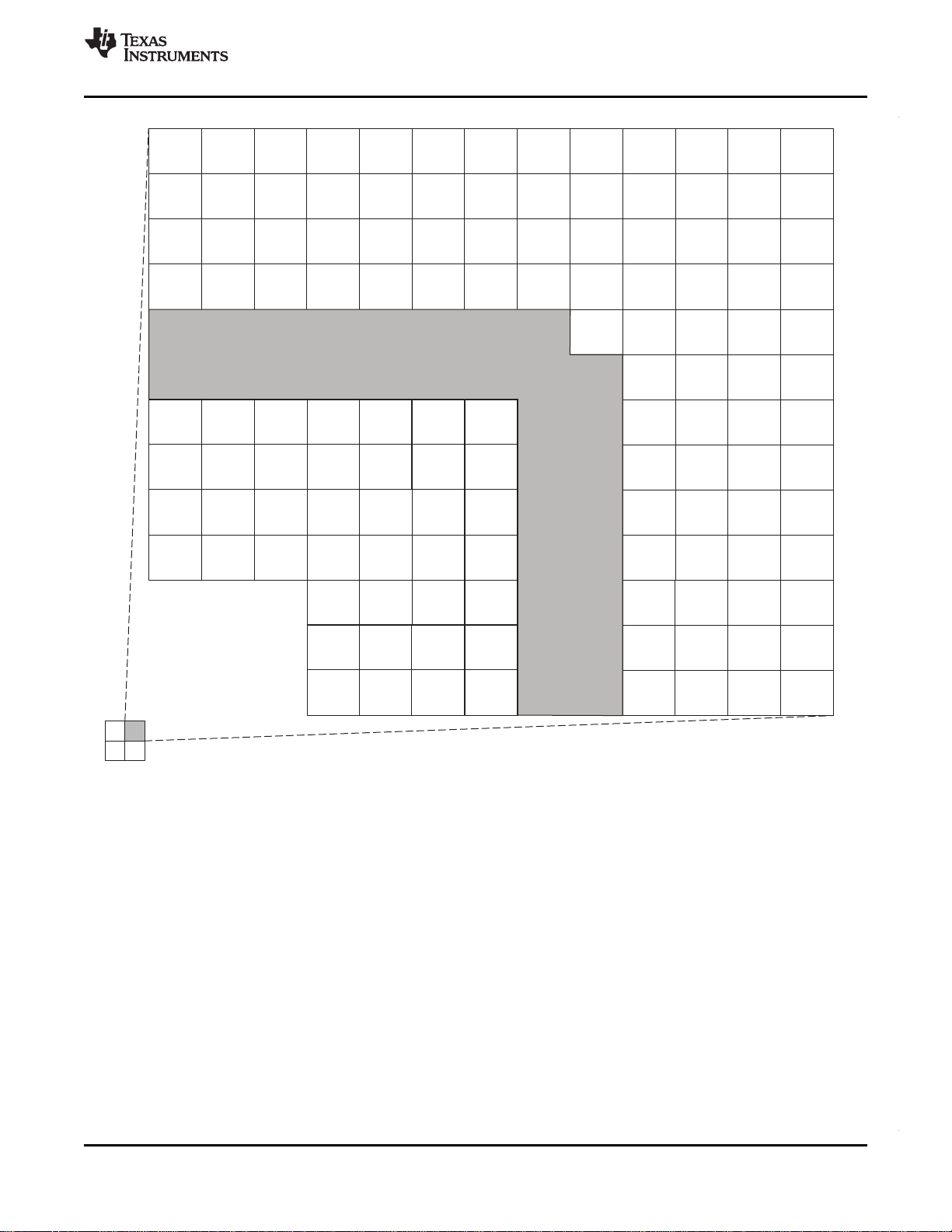

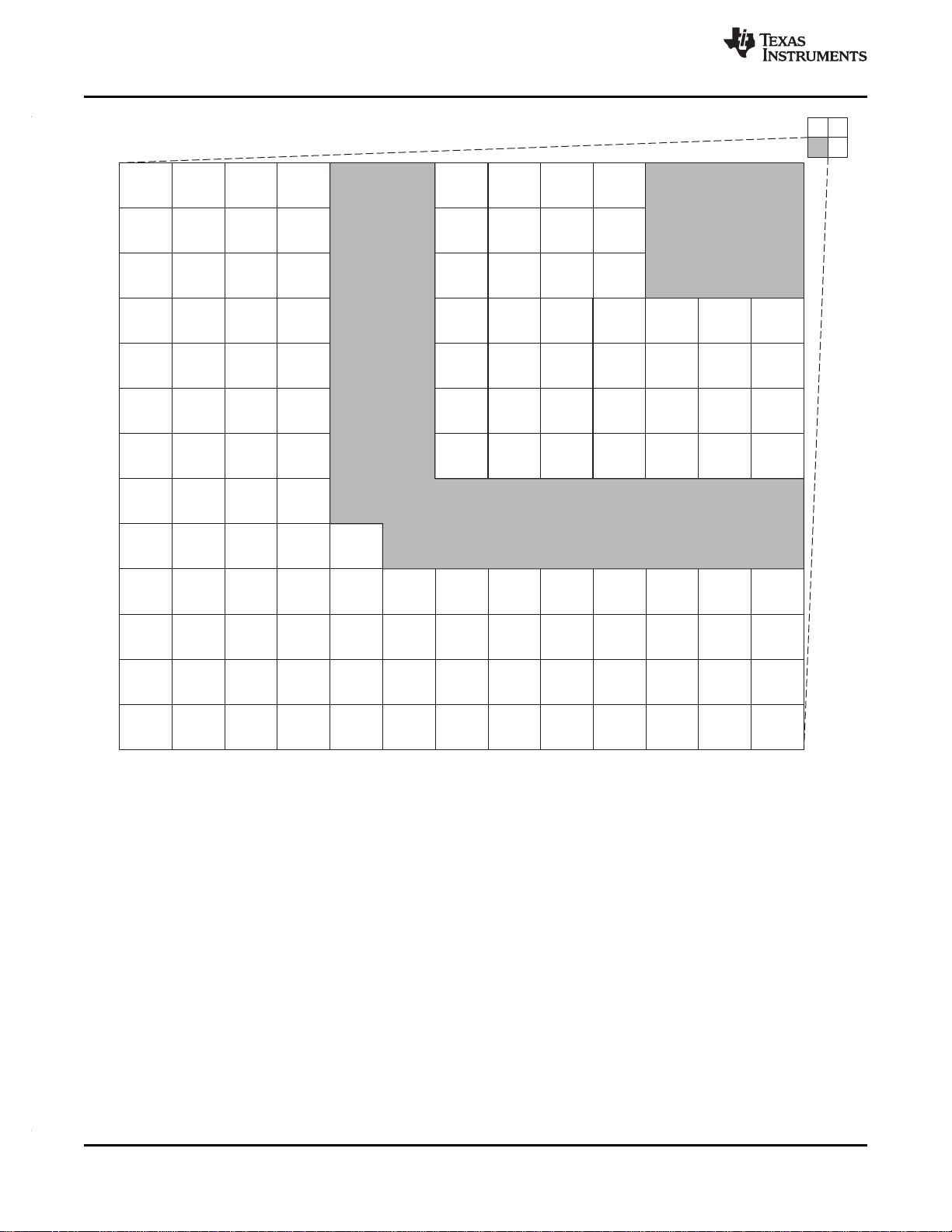

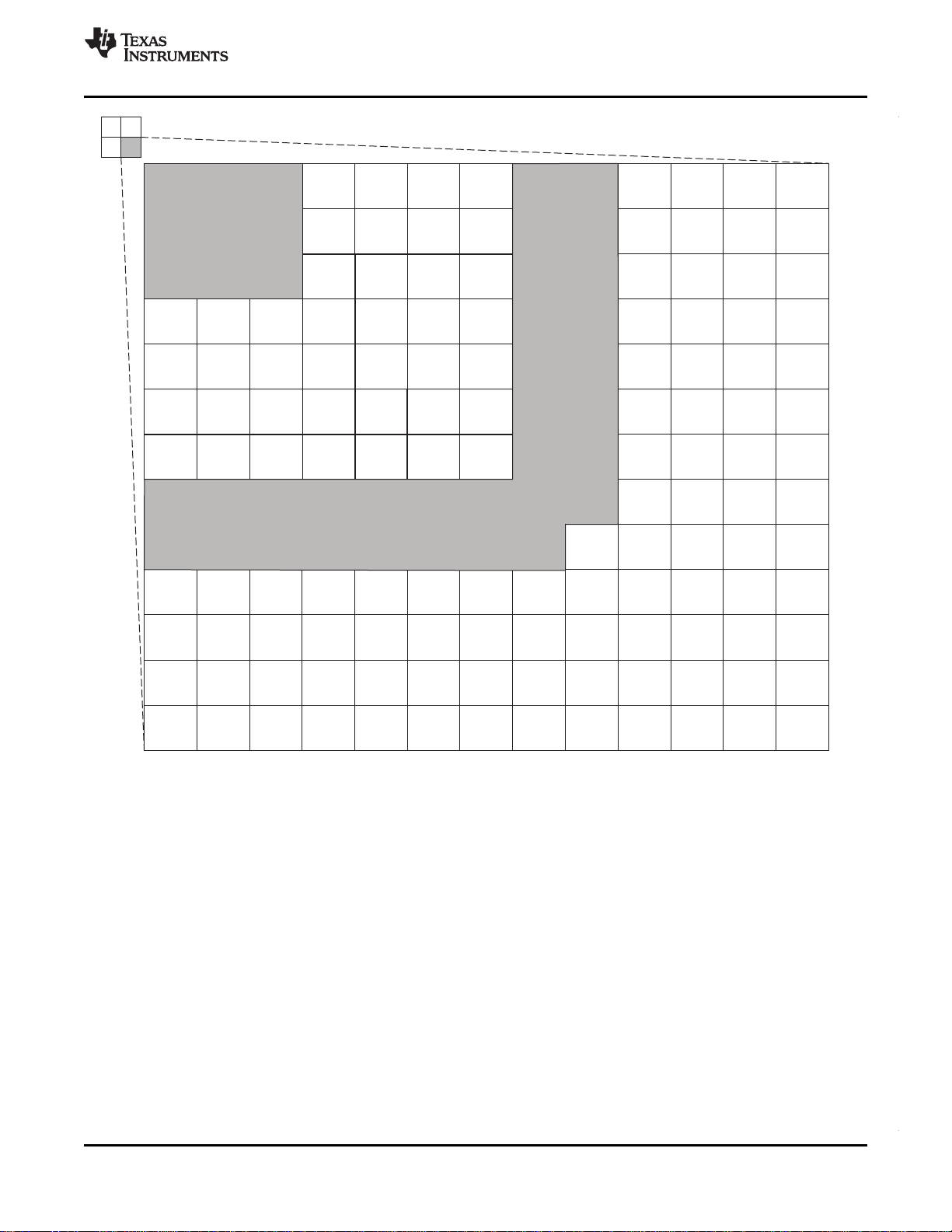

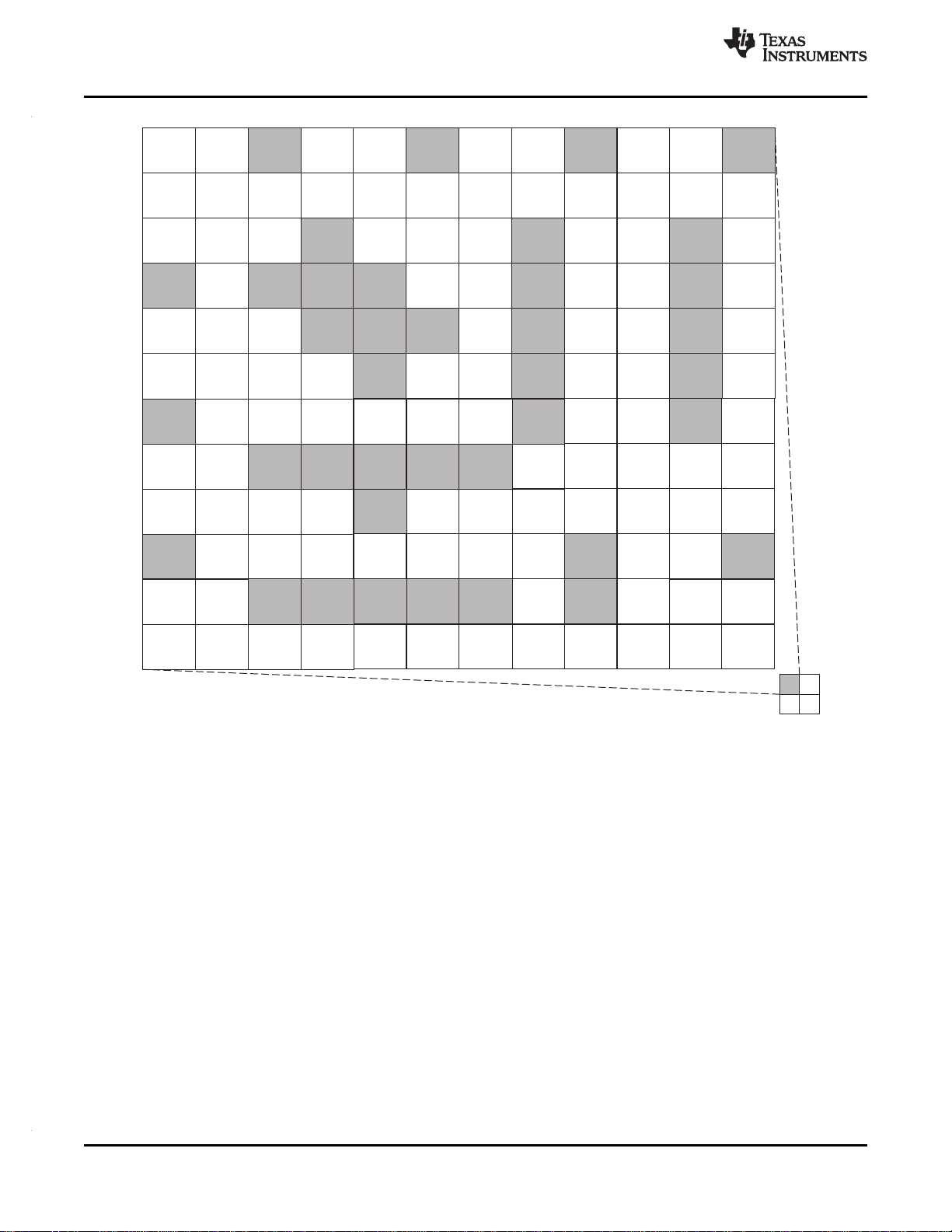

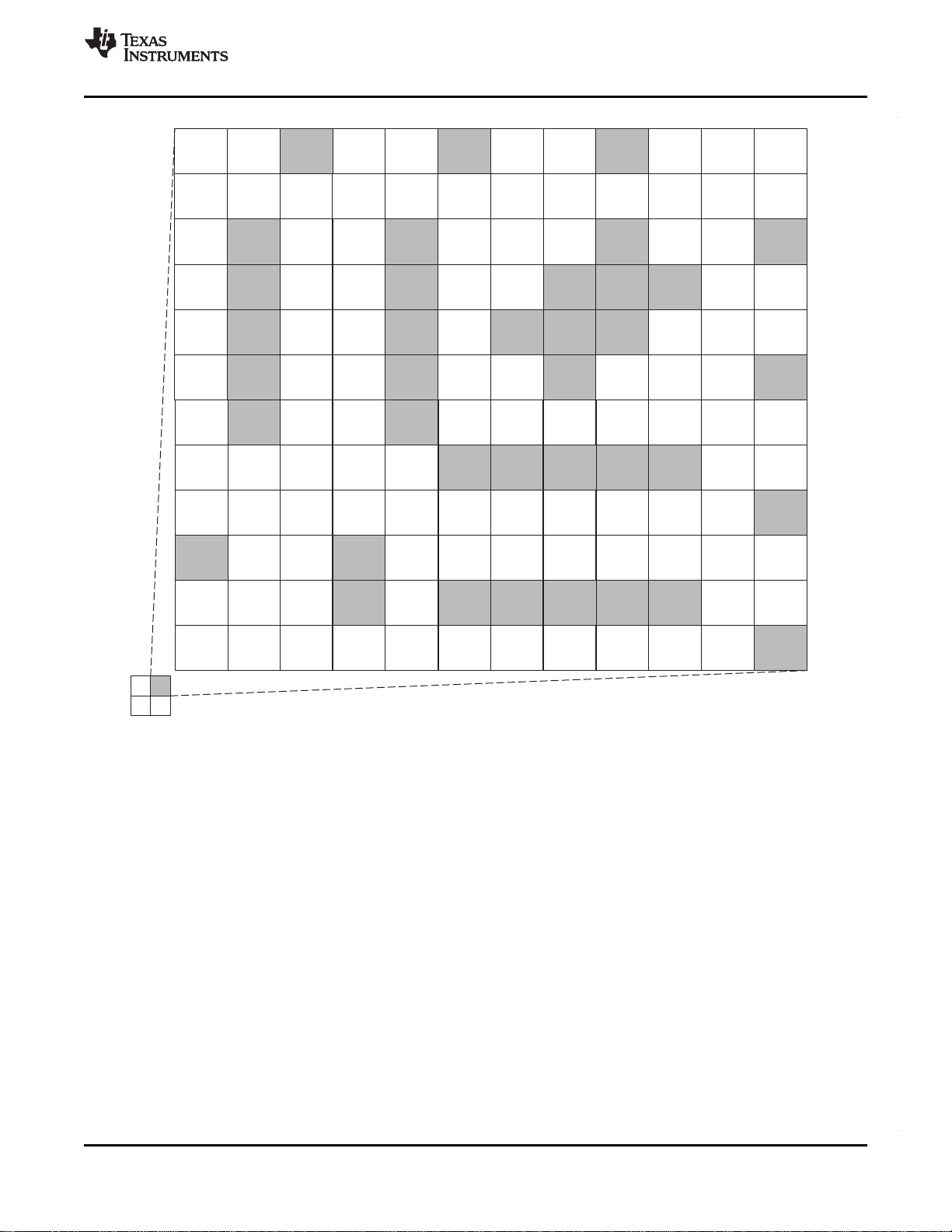

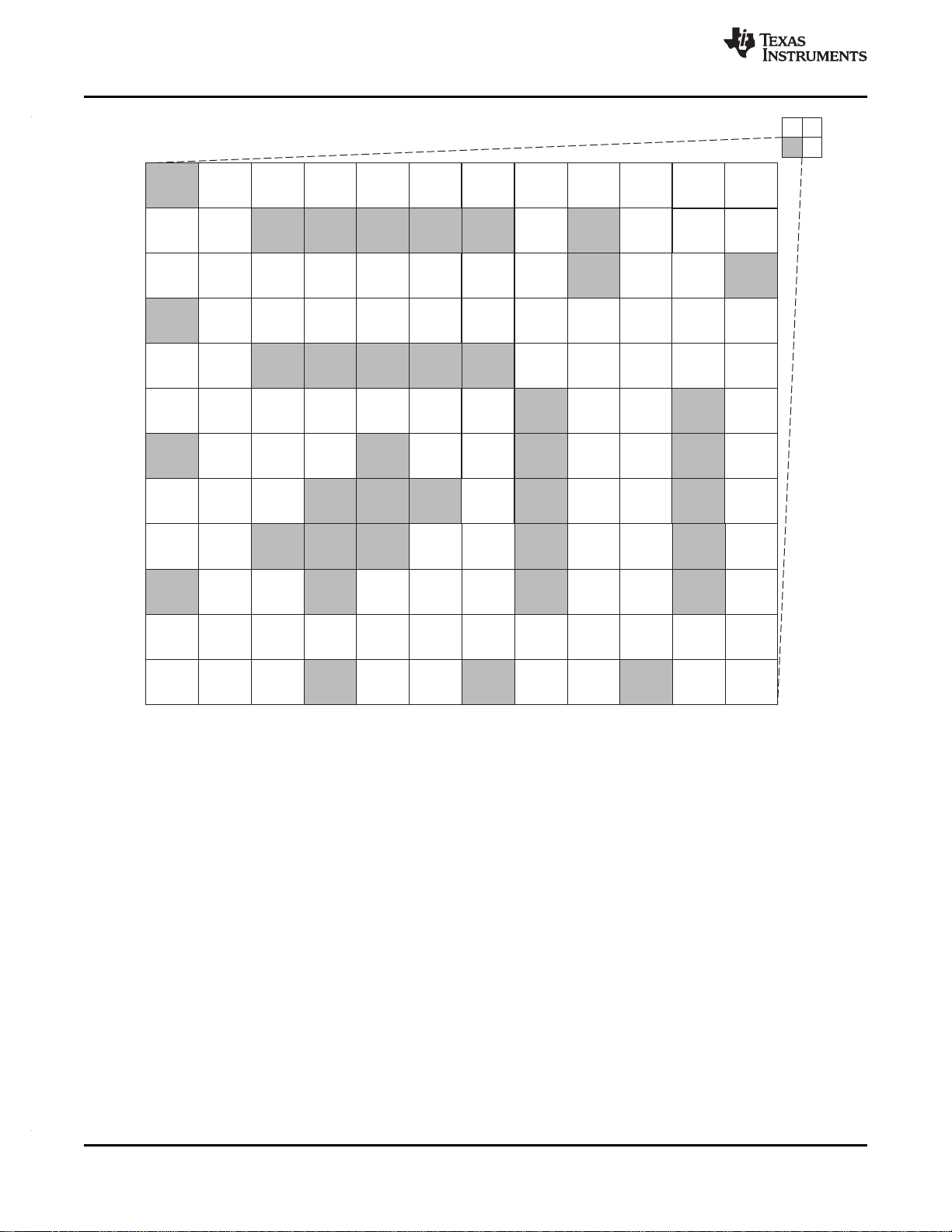

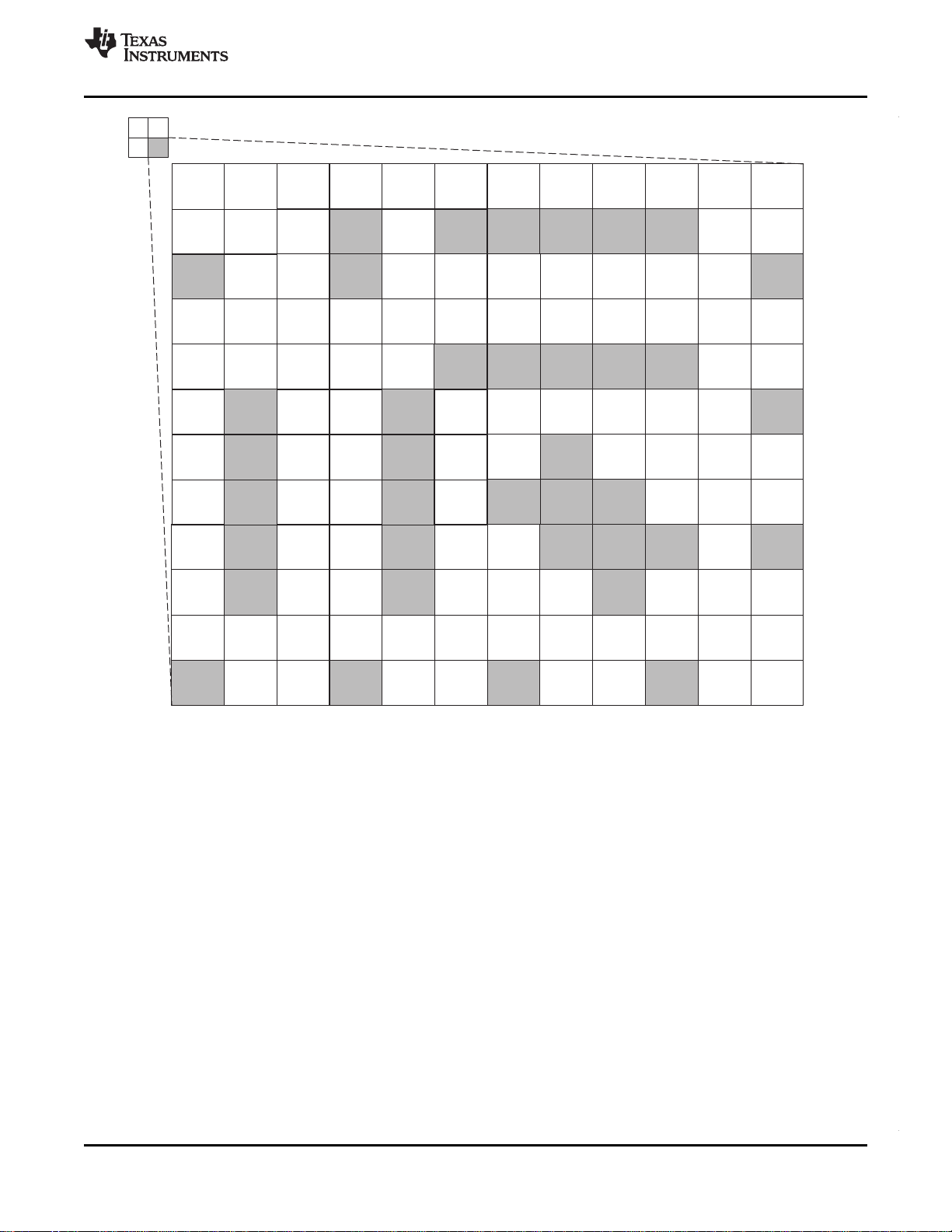

2 TERMINAL DESCRIPTION

2.1 Terminal Assignment

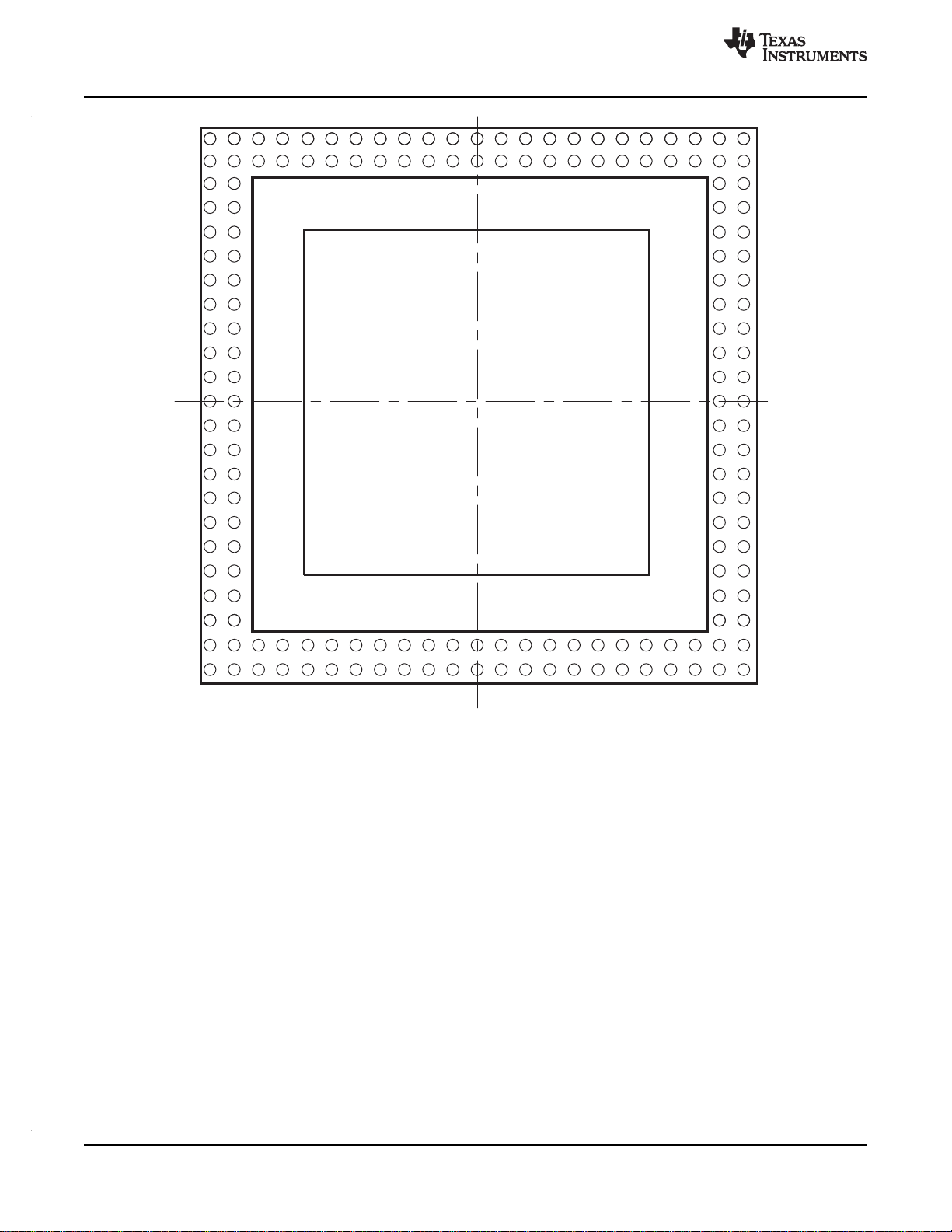

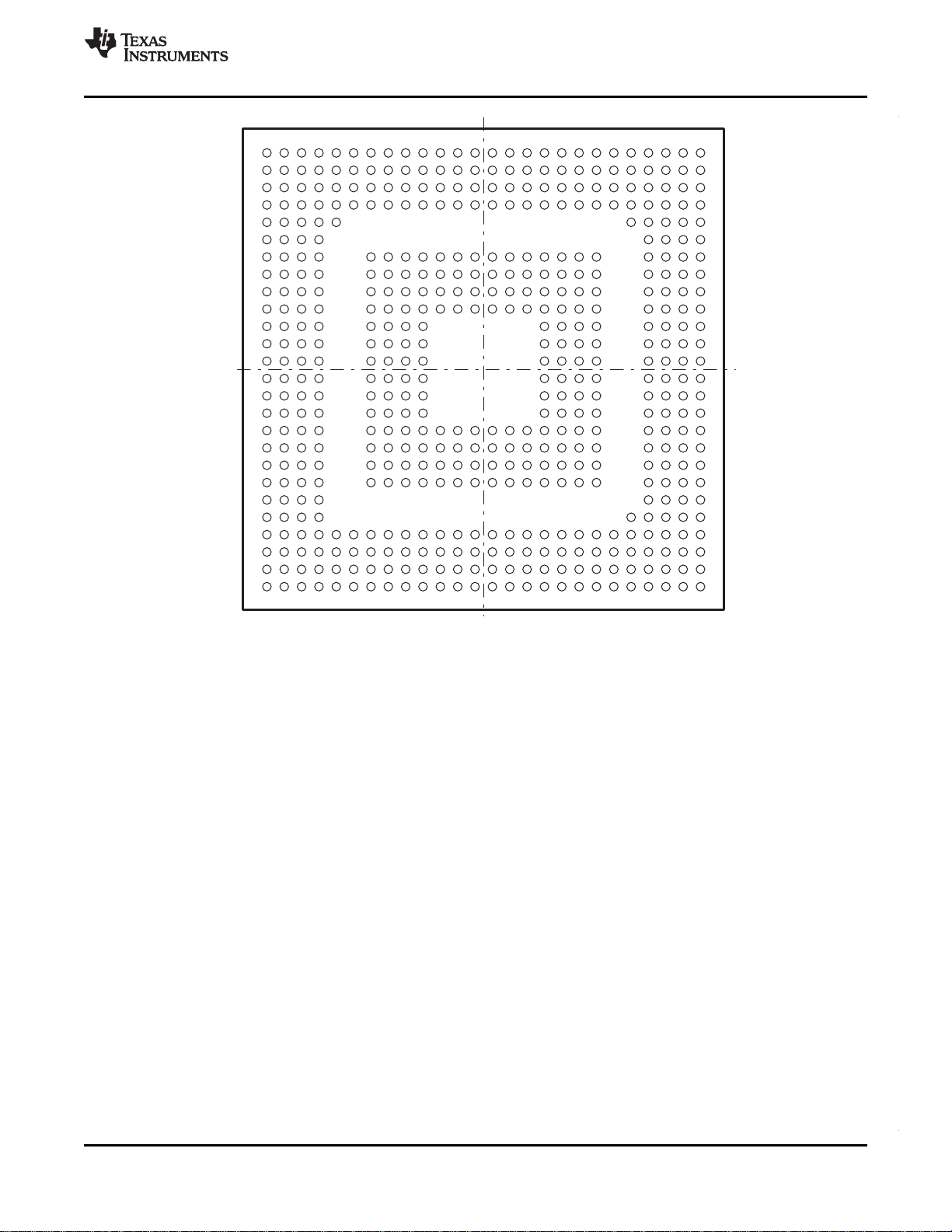

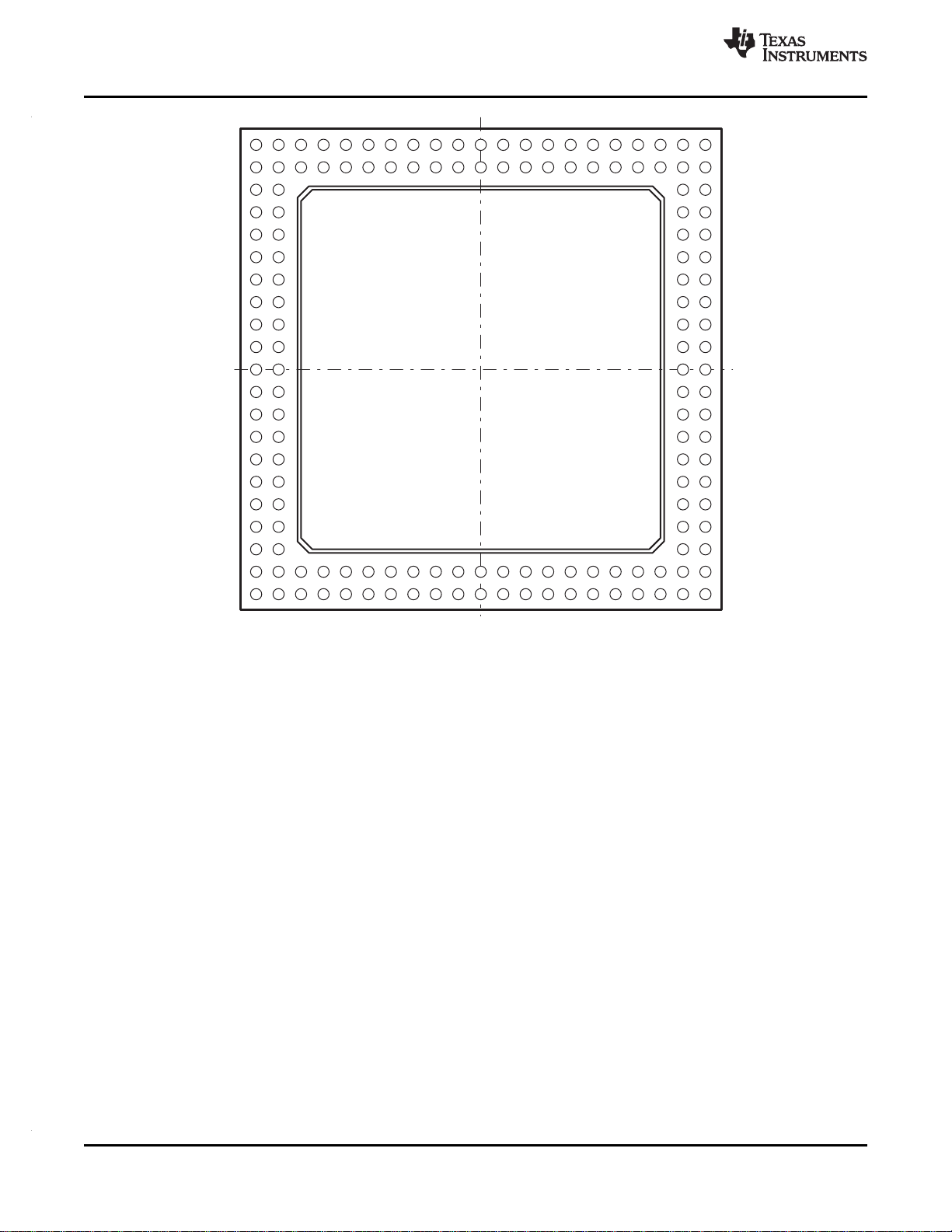

Figure 2-1 through Figure 2-5 show the ball locations for the 515- and 423- ball plastic ball grid array

(s-PBGA) packages. Table 2-1 through Table 2-25 indicate the signal names and ball grid numbers for

both packages.

Note: There are no balls present on the top of the 423-ball s-PBGA package.

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 7

Figure 2-1. DM3730/25 Digital Media Processor CBP s-PBGA-N515 Package (Bottom View)

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 8

PRODUCTPREVIEW

A

C

D

E

G

K

L

M

N

P

T

R

U

V

W

Y

AB

B

F

H

J

AA

AC

22

21

20

18

17

16

15

13

12 10

9

8

7

6

5

4

3

2

111

14

19

23

030-002

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

8 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Figure 2-2. DM3730/25 Digital Media Processor CBP s-PBGA-N515 Package (Top View)

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 9

PRODUCTPREVIEW

AF

AE

AD

AC

AB

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

1 2 3 4 56789

10 11

12 13 14 15 16 17 18 19 20 21 22 23

24 25 26

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-3. DM3730/25 Digital Media Processor CBC s-PBGA-515 Package (Bottom View)

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 9

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 10

PRODUCTPREVIEW

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

Figure 2-4. DM3730/25 Digital Media Processor CBC s-PBGA-515 Package (Top View)

10 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 11

PRODUCTPREVIEW

AD

AC

AB

AA

Y

W

V

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

1 2

3

4

5 6

7

8 9

10

11 121314

15 16

17

18 19

20

21 22

23

24

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-5. DM3730/25 Digital Media Processor CUS s-PBGA-N423 Package (Bottom View)

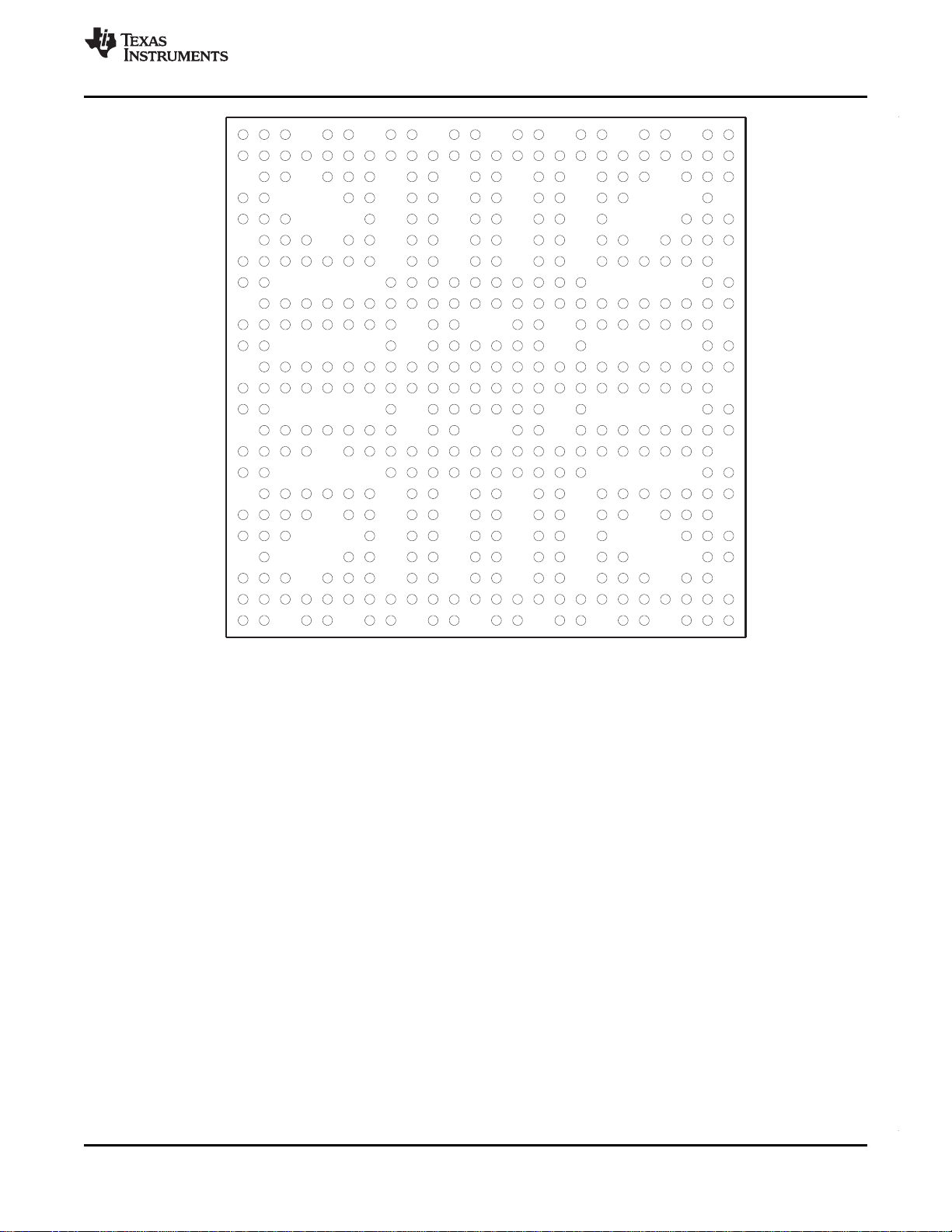

2.2 Pin Assignments

2.2.1 Pin Map (Top View)

The following pin maps show the top views of the 515-pin sPBGA package [CBP], the 515-pin sPBGA

package [CBC], and the 423-pin sPBGA package [CUS] pin assignments in four quadrants (A, B, C, and

D).

Note: A pin with an "NC" designator indicates No Connection. For proper device operation, these pins

must be left unconnected.

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 11

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 12

PRODUCTPREVIEW

A

98

vdds_mem

765432

NC

1

B

vdds_mem

vss

C

D

E

F

G

H

J

K

vdds_mem

NC

vdds_mem

NC

vss

vss

vdd_corevdd_core

vssvss

gpmc_nwe

gpmc_nadv

_ale

vdds_memvdds_mem

NC

gpmc_nbe0

_cle

gpmc_noe

NC

gpmc_wait3

vdd_core

gpmc_ncs1gpmc_d8

gpmc_nwp

vss

vdd_core

vss

vdds_memvdds_mem

vdd_mpu

_iva

gpmc_wait1

gpmc_a10gpmc_d9gpmc_d0

gpmc_a4

gpmc_wait2

vdd_mpu

_iva

gpmc_ncs0

vss

L

M

N

P

vdd_mpu

_iva

gpmc_wait0

gpmc_a9gpmc_d2

gpmc_d1

gpmc_ncs7

gpmc_a2

gpmc_a8

pop_k2

_m2

vss

gpmc_a1

gpmc_a7

pop_l2

_n2

pop_u1

_n1

vss

gpmc_d3gpmc_d10

vss

gpmc_ncs6

vss

gpmc_a3

14

NC

13

NC

121110

NC

vdds_mem

NC

vdds_mem

vssvss

vssvss

NCNC

NCNC

vssvss

vdd_mpu

_iva

vdd_mpu

_iva

vdd_mpu

_iva

vss

vdd_mpu

_iva

vdd_mpu

_iva

vss

vdd_mpu

_iva

NC

vdd_mpu

_iva

vdd_mpu

_iva

vdd_mpu

_iva

vss

pop_y23

_m1

NC NC

NC

NC

NC

NC

NC

NC

NC

NCNC

NCNCNC NCNCNC

NC

NC

NC NC

NC

NC NC

NC

NC

NC

NC NC

NC

NCNCNC

NC NC

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

A. Top Views are provided to assist in hardware debugging efforts.

Figure 2-6. CBP Pin Map [Quadrant A - Top View]

12 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 13

PRODUCTPREVIEW

A

20 21 22 23 24 25

cam_d5

26 27

pop_a22

_a27

28

B

cam_d2 cam_d10

vss

C

D

dss_hsync

E

F

G

H

J

K

vdds_mem

cam_vs

cam_hs

pop_a23

_a28

vdds_mem

cam_wen

cam_xclkb

pop_b23

_b28

vss

cam_fld

cam_d3

vss

cam_xclka

cam_d11

cam_pclk vdds_mem

vss

vdd_core cam_d4

dss_vsync

dss_pclk

vdd_core

dss_data6

dss_acbias

dss_data20

vdds

dss_data8

dss_data7

uart3_rx

_irrx

dss_data9

vss

vdds_mem

dss_data19 dss_data18 dss_data17

vdds

vdd_core

hdq_sio

dss_data21

pop_k1

_j28

vss

mcbsp1_fsx

cam_d8 cam_d6

vdds_

mmc1

vdd_core

dss_data16

cam_strobevdd_core

L

M

N

P

vss

vss

cam_d9

cam_d7

vdd_core

mmc1

_cmd

vss

vdd_core

mmc1

_dat2

mmc1

_dat1

mmc1

_dat0

mmc1

_clk

gpio_127

gpio_126

mmc1

_dat3

vdds_x

vdd_core

vdd_core

15

pop_a12

_a15

16

NC

17 18 19

NC

NC

vdds_mem

NC NC

vdds_mem

vdds_mem

NC

vss

vdd_core vdds_mem

NC

vss

NC

NC

uart3_cts

_rctx

uart3_rts

_sd

vss vss

vdd_core

vdda_dplls

_dll

vdd_core

vss

vss

vss vss

vdd_mpu

_iva

NC

NC

vdd_core

vdd_core

vdd_core

vss

i2c1_sda

cap_vdd

_sram_core

i2c1_scl

mcbsp2_dx

mcbsp2

_clkx

mcbsp2_fsx

uart3_tx

_irtx

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

pop_b12

_b15

vdds

pop_h22

_j27

pop_k22

_m26

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-7. CBP Pin Map [Quadrant B - Top View]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 13

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 14

PRODUCTPREVIEW

AH

9

etk_d5

8

etk_d15

7654

mmc2

_dat1

3

2

pop_ac2

_ah2

1

AG

mmc2

_cmd

mmc2

_dat2

vss

AF

etk_d8

AE

mmc2

_dat7

AD

AC

AB

AA

Y

W

etk_d13

vdds_mem

mmc2

_dat0

etk_d9etk_d14etk_d12

vssvss

pop_ab1

_ag1

etk_d11mcbsp3_dx

mcbsp3

_clkx

mmc2

_dat5

mmc2

_dat3

mmc2

_dat6

vdd_core

mcbsp3_dr

mcbsp3_fsx

mmc2

_clk

mcbsp4

_clkx

mcbsp4_dxmcbsp4_dr

vdd_core

mcspi1_cs1

mcspi1

_cs0

mcbsp4

_fsx

mcspi1_clk

mcspi1

_cs3

mcspi1

_cs2

uart1_tx

mcspi1

_somi

mcspi2_clk

pop_aa1

_aa1

vdd_mpu

_iva

mcspi2

_cs0

mcspi2

_somi

mcspi2_

simo

gpmc_d15

vdd_mpu

_iva

uart1_cts

vss

gpmc_d7

gpmc_d14

vdds

uart1_rx

uart1_rts

mcspi1

_simo

mmc2

_dat4

etk_d10

V

U

T

R

vss

gpmc_ncs2

mcspi2

_cs1

gpmc_d6

gpmc_d5

gpmc_ncs3

cap_vdd

_bb_mpu

_iva

gpmc_nbe1

vss

vdds_mem

vdd_mpu

_iva

gpmc_clk

gpmc_a5

gpmc_d13

gpmc_d4

vdd_mpu

_iva

gpmc_ncs5

gpmc_a6gpmc_d12gpmc_d11

vdds_mem

gpmc_ncs4

vss

cap_vdd

_sram

_mpu_iva

14

etk_d7

13121110

i2c3_scl

etk_d2

pop_ac9

_ah11

i2c3_sda

pop_ab11

_ag13

etk_d1

pop_ab9

_ag11

etk_d6

vss

etk_d0

etk_clk

sys_boot2

etk_d3

etk_d4etk_ctl

jtag_tckjtag_rtck

jtag_emu1

vdd_mpu

_iva

vdd_mpu

_iva

vdd_mpu

_iva

vss

vssvss

vdda_wkup

_bg_bb

vss

jtag_emu0

vss

vdd_mpu

_iva

vdd_mpu

_iva

vdd_mpu

_iva

vss

vdd_mpu

_iva

vss

vdd_mpu

_iva

pop_aa2

_aa2

vdds vdds

vdds

vdds

pop_u2

_af2

pop_ac8

_af1

pop_ab8

_ag10

pop_ac11

_ah13

pop_ac13

_ah10

pop_ac1

_ah1

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

Figure 2-8. CBP Pin Map [Quadrant C - Top View]

14 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 15

PRODUCTPREVIEW

AH

20

cap_vddu

_array

21

vss

22 23 24 25

sys

_nrespwron

26

27

pop_ac22

_ah27

28

AG

dss_data4 sys_clkout1

vdds

AF

vss

AE

i2c4_sda

AD

AC

AB

AA

Y

W

dss_data1

dss_data3

dss_data5

vdds

dss_data0

dss_data2

sys_boot1

pop_ab23

_ag28

sys_boot6

sys_off

_mode

sys

_nreswarm

sys_boot0

sys_clkreq

sys_nirq

vss

sys_boot5

vdds vdd_core

uart2_rx

i2c4_scl

dss_data11

dss_data10

vss vss

dss_

data22

dss_

data23

uart2_cts

dss_data13

dss_data12

uart2_tx

dss_

data15

dss_

data14

vss

vssa_dac

cvideo1

_out

cvideo1

_rset

cvideo2

_vfb

cvideo2

_out

vss

uart2_rts

sys_32ksys_clkout2

V

U

T

R

hsusb0

_data7

hsusb0

_data6

hsusb0

_data5

hsusb0

_data4

hsusb0

_data3

hsusb0

_data2

hsusb0

_data1

hsusb0_stp hsusb0_nxt

hsusb0

_data0

hsusb0_clk

vss

gpio_128

hsusb0_dir

gpio_129

vdda_dac

15 16

pop_ac14

_ah16

17 18 19

i2c2_scl

cam_d1

gpio_115

pop_ab13

_ag15

cam_d0

vdds

sys_xtalout sys_boot3

sys_boot4

i2c2_sda

vdd_core

vdd_core

sys_xtalin

jtag_tdi

mcbsp1

_clkr

vdd_core

vdd_core

mcbsp1_dx

mcbsp1

_clkx

vdd_core

vdd_core

mcbsp1_dr

mcbsp_clks

vss

mcbsp2_dr

vss

cap_vddu

_wkup

_logic

vdda_dpll

_per

jtag_tms

_tmsc

jtag_tdo

vdd_core

sys_

xtalgnd

vdd_core

vdd_mpu

_iva

vdd_core

vss

vss

vdds_sram

vss

vdd_mpu

_iva

jtag_ntrst

vdd_core

vdd_core

vdd_core

vss

mcbsp1_fsr

NC

NC

cvideo1

_vfb

pop_aa23

_ae28

vdds

pop_h23

_af28

pop_aa22

_af27

vdds

pop_l1

_ah15

gpio_113

pop_ac23

_ah28

vss

gpio_114

gpio_112

vdds

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-9. CBP Pin Map [Quadrant D - Top View]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 15

Product Folder Link(s): DM3730 DM3725

Submit Documentation Feedback

Page 16

PRODUCTPREVIEW

A

98765432

NC

1

B

vss

C

D

E

F

G

H

J

K

gpmc

_a11

pop_a1

_a1

NC

gpmc_

ncs2

vdds

uart1

_rx

vdd_mpu

_iva

mmc2

_dat7

vss

L

M

N

gpmc

_d14

pop_j1

_l1

mcbsp3

_dr

cap_vdd

_sram

_mpu_iva

vdds

13121110

vdd_mpu

_iva

vss

vdd_mpu

_iva

vdda_

dplls_

dll

vdd_mpu

_iva

gpmc_

ncs4

gpmc_

wait2

NC vss

cap_

vdd_bb

_mpu_iva

NC

sys_

boot6

i2c2_scl vss

vss

NC vss NC NC NC NC vss

NC

vdd_

core

gpmc_

ncs6

gpmc_

ncs3

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

vdds

NC

NC

NC

NC

gpmc_

wait3

gpmc_

ncs7

gpmc_

ncs5

sys_

boot2

sys_

boot1

I2C2_SDA

gpmc

_a9

gpmc

_a10

gpmc

_a7

gpmc

_a8

sys_

boot3

sys_

boot4

gpmc

_a5

gpmc

_a6

sys_

boot0

NC

vss

gpmc

_a4

sys_

boot5

vdds

gpmc

_a2

gpmc

_a3

vss

gpmc

_nbe1

gpmc

_a1

NC NC

vss

gpmc

_nbe0

_cle

NC

mmc2

_dat6

gpmc

_nwe

gpmc

_d15

mmc2

_dat5

uart1

_tx

gpmc

_clk

gpmc

_noe

vss

NC

vdd_mpu

_iva

vss

vdd_mpu

_iva

NC vss

vdd_mpu

_iva

NC NC NC NC NC

NC

NC

NC

NC

vssNC

vdd_

core

vdds

NC

NCNCNC

NC

NC

NC

vdd_mpu

_iva

vdd_mpu

_iva

NC

NC

vss

vdd_mpu

_iva

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

A. Top Views are provided to assist in hardware debugging efforts.

Figure 2-10. CBC Pin Map [Quadrant A - Top View]

16 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 17

PRODUCTPREVIEW

A

18 19 20 21 22 23

cam_wen

24 25 26

B

NC

cam_d2

C

D

E

F

G

H

J

K

pop_b16

_a20

NC NC

NC

NC

pop_

b21_b26

NC

NC

NC

cam_

xclka

NC

NC NC

NC

uart3_

rts_sd

dss_

data20

dss_

acbias

dss_

data7

hdq_sio

vdd_

core

L

M

N

vdds_

mmc1

cam_d9

14

NC

15 16 17

NC

NC

NC NC

NC

NC

NC

NC

vss

NC

vss

cap_vddu_

wkup_

logic

vss

vdd_

core

i2c1_scl

NC

NC

NC

vdds

NC

NC

NCNC

NC

vss

vss

NC NC

NC vss

cam_d3

cam_d5

cam_d4

vdds

cam_fld

cam_hs

cam_vs

vss

pop_

a20_a25

pop_

a21_a26

cam_

pclk

cam_d10

cam_

strobe

cam_d11

dss_

pclk

cam_

xclkb

dss_

data6

uart3_

cts_

rctx

uart3_

tx_

irtx

vss

NC

uart3_

rx_

irrx

dss_

data8

dss_

data9

i2c1_sda

pop_

h21_k26

vss

dss_

hsync

NC

vss

vdds

dss_

data16

dss_

data17

dss_

data19

dss_

vsync

dss_

data18

NC

cam_d8

dss_

data21

NC NC

gpio_126

vdd_

core

NC vss

vdd_

core

NCNCNCNCNCNC

NCNC

vdds

NCNC

vdds

NC

NC NC

mmc1_

dat2

NC

cap_vdd

_sram_

core

vdds

vss

mmc1_

cmd

mmc1_

dat0

mmc1_

dat1

mmc1_

dat3

mmc1_

clk

NCvss

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-11. CBC Pin Map [Quadrant B - Top View]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 17

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 18

PRODUCTPREVIEW

AF

9

etk_d14

87654321

AE

AD

AC

AB

AA

Y

W

V

U

etk_d13

sys_

nres

warm

pop_t2

_y2

NC

etk_d9

gpmc

_d8

vdd_mpu

_iva

T

R

P

pop_n2

_t2

gpmc

_d10

mcbsp4

_dx

uart1

_rts

mcspi1

_clk

NC

mcbsp3

_dx

gpmc

_d13

mcspi1

_simo

13121110

gpmc_

nadv_ale

jtag_

rtck

NC

vdd_mpu

_iva

sys_

nresp

wron

sys_off

_mode

vdd_mpu

_iva

vdd_mpu

_iva

vdds_

sram

vss

i2c3_scl

pop_aa11

_af13

pop_y9_

_af10

NC

uart1

_cts

vdd_

core

mcspi1

_cs0

mcspi1

_somi

jtag_

tdo

vdd_

core

vss

NC

vss vss

mcspi1

_cs1

mcspi1

_cs2

mmc2

_cmd

mmc2

_dat0

mmc2

_dat1

mcspi1

_cs3

vdds

mcbsp4

_fsx

gpmc

_d12

gpmc

_d11

mcbsp3

_clkx

mcbsp4

_dr

vdd_

core

mcspi2

_somi

mmc2

_dat3

mmc2

_dat2

vdd_mpu

_iva

mmc2

_dat4

mcspi2

_cs1

mcspi2

_cs0

vdd_mpu

_iva

mcbsp4

_clkx

mcbsp3

_fsx

vss

mcspi2

_clk

mcspi2

_simo

vdd_mpu

_iva

mmc2

_clk

sys_

clkout2

vdd_mpu

_iva

vdd_mpu

_iva

vdd_

core

vss

vdds

etk_d4

gpmc

_d9

gpmc

_d1

gpmc

_d0

etk_d3

etk_d8

etk_d5

etk_clk

etk_ctl

vss

gpmc

_d3

gpmc

_d2

etk_d0 i2c3_sda

gpmc

_d7

gpmc

_nwp

vdds

gpmc

_wait1

NC vss

gpmc

_wait0

NC NC

NCNCNCNC

gpmc

_ncs0

gpmc

_d5

etk_d1etk_d2

etk_d7

gpmc

_ncs1

gpmc

_d6

NC

pop_w2

_ae2

etk_d6 etk_d10

gpmc

_d4

etk_d12

vss NC

etk_d15

vdds

NC NC NC

pop_aa10

_af12

NC

pop_y7_

_af8

etk_d11

pop_aa6

_af5

pop_y2

_af4

NCNC

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

Figure 2-12. CBC Pin Map [Quadrant C - Top View]

18 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 19

PRODUCTPREVIEW

AF

18

19

sys_

xtalin

20 21 22

23

sys

_xtalgnd

24

25 26

AE

dss_

data1

AD

AC

AB

AA

Y

W

V

U

pop_y21

_ae26

vdd_

core

uart2

_cts

dss_

data13

dss_

data12

cvideo1

_rset

vssa_

dac

cvideo2

_out

cvideo2

_vfb

pop_

p21_u26

T

R

P

vdds

vdds_x

NC

cam_d7

14

pop_aa12

_af14

15 16 17

cam_d1 cam_d0

gpio_113

mcbsp1

_clkr

hsusb0

_data2

mcbsp2

_dx

gpio_129

gpio_128

vdda_

wkup_

bg_bb

i2c4_sda

jtag_tms

_tmsc

jtag_tdi

vss

vdda_

dpll_per

jtag_

ntrst

sys_nirq

gpio_127

vss

pop_aa21

_af26

sys_

clkout1

cap

_vddu

_array

mcbsp1

_dr

hsusb0

_stp

mcbsp2

_clkx

mcbsp1

_fsx

jtag_

emu1

cam_d6

NC NCNCNC

vdd_

core

mcbsp1

_clkx

mcbsp2

_dr

mcbsp

_clks

vss NC NC

vssNC

mcbsp2

_fsx

mcbsp1

_dx

jtag_tck

mcbsp1

_fsr

hsusb0

_dir

hsusb0

_data0

vdda_

dac

cvideo1

_out

cvideo1

_vfb

vdds

vss

hsusb0

_data3

hsusb0

_clk

hsusb0

_nxt

hsusb0

_data4

sys_

clkreq

jtag_

emu0

vss

hsusb0

_data7

hsusb0

_data5

hsusb0

_data6

hsusb0

_data1

NC vss

dss_

data14

uart2

_rts

NC

NC

vdds

dss_

data23

dss_

data15

dss_

data10

dss_

data22

vdds

NCNC

sys_32k

vss

vdds

NC

vss

NC

vdds

NC

vss

i2c4_scl gpio_112

vdds

vdds

vdds

uart2

_rts

uart2

_rx

uart2

_tx

dss_

data4

dss_

data5

vss

dss_

data11

pop_y20

_ae25

pop_aa20

_af25

pop_y19

_af24

pop_

aa19_af22

pop_y17

_af21

dss_

data3

dss_

data2

dss_

data0

gpio_114gpio_115

pop_aa13

_af15

pop_aa14

_af16

pop_y14

_af17

pop_aa17

_af18

sys_

xtalout

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-13. CBC Pin Map [Quadrant D - Top View]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 19

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 20

PRODUCTPREVIEW

A

987654321

B

C

D

E

F

G

H

J

K

sdrc_a0

NC

NC

L

M

gpmc

_d0

mcspi2

_cs1

121110

sdrc

_dqs0

sdrc

_dm2

vdds_x

gpmc

_ncs3

gpmc

_nwp

gpmc

_nadv

_ale

gpmc

_noe

gpmc

_a10

gpmc

_a8

gpmc

_a9

gpmc

_a6

gpmc

_d2

vdd_mpu

_iva

vss

vss

vdd_mpu

_iva

gpmc_

nbe0_cle

vdd_mpu

_iva

vdd_mpu

_iva

NC

sdrc

_dqs2

sdrc

_clk

sdrc

_nclk

sdrc_a4 sdrc_a3 sdrc_a1 sdrc_d3

sdrc

_dm0

sdrc_d7 sdrc_d18 sdrc_d19 sdrc_d21 sdrc_d8 sdrc_d10

sdrc_d9sdrc_d20sdrc_d16sdrc_d6sdrc_d2sdrc_d1sdrc_a5

gpmc

_wait3

gpmc

_wait0

sdrc_a2 sdrc_d0 sdrc_d4 sdrc_d5 sdrc_d22

sdrc_d17sdrc_a8sdrc_a9sdrc_a10

sdrc_a6

gpmc

_ncs0

gpmc

_ncs6

gpmc

_ncs4

sdrc_a7 sdrc_a13

sdrc_a14

vdd_

core

vdd_mpu

_iva

sdrc_a12sdrc_a11

gpmc

_ncs5

gpmc

_ncs7

gpmc

_nwe

vdd_mpu

_iva

vdd_mpu

_iva

vdd_

core

vdd_

core

vssvss

vdd_mpu

_iva

vdd_mpu

_iva

vdds

_mem

vdds

_mem

vdds

_mem

gpmc

_a4

gpmc

_a5

gpmc

_a7

gpmc

_a3

gpmc

_a2

gpmc

_a1

vdds

_mem

vdds

_mem

vdds

_mem

vss

vss

vdd_mpu

_iva

vssvss

gpmc_

nbe1

gpmc

_d1

gpmc

_d4

mcspi2

_cs0

vdd_mpu

_iva

vdd_mpu

_iva

vdd_mpu

_iva

vss

vss

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

A. Top Views are provided to assist in hardware debugging efforts.

Figure 2-14. CUS Pin Map [Quadrant A - Top View]

20 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 21

PRODUCTPREVIEW

A

16 17 18 19 20 21 22 23 24

B

cam_hs

C

D

E

F

G

H

J

K

dss_

data9

dss_

data19

dss_

acbias

L

M

13 14 15

sdrc_

dqs1

vdd_

core

cam_

xclka

uart3_

_cts_

rctx

hdq_si0

dss_

data6

dss_

data18

i2c1_sda

mmc1_

cmd

vdda

_dplls

_dll

cap_vdd

_sram

_core

vdds_

mem

cam_vs

vdd_

core

vss

cam_

strobe

cam_

pclk

vss

sdrc_

d14

sdrc_

dm3

sdrc_

dqs3

sdrc_

ncs0

sdrc_

nwe

uart3_

_rx_

irrx

uart3_

_rts_

sd

cam_d5

sdrc_

cke0

sdrc_

ncs1

sdrc_

d31

sdrc_

d30

sdrc_

d27

sdrc_

d15

sdrc_

d13

sdrc_

dm1

sdrc_

d12

sdrc_

d26

sdrc_

d28

sdrc_

ba0

sdrc_

ncas

sdrc_

cke1

cam_

xclkb

uart3_

_tx_

irtx

dss_

data20

sdrc_

nras

sdrc_

ba1

sdrc_

d29

sdrc_

d25

sdrc_

d11

sdrc_

d23

sdrc_

d24

vdds

dss_

hsync

dss_

data7

dss_

data8

dss_

vsync

cam_d10

cam_d3cam_wen

vdds_

mem

vdds_

mem

vdd_

core

vdds_

mem

vdds_

mem

cam_d2 cam_d4 cam_d11

dss_

pclk

dss_

data17

cam_fld

vdds_

mem

vss

vdd_

core

vss vss vss vss

vdd_

core

vdd_

core

dss_

data16

cam_d8

cam_d7cam_d9

dss_

data21

i2c1_scl

vdd_

core

vdd_

core

vdd_

core

vssvss

vss

vdd_

core

vdd_

core

vss

cam_d6

mmc1_

clk

mmc1_

dat0

mmc1_

dat1

mmc1_

dat2

vdds

vdds

vss

vdd_

core

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-15. CUS Pin Map [Quadrant B - Top View]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 21

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 22

PRODUCTPREVIEW

AD

9

etk_d14

87654321

AC

AB

AA

Y

W

V

U

T

R

sys_

nres

warm

vdd_mpu

_iva

P

N

gpmc

_d3

uart1

_rx

121110

vdd_mpu

_iva

vss

NC

uart1

_rts

vss

mcspi2

_clk

mmc2

_dat3

gpmc

_d7

gpmc

_d8

mcspi2

_simo

mcspi1

_cs0

vdd_mpu

_iva

sys_

clkout1

etk_d4

gpmc

_d14

gpmc

_clk

etk_clk

sys_

clkout2

vdds

jtag_tms

_tmsc

vdds_

sram

sys_

boot0

uart1_

cts

etk_d10 etk_d8 etk_d1 etk_d12

i2c3_sda

etk_d0

mcbsp3

_dx

mcspi1

_simo

mcbsp1

_cs3

cap_vddu_

wkup_logic

vdd_mpu

_iva

vdd_mpu

_iva

mcspi2

_somi

vdd_mpu

_iva

vss

vss

vss

vss

vdd_mpu

_iva

vss

vss

vss

vss

vss

gpmc

_d11

gpmc

_d5

gpmc

_d6

vdd_mpu

_iva

vdd_mpu

_iva

mcspi1

_clk

gpmc

_d9

gpmc

_d12

mcspi1

_somi

vssvssvss

vssvss

cap_vdd

_sram_

mpu_iva

gpmc

_d13

gpmc

_d10

vdd_mpu

_iva

vddsvdds

mcbsp3

_fsx

gpmc

_d15

mcbsp3

_dr

vdd_mpu

_iva

vddsvdds

uart1

_tx

mcbsp3

_clkx

mmc2

_dat2

vdds

mmc2

_dat1

mmc2

_dat6

mmc2

_clk

mmc2

_dat7

mmc2

_dat5

jtag_

rtck

sys_

nres

pwron

jtag_

tdi

jtag_

tdo

jtag_

ntrst

jtag_

tck

mmc2

_cmd

mmc2

_dat0

mmc2

_dat4

etk_d2 etk_d11etk_d6

etk_d5

etk_ctl

etk_d9

etk_d3 etk_d7 etk_d13 etk_d15

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

www.ti.com

Figure 2-16. CUS Pin Map [Quadrant C - Top View]

22 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 23

PRODUCTPREVIEW

AD

16

17

sys_

xtalin

18 19 20

21 22 23 24

AC

dss_

data3

AB

AA

Y

W

V

U

T

R

dss_

data15

dss_

data14

cvideo1

_rset

P

N

13 14 15

mcbsp1

_clkx

vdds

vss

hsusb0

_stp

mmc1_

dat3

gpio_126

cap_vdd

_bb_mpu

_iva

vdd_

core

hsusb0

_dir

hsusb0

_data0

cvideo2

_out

cvideo1

_vfb

sys_

clkreq

dss_

data23

sys_32k

sys_

boot6

vdda_

wkup

_bg_bb

i2c3_scl

vssa_dac

cam_d0

dss_

data12

sys_off

_mode

dss_

data10

dss_

data5

dss_

data0

cap_vddu

_array

sys_

xtalgnd

jtag_

emu0

i2c4_scl

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vss

vdds

vdds

vdds_

mmc1

gpio_129

vss

hsusb0

_clk

mcbsp2

_dx

vdd_

core

vdd_

core

hsusb0

_nxt

hsusb0

_data1

hsusb0

_data7

mcbsp2

_clkx

vdd_

core

vdd_

core

vdd_

core

vdd_

core

hsusb0

_data2

hsusb0

_data3

vdda_

dpll

_per

vdd_mpu

_iva

vdd_mpu

_iva

mcbsp2

_dr

mcbsp2

_fsx

dss_

data22

hsusb0

_data5

hsusb0

_data6

hsusb0

_data4

mcbsp1

_clkr

sys_

nirq

mcbsp1

_dx

vdd_mpu

_iva

cvideo2

_vfb

dss_

data13

mcbsp1

_dr

i2c4_sda

mcbsp

_clks

mcbsp1

_fsx

cvideo1

_out

mcbsp1

_fsr

dss_

data1

sys_

boot5

vdda_

dac

i2c2_sda i2c2_scl

sys_

boot1

sys_

boot4

cam_d1

dss_

data11

jtag_

emu1

dss_

data4

dss_

data2

sys_

boot3

sys_

boot2

sys_

xtaout

DM3730, DM3725

www.ti.com

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

Figure 2-17. CUS Pin Map [Quadrant D - Top View]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 23

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 24

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

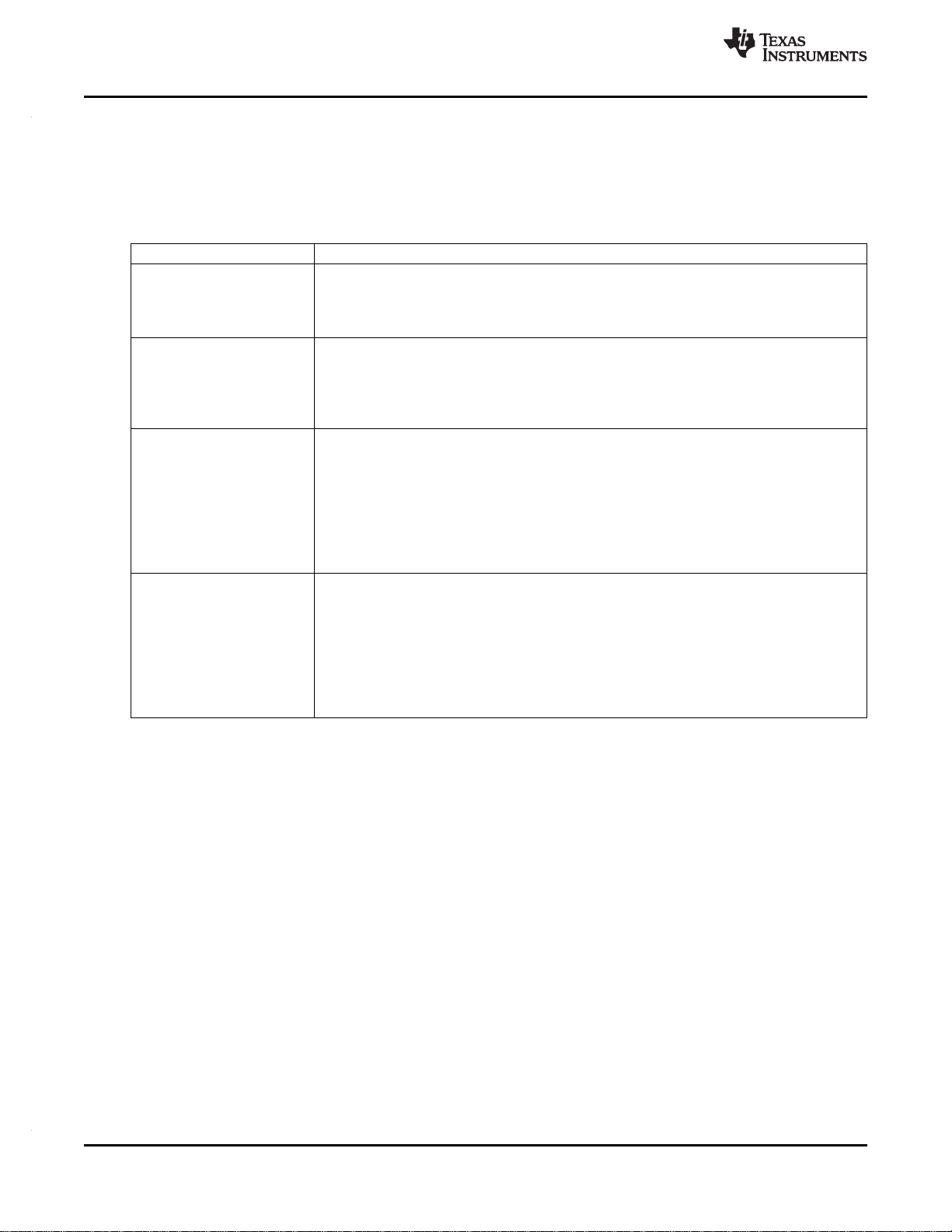

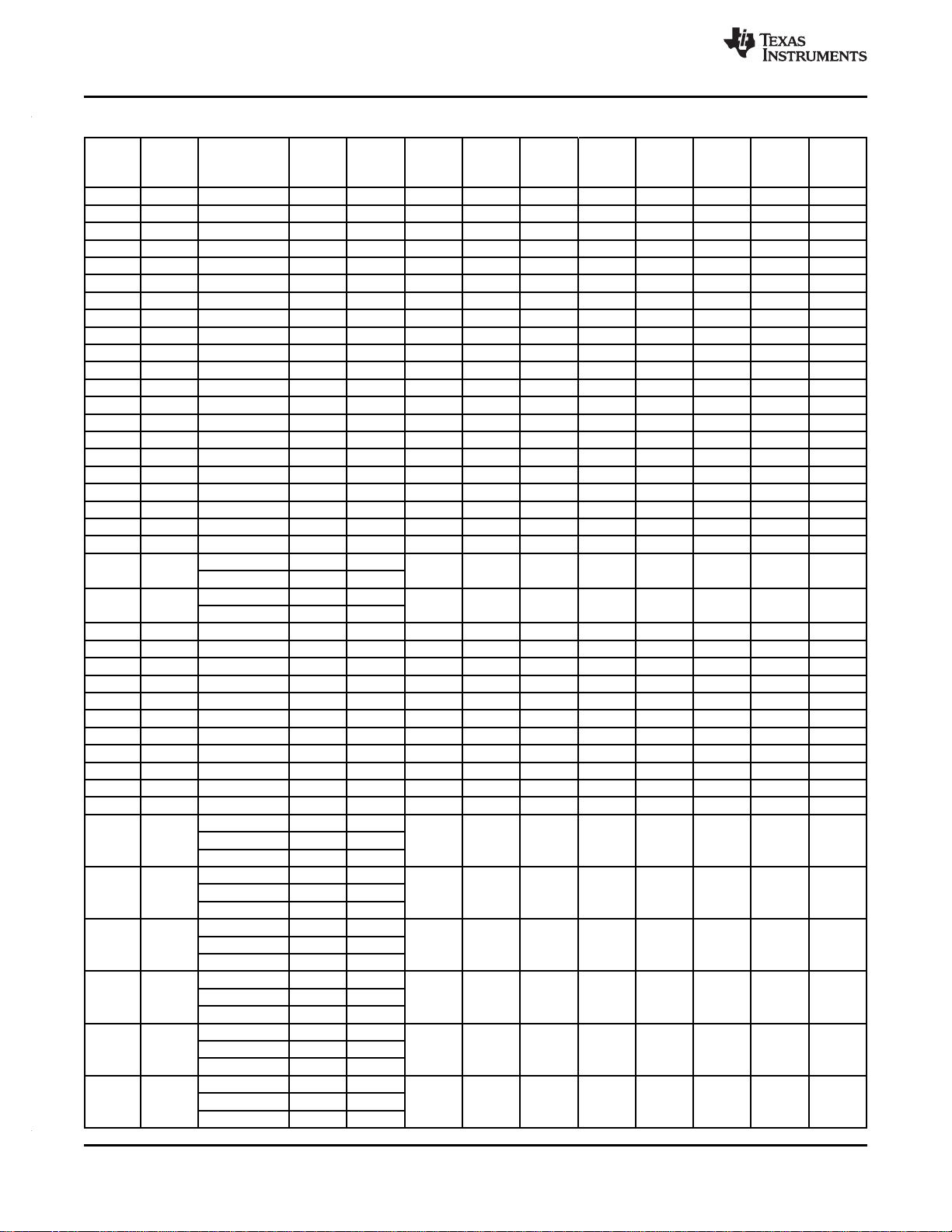

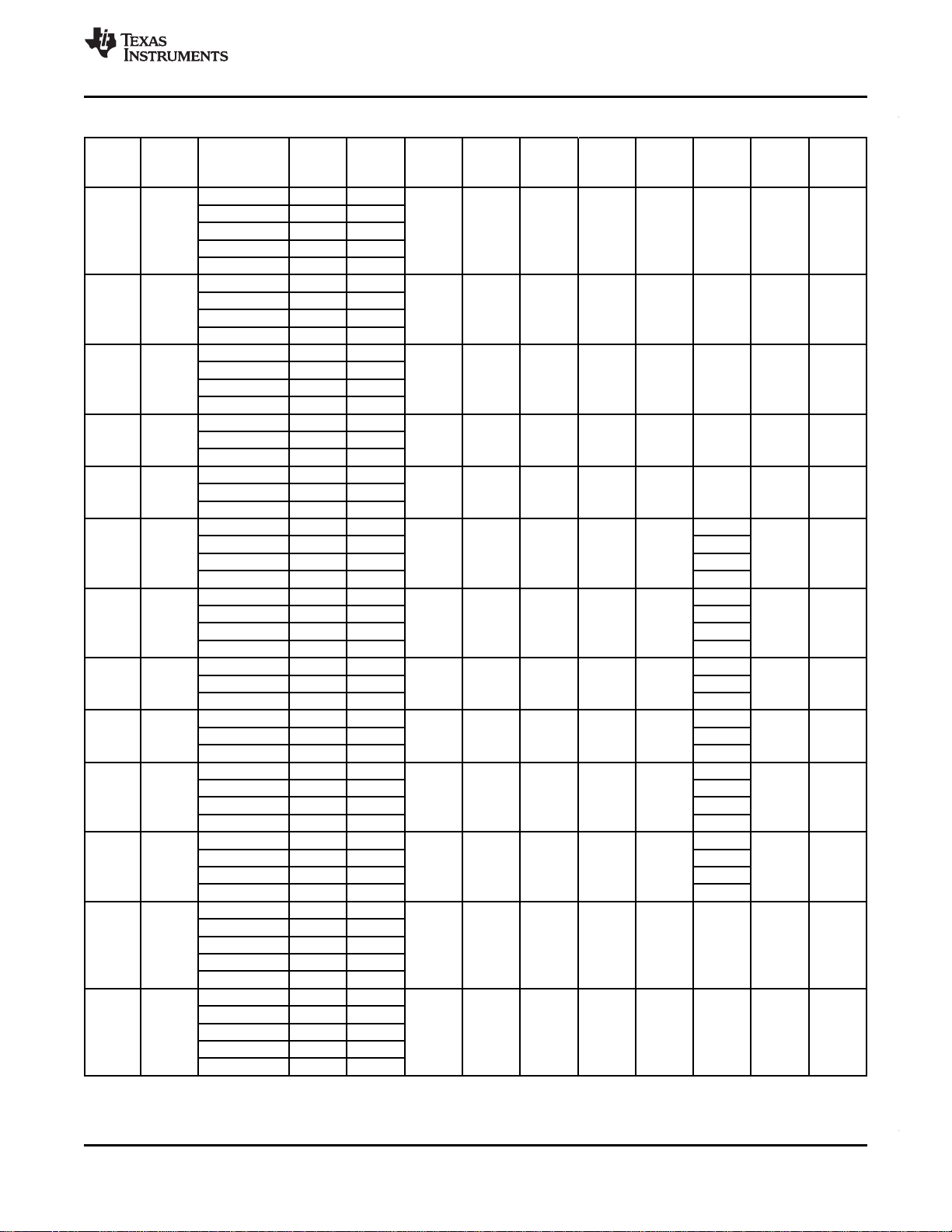

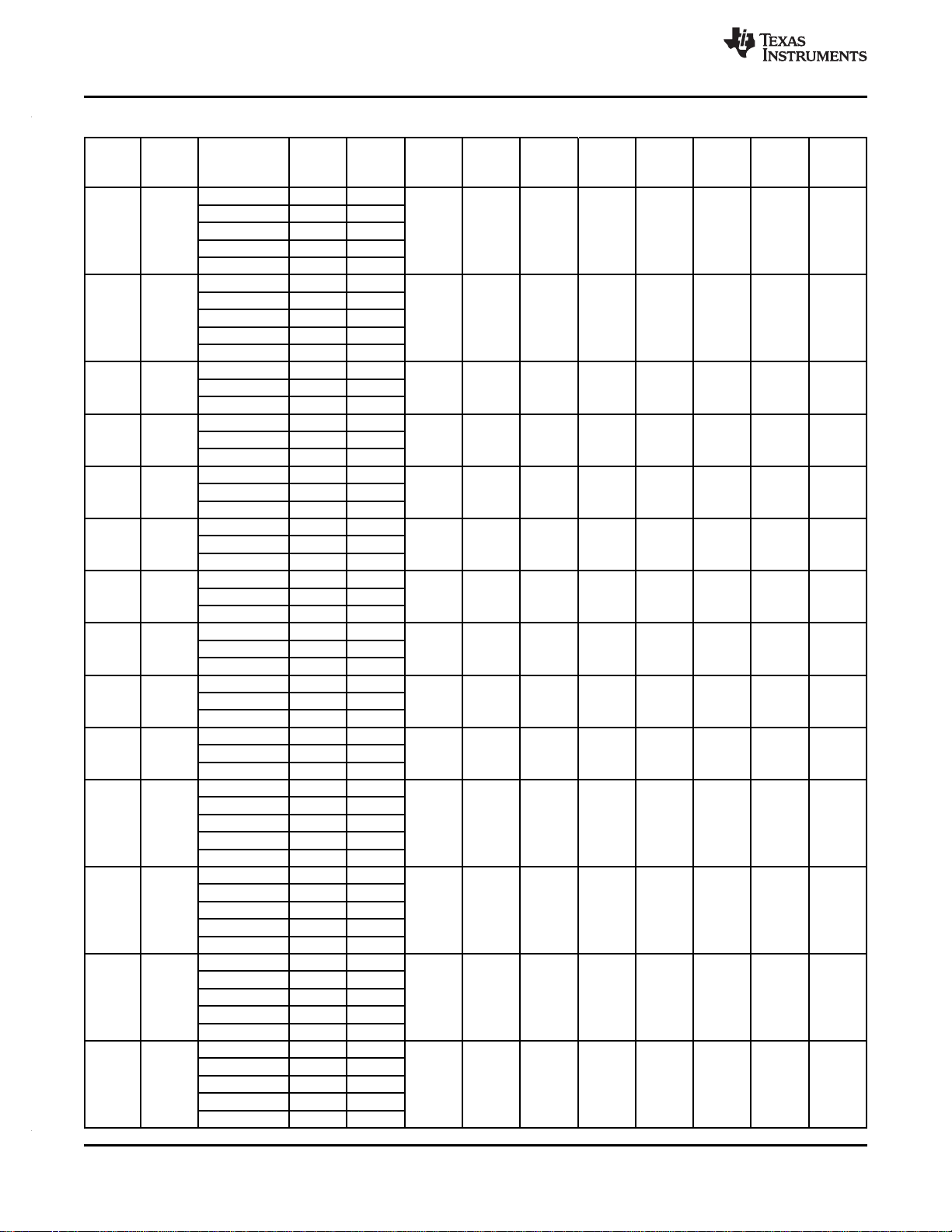

2.3 Ball Characteristics

Table 2-1 through Table 2-3 describe the terminal characteristics and the signals multiplexed on each pin

for the CBP, CBC, and CUS packages, respectively. The following list describes the table column

headers.

1. BALL BOTTOM: Ball number(s) on the bottom side associated with each signal(s) on the bottom.

2. BALL TOP: Ball number(s) on the top side associated with each signal(s) on the top.

3. PIN NAME: Names of signals multiplexed on each ball (also notice that the name of the pin is the

signal name in mode 0).

Note: Table 2-1 through Table 2-3 do not take into account subsystem pin multiplexing options.

Subsystem pin multiplexing options are described in Section 2.5, Signal Descriptions.

4. MODE: Multiplexing mode number.

(a) Mode 0 is the primary mode; this means that when mode 0 is set, the function mapped on the pin

corresponds to the name of the pin. There is always a function mapped on the primary mode.

Notice that primary mode is not necessarily the default mode.

Note: The default mode is the mode at the release of the reset; also see the RESET REL. MODE

column.

(b) Modes 1 to 7 are possible modes for alternate functions. On each pin, some modes are effectively

used for alternate functions, while some modes are not used and do not correspond to a functional

configuration.

5. TYPE: Signal direction

– I = Input

– O = Output

– I/O = Input/Output

– D = Open drain

– DS = Differential

– A = Analog

– PWR = Power

– GND = Ground

Note: In the safe_mode, the buffer is configured in high-impedance.

6. BALL RESET STATE: The state of the terminal at the power-on reset.

– 0: The buffer drives VOL(pulldown/pullup resistor not activated)

0(PD): The buffer drives VOLwith an active pulldown resistor.

– 1: The buffer drives VOH(pulldown/pullup resistor not activated)

1(PU): The buffer drives VOHwith an active pullup resistor.

– Z: High-impedance

– L: High-impedance with an active pulldown resistor

– H : High-impedance with an active pullup resistor

7. BALL RESET REL. STATE: The state of the terminal at the release of the System Control Module

reset (PRCM CORE_RSTPWRON_RET reset signal).

– 0: The buffer drives VOL(pulldown/pullup resistor not activated)

0(PD): The buffer drives VOLwith an active pulldown resistor.

– 1: The buffer drives VOH(pulldown/pullup resistor not activated)

1(PU): The buffer drives VOHwith an active pullup resistor.

– Z: High-impedance

– L: High-impedance with an active pulldown resistor

– H : High-impedance with an active pullup resistor

8. RESET REL. MODE: The mode is automatically configured at the release of the System Control

Module reset (PRCM CORE_RSTPWRON_RET reset signal).

9. POWER: The voltage supply that powers the terminal’s I/O buffers.

10. HYS: Indicates if the input buffer is with hysteresis.

www.ti.com

24 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 25

PRODUCTPREVIEW

DM3730, DM3725

www.ti.com

11. BUFFER STRENGTH: Drive strength of the associated output buffer.

12. PULL U/D - TYPE: Denotes the presence of an internal pullup or pulldown resistor. Pullup and

pulldown resistors can be enabled or disabled via software.

Note: The pullup/pulldown drive strength is equal to minimum = 50mA, typical = 100 mA, maximum =

250 mA (unless otherwise specified), except for CBP balls P27, P26, R27, and R25, and CUS balls

N22 and P24, which the pulldown drive strength is equal to 1.8 kΩ.

13. IO CELL: IO cell information.

Note: Configuring two pins to the same input signal is not supported as it can yield unexpected results.

This can be easily prevented with the proper software configuration.

In the DM3730/25 device, new Far End load Settings registers are added for some IOs. This

new feature configures the IO according to the transmission line and the

application/peripheral load. For a full description on these registers, see the System Control

Module / SCM Functional Description / Functional Register Description / Signal Integrity

Parameter Control Registers with Pad Group Assignment section of the AM/DM37x

Multimedia Device Technical Reference Manual (literature number SPRUGN4).

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

NA J2 sdrc_d0 0 IO L Z 0 vdds_mem Yes 4

NA J1 sdrc_d1 0 IO L Z 0 vdds_mem Yes 4

NA G2 sdrc_d2 0 IO L Z 0 vdds_mem Yes 4

NA G1 sdrc_d3 0 IO L Z 0 vdds_mem Yes 4

NA F2 sdrc_d4 0 IO L Z 0 vdds_mem Yes 4

NA F1 sdrc_d5 0 IO L Z 0 vdds_mem Yes 4

NA D2 sdrc_d6 0 IO L Z 0 vdds_mem Yes 4

NA D1 sdrc_d7 0 IO L Z 0 vdds_mem Yes 4

NA B13 sdrc_d8 0 IO L Z 0 vdds_mem Yes 4

NA A13 sdrc_d9 0 IO L Z 0 vdds_mem Yes 4

NA B14 sdrc_d10 0 IO L Z 0 vdds_mem Yes 4

NA A14 sdrc_d11 0 IO L Z 0 vdds_mem Yes 4

NA B16 sdrc_d12 0 IO L Z 0 vdds_mem Yes 4

NA A16 sdrc_d13 0 IO L Z 0 vdds_mem Yes 4

NA B19 sdrc_d14 0 IO L Z 0 vdds_mem Yes 4

NA A19 sdrc_d15 0 IO L Z 0 vdds_mem Yes 4

NA B3 sdrc_d16 0 IO L Z 0 vdds_mem Yes 4

NA A3 sdrc_d17 0 IO L Z 0 vdds_mem Yes 4

NA B5 sdrc_d18 0 IO L Z 0 vdds_mem Yes 4

NA A5 sdrc_d19 0 IO L Z 0 vdds_mem Yes 4

NA B8 sdrc_d20 0 IO L Z 0 vdds_mem Yes 4

NA A8 sdrc_d21 0 IO L Z 0 vdds_mem Yes 4

NA B9 sdrc_d22 0 IO L Z 0 vdds_mem Yes 4

NA A9 sdrc_d23 0 IO L Z 0 vdds_mem Yes 4

NA B21 sdrc_d24 0 IO L Z 0 vdds_mem Yes 4

NA A21 sdrc_d25 0 IO L Z 0 vdds_mem Yes 4

NA D22 sdrc_d26 0 IO L Z 0 vdds_mem Yes 4

NA D23 sdrc_d27 0 IO L Z 0 vdds_mem Yes 4

NA E22 sdrc_d28 0 IO L Z 0 vdds_mem Yes 4

NA E23 sdrc_d29 0 IO L Z 0 vdds_mem Yes 4

NA G22 sdrc_d30 0 IO L Z 0 vdds_mem Yes 4

NA G23 sdrc_d31 0 IO L Z 0 vdds_mem Yes 4

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

NOTE

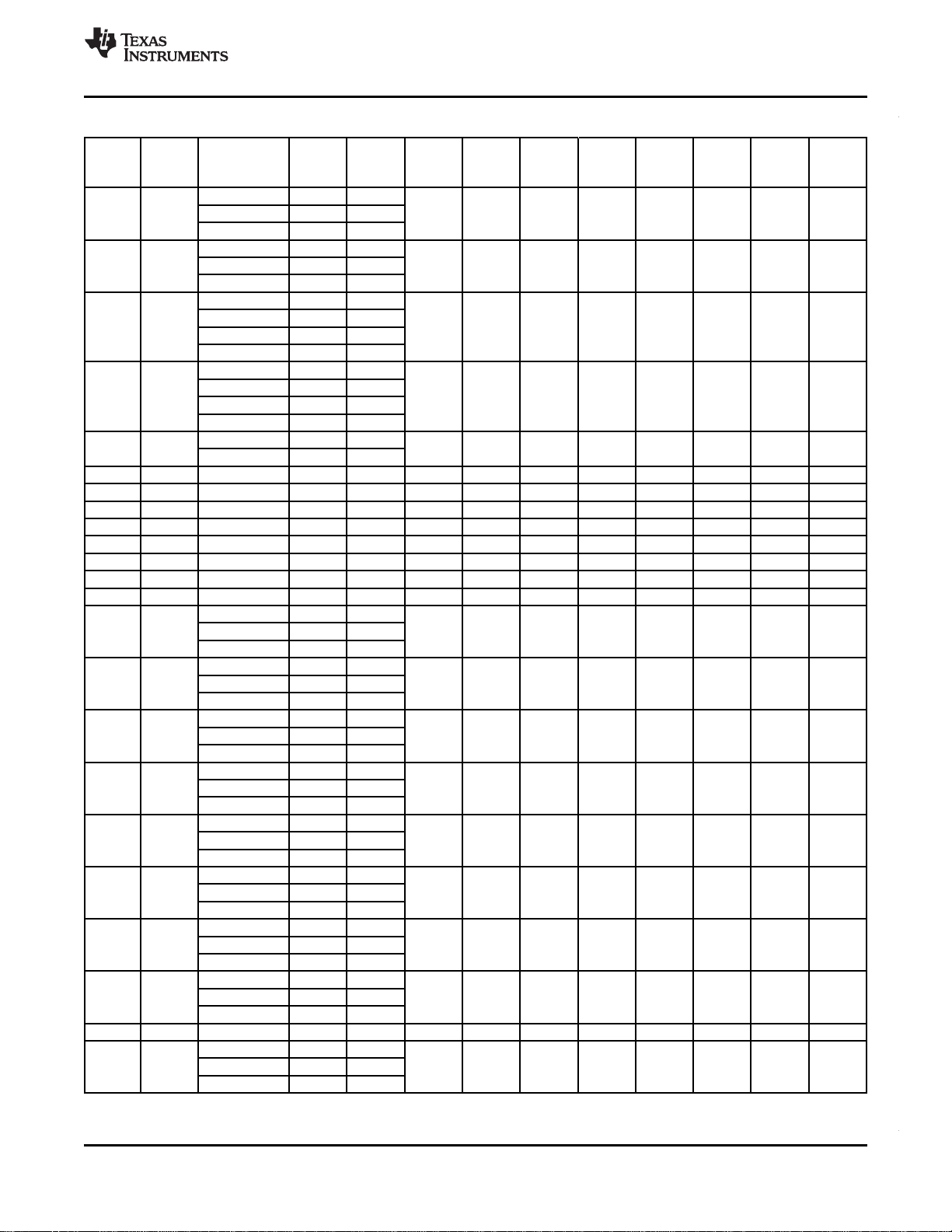

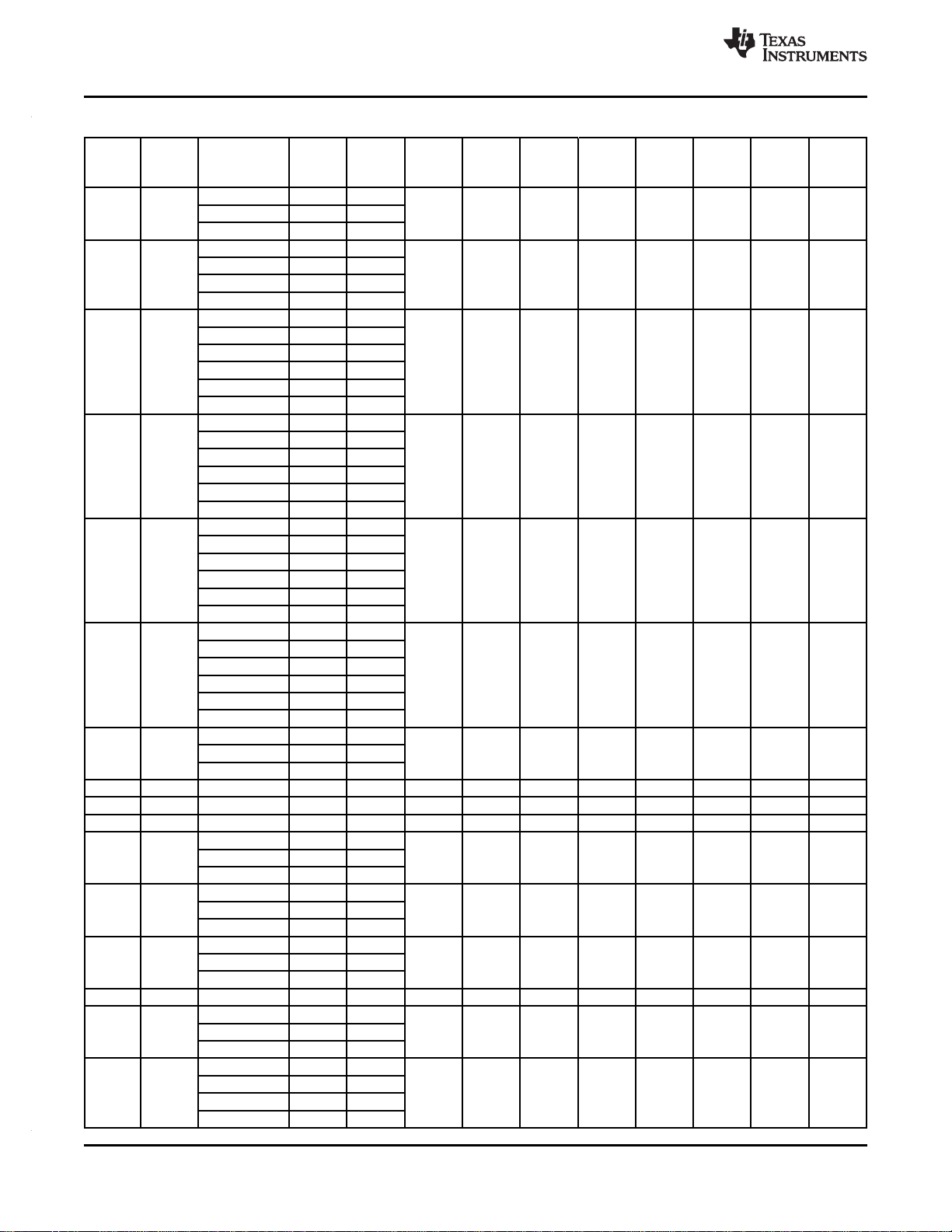

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BUFFER

STATE [7] [11]

(3)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

(10)

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 25

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 26

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

NA AB21 sdrc_ba0 0 O 0 0 0 vdds_mem No 4

NA AC21 sdrc_ba1 0 O 0 0 0 vdds_mem No 4

NA N22 sdrc_a0 0 O 0 0 0 vdds_mem No 4

NA N23 sdrc_a1 0 O 0 0 0 vdds_mem No 4

NA P22 sdrc_a2 0 O 0 0 0 vdds_mem No 4

NA P23 sdrc_a3 0 O 0 0 0 vdds_mem No 4

NA R22 sdrc_a4 0 O 0 0 0 vdds_mem No 4

NA R23 sdrc_a5 0 O 0 0 0 vdds_mem No 4

NA T22 sdrc_a6 0 O 0 0 0 vdds_mem No 4

NA T23 sdrc_a7 0 O 0 0 0 vdds_mem No 4

NA U22 sdrc_a8 0 O 0 0 0 vdds_mem No 4

NA U23 sdrc_a9 0 O 0 0 0 vdds_mem No 4

NA V22 sdrc_a10 0 O 0 0 0 vdds_mem No 4

NA V23 sdrc_a11 0 O 0 0 0 vdds_mem No 4

NA W22 sdrc_a12 0 O 0 0 0 vdds_mem No 4

NA W23 sdrc_a13 0 O 0 0 0 vdds_mem No 4

NA Y22 sdrc_a14 0 O 0 0 0 vdds_mem No 4

NA M22 sdrc_ncs0 0 O 1 1 0 vdds_mem No 4

NA M23 sdrc_ncs1 0 O 1 1 0 vdds_mem No 4

NA A11 sdrc_clk 0 IO L 0 0 vdds_mem Yes 4

NA B11 sdrc_nclk 0 O 1 1 0 vdds_mem No 4

NA J22 sdrc_cke0 0 O H 1 7 vdds_mem Yes 4

NA J23 sdrc_cke1 0 O H 1 7 vdds_mem NA 4

NA L23 sdrc_nras 0 O 1 1 0 vdds_mem No 4

NA L22 sdrc_ncas 0 O 1 1 0 vdds_mem No 4

NA K23 sdrc_nwe 0 O 1 1 0 vdds_mem No 4

NA C1 sdrc_dm0 0 O 0 0 0 vdds_mem No 4

NA A17 sdrc_dm1 0 O 0 0 0 vdds_mem No 4

NA A6 sdrc_dm2 0 O 0 0 0 vdds_mem No 4

NA A20 sdrc_dm3 0 O 0 0 0 vdds_mem No 4

NA C2 sdrc_dqs0 0 IO L Z 0 vdds_mem Yes 4

NA B17 sdrc_dqs1 0 IO L Z 0 vdds_mem Yes 4

NA B6 sdrc_dqs2 0 IO L Z 0 vdds_mem Yes 4

NA B20 sdrc_dqs3 0 IO L Z 0 vdds_mem Yes 4

N4 AC15 gpmc_a1 0 O L L 7 vdds_mem Yes 8 PU/ PD LVCMOS

M4 AB15 gpmc_a2 0 O L L 7 vdds_mem Yes 8 PU/ PD LVCMOS

L4 AC16 gpmc_a3 0 O L L 7 vdds_mem Yes 8 PU/ PD LVCMOS

K4 AB16 gpmc_a4 0 O L L 7 vdds_mem Yes 8 PU/ PD LVCMOS

T3 AC17 gpmc_a5 0 O L L 7 vdds_mem Yes 8 PU/ PD LVCMOS

R3 AB17 gpmc_a6 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

safe_mode_out1

safe_mode_out1

gpio_34 4 IO

safe_mode 7

gpio_35 4 IO

safe_mode 7

gpio_36 4 IO

safe_mode 7

gpio_37 4 IO

safe_mode 7

gpio_38 4 IO

safe_mode 7

gpio_39 4 IO

safe_mode 7

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BUFFER

STATE [7] [11]

(13)

7

(13)

7

(3)

(continued)

www.ti.com

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

(12)

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

PU/ PD LVCMOS

NA LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

NA LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

PU/ PD LVCMOS

26 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 27

PRODUCTPREVIEW

DM3730, DM3725

www.ti.com

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

N3 AC18 gpmc_a7 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

M3 AB18 gpmc_a8 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

L3 AC19 gpmc_a9 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

K3 AB19 gpmc_a10 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

NA AC20 gpmc_a11 0 O L L 7 vdds_mem Yes 8 PU/ PD LVCMOS

K1 M2 gpmc_d0 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

L1 M1 gpmc_d1 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

L2 N2 gpmc_d2 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

P2 N1 gpmc_d3 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

T1 R2 gpmc_d4 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

V1 R1 gpmc_d5 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

V2 T2 gpmc_d6 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

W2 T1 gpmc_d7 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

H2 AB3 gpmc_d8 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

K2 AC3 gpmc_d9 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

P1 AB4 gpmc_d10 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

R1 AC4 gpmc_d11 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

R2 AB6 gpmc_d12 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

T2 AC6 gpmc_d13 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

W1 AB7 gpmc_d14 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

Y1 AC7 gpmc_d15 0 IO H H 0 vdds_mem Yes 8 PU/ PD LVCMOS

G4 Y2 gpmc_ncs0 0 O 1 1 0 vdds_mem NA 8 NA LVCMOS

H3 Y1 gpmc_ncs1 0 O H 1 0 vdds_mem Yes 8 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

gpio_40 4 IO

safe_mode 7

gpio_41 4 IO

safe_mode 7

sys_ndmareq2 1 I

gpio_42 4 IO

safe_mode 7

sys_ndmareq3 1 I

gpio_43 4 IO

safe_mode 7

safe_mode 7

gpio_44 4 IO

safe_mode 7

gpio_45 4 IO

safe_mode 7

gpio_46 4 IO

safe_mode 7

gpio_47 4 IO

safe_mode 7

gpio_48 4 IO

safe_mode 7

gpio_49 4 IO

safe_mode 7

gpio_50 4 IO

safe_mode 7

gpio_51 4 IO

safe_mode 7

gpio_52 4 IO

safe_mode 7

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

(3)

(continued)

BALL BUFFER

STATE [7] [11]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 27

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 28

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

V8 NA gpmc_ncs2 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

U8 NA gpmc_ncs3 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

T8 NA gpmc_ncs4 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

R8 NA gpmc_ncs5 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

P8 NA gpmc_ncs6 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

N8 NA gpmc_ncs7 0 O H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

T4 W2 gpmc_clk 0 O L 0 0 vdds_mem Yes 8 PU/ PD LVCMOS

F3 W1 gpmc_nadv_ale 0 O 0 0 0 vdds_mem NA 8 PU/ PD LVCMOS

G2 V2 gpmc_noe 0 O 1 1 0 vdds_mem NA 8 PU/ PD LVCMOS

F4 V1 gpmc_nwe 0 O 1 1 0 vdds_mem NA 8 PU/ PD LVCMOS

G3 AC12 gpmc_nbe0_cle 0 O L 0 0 vdds_mem Yes 8 PU/ PD LVCMOS

U3 NA gpmc_nbe1 0 O L L 7 vdds_mem Yes 8 PU/ PD LVCMOS

H1 AB10 gpmc_nwp 0 O L 0 0 vdds_mem Yes 8 PU/ PD LVCMOS

M8 AB12 gpmc_wait0 0 I H H 0 vdds_mem Yes NA PU/PD LVCMOS

L8 AC10 gpmc_wait1 0 I H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

K8 NA gpmc_wait2 0 I H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

gpio_53 4 IO

safe_mode 7

sys_ndmareq0 1 I

gpio_54 4 IO

safe_mode 7

sys_ndmareq1 1 I

mcbsp4_clkx 2 IO

gpt_9_pwm_evt 3 IO

gpio_55 4 IO

safe_mode 7

sys_ndmareq2 1 I

mcbsp4_dr 2 I

gpt_10_pwm_evt 3 IO

gpio_56 4 IO

safe_mode 7

sys_ndmareq3 1 I

mcbsp4_dx 2 IO

gpt_11_pwm_evt 3 IO

gpio_57 4 IO

safe_mode 7

gpmc_io_dir 1 O

mcbsp4_fsx 2 IO

gpt_8_pwm_evt 3 IO

gpio_58 4 IO

safe_mode 7

gpio_59 4 IO

safe_mode 7

gpio_60 4 IO

safe_mode 7

gpio_61 4 IO

safe_mode 7

gpio_62 4 IO

safe_mode 7

gpio_63 4 IO

safe_mode 7

uart4_tx 2 O

gpio_64 4 IO

safe_mode 7

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BUFFER

STATE [7] [11]

(3)

(continued)

www.ti.com

28 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 29

PRODUCTPREVIEW

DM3730, DM3725

www.ti.com

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

J8 NA gpmc_wait3 0 I H H 7 vdds_mem Yes 8 PU/ PD LVCMOS

D28 NA dss_pclk 0 O H H 7 vdds Yes 8 PU/ PD LVCMOS

D26 NA dss_hsync 0 O H H 7 vdds Yes 8 PU/ PD LVCMOS

D27 NA dss_vsync 0 O H H 7 vdds Yes 8 PU/ PD LVCMOS

E27 NA dss_acbias 0 O L L 7 vdds Yes 8 PU/ PD LVCMOS

AG22 NA dss_data0 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AH22 NA dss_data1 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AG23 NA dss_data2 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AH23 NA dss_data3 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AG24 NA dss_data4 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AH24 NA dss_data5 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

E26 NA dss_data6 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

F28 NA dss_data7 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

sys_ndmareq1 1 I

uart4_rx 2 I

gpio_65 4 IO

safe_mode 7

gpio_66 4 IO

hw_dbg12 5 O

safe_mode 7

gpio_67 4 IO

hw_dbg13 5 O

safe_mode 7

gpio_68 4 IO

safe_mode 7

gpio_69 4 IO

safe_mode 7

uart1_cts 2 I NA

gpio_70 4 IO 8

safe_mode 7 8

uart1_rts 2 O 8

gpio_71 4 IO 8

safe_mode 7 8

gpio_72 4 IO 8

safe_mode 7 8

gpio_73 4 IO 8

safe_mode 7 8

uart3_rx_irrx 2 I NA

gpio_74 4 IO 8

safe_mode 7 8

uart3_tx_irtx 2 O 8

gpio_75 4 IO 8

safe_mode 7 8

uart1_tx 2 O

gpio_76 4 IO

hw_dbg14 5 O

safe_mode 7

uart1_rx 2 I

gpio_77 4 IO

hw_dbg15 5 O

safe_mode 7

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

(3)

(continued)

BALL BUFFER

STATE [7] [11]

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 29

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 30

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

F27 NA dss_data8 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

G26 NA dss_data9 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AD28 NA dss_data10 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AD27 NA dss_data11 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AB28 NA dss_data12 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AB27 NA dss_data13 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AA28 NA dss_data14 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

AA27 NA dss_data15 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

G25 NA dss_data16 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

H27 NA dss_data17 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

H26 NA dss_data18 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

H25 NA dss_data19 0 IO L L 7 vdds Yes 8 PU/ PD LVCMOS

E28 NA dss_data20 0 O H H 7 vdds Yes 8 PU/ PD LVCMOS

J26 NA dss_data21 0 O L L 7 vdds Yes 8 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

uart3_rx_irrx 2 I

gpio_78 4 IO

hw_dbg16 5 O

safe_mode 7

uart3_tx_irtx 2 O

gpio_79 4 IO

hw_dbg17 5 O

safe_mode 7

gpio_80 4 IO

safe_mode 7

gpio_81 4 IO

safe_mode 7

gpio_82 4 IO

safe_mode 7

gpio_83 4 IO

safe_mode 7

gpio_84 4 IO

safe_mode 7

gpio_85 4 IO

safe_mode 7

gpio_86 4 IO

safe_mode 7

gpio_87 4 IO

safe_mode 7

mcspi3_clk 2 IO

dss_data0 3 IO

gpio_88 4 IO

safe_mode 7

mcspi3_simo 2 IO

dss_data1 3 IO

gpio_89 4 IO

safe_mode 7

mcspi3_somi 2 IO

dss_data2 3 IO

gpio_90 4 IO

safe_mode 7

mcspi3_cs0 2 IO

dss_data3 3 IO

gpio_91 4 IO

safe_mode 7

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BUFFER

STATE [7] [11]

(3)

(continued)

www.ti.com

30 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 31

PRODUCTPREVIEW

DM3730, DM3725

www.ti.com

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

AC27 NA dss_data22 0 O L L 7 vdds Yes 8 PU/ PD LVCMOS

AC28 NA dss_data23 0 O L L 7 vdds Yes 8 PU/ PD LVCMOS

W28 NA cvideo2_out 0 AO 0 0 0 vdda_dac NA NA

Y28 NA cvideo1_out 0 AO 0 0 0 vdda_dac NA NA

Y27 NA cvideo1_vfb 0 AO 0 NA 0 vdda_dac NA NA

W27 NA cvideo2_vfb 0 AO 0 NA 0 vdda_dac NA NA

W26 NA cvideo1_rset 0 AIO 0 NA 0 vdda_dac No NA NA 10-bit DAC

A24 NA cam_hs 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

A23 NA cam_vs 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

C25 NA cam_xclka 0 O L L 7 vdds Yes 4 PU/ PD LVCMOS

C27 NA cam_pclk 0 I L L 7 vdds Yes 4 PU/ PD LVCMOS

C23 NA cam_fld 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

AG17 NA cam_d0 0 I L L 7 vdds Yes NA PU/PD LVCMOS

AH17 NA cam_d1 0 I L L 7 vdds Yes NA PU/PD LVCMOS

B24 NA cam_d2 0 I L L 7 vdds Yes 8 PU/ PD LVCMOS

C24 NA cam_d3 0 I L L 7 vdds Yes 8 PU/ PD LVCMOS

D24 NA cam_d4 0 I L L 7 vdds Yes 8 PU/ PD LVCMOS

A25 NA cam_d5 0 I L L 7 vdds Yes 8 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

mcspi3_cs1 2 O

dss_data4 3 IO

gpio_92 4 IO

safe_mode 7

dss_data5 3 IO

gpio_93 4 IO

safe_mode 7

gpio_94 4 IO

hw_dbg0 5 O

safe_mode 7

gpio_95 4 IO

hw_dbg1 5 O

safe_mode 7

gpio_96 4 IO

safe_mode 7

gpio_97 4 IO

hw_dbg2 5 O

safe_mode 7

cam_global_reset 2 IO

gpio_98 4 IO

hw_dbg3 5 O

safe_mode 7

gpio_99 4 I

safe_mode 7

gpio_100 4 I

safe_mode 7

gpio_101 4 IO

hw_dbg4 5 O

safe_mode 7

gpio_102 4 IO

hw_dbg5 5 O

safe_mode 7

gpio_103 4 IO

hw_dbg6 5 O

safe_mode 7

gpio_104 4 IO

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

(3)

(continued)

BALL BUFFER

STATE [7] [11]

(4)

(4)

(10)

(10)

NA 10-bit DAC

NA 10-bit DAC

NA 10-bit DAC

NA 10-bit DAC

Copyright © 2010, Texas Instruments Incorporated TERMINAL DESCRIPTION 31

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 32

PRODUCTPREVIEW

DM3730, DM3725

SPRS685A–AUGUST 2010–REVISED SEPTEMBER 2010

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

K28 NA cam_d6 0 I L L 7 vdds Yes NA PU/ PD LVCMOS

L28 NA cam_d7 0 I L L 7 vdds Yes NA PU/ PD LVCMOS

K27 NA cam_d8 0 I L L 7 vdds Yes NA PU/ PD LVCMOS

L27 NA cam_d9 0 I L L 7 vdds Yes NA PU/ PD LVCMOS

B25 NA cam_d10 0 I L L 7 vdds Yes 8 PU/ PD LVCMOS

C26 NA cam_d11 0 I L L 7 vdds Yes 8 PU/ PD LVCMOS

B26 NA cam_xclkb 0 O L L 7 vdds Yes 4 PU/ PD LVCMOS

B23 NA cam_wen 0 I L L 7 vdds Yes 4 PU/ PD LVCMOS

D25 NA cam_strobe 0 O L L 7 vdds Yes 4 PU/ PD LVCMOS

AG19 NA gpio_112 4 I L L 7 vdds Yes NA PU/PD LVCMOS

AH19 NA gpio_113 4 I L L 7 vdds Yes NA PU/PD LVCMOS

AG18 NA gpio_114 4 I L L 7 vdds Yes NA PU/PD LVCMOS

AH18 NA gpio_115 4 I L L 7 vdds Yes NA PU/PD LVCMOS

P21 NA mcbsp2_fsx 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

N21 NA mcbsp2_clkx 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

R21 NA mcbsp2_dr 0 I L L 7 vdds Yes 4 PU/ PD LVCMOS

M21 NA mcbsp2_dx 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

hw_dbg7 5 O

safe_mode 7

gpio_105 4 I

safe_mode 7

gpio_106 4 I

safe_mode 7

gpio_107 4 I

safe_mode 7

gpio_108 4 I

safe_mode 7

gpio_109 4 IO

hw_dbg8 5 O

safe_mode 7

gpio_110 4 IO

hw_dbg9 5 O

safe_mode 7

gpio_111 4 IO

safe_mode 7

cam_shutter 2 O

gpio_167 4 IO

hw_dbg10 5 O

safe_mode 7

gpio_126 4 IO

hw_dbg11 5 O

safe_mode 7

safe_mode 7

safe_mode 7

safe_mode 7 -

safe_mode 7 -

gpio_116 4 IO

safe_mode 7

gpio_117 4 IO

safe_mode 7

gpio_118 4 IO

safe_mode 7

gpio_119 4 IO

safe_mode 7

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BUFFER

STATE [7] [11]

(3)

(continued)

www.ti.com

32 TERMINAL DESCRIPTION Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): DM3730 DM3725

Page 33

PRODUCTPREVIEW

DM3730, DM3725

www.ti.com

Table 2-1. Ball Characteristics (CBP Pkg.)

BALL BALL RESET PULLUP

BOTTOM PIN NAME [3] MODE [4] TYPE [5] RESET REL. MODE POWER [9] HYS [10] /DOWN

[1] STATE [6] [8] TYPE [12]

N28 NA mmc1_clk 0 IO L L 7 vdds_mmc1(Yes 1 PU/ PD

M27 NA mmc1_cmd 0 O L L 7 vdds_mmc1(Yes 1 PU/ PD

N27 NA mmc1_dat0 0 IO L L 7 vdds_mmc1(Yes 1 PU/ PD

N26 NA mmc1_dat1 0 IO L L 7 vdds_mmc1(Yes 1 PU/ PD

N25 NA mmc1_dat2 0 IO L L 7 vdds_mmc1(Yes 1 PU/ PD

P28 NA mmc1_dat3 0 IO L L 7 vdds_mmc1(Yes 1 PU/ PD

P27 NA gpio_126

P26 NA gpio_127

R27 NA gpio_128

R25 NA gpio_129

AE2 NA mmc2_clk 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

AG5 NA mmc2_cmd 0 O H H 7 vdds Yes 4 PU/ PD LVCMOS

AH5 NA mmc2_dat0 0 IO H H 7 vdds Yes 4 PU/ PD LVCMOS

AH4 NA mmc2_dat1 0 IO H H 7 vdds Yes 4 PU/ PD LVCMOS

AG4 NA mmc2_dat2 0 IO H H 7 vdds Yes 4 PU/ PD LVCMOS

AF4 NA mmc2_dat3 0 IO H H 7 vdds Yes 4 PU/ PD LVCMOS

AE4 NA mmc2_dat4 0 IO L L 7 vdds Yes 4 PU/ PD LVCMOS

BALL TOP RESET STRENG IO CELL

[2] REL. TH (mA) [13]

(1)

gpio_120

safe_mode 7

(1)

gpio_121

safe_mode 7

(1)

gpio_122

safe_mode 7

(1)

gpio_123

safe_mode 7

(1)

gpio_124

safe_mode 7

(1)

gpio_125

safe_mode 7

(1)

safe_mode 7

(1)

safe_mode 7

(1)

safe_mode 7

(1)

safe_mode 7

mcspi3_clk 1 IO

gpio_130 4 IO

safe_mode 7