Texas Instruments BQ4830YMA-85 Datasheet

bq4830Y

RTC Module With 32Kx8 NVSRAM

Features

➤ Integrated SRAM, real-time

clock, crystal,power-fail control

circuit, and battery

➤ Real-Time Clock counts seconds

through years in BCD format

➤ RAM-like clock access

➤ Pin-compatible with industry-

standard 32K x 8 SRAMs

➤ Unlimited write cycles

➤ 10-year minimum data retention

and clock operation in the absence of power

➤ Automatic power-fail chip dese-

lect and write-protection

➤ Software clock calibration for

greater than 1 minute per month

accuracy

➤ 10% tolerance of V

for write-

CC

protect

Pin Connections

General Description

The bq4830Y RTC Module is a nonvolatile 262,144-bit SRAM organized as 32,768 words by 8 bits with

an integral accessible real-time

clock.

The device combines an internal

lithium battery,quartz crystal, clock

and power-fail chip, and a full

CMOS SRAM in a plastic 28-pin

DIP module. The RTC Module directly replaces industry-standard

SRAMs and also fits into many

EPROM and EEPROM sockets

without any requirement for special

write timing or limitations on the

number of write cycles.

Registers for the real-time clock and

clock calibration are located in registers 7FF8h–7FFFh of the memory array.

Pin Names

The clock registers are dual-port

read/write SRAM locations that are

updated once per second by a clock

control circuit from the internal

clock counters. The dual-port registers allow clock updates to occur

without interrupting normal access

to the rest of the SRAM array.

The bq4830Y also contains a power

fail-detect circuit. The circuit deselects the device whenever V

CC

falls

below tolerance, providing a high degree of data security. The battery is

electrically isolated when shipped

from the factory to provide maximum battery capacity. The battery

remains disconnected until the first

application of VCC.

Sept. 1996 B

A

1

14

A

2

12

A

3

7

4

A

6

5

A

5

A

6

4

A

7

3

8

A

2

A

9

1

A

10

0

11

DQ

0

12

DQ

1

13

DQ

2

V

14

SS

28-Pin DIP Module

28

V

CC

27

WE

26

A

13

25

24

23

22

21

20

19

18

17

16

15

PN483001.eps

A

A

A

OE

A

CE

DQ

DQ

DQ

DQ

DQ

8

9

11

10

7

6

5

4

3

A0–A

14

Address input

CE Chip enable

WE Write enable

OE Output enable

DQ0–DQ7Data in/data out

V

CC

V

SS

+5 volts

Ground

1

bq4830Y

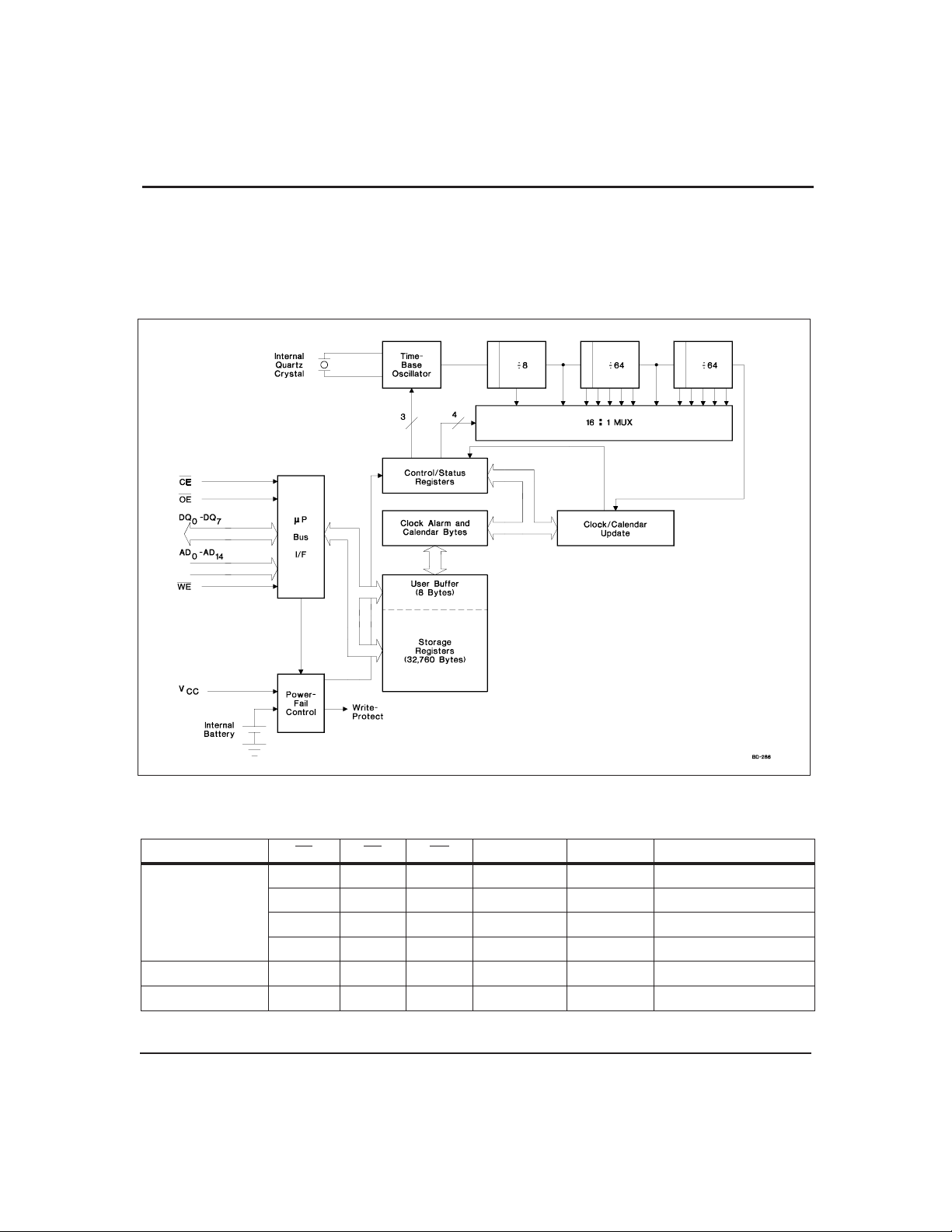

Functional Description

Figure 1 is a block diagram of the bq4830Y. The following sections describe the bq4830Y functional operation,

including memory and clock interface, and dataretention modes.

Truth Table

V

CC

(max.) V

<V

CC

(min.) V

>V

CC

(min.) > V

<V

PFD

≤ V

SO

Figure 1. Block Diagram

CE OE WE Mode DQ Power

X X Deselect High Z Standby

XVILWrite D

V

IL

V

IH

V

IH

V

IH

Read D

Read High Z Active

IN

OUT

SO

IH

V

IL

IL

V

IL

X X X Deselect High Z CMOS standby

X X X Deselect High Z Battery-backup mode

2

Active

Active

Sept. 1996 B

bq4830Y

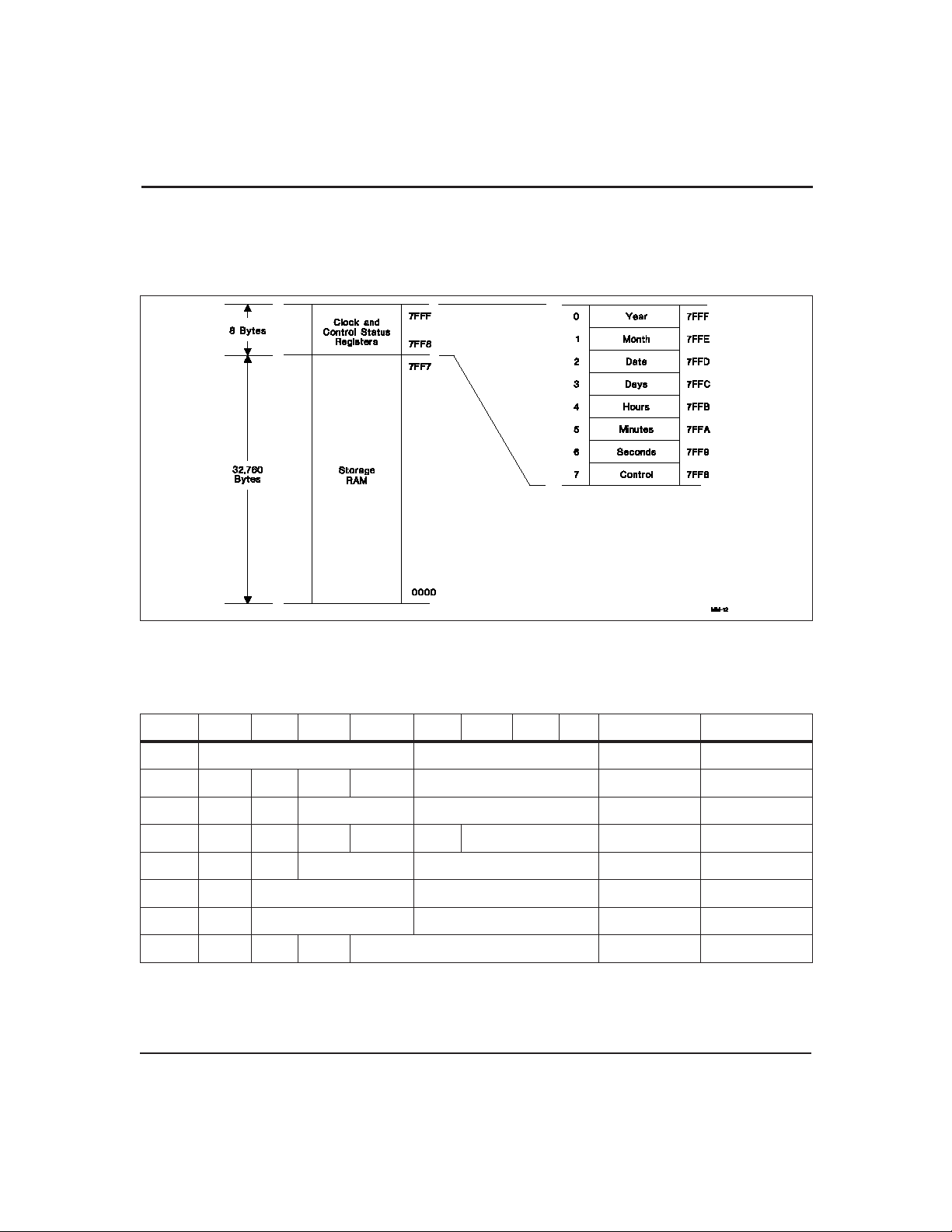

Address Map

The bq4830Y provides 8 bytes of clock and control status

registers and 32,760 bytes of storage RAM.

Figure 2. Address Map

Figure 2 illustrates the address map for the bq4830Y.

Table1is a map of the bq4830Y registers.

Table 1.bq4830Y Clock and Control Register Map

Address D7 D6 D5 D4 D3 D2 D1 D0 Range (h) Register

7FFF 10 Years Year 00–99 Year

7FFE X X X 10 Month Month 01–12 Month

7FFD X X 10 Date Date 01–31 Date

7FFC X FTE X X X Day 01–07 Days

7FFB X X 10 Hours Hours 00–23 Hours

7FFA X 10 Minutes Minutes 00–59 Minutes

7FF9 OSC 10 Seconds Seconds 00–59 Seconds

7FF8 W R S Calibration 00–31 Control

Notes: X = Unused bits; can be written and read.

Sept. 1996 B

Clock/Calendar data in 24-hour BCD format.

OSC = 1 stops the clock oscillator.

3

bq4830Y

Memory Interface

Read Mode

The bq4830Y is in read mode whenever OE (output enable) is low and CE (chip enable) is low. The device architecture allows ripple-through access of data from

eight of 262,144 locations in the static storage array.

Thus, the unique address specified by the 15 address inputs defines which one of the 32,768 bytes of data is to

be accessed. Valid data is available at the data I/O pins

within tAA(address access time) after the last address

input signal is stable, providing that the CE and OE

(output enable) access times are also satisfied. If the CE

and OE access times are not met, valid data is available

after the latter of chip enable access time (t

put enable access time (tOE).

and OE control the state of the eight three-state

CE

data I/O signals. If the outputs are activated before tAA,

the data lines are driven to an indeterminate state until

tAA. If the address inputs are changed while CE and OE

remain low, output data remains valid for tOH(output

data hold time), but goes indeterminate until the next

address access.

Write Mode

The bq4830Y is in write mode whenever WE and CE are

active. The start of a write is referenced from the

latter-occurring falling edge of WE or CE. A write is terminated by the earlier rising edge of WE or CE. The addresses must be held valid throughout the cycle. CE or

WE must return high for a minimum of t

t

from WE prior to the initiation of another read or

WR1

write cycle.

Data-in must be valid t

remain valid for t

kept high during write cycles to avoid bus contention;although, if the output bus has been activated by a low on

CE and OE, a low on WE disables the outputs tWZafter

WE falls.

DH1

prior to the end of write and

DW

or t

afterward. OE should be

DH2

Data-Retention Mode

With valid VCCapplied, the bq4830Y operates as a

conventional static RAM. Should the supply voltage

decay, the RAM automatically power-fail deselects,

write-protecting itself t

All outputs become high impedance, and all inputs are

treated as “don't care.”

If power-fail detection occurs during a valid access, the

memory cycle continues to completion. If the memory

cycle fails to terminate within time t

protection takes place. When VCCdrops below VSO, the

control circuit switches power to the internal energy

source,whichpreserves data.

after VCCfalls below V

WPT

ACE

WR2

WPT

) or out-

from CE or

PFD

, write-

The internal coin cell maintains data in the bq4830Y after the initial application of V

riod of at least 10 years when VCCis less than VSO.As

system power returns and Vcc rises above VSO, the battery is disconnected, and the power supply is switched to

external VCC. Write-protection continues for t

VCCreaches V

After t

,normal RAM operation can resume.

CER

to allow for processor stabilization.

PFD

for an accumulated pe-

CC

CER

Clock Interface

Reading the Clock

The interface to the clock and control registers of the

bq4830Y is the same as that for the general-purpose

storage memory. Once every second, the user-accessible

clock/calendar locations are updated simultaneously

from the internal real time counters. To prevent reading data in transition, updates to the bq4830Y clock registers should be halted. Updating is halted by setting

the read bit D6 of the control register to 1. As long as

the read bit is 1, updates to user-accessible clock locations are inhibited. Once the frozen clock information is

retrieved by reading the appropriate clock memory locations, the read bit should be reset to 0 in order to allow

updates to occur from the internal counters. Because the

internal counters are not halted by setting the read bit,

reading the clock locations has no effect on clock accuracy. Once the read bit is reset to 0, within one second

the internal registers update the user-accessible registers with the correct time. A halt command issued during a clock update allows the update to occur before

freezing the data.

Setting the Clock

Bit D7 of the control register is the write bit. Like the

read bit, the write bit when set to a 1 halts updates to

the clock/calendar memory locations. Once frozen, the

locations can be written with the desired information in

24-hour BCD format. Resetting the write bit to 0 causes

the written values to be transferred to the internal clock

counters and allows updates to the user-accessible registers to resume within one second. Use the write bit,D7,

only when updating the time registers (7FFF–7FF9).

Stopping and Starting the Clock Oscillator

.

The OSC bit in the seconds register turns the clock on or

off. If the bq4830Y is to spend a significant period of

time in storage, the clock oscillator can be turned off to

preserve battery capacity. OSC set to 1 stops the clock

oscillator. When OSC is reset to 0, the clock oscillator is

turned on and clock updates to user-accessible memory

locations occur within one second.

The OSC bit is set to 1 when shipped from the Benchmarq factory.

Sept. 1996 B

after

4

Calibrating the Clock

The bq4830Y real-time clock is driven by a quartz controlled oscillator with a nominal frequency of 32,768 Hz.

The quartz crystal is contained within the bq4830Y

package along with the battery. The clock accuracy of

the bq4830Y module is tested to be within 20ppm or

about 1 minute per month at 25°C. The oscillation rates

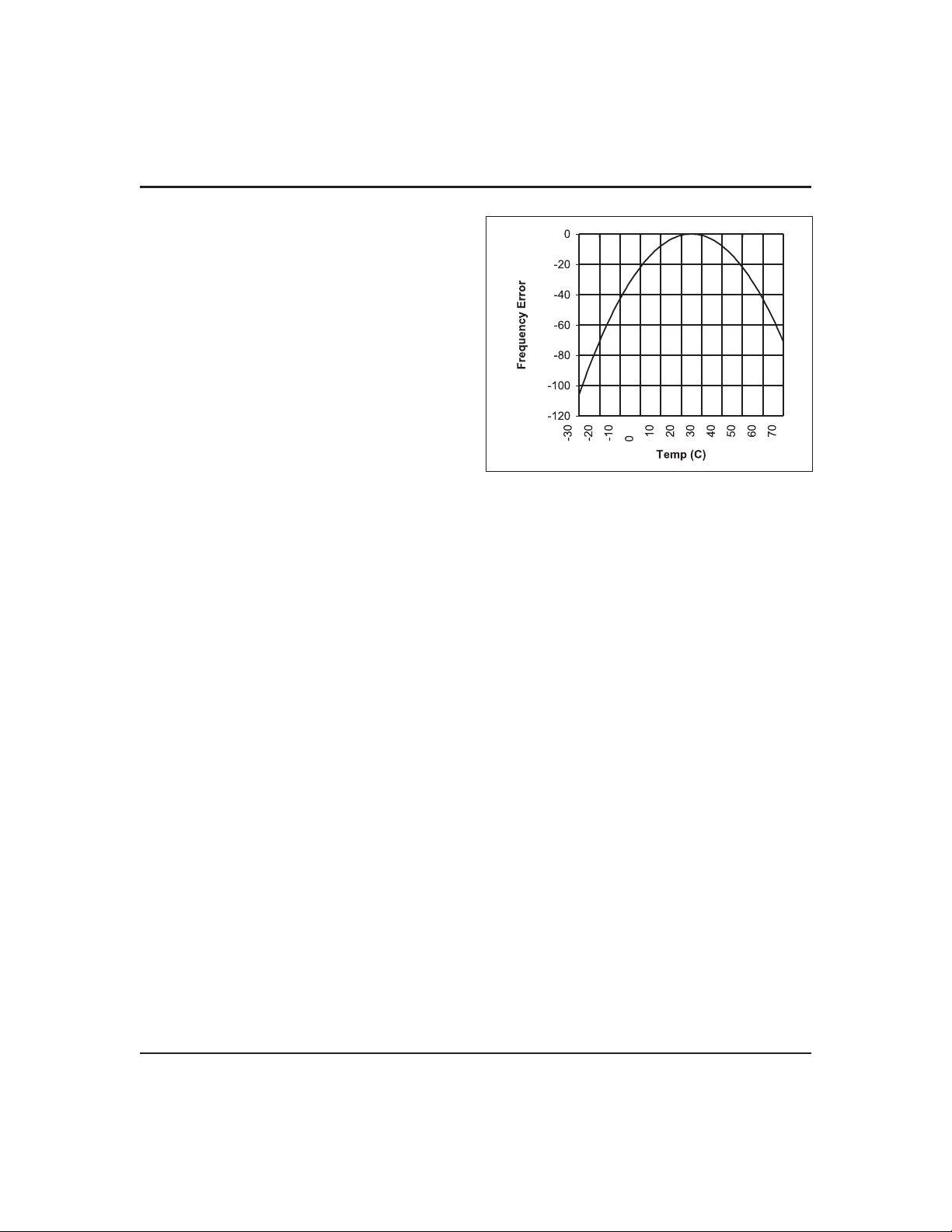

of crystals change with temperature as Figure 3 shows.

To compensate for the frequency shift, the bq4830Y offers onboard software clock calibration. The user can

adjust the calibration based on the typical operating

temperature of individual applications.

The software calibration bits are located in the control

register. Bits D0–D4 control the magnitude of correction, and bit D5 the direction (positive or negative) of

correction. Assuming that the oscillator is running at

exactly 32,786 Hz, each calibration step of D0–D4 adjusts the clock rate by +4.068 ppm (+10.7 seconds per

month) or -2.034 ppm (-5.35 seconds per month) depending on the value of the sign bit D5. When the sign bit is

1, positive adjustment occurs; a 0 activates negative adjustment. The total range of clock calibration is +5.5 or

-2.75 minutes per month.

Two methods can be used to ascertain how much cali-

bration a given bq4830Y may require in a system. The

first involves simply setting the clock,letting it run for a

month, and then comparing the time to an accurate

known reference like WWV radio broadcasts. Based on

the variation to the standard, the end user can adjust

the clock to match the system's environment even after

the product is packaged in a non-serviceable enclosure.

The only requirement is a utility that allows the end

user to access the calibration bits in the control register.

bq4830Y

Figure 3. Frequency Error

The second approach uses a bq4830Y test mode. When

the frequency test mode enable bit FTE in the days register is set to a 1, and the oscillator is running at exactly

32,768 Hz, the LSB of the seconds register toggles at

512 Hz. Any deviation from 512 Hz indicates the degree

and direction of oscillator frequency shift at the test

temperature. For example, a reading of 512.01024 Hz

indicates a (1E6 ∗ 0.01024)/512 or +20 ppm oscillator

frequency error, requiring ten steps of negative calibration (10 ∗ -2.034 or -20.34) or 001010 to be loaded into

the calibration byte for correction. To read the test frequency, the bq4830Y must be selected and held in an extended read of the seconds register, location 7FF9, without having the read bit set. The frequency appears on

DQ0. The FTE bit must be set using the write bit control. The FTE bit must be reset to 0 for normal clock operation to resume.

Sept. 1996 B

5

Loading...

Loading...