1

2

3

4

5

6 7 8 9 10

15

14

13

12

11

20 19 18 17 16

ACN

ACP

CMPOUT

CMPIN

ACOK

ACDET

IOUT

SDA

SCL

ILIM

IFAULT

SRN

SRP

GND

LODRV

REGN

BTST

HIDRV

PHASE

VCC

bq24707

bq24707A

www.ti.com

SLUSA78B –JULY 2010– REVISED MARCH 2011

1-4 Cell Li+ Battery SMBus Charge Controller With Independent Comparator and

Advanced Circuit Protection

Check for Samples: bq24707, bq24707A

bq24707

bq24707A

1

FEATURES

• SMBus Host-Controlled NMOS-NMOS

Synchronous Buck Converter with

Programmable 615kHz, 750kHz, and 885kHz

Switching Frequency

• Real Time System Control on ILIM Pin to Limit

Charge Current

• Enhanced Safety Features for Over Voltage

Protection, Over Current Protection, Battery,

Inductor, and MOSFET Short Circuit Protection

• Programmable Input Current, Charge Voltage,

Charge Current Limits

DESCRIPTION

The bq24707 and bq24707A are high-efficiency,

synchronous battery charger, offering low component

count for space-constraint, multi-chemistry battery

charging applications.

SMBus controlled input current, charge current, and

charge voltage DACs allow for very high regulation

accuracies that can be easily programmed by the

system power management micro-controller.

The IC uses the internal input current register or

external ILIM pin to throttle down PWM modulation to

reduce the charge current.

– ±0.5% Charge Voltage Accuracy up to 19.2V The IC provides an IFAULT output to alarm if any

– ±3% Charge Current Accuracy up to 8.128A

– ±3% Input Current Accuracy up to 8.064A

– ±2% 20x Adapter Current or Charge Current

Output Accuracy

• Programmable Adapter Detection and

Indicator

• Independent Comparator with Internal

Reference

MOSFET fault or input over current occurs. This

alarm output allows users to turn off input power

selectors when the fault occurs. Meanwhile, an

independent comparator with internal reference is

available to monitor input current, output current, or

output voltage.

The IC charges one, two, three, or four series Li+

cells, and is available in a 20-pin, 3.5×3.5 mm2QFN

package.

• Integrated Soft Start

• Integrated Loop Compensation

• AC Adapter Operating Range 5V-24V

• 15µA Off-State Battery Discharge Current

• 20-pin 3.5 x 3.5 mm2QFN Package

• bq24707: ACOK delay default 1.3s

• bq24707A: ACOK delay default 1.2ms

APPLICATIONS

• Portable Notebook Computers, UMPC,

Ultra-Thin Notebook, and Netbook

• Personal Digital Assistant

• Handheld Terminal

• Industrial and Medical Equipment

• Portable Equipment

1

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

© 2010–2011, Texas Instruments Incorporated

VCC

REGN

BTST

HIDRV

PHASE

LODRV

GND

SRP

SRN

Q4

Sis412DN

L1

4.7µH

SYSTEM

C10

10µF

RSR

10m?

R1

430k

R2

66.5k

C2

0.1µF

U1

bq24707

bq24707A

C8

10uF

Q3

Sis412DN

Q5 (BATFET)

Si4435DDY

C7

0.047µF

Adapter +

RAC 10m?

Pack +

C6

1µF

HOST

Dig I/O

SMBus

+3.3V

C4

100p

R4

10k

R5

10k

R7

316k

ACN

ACP

ACDET

ILIM

SDA

SCL

ACOK

IFAULT

CMPOUT

CMPIN

IOUT

Ci

2.2µF

Ri

2?

R9

10Ω

R3

10k

R8

100k

D1

BAT54

C9

10uF

C11

10µF

Pack -

C3

0.1µF

C5

1µF

C1

0.1µF

Total

Csys

220µF

Adapter -

ADC

Q1 (RBFET)

Si4435DDY

Q2 (ACFET)

Si4435DDY

PowerPad

R6

10k

Controlled

By Host

Controlled

By Host

D2

RB751V40

If no adapter,

and Iout is

needed, this

rail is on

+1.5V

R10

10k

R11

39.2k

R12

100k

R13

3.01M

C13

0.1µF

C14

0.1µF

R14

10Ω

R15

7.5Ω

*

*

bq24707

bq24707A

SLUSA78B –JULY 2010– REVISED MARCH 2011

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

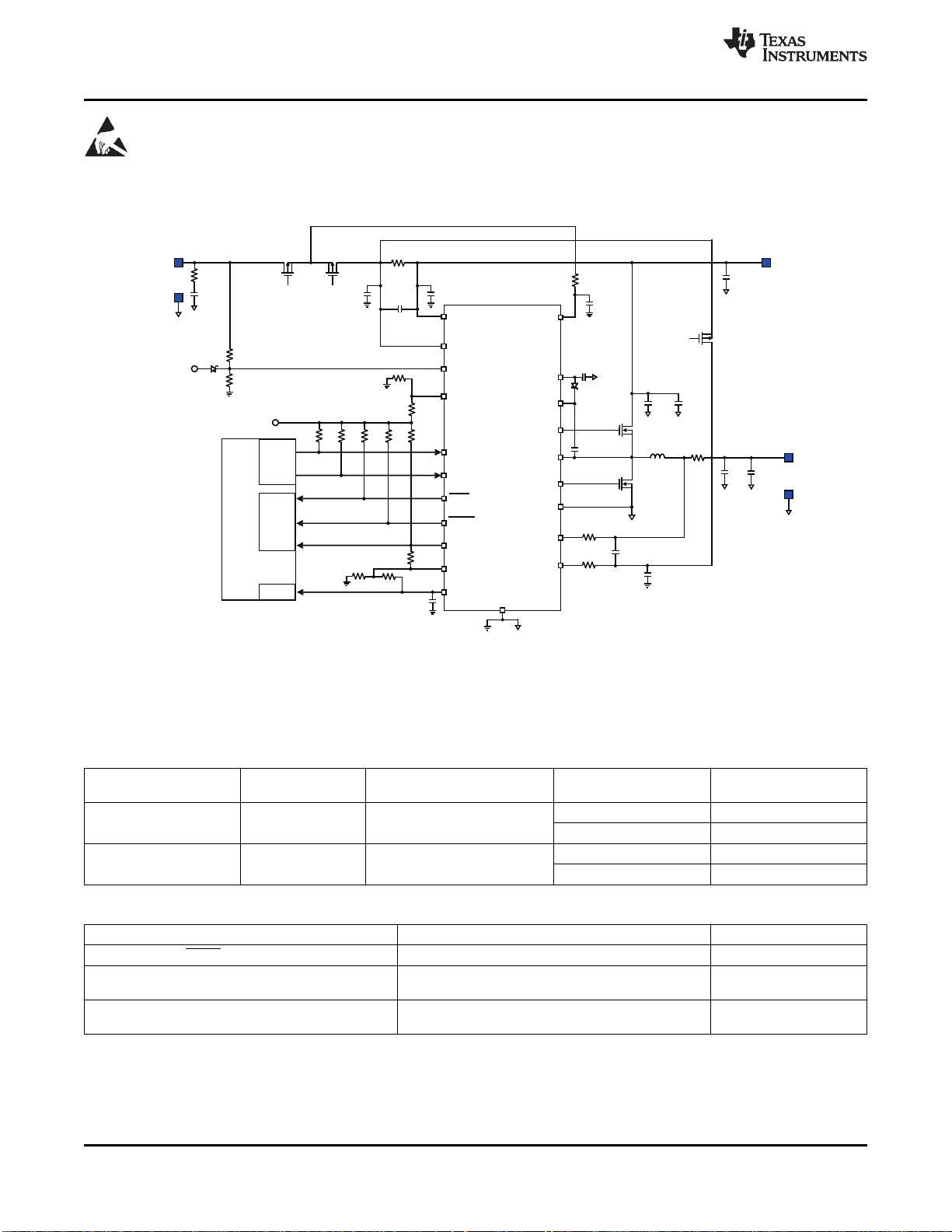

TYPICAL APPLICATION

Fs= 750kHz, I

= 4.096A, I

adpt

= 2.944A, I

chrg

lim

= 4A, V

= 12.592V, 90W adapter and 3S2P battery pack

chrg

See the application information about negative output voltage protection for hard shorts on battery to ground or

battery reverse connection.

Figure 1. Typical System Schematic

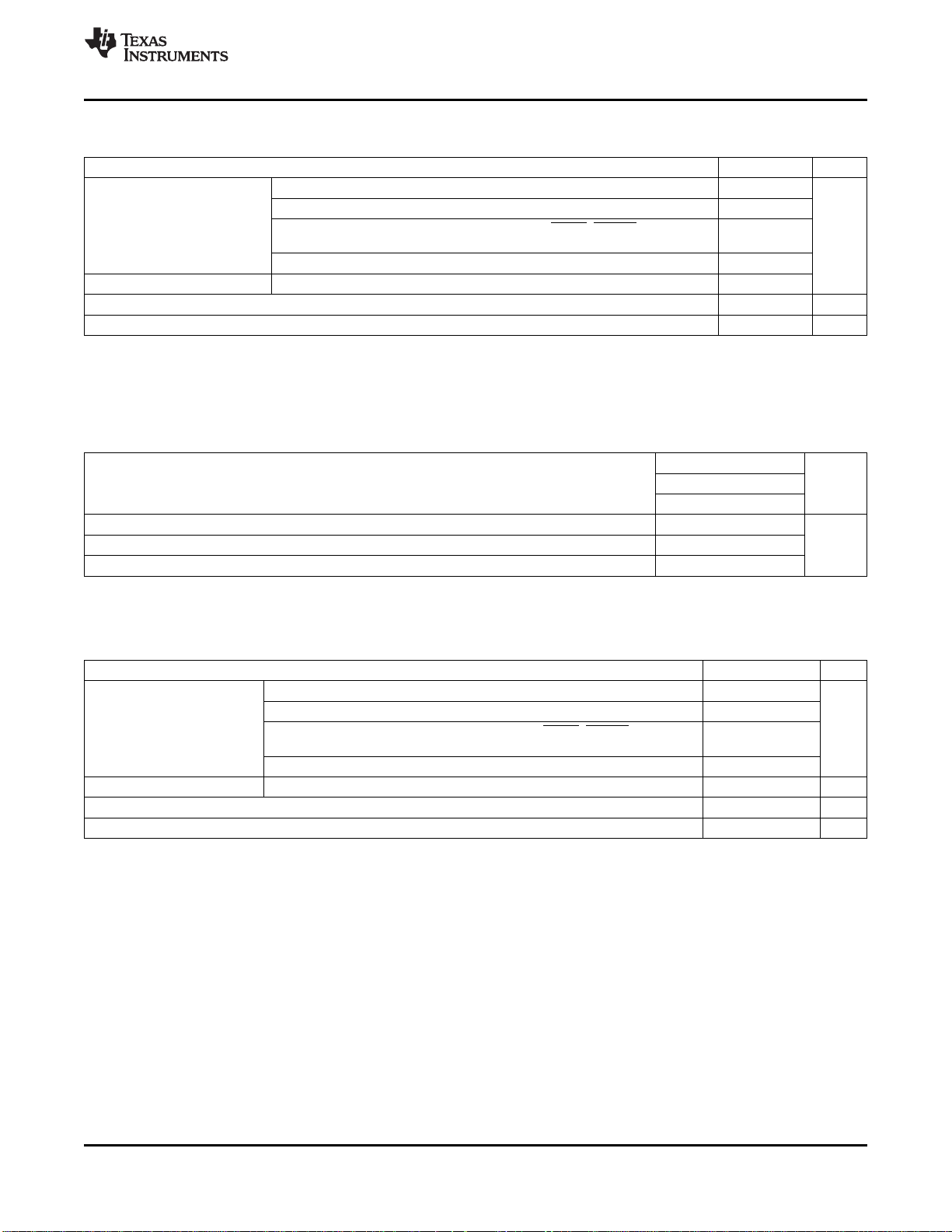

ORDERING INFORMATION

PART NUMBER IC MARKING PACKAGE QUANTITY

bq24707 BQ707 20-PIN 3.5 x 3.5mm2QFN

bq24707A BQ07A 20-PIN 3.5 x 3.5mm2QFN

Suggest fully charged battery ChargeVoltage() setting

Suggest fully charged battery ChargeCurrent() setting

2 Submit Documentation Feedback © 2010–2011, Texas Instruments Incorporated

Condition bq24707 bq24707A

ACOK default delay 1.3s 1.2ms

after termination

after termination

full scale charge voltage(12.592V for 3S battery) 0V

COMPARISON TABLE

Product Folder Link(s): bq24707 bq24707A

ORDERING NUMBER

(Tape and Reel)

bq24707RGRR 3000

bq24707RGRT 250

bq24707ARGRR 3000

bq24707ARGRT 250

0A 0A

bq24707

bq24707A

www.ti.com

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)

SRN, SRP, ACN, ACP, VCC –0.3 to 30

PHASE –2 to 30

Voltage range

Maximum difference voltage SRP–SRN, ACP–ACN –0.5 to 0.5

Junction temperature range, T

Storage temperature range, T

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND if not specified. Currents are positive into, negative out of the specified terminal. Consult Packaging

Section of the data book for thermal limitations and considerations of packages.

ACDET, SDA, SCL, LODRV, REGN, IOUT, ILIM, ACOK, IFAULT, CMPIN,

CMPOUT

BTST, HIDRV –0.3 to 36

J

stg

(1) (2)

THERMAL INFORMATION

THERMAL METRIC

θ

JA

ψ

ψ

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Junction-to-ambient thermal resistance 46.8

Junction-to-top characterization parameter 0.6 °C/W

JT

Junction-to-board characterization parameter 15.3

JB

(1)

SLUSA78B –JULY 2010– REVISED MARCH 2011

VALUE UNIT

–0.3 to 7 V

–40 to 155 °C

–55 to 155 °C

bq24707/bq24707A

RGR UNITS

20 PINS

RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

SRN, SRP, ACN, ACP, VCC 0 24

PHASE –2 24

Voltage range V

Maximum difference voltage SRP–SRN, ACP–ACN –0.2 0.2 V

Junction temperature range, T

Storage temperature range, T

ACDET, SDA, SCL, LODRV, REGN, IOUT, ILIM, ACOK, IFAULT, CMPIN,

CMPOUT

BTST, HIDRV 0 30

J

stg

0 6.5

0 125 °C

–55 150 °C

© 2010–2011, Texas Instruments Incorporated Submit Documentation Feedback 3

Product Folder Link(s): bq24707 bq24707A

bq24707

bq24707A

SLUSA78B –JULY 2010– REVISED MARCH 2011

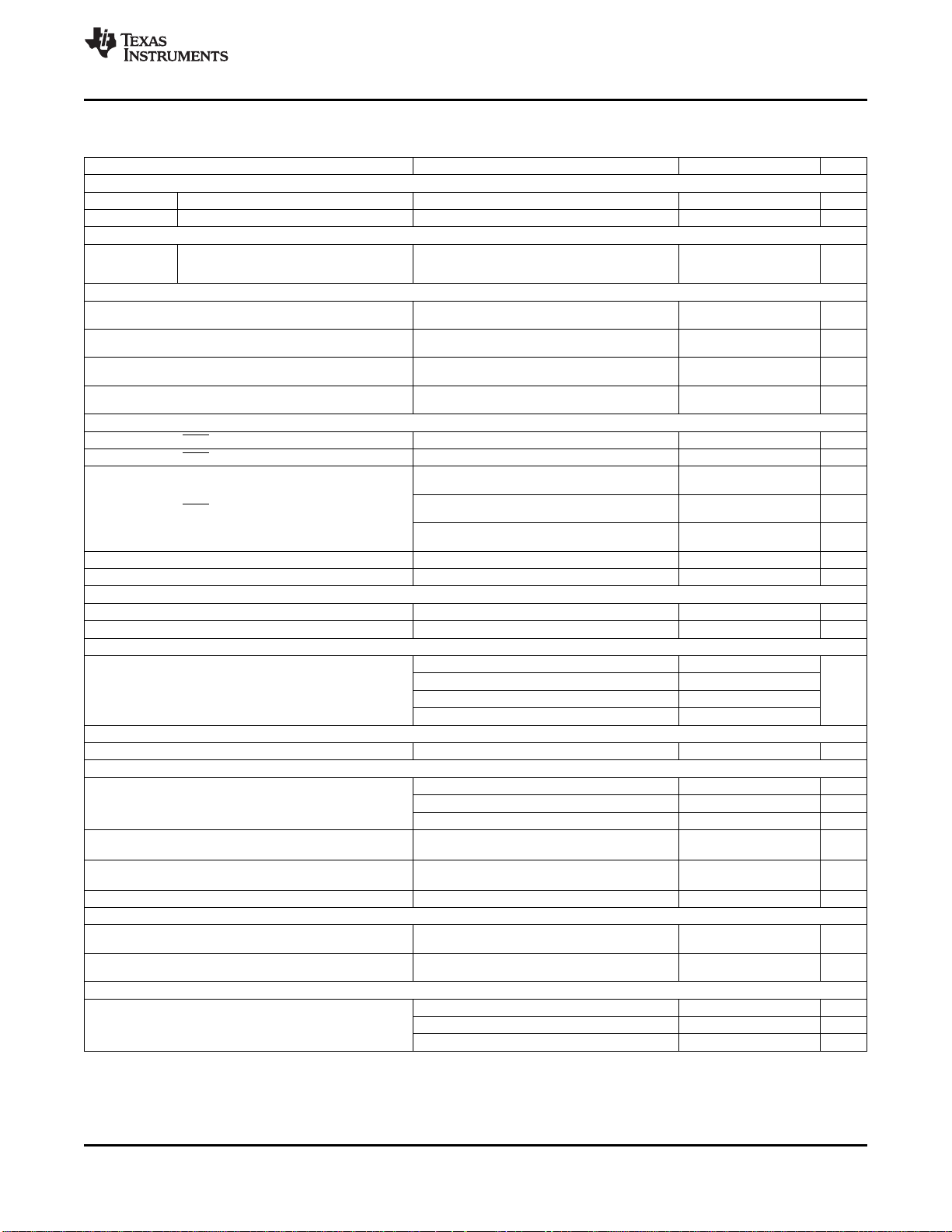

ELECTRICAL CHARACTERISTICS

4.5 V ≤ V

OPERATING CONDITIONS

V

VCC_OP

CHARGE VOLTAGE REGULATION

V

BAT_REG_RNG

V

BAT_REG_ACC

CHARGE CURRENT REGULATION

V

IREG_CHG_RNG

I

CHRG_REG_ACC

INPUT CURRENT REGULATION

V

IREG_DPM_RNG

I

DPM_REG_ACC

INPUT CURRENT OR CHARGE CURRENT SENSE AMPLIFIER

V

ACP/N_OP

V

SRP/N_OP

V

IOUT

I

IOUT

A

IOUT

V

IOUT_ACC

C

IOUT_MAX

REGN REGULATOR

V

REGN_REG

I

REGN_LIM

I

REGN_LIM_TSHUT

C

REGN

≤ 24 V, 0°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VCC Input voltage operating range 4.5 24 V

BAT voltage regulation range 1.024 19.2 V

Charge voltage regulation accuracy

Charge current regulation differential voltage range V

Charge current regulation accuracy 10mΩ current

sensing resistor

Input current regulation differential voltage range V

Input current regulation accuracy 10mΩ current

sensing resistor

Input common mode range Voltage on ACP/ACN 4.5 24 V

Output common mode range Voltage on SRP/SRN 0 19.2 V

IOUT output voltage range 0 1.6 V

IOUT output current 0 1 mA

Current sense amplifier gain V

Current sense output accuracy

Maximum output load capacitance For stability with 0 to 1mA load 100 pF

REGN regulator voltage V

REGN current limit mA

REGN output capacitor required for stability I

ChargeVoltage() = 0x41A0H

ChargeVoltage() = 0x3130H

ChargeVoltage() = 0x20D0H

ChargeVoltage() = 0x1060H

= V

IREG_CHG

SRP

- V

SRN

ChargeCurrent() = 0x1000H

ChargeCurrent() = 0x0800H

ChargeCurrent() = 0x0200H

ChargeCurrent() = 0x0100H

ChargeCurrent() = 0x0080H

= V

IREG_DPM

ACP

– V

ACN

InputCurrent() = 0x1000H

InputCurrent() = 0x0800H

InputCurrent() = 0x0400H

InputCurrent() = 0x0200H

(ICOUT)/V(SRP-SRN)

V

(SRP-SRN)

V

(SRP-SRN)

V

(SRP-SRN)

V

(SRP-SRN)

V

(SRP-SRN)

V

(SRP-SRN)

> 6.5V, V

VCC

V

REGN

V

REGN

= 100µA to 65mA 1 µF

LOAD

or V

(ACP-ACN)

or V

or V

or V

or V

or V

or V

= 0V, V

= 0V, V

= 40.96mV –2% 2%

(ACP-ACN)

= 20.48mV –4% 4%

(ACP-ACN)

= 10.24mV –15% 15%

(ACP-ACN)

= 5.12mV –20% 20%

(ACP-ACN)

= 2.56mV –33% 33%

(ACP-ACN)

= 1.28mV –50% 50%

(ACP-ACN)

> 0.6V (0-55mA load) 5.5 6 6.5 V

ACDET

> UVLO charge enabled and not in TSHUT 65 80

VCC

> UVLO charge disabled or in TSHUT 7 16

VCC

16.716 16.8 16.884 V

–0.5% 0.5%

12.529 12.592 12.655 V

–0.5% 0.5%

8.350 8.4 8.450 V

–0.6% 0.6%

4.163 4.192 4.221 V

–0.7% 0.7%

0 81.28 mV

3973 4096 4219 mA

–3% 3%

1946 2048 2150 mA

–5% 5%

410 512 614 mA

–20% 20%

172 256 340 mA

–33% 33%

64 128 192 mA

–50% 50%

0 80.64 mV

3973 4096 4219 mA

–3% 3%

1946 2048 2150 mA

–5% 5%

870 1024 1178 mA

–15% 15%

384 512 640 mA

–25% 25%

20 V/V

www.ti.com

4 Submit Documentation Feedback © 2010–2011, Texas Instruments Incorporated

Product Folder Link(s): bq24707 bq24707A

www.ti.com

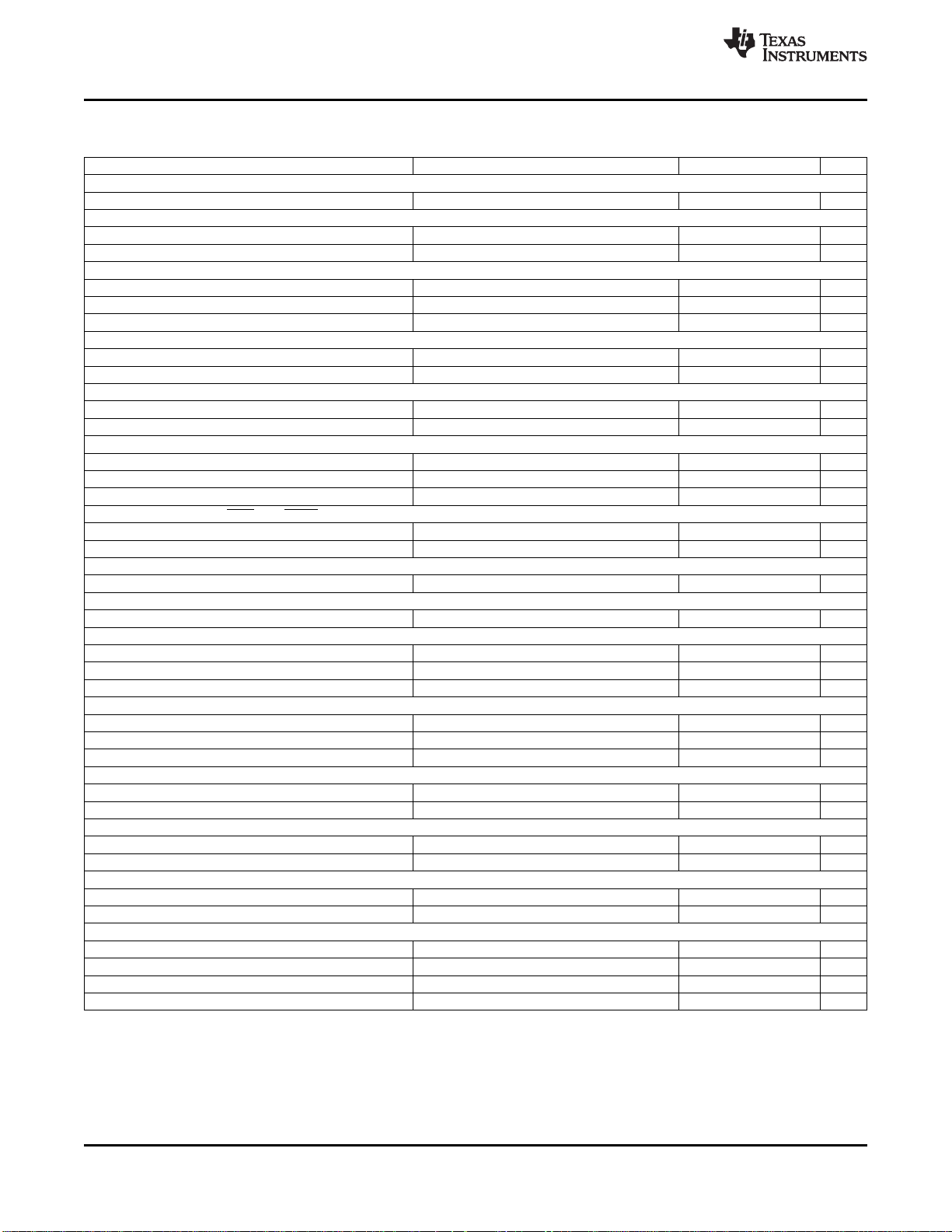

ELECTRICAL CHARACTERISTICS (continued)

4.5 V ≤ V

INPUT UNDERVOLTAGE LOCK-OUT COMPARATOR (UVLO)

V

UVLO

V

UVLO_HYS

FAST DPM COMPARATOR (FAST_DPM)

V

FAST_DPM

QUIESCENT CURRENT

I

BAT

I

STANDBY

I

AC_NOSW

I

AC_SW

ACOK COMPARATOR

V

ACOK_FALL

V

ACOK_RISE_HYS

t

ACOK_FALL_DEG

V

WAKEUP_RISE

V

WAKEUP_FALL

VCC to SRN COMPARATOR (VCC_SRN)

V

VCC-SRN_FALL

V

VCC-SRN _RHYS

HIGH SIDE IFAULT COMPARATOR (IFAULT_HI)

V

IFAULT_HI_RISE

LOW SIDE IFAULT COMPARATOR (IFAULT_LOW)

V

IFAULT_LOW_RISE

INPUT OVER-CURRENT COMPARATOR (ACOC)

V

ACOC

V

ACOC_min

V

ACOC_max

t

ACOC_DEG

BAT OVER-VOLTAGE COMPARATOR (BAT_OVP)

V

OVP_RISE

V

OVP_FALL

CHARGE OVERCURRENT COMPARATOR (CHG_OCP)

V

OCP_RISE

(1) User can adjust threshold via SMBus ChargeOption() REG0x12.

≤ 24 V, 0°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Input under voltage rising threshold V

Input under voltage falling hysteresis V

Fast DPM comparator stop charging rising threshold 108%

with respect to input current limit, voltage across input

sense resistor rising edge (specified by design)

Total battery leakage current to I

I

+ I

+ I

VCC

ACP

ACN

Standby quiescent current, I

Adapter bias current during charge, V

I

+ I

+ I

VCC

ACP

ACN

Adapter bias current during charge, V

I

+ I

+ I

VCC

ACP

ACN

VCC

SRN

+ I

+ I

ACP

SRP+IPHASE

+ I

ACN

+

ACOK falling threshold V

ACOK rising hysteresis V

ACOK falling deglitch (specified by design) 0.8 1.2 2 ms

WAKEUP detect rising threshold V

WAKEUP detect falling threshold V

VCC-SRN falling threshold V

VCC-SRN rising hysteresis V

(1)

rising 3.5 3.75 4 V

VCC

falling 340 mV

VCC

V

< V

VCC

BAT

V

> V

VCC

UVLO

TJ= 0 to 85°C

> V

VCC

UVLO

charge enabled, no switching, TJ= 0 to 85°C

> V

VCC

UVLO

charge enabled, switching, MOSFET Sis412DN

VCC>VUVLO

VCC>VUVLO

V

VCC>VUVLO

ChargeOption() bit [15] = 0 (default), (bq24707 only)

V

VCC>VUVLO

ChargeOption() bit [15] = 0 (default), (bq24707A only)

V

VCC>VUVLO

ChargeOption() bit [15] = 1

VCC>VUVLO

VCC>VUVLO

falling towards V

VCC

rising above V

VCC

ChargeOption() bit [8:7] = 00 200 300 450

ACP to PHASE rising threshold mV

ChargeOption() bit [8:7] = 01 330 500 700

ChargeOption() bit [8:7] = 10 (default) 450 700 1000

ChargeOption() bit [8:7] = 11 600 900 1250

PHASE to GND rising threshold 40 110 160 mV

(1)

Adapter over current rising threshold with respect to

input current limit, voltage across input sense resistor ChargeOption() bit [2:1] = 10 (default) 150% 166% 180%

rising edge

Min ACOC threshold clamp voltage 40 45 50 mV

Max ACOC threshold clamp voltage 140 150 160 mV

ChargeOption() bit [2:1] = 01 120% 133% 145%

ChargeOption() bit [2:1] = 11 200% 222% 240%

ChargeOption() bit [2:1] = 01 (133%),

InputCurrent() = 0x0400H (10.24mV)

ChargeOption() bit [2:1] = 11 (222%),

InputCurrent() = 0x1F80H (80.64mV)

ACOC deglitch time (specified by design) Voltage across input sense resistor rising to disable charge 1.7 2.5 3.3 ms

Over voltage rising threshold as percentage of V

V

BAT_REG

Over voltage falling threshold as percentage of V

V

BAT_REG

Charge over current rising threshold, measure voltage

drop across current sensing resistor

rising 103% 104% 106%

SRN

falling 102%

SRN

ChargeCurrent() = 0x0xxxH 54 60 66 mV

ChargeCurrent() = 0x1000H – 0x17C0H 80 90 100 mV

ChargeCurrent() = 0x1800 H– 0x1FC0H 110 120 130 mV

bq24707

bq24707A

SLUSA78B –JULY 2010– REVISED MARCH 2011

= 16.8V, TJ= 0 to 85°C 15 µA

, V

> 0.6V, charge disabled,

ACDET

, V

> 2.4V,

ACDET

, V

> 2.4V,

ACDET

, V

rising 2.376 2.4 2.424 V

ACDET

, V

falling 35 55 75 mV

ACDET

, V

rising above 2.4V,

ACDET

, V

rising above 2.4V,

ACDET

, V

rising above 2.4V, 10 50

ACDET

, V

rising 0.57 0.8 V

ACDET

, V

falling 0.3 0.51 V

ACDET

SRN

SRN

0.9 1.3 1.7 s

0.5 1 mA

1.5 3 mA

10 mA

70 125 180 mV

70 120 170 mV

μs

© 2010–2011, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Link(s): bq24707 bq24707A

bq24707

bq24707A

SLUSA78B –JULY 2010– REVISED MARCH 2011

ELECTRICAL CHARACTERISTICS (continued)

4.5 V ≤ V

CHARGE UNDER-CURRENT COMPARATOR (CHG_UCP)

V

UCP_FALL

LIGHT LOAD COMPARATOR (LIGHT_LOAD)

V

LL_FALL

V

LL_RISE_HYST

BATTERY LOWV COMPARATOR (BAT_LOWV)

V

BATLV_FALL

V

BATLV_RHYST

I

BATLV

THERMAL SHUTDOWN COMPARATOR (TSHUT)

T

SHUT

T

SHUT_HYS

ILIM COMPARATOR

V

ILIM_FALL

V

ILIM_RISE

LOGIC INPUT (SDA, SCL)

V

IN_ LO

V

IN_ HI

I

IN_ LEAK

LOGIC OUTPUT OPEN DRAIN (ACOK, SDA, IFAULT, CMPOUT)

V

OUT_ LO

I

OUT_ LEAK

ANALOG INPUT (ACDET, ILIM)

I

IN_ LEAK

ANALOG INPUT (CMPIN has 50kΩ series resistor and 2000kΩ pull down resistor)

I

IN_LEAK

PWM OSCILLATOR

F

SW

F

SW+

F

SW–

PWM HIGH SIDE DRIVER (HIDRV)

R

DS_HI_ON

R

DS_HI_OFF

V

BTST_REFRESH

PWM LOW SIDE DRIVER (LODRV)

R

DS_LO_ON

R

DS_LO_OFF

PWM DRIVER TIMING

t

LOW_HIGH

t

HIGH_LOW

INTERNAL SOFT START

I

STEP

t

STEP

INDEPENDENT COMPARATOR

V

IC_REF1

V

IC_REF2

R

S

R

DOWN

(2) User can adjust threshold via SMBus ChargeOption() REG0x12.

≤ 24 V, 0°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Charge under current falling threshold V

falling towards V

SRP

Light load falling threshold Measure voltage drop across current sensing resistor 1.25 mV

Light load rising hysteresis Measure voltage drop across current sensing resistor 1.25 mV

Battery LOWV falling threshold V

Battery LOWV rising hysteresis V

falling 2.4 2.5 2.6 V

SRN

rising 200 mV

SRN

Battery LOWV charge current limit 10mΩ current sensing resistor 0.5 A

Thermal shutdown rising temperature Temperature rising 155 °C

Thermal shutdown hysteresis, falling Temperature falling 20 °C

ILIM as CE falling threshold V

ILIM as CE rising threshold V

falling 60 75 90 mV

ILIM

rising 90 105 120 mV

ILIM

Input low threshold 0.8 V

Input high threshold 2.1 V

Input bias current V = 7 V –1 1 μA

Output saturation voltage 5 mA drain current 500 mV

Leakage current V = 7 V –1 1 μA

Input bias current V = 7 V –1 1 μA

Input bias current V = 7 V 1 3.5 7 μA

PWM switching frequency ChargeOption() bit [9] = 0 (default) 600 750 900 kHz

PWM increase frequency ChargeOption() bit [10:9] = 11 665 885 1100 kHz

PWM decrease frequency ChargeOption() bit [10:9] = 01 465 615 765 kHz

High side driver (HSD) turn-on resistance V

High side driver turn-off resistance V

Bootstrap refresh comparator threshold voltage V

Low side driver (LSD) turn-on resistance V

Low side driver turn-off resistance V

– VPH= 5.5 V, I = 10mA 12 20 Ω

BTST

– VPH= 5.5 V, I = 10mA 0.65 1.3 Ω

BTST

– VPHwhen low side refresh pulse is requested 3.85 4.3 4.7 V

BTST

= 6 V, I = 10 mA 15 25 Ω

REGN

= 6 V, I = 10 mA 0.9 1.4 Ω

REGN

Driver dead time from low side to high side 20 ns

Driver dead time from high side to low side 20 ns

Soft start step size In CCM mode, 10mΩ current sense resistor 64 mA

Soft start step time InCCM mode, 10mΩ current sense resistor 240 μs

(2)

Comparator reference ChargeOption() bit [4] = 0, rising edge (default) 0.585 0.6 0.615 V

Comparator reference ChargeOption() bit [4] = 1, rising edge 2.375 2.4 2.425 V

Series resistor 50 kΩ

Pull down resistor 2000 kΩ

SRN

www.ti.com

1 5 9 mV

6 Submit Documentation Feedback © 2010–2011, Texas Instruments Incorporated

Product Folder Link(s): bq24707 bq24707A

bq24707

bq24707A

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

4.5 V ≤ V

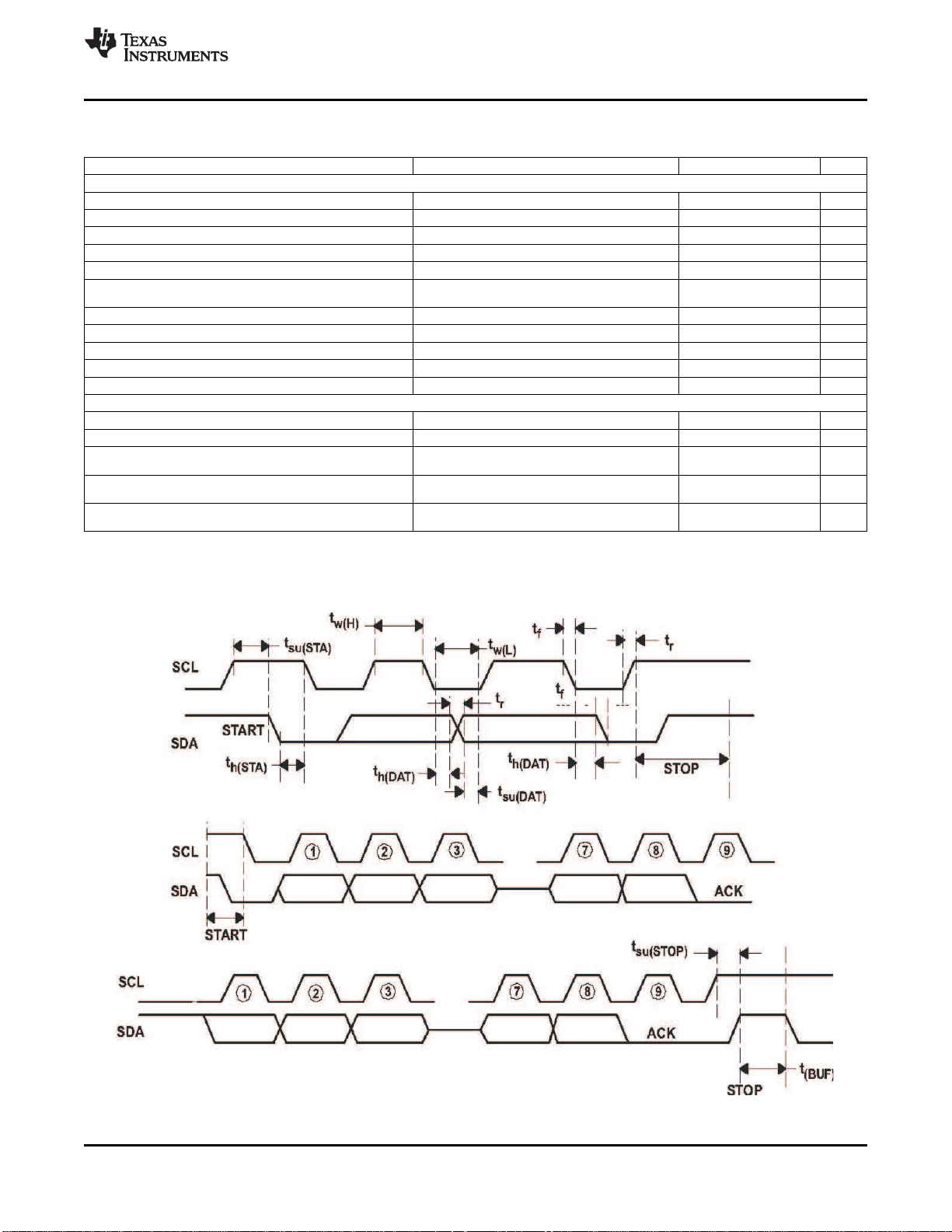

SMBus TIMING CHARACTERISTICS

t

R

t

F

t

W(H)

t

W(L)

t

SU(STA)

t

H(STA)

t

SU(DAT)

t

H(DAT)

t

SU(STOP)

t

(BUF)

F

S(CL)

HOST COMMUNICATION FAILURE

t

timeout

t

BOOT

t

WDI

t

WDI

t

WDI

(3) Devices participating in a transfer timeout when any clock low exceeds the 25ms minimum timeout period. Devices that have detected a

timeout condition must reset the communication no later than the 35ms maximum timeout period. Both a master and a slave must

adhere to the maximum value specified as it incorporates the cumulative stretch limit for both a master (10ms) and a slave (25ms).

(4) User can adjust threshold via SMBus ChargeOption() REG0x12.

≤ 24 V, 0°C ≤ TJ≤ 125°C, typical values are at TA= 25°C, with respect to GND (unless otherwise noted)

(VCC)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SCLK/SDATA rise time 1 μs

SCLK/SDATA fall time 300 ns

SCLK pulse width high 4 50 μs

SCLK pulse width low 4.7 μs

Setup time for START condition 4.7 μs

START condition hold time after which first clock

pulse is generated

Data setup time 250 ns

Data hold time 300 ns

Setup time for STOP condition 4 µs

Bus free time between START and STOP condition 4.7 μs

Clock frequency 10 100 kHz

SMBus bus release timeout

Deglitch for watchdog reset signal 10 ms

Watchdog timeout period, ChargeOption()

bit [14:13] = 01

Watchdog timeout period, ChargeOption()

bit [14:13] = 10

Watchdog timeout period, ChargeOption()

bit [14:13] = 11

(4)

(4)

(4)

(3)

(default)

SLUSA78B –JULY 2010– REVISED MARCH 2011

4 μs

25 35 ms

35 44 53 s

70 88 105 s

140 175 210 s

Figure 2. SMBus Communication Timing Waveforms

© 2010–2011, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Link(s): bq24707 bq24707A

bq24707

bq24707A

SLUSA78B –JULY 2010– REVISED MARCH 2011

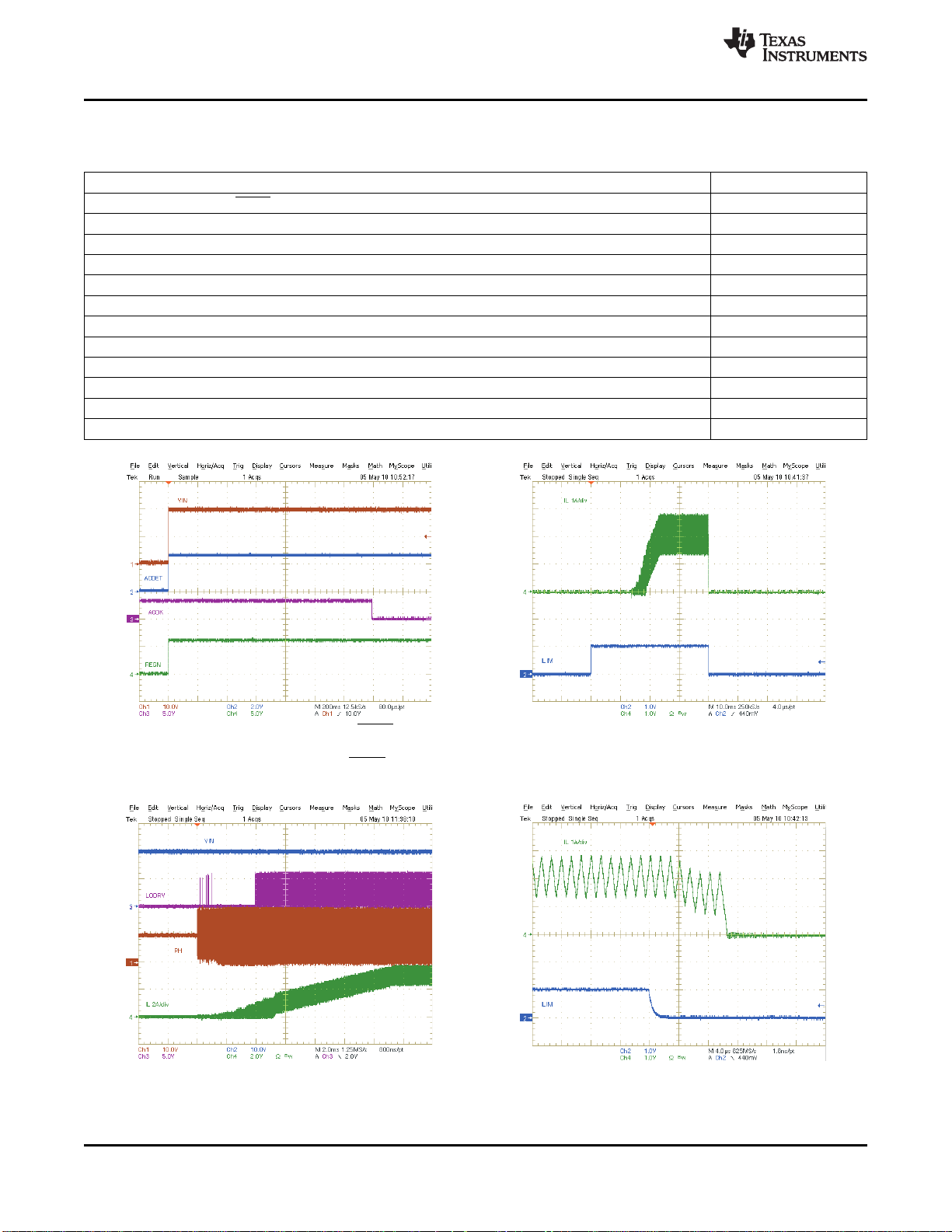

TYPICAL CHARACTERISTICS

Table 1. Table of Graphs

FIGURE NO.

VCC, ACDET, REGN and ACOK Power up (bq24707) Figure 3

Charge Enable by ILIM Figure 4

Current Soft-start Figure 5

Charge Disable by ILIM Figure 6

Continuous Conduction Mode Switching Waveforms Figure 7

Cycle-by-Cycle Synchronous to Non-synchronous Figure 8

100% Duty and Refresh Pulse Figure 9

System Load Transient (Input DPM) Figure 10

Battery Insertion Figure 11

Battery to Ground Short Protection Figure 12

Battery to Ground Short Transition Figure 13

Efficiency vs Output Current Figure 14

www.ti.com

CH1: VCC, 10V/div, CH2: ACDET, 2V/div, CH3: ACOK, 5V/div, CH2: ILIM, 1V/div, CH4: inductor current, 1A/div, 10ms/div

CH4: REGN, 5V/div, 200ms/div

Figure 3. VCC, ACDET, REGN and ACOK Power Up Figure 4. Charge Enable by ILIM

CH1: PHASE, 10V/div, CH2: Vin, 10V/div, CH3: LODRV, 5V/div,

CH4: inductor current, 2A/div, 2ms/div

Figure 5. Current Soft-Start Figure 6. Charge Disable by ILIM

8 Submit Documentation Feedback © 2010–2011, Texas Instruments Incorporated

(bq24707)

CH2: ILIM, 1V/div, CH4: inductor current, 1A/div, 4us/div

Product Folder Link(s): bq24707 bq24707A

www.ti.com

bq24707

bq24707A

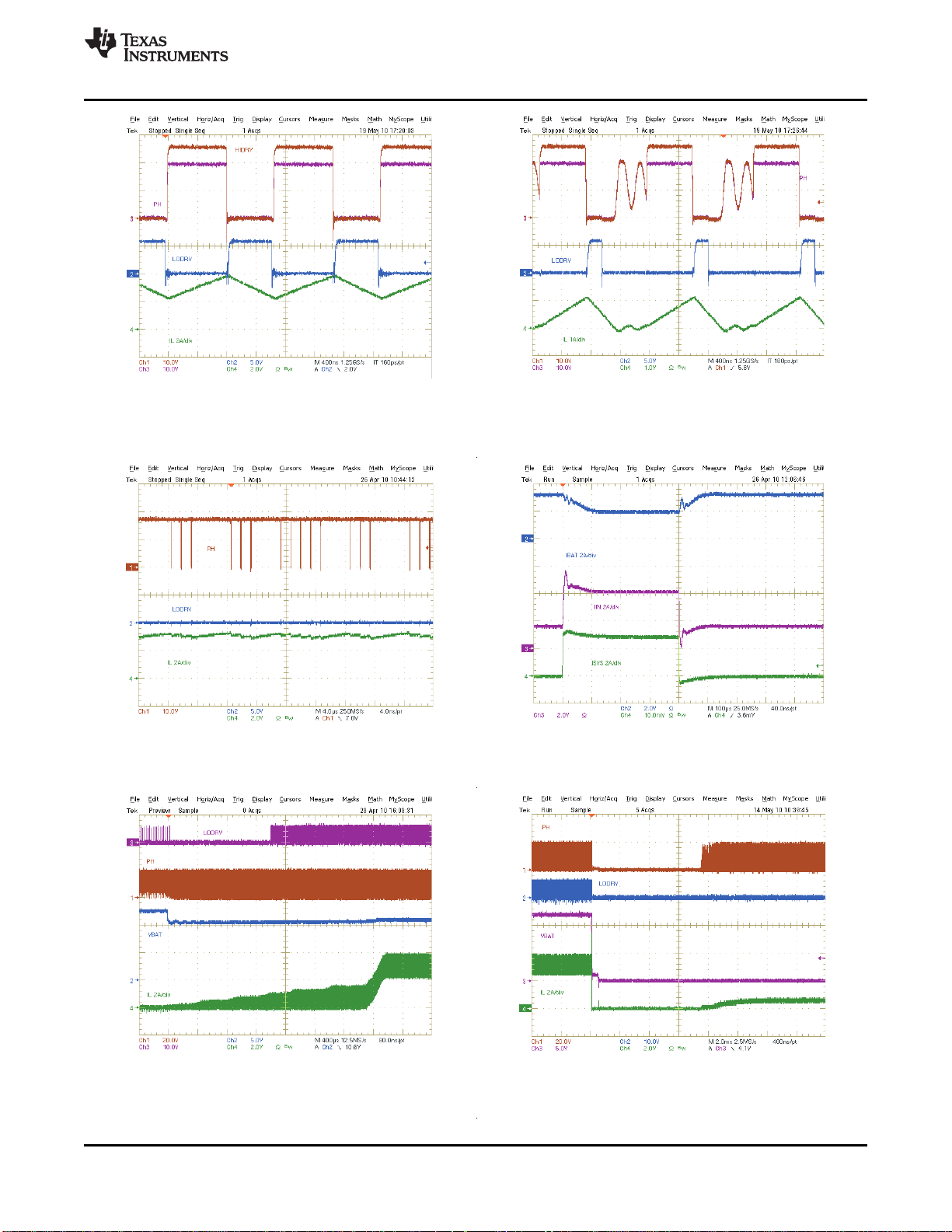

SLUSA78B –JULY 2010– REVISED MARCH 2011

CH1: HIDRV, 10V/div, CH2: LODRV, 5V/div, CH3: PHASE, 10V/div,

CH4: inductor current, 2A/div, 400ns/div

Figure 7. Continuous Conduction Mode Switching Figure 8. Cycle-by-Cycle Synchronous to

CH1: PHASE, 10V/div, CH2: LODRV, 5V/div, CH4: inductor current,

2A/div, 4us/div

Figure 9. 100% Duty and Refresh Pulse Figure 10. System Load Transient (Input DPM)

Waveforms Non-synchronous

CH1: HIDRV, 10V/div, CH2: LODRV, 5V/div, CH3: PHASE, 10V/div,

CH4: inductor current, 1A/div, 400ns/div

CH2: battery current, 2A/div, CH3: adapter current, 2A/div, CH4:

system load current, 2A/div, 100us/div

CH1: PHASE, 20V/div, CH2: battery voltage, 5V/div, CH3: LODRV,

10V/div, CH4: inductor current, 2A/div, 400us/div

Figure 11. Battery Insertion Figure 12. Battery to Ground Short Protection

© 2010–2011, Texas Instruments Incorporated Submit Documentation Feedback 9

Product Folder Link(s): bq24707 bq24707A

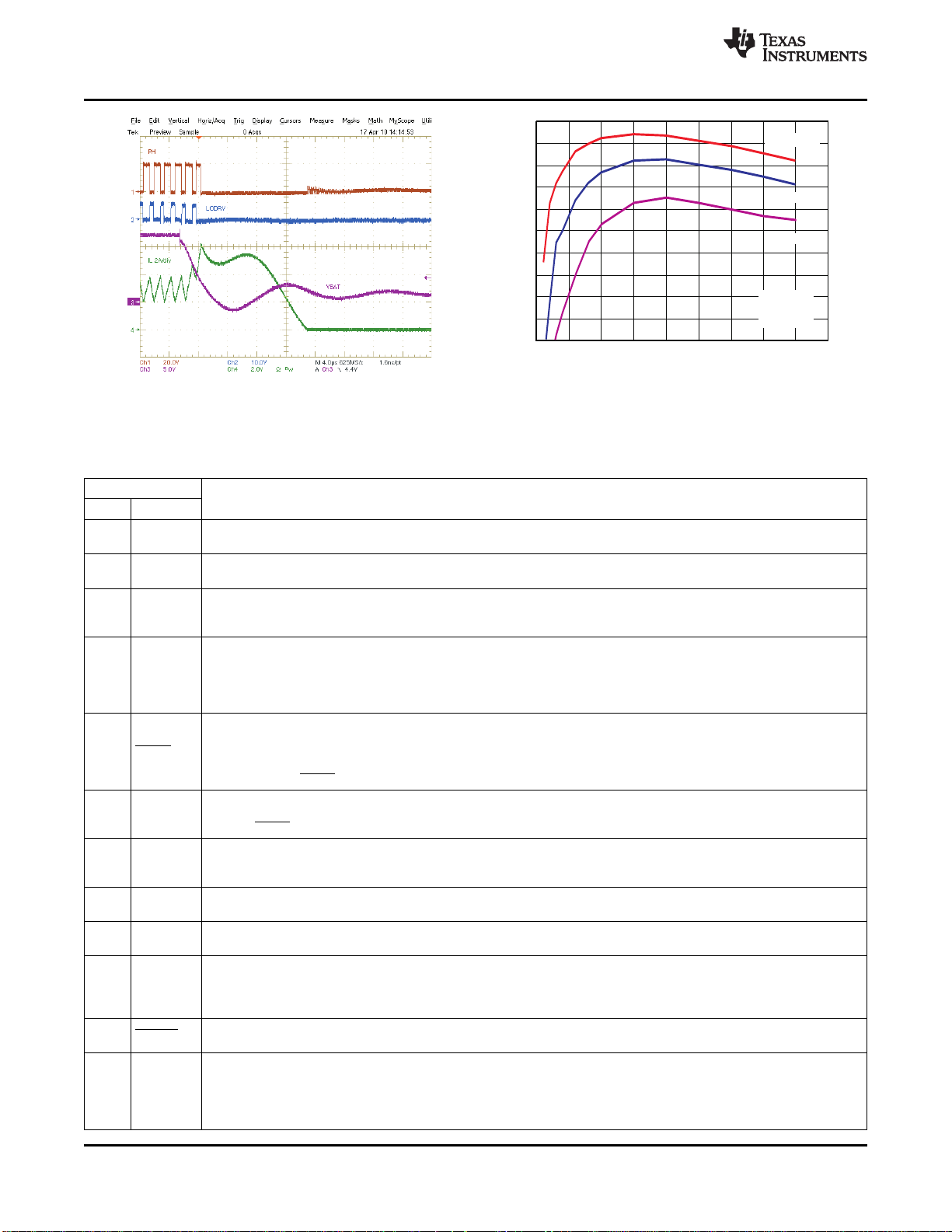

CH1: PHASE, 20V/div, CH2: LODRV, 10V/div, CH3: battery voltage,

5V/div, CH4: inductor current, 2A/div, 2ms/div

88

89

90

91

92

93

94

95

96

97

98

0 0.5 1 1.5 2 2.5 3 3.5 4 4.5

ChargeCurrent

4-cell16.8V

3-cell12.6V

2-cell8.4V

Efficiency-%

V =20V,

f=750kHz,

L =4.7 HIm

bq24707

bq24707A

SLUSA78B –JULY 2010– REVISED MARCH 2011

CH1: PHASE, 20V/div, CH2: LODRV, 10V/div, CH3: battery voltage,

5V/div, CH4: inductor current, 2A/div, 4us/div

Figure 13. Battery to Ground Short Transition Figure 14. Efficiency vs Output Current

PIN

NO. NAME

1 ACN

2 ACP

3 CMPOUT Internal reference is 0.6V or 2.4V, selectable by SMBus command ChargeOption(). When CMPIN is above the internal

4 CMPIN current comparison or from the SRN pin to the CMPIN pin to the GND pin for battery voltage comparison. The internal

5 ACOK voltage on the SRN pin, indicating a valid adapter is present to start charge. If any one of the above conditions cannot

6 ACDET input to the ACDET pin to the GND pin. When the ACDET pin is above 0.6V and VCC is above UVLO, REGN LDO is

7 IOUT the differential voltage across the sense resistor. Place a 100pF or less ceramic decoupling capacitor from the IOUT

8 SDA

9 SCL

10 ILIM

11 IFAULT

12 SRN filtering and connect to current sensing resistor. Connect a 0.1µF ceramic capacitor between current sensing resistor

10 Submit Documentation Feedback © 2010–2011, Texas Instruments Incorporated

Input current sense resistor negative input. Place an optional 0.1µF ceramic capacitor from ACN to GND for

common-mode filtering. Place a 0.1µF ceramic capacitor from ACN to ACP to provide differential mode filtering.

Input current sense resistor positive input. Place a 0.1µF ceramic capacitor from ACP to GND for common-mode

filtering. Place a 0.1µF ceramic capacitor from ACN to ACP to provide differential-mode filtering.

Open-drain output of independent comparator. Place a 10kΩ pull-up resistor from CMPOUT to pull-up supply rail.

reference, CMPOUT goes HIGH. Place a resistor between CMPIN and CMPOUT to program hysteresis.

Input of independent comparator. It has one 50kΏ series resistor and one 2000kΏ pull-down resistor. Program CMPIN

voltage by connecting a resistor divider from the IOUT pin to the CMPIN pin to the GND pin for adapter or charge

reference is 0.6V or 2.4V, selectable by SMBus command ChargeOption(). When CMPIN is above the internal

reference, CMPOUT goes HIGH. Place a resistor between CMPIN and CMPOUT to program hysteresis.

AC adapter detect open drain output. It is pulled LOW to GND by an internal MOSFET when the voltage on the

ACDET pin is above 2.4V, voltage on the VCC pin is above UVLO and voltage on the VCC pin is 245mV above the

meet, it is pulled HIGH to the external pull-up supply rail by an external pull-up resistor. Connect a 10kΩ pull-up

resistor from the ACOK pin to the pull-up supply rail.

Adapter detection input. Program the adapter valid input threshold by connecting a resistor divider from the adapter

present, ACOK comparator and IOUT are both active.

Buffered adapter or charge current output, selectable with SMBus command ChargeOption(). IOUT voltage is 20 times

pin to GND.

SMBus open-drain data I/O. Connect to the SMBus data line from the host controller or smart battery. Connect a 10kΩ

pull-up resistor according to SMBus specifications.

SMBus open-drain clock input. Connect to the SMBus clock line from the host controller or smart battery. Connect a

10kΩ pull-up resistor according to SMBus specifications.

Charge current limit input. Program ILIM voltage by connecting a resistor divider from the system reference 3.3V rail to

the ILIM pin to the GND pin. The lower of the ILIM voltage or DAC limit voltage sets the charge current regulation limit.

To disable control on ILIM, set ILIM above 1.6V. Once the voltage on the ILIM pin falls below 75mV, charge is

disabled. Charge is enabled when the ILIM pin rises above 105mV.

Open-drain output. It is pulled LOW by an internal MOSFET when ACOC or a short circuit is detected. It is pulled

HIGH to the external pull-up supply rail by an external pull-up resistor in normal condition.

Charge current sense resistor negative input. The SRN pin is for battery voltage sensing as well. Connect SRN pin to

a 7.5 Ω resistor first then from resistor another terminal connect a 0.1µF ceramic capacitor to GND for common-mode

to provide differential mode filtering. See application information about negative output voltage protection for hard

shorts on battery to ground or battery reverse connection by adding small resistor.

www.ti.com

PIN FUNCTIONS – 20-PIN QFN

DESCRIPTION

Product Folder Link(s): bq24707 bq24707A

bq24707

bq24707A

www.ti.com

PIN FUNCTIONS – 20-PIN QFN (continued)

PIN

NO. NAME

Charge current sense resistor positive input. Connect SRP pin to a 10 Ω resistor first then from resistor another

13 SRP

14 GND

15 LODRV Low side power MOSFET driver output. Connect to low side n-channel MOSFET gate.

16 REGN voltage on the ACDET pin is above 0.6V and voltage on VCC is above UVLO. Connect a 1uF ceramic capacitor from

17 BTST

18 HIDRV High side power MOSFET driver output. Connect to the high side n-channel MOSFET gate.

19 PHASE High side power MOSFET driver source. Connect to the source of the high side n-channel MOSFET.

20 VCC

PowerPAD solder PowerPAD to the board, and have vias on the PowerPAD plane connecting to analog ground and power

terminal connect to current sensing resistor. Connect a 0.1µF ceramic capacitor between current sensing resistor to

provide differential mode filtering. See application information about negative output voltage protection for hard shorts

on battery to ground or battery reverse connection by adding small resistor.

IC ground. On PCB layout, connect to the analog ground plane, and only connect to power ground plane through the

PowerPAD underneath the IC.

Linear regulator output. REGN is the output of the 6V linear regulator supplied from VCC. The LDO is active when the

REGN to GND.

High side power MOSFET driver power supply. Connect a 0.047µF capacitor from BTST to PHASE, and a bootstrap

Schottky diode from REGN to BTST.

Input supply, diode OR from adapter or battery voltage. Use 10Ω resistor and 1µF capacitor to ground as low pass

filter to limit inrush current.

Exposed pad beneath the IC. Analog ground and power ground star-connected only at the PowerPAD plane. Always

ground planes. It also serves as a thermal pad to dissipate the heat.

DESCRIPTION

SLUSA78B –JULY 2010– REVISED MARCH 2011

© 2010–2011, Texas Instruments Incorporated Submit Documentation Feedback 11

Product Folder Link(s): bq24707 bq24707A

UVLO

WAKEUP

3.75V

0.6V

EN_REGN

2.4V

ACOK_DRV

20X

VREF_IAC

20X

VREF_ICHG

VREF_VREG

FBO EAI

EAO

RAMP

Frequency **

200mV

4mA in

BATOVP

SMBus Interface

ChargeOption()

ChargeCurrent()

ChargeVoltage()

InputCurrent()

ManufactureID()

DeviceID()

15

14

19

18

17

7

13

12

5

6

20

2

1

8

9

3

10uA

REGN

LDO

REGN

LDO

VFB

BATOVP

VFB

104%VREF_VREG

VCC

SRN+245mV

VCC-SRN

CHG_UCP

5mV

SRP-SRN

CHG_OCP

SRP-SRN

60mV/90mV/120mV

BAT_LOWV

2.5V

SRN

TSHUT

Tj

155?C

REFRESH

4.3V

BTST-PH

1X

10

VCC

ACDET

ACOK

IOUT

ACP

ACN

ILIM

SRP

SRN

SDA

SCL

GND

LODRV

REGN

PHASE

HIDRV

BTST

CMPOUT

CMPIN

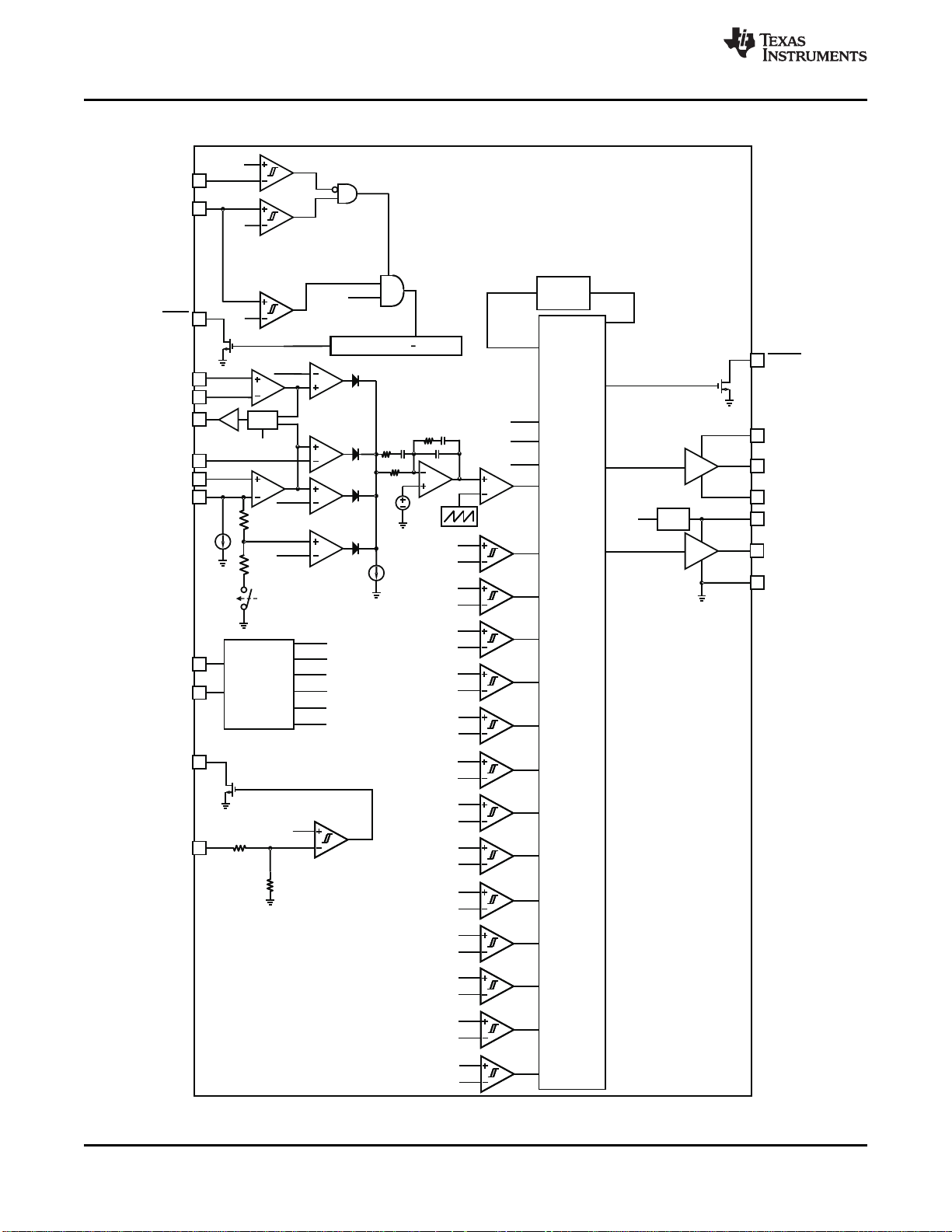

bq24707 and bq24707A Block Diagram

** Threshold or deglitch time is adjustable by ChargeOption()

Type III

Compensation

ACGOOD

VCC_SRN

CE

ILIM

105mV

WATCHDOG

TIMEOUT

EN_REGN

EN_CHRG

HSON

LSON

Driver Logic

IFAULT_HI

ACP-PH

700mV **

ACOC

ACP-ACN

1.66xVREF_IAC **

MUX

4

1.3s rising deglitch** (bq24707)

1.2ms rising deglitch** (bq24707A)

IFAULT_LOPH-GND

110mV

LIGHT_LOAD

1.25mV

SRP-SRN

PWM

WATCHDOG

TIMER

175s **

WATCHDOG

TIMER

175s **

DAC_VALID

CHARGE_INHIBIT

ACOK_DRV

16

11

IFAULT

IFAULT

0.6V **

CMPOUT_DRV

50kΩ

2000kΩ

IOUT_SEL

DAC_VALID

CHARGE_INHIBIT

VREF_VREG

VREF_ICHG

VREF_IAC

IOUT_SEL

WAKEUP

FAST_DPM

ACP-ACN

1.08xVREF_IAC

bq24707

bq24707A

SLUSA78B –JULY 2010– REVISED MARCH 2011

www.ti.com

FUNCTIONAL BLOCK DIAGRAM

Figure 15. Functional Block Diagram for bq24707 and bq24707A

12 Submit Documentation Feedback © 2010–2011, Texas Instruments Incorporated

Product Folder Link(s): bq24707 bq24707A

Loading...

Loading...