Texas Instruments 5962-9753001QXA Datasheet

TSB12L V31

Data Manual

IEEE 1394-1995 General-Purpose

Link-Layer Controller

For Computer Peripherals and

Consumer Audio/Video Electronics

SLLS255A

SEPTEMBER 1998

Printed on Recycled Paper

IMPORTANT NOTICE

T exas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue

any product or service without notice, and advise customers to obtain the latest version of relevant information

to verify, before placing orders, that information being relied on is current and complete. All products are sold

subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those

pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in

accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent

TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily

performed, except those mandated by government requirements.

CERT AIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MA Y INVOLVE POTENTIAL RISKS OF

DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL

APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICA TIONS IS UNDERST OOD TO

BE FULLY AT THE CUSTOMER’S RISK.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent

that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other

intellectual property right of TI covering or relating to any combination, machine, or process in which such

semiconductor products or services might be or are used. TI’s publication of information regarding any third

party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.

Copyright 1998, Texas Instruments Incorporated

iii

Contents

Section Title Page

1 Overview 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1 Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Features 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Related Documents 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

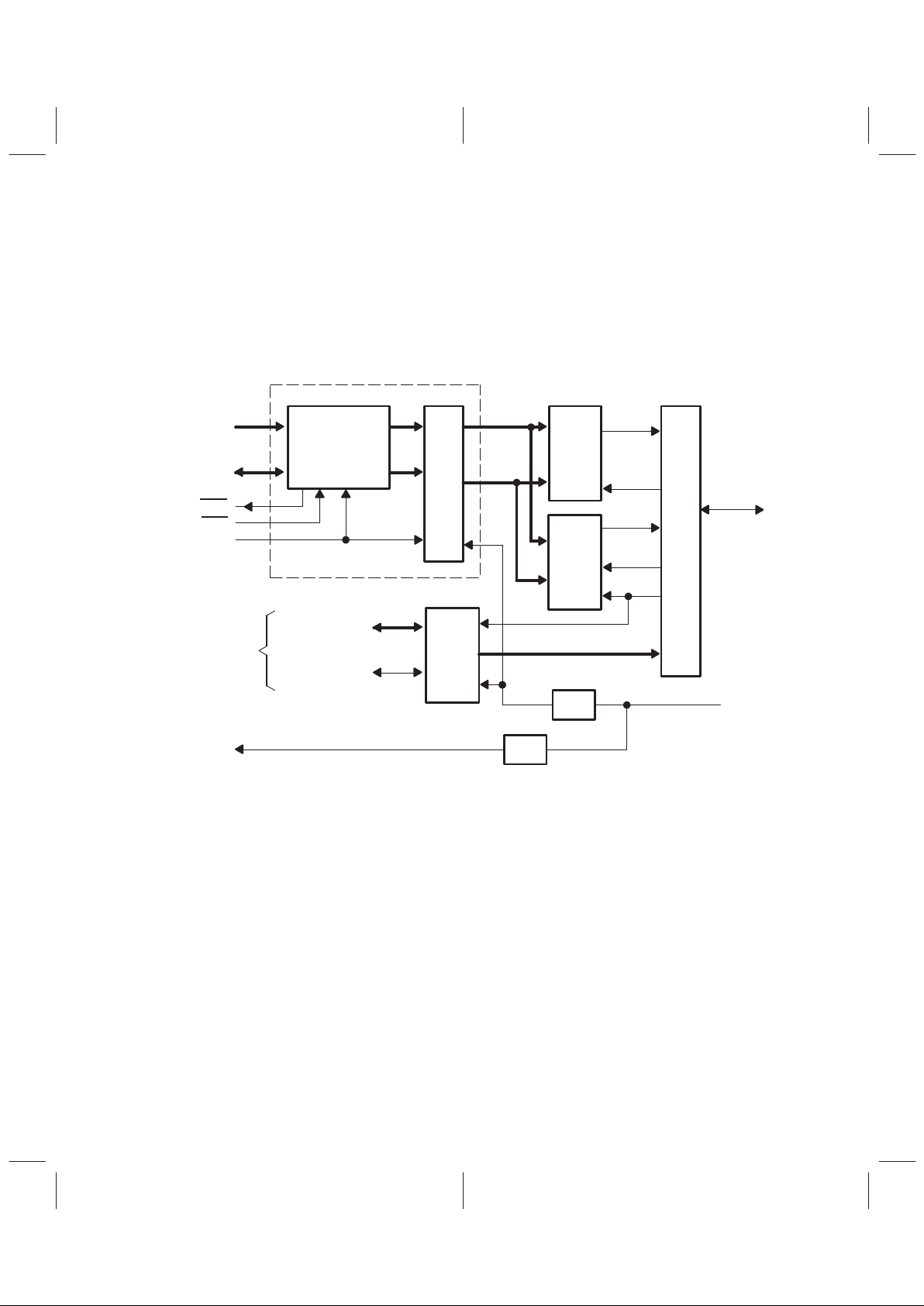

1.4 Functional Block Diagram 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

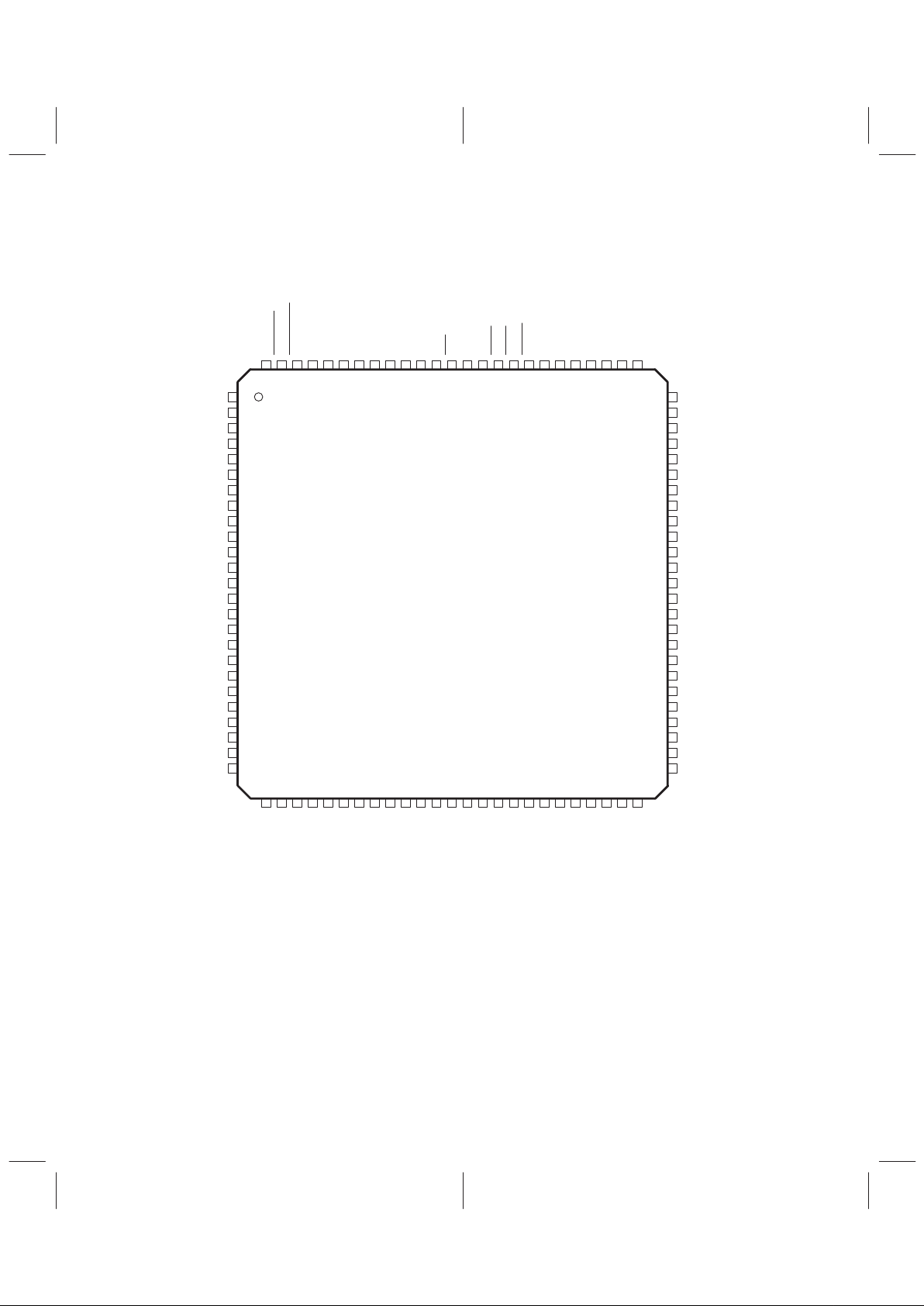

1.5 Terminal Assignments 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.6 Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 Architecture 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1 Functional Block Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 FIFO 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Microcontroller Interface 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.3 Link Core 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.4 Data Mover (DM) Control 2–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Internal Registers 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1 Memory and Configuration Address Space Register Map 3–1. . . . . . . . . . . . . . . . . . .

3.1.1 TSB12LV31 Configuration Registers 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Configuration Register Definitions 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Version Register @00h 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 MISC Register @04h 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.3 Control Register @08h 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.4 Interrupt/Interrupt Mask Register @0Ch/10h 3–5. . . . . . . . . . . . . . . . . . . . . . . . .

3.2.5 Cycle Timer Register @14h 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.6 IsoPort Number Register @18h 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.7 Diagnostics Register @20h 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.8 Phy Access Register @24h 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.9 ATF Status Register @30h 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.10 Bus Reset Register @34h 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.11 Self-ID Check Register @38h 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.12 GRF Status Register @3Ch 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.13 FIFO State Register @50h 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.14 Isochronous Control Register @54h 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.15 Isochronous Mode Register @58h 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.16 Isochronous Header Register @5Ch 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

iv

Contents (continued)

Section Title Page

4 FIFO Access 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1 FIFO Access 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.1 A TF Access 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.1.2 General-Receive-FIFO (GRF) 4–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 TSB12LV31 Data Formats 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1 Asynchronous Transmit (Host Bus to TSB12LV31) 5–1. . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 Quadlet Transmit 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 Block Transmit 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3 Quadlet Receive 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.4 Block Receive 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Isochronous Transmit (Host Bus to TSB12LV31) 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3 Isochronous Receive (TSB12LV31 to Host Bus) 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4 Snoop 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5 CycleMark 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6 Phy Configuration 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7 Receive Self-ID Packet 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6 Electrical Characteristics 6–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.1 Absolute Maximum Ratings Over Free-Air Temperature Range 6–1. . . . . . . . . . . . . .

6.2 Recommended Operating Conditions 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.3 Electrical Characteristics Over Recommended Ranges of Supply Voltage and

Operating Free-Air Temperature Range 6–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Microcontroller Write Switching Characteristics Over Operating Free-Air

Temperature Range 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.5 Microcontroller Read Switching Characteristics Over Operating Free-Air

Temperature Range 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.6 IsoPort Phase 1, 2, and 3 Switching Characteristics Over Operating Free-Air

Temperature Range 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.7 IsoPort Receive Switching Characteristics Over Operating Free-Air

Temperature Range 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.8 Link Read/Write Switching Characteristics Over Operating Free-Air

Temperature Range 6–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6.9 Output Signals Synchronous with ISOCK Switching Characteristics Over Operating

Free-Air Temperature Range 6–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7 Mechanical Information 7–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

List of Illustrations

Figure Title Page

1–1 TSB12LV31 Functional Block Diagram 1–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 Terminal Assignments 1–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

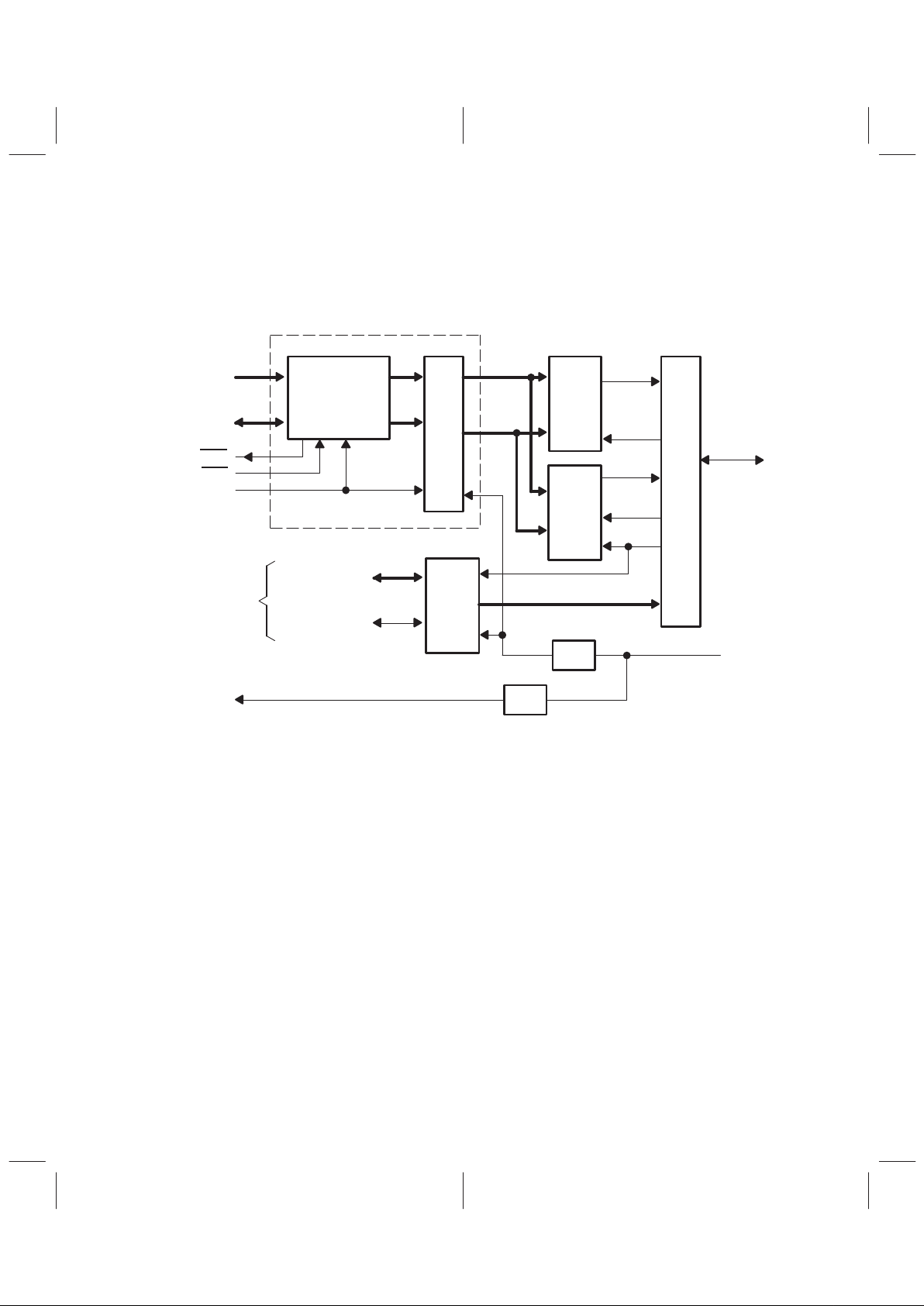

2–1 TSB12LV31 Functional Block Diagram 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

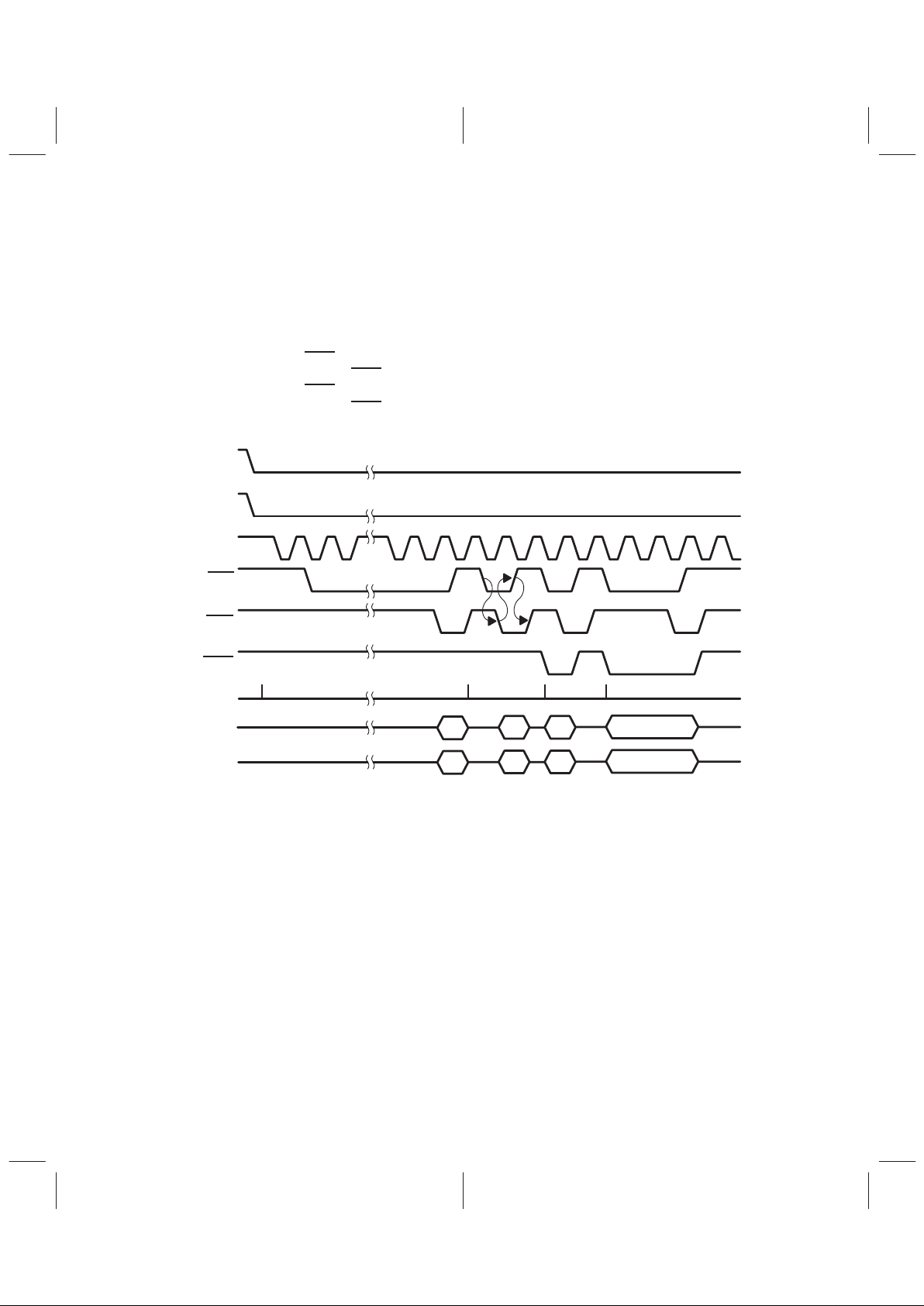

2–2 Typical Handshake Doublet-Mode Timing Waveforms 2–2. . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Typical Handshake Byte-Mode Timing Waveforms 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Pulse Mode Timing Waveforms 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

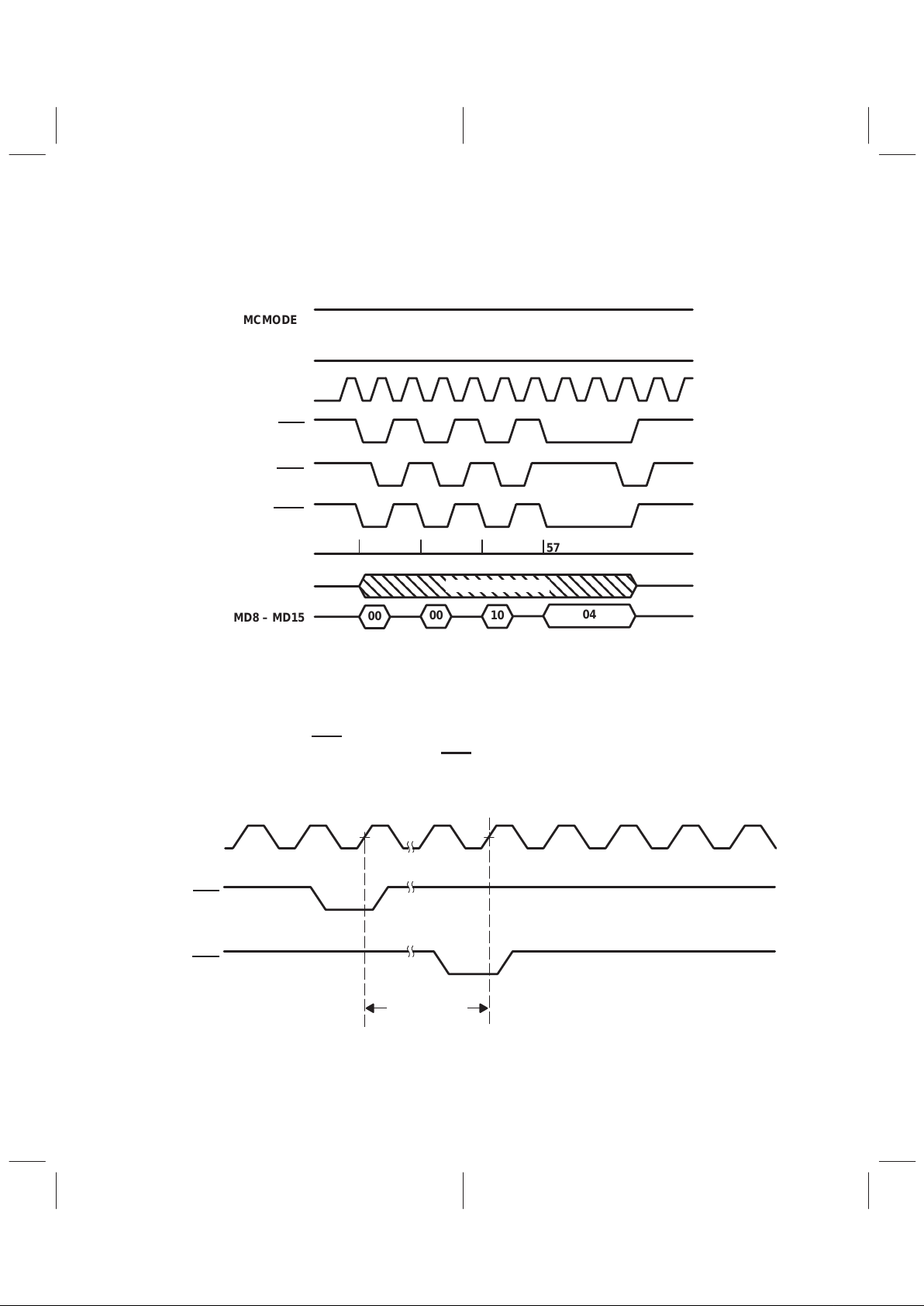

2–5 Timing Waveforms for 16-Bit Pulse Mode with Fixed Timing 2–5. . . . . . . . . . . . . . . . . . . . .

2–6 Timing Waveforms for 8-Bit Pulse Mode with Fixed Timing 2–7. . . . . . . . . . . . . . . . . . . . . .

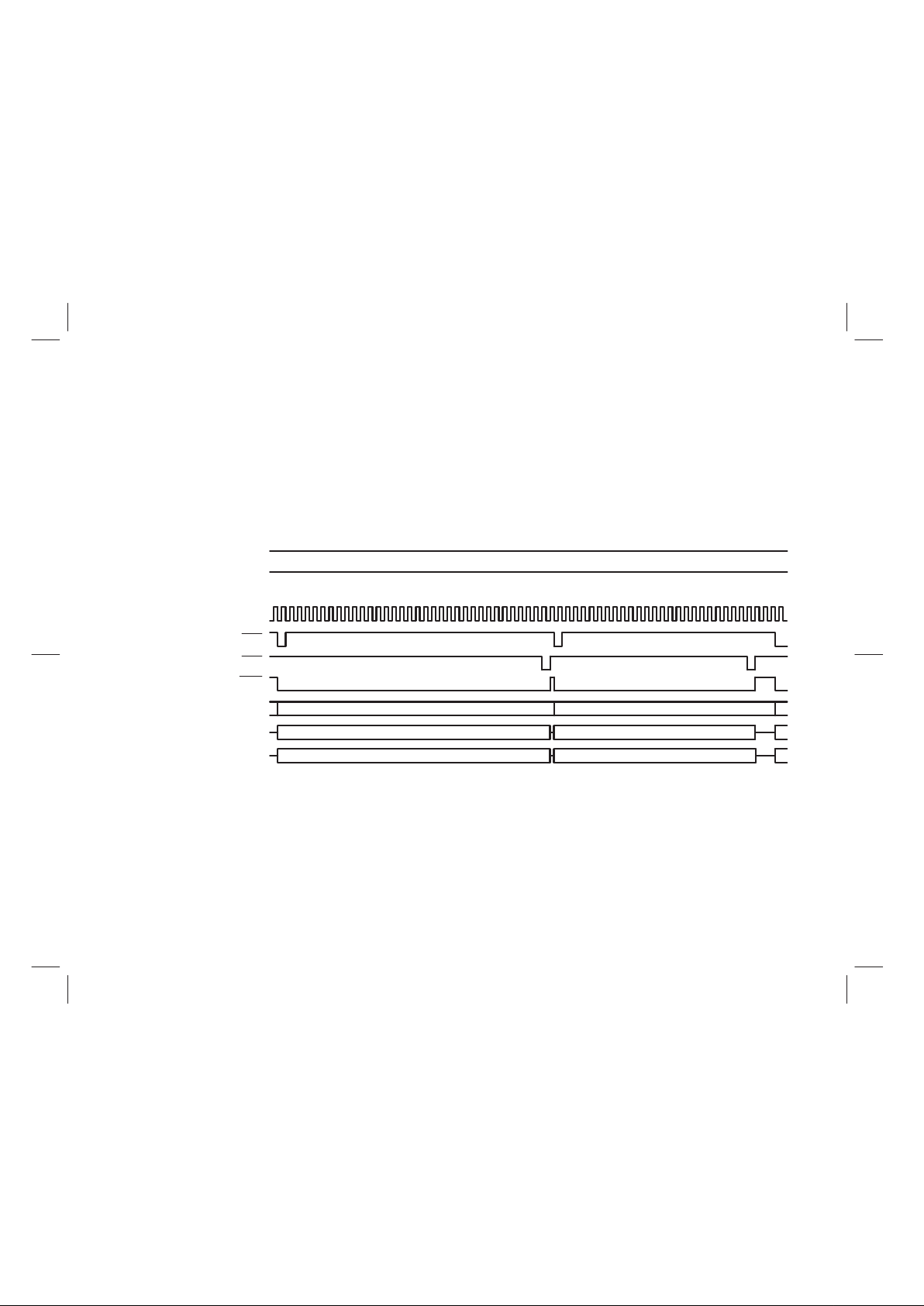

2–7 Microcontroller Byte Stack Operation (Write) 2–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 Microcontroller Byte UnStack Operation (Read) 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–9 Link Core Components 2–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–10 Isochronous DM Flow Control (TSB12LV31 Transmit) 2–12. . . . . . . . . . . . . . . . . . . . . . . .

2–11 Isochronous Transmit Data Path 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Configuration Register (CFR) Map 3–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 TSB12LV31 Controller-FIFO-Access Address Map 4–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Quadlet-Transmit Format 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Block-Transmit Format 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Quadlet-Receive Format 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Block-Receive Format 5–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Isochronous-Transmit Format 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Isochronous-Receive Format 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 Snoop Format 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 CycleMark Format 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Phy Configuration Format 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Receive Self-ID Format 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 Phy Self-ID Packet #0 Format 5–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 Phy Self-ID Packet #1, Packet #2, and Packet #3 Format 5–10. . . . . . . . . . . . . . . . . . . . .

6–1 Microcontroller Write-Operation Timing Waveforms 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Microcontroller Read-Operation Timing Waveforms 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 IsoPort Phase 1 (Four-Byte Preread) Timing Waveforms 6–5. . . . . . . . . . . . . . . . . . . . . . . .

6–4 IsoPort Phase 2 (Data Transmit to End of Packet) Timing Waveforms 6–6. . . . . . . . . . . . .

6–5 IsoPort Phase 3 (End of Block) Timing Waveforms 6–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 IsoPort Receive Timing Waveforms 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–7 Isochronous Receive of One Quadlet at 200 Mbits/s 6–8. . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–8 Isochronous-Receive Four Quadlets with Data Error at 200 Mbits/s 6–9. . . . . . . . . . . . . . .

6–9 Link Read Waveforms 6–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–10 Link Write Waveforms 6–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–11 Synchronous ISOCK Output Waveforms 6–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

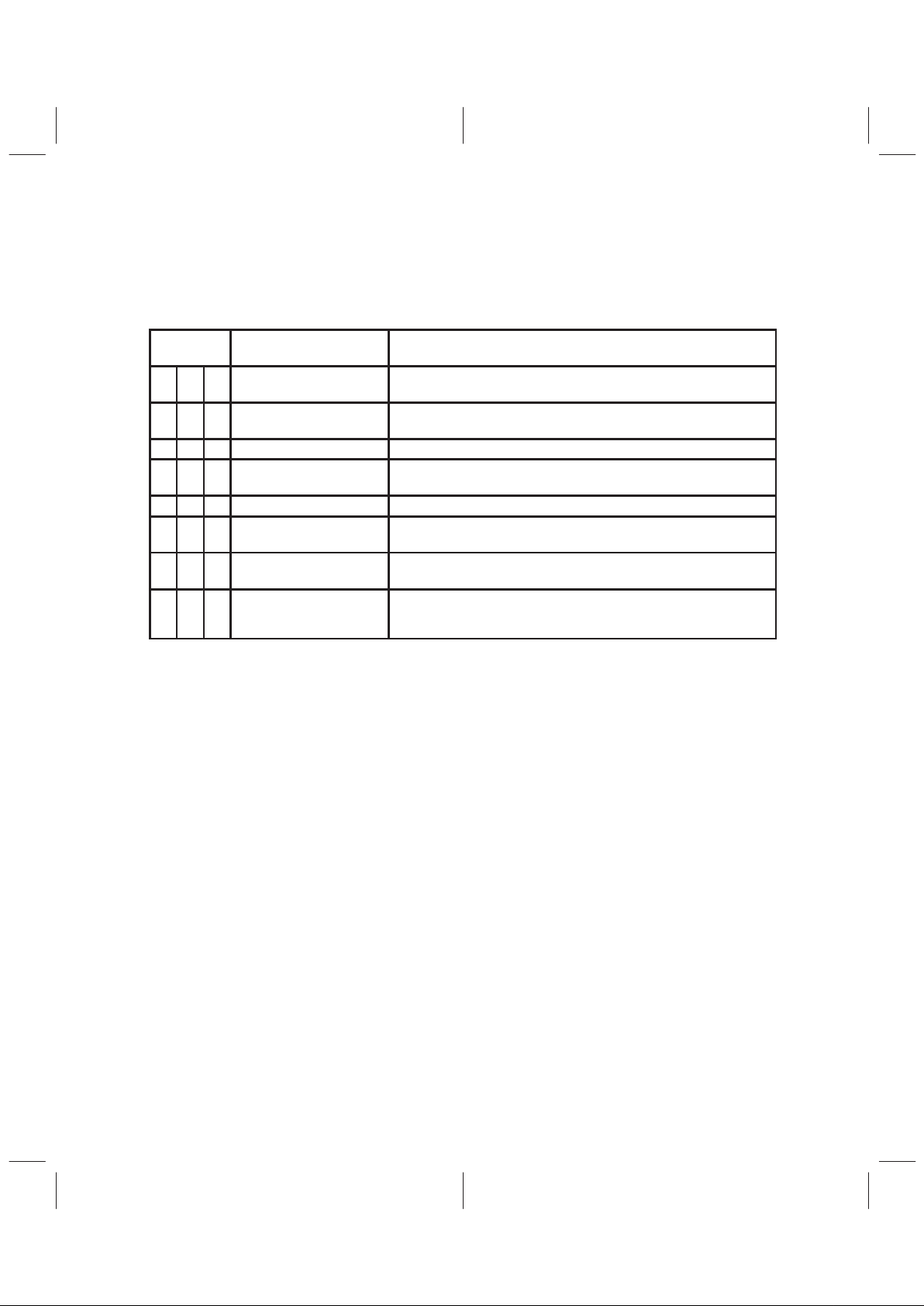

List of Tables

Table Title Page

1–1 Terminal Functions 1–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 STAT0 and STAT1 Programming 1–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 Isochronous Transmit Packet Structure 2–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–1 Memory and Configuration Address Space Map 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–2 MISC Register Field Descriptions @04h 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–3 Control Register Field Descriptions @08h 3–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–4 Interrupt/Interrupt Mask Register Field Descriptions @0Ch/10h 3–5. . . . . . . . . . . . . . . . . .

3–5 Cycle-Timer Register Field Descriptions @14h 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–6 IsoPort Number Register Field Descriptions @18h 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–7 Diagnostics Register Field Descriptions @20h 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–8 Recommended Range for XtendClk 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–9 Phy Access Register @24h 3–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–10 ATF Status Register @30h 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–11 Bus Reset Register @34h 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–12 Self-ID Check Register@38h 3–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–13 GRF Status Register @3Ch 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–14 FIFO State Register @50h 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–15 Isochronous Control Register @54h 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–16 Isochronous Mode Register @58h 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3–17 Isochronous Mode Register@5Ch 3–13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–1 Quadlet-Transmit Format Functions 5–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–2 Block-Transmit Format Functions 5–2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 Quadlet-Receive Format Functions 5–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 Block-Receive Format Functions 5–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 Isochronous-Transmit Functions 5–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 Isochronous-Receive Functions 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 Snoop Functions 5–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 CycleMark Function 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 Phy Configuration Functions 5–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 Receive Self-ID Function 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 GRF Contents With Three Nodes on a Bus 5–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 Phy Self-ID Functions 5–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vii

List of Tables (continued)

Table Title Page

6–1 Microcontroller Write Timing 6–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 Microcontroller Read Timing 6–4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–3 IsoPort Timing Phases 1, 2, and 3 6–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–4 IsoPort Receive Timing 6–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–5 Link Read/Write Timing 6–10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–6 Synchronous ISOCK Output Timing 6–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

viii

1–1

1 Overview

1.1 Description

The TSB12LV31 performs bidirectional asynchronous/isochronous data transfers to and from an IEEE

1394-1995 serial bus physical layer (phy) device. The TSB12LV31 is tailored and optimized for use as a

peripheral

link-layer controller (LLC). TSB12LV31 asynchronous and isochronous operations are

summarized as follows:

TSB12LV31 asynchronous transmit: From asynchronous transmit FIFO (ATF)

TSB12LV31 asynchronous receive: To general receive FIFO (GRF)

TSB12L V31 isochronous transmit: From 8-bit IsoPort

TSB12L V31 isochronous receive: To 8 bit IsoPort,

To GRF, or

To 8-bit IsoPort and T o GRF

This document is not intended to serve as a tutorial on the 1394; users should refer to the IEEE 1394-1995

standard for more detailed information.

1.2 Features

The TSB12LV31 supports the following features:

• Provisions of IEEE 1394-1995 Standard for High-Performance Serial Bus (1394)

†

• Fully Interoperable with FireWire Implementation of 1394

• Compatible with Texas Instruments TSB11LV01 and TSB21LV03 Physical Layer Controllers

(Phys)

• Single 3.3-V supply operation with 5-V Tolerant Capabilities using 5-V Bias Terminals

• High-performance 100-Pin PZ (S–PQFP–G100) package.

• Programmable Microcontroller Interface with 8-Bit or 16-Bit Data Bus, Three Modes of Operation,

and Clock Frequency to 50 Mhz

• 50-quadlet (200-Byte) FIFO Accessed Through Microcontroller Interface Supports

Asynchronous and Isochronous Operations

• Programmable FIFO Size For Asynchronous Transmit FIFO and General-Receive FIFO

• Single-Channel Support for Isochronous Transmit from Unbuffered 8-Bit Isochronous Port

(IsoPort)

• Isochronous Receive to FIFO or to Unbuffered 8-Bit IsoPort

• Isochronous Header Synchronous-Bit Detection on Receive

• Automatically Reports IRM NODE_ID and Verifies Automatic 1394 Self-ID

• Transfer Rates of 100 Mbits/s and 200 Mbits/s

• Asynchronous Packet Reception to Internal FIFO (Accessed Through the Microcontroller

Interface)

• Asynchronous Packet Transmission from Internal FIFO (Accessed Through the Microcontroller

Interface)

• Generation of External Microcontroller Clock from SCLK (SCLK/4)

• Generation of 32-Bit Cyclic Redundancy Check (CRC) for Transmission of 1394 Packets

• 32-Bit CRC Checking on Reception of 1394 Packets

†

Implements technology covered by one or more patents of Apple Computer, Incorporated and SGS Thomson, Limited.

FireWire is a trademark of Apple Computer, Incorporated.

1–2

1.3 Related Documents

The following document is applicable and should be referenced for additional information:

• IEEE STD IEEE 1394-1995 High Performance Serial Bus

1.4 Functional Block Diagram

The functional block diagram of the TSB12LV31 is shown in Figure 2–1.

MA0 – MA7

MD0 – MD15

BCLK

Byte Stacker

8-/16-to-32 bits

8

/

16

/

8

/

32

/

8

/

32

/

Address

Data

FIFO

CFR

Control

ATF

ARF

IRF

Phy/LLC

Interface

Host Interface

Link Core

DM

ISOD0 – ISOD7

Isochronous

Control

8

/

Isochronous

Port (IsoPort)

32

/

ITF

÷ 2

SCLK

÷ 4

MCLK

Microcontroller

Interface

MCA

MCS

Status

Figure 1–1. TSB12LV31 Functional Block Diagram

1–3

1.5 Terminal Assignments

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

MD13

MD12

GND

MD9

MD8

MD7

MD6

MD5

MD4

GND

MD2

MD1

MCLK

BCLK

MA7

MA6

GND

GND

ISOD1

ISOD2

ISOD3

ISOD7

ISOD4

ISOD5

ISOD6

GND

ISORST

ISORW

CONTNDR

IDATARDY

IDMDONE

PKTFLAG

GND

CYCLEIN

CYCLEOUT

RESET

IDMRST

GND

CYDONE

CYSTART

STAT1

STAT0

MARXD

MBUSY

MCMODE1

MCMODE0

MD15

MD14

GND

GND

D3D2D1

D0

CTL1

SCLK

LREQ

NTBIHIZ

NTOUT

NTCLK

MA0

MA1

GND

MA4

MA5

MD11

V

CC

5V

RAMEZ

CC

V

PZ PACKAGE

(TOP VIEW)

ISOD0

ISOCK

MIRXD

MD10

MD3

MD0

CTL0

MA2

V

CC

V

CC

ISOERROR

V

CC

CC

V

GND

CC

V5V

CC

V

MA3

V

CC

V

CC

V

CC

VCC5V

CC

V

CC

V

CC

V

CC

V5V

GND

POWERON

TSB12LV31

INT

MCS

MCA

MWR

Figure 1–2. Terminal Assignments

1–4

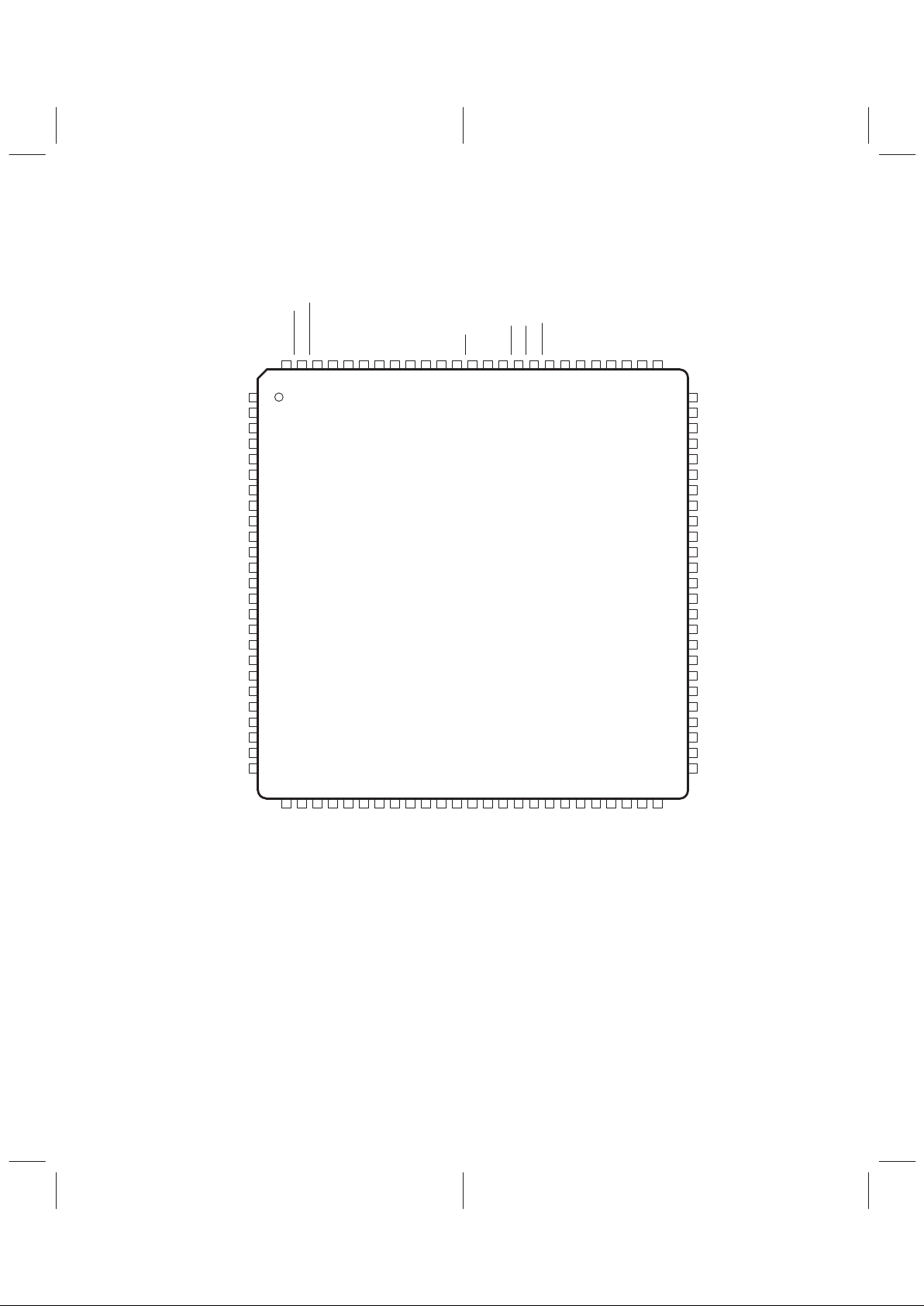

1.6 Terminal Assignments

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

MD13

MD12

GND

MD9

MD8

MD7

MD6

MD5

MD4

GND

MD2

MD1

MCLK

BCLK

MA7

MA6

GND

GND

ISOD1

ISOD2

ISOD3

ISOD7

ISOD4

ISOD5

ISOD6

GND

ISORST

ISORW

CONTNDR

IDATARDY

IDMDONE

PKTFLAG

GND

CYCLEIN

CYCLEOUT

RESET

IDMRST

GND

CYDONE

CYSTART

STAT1

STAT0

MARXD

MBUSY

MCMODE1

MCMODE0

MD15

MD14

GND

GND

D3D2D1

D0

CTL1

SCLK

LREQ

NTBIHIZ

NTOUT

NTCLK

MA0

MA1

GND

MA4

MA5

MD11

V

CC

5V

RAMEZ

CC

V

WN PACKAGE

(TOP VIEW)

ISOD0

ISOCK

MIRXD

MD10

MD3

MD0

CTL0

MA2

V

CC

V

CC

ISOERROR

V

CC

CC

V

GND

CC

V5V

CC

V

MA3

V

CC

V

CC

V

CC

VCC5V

CC

V

CC

V

CC

V

CC

V5V

GND

POWERON

TSB12LV31M

INT

MCS

MCA

MWR

Figure 1–3. Terminal Assignments

1–5

1.7 Terminal Functions

The terminal functions are described in Table 1–1.

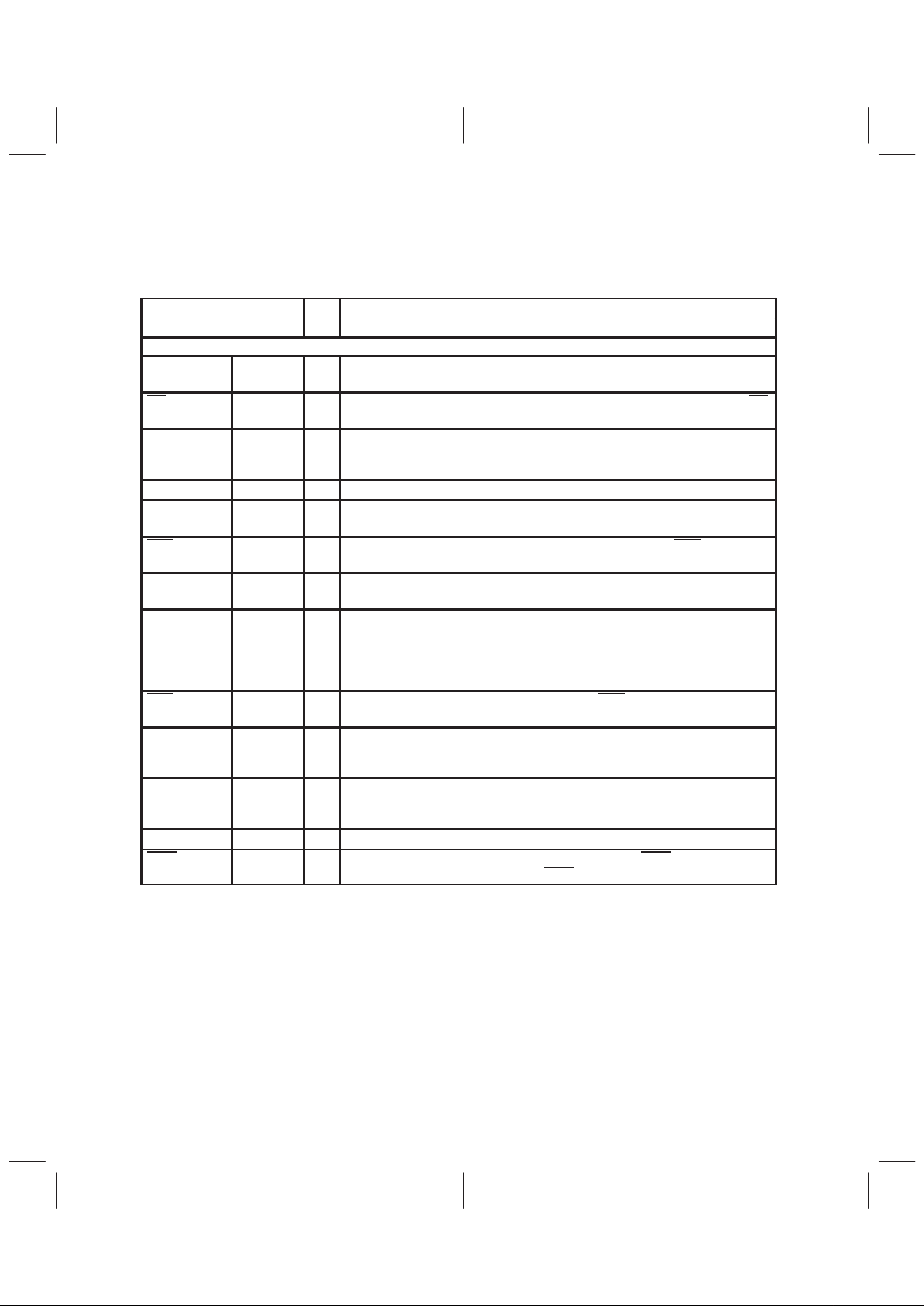

Table 1–1. Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

Microcontroller Interface

BCLK 54 I Microcontroller clock. BCLK is supplied to the TSB12LV31 and has a maximum

speed rating of 50 MHz.

INT 88 O Interrupt from the TSB12LV31 to microcontroller. When asserted low, INT

indicates that an interrupt has occurred.

MA0 – MA7 43 – 45

47 – 49

52 – 53

I Microcontroller address bus. MA0 is the MSB of these 8 bits.

MARXD 89 O Asynchronous packet received indicator. MARXD pulses for one ISOCK cycle.

MBUSY 82 I Microcontroller busy indicator. When MBUSY is asserted high, the TSB12LV31

returns an acknowledge packet with a busy code even when the GRF is not full.

MCA 84 O Microcontroller cycle acknowledge. When asserted low, MCA signals an

acknowledge of the microcontroller cycle from the TSB12L V31.

MCLK 55 O General-purpose clock output. MCLK is equal to SCLK/4, which is 12.288 MHz

nominal.

MCMODE0

MCMODE1

79

80

I Microcontroller mode select:

00: 16-bit data bus (MD0 – MD15), CS/CA handshake mode

01: 16-bit data bus (MD0 – MD15), fixed CS/CA timing

10: 8-bit data bus (MD8 – MD15), CS/CA handshake mode

11: 8-bit data bus (MD8 – MD15), fixed CS/CA timing

MCS 85 I Microcontroller cycle start. When asserted low, MCS signals the microcontroller

cycle start.

MD0 – MD7 57 – 60

63 – 65

67

I/O Microcontroller data bus. MD0 – MD7 are the MSBs of MD. MD0 is the MSB of

these 8 bits.

MD8 – MD15 68 – 70

72 – 74

77 – 78

I/O Microcontroller data bus. MD8 – MD15 are the LSBs of MD. MD8 is the MSB of

these 8 bits.

MIRXD 90 O Isochronous packet received indicator. MIRXD pulses for one ISOCK cycle.

MWR 83 I Microcontroller write/read indicator. When asserted high, MWR indicates a read to

the TSB12LV31. When asserted low, MWR

indicates a write.

1–6

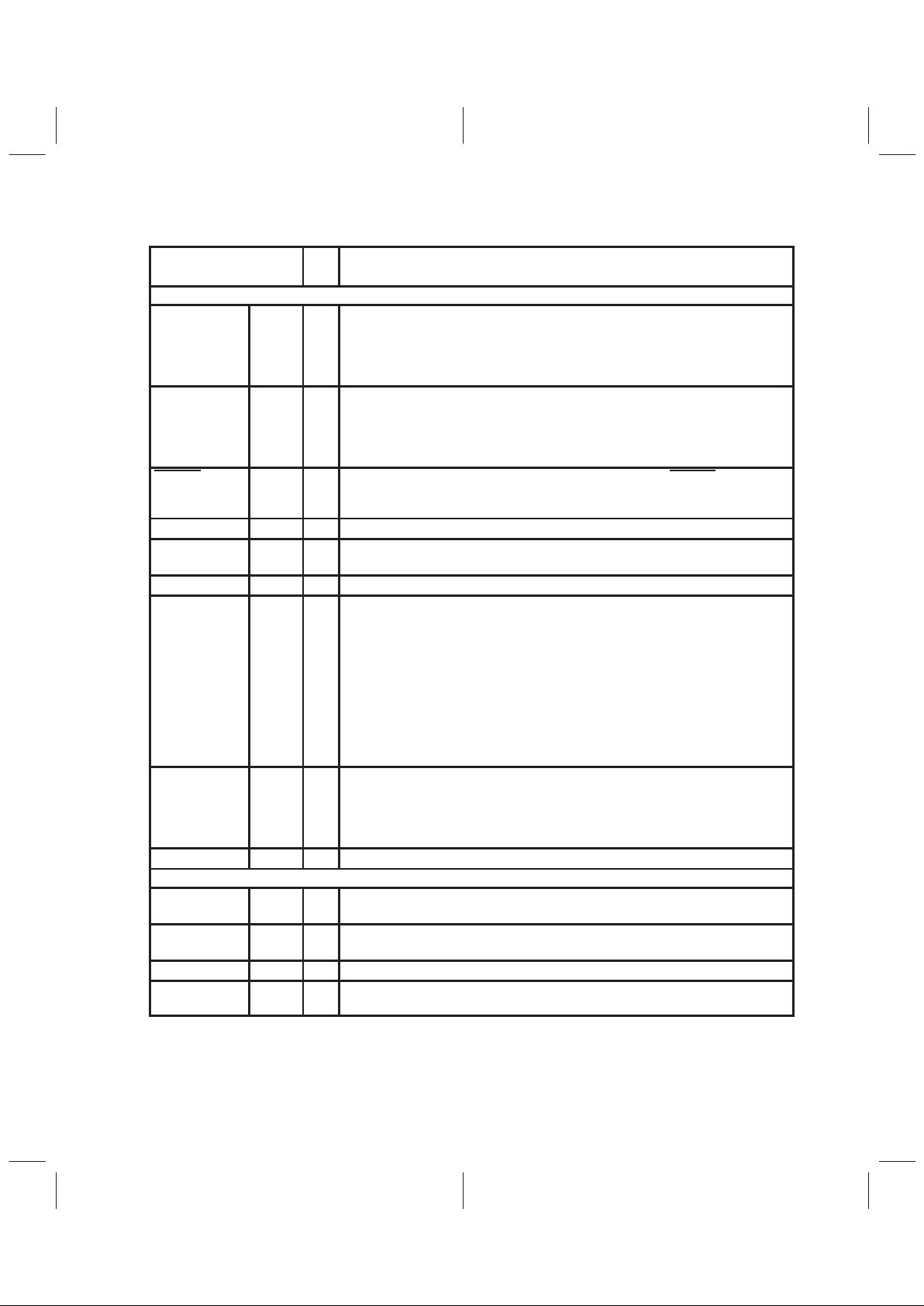

Table 1–1. Terminal Functions (Continued)

TERMINAL

NAME NO.

I/O

DESCRIPTION

IsoPort Interface

IDATARDY 18 I External isochronous data is ready. IDATARDY is a handshaking signal used for

isochronous transmit. When data is ready for transmiting IDATARDY must be

asserted high. IDMDONE is asserted low indicating that the transmitter is ready to

accept data. At the conclusion of the entire block transmit, IDMDONE is asserted high

and IDATARDY is asserted low.

IDMDONE 19 O Isochronous transfer has completed. IDMDONE is a handshaking signal used for

isochronous transmit. When data is ready for transmiting IDATARDY must be

asserted high. IDMDONE is asserted low indicating that the transmitter is ready to

accept data. At the conclusion of the entire block transmit, IDMDONE is asserted high

and IDATARDY is asserted low.

IDMRST 98 I Reset for isochronous DMA state machine, active low. IDMRST is valid for

isochronous transmits only. It performs an immediate abort of any isochronous

transmit activity.

ISOCK 13 O IsoPort clock. Read Clock (25 Mhz)

ISOD0 – ISOD7 2 – 5

7 – 10

I/O IsoPort data. ISOD0 – ISOD carry the IsoPort data. ISOD0 is the MSB.

ISOERROR 22 O Isochronous error. When set, ISOERROR indicates an error in the received packet.

ISORST 14 O Reset IsoPort Read address pointer to zero. The ISORST pulses for one ISOCK clock

period when:

• The transmitting node has one or more synchronous bits set in the Iso Header

register

and

• The corresponding bit is also set in the ISyncRcvN field (see subsection 3.2.6)

of the IsoPort Number register of the receiving mode.

For isochronous transmit, ISORST pulses at the beginning of a new data block fetch

sequence.

ISORW 15 O Enable to increment external IsoPort address pointer. ISORW is valid for both transmit

and receive. For transmit, ISORW goes high indicating that isochronous data is

clocked-in from the IsoPort (ISOD0 – ISOD7) at the ISOCK clock rate. For receive,

ISORW goes high and indicates that data is present on ISOD0 – ISOD7 and must be

clocked out with ISOCK.

PKTFLAG 20 O Packet flag. When set, PKTFLAG indicates the first or last quadlet of a packet

Phy Interface

CTL0

CTL1

3332I/O Control 1 and control 0 of the phy-link control bus. CTL0 is the MSB.

D0 – D3 30 – 27 I/O Data 0–3 of the phy-link data bus. Data is expected on D0 and D1 at 100 Mbits/s and

D0 – D3 at 200 Mbits/s. D0 is the MSB.

LREQ 35 O LLC request to phy. LREQ makes bus requests and accesses the phy.

SCLK 34 I System clock. SCLK is a 49.152-MHz clock from the phy and from which the

24.576-MHz clock is generated.

1–7

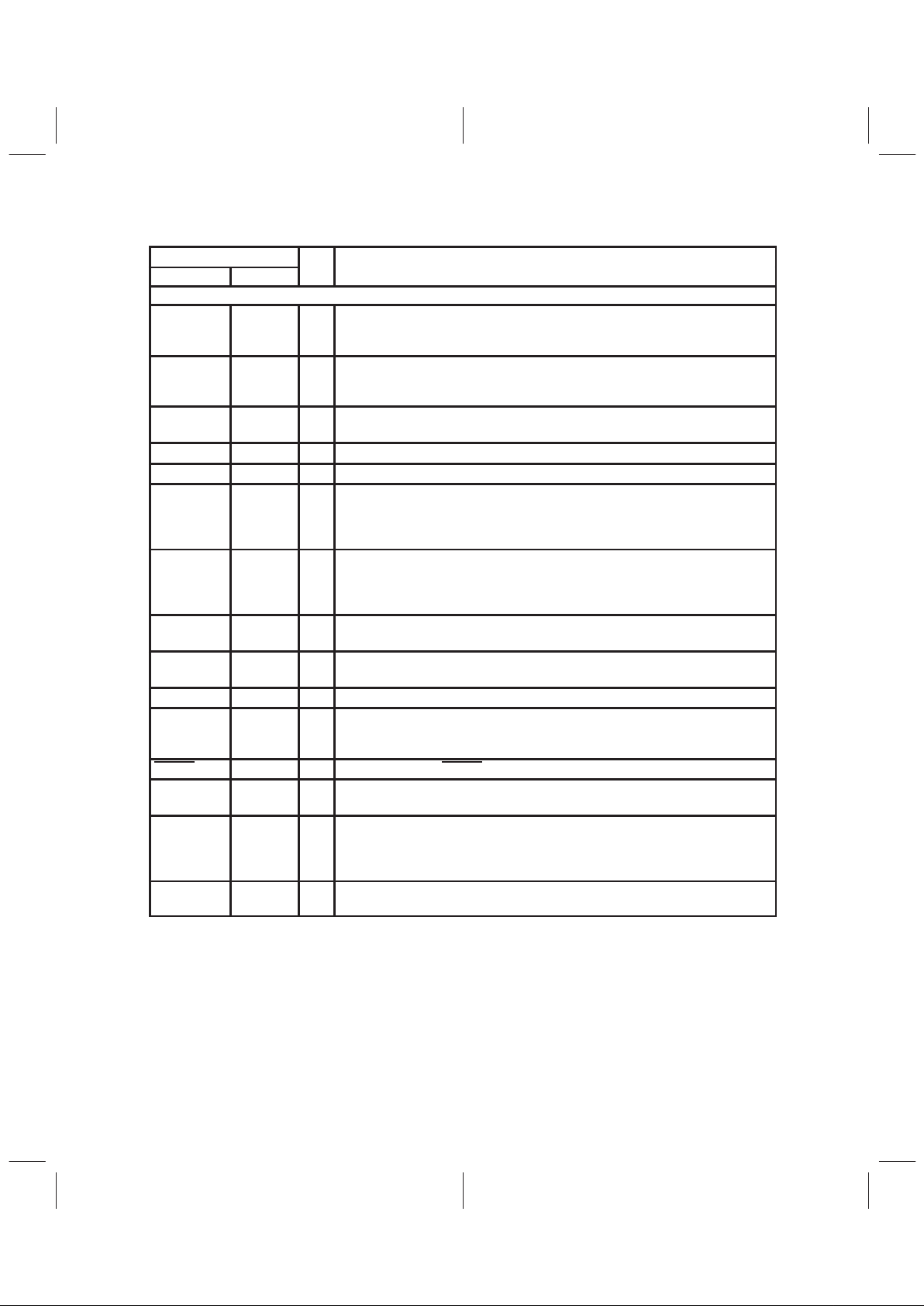

Table 1–1. Terminal Functions (Continued)

TERMINAL

NAME NO.

I/O

DESCRIPTION

Miscellaneous Functions

CONTNDR 17 I Bus contender. When asserted, this node is designated as a contender for

Isochronous Resource Manager or Bus Manager functions. The state of

CONTNDR must match the state of the phy contender terminal.

CYCLEIN 23 I Cycle in. This input is an optional external 8-kHz clock used as the cycle clock, and it

should only be used if attached to the cycle-master node. It is enabled by the cycle

source bit and should be tied high when not used.

CYCLEOUT 24 O Cycle out. This output is the LLC version of the cycle clock. It is based on the timer

controls and received cycle-start messages.

CYDONE 95 O Isochronous cycle done indicator. CYDONE pulses for one ISOCK cycle.

CYSTART 94 O Isochronous cycle start indicator. CYSTART pulses for one ISOCK cycle.

GND 1,11,21

26,36,46

51,61,71

76,86,96

Ground reference

NTBIHIZ 38 I NAND tree bidirectional 3–state output. When NTBIHIZ is low, the bidirectional I/Os

operate in a normal state. When NTBIHIZ is high, the bidirectional I/Os are in the

3–state output mode. This is a manufacturing test mode and should be grounded

under normal operating conditions.

NTCLK 40 I NAND clock input. The NAND-tree clock is used for VIH and VIL manufacturing

tests. This input should be grounded under normal operating conditions.

NTOUT 39 O NAND tree output. This output should remain open under normal operating

conditions.

POWERON 97 O Link power-on indicator (BCLK/32 square wave)

RAMEZ 42 I RAM 3-state enable. When RAMEZ is low, the FIFOs are enabled. When RAMEZ is

high, the FIFOs are 3-state outputs. This is a manufacturing test mode condition

and should be grounded under normal operating conditions.

RESET 99 I Reset (active low). RESET is the asynchronous reset to the LLC.

STAT0

STAT1

92

93

O Status signal. STATn is the output signal selected with the CFR address 20h (see

Table 1–2).

V

CC

6,16,25

31,41,50

56,66,75

81,91,100

3.3-V (±0.3 V) power supplies

VCC5V 12,37,62

87

5.0-V (±0.5-V) power supplies. VCC5V is 3.3 V (±0.3 V) on a 3-V only system.

1–8

1.7.1 STAT0 and STAT1 Programming

STAT0 and STAT1 are programmable output terminals. Each terminal can be independently programmed

to show one of eight possible internal hardware statuses. STAT0 is controlled by StatSel0 (see subsection

3.2.7). STAT1 is controlled by StatSel1 (see subsection 3.2.7).

Table 1–2. STAT0 and STAT1 Programming

StatSel0 or

StatSel1

STAT0/STAT1 DESCRIPTION

0 0 0

GRF full

(default setting for STAT0)

GRF full is set when the value of GRF Remain = 0 (see subsection

3.2.13).

0 0 1 GRF empty

GRF empty is set when the size of the GRF is equal to the value of GRF

Remain (see subsection 3.2.13).

0 1 0 ATF full ATF full is set when the value of A TF Remain = 0 (see subsection 3.2.13).

0 1 1

ATF empty

(default setting for STAT1)

ATF empty is set when the size of the ATF is equal to the value of ATF

Remain (see subsection 3.2.13).

1 0 0 Bus Reset Bus reset is set for one ISOCK cycle when a bus reset is detected.

1 0 1 Arbitration Reset gap

Arbitration reset gap is set for one ISOCK cycle when an arbitration reset

gap is detected.

1 1 0 Subaction gap

Subaction gap is set for one ISOCK cycle when a subaction gap is

detected.

1 1 1

Isochronous transmit

buffer empty

Isochronous transmit buffer empty is set when an entire packet has been

transmitted or, conversely , is low indicating that a packet is in the process

of being transmitted.

2–1

2 Architecture

2.1 Functional Block Diagram

The functional block diagram of the TSB12LV31 is shown in Figure 2–1.

MA0 – MA7

MD0 – MD15

BCLK

Byte Stacker

8-/16-to-32 bits

8

/

16

/

8

/

32

/

8

/

32

/

Address

Data

FIFO

CFR

Control

ATF

ARF

IRF

Phy/LLC

Interface

Host Interface

Link Core

DM

ISOD0 – ISOD7

Isochronous

Control

8

/

Isochronous

Port (IsoPort)

32

/

ITF

÷ 2

SCLK

÷ 4

MCLK

Microcontroller

Interface

MCA

MCS

Status

Figure 2–1. TSB12LV31 Functional Block Diagram

2.1.1 FIFO

The internal physical FIFO can be partitioned into two logical FIFOs. Each FIFO is programmable in size

from 0 to 50 quadlets. For a given combination of FIFO sizes, the sum total of the two FIFO sizes must be

less than or equal to 50 quadlets.

2.1.2 Microcontroller Interface

All microcontroller reads/writes are initiated by the microcontroller. Microcontroller modes of operation are

shown in Figure 2–2, Figure 2–4, and Figure 2–5. Microcontroller operational protocol is described in

Figure 2–7 and Figure 2–8. Microcontroller write/read timing is shown in Figure 4–1 and Figure 4–3.

2.1.2.1 Byte Stacker/Host Interface

The byte stacker allows the TSB12LV31 to be easily connected to most host processors. The byte stacker

consists of a programmable 8-/16-bit data bus and an 8-bit address bus. The TSB12LV31 uses cycle-start

and cycle-acknowledge handshake signals to allow the local bus clock and the 1394 clock to be

asynchronous to one another. The TSB12LV31 is interrupt driven to reduce polling.

2–2

2.1.2.2 Microcontroller Handshake Mode

Figure 2–2 shows a typical handshake sequence in doublet (16-bit) mode for a read followed by a write. In

this example, the quadlet value A0 00 00 00h is being read from the configuration register 0Ch followed

immediately by a write to the same register with the value 20 00 00 00h. Also see Figure 6–1 and

Figure 6–2.

The handshake mode timing sequence is as follows:

1. The host takes MCS

low to signal start of access.

2. The TSB12LV31 takes MCA

low to signal that the requested operation is complete.

3. The host takes MCS high to signal the end of the access.

4. The TSB12LV31 takes MCA

high to acknowledge the end of the access.

BCLK

MCS

MCA

MWR

MA0– MA7

MD0 – MD7

0C0E0C 0E

A0

2000

00

MD8 – MD15

00

0000

00

MCMODE0

MCMODE1

NOTE A: MCMODE0 = 0, MCMODE1 = 0 handshake read/write

Figure 2–2. Typical Handshake Doublet-Mode Timing Waveforms

2–3

Figure 2–3 shows a typical handshake sequence in byte (8-bit) mode for a write operation. In this example,

the quadlet value 00 00 10 04h is being written to the configuration register 54h. Note that the most significant

byte of the data bus, MD0 – MD7, is not used in this mode. Also see Figure 6–1 and Figure 6–2.

BCLK

MCS

MCA

MWR

MA0– MA7

MD0 – MD7

5554 56

MD8 – MD15

00

1000

04

57

MCMODE0

MCMODE1

DON’T CARE

NOTE A: MCMODE0 = 1, MCMODE1 = 0 handshake byte write

Figure 2–3. Typical Handshake Byte-Mode Timing Waveforms

2.1.2.3 Microcontroller Pulse Mode

Figure 2–4 shows typical timing in pulse mode. The pulse-mode timing sequence is as follows:

1. The host pulses MCS

low for one clock cycle to signal the start of the access.

2. After n clocks, the TSB12LV31 pulses MCA

low for one clock cycle to signal that the requested

operation is complete.

BCLK

MCS

MCA

n clocks

(See Note A)

50% 50%

NOTE A: In this figure, n clocks is determined by clock synchronization and by which byte of the quadlet is being

addressed.

Figure 2–4. Pulse Mode Timing Waveforms

2–4

2.1.2.4 Microcontroller 16-Bit Pulse Mode with Fixed Timing

Figure 2–5 shows a pulse with a fixed timing sequence in doublet (16-bit) mode for a write operation with

XtendClk set to 0. In this example, the quadlet value 00 0C 13 1Ch is being written to the configuration

register 5Ch. Also see Figure 6–1 and Figure 6–2.

The timing sequence for pulse mode with fixed timing is as follows:

1. The host pulses MCS low for one clock cycle to signal the start of the access

2. After n clocks, the TSB12LV31 pulses MCA

low for one clock cycle to signal the requested

operation is complete.

2–5

MCMODE0

MCMODE1

BCLK

MCS

MCA

MWR

MA0 – MA7

MD0 – MD7

MD8 – MD15

5C 5E

00 13

0C 1C

Figure 2–5. Timing Waveforms for 16-Bit Pulse Mode with Fixed Timing

Figure 2–5. Timing Waveforms for 16-Bit Pulse Mode with Fixed Timing

2–6

2.1.2.5 Microcontroller 8-Bit Pulse Mode with Fixed Timing

Figure 2–6 shows a pulse with a fixed timing sequence in byte (8-bit) mode for a write operation with

XtendClk set to 11h. In this example, the quadlet value 00 00 08 02h is being written to the configuration

register 54h. Note that MD0 – MD7 is not used in this mode (see Figure 6–1 and Figure 6–2).

Loading...

Loading...