54AC16822, 54ACT16822

74AC16822, 74ACT16822

20-BIT D-TYPE FLIP-FLOPS WITH 3-STATE OUTPUTS

SCAS402 – JUNE 1990

• Members of Texas Instruments Widebus

Family

• Packaged in Shrink Small-Outline 300-mil

Packages (SSOP) and 380-mil Fine-Pitch

Ceramic Flat Packages Using 25-mil

Center-to-Center Pin Spacings

• Inputs are TTL- or CMOS-Voltage

Compatible

• 3-State Outputs Drive Bus Lines Directly

• Flow-Through Architecture Optimizes PCB

Layout

• Distributed V

and GND Pin Configuration

CC

Minimizes High-Speed Switching Noise

• EPIC (Enhanced-Performance Implanted

CMOS) 1-µm Process

• 500-mA Typical Latch-Up Immunity at

125°C

description

The ’AC16822 and ’ACT16822 are inverting 20-bit

D-type flip-flops composed of two 10-bit sections

with separate control signals. For either 10-bit

flip-flop section, the inverse of the data present at

the corresponding D inputs is stored in the

flip-flops on the rising edge of the clock input

(1CLK or 2CLK) and appears on the appropriate

Q outputs if the output enable 1OE

If 1OE

(or 2OE) is high, the outputs are in the

high-impedance state. 1OE

affect the operation of the flip-flops. Previously

stored data can be retained or new data can be

entered while the outputs are in the

high-impedance state.

FUNCTION TABLE, EACH SECTION

INPUTS

CLK OE

↑ H Current D Data Z

L H Previous D Data Z

↑ L Current D Data Inverse of Current D Data

L L Previous D Data Inverse of Previous D Data

FLIP-FLOP DATA Q OUTPUTS

(or 2OE) is low.

(or 2OE) does not

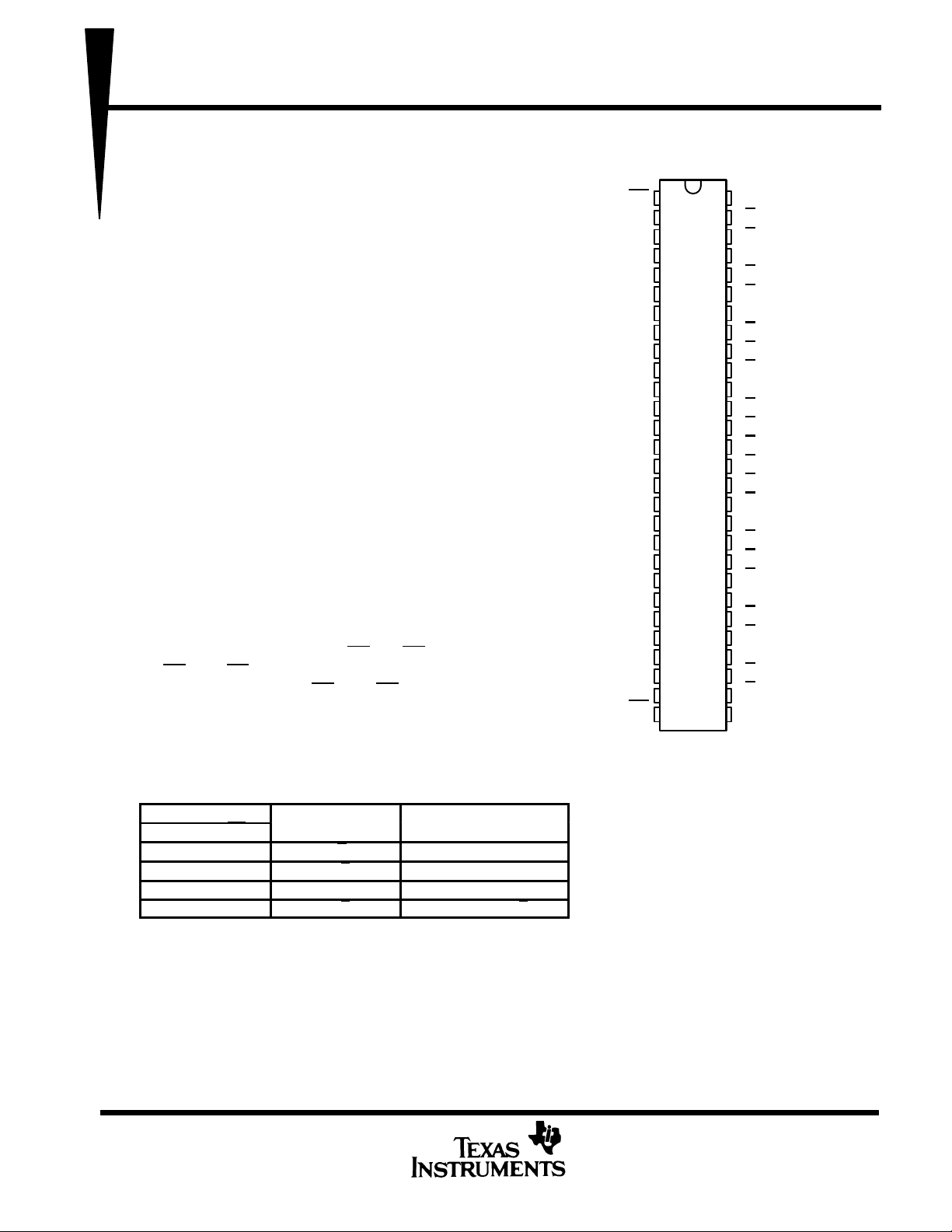

6822, 74ACT16822 . . . DL PACKAGE

6822, 54ACT16822 . . . WD PACKAGE

(T0P VIEW)

1OE

1

56

1Q1

1Q2

GND

GND

1Q10

GND

GND

2Q10

1Q3

1Q4

V

CC

1Q5

1Q6

1Q7

1Q8

1Q9

2Q1

2Q2

2Q3

2Q4

2Q5

2Q6

V

CC

2Q7

2Q8

2Q9

2OE

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

1CLK

1D

1

1D

2

GND

1D

3

1D

4

V

CC

1D5

1D

6

1D

7

GND

1D

8

1D

9

1D

10

2D

1

2D2

2D

3

GND

2D

4

2D

5

2D

6

V

CC

2D7

2D

8

GND

2D

9

2D

10

2CLK

PRODUCT PREVIEW

EPIC and Widebus are trademarks of Texas Instruments

Incorporated.

PRODUCT PREVIEW information concerns products in

the formative or design phase of development.

Characteristic data and other specifications are design

goals. Texas Instruments reserves the right to change or

discontinue these products without notice.

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Copyright 1990, Texas Instruments Incorporated

1

54AC16822, 54ACT16822

74AC16822, 74ACT16822

20-BIT D-TYPE FLIP-FLOPS WITH 3-STATE OUTPUTS

The 74AC16822 and 74ACT16822 are packaged in TI’s shrink small-outline package (SSOP) with 25-mil

center-to-center pin spacings. This package provides twice the I/O pin count and functionality of a standard

small-outline package in the same printed-circuit-board area.

The ’AC16822 has CMOS-compatible input thresholds. The ’ACT16822 has TTL-compatible input thresholds.

The 54AC16822 and 54ACT16822 are characterized over the full military temperature range of –55°C to 125°C.

The 74AC16822 and 74ACT16822 are characterized for operation from –40°C to 85°C.

logic diagram (positive logic)

PRODUCT PREVIEW

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

IMPORTANT NOTICE

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor

product or service without notice, and advises its customers to obtain the latest version of relevant information

to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at

the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are

utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each

device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or

severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED

TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER

CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI

products in such applications requires the written approval of an appropriate TI officer . Questions concerning

potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer’s applications, adequate design and operating

safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or

infringement of patents or services described herein. Nor does TI warrant or represent that any license, either

express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property

right of TI covering or relating to any combination, machine, or process in which such semiconductor products

or services might be or are used.

Copyright 1996, Texas Instruments Incorporated

Loading...

Loading...