Page 1

User Manual

VX4244

16-Channel Digitizer Module

070-9067-06

This document supports firmware version X.XX

and above.

Warning

The servicing instructions are for use by qualified

personnel only. To avoid personal injury, do not

perform any servicing unless you are qualified to

do so. Refer to the Safety Summary prior to

performing service.

Page 2

Copyright T ektronix, Inc. 1994. All rights reserved. Licensed software products are owned by Tektronix or its suppliers

and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the

Rights in T echnical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the

Commercial Computer Software – Restricted Rights clause at F AR 52.227-19, as applicable.

T ektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes

that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

T ektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070–1000

TEKTRONIX and TEK are registered trademarks of T ektronix, Inc.

Page 3

WARRANTY

T ektronix warrants that this product will be free from defects in materials and workmanship for a period of three (3) years

from the date of shipment. If any such product proves defective during this warranty period, T ektronix, at its option, either

will repair the defective product without charge for parts and labor, or will provide a replacement in exchange for the

defective product.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the

warranty period and make suitable arrangements for the performance of service. Customer shall be responsible for

packaging and shipping the defective product to the service center designated by T ektronix, with shipping charges prepaid.

T ektronix shall pay for the return of the product to Customer if the shipment is to a location within the country in which the

T ektronix service center is located. Customer shall be responsible for paying all shipping charges, duties, taxes, and any

other charges for products returned to any other locations.

This warranty shall not apply to any defect, failure or damage caused by improper use or improper or inadequate

maintenance and care. T ektronix shall not be obligated to furnish service under this warranty a) to repair damage resulting

from attempts by personnel other than T ektronix representatives to install, repair or service the product; b) to repair

damage resulting from improper use or connection to incompatible equipment; or c) to service a product that has been

modified or integrated with other products when the effect of such modification or integration increases the time or

difficulty of servicing the product.

THIS WARRANTY IS GIVEN BY TEKTRONIX WITH RESPECT TO THIS PRODUCT IN LIEU OF ANY

OTHER WARRANTIES, EXPRESSED OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY

IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

TEKTRONIX’ RESPONSIBILITY TO REPAIR OR REPLACE DEFECTIVE PRODUCTS IS THE SOLE AND

EXCLUSIVE REMEDY PROVIDED TO THE CUST OMER FOR BREACH OF THIS WARRANTY. TEKTRONIX

AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT , SPECIAL, INCIDENTAL, OR

CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS

ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Page 4

Table of Contents

Getting Started

Operating Basics

General Safety Summary iii. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Service Safety Summary vii. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Preface ix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Getting Started 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Product Description 1–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Accessories 1–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Controls and Indicators 1–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Configuration 1–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installation 1–9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Installation Checklist 1–11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Check 1–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Basics 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power-on 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Front-Panel Indicators 2–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Instrument I/O – VXIbus Basics 2–3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Syntax and Commands

Appendices

Glossary and Index

Command Syntax 3–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Command Groups 3–5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Command Descriptions 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IEEE 488.2 Common Commands 3–51. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix A: Specifications A–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix B: Input/Output Connections B–1. . . . . . . . . . . . . . . . . . . . . . . .

Appendix C: Self Test Failures C–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix D: Module Diagnostic Commands D–1. . . . . . . . . . . . . . . . . . . .

Appendix E: Examples E–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Appendix F: Performance Verification Tests F–1. . . . . . . . . . . . . . . . . . . .

Appendix H: User Service G–1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VX4244 16-Channel Digitizer Module User Manual

i

Page 5

General Safety Summary

Review the following safety precautions to avoid injury and prevent damage to

this product or any products connected to it.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read

the General Safety Summary in other system manuals for warnings and cautions

related to operating the system.

Injury Precautions

Avoid Electric Overload

Ground the Product

Do Not Operate Without

Covers

Use Proper Fuse

Do Not Operate in

Wet/Damp Conditions

Do Not Operate in an

Explosive Atmosphere

To avoid electric shock or fire hazard, do not apply a voltage to a terminal that is

outside the range specified for that terminal.

This product is indirectly grounded through the grounding conductor of the

mainframe power cord. To avoid electric shock, the grounding conductor must

be connected to earth ground. Before making connections to the input or output

terminals of the product, ensure that the product is properly grounded.

To avoid electric shock or fire hazard, do not operate this product with covers or

panels removed.

To avoid fire hazard, use only the fuse type and rating specified for this product.

To avoid electric shock, do not operate this product in wet or damp conditions.

To avoid injury or fire hazard, do not operate this product in an explosive

atmosphere.

Product Damage Precautions

Provide Proper Ventilation

Do Not Operate With

Suspected Failures

VX4244 16-Channel Digitizer Module User Manual

To prevent product overheating, provide proper ventilation.

If you suspect there is damage to this product, have it inspected by qualified

service personnel.

iii

Page 6

General Safety Summary

Safety Terms and Symbols

Terms in This Manual

Terms on the Product

These terms may appear in this manual:

WARNING. Warning statements identify conditions or practices that could result

in injury or loss of life.

CAUTION. Caution statements identify conditions or practices that could result in

damage to this product or other property.

These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the

marking.

WARNING indicates an injury hazard not immediately accessible as you read the

marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product

The following symbols may appear on the product:

DANGER

High Voltage

Protective Ground

(Earth) T erminal

ATTENTION

Refer to Manual

Double

Insulated

iv

VX4244 16-Channel Digitizer Module User Manual

Page 7

Certifications and Compliances

General Safety Summary

Overvoltage Category

Overvoltage categories are defined as follows:

CAT III: Distribution level mains, fixed installation

CAT II: Local level mains, appliances, portable equipment

CAT I: Signal level, special equipment or parts of equipment, telecommunica-

tion, electronics

VX4244 16-Channel Digitizer Module User Manual

v

Page 8

Service Safety Summary

Only qualified personnel should perform service procedures. Read this Service

Safety Summary and the General Safety Summary before performing any service

procedures.

Do Not Service Alone

Use Care When Servicing

With Power On

Do not perform internal service or adjustments of this product unless another

person capable of rendering first aid and resuscitation is present.

Dangerous voltages or currents may exist in this product. Disconnect power,

remove battery (if applicable), and disconnect test leads before removing

protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

VX4244 16-Channel Digitizer Module User Manual

vii

Page 9

Preface

Conventions

This is the user manual for the VX4244 16-Channel Digitizer Module.

Please read and follow all instructions for installation and configuration. Use the

Installation Checklist to insure proper installation, and as a record of initial

settings.

This manual assumes you are familiar with VXIbus instruments and operation,

and with the purpose and function of this instrument. The Operating Basics

section gives a summary of VXIbus operation, and presents an overview of this

instrument’s operation.

The Syntax and Commands section has a summary of all the commands, and

detailed descriptions of each command.

The names of all switches, controls, and indicators appear in this manual exactly

as they appear on the instrument.

Specific conventions for programming are given in the section Syntax and

Commands and in Appendix E: Examples.

VX4244 16-Channel Digitizer Module User Manual

ix

Page 10

Getting Started

Product Description

This section begins with a brief description of the VX4244, and then explains

how to configure and install the module in a VXIbus mainframe. Then you can

choose to perform the quick functional check, also included in this section, to

gain confidence that the instrument operates properly.

The VX4244 16-Channel Digitizer Module is a printed circuit board assembly

for use in a mainframe conforming to the VXIbus Specification. The VX4244

supplies sixteen channels of 16-bit differential input, analog-to-digital conversion data, sampling at up to 200 kHz. The sixteen analog inputs are organized as

four groups of four channels each. Each group can operate independently, or in

concert with any or all of the other groups. For example, one group could be

actively acquiring data, while the second group is waiting for a trigger, the third

group transferring data, and the fourth group is being post-processed. Programmable features of each channel group include the sampling frequency, arming,

triggering, acquisition control (pre-/center-/post-triggering), and the number of

active channels in the group. In addition, each channel’s input range is independently programmable.

Triggering

Time-tag

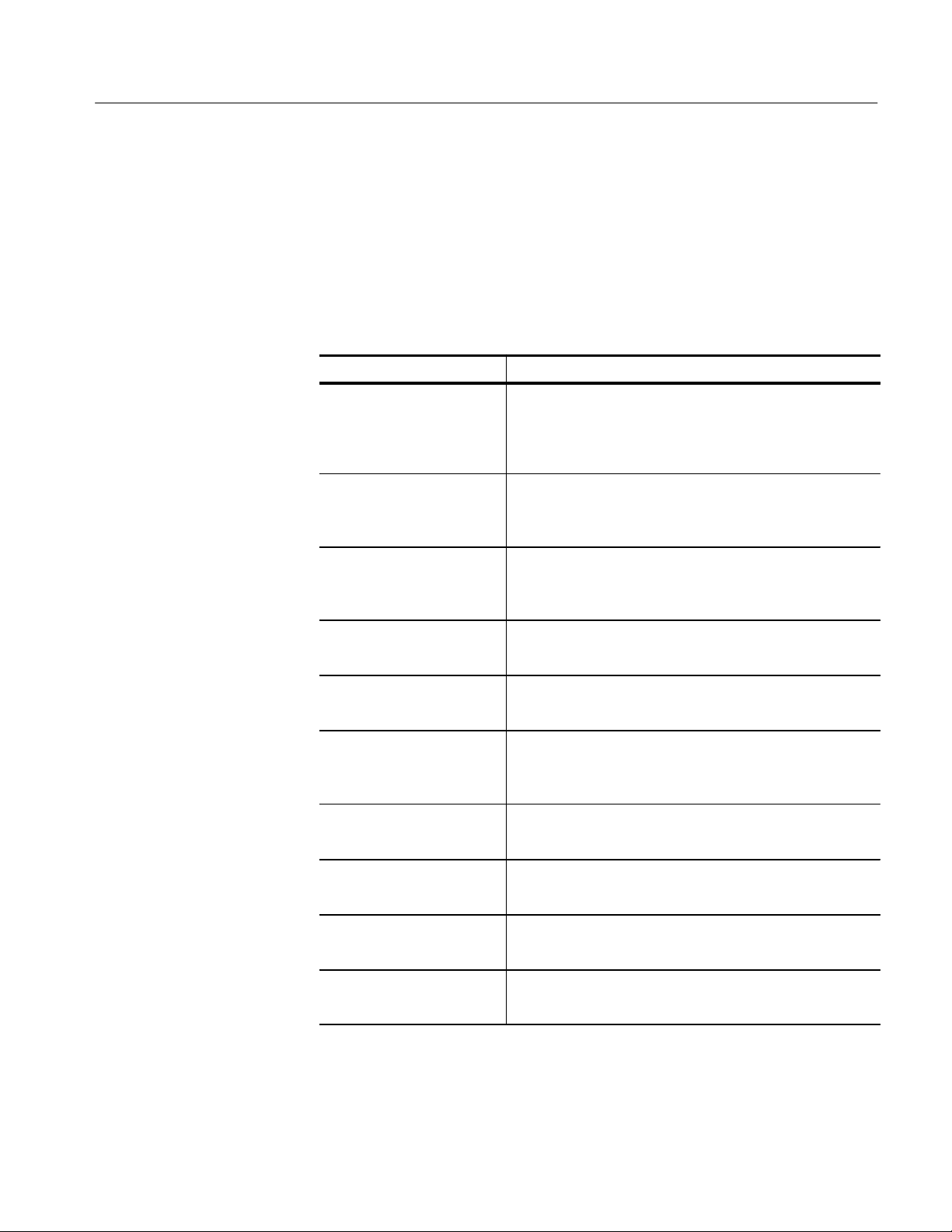

Refer to Figure 1–1 for a functional block diagram of the VX4244.

The VX4244 provides extensive triggering control. The trigger inputs for each

channel group include the eight VXI TTL triggers, an external trigger input, an

internal (software) trigger, the VXI command trigger, and a four-quadrant

threshold/ slope trigger. Any or all of these twelve conditions can be logically

ANDed or ORed to generate the group trigger (except for the VXI command and

software triggers, which are mutually exclusive). In addition, each of the four

group triggers is fed to a master trigger logic circuit, which allows the four group

triggers to be logically ANDed or ORed to generate a master trigger output. The

master trigger out can also be programmed to strobe any of the eight VXI TTL

triggers.

A 32-bit time-tag counter is provided for each channel group. The input to the

time-tag can be either the VXI 10 MHz ECL clock (100 ns resolution), or the

master sampling clock. The time-tag clocks are free-running until the channel

group is triggered (at which time the counters are inhibited from counting). The

SYNC signal described below can be used to reset the time-tag counters.

VX4244 16-Channel Digitizer Module User Manual

1–1

Page 11

Getting Started

1 of 4 Analog

Front End

Channel Group

Memory

Master Clock

32–Bit Counter

/32

Read

GRP 1 32-BIT Register

Time

GRP 2 32-BIT Register

GRP 3 32-BIT Register

Tag

/32

GRP 4 32-BIT Register

Time Tag Circuitry

Cross Switch

Select 1, 2 or

4 Channels

A/D Front

End

Armed/Triggered

LED’S

POWER

FAIL

ACCESS

ERROR

MSB

LSB

Select LED

Display Group

ARMED

TRIG

MIP

MC

Development Board Interface

VXI

10MHz

Not Triggered = Enabled

Trigger 1–4

Clear

Time Tag

Enables

Group

1–4

Status

Development

Board Interface

External

Sync In

TTL Trig

Sync

1

2

3

4

VXI (FDC) Ram Interface

Serial/Parallel

Serial/Parallel

Serial/Parallel

Serial/Parallel

Control

XC3042

Memory

Arbitration

& Control

FDC

DMA

Req

CPU

Sync

Sync Out

Master Clock Out

External Clock In

Sample

Clocks

Data Bus /16

Address Bus

Control

FDC Transfer Request (to 66901)

CPU

68330

/16

CPU Address/Data Bus

4MHz

Clock Sync

Clear

Master Clock

Clear

Clock 1

Clock 2

Clock 3

Clock 4

64K X 16

SRAM

/16/16

/16

CPU Data Bus

VXI

10MHz

Divide by 1 to 65280

Divide by 2

30.6362Hz - 2.0MHz

76.5931Hz - 5.0MHz

Grp 1

Divide by

1/65280

Ext

Grp 2

Divide by

1/65280

Ext

64K X 16

SRAM

CPU RAM Interface

RAM

128K

X 16

FDC Requests

FDC Requests

from Front-End’s

from Front-End’s

Ext

64K X 16

68901 Interrupt

Control

Clock Circuitry

Grp 3

Divide by

1/65280

SRAM

ROM

64K

X 16

Divide by

1/65280

Ext

64K X 16

SRAM

Threshold Comparator

(8 bit)

P P>Q

Flash

ROM

256K

X 16

To CPU

Int 5

Int 4

ASIC Interrupts

Write FIFO Empty

Read FIFO Full

Programmable (ASIC Int 1)

Programmable (ASIC Int 2)

Grp 4

31..16

15..0

Q

SYSD

31..16

SYSD

15..0

Figure 1–1: VX4244 Block Diagram

1–2

VX4244 16-Channel Digitizer Module User Manual

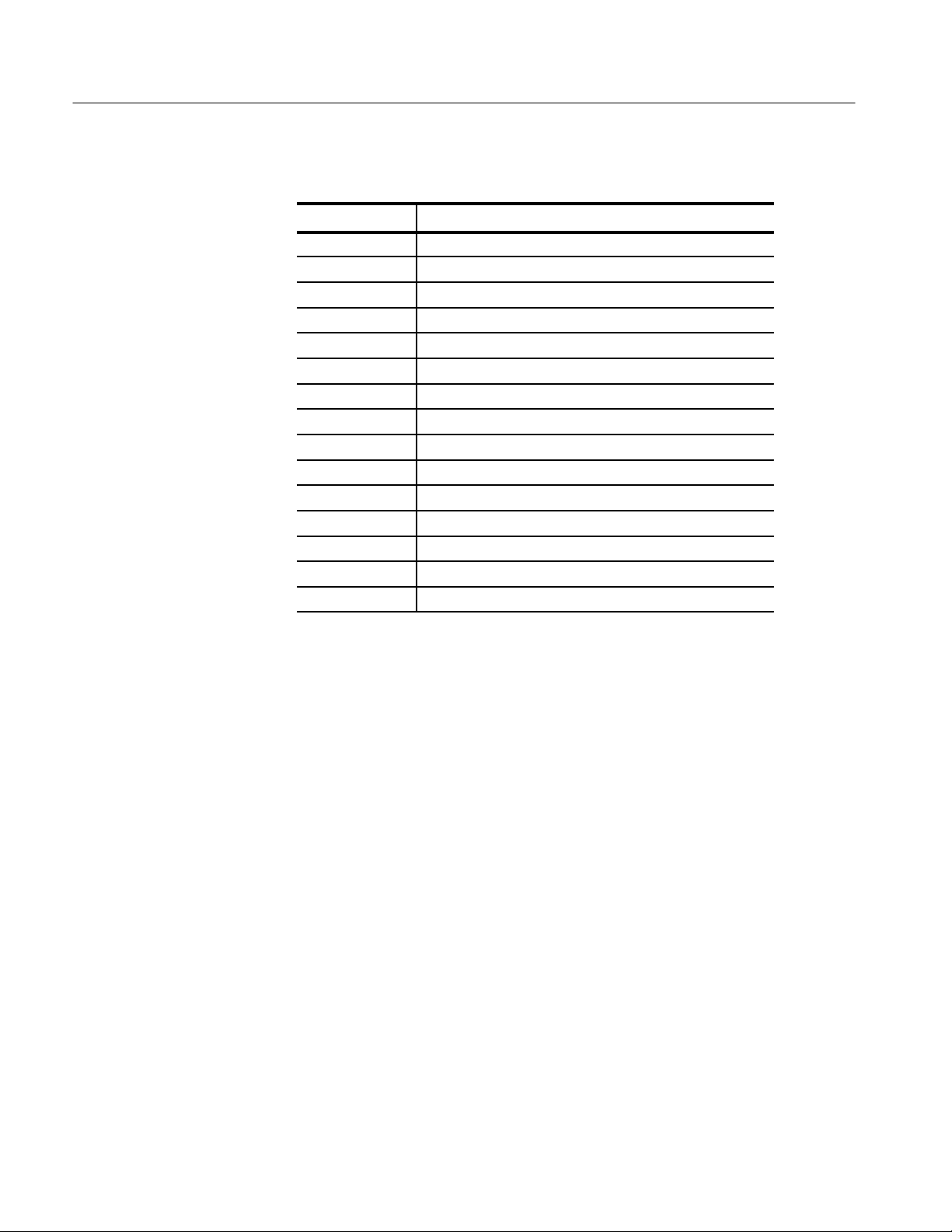

Page 12

SYSD 31..16

SYSD 15..0

VXI Interface

Sys Data Bus

Word

Long Word

High/Low Word

Getting Started

VME D31-16

VME D15-0

ASIC Interrupts

Write FIFO Empty

Read FIFO Full

Programmable (ASIC Int 1)

Programmable (ASIC Int 2)

I/O Group

Select

Clock 1

Clock 2

Clock 3

Clock 4

Sample

Clock Out

Group Select

1 of 4

Channel

FDC (DMA)

Requests

(0-3)

FDC

Chan

4/5

Trigger Circuitry

Group Select

1 of 4

Trigger Out

Master Trigger Out

64K X 16

SRAM

AND/OR

One

Shot

Address

Decode

Sys Addr Bus

SAD Bus

System Interface

Trigger 1

Trigger 2

Trigger 3

Trigger 4

21 US Nominal

Low Pulse

MUX’d

Address/Data

ASIC

ADG294

Interface

Threshold Detect

(Quadrant Slope)

Group 1

AND/OR

Group 2

AND/OR

Group 3

AND/OR

Group 3

AND/OR

TTL Trig Sync

VXI

XC3042

Trigger

Control

SAD 15-0

VME

A31-16

Enable

Enable

VME

Interrupts

External Trigger In

VXI CMD Trigger

CPU Trigger

VXI TTL Triggers 7..0

Select

1 of 8

Select

1 of 7

VXI TTL

Triggers

VX4244 16-Channel Digitizer Module User Manual

1–3

Page 13

Getting Started

Synchronization

Sampling

Data Collection

A SYNC function is provided for synchronizing multiple digitizers. This

function can be programmed to use any of seven (1 through 7) VXI TTL trigger

inputs (if enabled), a software command, or an external sync input. The SYNC

input is the logical OR of these conditions. The SYNC signal is global to all

channel groups, and resets all frequency generation counters on the module. In

addition, the SYNC signal is used to reset the time-tag counters. A front panel

SYNC OUT signal is provided which is the logical OR of the three conditions

described above.

The module uses a two-stage clock scheme. The first stage is the master

(reference) clock. Its source can be programmed to be either internal (4 MHz) or

the VXI 10 MHz ECL clock. This clock is divided by two, then fed to a 16-bit

divider to generate the master clock. The master clock is then fed to each of the

four channel groups, which employ an additional 16-bit divider to generate the

actual sampling clock for the group. In addition, each group can be programmed

to use the EXTERNAL CLOCK input signal from the front panel.

Pre-/center-/post-triggering is programmable for each channel group. In addition,

Fast Data Channel (FDC) requests can be generated at programmable sample

counts. This programmability allows data to be transferred from a group at the

same time data is being acquired.

Configuration

Inputs

DSP

The number of channels active within each group is programmable. Any one of

the four channels may be enabled, or any two of the four channels, or all four

channels can be enabled. A total of 256 Kwords of memory is available to each

channel group. If only one channel is enabled, it gets the entire 256 Kwords. For

two channels, each channel gets 128 Kwords, and for four channels, each

channel gets 64 Kwords.

Each channel’s differential input range is independently programmable to ±0.2,

0.5, 1.0, 2.0, 5.0, 10.0, or 20.0 V. Single-ended signals can be acquired by

grounding the negative side of the input.

An isolation relay is supplied for each input, to protect both the module and the

unit-under-test from spurious voltages on power-on. These relays switch between

an on-board reference for self test (default), and the analog inputs.

To facilitate interfacing to digital signal processors, all serial bit streams and

required control signals from all sixteen A/D channels are brought out through

the front-edge connector.

1–4

VX4244 16-Channel Digitizer Module User Manual

Page 14

Getting Started

BITE (Built-in Test

Accessories

Fuses

Equipment)

The VX4244 Module has +5, –5, +12, –12, +24, –24, and –2 V fuse(s). The

fuses protect the module in case of an accidental shorting of the power bus or

any other situation where excessive current might be drawn.

If the +5 V fuse opens, the VXIbus Resource Manager will be unable to assert

SYSFAIL INHIBIT on this module to disable SYSFAIL*.

If any fuse opens, the fault must be removed before the fuse is replaced. Refer to

a qualified service person for assistance.

Built-in Test Equipment is provided by extensive self tests that are automatically

invoked on power-up, and may also be invoked on command. Circuitry tested

includes the CPU and all memory, the Analog-to-Digital (A/D) converters,

thresholds, latches and counters, the analog front-end, and the signal cross

switching. Arming, triggering, measurement complete, time-tag, and EEPROM

are also tested. The front panel LEDs provide visual BITE for module operation.

Table 1–1 lists the standard accessories included with the VX4244.

T able 1–1: Standard Accessories

Accessory Part Number

VX4244 User Manual 070-9067-XX

VX4244 Reference Manual 070-9377-XX

VX4244 16-Channel Digitizer Module User Manual

1–5

Page 15

Getting Started

Controls and Indicators

The following controls and indicators are provided to select and display the

functions of the VX4244 Module’s operating environment. See Figures 1–2

and 1–3 for their physical locations.

Switches

LEDs

LEDs

Signal

Inputs

Digital

I/O

The Logical Address switches must be correctly set to insure proper operation.

See Configuration for details of how to set the switches.

The following LEDs are visible at the top of the VX4244 Module’s front panel to

indicate the status of the module’s operation. See Operating Basics for a

description of each LED’s meaning.

POWER FAIL

ARMED ACCESS

TRIG ERROR

MIP GRP2

MC GRP1

S79 MSD

S89 LSD

Logical

Address

Switches

1–6

Figure 1–2: VX4244 Connector, Indicator, and Switch Locations

VX4244 16-Channel Digitizer Module User Manual

Page 16

LEDs

Signal

Inputs

Digital

I/O

Getting Started

Configuration

Logical Address Switches

Figure 1–3: VX4244 Front Panel

The following switches must be correctly set to insure proper operation. Refer to

Figure 1–2 for their physical locations.

Each function module in a VXIbus System must be assigned a unique logical

address, from 1 to 255 decimal. The base VMEbus address of the VX4244 is set

to a value between 1 and FFh (255d) by two hexadecimal rotary switches. Align

the desired switch position with the arrow on the module shield.

VX4244 16-Channel Digitizer Module User Manual

1–7

Page 17

Getting Started

The actual physical address of the VX4244 Module is on a 64 byte boundary. If

the switch representing the most significant digit (MSD) of the logical address is

set to position X and the switch representing the least significant digit (LSD) of

the logical address is set to position Y, then the base physical address of the

VX4244 will be [(64d * XYh) + 49152d]. For example:

L.A. MSD LSD Base Physical Address (d)

Ah 0 A (64 * 10) + 49152 = 49792d

15h 1 5 (64 * 21) + 49152 = 50496d

where:

L.A. = Logical Address

MSD = Most Significant Digit

LSD = Least Significant Digit

IEEE-488 Address

Front Panel Connectors

Using the VX4244 Module in an IEEE-488 environment requires knowing the

module’s IEEE-488 address in order to program it. Different manufacturers of

IEEE-488 interface devices may have different algorithms for equating a logical

address with an IEEE-488 address. Consult the operating manual of the

IEEE-488 Interface Module being used.

The front panel has two 50-pin D-type connectors. Refer to Appendix B for

connector pinouts.

1–8

VX4244 16-Channel Digitizer Module User Manual

Page 18

Installation

Getting Started

This section describes how to install the VX4244.

Tools Required

Requirements and

Cautions

A slotted screwdriver set is required for proper installation.

The VX4244 Module is a C size VXIbus instrument module and therefore may

be installed in any C or D size VXIbus mainframe slot other than slot 0. If the

module is being installed in a D size mainframe, consult the operating manual

for the mainframe to determine how to install the module in that particular

mainframe. Setting the module’s Logical Address switch defines the module’s

programming address. Refer to Configuration for information on selecting and

setting the module’s logical address. To avoid confusion, it is recommended that

the slot number and the logical address be the same.

NOTE. Note that there are two printed ejector handles on the card. To avoid

installing the card incorrectly, make sure the ejector marked “VX4244” is at the

top.

In order to maintain proper mainframe cooling, unused mainframe slots must be

covered with the blank front panels supplied with the mainframe.

Based on the number of instrument modules ordered with a Tektronix mainframe, blank front panels are supplied to cover all unused slots. Additional

VXIbus C size single-slot and C size double-slot blank front panels can be

ordered from your Tektronix supplier.

NOTE. Verify that the mainframe is able to provide adequate cooling and power

with this module installed. Refer to the mainframe Operating Manual for

instructions.

If the VX4244 is used in a Tektronix Mainframe, all VX4244 cooling requirements will be met.

NOTE. If the VX4244 Module is inserted in a slot with any empty slots to the left

of the module, the VME daisy-chain jumpers must be installed on the backplane

in order for the VXI Module to operate properly. Check the manual of the

mainframe being used for jumpering instructions.

VX4244 16-Channel Digitizer Module User Manual

1–9

Page 19

Getting Started

Installation Procedure

Follow these steps to install the VX4244.

CAUTION. The VX4244 Module is a piece of electronic equipment and therefore

has some susceptibility to electrostatic damage (ESD). ESD precautions must be

taken whenever the module is handled.

1. Record the revision level, serial number (located on the label on the top

shield of the VX4244), and switch settings on the Installation Checklist.

2. The module can now be inserted into one of the instrument slots of the

mainframe.

3. Cable Installation. If the mainframe has a cable tray, route the cable from the

front panel of the module down through the cable tray at the bottom of the

mainframe and out the rear of the mainframe.

1–10

Figure 1–4: Module Installation

VX4244 16-Channel Digitizer Module User Manual

Page 20

Installation Checklist

Getting Started

Installation parameters will vary depending on the mainframe being used. Be

sure to consult the mainframe Operating Manual before installing and operating

the module.

Revision Level:

Serial No.:

Mainframe Slot Number:

Switch Settings:

VXIbus Logical Address Switch:

(FFh enables dynamic configuration.)

Interrupt Level Select Switch: Dynamically programmed by the Resource

Manager.

Cables Installed: (if any)

Performed by: _______________________ Date: _____________

VX4244 16-Channel Digitizer Module User Manual

1–11

Page 21

Getting Started

Functional Check

The VX4244 Module will execute a self test at power-on, or on direction of a

VXIbus hard or soft reset condition, or on command. The power-on self test

consists of an interface self test and an instrument self test. The commanded self

test performs only the instrument self test. A VXIbus hard reset occurs when

another device, such as the VXIbus Resource Manager, asserts the backplane line

SYSRST*. A VXIbus soft reset occurs when another device, such as the

VX4244’s commander, sets the Reset bit in the VX4244’s Control register.

At power-on, as well as during self test, all analog inputs remain isolated from

the module’s front panel connector.

During power-on, or a hard or soft reset, the following actions take place:

1. The SYSFAIL* (VME system-failure) line is set active, indicating that the

module is executing a self test, and the Failed LED is on. In the case of a

soft reset, SYSFAIL* is set. However, all Tektronix/CDS commanders will

simultaneously set SYSFAIL INHIBIT. This is done to prevent the resource

manager from prematurely reporting the failure of a card.

2. A subset of the instrument self test, as described in the *TST command, is

then executed. This tests the CPU and all memory, the Analog to Digital

(A/D) converters, thresholds, latches and counters, and the analog front-end.

Arming, triggering, measurement complete, time-tag, and EEPROM are also

tested. If the self test fails, the module makes an internal record of what

failure(s) occurred. The ERROR? command can be used to view the results.

3. On completion of the interface self test, SYSFAIL* is de-asserted. If the test

fails, the SYSFAIL* line remains active. If the interface self test passed, the

SYSFAIL* line is released, and the module enters the VXIbus PASSED state

(ready for normal operation). If it failed, the module enters the VXIbus

FAILED state.

After self test, the module is returned to its default state, as described in the

*RST command description.

Self test can also be run at any time during normal operation by using the *TST

command. This test is more comprehensive than the power-on test, as it is not

subject to the 5 second completion requirement. At the end of a self test initiated

by this command, the module is restored to its power-on state.

1–12

VX4244 16-Channel Digitizer Module User Manual

Page 22

Getting Started

During a commanded self test:

1. SYSFAIL* is not asserted.

2. The module executes a comprehensive test of the instrument.

3. When the self test is completed, the module sets itself to the power-on

default state, with the exception of queuing any errors detected by the self

test. The ERROR? command can be used to view the results.

SYSFAIL * Operation

SYSFAIL* becomes active during power-on, hard or soft reset, self test, or if the

module loses any of its power voltages. When the mainframe Resource Manager

detects SYSFAIL* set, it will attempt to inhibit the line. This will cause the

VX4244 Module to deactivate SYSFAIL* in all cases except when +5 V power

is lost.

VX4244 16-Channel Digitizer Module User Manual

1–13

Page 23

Operating Basics

Power-on

The VX4244 16-Channel Digitizer Module is a VXIbus Message Based

instrument, and communicates using the VXIbus Word Serial Protocol. The

module is programmed by ASCII characters issued from the system controller to

the VX4244 via the module’s VXIbus commander and the VXIbus mainframe

backplane. Refer to the manual for the VXIbus device that will be the VX4244

Module’s commander for details on the operation of that device.

The sixteen analog inputs of the VX4244 are organized as four groups of four

channels each. Each group can operate independently, or in concert with any or

all of the other groups. For example, one group could be actively acquiring data,

while the second group is waiting for a trigger, the third group transferring data,

and the fourth group is being post-processed. Programmable features of each

channel group include the sampling frequency, arming, triggering, acquisition

control (pre-/center-/post-triggering), and the number of active channels in the

group. In addition, each channel’s input range is independently programmable.

The VX4244 will complete its self test and be ready for programming five

seconds after power-on. The VXIbus Resource Manager may add an additional

one or two second delay. The Power LED will be on, and all other LEDs off. The

MSG LED will blink during the power-on sequence as the VXIbus Resource

Manager addresses all modules in the mainframe. The default condition of the

module after power-on is is listed in the *RST command description. Self test

failures are described in Appendix C.

The format and syntax for the command strings is described in Syntax and

Commands. An alphabetical listing of the complete description of each command

is in the Command Descriptions.

Front-Panel Indicators

The VX4244 current operating status may be determined from the LEDs on the

front panel.

Power LED

Failed LED

VX4244 16-Channel Digitizer Module User Manual

This green LED is normally lighted and is extinguished if the ±5, –2, ±12, or

±24 V supplies fail or module fuses blow.

This normally off red LED is lighted whenever SYSFAIL* is asserted, indicating

a module failure. Module failures include failure to correctly complete an

2–1

Page 24

Operating Basics

interface self test, loss of a power rail, or failure of the module’s central

processor.

If the module loses any of its power voltages, the Failed LED will go on and

SYSFAIL* will be asserted. A module power failure is indicated when the

module’s Power LED is extinguished.

Access LED

Armed LED

TRIG (Triggered) LED

MIP (Measurement In

Progress) LED

MC (Measurement

Complete) LED

Error LED

This yellow LED is normally off. When lighted, it indicates that the module is

processing a VMEbus cycle. The LED is controlled by circuitry that appears to

stretch the length of the VMEbus cycle. For example, a 5 s cycle will light the

LED for approximately 0.2 seconds. The LED will remain lighted if the module

is being constantly accessed.

When lighted, this green LED indicates the channel group is “armed” and is

awaiting or processing the trigger. This LED goes out when data sampling is

complete.

When lighted, this green LED indicates the channel group has triggered.

When lighted, this green LED indicates that sampling for the channel group is

taking place. The LED is turned off whenever the memory is full, the memory is

accessed via the CPU, or the module is halted or reset.

This green LED indicates the conversion process for the channel group is

complete.

This yellow LED indicates an error has been detected by the module. It is cleared

when all errors have been read from the module, or the module is reset.

2–2

GRP2, GRP1 LEDs

These LEDs reflect the current channel group being displayed (see the DISPlay

command). They are encoded as shown below.

GRP2 GRP1 Group

Off Off 1

Off On 2

On Off 3

On On 4

VX4244 16-Channel Digitizer Module User Manual

Page 25

Instrument I/O – VXIbus Basics

CAUTION. If the user’s mainframe has other manufacturer’s computer boards

operating in the role of VXIbus foreign devices, the assertion of BERR* (as

defined by the VXIbus Specification) may cause operating problems on these

boards.

The VX4244 Module is a C size single slot VXIbus Message-Based Word Serial

instrument. It uses the A16, D16 VME interface available on the backplane P1

connector and does not require any A24 or A32 address space. The module is a

D16 interrupter.

The VX4244 Module is neither a VXIbus commander or VMEbus master, and

therefore it does not have a VXIbus Signal register. The VX4244 is a VXIbus

message based servant.

The module supports the Normal Transfer Mode of the VXIbus, using the Write

Ready, Read Ready, Data In Ready (DIR), and Data Out Ready (DOR) bits of

the module’s Response register.

Operating Basics

A Normal Transfer Mode read of the VX4244 Module proceeds as follows:

1. The commander reads the VX4244’s Response register and checks if the

Write Ready and DOR bits are true. If they are, the commander proceeds to

the next step. If not, the commander continues to poll these bits until they

become true.

2. The commander writes the Byte Request command (0DEFFh) to the

VX4244’s Data Low register.

3. The commander reads the VX4244’s Response register and checks if the

Read Ready and DOR bits are true. If they are, the commander proceeds to

the next step. If not, the commander continues to poll these bits until they

become true.

4. The commander reads the VX4244’s Data Low register.

A Normal Transfer Mode Write to the VX4244 Module proceeds as follows:

1. The commander reads the VX4244’s Response register and checks if the

Write Ready and DIR bits are true. If they are, the commander proceeds to

the next step. If not, the commander continues to poll the Write Ready and

DIR bits until they are true.

2. The commander writes the Byte Available command which contains the data

(0BCXX or 0BDXX, depending on the End bit) to the VX4244’s Data Low

register.

VX4244 16-Channel Digitizer Module User Manual

2–3

Page 26

Operating Basics

The VX4244 Module also supports the Fast Handshake Mode during readback.

In this mode, the module is capable of transferring data at optimal backplane

speed without the need of the commander’s testing any of the handshake bits.

The VX4244 Module asserts BERR* to switch from Fast Handshake Mode to

Normal Transfer Mode, per VXI Specification. The VX4244’s Read Ready,

Write Ready, DIR and DOR bits react properly, in case the commander does not

support the Fast Handshake Mode.

A Fast Handshake Transfer Mode Read of the VX4244 Module proceeds as

follows:

1. The commander writes the Byte Request command (0DEFFh) to the

VX4244’s Data Low register.

2. The commander reads the VX4244’s Data Low register.

The VX4244 Module has no registers beyond those defined for VXIbus message

based devices. All communications with the module are through the Data Low

register, the Response register or the VXIbus interrupt cycle. Any attempt by

another module to read or write to any undefined location of the VX4244’s

address space may cause incorrect operation of the module.

VX4244 Configuration

Registers

As with all VXIbus devices, the VX4244 Module has registers located within a

64 byte block in the A16 address space.

The base address of the VX4244 device’s registers is determined by the device’s

unique logical address and can be calculated as follows:

Base Address = V * 40H + C000H

where V is the device’s logical address as set by the Logical Address switches.

Table 2–1 is a list of the VX4244 Configuration registers with a complete

description of each. In this list, RO = Read Only, WO = Write Only, R = Read,

and W = Write. The address is relative to the module’s base address.

T able 2–1: Register Definitions

Register Address T ype Value (Bits 15–0)

ID Register 0000H RO 1011 1111 1111 1 100 (BFFCh)

Device Type 0002H RO See Device Type definition below

Status 0004H R Defined by state of interface

Control 0004H W Defined by state of interface

2–4

Offset 0006H WO Not used

Protocol 0008H RO 1111 0111 1111 1111 (F7FFh)

Response 000AH RO Defined by state of the interface

VX4244 16-Channel Digitizer Module User Manual

Page 27

Operating Basics

T able 2–1: Register Definitions (Cont.)

Register Value (Bits 15–0)TypeAddress

Data High 000CH Not used

Data Low 000EH W See Data Low definition below

Data Low 000EH R See Data Low definition below

Register Bit Definitions. The Read Protocol command response is F62Bh.

VX4244 16-Channel Digitizer Module User Manual

2–5

Page 28

Command Syntax

Command protocol and syntax for the VX4244 Module are as follows:

H A command string consists of a string of ASCII-encoded characters (up to

H Commands can be sent either individually, or strung together by delimiting

255 maximum) terminated by a <program message terminator>. The

<program message terminator> is optional white space, followed by any one

of the following command terminations:

A line feed <LF> character (0a hex, 10 decimal)

The END bit set

The END bit with a line feed

The command string is buffered until the terminator is encountered, at which

time the entire string is processed.

the individual commands with a semi-colon (;). For example, the string

sets channel 2 to a voltage range of ±10 volts, and group 1’s trigger source to

the external trigger input.

NOTE. Up to twenty command strings can be queued for processing by the

module. If this limit is exceeded, the additional command strings will be lost,

until space is freed up on the input queue. The Wait to Continue (*WAI) and

Operation Complete Query (*OPC?) commands will block processing and cause

the queue to fill up.

H All characters in a command may be sent in either upper or lower case form.

H Multiple data parameters passed by a command, or returned in a response are

separated by a comma (,).

VX4244 16-Channel Digitizer Module User Manual

3–1

Page 29

Command Syntax

H White space characters can be used to make a command string more

readable, and are ASCII-encoded bytes in the range 00–09, 0B–20 hex

(0–9,11–32 decimal). This range includes the ASCII control characters and

the space, but excludes the line feed <LF>. White space characters are

ignored when legally encountered in a command string. White space is

allowed anywhere in a command string, EXCEPT for the following:

Within a program mnemonic (for example, VO LT)

Around a colon (:) mnemonic separator (for example, VOLT: RANGE or

VOLT :RANGE)

Between a mnemonic and a (?) (for example, VOLT:RANGE ?)

Following an asterisk (*) (for example, * STB?)

Within a number (for example, 12 34)

Within a channel/group list (for example, ( @1) or (@1, 2) )

The following is a legal command string illustrating the use of white space:

VOLT:RANGE 1.00E+1 (@1,2,5:9); ERR?; fetch:data? 10 , 11

Without white spaces, this string is:

VOLT:RANGE1.00E+1(@1,2,5,9);ERR?;fetch:data?10,11

H A question mark (?) following a command indicates a response is to be

returned. All responses from the module are terminated with the line feed

<LF> (0a hex) character.

NOTE. If a read operation is performed without first issuing a command

requiring a response (?), a BUS TIMEOUT will occur.

H In the command descriptions, the following special characters are used.

Except for the colon (:), these characters are not part of the command, and

should not be sent. If an optional field is omitted, the command’s default will

be applied.

[ ] Brackets indicate an optional field

| A bar indicates a logical OR choice

: A colon is used to separate command fields

3–2

< > Field indicator

VX4244 16-Channel Digitizer Module User Manual

Page 30

Command Syntax

Field Definitions

<channel list>. The channel list field is used to apply commands to multiple

channels. Channels can be listed individually, separated by a comma; sequentially, separated by a colon; or a combination of the two. For example,

(@1,3,5,9:11,16) specifies channels 1, 3, 5, 9, 10, 11, and 16. Valid channel

numbers are 1 through 16. If a query response is expected from the command,

the response is returned in the same order as the channel list. For example

specifying (@1,16,2) returns the value of channel 1, followed by the value of

channel 16, followed by the value of channel 2. In addition (ALL) can be

specified as a channel list, equivalent to (@1:16).

<group list>. The group list field is used for those commands which apply to a

channel group. There are four channel groups of four channels each:

Group Channels

1 1 – 4

2 5 – 8

3 9 – 12

4 13 – 16

The same syntax as the <channel list> applies to the <group list>. For example,

(@1,2,3:4) specifies groups 1, 2, 3, and 4. In addition (ALL) can be specified as

a group list, equivalent to (@1:4).

Specifiers

<channel id> or <group id>. Some commands can only be specified on a single

channel or group. The syntax is the same as above, but only one channel or

group can be specified, for example, (@1).

<boolean>. ASCII 0 or 1

<hex16 value>. 16 bit hex value, ASCII 0000 through FFFF, right justified.

<x..y>. Any single value between x and y, inclusive of x and y.

VX4244 16-Channel Digitizer Module User Manual

3–3

Page 31

Command Syntax

Syntax Example

Numeric Value Formats

Capital letters indicate the minimum required characters which need to be sent.

Lower case letters are optional. As an example, the syntax of one of the voltage

commands is given as:

[SENSe:]VOLTage[:DC]:RANGe[:UPPer] <voltage> [<channel list>]

Each of the following is a valid form of this command:

SENSE:VOLTAGE:DC:RANGE:UPPER 1.0E+00 (@1)

volt:dc:rang:upp 1.0 (@1)

volt:rang:upp 1 (@1)

volt:rang 1 (defaults to channel 1)

When specifying numeric values, fixed or floating-point formats are allowed. All

numbers are rounded to the nearest value appropriate for the particular command

as specified in the command description. If a sign is not specified, the number is

assumed to be positive.

A number whose value is 5 can be represented by any of the following:

5

5.0000

+.5e1

+05

50E-1

5.0

0.500E+001

0.0000000000000005e16

3–4

VX4244 16-Channel Digitizer Module User Manual

Page 32

Functional Command Groups

This section lists the VX4244 commands by functional command group.

System Commands

Module Commands

Command Summary

Although these non-data commands are initiated by the VX4244’s commander

rather than the system controller, they have an effect on the VX4244 Module.

The following VXIbus Instrument Protocol Commands will affect the VX4244:

Command Effect

Clear The module clears its VXIbus interface and any pending commands.

Current module operations are unaffected.

Trigger If programmed, this command can be used to trigger the VX4244

sampling process.

Begin Normal

Operation

Read Protocol The module will return its protocol to its commander.

The module will begin operation if it has not already done so.

A summary of the VX4244 Module’s commands is listed below. This is

followed by detailed descriptions of each of the commands. A sample program

using these commands is shown in Appendix E: Examples.

Command Description

ABORt stops data sampling on the group(s) specified.

ARM controls the use of the external ARM input, and zeroing memory when

CALibrate calibrates the channel specified for the voltage range specified.

DISPlay controls the LED display on the front panel: ARMED, TRIG, MIP, and

ERRor reads the error messages from the module or returns the number of

FDC sets up Fast Data Channel functions.

FETCh retrieves some basic signal parameters.

FORMat enables/disables overrun flagging.

FREQuency sets various sampling clock parameters, and controls clock synchro-

INITiate arms the specified channel groups.

OUTPut controls various output functions of the module.

VX4244 16-Channel Digitizer Module User Manual

a group(s) is INITiated.

MC, showing the state of the specified channel group.

error messages queued.

nization.

3–5

Page 33

Functional Command Groups

>

comm

event

status reporting.

Command Description

ROSCillator sets the reference (master) clock frequency.

ROUTe defines the active channels within a channel group.

SWEep sets up the group sampling frequencies and record lengths

TRIGger sets group triggering parameters.

VERSion returns the SCPI command version level.

VOL Tage sets the input voltage ranges of the channels.

IEEE 488.2 Commands

Command Description

*CAL? Calibration query; returns the calibration status.

*CLS Clear Status command; clears the Event Status Register (ESR) and

any pending Service Requests (SRQs).

*ESE <mask

*ESE? Event Status Enable (ESE) query; returns the value of the Event Status

*ESR? Event Status Register (ESR) query; returns the value of the Event

*IDN? Identification query; returns a 4-field response.

*OPC Operation Complete command; controls setting the OPC bit in the

*OPC? Operation Complete query; puts a 1 in the output queue when all

*RST Reset; resets the module to its power-on state.

*SRE Service Request Enable (SRE) register; defines the mask for

*SRE? Service Request Enable (SRE) query; returns the value of the Service

Event Status Enable (ESE)

Enable register.

Status Register.

Event Status register (ESR).

pending operations have been completed.

generating VXI Request True interrupts.

Request Enable register.

and; defines the mask for

3–6

*STB? Status Byte (SB) query; returns the value of the status byte register.

*TST Execute the self test.

*TST? Self Test query; returns the self test status.

*WAI W ait to Continue; suspends command processing until all pending

operations have been completed.

VX4244 16-Channel Digitizer Module User Manual

Page 34

Command Descriptions

This section lists the VX4244-specific commands and queries in alphabetic

order. The IEEE 488.2 Common Commands are listed in the next section.

ABORt

Command Syntax

Query Syntax

Query Response(s)

*RST Value

Limits

Related Commands

Description

Examples

N/A

N/A

N/A

N/A

INITiate

The ABORt command disarms and stops data sampling (if active) on the

specified group(s). All input relays of the specified group(s) are opened.

If [<group list>] is not specified, it defaults to 1.

Command Response

ABORT (@1) N/A; abort sampling on channel group 1.

abor (@1:4) N/A; abort sampling on all channel groups.

VX4244 16-Channel Digitizer Module User Manual

3–7

Page 35

Command Descriptions

ARM

Command Syntax

Query Syntax

Query Response(s)

ARM

[:SEQuence[<n>]]

[:LAYer[<n>]]

:SLOPe POSitive | NEGative

:SOURce EXTernal | IMMediate [<group list>]

:ZERO <boolean> [<group list>]

ARM

[:SEQuence[<n>]]

[:LAYer[<n>]]

:SLOPe?

:SOURce? [<group list>]

:ZERO? [<group list>]

:SLOPe POS | NEG

:SOURce EXT | IMM

:ZERO 0 | 1 (1 = enabled)

*RST Value

Limits

Related Commands

Description

:SLOPe POSitive

:SOURce IMMediate (all groups)

:ZERO 0 (all groups)

<boolean> 0 | 1

<n> 1 to 32767

INITiate

The ARM commands define various conditions for arming the group triggers in

response to an INITiate command.

ARM:SLOPe defines the active edge of the external arm input. It is executed on

receipt of an INITiate command.

ARM:SOURce EXTernal enables the external arm input. If EXTernal is

specified, the INITiate command arms the external arm input, which must

3–8

VX4244 16-Channel Digitizer Module User Manual

Page 36

Command Descriptions

transition through the specified slope to arm the triggers. ARM:SOURce

IMMediate internally arms the triggers on INITiate.

ARM:ZERO controls whether group memory is zeroed prior to arming the

triggers when an INITiate command is received. A ‘1’ indicates memory is to be

cleared. A ‘0’ does not clear the memory.

If [<group list>] is not specified, it defaults to 1. If <boolean> is not specified, it

defaults to 0.

The optional SEQuence and LAYer fields are included for SCPI compatibility

only, and have no effect on the module.

NOTE. The ARMED LED reflects the state of the internal armed signal only.

When the module is armed, the LED will light regardless of the state of the

external armed input (if enabled).

Examples

NOTE. The external arm input is global to all channel groups. If a channel group

has been previously initiated with negative slope, and external arm is enabled

(and has not armed), then initiating a new channel group with a positive arm

slope will cause the first group’s external arm to become active.

Command Response

ARM:SEQUENCE1:

LA YER1:SLOPE NEGATIVE

arm:slop? NEG<LF>

arm:sour ext (@2) N/A; set group 2 to enable external arm.

arm:source?(all) IMM,EXT,IMM,IMM<LF>

ARM:zero 1 (@2,4) N/A; enable zeroing of memory for groups 2 and 4.

arm:zero?(@1:4) 0,1,0,1<LF>

N/A; set external arm slope to negative edge true.

VX4244 16-Channel Digitizer Module User Manual

3–9

Page 37

Command Descriptions

CALibrate

Command Syntax

Query Syntax

Query Response(s)

*RST value

Limits

Related Commands

CALibrate

:VALUe <calibration value> [<channel id>]

:ZERO <voltage range> [<channel id>]

CALibrate

:VALUe?

:ZERO?

:VALUe? +xx.xxxxxx, +yy.yyyyy

(x’s = offset value; y’s = gain value)

:ZERO? +xx.xxxxxx (offset value)

N/A

<calibration value> 0.0796 – 19.90

<voltage range> 0.2 – 20.0 (rounded up to nearest input range)

*CAL?

3–10

Description

This command calibrates the range specified for the channel specified. The

CAL:VALUE command calibrates the gain and offset for the value specified (see

the table below). The CAL:ZERO command calibrates only the offset for the

range and channel specified. If <voltage range> is zero, the CAL:ZERO

command will calibrate the offset for all ranges on the channel specified.

The Error LED will blink while the calibration command is being executed. This

command resets the module prior to execution. After completion, the module is

restored to its *RST state with the exception that calibration errors (if any) will

be queued.

The CAL:VALUe? query returns the calibrated offset and gain values. The

CAL:ZERO? query returns the calibrated offset value.

The *CAL? query, the Operation Complete bit of *ESR?, or the *SRE interrupt

can be used to determine when the calibration has completed. If the calibration

fails, the ERRor? command can be used to view the results.

VX4244 16-Channel Digitizer Module User Manual

Page 38

Command Descriptions

The following commands are allowed during the CALibrate routine (all others

are ignored):

*CAL? *ESE? *ESR? *IDN?

*SRE? *STB? *TST? *WAI

*OPC *OPC?

If [<channel id>] is not specified, it defaults to 1.

For firmware revisions 1.3 and later, a differential calibration is performed to

increase the DC accuracy of the input ranges. That is, each range is calibrated

based on its +95% and –95% values. See Appendix G for the calibration

procedure. Use the following calibration values to calibrate the implied input

range:

Examples

Input V oltage Span Recommended Calibrator

Voltage

±0.0796 – ±0.199 ±0.190 VDC 0.2

±0.199 – ±0.499 ±0.475 VDC 0.5

±0.499 – ±0.999 ±0.950 VDC 1.0

±0.999 – ±1.990 ±1.900 VDC 2.0

±1.990 – ±4.990 ±4.750 VDC 5.0

±4.990 – ±9.990 ±9.500 VDC 10.0

±9.990 – ±19.90 ±19.00 VDC 20.0

Command Response

CALibrate:VALUe 0.19 (@5) N/A; calibrate the gain and offset of the 0.2 volt range for

channel 5 to an input value of 0.19 volts.

CAL:ZERO 5(@16) N/A; zero the offset for channel 16, range 5.

CAL:ZERO 0 (@1) N/A; zero the offset for all channel 1 ranges.

CALibrate:VALUe? +0.000006,–0.190006<LF>

CAL:ZERO? +0.000006<LF>

Range Calibrated

VX4244 16-Channel Digitizer Module User Manual

3–11

Page 39

Command Descriptions

DISPlay:GROUp

Command Syntax

Query Syntax

Query Response(s)

*RST Value

Limits

Related Commands

Description

1 to 4 (currently displayed group)

1

1 through 4

N/A

The DISPlay:GROUp command controls the display on the front panel for the

ARMED, TRIG (triggered), MIP (measurement in progress), and MC (measurement complete) LEDs. The state of these signals for the group specified is

displayed. A lighted LED indicates the signal is active.

The group LEDs also provide a visual indication of which channel group is

being displayed. These LEDs are encoded as:

3–12

Examples

GRP2 GRP1 Group

Unlit Unlit 1

Unlit Lit 2

Lit Unlit 3

Lit Lit 4

If [<1..4>] is not specified, it defaults to 1.

Command Response

DISPLAY:GROUP 3 N/A; display group 3’s status.

DISP:GROUP? 3<LF>

disp:grou 1 N/A; display group 1’s status.

VX4244 16-Channel Digitizer Module User Manual

Page 40

ERRor?

Command Descriptions

Command Syntax

Query Syntax

Query Response(s)

*RST Value

Limits

Related Commands

Description

N/A

[SYSTem:]

ERRor?

ERRor:COUNt?

Error message or number of errors queued.

N/A

N/A

N/A

The error command reads the error messages from the module. Up to 20 errors

can be queued. Errors are output on a first-in first-out basis. If the error queue is

filled, the last error in the queue is overwritten with the message –350,“Queue

overflow”. If no errors are queued, or when the queue has been emptied, the

module will respond with 0,“No error”. Where applicable, a <description> field

is provided to clarify the error. The maximum error message length is 255

characters.

The ERR:COUNT? command returns the number of error messages queued.

If enabled, the module will set the appropriate Error bit in the Event Status

register (*ESR? command) when an error is detected. See the *ESR? command

for more detail.

Error values from –100 to –199 are Command errors. Error values from –200 to

–299 are Execution errors. Error values from –300 to –399 are Device Dependent

errors. Error values from –400 to –499 are Query errors. Error messages are:

0,"No error"

-100,"Command error;<description>"

-102,"Syntax error;<description>"

-103,"Invalid separator;<description>"

-109,"Missing parameter;<description>"

-110,"Command header error;<description>

-112,"Program mnemonic too long;<description>"

-113,"Undefined header;<description>"

VX4244 16-Channel Digitizer Module User Manual

3–13

Page 41

Command Descriptions

-131,"Invalid suffix;<description>"

-171,"Invalid expression;<description>"

-220,"Parameter error;<description>"

-221,"Settings conflict;<description>"

-222,"Data out of range;<description>"

-223,"Too much data;<description>"

-300,"Device-specific error;LCA failure,<description>"

-300,"Device-specific error;EEPROM error,<description>"

-300,"Device-specific error;Calibration error,<description>"

-311,"Memory error;<description>"

-315,"Configuration memory lost;<description>"

-330,"Self-test failed;<description>"

-350,"Queue overflow"

-400,"Query error;Missing `?'<description>"

-410,"Query INTERRUPTED"

Examples

Command Response

SYSTEM:ERROR? 0,“No error”<LF>

err? –1 13,“Undefined header;VOLX:RANGE 5”<LF>

ERR:Count? 1<LF>

3–14

VX4244 16-Channel Digitizer Module User Manual

Page 42

FETCh

Command Descriptions

Command Syntax

Query Syntax

Query Response(s)

*RST Value

Limits

N/A

FETCh

:MAXimum? [<count>][,<starting address>] [<channel id>]

:MINimum? [<count>][,<starting address>] [<channel id>]

:AVErage? [<count>][,<starting address>] [<channel id>]

:TRMS? [<count>][,<starting address>] [<channel id>]

:DATa? <count> [,<starting address>] [<channel id>]

:BINary? <count> [,<starting address>] [<channel id>]

:PTRansition? [<count>][,<starting address>] [<channel id>]

:NTRansition? [<count>][,<starting address>] [<channel id>]

:TIMEtag? [<group list>]

See the examples below.

<count> the amount of memory available/channel

<starting address> 0 (trigger address)

<count> 1 to the amount of memory available/channel

Related Commands

Description

<starting address> ± the amount of memory available/channel

ROUTe

TRIGger:OFFSet?

The FETCh commands retrieve some basic signal parameters.

<count> defines the number of samples to perform the FETCh on. For example,

FETCh:MAX 100 returns the maximum value found in the first 100 samples

after the trigger. If <count> is not specified, it defaults to the amount of memory

available for that channel. <count> MUST be specified for FETCh:BINary and

FETCh:DATa, or an out of range error will be generated.

<starting address> defines the starting address of the data relative to the trigger

address (address 0). For example, FETCh:MIN 100,–50 returns the minimum

value found in 100 samples beginning 50 locations before the trigger, the trigger

point (address 0), and ending 49 locations after the trigger. If <starting address>

is not specified, it defaults to 0. If a single channel is active in a group, there is a

four sample ambiguity as to the actual trigger address. For example, if a

VX4244 16-Channel Digitizer Module User Manual

3–15

Page 43

Command Descriptions

threshold trigger was specified, the actual trigger point can be anywhere from

address 0 to address 3. For two channels/group, the ambiguity is 2 (address 0 to

1). For four channels/group, there is no ambiguity. See the TRIGger:OFFSet?

query for determining the actual trigger location.

If <channel id> is not specified, it defaults to 1. Except for time-tag data, note

that only one channel can be specified per FETCh command. Also, the channel

specified must have been ROUTed, or an error will be generated when a FETCh

command is received.

Because the FETCh commands take a relatively long time to process, the Error

LED will blink while the FETCh command is being executed. If a FETCh is

requested on an armed channel, the channel’s group will be disarmed before

executing the FETCh. For this case, address 0 is set to the current write address

of the memory (presumably the oldest data in memory).

MAXimum returns the maximum value found for the channel specified.

MINimum returns the minimum value found.

AVErage returns the average value calculated.

DATa returns ASCII encoded data. A maximum of 1000 data values can be

returned per FETCh command.

BINary returns two’s complement binary data via word serial. A maximum of

5000 binary data values can be returned per FETCh command. For two’s

complement data, hex 8000 represents negative full scale (–32768 decimal), hex

0000 represents 0, and hex 7fff represents positive full scale (32768 decimal).

One bit below zero is ffff hex, and one bit above zero is 0001 hex. The actual

value of the sample is (binary value * (voltage range / 32768)). For word serial

transfers, the most significant byte is transferred first, followed by the least

significant byte.

PTRansition returns the maximum positive transition found between any two

successive data points.

NTRansition returns the maximum negative transition found between any two

successive data points.

TRMS returns the true RMS value of the data. The TRMS is the square root of

the sum of the squares of each data point, divided by the number of samples.

For the MAX, MIN, PTR, and NTR responses, the second value returned is the

address of the data relative to the trigger address (0).

3–16

TIMEtag reads the time tag values of the specified group(s). The resolution of

the time is based on the source programmed by the FREQ:TIMEtag command.

The time-tag counters are zeroed when a synchronization pulse is received, then

immediately begin counting. The counters continuously count until their

respective group is triggered, at which time their count is frozen. This provides

VX4244 16-Channel Digitizer Module User Manual

Page 44

Command Descriptions

the relative time between group triggers and absolute time relative to the sync

signal.

For a time-tag clock source of 10 MHz (100 ns resolution), the counters can

count to 100e–9 * (2^32 – 1) = 429.497 seconds before rolling over. If the

master clock were selected at 200 kHz (5 s resolution), the counters would

count to 21474.8 seconds (5.965 hours). If [<group list>] is not specified, it

defaults to 1.

Examples

Command Response

FETCH:MAXIMUM?(@1) Fetch the maximum value of channel 1. The first value is the

maximum value found. The second value is the address of the

maximum value.

+1 1.123456,0123456<LF>

fetch:data? 3,123455 Fetch the data around the maximum value found in the

example above.

+1 1.123000,+11.123456,+11.123400<LF>

fetc:min? 100 Fetch the minimum value of 100 samples beginning at address

0 of channel 1.

–1.123456,0000000<LF>

fetch:ave? (@16) Fetch the average value of channel 16.

+3.333333<LF>

fetch:data? 3,250 Fetch 3 data values beginning 250 locations after the trigger.

+1 1.123456, +1.234567, –1.234567<LF>

fetch:bin? 100,321 Fetch 100 binary samples beginning 321 locations after the

trigger.

––– returns two’s complement binary data –––

fetch:ptr? Fetch the maximum positive transition found.

fetch:ntr? Fetch the maximum negative transition found.

fetch:timetag?(@2) Fetch the time-tag value of channel 2.

fetch:trms? Fetch the true RMS value.

VX4244 16-Channel Digitizer Module User Manual

+1.234567,0123456<LF>

–1.234567,0123456<LF>

+1.123456789012E+02<LF>

+0.003009<LF>

3–17

Page 45

Command Descriptions

FORMat

Command Syntax

Query Syntax

Query Response(s)

*RST Value

Limits

Related Commands

Description

!

"

!

"

:OVERrun 0 | 1 (1 = enabled)

:OVERrun 0 (off)

<boolean> 0 to 1

VXI:FDC

INITiate

The FORMat:OVERrun command controls flagging of data loss during

continuous Fast Data Channel (FDC) data acquisition.

The OVERrun option is a means to flag data loss when collecting data in a

continuous (free-run) acquisition scenario. As memory is being filled, periodic

Fast Data Channel (FDC) requests can be generated to off-load the data from the

module. If the system controller does not off-load the data sufficiently fast,

overrun can occur since data is continuously being acquired.

3–18

The overrun option uses the least significant bit (LSB) of the 16-bit data to flag

when overrun has occurred. An LSB of 0 indicates no overrun. If overrun occurs,

the LSB is set high for the four samples prior to where data loss occurred, and

additional data acquisition is inhibited. As memory is freed by off-loading data

from the module, additional data samples can be acquired.

For example, suppose that the module was set up with overrun enabled in the

2048 sample FDC AUTO mode, and initiated continuously:

If no FDC transfers occurred, the module would collect 128 buffers of 2048

samples each, and then inhibit additional collection until a buffer was freed. The

last four samples of the 128th buffer would have the LSB bit set to 1.

VX4244 16-Channel Digitizer Module User Manual

Page 46

Command Descriptions

The overrun function is global to all channel groups on the module. Because it

affects the data values being acquired, it can not be modified if any group is

actively sampling data. An error will be generated on receipt of an INITiate

command if this is attempted. A ‘1’ enables the overrun mode. A ‘0’ disables it.

Examples

Command Response

FORMAT:OVERRUN? 0<LF>

form:over 1 No response; enable overrun mode.

VX4244 16-Channel Digitizer Module User Manual

3–19

Page 47

Command Descriptions

FREQuency:TINTerval

FREQuency:RANGe

Command Syntax

Query Syntax

Query Response(s)

*RST Value

Limits

[SENSe:]

FREQuency

:TINTerval [<time interval>] [<group list>]

:RANGe [<frequency>] [<group list>]

[SENSe:]

FREQuency

:TINTerval? [<group list>]

:RANGe? [<group list>]

:TINTerval +x.xxxxxxxE+xx (time interval)

:RANGe +x.xxxxxxxE+xx (frequency value)

:TINTerval 5 s (all groups)

:RANGe 200 kHz (all groups)

:TINTerval (1 to 65280) / (ROSCillator frequency)

5 s minimum

3–20

Related Commands

Description

:RANGe (ROSCillator frequency) / (1 to 65280)

200 kHz Maximum

FREQ:SYNChronize

FREQ:SOURce

ROSCillator

The FREQ:TINTerval and FREQ:RANGe commands define the sampling

period/frequency of a channel group(s).

The FREQ:TINT and FREQ:RANGe commands set the sampling time interval/

sampling frequency of the group(s) specified. The VX4244 Module uses a

two-stage clock scheme. The first stage is the reference (master) clock. This

clock (ROSCillator) is fed to each of the four channel groups, which use dividers

to generate the actual sampling clock of that group. These dividers can generate a

sampling frequency of 1 to 1/65280th of the reference clock.

VX4244 16-Channel Digitizer Module User Manual

Page 48

Command Descriptions

The maximum group frequency is the lesser of the programmed value, the

ROSCillator frequency / 2, or 200 kHz. If the specified frequency is greater than

the (ROSCillator frequency / 2), an out of range error message will be generated.

Programmed values are rounded to the nearest divisible integer value.

The query responses to the FREQ:TINT and FREQ:RANGe commands return

the actual (rounded) time interval/frequency values programmed. The

FREQ:TINT and FREQ:RANGe commands are reciprocals of each other (time =

1 / frequency).

If FREQ:SOURce:INTernal is specified, the dividers described above are used.

EXTernal feeds the external clock directly to the analog/digital converters. That

is, no division is performed on the external clock.

If [<group list>] is not specified, it defaults to 1. If <frequency> is not specified,

it defaults to the lesser of the (ROSCillator frequency) / 2, or 200 kHz.

NOTE. Be careful when using these commands. They are executed immediately

after processing. Unlike programming the ROSCillator, these commands are

allowed while a channel group is actively sampling. This is to allow dynamic

modification of the sampling interval(s). The normal mode of operation is to

program these parameters prior to arming the channel groups.

Examples

NOTE. Modifying the ROSCillator source or frequency automatically modifies

the group frequencies to the lesser of the (ROSCillator frequency) / 2, or

200 kHz. Therefore the ROSCillator should be programmed (if required) prior to

the group frequencies.

Command Response

SENSE:FREQUENCY

:RANGE 200E3 (@1:4)

freq:tint 10e–6 (@2) N/A; set group 2 to a 10 second sampling period (100 kHz

freq:tint? (@2) +1.0000000E–05<LF>

freq:rang? (@1,2) +2.0000000E+05,+1.0000000E+05<LF>

N/A; set the sampling frequency of all channel groups to

200 kHz (5 s sampling period).

sampling frequency).

VX4244 16-Channel Digitizer Module User Manual

3–21

Page 49

Command Descriptions

FREQuency:SOURce

FREQuency:SLOPe

FREQuency:TIMEtag

Command Syntax

Query Syntax

Query Response(s)

*RST Value

'!)

$! * $! $"'# %&

&( * &(

& * &"$

'!)

$"'# %&

&

:SOURce INT | EXT

:SLOPe POS | NEG

:TIMEtag CLK10 | ROSC

:SOURce Internal

:SLOPe Positive

3–22

Limits

Related commands

Description

:TIMEtag Clk10

N/A

ROSCillator

FREQ:RANGe

FETCh:TIMEtag

FREQ:SYNChronize

The FREQ:SOURce command sets the source of the clock for the FREQ:TINT/

FREQ:RANGe commands. INTernal uses the internal clocks to generate the

sampling frequencies for the group(s) specified. EXTernal uses the external clock

input as the sampling clock.

VX4244 16-Channel Digitizer Module User Manual

Page 50

Command Descriptions

The FREQ:SLOPe command sets the active edge of the external clock input to

either positive true or negative true. Data is sampled on the falling edge of the

clock.

The FREQ:TIMEtag command sets the source of the time-tag clock to either the

VXI 10 MHz ECL clock or the ROSCillator clock.

If [<group list>] is not specified, it defaults to 1.

NOTE. Be careful when using these commands. They are executed immediately

upon processing. Unlike programming the ROSCillator, these commands are

allowed while a channel group is actively sampling. This is to allow dynamic

modification of the parameters. The normal mode of operation is to program

these parameters prior to arming the channel groups.

Examples

Command Response

freq:source ext N/A; set group 1 to external clock input.

freq:sour? (all) EXT,INT,INT ,INT<LF>

freq:sour? (@2,1) INT ,EXT<LF>

freq:slope negative N/A; set external clock slope to negative edge.

freq:slop? NEG<LF>

freq:time? CLK10<LF>

freq:timetag rosc N/A; set the time-tag clock source to the reference oscillator.

freq:time? ROSC<LF>

VX4244 16-Channel Digitizer Module User Manual

3–23

Page 51

Command Descriptions

FREQuency:SYNChronize

Command Syntax

Query Syntax

Query Response(s)

*RST Value

($*

!&%$"+

# "'") , '")

"'

& ,

($*

!&%$"+

#

&

:LEVEl POS | NEG

:TTLTrg 1 to 7 | 8 (off)

:LEVEl Negative

:TTLTrg 8 (off)

Limits

Related Commands

Description

:TTLTrg 1 through 8

ROSCillator

FREQuency: RANGE

FETCh:TIMEtag

This command synchronizes the clocks for the channel groups, and/or synchronizes the clocks of multiple modules. Three means are provided for synchronization: via command (FREQ:SYNC:IMM); via the external sync input; or via one

of the VXI TTL triggers (FREQ:SYNC:TTLTrg <1..7>). Synchronization will

occur when any of these three signals is active (logical OR). The synchronization