Model 2001 Multimeter

Repair Manual

2001-902-01 Rev. C / May 2011

moc.yelhtiek.www

ECNEDIFNOC FO ERUSAEM RETAERG A

Model 2001 Multimeter

Repair Manual

© 1993-2011, Keithley Instruments, Inc.

Cleveland, Ohio, U.S.A.

All rights reserved.

Reproduction and distribution of this technical manual is authorized for government purposes.

Any unauthorized reproduction, photocopy, or use the information herein, in whole or in part,

without the prior written approval of Keithley Instruments, Inc. is strictly prohibited.

All Keithley Instruments product names are trademarks or registered trademarks of Keithley

Instruments, Inc. Other brand names are trademarks or registered trademarks of their respective

holders.

The Lua 5.0 software and associated documentation files are copyright © 1994-2008, Tecgraf,

PUC-Rio. Terms of license for the Lua software and associated documentation can be a ccessed at

the Lua licensing site (http://www.lua.org/license.html).

Document number: 2001-902-01 Rev. C / May 2011

The following safety precautions should be observed before using this product and any associated instrumentation. Although some

instruments an d access ories would n ormally be used with non-h azardous voltag es, there are situ ations where h azardous condition s may

be present.

This product is inte nded for us e by qual ified person nel who recognize s hock haz ards and are famili ar with the s afety prec autions requ ired

to avoid possible in jury. Rea d and fo llow all inst a llatio n, opera tion, an d mai ntenanc e info rmatio n carefu lly b efore us ing the product. Ref er

to the user documentation for complete product specifications.

If the product is used in a manner not specified, the protection provided by the product warranty may be impaired.

The types of product users are:

Safety Precautions

Responsible body i

operated within its specifications and operating limits, and for ensuring that operators are adequately trained.

Operators

They must be protected from electric shock and contact with hazardous live circuits.

Maintenance personnel

replacing consuma ble ma terials . Main tenanc e proc edures are descri bed in t he u ser docum ent ation. The proced ures expl icitly st ate if th e

operator may perform them. Otherwise, they should be performed only by service personnel.

Service personnel are trained to work on live circuits, perform safe installations, and repair products. Only properl y trained serv ice

personnel may perform installation and service procedures.

Keithley Instruments products are designed for use with electrical signals that are rated Measurement Category I and Measurement

tegory II, as described in the International Electrotechnical Commission (IEC) Standard IEC 60664. Most measurement, control, and

Ca

data I/O signals are Measurement Ca tegory I and must not be dire ctly connected to ma ins voltag e or to voltage sourc es with high transient

over-voltages. Measur ement Category II connections require protection for high transient over-voltages often associated with local AC

mains connect ions. Assume all measurement, co ntrol, and dat a I/O connec tions are for conn ection to Cate gory I sources u nless otherwise

marked or described in the user documentation.

Exercise extreme caution when a shock hazard is present. Lethal vo

American National Standards Institute (ANSI) states that a shock hazard exists when voltage levels greater than 30V RMS, 42.4V peak,

or 60VDC are present. A good safety practice is to expect that hazardous voltage is present in any unknown circuit before measuring.

Operators of this product must be protected from electric shock at all times. The responsible body must ensure that operators are

p

revented access and /or insulate d from every connection point. In some case s, connect ions must b e exposed to potential human contact.

Product operators in th ese ci rcu ms t ances must be train ed t o p r otec t themselves from the ri sk of electric shock. If the ci rcu it is capable of

operating at or above 1000V, no conductive part of the circuit may be exposed.

use the product for its inten ded function. T hey must be trained in e lectrical safe ty procedures a nd proper us e of the inst rument.

s the individual or group responsible for the use and maintenance of equipment, for ensuring that the equipment is

perform routine procedures on the produ ct to keep it operatin g p rop erly, for example, setting the li ne v oltage or

ltage may be present on cable connector jacks or test fixtures. The

Do not connect switc hing cards direc tly to unlim ited power circui ts. They ar e intended to b e used with im pedance-lim ited sources

connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current

and voltage to the card.

Before operating an instrument, ensure that the line cord is connected to a properly-grounded power receptacle. Inspect the conne

cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

. NEVER

cting

11/07

When installing equipment where access to the main power cord is restricted, such as rack mounting, a separat e main input power

!

disconnect device must be provided in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any other instruments while power is applied to the circuit under te

AL W AYS remove powe r from the entire te st system and d ischarge an y capa citors before: c onnecting or disconne cting cab les or jumpers,

installing or removing switching cards, or making internal changes, such as installing or removing jumpers.

Do not touch any o bject that could pro vide a c urrent p ath to the com mon sid e of the c ircuit under t est or p ower line (e arth) gro

make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the voltage being measured.

The instrument and accessories must be used in accordance with its specifications and operating instructions, or the safety of the

equipment may be impaired.

Do not exceed the maxi mum s ignal levels of the ins tru ment s and acces sories , as defi ned in th e spec ifica tion s and op erating inform

and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with the same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the

interlock.

If a screw is present, connect it to safety earth ground using the wire recommended in the user documentation.

The symbol on an instrument indicates that the user should refer to the operating instructions located in the user documentation.

The symbol on an instrument shows that it can source or measure 1000V or more, including the combined effect of normal and

common mode voltages. Use standard safety precautions to avoid personal contact with these voltages.

st.

und. Always

ation,

use of a lid

The symbol on an instrument shows that th e surface may be hot. Avoid personal conta c t to prevent burns.

The symbol indicates a connection terminal to the equipment frame.

If this symbol is on a product, it indicates that mercury is present in the display lamp. Please note that the lamp must be properly

disposed of according to federal, state, and local laws.

ARNING heading in the user documentation explains dangers that might result in personal injury or death. Always read the

The W

associated information very carefully before performing the indicated procedure.

The CA

warranty.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

T o main tain protecti on from electric sho ck and fire, replacem ent component s in mains circu its - includi ng the power trans former , tes

and input jacks - must be purchased from Keithley Instruments. Standard fuses with applicable national safety approvals may be used if

the rating and type are the same. Other components that are not safety-related may be purchased from other suppliers as long as they

are equivalent to the original component (note that selected parts should be purchased only through Keithley Instruments to maintain

accuracy and function ality of the product). If you ar e unsure about the applicabi lity of a replacement co mponent, call a Keithley Ins truments

office for information.

To clean an instrument, use a damp cloth or mild, water-based cleaner. Clean the exterior of the instrument only. Do not apply cl

directly to the instrumen t or allow liqui ds to enter or spi ll on the inst rument. Produ cts tha t consist of a circuit board wi th no case or chassis

(e.g., a data acquisition board for installation into a computer) should never require cleaning if handled according to instructions. If the

board becomes contaminated and operation is affected, the board should be returned to the factory for proper cleaning/servicing.

UTION heading in th e u se r documentation e xp lains hazards that could damage the i nst rum ent . Such damage may inv al ida te the

t leads,

eaner

Table of Contents

1 Routine Maintenance

1.1 Introduction.......................................................................................................................................................1-1

1.2 Line fuse replacement .......................................................................................................................................1-1

1.3 Current fuse replacement ..................................................................................................................................1-2

1.3.1 Front AMPS input fuse............................................................................................................................ 1-2

1.3.2 Rear AMPS input fuse.............................................................................................................................1-2

1.4 Fan filter cleaning .............................................................................................................................................1-3

1.5 Firmware updates..............................................................................................................................................1-3

2 T roubleshooting

2.1 Introduction.......................................................................................................................................................2-1

2.2 Repair considerations........................................................................................................................................2-1

2.3 Power-on test.....................................................................................................................................................2-2

2.4 Front panel tests ................................................................................................................................................2-2

2.4.1 KEYS Test...............................................................................................................................................2-2

2.4.2 DISPLAY PATTERNS Test...................................................................................................................2-3

2.5 Built-in test........................................................................................................................................................2-3

2.5.1AUTOMATIC Testing2-6

2.5.2 MANUAL Testing...................................................................................................................................2-6

2.6 Diagnostics........................................................................................................................................................2-7

2.7 R1_STB and R2_STB shift registers ..............................................................................................................2-11

2.8 Display board checks ......................................................................................................................................2-14

2.9 Power supply checks....................................................................................................................................... 2-14

2.10 Documentation................................................................................................................................................2-15

2.10.1 Display board circuit theory..................................................................................................................2-17

2.10.2 Power supply circuit theory...................................................................................................................2-17

2.10.3 Built-in test documentation ................................................................................................................... 2-18

3 Disassembly

3.1 Introduction.......................................................................................................................................................3-1

3.2 Handling and cleaning precautions...................................................................................................................3-1

3.2.1 PC-board handling...................................................................................................................................3-1

i

3.2.2 Solder repairs........................................................................................................................................... 3-2

3.3 Special handling of static sensitive devices...................................................................................................... 3-2

3.4 Case cover and shield removal ......................................................................................................................... 3-2

3.4.1 Case cover removal................................................................................................................................. 3-2

3.4.2 Analog board top shield removal ............................................................................................................ 3-3

3.5 PC-boards removal ........................................................................................................................................... 3-3

3.5.1 Digital board............................................................................................................................................ 3-3

3.5.2 A/D converter board................................................................................................................................ 3-3

3.5.3 Analog board...........................................................................................................................................3-4

3.6 Front panel disassembly.................................................................................................................................... 3-5

3.7 Cooling fan removal ......................................................................................................................................... 3-5

3.8 Main CPU firmware replacement.....................................................................................................................3-6

3.9 Instrument re-assembly..................................................................................................................................... 3-6

3.10 Assembly drawings........................................................................................................................................... 3-6

4 Replaceable Parts

4.1 Introduction....................................................................................................................................................... 4-1

4.2 Parts lists........................................................................................................................................................... 4-1

4.3 Ordering information........................................................................................................................................4-1

4.4 Factory service.................................................................................................................................................. 4-1

4.5 Component layouts........................................................................................................................................... 4-1

ii

List of Illustrations

1 Routine Maintenance

Figure 1-1 Line fuse location ................................................................................................................................. 1-1

Figure 1-2 Front AMPS input fuse location........................................................................................................... 1-2

Figure 1-3 Rear AMPS input fuse location............................................................................................................ 1-3

2 T roubleshooting

Figure 2-1 Model 2001 overall block diagram..................................................................................................... 2-16

iii

Ω

Ω

Ω

List of Tables

1 Routine Maintenance

Table 1-1 Power line fuse ..................................................................................................................................... 1-2

Table 1-2 Current fuse .......................................................................................................................................... 1-2

2 T roubleshooting

Table 2-1 Built-in-test summary........................................................................................................................... 2-3

Table 2-2 DIAGNOSTICS test modes (all functions except

Table 2-3 DIAGNOSTICS test modes (

Table 2-4 DIAGNOSTICS test modes (

Table 2-5 DIAGNOSTICS bit patterns (DC_STB registers).............................................................................. 2-10

Table 2-6 Bit patterns for R1_STB registers....................................................................................................... 2-12

Table 2-7 Bit patterns for R2_STB registers....................................................................................................... 2-13

Table 2-8 Display board checks.......................................................................................................................... 2-14

Table 2-9 Power supply checks........................................................................................................................... 2-15

Table 2-10 DC_STB control registers................................................................................................................... 2-19

Table 2-11 R1_STB control registers ................................................................................................................... 2-20

Table 2-12 R2_STB control registers ................................................................................................................... 2-21

Table 2-13 Multiplexer (U511)............................................................................................................................. 2-22

4 function; 20 Ω and 200 Ω ranges)..................................................... 2-9

4 function; 2k Ω thru 200k Ω ranges) .................................................. 2-9

4)......................................................................... 2-8

4 Replaceable Parts

Table 4-1 Model 2001 A/D board, parts list......................................................................................................... 4-2

Table 4-2 Model 2001 analog board, parts list ..................................................................................................... 4-5

Table 4-3 Model 2001 digital board, parts list.................................................................................................... 4-15

Table 4-4 Model 2001 display board, parts list................................................................................................... 4-19

Table 4-5 Model 2001 miscellaneous, parts list...................................................................................................4-21

v

OR SERVICABLE PARTS,SERVICE BY QUALIFIED PERSONNEL ONLY.

OR SERVICABLE PARTS,SERVICE BY QUALIFIED PERSONNEL ONLY.

AGAINST FIRE HAZARD,REPLACE FUSE WITH SAME TYPE AND RATING.

1

Routine Maintenance

1.1 Introduction

In general, the information in this section deals with

routine type maintenance that can be performed by the

operator. This information is arranged as follows:

1.2 Line fuse replacement

place a blown line power fuse.

1.3 Current fuse replacement

place a blown current fuse.

1.4 Fan Þlter cleaning

and clean the Þlter element for the cooling fan.

1.5 Firmware updates

action for Þrmware updates provided by Keithley.

Explains how to re-

Explains how to re-

Explains how to remove

Recommends a course of

1.2 Line fuse replacement

WARNING

Disconnect the line cord at the rear

panel. Remove all test leads connected to the instrument (front and rear).

1. Insert a bladed screwdriver into the slot of the fuse

carrier.

2. While pushing in, turn the screwdriver counterclockwise until the spring loaded fuse carrier releases from the fuse holder.

3. Pull out the fuse carrier and replace the fuse with

the type speciÞed in Table 1-1.

CAUTION

To prevent instrument damage, use

only the fuse type speciÞed in Table

1-1.

4. Re-install the fuse carrier.

DIGITAL I/O

IN OUT

TRIGGER

LINK

LINE RATING

90-134VAC

180-250VAC

50, 60, 400HZ

55VA MAX

(CHANGE IEEE ADDRESS

WITH FRONT PANEL MENU)

IEEE-488

LINE FUSE

SLOWBLOW

1/2A, 250V

Line

Fuse

The power line fuse is accessible from the rear panel,

just below the ac power receptacle (see Figure 1-1). Perform the following steps to replace the line fuse:

Figure 1-1

Line fuse location

1-1

Routine Maintenance

NOTE

If the power line fuse continues to

blow, a circuit malfunction exists and

must be corrected. Refer to the troubleshooting section of this manual for

assistance.

Table 1-1

Power line fuse

Keithley

Size Rating

5

×

20mm 250V, ½ A, Slo-Blo FU-71

Part No.

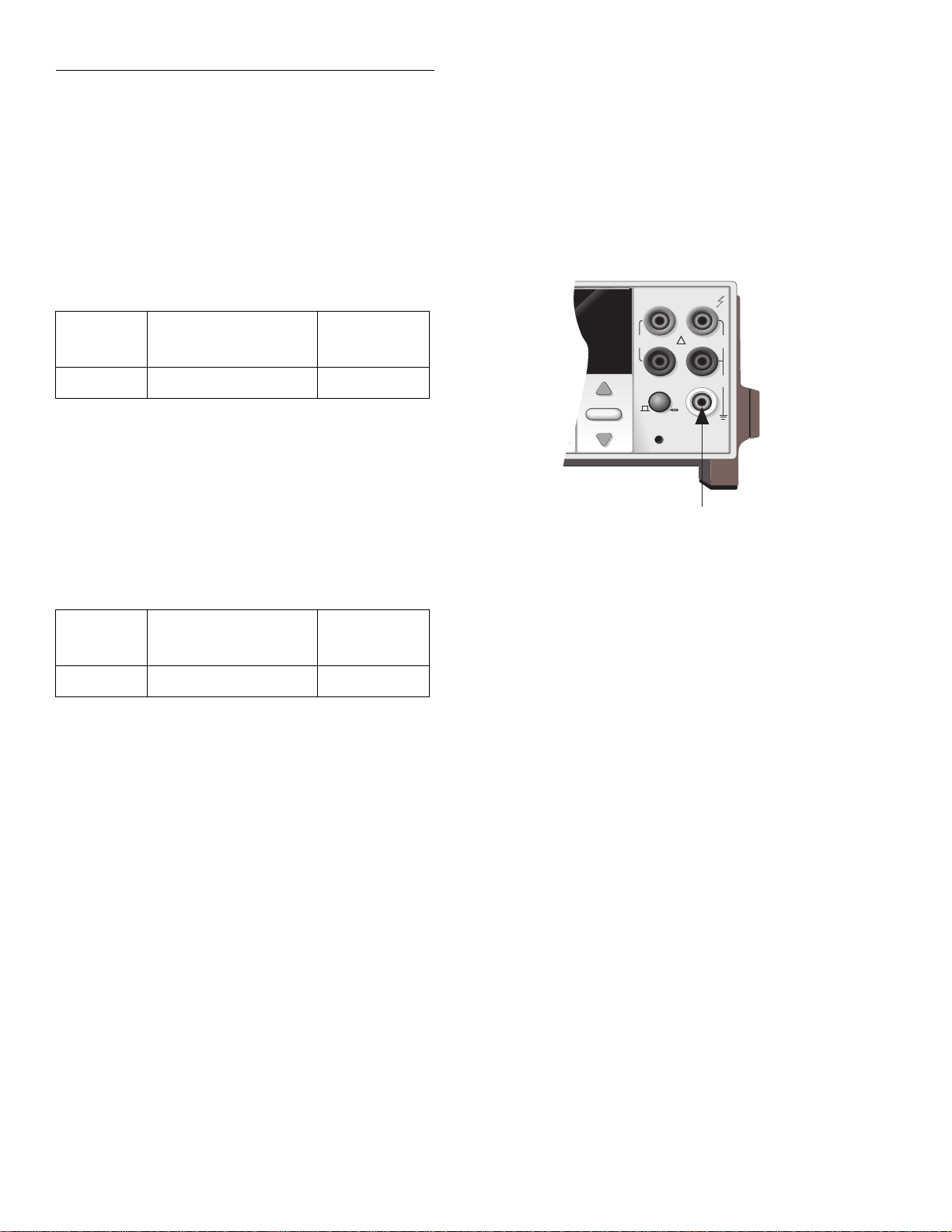

1.3 Current fuse replacement

Each AMPS input (front and rear) has its own current

fuse. When replacing a current fuse, use the type speciÞed in Table 1-2.

CAUTION

To prevent instrument damage, use

only the type speciÞed in Table 1-2.

3. Re-install the fuse carrier.

SENSE

MATH 4W AUTO ARM TRIG SMPL

2001 MULTIMETER

RANGE

AUTO

RANGE

Ω 4 WIRE

350V

PEAK

INPUTS

FR

FRONT/REAR

INPUT

HI

1100V

!

PEAK

LO

500V

PEAK

2A 250V

AMPS

CAL

AMPS

Fuse

Table 1-2

Current fuse

Keithley

Size Rating

5

×

20mm 250V, 2A, Normal-Blo FU-48

Part No.

WARNING

Disconnect the instrument from the

power line and remove all test leads

(front and rear).

1.3.1 Front AMPS input fuse

The front panel AMPS jack functions as the AMPS input terminal and as the carrier for the AMPS fuse (see

Figure 1-2). Perform the following steps to replace the

fuse:

Figure 1-2

Front AMPS input fuse location

1.3.2 Rear AMPS input fuse

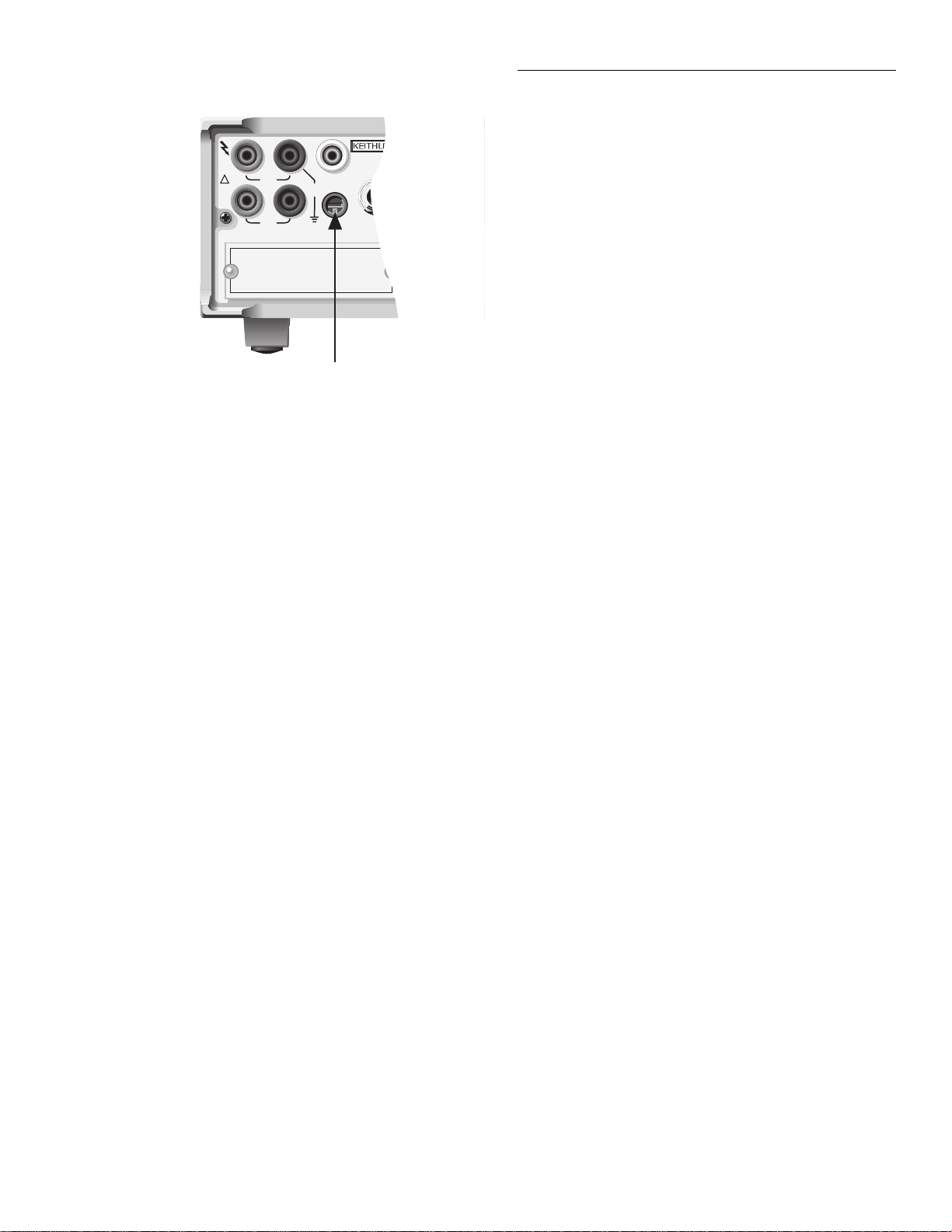

The rear AMPS input fuse is located just below the

AMPS input jack (see Figure 1-3). Perform the following steps to replace the fuse:

1. Insert a bladed screwdriver into the slot of the fuse

carrier.

2. While pushing in, turn the screwdriver counterclockwise until the spring loaded fuse carrier releases from the fuse holder.

3. Pull out the fuse carrier and replace the fuse with

the type speciÞed in Table 1-2.

CAUTION

1. Push in the AMPS input jack and turn counterclockwise until the spring loaded fuse carrier releases from the fuse holder.

2. Pull out the fuse carrier and replace the fuse with

the type speciÞed in Table 1-2.

1-2

To prevent instrument damage, use

only the fuse type speciÞed in Table

1-2.

4. Re-install the fuse carrier.

WARNING:NO INTERNAL OPERATOR SERVICABLE PARTS,SERVIC

WARNING:NO INTERNAL OPERATOR SERVICABLE PARTS,SERVIC

CAUTION:FOR CONTINUED PROTECTION AGAINST FIRE HAZARD,REPLA

CAUTION:FOR CONTINUED PROTECTION AGAINST FIRE HAZARD,REPLA

INPUT

1100V

!

HI LO

PEAK

350V

PEAK

SENSE

Ω 4 WIRE

OPTION SLOT

Figure 1-3

Rear AMPS input fuse location

500V

PEAK

AMPS

2A MAX

AMPS

FUSE

2A, 250V

Amps

Fuse

EXTERNAL

TRIGGER

INPUT

Routine Maintenance

the cover plate.

WARNING

Exercise care when handling the Þlter assembly. The Þlter element is a

metal screen with sharp edges that

could cause injury if not handled

carefully.

The Þlter element is made of a rugged metal screen allowing the use of any type cleaning solution to clean it.

A small metal brush can be used to remove dirt and debris. After cleaning the Þlter, rinse thoroughly with water. Make sure the Þlter assembly is completely dry

before re-installing it.

1.4 Fan filter cleaning

The Þlter for the cooling fan requires periodic cleaning

to maintain proper ventilation. The fan Þlter is accessible from the rear panel. Perform the following steps to

remove the Þlter for cleaning:

1. While facing the rear panel, locate the lower righthand corner of the Þlter cover plate.

2. At this corner, place a thin-bladed screwdriver between the cover plate and the rear panel and gently

pry the Þlter assembly away from the chassis.

The Þlter element is permanently Þxed to the cover

plate. Do not attempt to remove the Þlter element from

1.5 Firmware updates

It is possible that you may receive a Þrmware update

from Keithley to enhance operation and/or Þx ÒbugsÓ.

The Þrmware program for the main microprocessor is

contained in U611 (EPROM). A socket is used on the pc

board for this device to make replacement relatively

easy.

The replacement procedure requires that the case cover

be removed. Also, this surface mount, static-sensitive

device requires special handling. As a result, the Þrmware update should only be performed by qualiÞed

1-3

Routine Maintenance

service personnel. The procedure to replace the Þrmware (U611) is contained in paragraph 3.8.

1-4

2

Troubleshooting

WARNING

The information in this section is intended for qualiÞed service personnel. Some of these procedures may

expose you to hazardous voltages. Do

not perform these hazardous procedures unless you are qualiÞed to do

so.

2.1 Introduction

This section of the manual will assist you in troubleshooting the Model 2001. Included are self-tests, test

procedures, troubleshooting tables and circuit descriptions. It is left to the discretion of the repair technician

to select the appropriate tests and documentation

needed to troubleshoot the instrument.

This section is arranged as follows:

2.2 Repair considerations

ations that should be noted before making any repairs to the Model 2001.

2.3 Power-on test Ñ Describes the tests that are per-

formed on its memory elements every time the

instrument is turned on.

Covers some consider-

2.5 Built-In tests Ñ Provides the procedures to test

and exercise the various circuits on the digital

board, analog board and A/D converter boards.

2.6 Diagnostics Ñ Explains how to use the Diagnos-

tics test mode of the Model 2001. In general, Diagnostics locks-up the instrument in various

states of operation. With the instrument in a static

state, you can then check the state of the various

logic levels on the control registers and signal

trace through the unit.

2.7 R1_STB and R2_STB registers Ñ Provides shift

register bit patterns for the basic measurement

functions and ranges.

2.8 Display board checks Ñ Provides display board

checks that can be made if Front Panel Tests fail.

2.9 Power supply checks Ñ Provides power supply

checks that can be made if the integrity of the

power supply is questioned.

2.10 Documentation Ñ Provides support documen-

tation for the various troubleshooting tests and

procedures. Included is some basic circuit theory

for the display board and power supply, and support documentation for Built-in Test.

2.4 Front panel tests Ñ Provides the procedures to

test the functionality of the front panel keys and

the display.

2.2 Repair considerations

Before making any repairs to the Model 2001, be sure to

read the following considerations.

2-1

Troubleshooting

CAUTION

The PC-boards are built using surface mount techniques and require

specialized equipment and skills for

repair. If you are not equipped and/or

qualiÞed, it is strongly recommended that you send the unit back to the

factory for repairs or limit repairs to

the pc-board replacement level (see

following NOTE).

Without proper equipment and training, you could damage a PC-board

beyond repair.

NOTE

For units that are out of warranty,

completely assembled PC-boards can

be ordered from Keithley to facilitate

repairs.

1. Repairs will require various degrees of disassembly. However, it is recommended that the Front

Panel Tests (paragraph 2.4) and Built-In-Test (paragraph 2-5) be performed prior to any disassembly.

The disassembly instructions for the Model 2001

are contained in Section 3 of this manual.

2. Do not make repairs to surface mount pc-boards

unless equipped and qualiÞed to do so (see previous CAUTION).

3. When working inside the unit and replacing parts,

be sure to adhere to the handling precautions and

cleaning procedures explained in paragraph 3.2.

4. Many CMOS devices are installed in the Model

2001. These static-sensitive devices require special

handling as explained in paragraph 3.3.

5. Anytime a circuit board is removed or a component is replaced, the Model 2001 will have to be

recalibrated.

2.4 Front panel tests

There are two Front Panel Tests; one to test the functionality of the front panel keys and one to test the display. In the event of a test failure, refer to paragraph 2.8

to troubleshoot the display board.

2.4.1 KEYS Test

The KEYS test allows you to check the functionality of

each front panel key. Perform the following steps to

run the KEYS test.

1. Display the MAIN MENU by pressing the MENU

key.

2. Use the or key to place the cursor on TEST

and press ENTER to display the SELF-TEST

MENU.

3. Place the cursor on FRONT-PANEL-TESTS and

press ENTER to display the following menu:

FRONT PANEL TESTS

KEYS DISPLAY-PATTERNS

4. Place the cursor on KEYS and press ENTER to start

the test. When a key is pressed, the label name for

that key will be displayed to indicate that it is functioning properly. When the key is released, the

message ÒNo keys pressedÓ is displayed.

5. Pressing EXIT tests the EXIT key. However, the second consecutive press of EXIT aborts the test and

returns the instrument to the SELF-TEST MENU.

Keep pressing EXIT to back out of the menu structure.

2.4.2 DISPLAY PATTERNS Test

The display test allows you to verify that each pixel

and annunciator in the vacuum ßuorescent display is

working properly. Perform the following steps to run

the display test:

2.3 Power-on test

During the power-on sequence, the Model 2001 will

perform a checksum test on its EPROM (U611 and

U618) and test its RAM (U608, U609, and U610. If one

of these tests fail the instrument will lock up.

2-2

1. Display the MAIN MENU by pressing the MENU

key.

2. Use the or key to place the cursor on TEST

and press ENTER to display the SELF-TEST

MENU.

3. Place the cursor on FRONT-PANEL-TESTS and

press ENTER to display the following menu:

Troubleshooting

FRONT PANEL TESTS

KEYS DISPLAY-PATTERNS

4. Place the cursor on DISPLAY-PATTERNS and

press ENTER to start the display test. There are Þve

parts to the display test. Each time a front panel

key (except EXIT) is pressed, the next part of the

test sequence is selected. The Þve parts of the test

sequence are as follows:

A. Checkerboard pattern (alternate pixels on) and

all annunciators.

B. Checkerboard pattern and the annunciators

that are on during normal operation.

C. Horizontal lines (pixels) of the Þrst digit are se-

quenced.

D. Vertical lines (pixels) of the Þrst digit are se-

quenced.

E. Each digit (and adjacent annunciator) is se-

quenced. All the pixels of the selected digit are

on.

5. When Þnished, abort the display test by pressing

EXIT. The instrument returns to the SELF-TEST

MENU. Keep pressing EXIT to back out of the

menu structure.

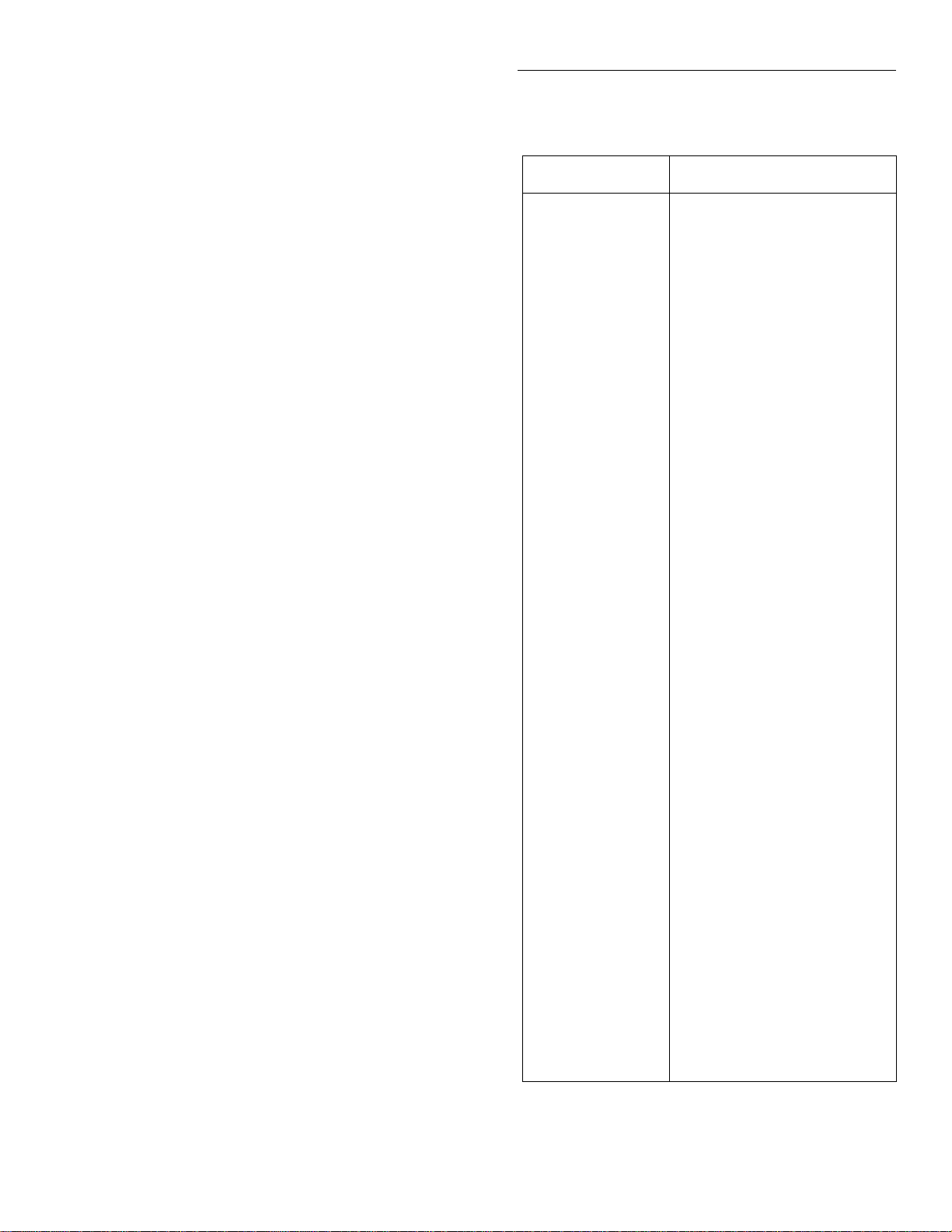

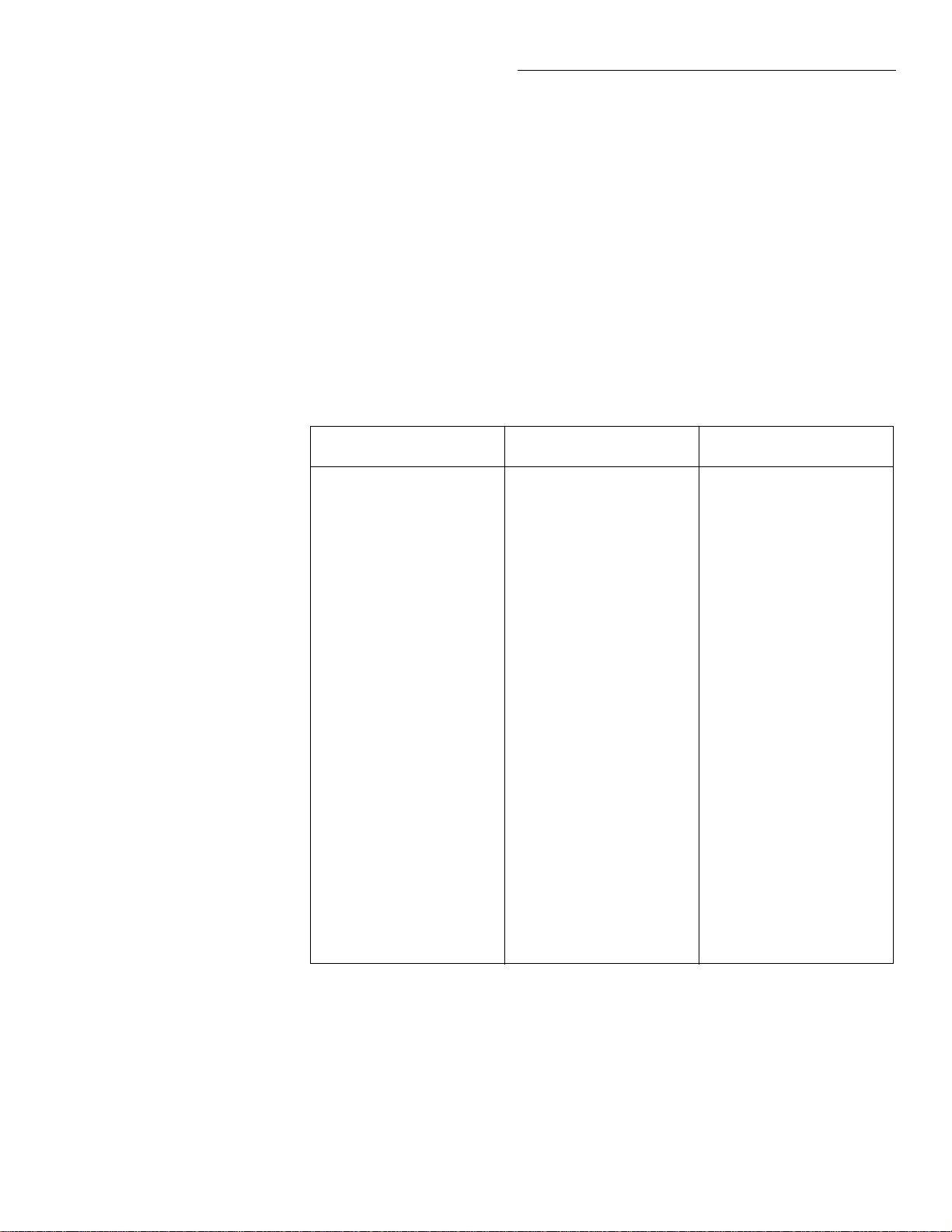

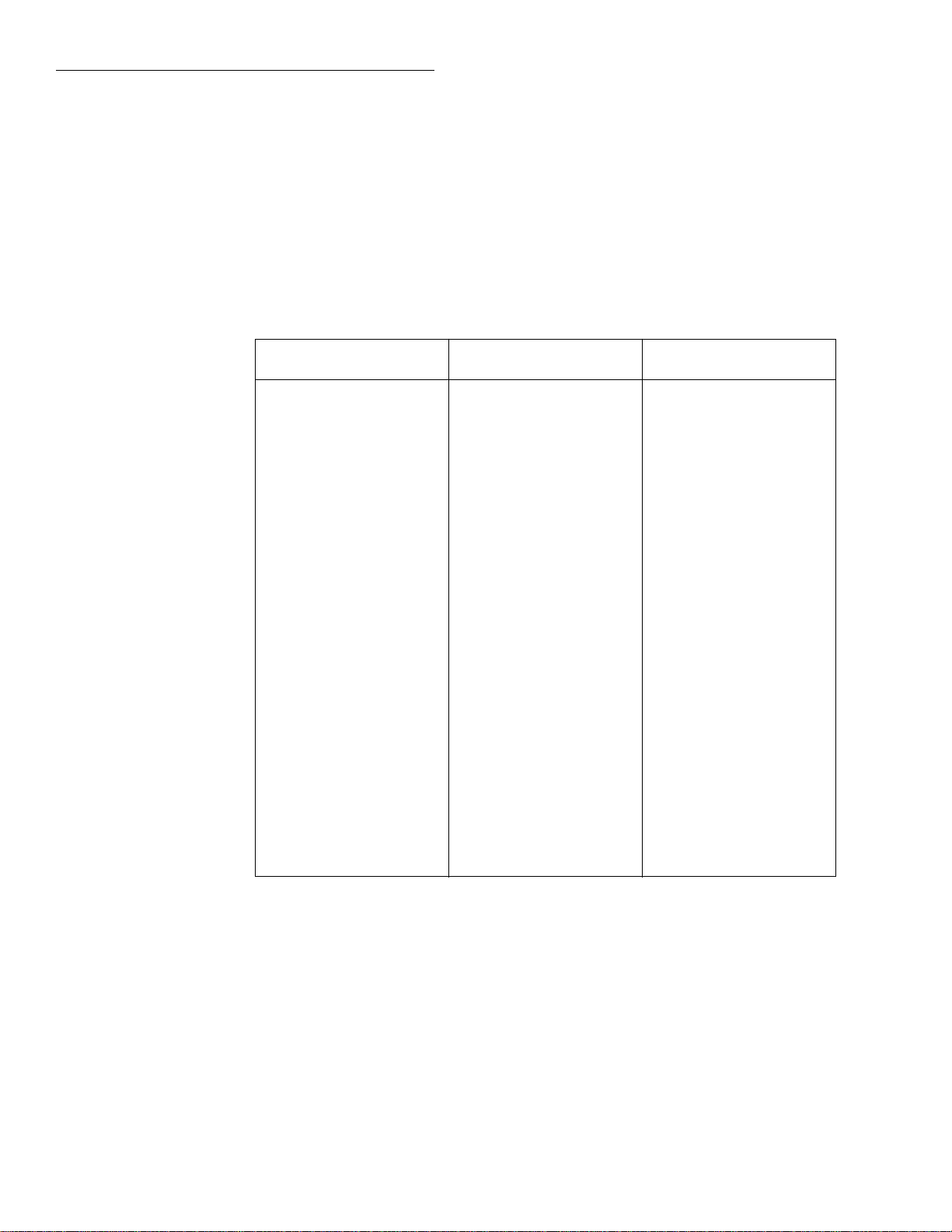

Table 2-1

Built-in-test summary

Test Circuit tested/exercised

100 Series

100.1

101 Series

101.1

102 Series

102.1

103 Series

103.1 - 103.4

103.5

104 Series

104.1

104.2

105 Series

105.1 - 105.6

105.7

Memory:

EPROM

Memory:

RAM

Memory:

2

E

PROM

Digital I/O:

Digital Output

Digital Input

IEEE-488 Bus:

Handshake

Data

Triggers:

System Trigger Bus

External Trigger /Voltmeter Complete

105.8

Group Execute Trigger

(GET)

105.11 - 105.18

Trigger Shorts

2.5 Built-in test

BUILT-IN TEST is used to test and exercise various circuits and components on the digital board, analog

board and A/D converter board. The Built-In Tests are

listed in Table 2-1. Many of the tests are actual pass/fail

type tests, while others are circuit exercises that are

used for subsequent tests. Each Built-In Test can be run

manually. After a test is manually run, operation is

ÒfrozenÓ to allow the technician to troubleshoot the circuit. Troubleshooting documentation for each Built-In

Test is provided in paragraph 2.10.3.

200 Series

200.1

200.2

200.3

200.4

200.5

200.6

200.7

201 Series

201.1

201.2

201.3

300 Series

300.1

300.2

300.3

301 Series

301.1

301.2

A/D Converter:

A/D Zero

A/D Noise

FAST Circuit

x10 Line Cycle Integration

x0.1 Line Cycle Integration

x0.02 Line Cycle Integration

x0.01 Line Cycle Integration

Calibration:

Test Cal Zero

7V Reference

1.75V Reference

A/D Multiplexer (MUX),

A/D Buffer:

7V Reference, x1.5 Gain

1.75V Reference, x5 Gain

0V Reference, x50 Gain

Input Buffer:

Front End (FE) Zero

Divide by 100

2-3

Troubleshooting

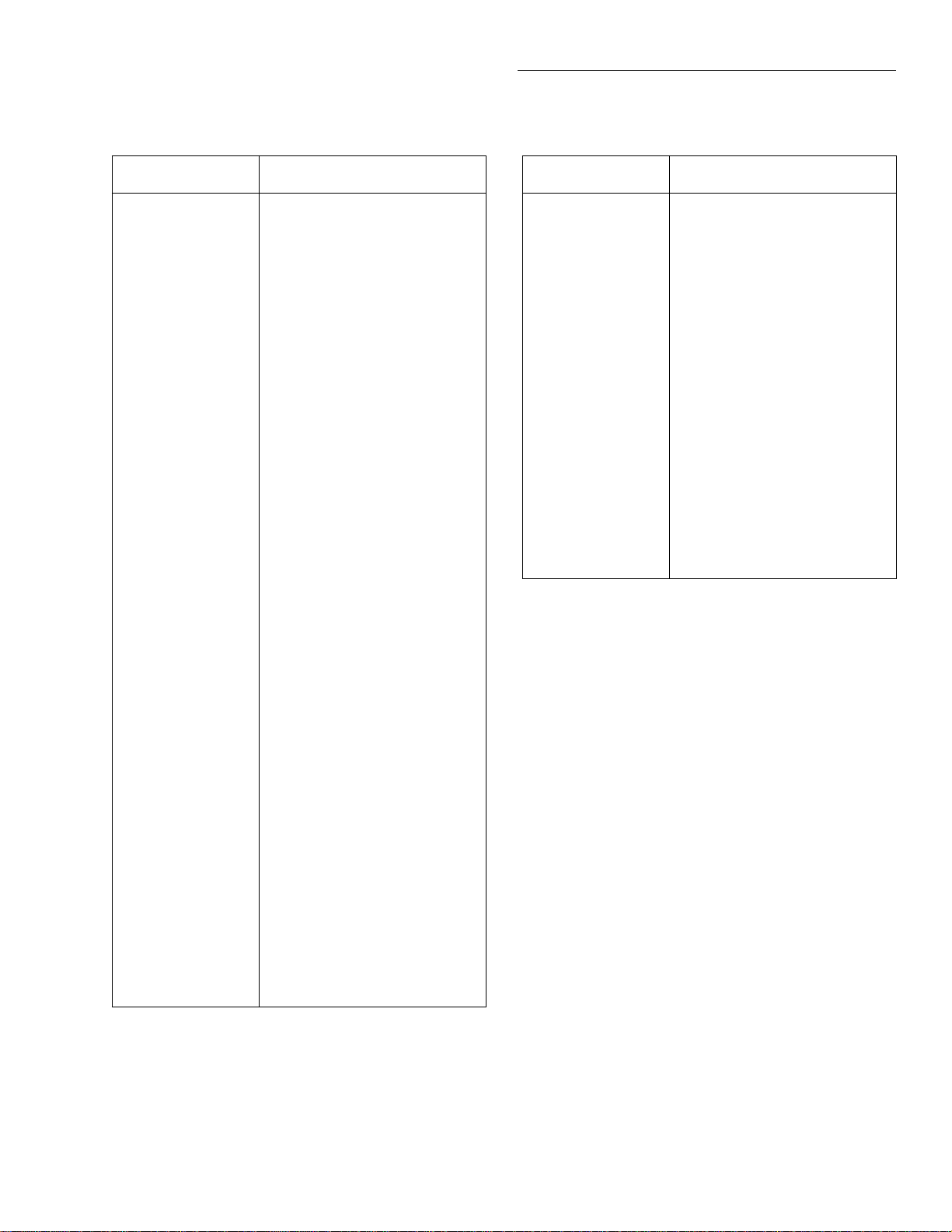

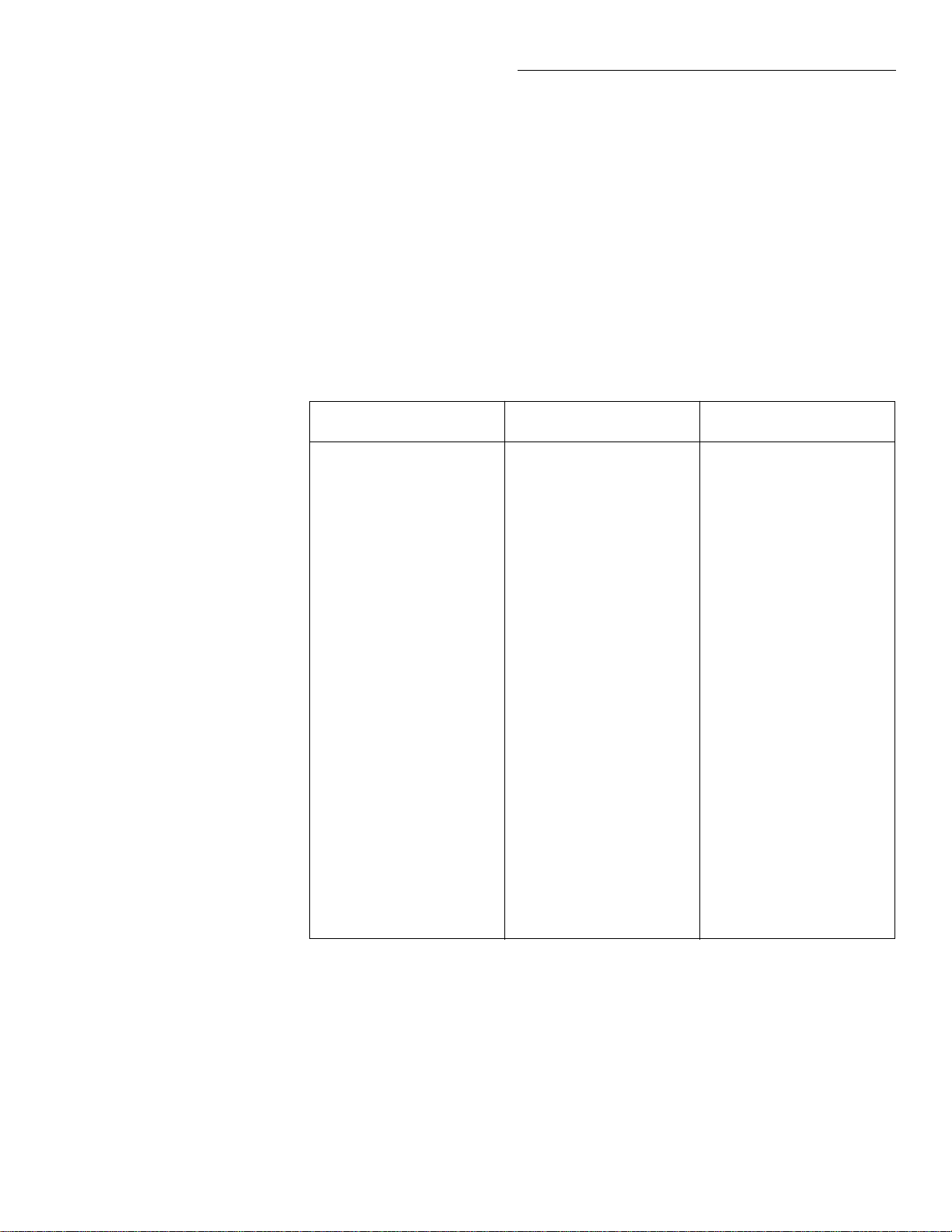

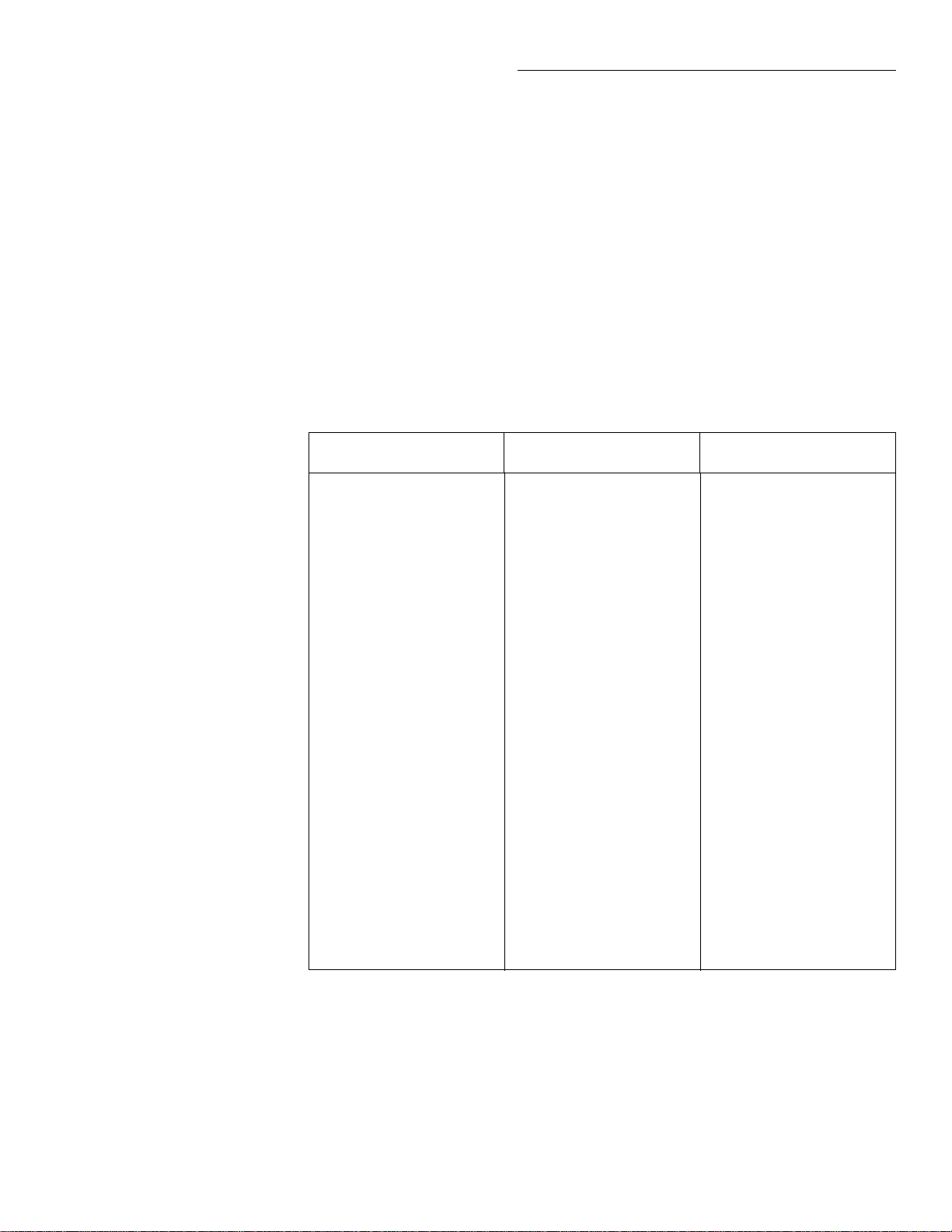

Table 2-1 (cont.)

Built-in-test summary

Test Circuit tested/exercised

302 Series

302.1

Ohms:

Zero Reference Measurement (for next test)

302.2

Open Circuit Ohms and

Ohms Protection

303 Series

303.1

Input Path:

Zero Reference Measurement (for next test)

303.2

Open Circuit Ohms and

Ohms Protection

303.3

Front End (FE) Zero Protection

304 Series

304.1

Ohms Sources:

Zero Reference Measurement (for tests 304.2 -

304.7)

304.2

0.98mA and 9.2mA Ohms

Sources

304.3

89

µ

A and 0.98mA Ohms

Sources

304.4

7

µ

A and 89

µ

A Ohms

Sources

304.5

770nA and 7

µ

A Ohms

Sources

304.6

70nA and 770nA Ohms

Sources

304.7

4.4nA and 770nA Ohms

Sources

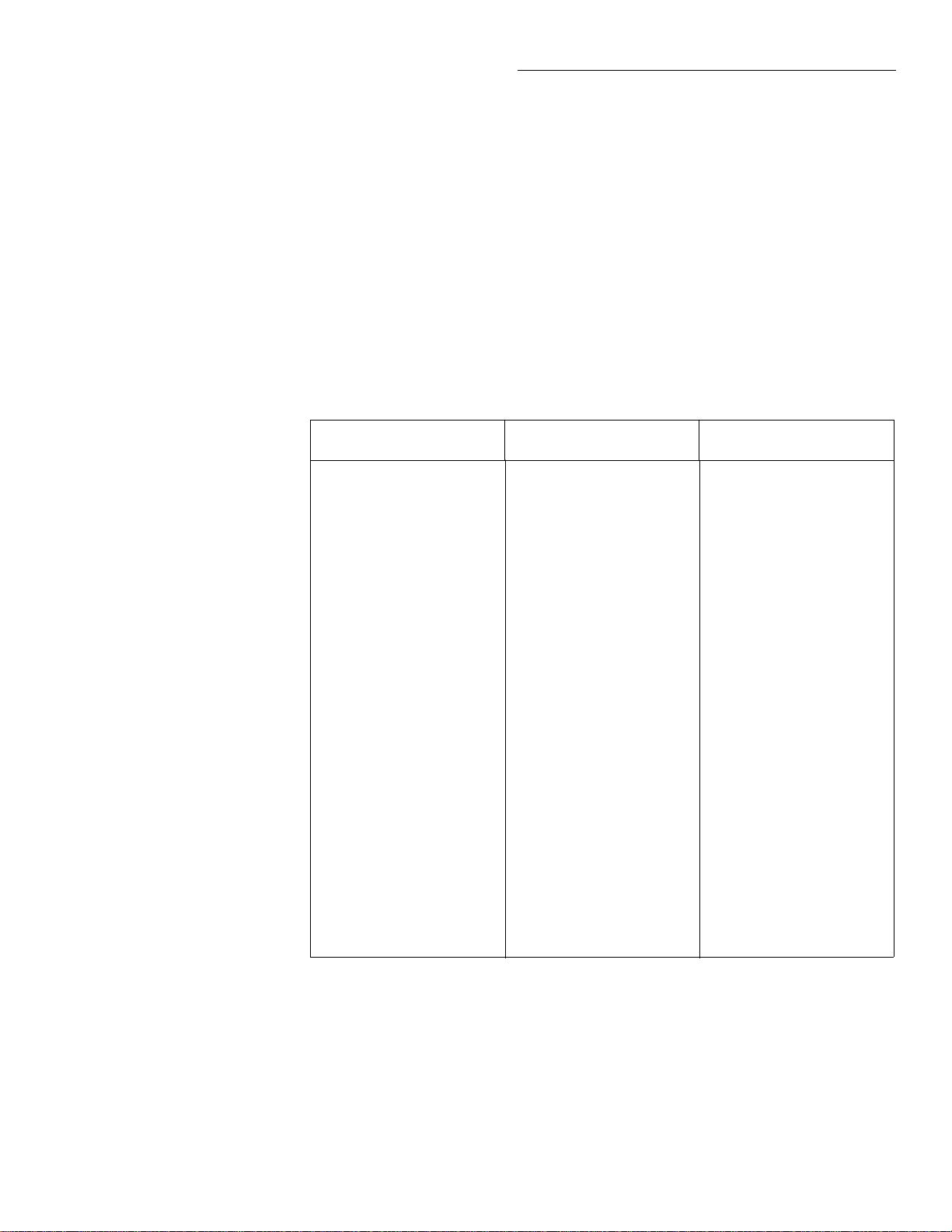

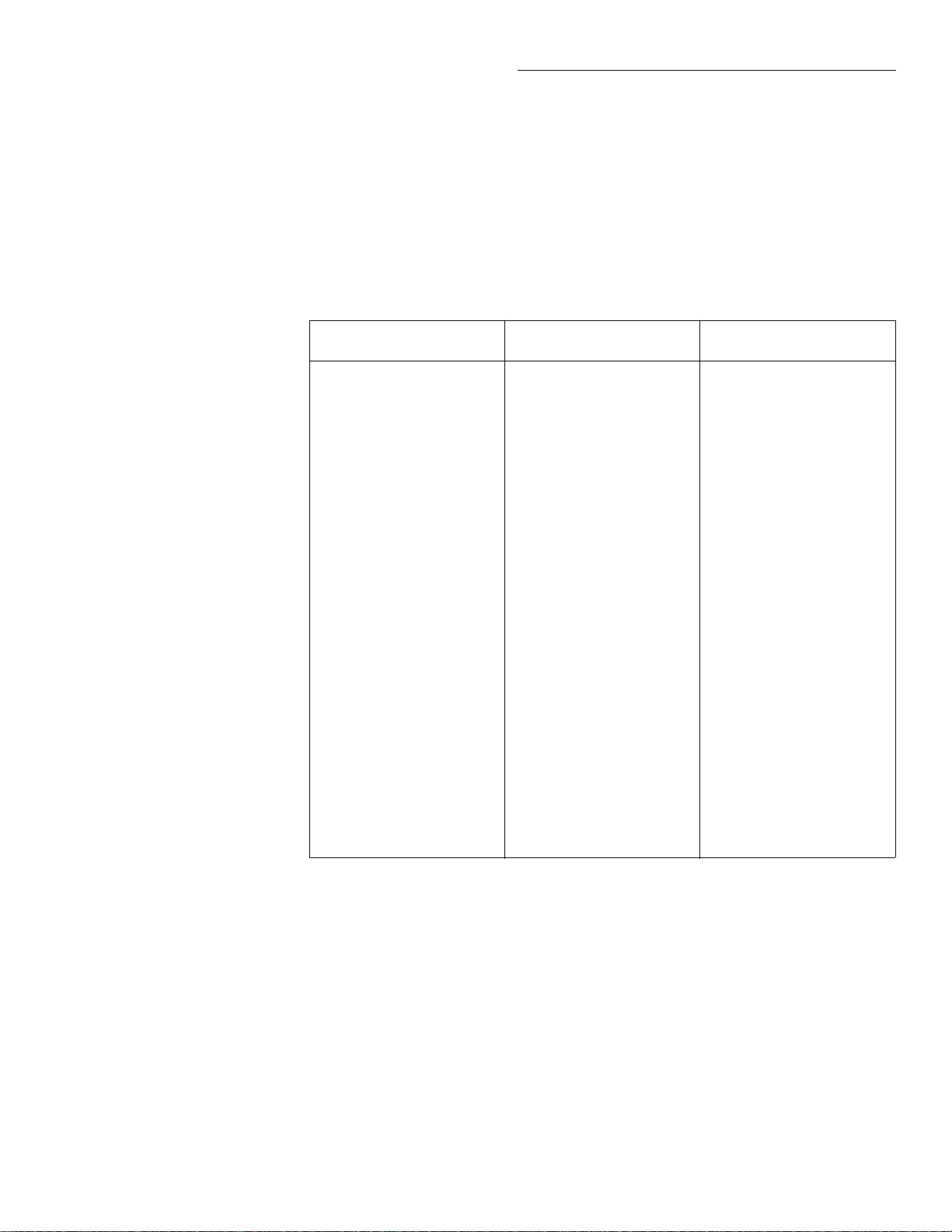

Table 2-1 (cont.)

Built-in-test summary

Test Circuit tested/exercised

308 Series

308.1

4-Digit Mode:

A/D MUX 4-Digit Signal

Path

308.2

A/D MUX 4-Digit Zero

Path

309 Series

309.1

309.2

309.3

309.4

Amps:

A Range

200

µ

2mA Range

20mA Range

Reference Measurement

(for tests 309.5 and 309.6)

309.5

309.6

310 Series

310.1

400 Series

200mA Range

2A Range

Protection:

Amps Protection

Digital-to-Analog Converter

(DAC):

400.1

400.2

400.3

400.4

400.5

401 Series

401.1

402 Series

402.1

-4.21V Output

-2.08V Output

-0.001V Output

+2.25V Output

+4.33V Output

Signal Switching:

Zero Cal Switch

Signal Switching:

Frequency Switch

305 Series

305.1

305.2

306 Series

306.1

307 Series

307.1

307.2

307.3

2-4

Input Divider:

Zero Reference Measurement (for next test)

Divide by 100

Switching:

Ohms Cal Switch

Cal Divider:

Zero Reference Measurement (for next test)

A/D MUX /10

A/D MUX /Buffer (x-0.5)

403 Series

403.1

404 Series

404.1

404.2

404.3

404.4

404.5

Signal Switching:

Ground Switch

Absolute Value (x1 Gain):

-Full Scale DAC Output

-Half Scale DAC Output

Zero DAC Output

+Half Scale DAC Output

+Full Scale DAC Output

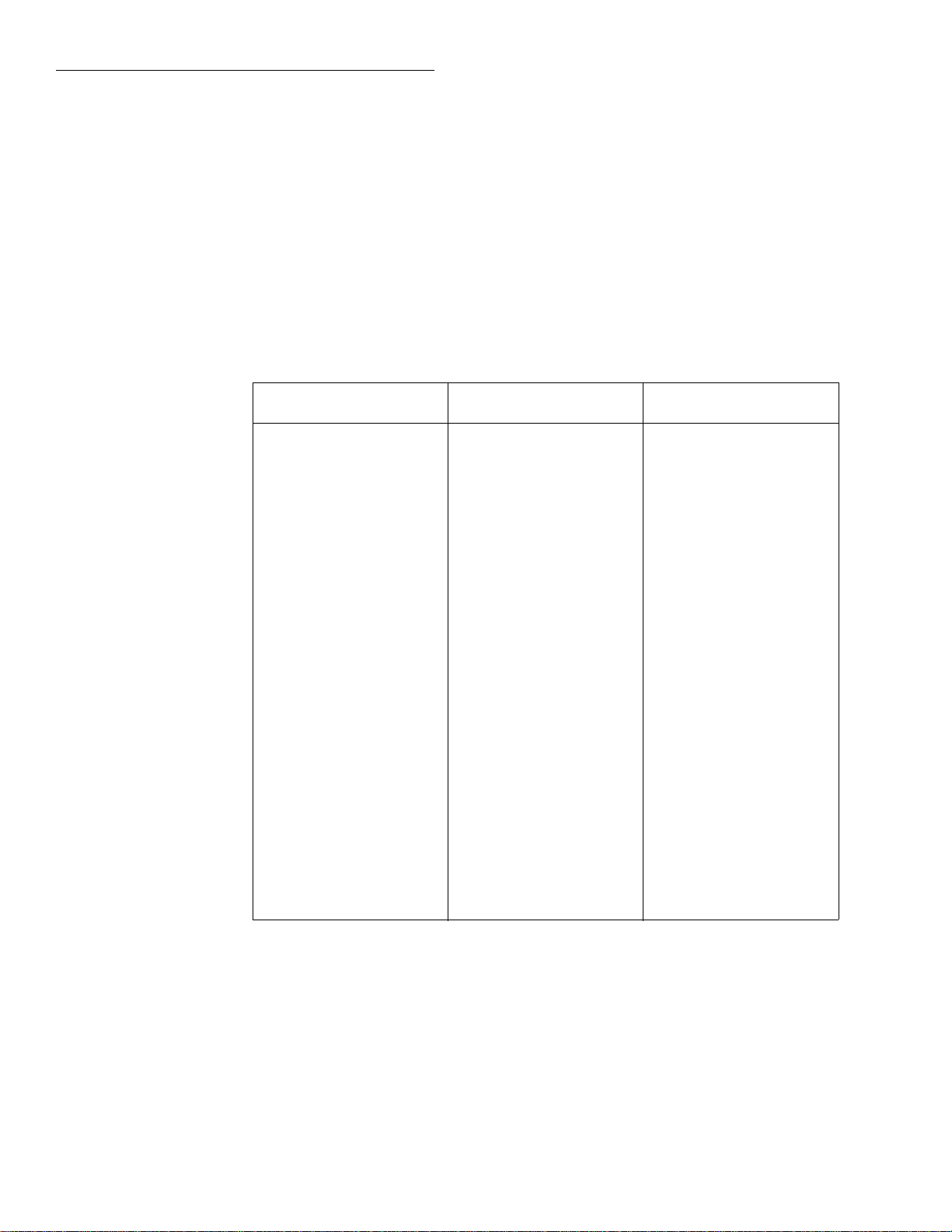

Troubleshooting

Table 2-1 (cont.)

Built-in-test summary

Test Circuit tested/exercised

405 Series

405.1

405.2

405.3

405.4

405.5

405.6

405.7

405.8

406 Series

406.1

406.2

406.3

406.4

406.5

406.6

407 Series

407.1

407.2

407.3

408 Series

408.1

408.2

408.3

408.4

408.5

408.6

Absolute Value (x10 Gain):

Gain Comparison (Large

+DAC Output)

Gain Comparison (Large

+DAC Output)

Gain Comparison (Small

+DAC Output)

Gain Comparison (Small

+DAC Output)

Gain Comparison (Small

-DAC Output)

Gain Comparison (Small

-DAC Output)

Gain Comparison (Large

-DAC Output)

Gain Comparison (Large

-DAC Output)

Test Buffer:

Measure DAC Output (for

test 406.6)

Test Buffer Output (-1.13V)

Read Test Buffer (for test

406.6)

Read DAC Output (for test

406.6)

Test Buffer Output (-0.01V)

Voltage Comparisons

Front End:

2V Range

200V Range

750V Range

/200 Correction Factor:

Circuit Setup (for next test)

Signal Stored (for next test)

Setup (for test 408.5) and

Measurement (for test

408.6)

Same as Test 408.3 but no

measurement.

Signal Stored (for next test)

Signal Comparisons

Table 2-1 (cont.)

Built-in-test summary

Test Circuit tested/exercised

409 Series

409.1

409.2

409.3

409.4

409.5

409.6

410 Series

410.1

411 Series

411.1

411.2

412 Series

412.1

/750 Correction Factor:

Circuit Setup (for next test)

Signal Stored (for next test)

Setup (for test 409.5) and

Measurement (for test

409.6)

Same as Test 409.3 but no

measurement.

Signal Stored (for next test)

Signal Comparisons

Converter:

TRMS Converter

Filters:

TRMS Filter

Variable Gain AmpliÞer

Filter

Switching:

AC Amps Switch

Typical Way To Use BUILT-IN-TEST

1. Run the AUTOMATIC Built-In-Test as explained in

paragraph 2.5.1 and note the Þrst (lowest numbered) test that has failed. You should always address the lowest numbered test failure Þrst because

that failure could cause subsequent tests to fail.

2. Familiarize yourself with the failed circuit. Documentation for the Built-In Tests are provided in

paragraph 2.10.3. Be sure to read the documentation for the complete series. For example, if test

200.4 fails, read the documentation for all 200 series tests (200.1 through 200.7). Note that the documentation directs you to the appropriate

schematic(s) for the circuit.

3. Manually run the test that failed as explained in

paragraph 2.5.2. Keep in mind that many of the

pass/fail type tests require that one or more circuit

exercise tests be run Þrst. Using the manual step

looping mode will ÒfreezeÓ instrument operation

after a test is run.

4. After manually running the test, use the test documentation and your troubleshooting expertise to

locate the problem.

2-5

Troubleshooting

5. After repairing the instrument, start again at step 1

to check the integrity of the repair and to see if

there are any other failures.

2.5.1 AUTOMATIC Testing

1. Display the MAIN MENU by pressing the MENU

key.

2. Use the or key to place the cursor on TEST

and press ENTER to display the SELF-TEST

MENU.

3. Place the cursor on BUILT-IN-TEST and press ENTER to display the following menu:

BUILT-IN TEST

AUTOMATIC MANUAL

4. Place the cursor on AUTOMATIC and press ENTER. The following prompt is displayed:

CONTINUOUS REPEAT?

NO YES

The star (*) is only displayed if a failure occurs.

7. If all the tests passed (no star displayed), use the

EXIT key to back out of the menu structure. Otherwise, press ENTER to display the test number of

the Þrst failure. You can display any additional failures by using the and keys. With a failed test

displayed, pressing the INFO key provides an abbreviated description of the failure. Paragraph 2.10

provides detailed documentation for troubleshooting the defective circuit. When Þnished, use EXIT

to back out of the menu structure.

2.5.2 MANUAL Testing

1. Display the MAIN MENU by pressing the MENU

key.

2. Use the or key to place the cursor on TEST

and press ENTER to display the SELF-TEST

MENU.

3. Place the cursor on BUILT-IN-TEST and press ENTER to display the following menu:

In the non-repeat mode (NO), the testing process

stops after all tests have been performed one time.

In the continuous repeat mode (YES), the testing

process loops around and repeats indeÞnitely until

the EXIT key is pressed to stop the tests.

5. Place the cursor on the desired repeat mode selection (NO or YES) and press ENTER to start the testing process. The instrument displays the number

of the test being run. An ÒAÓ on the display indicates that the tests are being run automatically in

the non-repeat mode. An ÒACÓ indicates that the

tests are being run automatically in the continuous

repeat mode. If a failure occurs, a star (*) appears at

the right hand end of the display and remains on

for the remainder of the tests.

6. If the non-repeat mode is selected, the testing process automatically stops when all the tests have

been performed. If the continuous repeat mode is

selected, you will have to manually stop the testing

process by pressing EXIT. When EXIT is pressed,

all the tests in a series already started will be allowed to Þnish.

When the testing process stops, the following message is displayed:

All tests complete *

Press ENTER to review or EXIT

BUILT-IN TEST

AUTOMATIC MANUAL

4. Place the cursor on MANUAL and press ENTER to

display the currently selected test series number.

Test number: 100

This test number indicates that the 100 series tests

can be performed. In this case there is only one test;

test 100.1.

5. Use the or to display the desired test series

number. For example, if you wish to run test 200.5,

display the series 200 test number.

Test number: 200

6. With the desired test series number displayed,

press ENTER. The following menu displayed:

SELECT LOOPING

SINGLE CONTINUOUS STEP

7. Place the cursor on the desired looping selection

and press ENTER.

A. SINGLE Looping performs all the tests in the

speciÞed series. The instrument displays the

number of the test being run, and an ÒMÓ is dis-

2-6

Troubleshooting

played to indicate that the tests are being run in

the manual single looping mode. If a failure occurs, a star (*) appears at the right hand end of

the display and remains on for the remainder

of the tests in the series. This testing process automatically stops after the last test in the series

is completed. This test process can also be

stopped by pressing EXIT. When EXIT is

pressed, any test in process will be allowed to

Þnish before aborting the testing process.

B. CONTINUOUS looping continuously repeats

all the tests in the speciÞed series until the testing process is manually stopped. During testing, the ÒMCÓ message is displayed to indicate

that tests are being run in the manual continuous looping mode. If a failure occurs, a star (*)

appears at the right hand end of the display

and remains on for the remainder of the tests in

the series. This test process can be stopped by

pressing EXIT. When EXIT is pressed, any test

in process will be allowed to Þnish before

aborting the testing process.

C. STEP looping is used to perform one test at a

time. Each press of the ENTER key performs

the displayed test. The ÒMSÓ message is displayed to indicate that tests are being run in the

manual step looping mode. If a failure occurs,

a star (*) appears at the right hand end of the

display and remains on for the remainder of

the tests in the series. The instrument automatically aborts the testing process after the last

test in the series is run. If you do not wish to

run all the tests in the series, simply press EXIT

after the desired test is run.

8. After the testing process is stopped, the following

message is displayed:

All tests complete *

Press ENTER to review or EXIT

The star (*) is only displayed if a failure occurs.

9. In the event of no test failures, press any key to return to the BUILT-IN TEST menu. If you wish to

run more tests, repeat steps 4 through 8.

In the event of a failure, press ENTER to display

the Þrst test that failed. Other test failures can be

displayed by using the and keys. The INFO

key can be used to provide a brief summary of each

displayed test failure. Paragraph 2.10.3 provides

detailed documentation for troubleshooting the

defective circuit. When Þnished, press EXIT to re-

turn to the BUILT-IN TEST menu. If you wish to

run more tests, repeat steps 4 through 8.

10. When Þnished with BUILT-IN TEST, use the EXIT

key to back out of the menu structure.

2.6 Diagnostics

The Model 2001 has diagnostic test modes which allow

you to ÒfreezeÓ instrument operation to allow you to

check logic levels on the DC_STB control registers

(U303, U300, U800 and U801). The known bit pattern at

these registers can then be used for signal tracing

through the unit. Table 2-10 provides a brief description of each register bit.

Perform the following steps to use DIAGNOSTICS:

1. Select the desired function and range to be

checked. Note that there are no range selections for

FREQ and TEMP.

2. Display the MAIN MENU by pressing the MENU

key.

3. Using the or key to place the cursor on TEST

and press ENTER to display the SELF-TEST

MENU.

4. Place the cursor on DIAGNOSTICS and press ENTER. The Þrst diagnostic test mode (Signal Phase

or Ohms Sense High) is selected (displayed).

5. Perform the following steps to determine the bit

pattern at the control registers:

A. Refer to one of the following DIAGNOSTIC

Test Modes tables to determine the bit pattern

designator (A through X) for the selected function/range:

Table 2-2 Ñ All functions except

Table 2-3 Ñ

Table 2-4 Ñ

ranges

B. Once the bit pattern designator is determined,

use Table 2-5 to determine the logic state of

each register bit.

Example: Assume the 20VDC range is selected

and the instrument is in the ÒSignal PhaseÓ of

DIAGNOSTICS. From Table 2-2, the bit pattern

designator is C. Table 2-5 provides the logic

states for bit pattern C.

6. Use the cursor keys to select the other diagnostic

test modes. The key scrolls forward through the

Ω

4 function; 20

Ω

4 function, 2k

Ω

and 200

Ω

, 20k

Ω

4

Ω

Ω

and 200k

ranges

Ω

2-7

Troubleshooting

test modes and the key scrolls backward.

Again, use the appropriate tables to determine the

bit pattern at the control registers.

7. When Þnished, press EXIT three times to back out

Table 2-2

DIAGNOSTICS test modes (all functions except Ω4)

Test mode Selected function Selected range Bit pattern

Signal Phase DCV 200mV

ACV, ACI and FREQ All E

DCI All F

Ω220Ω, 200Ω

TEMP RTD (open input) Ñ H

of the menu structure and return to the normal

measurement mode of operation.

8. If you wish to check another function/range, repeat steps 1 through 7.

designator*

A

2V, 200V

20V

1000V

B

C

D

G

2kΩ-200MΩ

1GΩ

H

I

TEMP TC Ñ B

7V div by 1 * 1 All (except Ω4) All J

7V div by 1 * 1.5 All (except Ω4) All K

2V div by 1 * 5 All (except Ω4) All L

0V div by 1 * 1 All (except Ω4) All M

0V div by 1 * 5 All (except Ω4) All N

0V div by 1 * 50 All (except Ω4) All O

0V div by 1 * 1.5 All (except Ω4) All P

FE zero for 200mV All (except Ω4) All Q

FE zero for 2V All (except Ω4) All R

*Bit patterns are provided in Table 2-5.

2-8

Troubleshooting

Table 2-3

DIAGNOSTICS test modes (

and 200

Ω

ranges)

Ω

4 function; 20

Test mode Bit pattern

designator*

Ohms sense high G

7V div by 1 * 1 P

7V div by 1 * 1.5 Q

2V div by 1 * 5 R

0V div by 1 * 1 S

0V div by 1 * 5 T

0V div by 1 * 50 U

0V div by 1 * 1.5 V

Ohms sense minus W

FE zero for 2V X

*See Table 2-5 for bit patterns.

Table 2-4

Ω

DIAGNOSTICS test modes (

thru 200k

Ω

ranges)

Ω

4 function; 2k

Ω

Test mode Bit pattern

designator*

Ohms sense high H

7V div by 1 * 1 P

7V div by 1 * 1.5 Q

2V div by 1 * 5 R

0V div by 1 * 1 S

0V div by 1 * 5 T

0V div by 1 * 50 U

0V div by 1 * 1.5 V

FE zero for 200mV W

Ohms sense minus X

*See Table 2-5 for bit patterns.

2-9

Troubleshooting

Registers

U303 U300 U800 U801

Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1

D XX111110 01110111 01010101 01000100

E XX101101 01111111 01010101 01000100

F XX011011 01111111 01010101 01000100

B XX111101 01110111 01010101 01000100

C XX111111 00011110 01010101 01000100

A XX111011 01110111 01010101 01000100

Bit

DIAGNOSTICS bit patterns (DC_STB registers)

Table 2-5

pattern

G XX111011 01110111 11010101 01000100

H XX111101 01110111 11010101 01000100

I XX111110 01110111 11010101 01000100

J XX111110 01111011 01101010 10000100

K XX111111 01011011 01010101 01000100

L XX110101 01111111 01101010 10000100

M XX111110 00111111 01010101 01000100

N XX111101 00111111 01101010 10000100

O XX111011 00111111 01010101 01000100

P XX111111 00011111 01101010 10000100

Q XX111011 11110101 01010101 01000100

R XX111101 11110101 01101010 10000100

S 00111110 00111111 01101010 01010101

T 00111101 00111111 01010101 10101110

U 00111011 00111111 01101010 01010101

V 00111110 00011111 01010101 10101110

W 00111011 11110100 01101010 01010101

X 00111101 11110101 01010101 10101110

2-10

Troubleshooting

2.7 R1_STB and R2_STB shift registers

Table 2-6 and Table 2-7 are provided to allow you to

check logic levels on the R1_STB and R2_STB shift registers (U302, U305, U307, U501, U530, U500 and U505)

for each basic measurement function (DCV, ACV, DCI,

ACI,

Ω

2 and

Ω

4) and range. The known bit pattern at

these registers can then be used for signal tracing

through the unit. Tables 2-11 and Table 2-12provide a

brief description of each register bit.

To use these tables, simply place the instrument in the

designated function and range and check the output of

the shift registers for the indicated bit pattern. The bit

patterns in these tables assume the following conditions:

NPLC > 0.01

AC Type = RMS or Average

Offset Compensated Ohms = Off

Current Measurement Mode = Normal (No In-Circuit I)

2-11

Troubleshooting

10011010

11011010

11011010

11011010

11011010

11011010

11011010

11011010

11011010

11011010

11011010

11011010

10011000

10011001

10011010

10011011

00011011

10011011

10011011

11011100

11011101

11011110

11011111

11110100

11000000

U302 U305 U307

01111111

01111111

Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1

200V, 1000V

DCV 200mV-20V

Function Range Registers

Bit patterns for R1_STB registers

Table 2-6

ACV All 01111111 11000000 11111010

11000000

01111010

DCI 200µA

11000000

11000000

01110110

01101110

2mA

20mA

11000000

11000000

01011110

00111111

200mA

2A

11000000

01111010

ACI 200µA

11000000

11000000

01110110

01101110

2mA

20mA

11000000

11000000

01011110

00111110

200mA

2A

11110110

01111111

Ω220Ω

11110110

01111111

200Ω, 2kΩ

11110110

01111111

20kΩ

11110110

01111111

200kΩ

11111110

01111111

2MΩ

11111110

01111111

20MΩ

01111110

01111111

200MΩ, 1GΩ

10110010

01111111

Ω420Ω

10110010

01111111

200Ω, 2kΩ

10110010

01111111

20kΩ

10110010

01111111

200kΩ

2-12

Table 2-7

Bit patterns for R2_STB registers

Registers

U501 U530

Function Range

DCV All 0110101000000000

ACV 200mV

2V

20V

200V

750V

DCI All 0110101000000000

ACI All 0110000110000000

Ω2, Ω4 All 0110101000000000

Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1

01110001

01110001

01110001

01110001

01110001

10000000

10000000

10000000

10000000

10000000

Registers

Troubleshooting

U500 U505

Range Range

DCV All 10100011 00000111

ACV 200mV

2V

20V

200V

750V

DCI All 10100111 00011111

ACI All 11101111 01001111

Ω2, Ω4 All 10100011 00000111

Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1

11101101

11101001

11101110

11101110

11101010

10011111

10111111

00011110

00011110

00011110

2-13

Troubleshooting

2.8 Display board checks

If the FRONT PANEL TESTS (paragraph 2.4) indicate

that there is a problem on the display board, use Table

2-8.

Circuit theory for the display is provided in paragraph

2.9.1.

Table 2-8

Display board checks

Step Item/component Required condition Remarks

1 FRONT PANEL TESTS Verify that all pixels operate Use SELF-TEST MENU selection

2 P1033, pins 4, 6, 14 and 16 5VAC, ±0.3VAC VFD Þlament

2.9 Power supply checks

Power supply problems can be checked out using Table 2-9.

3 P1033, pin 5 +5V, ±5% Digital +5V supply

4 P1033, pin 9 +60V, ±10% VFD +60V supply

5 P1033, pin 12 Goes low brießy on power-up,

then goes high

6 P1033, pin 2 4MHz square wave Controller 4MHz clock

7 P1033, pin 8 Pulse train every 1msec Control from main processor

8 P1033, pin 10 Brief pulse train when front

panel key is pressed

Microcontroller RESET line

Key down data sent to main processor.

2-14

Table 2-9

Power supply checks

Step Item/component Required condition Remarks

1 F100 line fuse Check continuity Remove to check

Troubleshooting

2 Line power Plugged into live receptacle,

power on

3 U108, pin 3 +5V, ±5% Reference to Common 3

4 U107, pin 3 +15V, ±0.75V Reference to COM

5 U102, pin 3 -15V, ±0.75V Reference to COM

6 CR109, +BS +34V to +38V Reference to Common 3

7 CR110, -BS -34V to -38V Reference to Common 3

8 U103, pin 3 ~+18V Reference to Isolated Common

9 U103, pin 2 +8V Reference to Isolated Common

10 U619, +5VC +5V, ±5% Reference to Digital Common

11 U629, pin 3` +5V, ±5% Reference to Digital Common

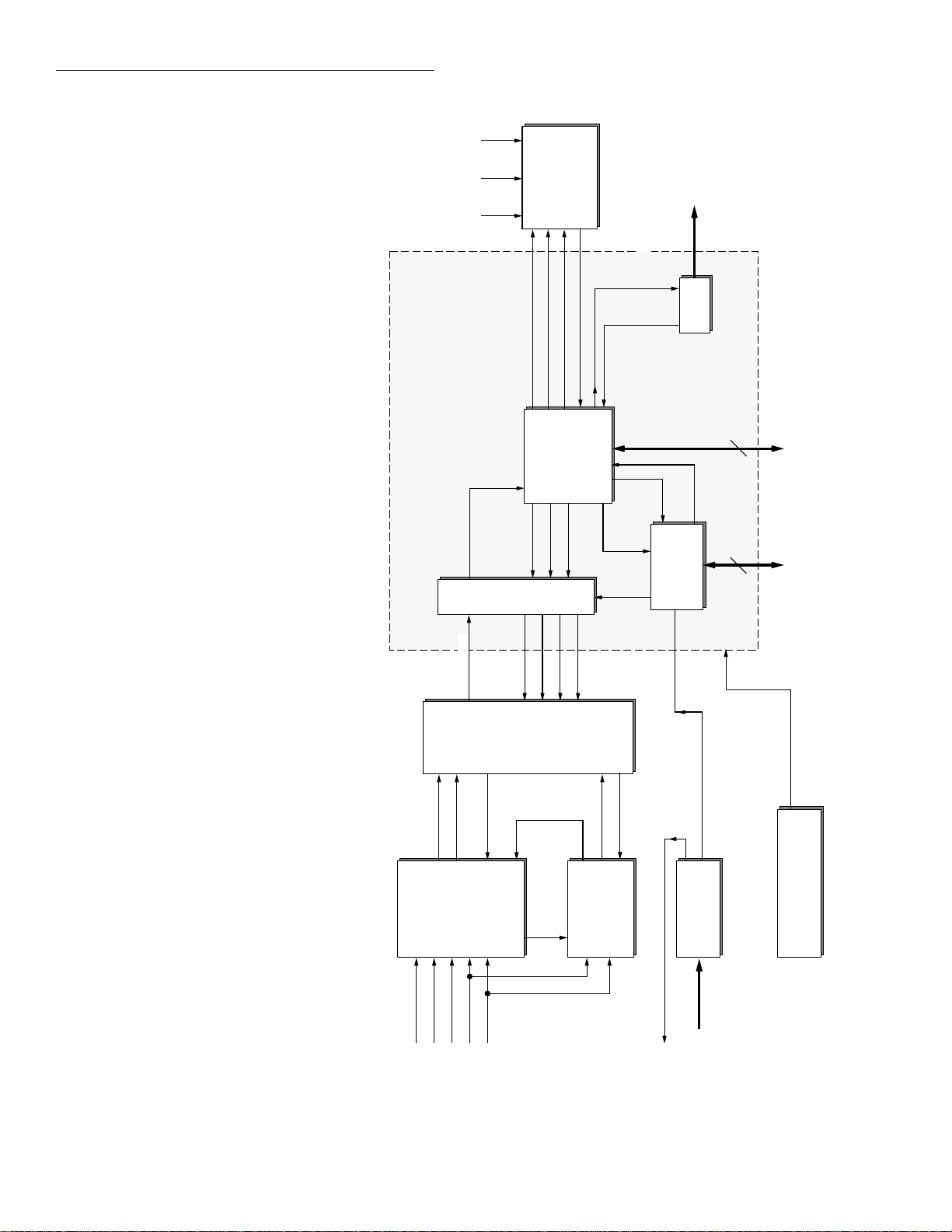

2.10 Documentation

The following information is provided to support the

troubleshooting tests and procedures previously covered in this section of the manual. Figure 2-1 provides

an overall block diagram of the Model 2001 showing

the major circuit groups. Most circuits in the Model

2001 are tested and/or exercised by Built-in Test. A

short description for each of these tests explains how

that particular circuit operates. The display board and

the power supply are not tested by Built-in Test. Thus,

some basic theory is provided for these circuits in paragraphs 2.10.1 and 2.10.2.

Check for correct power up

sequence

2-15

Troubleshooting

Digital

55 Vdc 5 Vdc 5.5 Vac

Front

Panel

Controller

Front Panel Reset

Front Panel Clock

Front Panel Data Out

Front Panel Data In

68302

IEEE

Data Out

IEEE

Data

Trigger

(DMA)

In (ISR)

Software

Delay

IEEE-488 Bus

GPIB

56

Digital I/O

Trigger

F/R Status

DC SIG/REF

Signal

DC Input

ADC Data In

O

PTOIS

ADC Data In

DC/MUX FETS

Conditioning

CLK

ADC

CLK

TRMS,

DATA

DATA

AVE,

Amps

O

STB

PK

STB

TRG

Control

Data Out

FREQ Out

Signal

AC Input

Hardware

Trigger

AC FETS

(w/freq)

Conditioning

Select

Trigger

Logic

Scanner Control Out

Option

Scanner

FREQ In

External Trigger,

Power Supply

Meter Complete

Trigger Bus

Figure 2-1

Model 2001 overall block diagram

2-16

Amps

Sense HI

Sense LO

Scanner Output

Scanner

Inputs

Input HI

Input LO

Troubleshooting

2.10.1 Display board circuit theory

The following information provides some basic circuit

theory that can be used as an aide to troubleshoot the

display and keyboard.

Display microcontroller

U902 is the display microcontroller that controls the

VFD (vacuum ßuorescent display) and interprets key

data. The microcontroller has four peripheral I/O

ports that are used for the various control and read

functions.

Display data is serially transmitted to the microcontroller from the digital board via the TXB line to the microcontroller PD0 terminal. In a similar manner, key

data is serially sent back to the digital board through

the RXB line via PD1. The 4MHz clock for the microcontroller is generated on the digital board.

Vacuum fluorescent display

2.10.2 Power supply circuit theory

The following information provides some basic circuit

theory that can be used as an aide to troubleshoot the

power supply.

Pre-regulator circuit

The pre-regulator circuit regulates power to the transformer. When power is applied to the instrument, a

power transformer secondary voltage (pins 12 and 13)

is rectiÞed (CR622), doubled (C624, C630, CR624 and

CR625) and applied to U619 which is a +5V regulator.

This +5V (+5VC) is used for the pre-regulator circuit.

The pre-regulator circuit monitors the voltage level on

C611 using an integrator (U627). The voltage on C611

(typically around 7.5V) is divided by three through

R712 and R713 and applied to the inverting input (pin

2) of the integrator. The +5V (+5VC) is divided by two

through R706 and R708. This 2.5V reference is applied

to the non-inverting input (pin 3) of the integrator.

DS901 is the VFD (vacuum ßuorescent display) module, which can display up to 49 characters. Each char-

acter is organized as a 5 × 7 matrix of dots or pixels and

includes a long under-bar segment to act as a cursor.

The display uses a common multiplexing scheme with

each character refreshed in sequence. U903 and U904

are the grid drivers, while U901 and U905 are the dot

drivers. Note that dot driver and grid driver data is serially transmitted from the microcontroller (PD3 and

PC1).

The VFD requires both +60VDC and 5VAC for the Þlaments. These VFD voltages are supplied by U625,

which is located on the digital board.

Key matrix

The front panel keys (S901-S931) are organized into a

row-column matrix to minimize the number of microcontroller peripheral lines required to read the keyboard. A key is read by strobing the columns and

reading all rows for each strobed column. Key down

data is interpreted by the display microcontroller and

sent back to the main microprocessor using proprietary

encoding schemes.

When the voltage on the inverting input of the integrator is less than the 2.5V reference on the non-inverting

input, the integrator output ramps in the positive direction. This positive ramp turns on Q608 which pulls

the CONT line low to digital common. With CONT

connected to common, current ßows through the photodiode of U100 and generates a positive voltage at the

gate of FET Q528. As Q528 turns on, the 470Ω resistor

(R100) becomes shunted and results in less effective resistance to the transformer. The resultant increase in

current (power) will increase the voltage on C611.

Conversely, when the voltage on the inverting input of

the integrator is more than the 2.5V reference, the integrator output ramps in the negative direction and begins to turn Q608 off. This will decrease current

through U100, decrease the positive voltage on Q528

and thus, increase the effective resistance to the transformer. The resultant decrease in current (power) will

decrease the voltage of C611.

This constant regulation of effective resistance in series

with the transformer regulates the power delivered to

the instrument.

2-17

Troubleshooting

Line voltage (110V/220V) selection circuit

This circuit automatically selects the proper power line

voltage setting for the instrument. The line selection

circuit derives its power from the AC1 and AC2 lines

on the primary side of the transformer. RectiÞer CR101

applies approximately +18V to regulator U103. The

output of U103 provides the +8V for the line voltage selection circuit and the HI/LO voltage control circuit.

U106 is a comparator that has a +4V reference (via voltage divider R125 and R126) applied to its non-inverting input. The inverting input monitors the voltage on

C111. When the voltage at the inverting input is greater

than 4V, the output of U106 goes low and turns on FET

Q103. With Q103 on, +8V will be applied to the

+RELAY1 line which energizes relay K101 to select the

110V setting. Conversely, when the voltage at the inverting input is less than 4V, the output of U106 goes

high and turns off Q103. With Q103 off, the +8V is removed from K101 and thus, the line voltage setting defaults to 220V.

The AC power line is tied to C111 through CR104, R227

and R114 via control line ACL. When the AC power

line voltage is less than approximately 135VAC, sufÞcient charge remains on C111 to keep the inverting input of U106 above 4V to ultimately energize K101

(110V setting). When the AC power line voltage is

greater than approximately 18VAC, charge will be

pulled from C111 dropping the voltage at the inverting

input of the comparator to less than 4V. This will de-energize K101 (220V setting).

HI/LO voltage control circuit

This circuit automatically selects the appropriate HI/

LO setting for the available power line voltage. During

power-up, the line voltage is rectiÞed (CR100), divided

(R103 and R105, or R102 and R105) and applied to the

base of Q101.

If the voltage level at the base of Q101 is high (above

zener VR101), the transistor will turn on and apply

power to the ISO1+ and ISO1- lines. With power applied to ISO1+ and ISO1-, U105 will turn on and allow

Q105 to be forward biased. With U105 and Q105 on,

TRIG of U110 will be pulled low and allow its output

(OUT) to latch at +8V which will turn on FET Q102.

With Q102 on, the -RELAY2 line will be connected to

common, and thus energize K100 (HI setting).

If the power line voltage decreases to a low level, U105

will turn off, but the output of U110 will remain latched

at +8V. However, the LOW line will be driven low turning on U109. With U109 and Q106 on, +8V will be applied to THR of U110 forcing its output (OUT) to reset

to low. With the gate of Q102 low, the FET will turn off

and open the relay coil circuit for K100 (LO setting).

The LOW line is controlled by comparator U628. The

inverting input of the comparator is connected to the

2.5V reference. The non-inverting input monitors (via

divider R709 and R711) C611. As previously explained,

the typical power line voltage level will apply around

7.5V to C611. However, if the line voltage decreases

such that the voltage on C611 becomes less than 6V, the

voltage level on the non-inverting input of the comparator will drop below 2.5V causing its output (LOW

line) to go low.

2.10.3 Built-in test documentation

The information in this paragraph provides documentation for each Built-In Test. Paragraph 2.5 explains

how to use the Built-In Test.

The following documentation is provided for each

Built-In Test:

1. Test Type Ñ Some tests are pass/fail type tests

while others are circuit exercises that are used for

subsequent tests.

2. Failure Analysis Ñ For pass/fail type tests, a summary is provided to explain the cause of the failure.

3. Description Ñ Provides a description of the circuit

being tested.

4. Schematic Reference Ñ Directs you to the appropriate schematic(s) for the circuit being tested.

5. High Suspect Components Ñ When appropriate,

possible defective components and/or circuits are

listed. It is left to the expertise of the repair technician to pin-point the problem.

6. Shift Registers Ñ For tests starting with 200.1, the

logic states for the control shift registers are provided. After one of these tests is manually run, you

can check the registers for the correct logic levels.

Tables 2-10 through 2-12 provide functional descriptions for the register bits.

7. Multiplexer Ñ For manually run tests that exercise

the multiplexer (U511), you can use Table 2-13 to

check the logic levels on its control lines.

2-18

Table 2-10

DC_STB control registers

Register Bit Pin Control Description

Troubleshooting

U801 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

U800 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

U300 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

4

5

6

7

14

13

12

11

4

5

6

7

14

13

12

11

4

5

6

7

14

13

12

11

FAST

LST_PH

FREQ_EN

I3, FREQ_LOAD

I4

I5

I6

I7

I8

I9

I10

I11

I12

I13

OHMCA

OHMCB

BUF, /BUF

VLO2, BSCOM

/REF

//1

/CAL

//2

/ZERO

FE ZERO, ONE SHOT

1 = FAST integration on A/D converter (ADC).

1 = Normal ADC operation.

1 = Normal ADC operation.

1 = Normal ADC operation.

Set ADC conversion rate (LSB).

Set ADC conversion rate.

Set ADC conversion rate.

Set ADC conversion rate.

Set ADC conversion rate.

Set ADC conversion rate.

Set ADC conversion rate.

Set ADC conversion rate.

Set ADC conversion rate.

Set ADC conversion rate (MSB).

Select Ohms Cal on U325 (LSB).

Select Ohms Cal on U325 (MSB).

1 = Q306 on and Q304 off.

0 = -8VF to VLO2, 1 = -8VF to BSCOM.

0 = 7V ref to A/D Buffer (via U317).

0 = Input Buffer to A/D Buffer (Q308 and Q313

on).

0 = Cal Divider to A/D Buffer (via U319).

0 = -0.5 or 1.5 gain (via U319).

0 = Zero to A/D Buffer (via U319).

1 = Q527 and Q539 on, 0 = ONE SHOT (via U334)

for PRECHARGE (Q538 on).

U303 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

4

5

6

7

14

13

12

11

/X1

/X5

/X50

/2VREF

/AC

/DCA

nc

nc

0 = x1 A/D Buffer; U318 (/X1) closed.

0 = x5 A/D Buffer; U318 (/X5) closed.

0 = x50 A/D Buffer; U318 (/X50) closed.

0 = 1.75V ref to A/D Buffer (via U318).

0 = ACV/A to A/D Buffer (via U320).

0 = DCA to A/D Buffer (via U320).

x

x

2-19

Troubleshooting

Table 2-11

R1_STB control registers

Register Bit Pin Control Description

U307 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

U305 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

U302 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

4

5

6

7

14

13

12

11

4

5

6

7

14

13

12

11

4

5

6

7

14

13

12

11

OHM FA

OHM FB

4W OHM

/OHM CAL

/4 DIGIT

OHM FD

/LOV/OHM, BSCOM

/2M

4 DIGIT

OHM

VLO, /VLO

HI OHM, /HI OHM

/HIV

/DIVIDER, BSCOM

OHM SELECT, /4W

OHM, BSCOM

/200M

/ACA

/ACAL

/200µA

/2mA

/20mA

/200mA

/2A

nc

U332 ohms range select (LSB).

U332 ohms range select (MSB).

0 = U323 closed, 1 = U323 open.

0 = OHM CAL to A/D Buffer (via U320).

0 = BSCOM or common (via U317) to A/D Buffer

(U319 closed).

1 = U332 Inhibit (INH); all channels off.

1 = Q333 off, 0 = Q333 on to connect signal to BSCOM.

0 = Q329 on (10MΩ range).

0 = Common to A/D Buffer (via U317).

1 = K300 closed (OHMS relay).

1 = U336 and U337 turns on Q337-Q340.

1 = Q320 and Q312 off, Q324 on.

1 = Q328 off; opens divider common.

1 = Q525 off, 0 = Q525 on to connect divider signal to

BSCOM.

0 = U323 closed and Q331 on to connect signal to

BSCOM.

0 = U323 closed (/16 gain for 4.4nA ohms source).

0 = U320 (ACA) and U522 (ACBS) closed.

0 = U323 closed.

0 = U317 closed (1kΩ shunt).

0 = U317 closed (100Ω shunt).

0 = Q311 on (10Ω shunt).

0 = Q309 and Q307 on (1Ω shunt).

0 = Q310 and Q305 on (0.1Ω shunt).

x

2-20

Table 2-12

R2_STB control registers

Register Bit Pin Control Description

Troubleshooting

U505 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

U500 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

U530 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

4

5

6

7

14

13

12

11

4

5

6

7

14

13

12

11

4

5

6

7

14

13

12

11

DCF

SELFTEST

SELFTESTEN

SHORT

REL1

REL2

REL3

REL4

750V

ACLOW

RANGE

/PEAK

/RSTPK

TRIG9

TRIGLEV

SEL

TRIG8

TRIG7

TRIG6

TRIG5

TRIG4

TRIG3

TRIG2

TRIG1

0 = U526 (divider) closed and U526 (ACA) open.

1 = Q518 off, U513 arms U503, and U522 (control pin 9) open.

1 = Arms U513 (pin 5) for SELFTEST.

0 = U526 closed (common to AC Buffer).

1 = Q504 on; closes relay K502 (ACV).

1 = Q519 on; closes relay K503 (SELFTEST).

1 = Opens U510 and turns on Q500 which closes relay K501 (pins

4 and 5).

1 = Q502 on; closes K500 (Q503 on).

0 = U526 on (/500 AC divider).

0 = Q513 on and Q516 off, 1 = Q513 off and Q516 on.

1 = U515 closed and Q508 on (x10 rectiÞer).

0 = Q533 off; disables peak circuit.

0 = U510 (pin 9) closed and U510 (pin 16) open.

0 = Q520 off; increases DAC resolution (1/512).

0 = U515 closed and Q542 on.

0 = Hold DAC B, 1 = hold DAC A.

Bit DB0 of DAC U531 (LSB).

Bit DB1 of DAC U531.

Bit DB2 of DAC U531.

Bit DB3 of DAC U531.

Bit DB4 of DAC U531.

Bit DB5 of DAC U531.

Bit DB6 of DAC U531.

Bit DB7 of DAC U531 (MSB).

U501 Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

4

5

6

7

14

13

12

11

SEL1

SEL2

SEL3

FREQ

RMS

DAC

nc

nc

SEL1, SEL2 and SEL3 control lines

determine which MUX switch (U511)

is closed (see Table 2-13).

1 = Arms U508 and closes U522.

0 = U532 (pin 9) closed and U510 open.

0 = U532 (pin 1) closed; DAC V to AC Buffer.

x

x

2-21

Troubleshooting

Table 2-13

Multiplexer (U511)

MUX Control Lines

Selected InputSEL3 SEL2 SEL1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

IN1; Peak output

IN2; Filter output

IN3; TRMS output

IN4; ACF output

IN5; RectiÞer output

IN6; SELFTEST OUT

IN7; AMP IN output

IN8; Common

2-22

Type

Failure analysis

Description

High suspect

components

Type

Failure analysis

Description

High suspect

components

Type

Failure analysis

Description

High suspect

components

Troubleshooting