Page 1

STA517B

60 V 6 A quad power half bridge

Features

■ Minimum input output pulse width distortion

■ 200 mΩ R

complementary DMOS output

dsON

stage

■ CMOS compatible logic inputs

■ Thermal protection

■ Thermal warning output

■ Under voltage protection

Description

STA517B is a monolithic quad half bridge stage in

Multipower BCD Technology. The device can be

used as dual bridge or reconfigured, by

connecting CONFIG pin to Vdd pin, as single

bridge with double current capability, and as half

bridge (Binary mode) with half current capability.

The device is particularly designed to make the

output stage of a stereo all-digital high efficiency

(DDX™) amplifier capable to deliver 175 + 175 W

@ THD = 10 % at V

load and 350 W @ THD = 10 % at V

4 Ω load in single BTL configuration.

54 V output power on 8 Ω

cc

54 V on

cc

Power SO36 slug up

The input pins have threshold proportional to V

L

pin voltage.

Table 1. Device summary

Part number Package Packaging

STA517B Power SO36 slug up Tube

STA517B13TR Power SO36 slug up Tape and reel

March 2007 Rev 2 1/13

www.st.com

1

Page 2

Contents STA517B

Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Pin lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4 Power supply and control sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . 8

5 Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6 Mechanical and package data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

7 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2/13

Page 3

STA517B Introduction

1 Introduction

Figure 1. Application circuit (dual BTL)

+V

CC

C55

1000µF

8Ω

8Ω

+3.3V

TH_WAR

100nF

V

1A

CC

15

IN1A

CONFIG

PWRDNPWRDN

FAULT

TRI-STATE

TH_WAR

IN1B

VCCSIGN

V

SIGN

CC

IN2A

GND-Reg

GND-Clean

IN2B

GNDSUB

29

V

23

L

24

25

PROTECTIONS

27

LOGIC

26

28

30

21

V

DD

22

V

DD

33

V

REGULATORS

SS

34

V

SS

35

36

31

20

19

32

1

IN1A

R57

R59

10K

10K

C58

100nF

IN1B

C58

C53

100nF

C60

100nF

IN2A

IN2B

M3

M2

&

M5

M4

M17

M15

M16

M14

C30

1µF

17

OUT1A

16

OUT1A

GND1A

14

1B

12

V

CC

11

OUT1B

10

OUT1B

13

GND1B

7

V

2A

CC

C32

1µF

8

OUT2A

9

OUT2A

GND2A

6

V

2B

4

CC

3

OUT2B

2

OUT2B

5

GND2B

L18 22µH

C20

100nF

C52

330pF

R63

20

C31

1µF

L19 22µH

L113 22µH

C109

330pF

R104

20

C33

1µF

L112 22µH

D00AU1148B

R100

100nF

C110

100nF

R103

R102

C111

100nF

C99

R98

100nF

6

C23

470nF

C101

6

100nF

C21

C107

100nF

6

C108

470nF

C106

6

100nF

3/13

Page 4

Pin lists STA517B

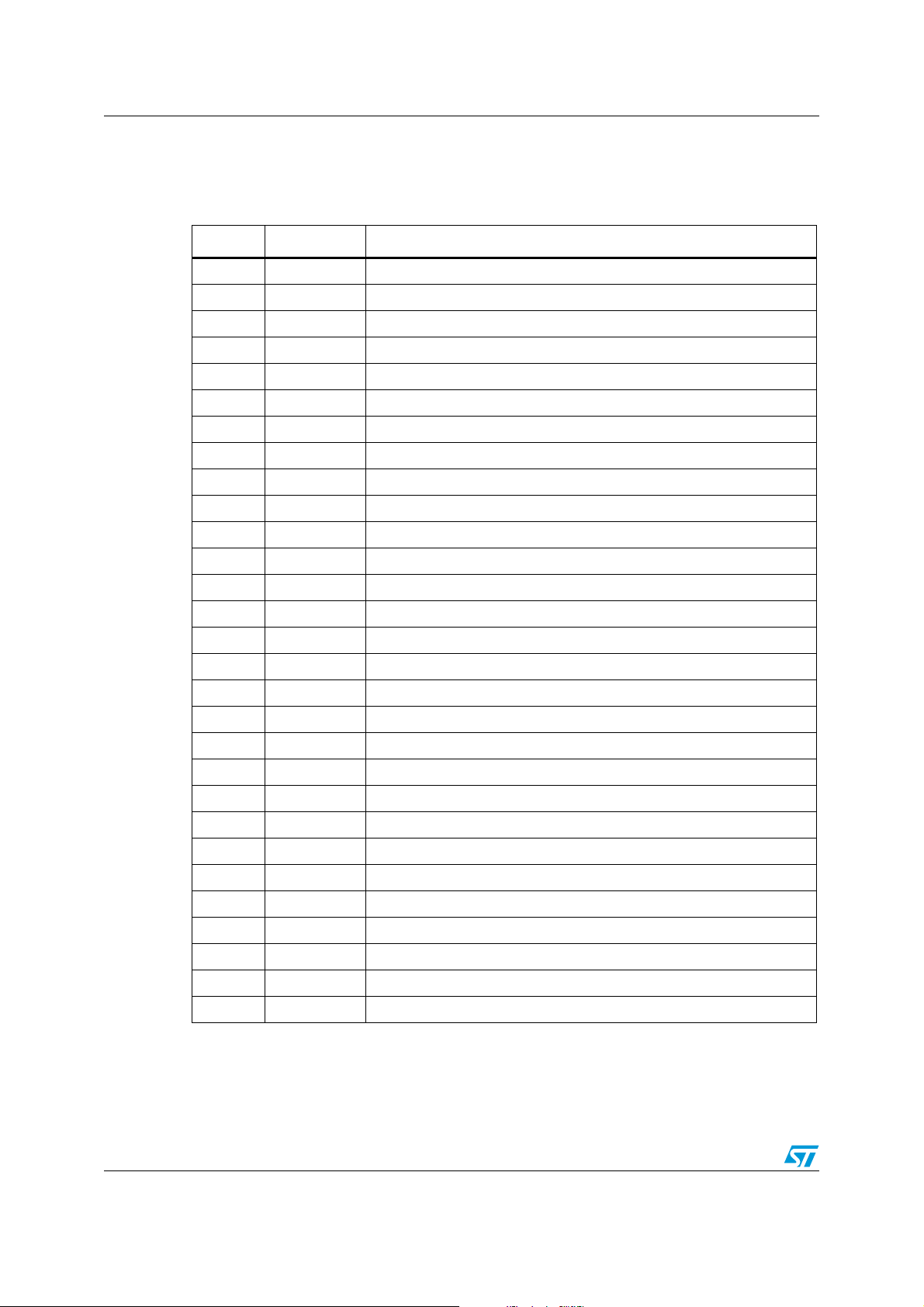

2 Pin lists

Table 2. Pin function

Number Pin Description

1 GND-SUB Substrate ground

2, 3 OUT2B Output half bridge 2B

4 VCC2B Positive supply

5 GND2B Negative supply

6 GND2A Negative supply

7 VCC2A Positive supply

8, 9 OUT2A Output half bridge 2A

10, 11 OUT1B Output half bridge 1B

12 VCC1B Positive supply

13 GND1B Negative supply

14 GND1A Negative supply

15 VCC1A Positive supply

16, 17 OUT1A Output half bridge 1A

18 NC Not connected

19 GND-CLEAN Logical ground

20 GND-REG Ground for regulator Vdd

21, 22 VDD 5 V regulator referred to ground

23 V

24 CONFIG Configuration pin

25 PWRDN Stand-by pin

26 TRI-STATE Hi-Z pin

27 FAULT Fault pin advisor

28 TH-WAR Thermal warning advisor

29 IN1A Input of half bridge 1A

30 IN1B Input of half bridge 1B

31 IN2A Input of half bridge 2A

32 IN2B Input of half bridge 2B

33, 34 VSS 5 V regulator referred to +Vcc

35, 36 VCC SIGN Signal positive supply

L

High logical state setting voltage

4/13

Page 5

STA517B Pin lists

Table 3. Functional pin status

Pin name Logical value Status

FAULT 0 Fault detected (short circuit or thermal for example)

(1)

FAULT

TRI-STATE 0 All powers in Hi-Z state

TRI-STATE 1 Normal operation

PWRDN 0 Low absorption

PWRDN 1 Normal operation

THWAR 0 Temperature of the IC =130

THWAR

(1)

CONFIG 0 Normal operation

1 Normal operation

1 Normal operation

o

C

CONFIG

(2)

1

OUT1A=OUT1B; OUT2A=OUT2B

(IF IN1A = IN1B; IN2A = IN2B)

1. The pin is open collector. To have the high logic value, it needs to be pulled up by a resistor.

2. CONFIG = 1 means connect Pin 24 (CONFIG) to Pins 21, 22 (Vdd)

Figure 2. Pin connection

V

Sign

CC

VCCSign

V

V

IN2B

IN1B

IN1A

FAULT

TRI-STATE

PWRDN

CONFIG

V

DD

V

DD

36

35

SS

SS

V

34

33

32

31

30

29

28

26

25

23

L

22

21

20

19

D01AU1273

1

GND-SUB

2

OUT2B

3

OUT2B

4

5

6

7

8

9

1027

11

12

1324

14

15

16

17

18

2B

V

CC

GND2B

GND2AIN2A

V

2A

CC

OUT2A

OUT2ATH_WAR

OUT1B

OUT1B

V

1B

CC

GND1B

GND1A

V

1A

CC

OUT1A

OUT1AGND-Reg

N.C.GND-Clean

5/13

Page 6

Electrical characteristics STA517B

3 Electrical characteristics

Table 4. Absolute maximum ratings

Symbol Parameter Value Unit

V

CC

V

max

T

op

, T

T

stg

Table 5. Thermal data

DC supply voltage (Pins 4,7,12,15) 60 V

Maximum voltage on pins 23 to 32 5.5 V

Operating temperature range 0 to 70 °C

Storage and junction temperature -40 to 150 °C

j

Symbol Parameter Min. Typ. Max. Unit

T

j-case

T

jSD

T

warn

t

hSD

Table 6. Electrical characteristics

Thermal resistance junction to case (thermal pad) 1 2.5 °C/W

Thermal shut-down junction temperature 150 °C

Thermal warning temperature 130 °C

Thermal shut-down hysteresis 25 °C

(VL= 3.3 V; Vcc = 50 V; Tamb = 25 °C unless otherwise specified)

Symbol Parameter Test conditions Min. Typ. Max.

R

I

g

g

dsON

dss

N

P

Power Pchannel/Nchannel MOSFET

R

dsON

Power Pchannel/Nchannel leakage Idss 100

Power Pchannel R

Power Nchannel R

matching Id=1A 95

dsON

matching Id=1A 95

dsON

Dt_s Low current dead time (static) see Figure 4 10 20

Dt_d High current dead time (dynamic)

t

d ON

t

d OFF

t

r

t

f

V

CC

V

IN-High

V

IN-Low

I

IN-H

I

IN-L

Turn-on delay time Resistive load 100

Turn-off delay time Resistive load 100

Rise time

Fall time

Supply operating voltage 10 56

High level input voltage VL/2

Low level input voltage VL/2

High level Input current Pin voltage = V

Low level input current Pin voltage = 0.3 V 1

Id=1A 200 240

L=22µH, C = 470nF

Rl = 8 Ω, Id=4.5A

50

see Figure 5

Resistive load

see Figure 4

Resistive load

see Figure 4

25

25

-300mV

L

1

+300mV

Unit

mΩ

µA

%

%

ns

ns

ns

ns

ns

ns

V

V

V

µA

µA

6/13

Page 7

STA517B Electrical characteristics

Table 6. Electrical characteristics (continued)

(VL= 3.3 V; Vcc = 50 V; Tamb = 25 °C unless otherwise specified)

Symbol Parameter Test conditions Min. Typ. Max.

Unit

I

PWRDN-H

V

Low

V

High

I

VCC-

PWRDN

High level PWRDN pin input current VL= 3.3 V 35

Low logical state voltage VL (pin

PWRDN, TRISTATE)(seeTab le 7)

High logical state voltage VH (pin

PWRDN, TRISTATE)(seeTab le 7)

Supply current from Vcc in power down PWRDN = 0 3

Output current pins

I

FAULT

FAULT -TH-WARN when

FAULT CONDITIONS

I

VCC-hiz

I

VCC

I

OUT-SH

V

UV

V

OV

t

pw_min

1. See specific application note number: AN1994.

Table 7. VLow, VHigh variation with VL

Supply current from Vcc in Tristate Tristate = 0 22

Supply current from Vcc in operation

both channel switching)

Over current protection threshold Isc

(short circuit current limit)1

(1)

Under voltage protection threshold 7

Over voltage protection threshold 60 70

Output minimum pulse width No load 25 40

= 3.3 V 0.8

V

L

= 3.3 V 1.7

V

L

Vpin = 3.3 V 1

Input pulse width

= 50 % duty

Switching frequency

70

= 384 Khz;

No LC filters

6.5 8 10

µA

V

V

mA

mA

mA

mA

A

V

V

ns

V

L

VLow min VHigh max Unit

2.7 0.7 1.5 V

3.3 0.8 1.7 V

5 0.85 1.85 V

Table 8. Logic truth table (see Figure 2)

Tristate INxA INxB Q1 Q2 Q3 Q4 Output mode

0 x x OFF OFF OFF OFF Hi-Z

1 0 0 OFF OFF ON ON DUMP

1 0 1 OFF ON ON OFF NEGATIVE

1 1 0 ON OFF OFF ON POSITIVE

1 1 1 ON ON OFF OFF Not used

7/13

Page 8

Power supply and control sequencing STA517B

4 Power supply and control sequencing

To guarantee correct operation and reliability, a correct turn on/off sequence must be

followed. Figure 3 shows the correct power on sequence.

Figure 3. Correct power-on sequence

V

Vcc > V

L

PWRDN

IN

Vcc must turn on before V

in order to prevent uncontrolled current flowing through an

L

internal protection diode connected between V

V

cc

V

L

(logic supply) and Vcc (high power supply).

L

Failure to do so could result in damage to the device.

PWRDN must be released after V

is switched on. An input signal can then be sent to the

L

power stage.

t

t

t

8/13

Page 9

STA517B Test

5 Test

Figure 4. Test circuit

Low current dead time = MAX(DTr,DTf)

+Vcc

Duty cycle = 50%

M58

INxY

M57

OUTxY

gnd

Figure 5. Current dead time test circuit

High Current Dead time for Bridge application = ABS(DTout(A)-DTin(A))+ABS(DTOUT(B)-DTin(B))

Duty cycle=A Duty cycle=B

DTin(A)

INxA

M58

M57

Q1

OUTxA

Q3

DTout(A)

Iout=4.5A

C69

470nF

+V

CC

Rload=8Ω

C71 470nF

OUTxY

DTfDTr

R 8Ω

+

V67 =

-

vdc = Vcc/2

D03AU1458

M64

OUTxB

Q2

M63

Q4

DTout(B) DTin(B)

L68 22µL67 22µ

Iout=4.5A

C70

470nF

Vcc

(3/4)Vcc

(1/2)Vcc

(1/4)Vcc

t

INxB

Duty cycle A and B: Fixed to have DC output current of 4.5A in the direction shown in figure

9/13

D00AU1162

Page 10

Test STA517B

Figure 6. Typical single BTL configuration to obtain 350 W @ THD 10 %, RL = 4 Ω,

VCC = 54 V

+3.3V

100nF

100nF

10K

X7R

TH_WAR

nPWRDN

10K

100nF

IN1A

IN1B

100nF

X7R

100nF

X7R

Add.

(a)

V

L

23 N.C.

GND-Clean

19

GND-Reg

20

V

DD

21

V

DD

22

CONFIG

24

TH_WAR

28

PWRDN

25

FAULT

27

26

TRI-STATE

IN1A

29

IN1B

30

IN2A

31

IN2B

32

V

SS

33

V

SS

34

VCCSIGN

35

SIGN

V

CC

36

GNDSUB

1

18

17

OUT1A

16

OUT1A

11

OUT1B

10

OUT1B

OUT2A

9

OUT2A

8

OUT2B

3

OUT2B

2

V

1A

CC

15

V

1B

CC

12

2A

V

CC

7

2B

V

CC

4

GND1A

14

GND1B

13

GND2A

6

GND2B

5

22Ω

1/2W

330pF

1µF

X7R

1µF

X7R

D04AU1545

12µH

12µH

1/2W

1/2W

100nF

FILM

100nF

6.2

X7R

680nF

100nF

FILM

2200µF

63V

100nF

X7R

+36V

FILM

6.2

4Ω

+36V

Figure 7. Typical quad half bridge configuration

+V

CC

C21

2200µF

4Ω

4Ω

4Ω

4Ω

+3.3V

TH_WAR

100nF

1P

V

CC

IN1A

CONFIG

PWRDNPWRDN

FAULT

TRI-STATE

TH_WAR

VCCSIGN

V

SIGN

CC

GND-Reg

GND-Clean

GNDSUB

29

V

23

L

24

25

PROTECTIONS

27

LOGIC

26

28

IN1B

30

V

21

DD

V

22

DD

33

V

REGULATORS

SS

34

V

SS

35

36

IN2A

31

20

19

32

IN2B

1

IN1A

R57

R59

10K

10K

C58

100nF

IN1B

C58

C53

100nF

C60

100nF

IN2A

IN2B

M3

M2

&

M5

M4

M17

M15

M16

M14

15

17

16

14

12

11

10

13

7

8

9

6

4

3

2

5

OUTPL

OUTPL

PGND1P

V

CC

OUTNL

OUTNL

PGND1N

V

CC

OUTPR

OUTPR

PGND2P

V

CC

OUTNR

OUTNR

PGND2N

D03AU1474

L11 22µH

C71

R41

100nF

20

R51

C41

330pF

1N

C51

100nF

1µF

330pF

2P

330pF

2N

C52

1µF

100nF

330pF

6

C61

L12 22µH

C72

R42

100nF

20

R52

C42

6

L13 22µH

C73

R43

100nF

20

R53

C43

6

C62

L14 22µH

C74

R44

100nF

20

R54

C44

6

100nF

100nF

100nF

100nF

R61

C31 820µF

5K

C91

C81

C82

C83

C84

1µF

R62

5K

R63

C32 820µF

5K

C92

1µF

R64

5K

R65

C33 820µF

5K

C93

1µF

R66

5K

R67

C34 820µF

5K

C94

1µF

R68

5K

For more information, refer to the application note “ST50X and STA51X digital power

amplifiers”.

a. A PWM modulator as driver is required. This result was obtained using the STA30X+STA50X demo board.

10/13

Page 11

STA517B Mechanical and package data

6 Mechanical and package data

Figure 8. Power SO36 (slug up) mechanical data and package dimension

M.

DI

A 3.25 3.43 0.128 0.135

A2 3.1 3.2 0.122 0.126

A4 0.8 1 0.031 0.039

A5 0.2 0.008

a1 0.030

b 0.22 0.38 0.008 0.015

c 0.23 0.32 0.009 0.012

D 15.8 16 0.622 0.630

D1 9.4 9.8 0.37 0.38

D2 1 0.039

E 13.9 14.5 0.547 0.57

E1 10.9 11.1 0.429 0.437

E2 2.9 0.114

E3 5.8 6.2 0.228 0.244

E4 2.9 3.2 0.114 1.259

e0.65 0.026

e3 11.05 0.435

G 0 0.075 0 0.003

H 15.5 15.9 0.61 0.625

h 1.1 0.043

L 0.8 1.1 0.031 0.043

N 10˚ 10˚

s8˚8˚

(1) “D and E1” do not include mold flash or protusions.

Mold flash or protusions shall not exceed 0.15mm (0.006”)

(2) No intrusion allowed inwards the leads.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

-0.040

0.0011

-0.0015

OUTLINE AND

MECHANICAL DATA

PowerSO36 (SLUG UP)

7183931 D

11/13

Page 12

Revision history STA517B

7 Revision history

Table 9. Document revision history

Date Revision Changes

01-Feb-2007 1 Initial release

19-Mar-2007 2 Update to reflect product maturity.

12/13

Page 13

STA517B

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2007 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

13/13

Loading...

Loading...