TS4984

2 x 1W Stereo audio power amplifier

with active low standby mode

■ Operating from VCC=2.2V to 5.5V

■ 1W output power per channel @ V

CC

=5V,

THD+N=1%, RL=8Ω

■ 10nA standby current

■ 62dB PSRR @ 217Hz with grounded inputs

■ High SNR: 100dB(A) typ.

■ Near-zero pop & click

■ Available in QFN16 4x4 mm, 0.5mm pitch,

leadfree package

Description

The TS4984 has been designed for top of the

class stereo audio applications. Thanks to its

compact and power dissipation efficient QFN

package, it suits various applications.

With a BTL configuration, this Audio Power

Amplifier is capable of delivering 1W per channel

of continuous RMS output power into an 8

@ 5V.

An externally controlled standby mode control

reduces the supply current to less than 10nA per

channel. The device also features an internal

thermal shutdown protection.

Ω load

Pin Connections (top view)

TS4984IQ — TQFN16 4x4mm

VO-L

IN- L

IN- L

IN+ L

IN+ L

BYPASS L

BYPASS L

NC

NC

VO-L

VO+L

VO+L

16 15 14

16 15 14

16 15 14

1

1

2

2

3

3

4

4

56 7

56 7

GND1 GND2 VO+R VO-R

GND1 GND2 VO+R VO-R

VCC1

VCC1

VCC2

VCC2

13

13

13

8

8

12

12

11

11

10

10

STBY

STBY

BYPASS R

BYPASS R

IN+ R

IN+ R

9

9

IN- R

IN- R

The gain of each channel can be configured by

external gain setting resistors.

Applications

■ Cellular mobile phones

■ Notebook computers & PDAs

■ LCD monitors & TVs

■ Portable audio devices

Order Codes

Part Number Temperature Range Package Packaging Marking

TS4984IQT -40, +85°C QFN Tape & Reel K984

January 2005 Revision 1 1/29

TS4984 Typical Application

1 Typical Application

Figure 1 shows a schematic view of a typical audio amplification application using the TS4984. Table 1

describes the components used in this typical application.

Figure 1: Typical application schematic

Cfeed-L

Rfeed-L

22k

VCC

+

Cs

1u

Input R

GND

GND

Wire opti onal

Internal connection

Cin-LInput L

100n

Cin-R

100n

145

Rin-L

22k

VCC

1

2

3

+

Cb

1u

Rin-R

22k

1

2

12

3

10

9

11

Cfeed-R

Rfeed-R

22k

IN-L

IN+L

Standby

Bypass L

IN+R

IN-R

Bypass R

VCC1

-

+

GND1

-

AV = -1

+

-

AV = -1

+

GND2 VCC2

6 13

Bias

+

-

VO-L

VO+L

VO-R

VO+R

TS4984

U1

16

15

8

7

Neg. Output L

Pos. Output L

Neg. Output R

Pos. Output R

Table 1: External component descriptions

Components Functional Description

Inverting input resistors which sets the closed loop gain in conjunction with R

also form a high pass filter with C

(fc = 1 / (2 x Pi x RIN x CIN)).

IN

Input coupling capacitors which blocks the DC voltage at the amplifier input terminal.

Feedback resistors which sets the closed loop gain in conjunction with RIN.

Supply Bypass capacitor which provides power supply filtering.

Bypass pin capacitor which provides half supply filtering.

Closed loop gain in BTL configuration = 2 x (R

/ RIN) on each channel.

FEED

2/29

R

IN L,R

C

IN L,R

R

FEED L,R

C

C

A

V L, R

S

B

. These resistors

feed

Absolute maximum ratings and operating conditions TS4984

2 Absolute maximum ratings and operating conditions

Table 2: Key parameters and their absolute maximum ratings

Symbol Parameter Value Unit

V

T

T

R

ESD

Supply voltage

CC

V

Input Voltage

i

Operating Free Air Temperature Range

oper

Storage Temperature

stg

T

Maximum Junction Temperature

j

Thermal Resistance Junction to Ambient

thja

QFN16 120

P

Power Dissipation

d

Human Body Model

ESD Machine Model 200 V

Latch-up Immunity 200mA

1) All voltages values are measured with respect to the ground pin

2) The magnitude of input signal must never exceed VCC + 0.3V / GND - 0.3V

3) The voltage value is measured with respect from pin to supply

1

2

6V

GND to V

CC

V

-40 to + 85 °C

-65 to +150 °C

150 °C

°C/W

Internally Limited

3

2kV

Table 3: Operating conditions

Symbol Parameter Value Unit

V

V

V

R

OUTGND

T

R

1) When mounted on a 4-layer PCB with via

2) When mounted on a 2 layer PCB

Supply Voltage

CC

Common Mode Input Voltage Range 1.2V to V

ICM

Standby Voltage Input:

Device ON

STB

Device OFF

Load Resistor

R

L

Resistor Output to GND (V

Thermal Shutdown Temperature

SD

STB

= GND)

Thermal Resistance Junction to Ambient

1

QFN16

THJA

QFN16

2

2.2 to 5.5 V

CC

≤ V

1.35

GND ≤ V

STB

STB

≤ V

≤ 0.4

CC

≥ 4 Ω

≥ 1MΩ

150 °C

45

85

V

V

°C/W

3/29

TS4984 Electrical characteristics

3 Electrical characteristics

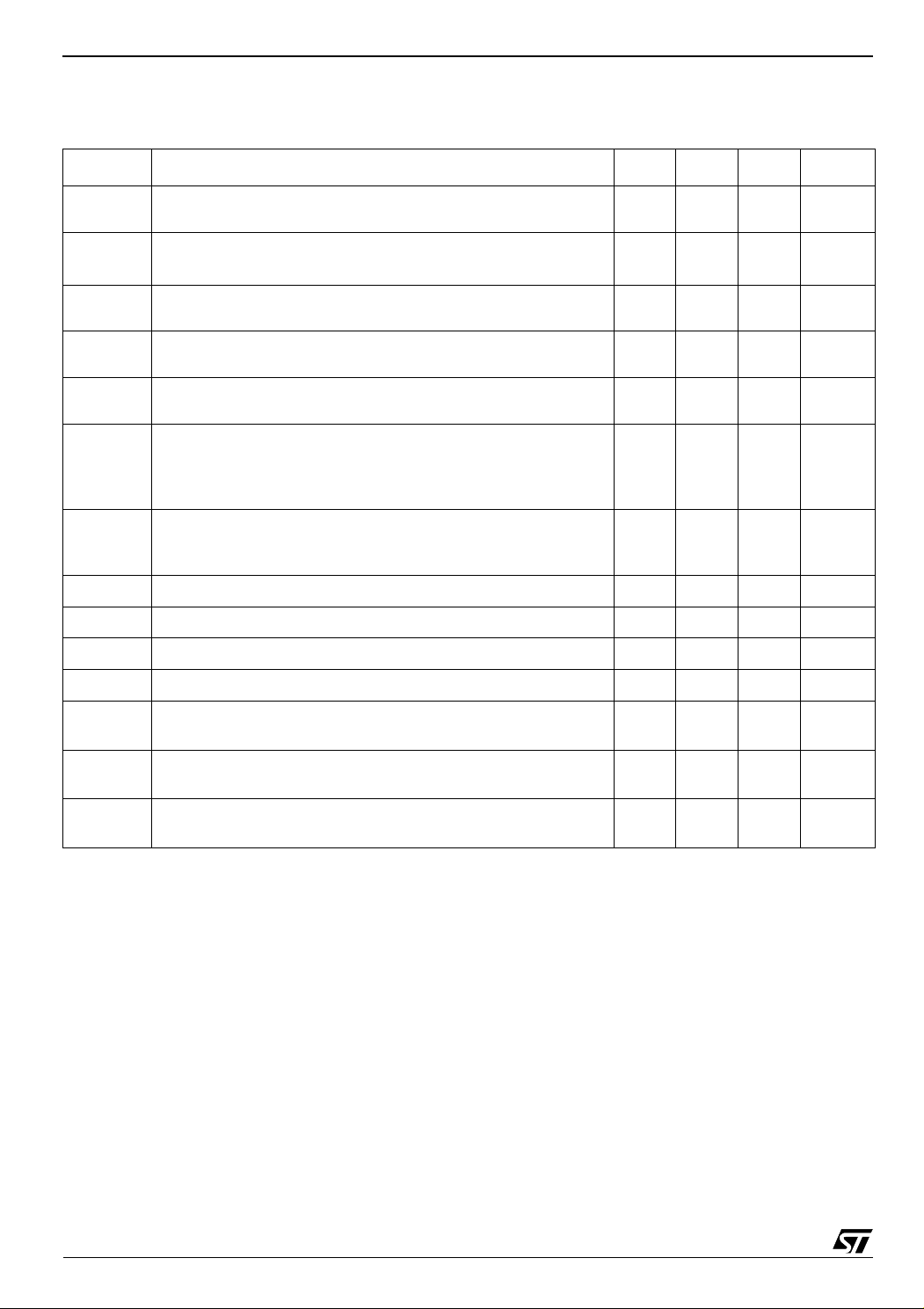

Table 4: Electrical characteristics for VCC= +5V, GND = 0V, T

= 25°C (unless otherwise

amb

specified)

Symbol Parameter Min. Typ. Max. Unit

I

CC

I

STANDBY

Voo

P

THD + N

PSRR

Crosstalk

T

WU

T

STDB

V

STDBH

V

STDBL

Φ

GM

GBP

Supply Current

No input signal, no load 7.4 12

Standby Current

1

No input signal, Vstdby = GND, RL = 8Ω

Output Offset Voltage

No input signal, RL = 8

Output Power

out

THD = 1% Max, F = 1kHz, RL = 8

Ω 110

Ω

0.8 1 W

Total Harmonic Distortion + Noise

Po = 1Wrms, Av = 2, 20Hz

Power Supply Rejection Ratio

≤ F ≤ 20kHz, RL = 8Ω

2

RL = 8Ω, Av = 2, Vripple = 200mVpp, Input Grounded

F = 217Hz

F = 1kHz

Channel Separation, R

= 8Ω

L

55

55

F = 1kHz

F = 20Hz to 20kHz

Wake-Up Time (Cb = 1µF)

Standby Time (Cb = 1µF)

Standby Voltage Level High

Standby Voltage Level Low

Phase Margin at Unity Gain

M

R

= 8Ω, CL = 500pF

L

Gain Margin

= 8Ω, CL = 500pF

R

L

Gain Bandwidth Product

= 8Ω

R

L

10 1000 nA

0.2 %

62

64

-92

-70

90 130 ms

10 µs

1.3 V

0.4 V

65 Degrees

15 dB

1.5 MHz

mA

mV

dB

dB

1) Standby mode is activated when Vstdby is tied to Gnd.

2) All PSRR data limits are guaranteed by production sampling tests

Dynamic measurements - 20*log(rms(Vout)/rms(Vripple)). Vripple is the sinusoid al signal superimposed upon Vcc.

4/29

Electrical characteristics TS4984

Table 5: Electrical characteristics for VCC = +3.3V, GND = 0V, T

= 25°C (unless otherwise

amb

specified)

Symbol Parameter Min. Typ. Max. Unit

I

CC

I

STANDBY

Voo

P

THD + N

PSRR

Crosstalk

T

WU

T

STDB

V

STDBH

V

STDBL

Φ

GM

GBP

Supply Current

No input signal, no load 6.6 12

Standby Current

1

No input signal, Vstdby = GND, RL = 8Ω

Output Offset Voltage

No input signal, RL = 8

Output Power

out

THD = 1% Max, F = 1kHz, RL = 8

Ω 110

Ω

300 450 mW

Total Harmonic Distortion + Noise

Po = 400mWrms, Av = 2, 20Hz

Power Supply Rejection Ratio

≤ F ≤ 20kHz, RL = 8Ω

2

RL = 8Ω, Av = 2, Vripple = 200mVpp, Input Grounded

F = 217Hz

F = 1kHz

Channel Separation, R

= 8Ω

L

55

55

F = 1kHz

F = 20Hz to 20kHz

Wake-Up Time (Cb = 1µF)

Standby Time (Cb = 1µF)

Standby Voltage Level High

Standby Voltage Level Low

Phase Margin at Unity Gain

M

= 8Ω, CL = 500pF

R

L

Gain Margin

R

= 8Ω, CL = 500pF

L

Gain Bandwidth Product

L

= 8Ω

R

10 1000 nA

0.1 %

61

63

-94

-68

110 140 ms

10 µs

1.2 V

0.4 V

65 Degrees

15 dB

1.5 MHz

mA

mV

dB

dB

1) Standby mode is activated when Vstdby is tied to Gnd

2) All PSRR data limits are guaranteed by production sampling tests

Dynamic measurements - 20*log(rms(Vout)/rms(Vripple)). Vripple is the sinusoidal signal superimposed upon Vcc.

5/29

TS4984 Electrical characteristics

Table 6: Electrical characteristics for VCC = +2.6V, GND = 0V, T

= 25°C (unless otherwise

amb

specified)

Symbol Parameter Min. Typ. Max. Unit

I

CC

I

STANDBY

Voo

Pout

THD + N

PSRR

Crosstalk

T

WU

T

STDB

V

STDBH

V

STDBL

Φ

GM

GBP

Supply Current

No input signal, no load 6.2 12

Standby Current

1

No input signal, Vstdby = GND, RL = 8Ω

Output Offset Voltage

No input signal, RL = 8

Output Power

THD = 1% Max, F = 1kHz, RL = 8

Ω 110

Ω

200 250 mW

Total Harmonic Distortion + Noise

Po = 200mWrms, Av = 2, 20Hz

Power Supply Rejection Ratio

≤ F ≤ 20kHz, RL = 8Ω

2

RL = 8Ω, Av = 2, Vripple = 200mVpp, Input Grounded

F = 217Hz

F = 1kHz

Channel Separation, R

= 8Ω

L

55

55

F = 1kHz

F = 20Hz to 20kHz

Wake-Up Time (Cb = 1µF)

Standby Time (Cb = 1µF)

Standby Voltage Level High

Standby Voltage Level Low

Phase Margin at Unity Gain

M

= 8Ω, CL = 500pF

R

L

Gain Margin

R

= 8Ω, CL = 500pF

L

Gain Bandwidth Product

= 8Ω

R

L

10 1000 nA

0.1 %

60

62

-95

-68

125 150 ms

10 µs

1.2 V

0.4 V

65 Degrees

15 dB

1.5 MHz

mA

mV

dB

dB

1) Standby mode is activated when Vstdby is tied to Gnd

2) All PSRR data limits are guaranteed by production sampling tests

Dynamic measurements - 20*log(rms(Vout)/rms(Vripple)). Vripple is the sinusoidal signal superimposed upon Vcc.

6/29

Electrical characteristics TS4984

0.1 1 10 100 1000 10000

-40

-20

0

20

40

60

80

100

-200

-160

-120

-80

-40

0

Gain

Phase

Gain (dB)

Frequency (kHz)

Vcc = 5V

CL = 560pF

Tamb = 25°C

Phase (°)

0.1 1 10 100 1000 10000

-40

-20

0

20

40

60

80

100

-200

-160

-120

-80

-40

0

Gain

Phase

Gain (dB)

Frequency (kHz)

Vcc = 3.3V

CL = 560pF

Tamb = 25°C

Phase (°)

0.1 1 10 100 1000 10000

-40

-20

0

20

40

60

80

100

-200

-160

-120

-80

-40

0

Gain

Phase

Gain (dB)

Frequency (kHz)

Vcc = 2.6V

CL = 560pF

Tamb = 25°C

Phase (°)

Figure 2: Open loop frequency response

60

40

20

0

Gain (dB)

-20

-40

-60

0.1 1 10 100 1000 10000

Phase

Vcc = 5V

RL = 8

Ω

Tamb = 25°C

Frequency (kHz)

Gain

Figure 3: Open loop frequency response

60

40

20

0

Gain (dB)

-20

-40

-60

0.1 1 10 100 1000 10000

Vcc = 3.3V

RL = 8

Ω

Tamb = 25°C

Phase

Gain

Frequency (kHz)

0

-40

-80

-120

-160

-200

0

-40

-80

-120

-160

-200

Figure 5: Open loop frequency response

Phase (°)

Figure 6: Open loop frequency response

Phase (°)

Figure 4: Open loop frequency response

60

40

20

0

Gain (dB)

-20

-40

-60

0.1 1 10 100 1000 10000

Vcc = 2.6V

RL = 8

Ω

Tamb = 25°C

Phase

Gain

Frequency (kHz)

Figure 7: Open loop frequency response

0

-40

-80

Phase (°)

-120

-160

-200

7/29

TS4984 Electrical characteristics

Figure 8: Power supply rejection ratio (PSRR)

vs. frequency

0

Vripple = 200mVpp

-10

Av = 2

Input = Grounded

-20

Cb = Cin = 1µF

RL >= 4

-30

-40

PSRR (dB)

-50

-60

-70

Ω

Tamb = 25°C

100 1000 10000 100000

Vcc :

2.2V

2.6V

3.3V

5V

Frequency (Hz)

Figure 9: Power supply rejection ratio (PSRR)

vs. frequency

0

Vripple = 200mVpp

-10

Av = 5

Input = Grounded

Cb = Cin = 1µF

-20

RL >= 4

Ω

Tamb = 25°C

-30

PSRR (dB)

-40

-50

-60

100 1000 10000 100000

Vcc :

2.2V

2.6V

3.3V

5V

Frequency (Hz)

Figure 11: Power supply rejection ratio (PSRR)

vs. frequency

0

-10

-20

-30

PSRR (dB)

-40

-50

-60

Vripple = 200mVpp

Av = 2

Input = Grounded

Cb = 0.1µF, Cin = 1µF

RL >= 4

Ω

Tamb = 25°C

Vcc = 5, 3.3, 2.5 & 2.2V

100 1000 10000 100000

Frequency (Hz)

Figure 12: Power supply rejection ratio

(PSRR) vs. frequency

0

Vripple = 200mVpp

-10

Rfeed = 22kΩ

Input = Floating

-20

Cb = 1µF

RL >= 4

-30

-40

PSRR (dB)

-50

-60

-70

-80

Ω

Tamb = 25°C

100 1000 10000 100000

Vcc = 2.2, 2.6, 3.3, 5V

Frequency (Hz)

Figure 10: Power supply rejection ratio

(PSRR) vs. frequency

0

8/29

Vripple = 200mVpp

Av = 10

-10

Input = Grounded

Cb = Cin = 1µF

-20

RL >= 4

Ω

Tamb = 25°C

-30

PSRR (dB)

-40

-50

100 1000 10000 100000

Vcc :

2.2V

2.6V

3.3V

5V

Frequency (Hz)

Figure 13: Power supply rejection ratio

(PSRR) vs. frequency

0

Vripple = 200mVpp

-10

Rfeed = 22kΩ

Input = Floating

-20

Cb = 0.1µF

RL >= 4

-30

-40

PSRR (dB)

-50

-60

-70

-80

Ω

Tamb = 25°C

100 1000 10000 100000

Vcc = 2.2, 2.6, 3.3, 5V

Frequency (Hz)

Electrical characteristics TS4984

-3.0 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0

-60

-50

-40

-30

-20

-10

0

Vcc = 3.3V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 5

Tamb = 25°C

PSRR (dB)

Differential DC Output Voltage (V)

-3.0 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0

-50

-40

-30

-20

-10

0

Vcc = 3.3V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 10

Tamb = 25°C

PSRR (dB)

Differential DC Output Voltage (V)

Figure 14: Power supply rejection ratio

(PSRR) vs. DC output voltage

0

-10

-20

-30

-40

PSRR (dB)

-50

-60

-70

-5-4-3-2-1012345

Vcc = 5V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 2

Tamb = 25°C

Differential DC Output Voltage (V)

Figure 15: Power supply rejection ratio

(PSRR) vs. DC output voltage

0

-10

-20

-30

PSRR (dB)

-40

Vcc = 5V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 5

Tamb = 25°C

Figure 17: Power supply rejection ratio

(PSRR) vs. DC output voltage

0

-10

-20

-30

-40

PSRR (dB)

-50

-60

-70

-3.0 -2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5 3.0

Vcc = 3.3V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 2

Tamb = 25°C

Differential DC Output Voltage (V)

Figure 18: Power supply rejection ratio

(PSRR) vs. DC output voltage

-50

-60

-5-4-3-2-1012345

Differential DC Output Voltage (V)

Figure 16: Power supply rejection ratio

(PSRR) vs. DC output voltage

0

Vcc = 5V

-10

-20

-30

PSRR (dB)

-40

-50

-5-4-3-2-1012345

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 10

Tamb = 25°C

Differential DC Output Voltage (V)

Figure 19: Power supply rejection ratio

(PSRR) vs. DC output voltage

9/29

TS4984 Electrical characteristics

0.1 1

-80

-70

-60

-50

-40

-30

Av=10

Vcc:

2.6V

3.3V

5V

Av=5

Vcc:

2.6V

3.3V

5V

Av=2

Vcc:

2.6V

3.3V

5V

Tamb=25°C

PSRR at 217Hz (dB)

Bypass Capacitor Cb ( F)

Figure 20: Power supply rejection ratio

(PSRR) vs. DC output voltage

0

-10

-20

-30

-40

PSRR (dB)

-50

-60

-70

-2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5

Vcc = 2.6V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 2

Tamb = 25°C

Differential DC Output Voltage (V)

Figure 21: Power supply rejection ratio

(PSRR) vs. DC output voltage

0

-10

-20

-30

PSRR (dB)

-40

-50

-60

-2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5

Vcc = 2.6V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 5

Tamb = 25°C

Differential DC Output Voltage (V)

Figure 23: Power supply rejection ratio

(PSRR) at f=217Hz vs. bypass

capacitor

Figure 24: Output power vs. power supply

voltage

2.00

RL = 4

1.75

1.50

1.25

1.00

Pout (W)

0.75

0.50

0.25

0.00

Ω

F = 1kHz

BW < 125kHz

Tamb = 25°C

2.5 3.0 3.5 4.0 4.5 5.0 5.5

THD+N=10%

THD+N=1%

Vcc (V)

Figure 22: Power supply rejection ratio

(PSRR) vs. DC output voltage

0

-10

-20

-30

PSRR (dB)

-40

-50

-2.5 -2.0 -1.5 -1.0 -0.5 0.0 0.5 1.0 1.5 2.0 2.5

10/29

Vcc = 2.6V

Vripple = 200mVpp

RL = 8

Ω

Cb = 1µF

AV = 10

Tamb = 25°C

Differential DC Output Voltage (V)

Figure 25: Output power vs. power supply

voltage

1.75

RL = 8

Ω

F = 1kHz

1.50

1.25

1.00

0.75

Pout (W)

0.50

0.25

0.00

BW < 125kHz

Tamb = 25°C

2.5 3.0 3.5 4.0 4.5 5.0 5.5

THD+N=10%

THD+N=1%

Vcc (V)

Electrical characteristics TS4984

4 8 12 16 20 24 28 32

0.00

0.05

0.10

0.15

0.20

0.25

0.30

0.35

0.40

THD+N=10%

THD+N=1%

Vcc = 2.6V

F = 1kHz

BW < 125kHz

Tamb = 25°C

Pout (W)

Load resistance

0.0 0.2 0.4 0.6 0.8 1.0 1.2

0.0

0.4

0.8

1.2

1.6

2.0

2.4

RL=16

Ω

RL=8

Ω

Vcc=5V

F=1kHz

THD+N<1%

RL=4

Ω

Power Dissipation (W)

Output Power (W)

Figure 26: Output power vs. power supply

voltage

1.0

RL = 16

0.9

0.8

0.7

0.6

0.5

0.4

Pout (W)

0.3

0.2

0.1

0.0

Ω

F = 1kHz

BW < 125kHz

Tamb = 25°C

2.5 3.0 3.5 4.0 4.5 5.0 5.5

THD+N=10%

THD+N=1%

Vcc (V)

Figure 27: Output power vs. power supply

voltage

0.60

RL = 32

0.55

0.50

0.45

0.40

0.35

0.30

0.25

Pout (W)

0.20

0.15

0.10

0.05

0.00

Ω

F = 1kHz

BW < 125kHz

Tamb = 25°C

2.5 3.0 3.5 4.0 4.5 5.0 5.5

THD+N=10%

THD+N=1%

Vcc (V)

Figure 29: Output power vs. load resistor

0.7

0.6

0.5

0.4

0.3

Pout (W)

0.2

THD+N=1%

0.1

0.0

4 8 12 16 20 24 28 32

THD+N=10%

Load resistance

Vcc = 3.3V

F = 1kHz

BW < 125kHz

Tamb = 25°C

Figure 30: Output power vs. load resistor

Figure 28: Output power vs. load resistor

1.75

1.50

1.25

1.00

0.75

Pout (W)

0.50

THD+N=1%

0.25

0.00

4 8 12 16 20 24 28 32

THD+N=10%

Load Resistance (W)

Figure 31: Power dissipation vs. output power

Vcc = 5V

F = 1kHz

BW < 125kHz

Tamb = 25°C

11/29

TS4984 Electrical characteristics

No Loads

Tamb=25°C

Vcc = 5V

No Loads

Tamb=25°C

Figure 32: Power dissipation vs. output power

1.2

Vcc=3.3V

F=1kHz

1.0

THD+N<1%

0.8

0.6

0.4

Power Dissipation (W)

0.2

0.0

RL=16

0.0 0.1 0.2 0.3 0.4 0.5 0.6

RL=8

Ω

RL=4

Ω

Ω

Output Power (W)

Figure 33: Power dissipation vs. output power

0.7

Vcc=2.6V

F=1kHz

0.6

THD+N<1%

0.5

0.4

RL=4

Ω

Figure 35: Clipping voltage vs. power supply

voltage and load resistor

0.9

Tamb = 25 C

0.8

Vout1 & Vout2

Clipping Voltage Low side (V)

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0.0

RL = 4

Ω

RL = 8

Ω

RL = 16

Ω

2.5 3.0 3.5 4.0 4.5 5.0

Vcc (V)

Figure 36: Current consumption vs. power

supply voltage

0.3

RL=8

0.2

Power Dissipation (W)

0.1

0.0

RL=16

0.00 0.04 0.08 0.12 0.16 0.20 0.24 0.28

Ω

Ω

Output Power (W)

Figure 34: Clipping voltage vs. power supply

voltage and load resistor

1.0

Tamb = 25 C

0.9

Vout1 & Vout2

Clipping Voltage High side (V)

0.8

0.7

0.6

0.5

0.4

0.3

0.2

2.5 3.0 3.5 4.0 4.5 5.0

RL = 4

RL = 8

Ω

Vcc (V)

Ω

RL = 16

Ω

Figure 37: Current consumption vs. standby

voltage at Vcc=5V

12/29

Electrical characteristics TS4984

Figure 38: Current consumption vs. standby

voltage at Vcc=3.3V

Vcc = 3.3V

No Loads

Tamb=25°C

Figure 39: Current consumption vs. standby

voltage at Vcc=2.6V

Figure 41: THD+N vs. output power

10

RL = 4

Ω

F = 20Hz

Av = 2

Cb = 1µF

1

BW < 125kHz

Tamb = 25°C

0.1

THD+N (%)

0.01

1E−3 0.01 0.1 1

Vcc=2.2V

Vcc=2.6V

Vcc=3.3V

Vcc=5V

Pout (W)

Figure 42: THD+N vs. output power

10

RL = 8

THD+N (%)

F = 20Hz

Av = 2

1

Cb = 1µF

BW < 125kHz

Tamb = 25°C

0.1

Ω

Vcc=2.2V

Vcc=2.6V

Vcc=3.3V

Vcc=5V

Vcc = 2.6V

No Loads

Tamb=25°C

Figure 40: Current consumption vs. standby

voltage at Vcc=2.2V

Vcc = 2.2V

No Loads

Tamb=25°C

0.01

1E−3

1E−3 0.01 0.1 1

Pout (W)

Figure 43: THD+N vs. output power

10

RL = 16

Ω

F = 20Hz

Av = 2

1

Cb = 1µF

BW < 125kHz

Tamb = 25°C

0.1

THD+N (%)

0.01

1E−3

1E−3 0.01 0.1 1

Vcc=2.2V

Vcc=2.6V

Vcc=3.3V

Vcc=5V

Pout (W)

13/29

TS4984 Electrical characteristics

1E−3 0.01 0.1 1

0.1

1

10

Vcc = 3.3V

Vcc = 5V

Vcc = 2.6V

Vcc = 2.2V

RL = 4

Ω

F = 20kHz

Av = 2

Cb = 1µF

BW < 125kHz

Tamb = 25°C

THD+N (%)

Pout (W)

1E−3 0.01 0.1 1

0.1

1

10

Vcc = 3.3V

Vcc = 5V

Vcc = 2.6V

Vcc = 2.2V

RL = 8

Ω

F = 20kHz

Av = 2

Cb = 1µF

BW < 125kHz

Tamb = 25°C

THD+N (%)

Pout (W)

Figure 44: THD+N vs. output power

10

RL = 4

Ω

F = 1kHz

Av = 2

Cb = 1µF

1

BW < 125kHz

Tamb = 25°C

0.1

THD+N (%)

0.01

1E−3 0.01 0.1 1

Vcc = 2.2V

Vcc = 2.6V

Vcc = 3.3V

Vcc = 5V

Pout (W)

Figure 45: THD+N vs. output power

10

RL = 8

THD+N (%)

F = 1kHz

Av = 2

Cb = 1µF

1

BW < 125kHz

Tamb = 25°C

0.1

Ω

Vcc = 2.2V

Vcc = 2.6V

Vcc = 3.3V

Vcc = 5V

Figure 47: THD+N vs. output power

Figure 48: THD+N vs. output power

0.01

1E−3 0.01 0.1 1

Pout (W)

Figure 46: THD+N vs. output power

10

RL = 16

Ω

F = 1kHz

Av = 2

Cb = 1µF

1

BW < 125kHz

Tamb = 25°C

0.1

THD+N (%)

0.01

1E−3 0.01 0.1 1

Vcc = 2.2V

Vcc = 2.6V

Vcc = 3.3V

Vcc = 5V

Pout (W)

Figure 49: THD+N vs. output power

10

RL = 16

Ω

F = 20kHz

Av = 2

Cb = 1µF

BW < 125kHz

1

Tamb = 25°C

THD+N (%)

0.1

1E−3 0.01 0.1 1

Vcc = 2.2V

Vcc = 2.6V

Vcc = 3.3V

Vcc = 5V

Pout (W)

14/29

Electrical characteristics TS4984

2.5 3.0 3.5 4.0 4.5 5.0

70

75

80

85

RL=16

Ω

Av = 10

Cb = 1µF

THD+N < 0.7%

Tamb = 25°C

RL=4

Ω

RL=8

Ω

Signal to Noise Ratio (dB)

Power Supply Voltage (V)

Figure 50: THD+N vs. frequency

RL=4

Ω

Av=2

0.1

Cb = 1µF

Bw < 125kHz

Tamb = 25°C

Vcc=2.2V, Po=40mW

THD + N (%)

0.01

100 1000 10000

Vcc=5V, Po=1W

Frequency (Hz)

Figure 51: THD+N vs. frequency

RL=8

Ω

Av=2

0.1

Cb = 1µF

Bw < 125kHz

Tamb = 25°C

Vcc=5V, Po=O.8W

Figure 53:

SIgnal to noise ratio vs. power supply

with unweighted filter (20Hz to 20kHz)

100

95

RL=16

Ω

RL=8

Ω

90

Signal to Noise Ratio (dB)

85

20k20

2.5 3.0 3.5 4.0 4.5 5.0

RL=4

Ω

Power Supply Voltage (V)

Av = 2

Cb = 1µF

THD+N < 0.7%

Tamb = 25°C

Figure 54: SIgnal to noise ratio vs. pwr supply

with unweighted filter (

20Hz to 20kHz)

Vcc=2.2V, Po=70mW

THD + N (%)

0.01

100 1000 10000

Frequency (Hz)

Figure 52: THD+N vs. frequency

RL=16

Ω

Av=2

0.1

Cb = 1µF

Bw < 125kHz

Tamb = 25°C

THD + N (%)

0.01

100 1000 10000

Vcc=5V, Po=O.5W

Vcc=2.2V, Po=70mW

Frequency (Hz)

20k20

Figure 55: SIgnal to noise ratio vs. power

supply with A weighted filter

105

100

RL=8

RL=4

95

Signal to Noise Ratio (dB)

90

20k20

2.5 3.0 3.5 4.0 4.5 5.0

Ω

Power Supply Voltage (V)

Ω

RL=16

Ω

Av = 2

Cb = 1µF

THD+N < 0.7%

Tamb = 25°C

15/29

TS4984 Electrical characteristics

100 1000 10000

-120

-100

-80

-60

-40

-20

0

Vcc = 2.6V

Av = 2

Pout = 180mW

RL = 8

Ω

BW < 125kHz

Tamb = 25 C

L to R

R to L

Crosstalk (dB)

Frequency (Hz)

100 1000 10000

-120

-100

-80

-60

-40

-20

0

Vcc = 2.2V

Av = 2

Pout = 70mW

RL = 8

Ω

BW < 125kHz

Tamb = 25 C

L to R

R to L

Crosstalk (dB)

Frequency (Hz)

246810

10

15

20

25

30

35

40

45

50

A Weighted Filter

Unweighted Filter

Vcc = 2.2V to 5V

Cb = 1µF

RL = 8Ω

Tamb = 25°C

Output Noise Voltage ( Vrms)

Closed Loop Gain

Figure 56: SIgnal to noise ratio vs. power

supply with A weighted filter

95

90

RL=16

Ω

RL=8

85

RL=4

Ω

Signal to Noise Ratio (dB)

80

2.5 3.0 3.5 4.0 4.5 5.0

Power Supply Voltage (V)

Ω

Av = 10

Cb = 1µF

THD+N < 0.7%

Tamb = 25°C

Figure 57: Crosstalk vs. frequency

0

Vcc = 5V

Av = 2

-20

Pout = 1W

RL = 8

Ω

BW < 125kHz

Tamb = 25 C

L to R

R to L

Crosstalk (dB)

-100

-40

-60

-80

Figure 59: Crosstalk vs. frequency

Figure 60: Crosstalk vs. frequency

-120

100 1000 10000

Frequency (Hz)

Figure 58: Crosstalk vs. frequency

0

Vcc = 3.3V

Av = 2

-20

Pout = 300mW

RL = 8

-40

-60

-80

Crosstalk (dB)

-100

-120

16/29

Ω

BW < 125kHz

Tamb = 25 C

L to R

100 1000 10000

Frequency (Hz)

R to L

Figure 61: Output noise voltage, device ON

Electrical characteristics TS4984

Figure 62: Output noise voltage, device in

standby

3.00

2.75

2.50

2.25

2.00

1.75

1.50

1.25

1.00

Output Noise Voltage ( Vrms)

0.75

0.50

0.25

0.00

Unweighted Filter

A Weighted Filter

Vcc = 2.2V to 5V

Cb = 1µF

RL = 8

Ω

Tamb = 25°C

246810

Closed Loop Gain

Figure 63: Power derating curves

3.5

3.0

2.5

2.0

1.5

1.0

0.5

No Heat sink

QFN16 Package Power Dissipation (W)

0.0

0 25 50 75 100 125 150

Mounted on 4-layer PCB with via

Mounted on 2-layer PCB

Ambiant Temperature ( C)

17/29

TS4984 Application Information

4 Application Information

The TS4984 integrates two monolithic power amplifiers with a BTL (Bridge Tied Load) output type

(explained in more detail in Section 4.1). For this discussion, only the left-channel amplifier will be

referred to.

Referring to the schematic in Figure 64, we assign the following variables and values:

V

=IN-L

in

V

=VO-L, V

out1

= Rin-L, R

R

in

C

= Cfeed-L

feed

Figure 64: Typical application schematic - left channel

out2

= Rfeed-L

feed

=VO+R

Cfeed = Cfeed-L

GND

VCC

Cin = Cin-LInput L

Rin = Rin-L

Vin-

Vin+

+

Cb

1u

IN-L

=

IN+L

=

Standby

Bypass

VCC1

-

+

Bias

VCC2

-

AV = -1

+

Rfeed = Rfeed-L

+

Cs

1u

TS4984

Vout 1

Vout 2

VO-L

=

RL

VO+L

=

4.1 BTL configuration principle

BTL (Bridge Tied Load) means that each end of the load is connected to two single-ended output

amplifiers. Thus, we have:

Single-ended output 1 = V

Single-ended output 2 = V

out1=Vout

=-V

out2

(V),

(V), V

out

out1-Vout2

=2V

out

(V)

The output power is:

2V

()

P

out

-------------------------------------=

outRMS

R

2

L

For the same power supply voltage, the output power in a BTL configuration is four times higher than the

output power in a single-ended configuration.

18/29

Application Information TS4984

4.2 Gain in typical application schematic

The typical application schematic (Figure 64) is shown on page 18.

In the flat region (no C

effect), the output voltage of the first stage is:

in

V

For the second stage: V

out2

=-V

out1

(V)

The differential output voltage is:

V

out2Vout1

The differential gain, referred to as G

V

is in phase with Vin and V

out2

loudspeaker should be connected to V

for greater convenience, is:

v

G

v

is phased 180° with Vin. This means that the positive terminal of the

out1

out2

4.3 Low and high frequency response

In the low frequency region, C

starts to have an effect. Cin forms with Rin a high-pass filter with a -3dB

in

cut-off frequency:

R

feed

V–in()

out1

--------------- (V)=

R

in

R

– 2V

V

–

out2Vout1

------------------------------------ 2

V

in

in

--------------- (V)=

and the negative to V

1

CL

-------------------------- (Hz)=

2πR

inCin

F

feed

R

in

R

feed

---------------==

R

in

out1

.

In the high frequency region, you can limit the bandwidth by adding a capacitor (C

. It forms a low-pass filter with a -3dB cut-off frequency. FCH is in Hz.

R

feed

F

----------------------------------------

CH

2πR

1

feedCfeed

(Hz)=

) in parallel with

feed

19/29

TS4984 Application Information

The following graph (Figure 65) shows an example of C

Figure 65: Frequency response gain versus C

10

5

0

-5

-10

Gain (dB)

-15

-20

-25

10 100 1000 10000

Cin = 82nF

& C

in

Cin = 470nF

Cin = 22nF

Frequency (Hz)

Cfeed = 330pF

4.4 Power dissipation and efficiency

Hypotheses:

l

Voltage and current in the load are sinusoidal (V

l

Supply voltage is a pure DC source (Vcc).

out

Regarding the load we have:

and C

in

feed

Cfeed = 680pF

Cfeed = 2.2nF

Rin = Rfeed = 22k

Tamb = 25°C

and I

out

influence.

feed

).

Ω

V

out

= V

PEAK

sinωt (V)

and

V

out

=

-------------- (A)

I

out

R

L

and

2

2R

L

V

PEAK

=

P

------------------------- (W)

out

Therefore, the average current delivered by the supply voltage is:

V

I

CC

AVG

PEAK

= 2

------------------- (A)

πR

L

The power delivered by the supply voltage is:

P

supply

⋅= W()

V

CCICC

AVG

20/29

Application Information TS4984

Then, the power dissipated by each amplifier is:

–= W()

P

out

CC

L

–⋅= W()

P

outPout

P

P

diss

diss

P

supply

22V

------------------------

π R

and the maximum value is obtained when:

∂P

--------------------- = 0

∂P

diss

out

and its value is:

2

2V

cc

------------ -= W()

π2R

L

Note:

P

dissmax

This maximum value is only depending on power supply voltage and load values.

The efficiency, η, is the ratio between the output power and the power supply:

πV

P

--------------------- =

η =

P

supply

The maximum theoretical value is reached when V

π

----- = 78.5%

4

out

------------------------4V

= VCC, so that:

PEAK

PEAK

CC

The TS4984 has two independent power amplifiers, and each amplifier produces heat due to its power

dissipation. Therefore, the maximum die temperature is the sum of the each amplifier’s maximum power

dissipation. It is calculated as follows:

In most cases, P

diss L

P

P

= P

= Power dissipation due to the left channel power amplifier.

diss L

= Power dissipation due to the right channel power amplifier.

diss R

diss R

, giving:

Total P

Tot al P

diss

diss=Pdiss L+Pdiss R

2P

dissL

(W)=

(W)

or, stated differently:

42V

CC

Total P

diss

------------------------P

π R

L

2P

–= W()

out

out

21/29

TS4984 Application Information

4.5 Decoupling the circuit

Two capacitors are needed to correctly bypass the TS4984. A power supply bypass capacitor C

bias voltage bypass capacitor C

C

has particular influence on the THD+N in the high frequency region (above 7 kHz) and an indirect

S

influence on power supply disturbances. With a value for C

.

B

of 1 µF, you can expect similar THD+N

S

and a

S

performances to those shown in the datasheet. For example:

l

In the high frequency region, if CS is lower than 1 µF, it increases THD+N and disturbances on the

power supply rail are less filtered.

l

On the other hand, if CS is higher than 1 µF, those disturbances on the power supply rail are more

filtered.

C

has an influence on THD+N at lower frequencies, but its function is critical to the final result of PSRR

b

(with input grounded and in the lower frequency region), in the following manner:

l

If Cb is lower than 1µF, THD+N increases at lower frequencies and PSRR worsens.

l

If Cb is higher than 1µF, the benefit on THD+N at lower frequencies is small, but the benefit to PSRR

is substantial.

Note that C

has a non-negligible effect on PSRR at lower frequencies. The lower the value of Cin, the

in

higher the PSRR.

4.6 Wake-up time, T

WU

When the standby is released to put the device ON, the bypass capacitor Cb will not be charged

immediately. As C

is directly linked to the bias of the amplifier, the bias will not work properly until the C

b

voltage is correct. The time to reach this voltage is called wake-up time or TWU and specified in electrical

characteristics table with C

If C

has a value other than 1 µF, please refer to the graph in Figure 66 to establish the wake-up time

b

=1µF.

b

value.

b

Due to process tolerances, the maximum value of wake-up time could be establish by the graph in

Figure 67.

Figure 66: Typical wake-up time vs. C

600

Tamb=25°C

Startup Time (ms)

Note:

22/29

500

400

300

200

100

0

0.1

Vcc=2.6V

1234

Bypass Capacitor Cb ( F)

Bypass capacitor Cb as also a tolerance of typically +/-20%. To calculate the wake-up time with this tolerance,

refer to the previous graph (considering for example for C

Vcc=3.3V

Vcc=5V

b

4.7

Figure 67: Maximum wake-up time vs. C

Tamb=25°C

600

500

400

300

200

Max. Startup Time (ms)

100

0

= 1 µF in the range of 0.8 µF ≤ 1µF≤ 1.2 µF).

b

Vcc=2.6V

1234

Bypass Capacitor Cb ( F)

Vcc=3.3V

Vcc=5V

b

4.70.1

Application Information TS4984

4.7 Shutdown time

When the standby command is set, the time required to put the two output stages in high impedance and

the internal circuitry in shutdown mode is a few microseconds.

Note:

In shutdown mode, Bypass pin and Vin- pin are short-circuited to ground by internal switches. This allows for

the quick discharge of the C

and Cin capacitors.

b

4.8 Pop performance

Pop performance is intimately linked with the size of the input capacitor C

capacitor C

The size of C

.

b

is dependent on the lower cut-off frequency and PSRR values requested. The size of C

in

is dependent on THD+N and PSRR values requested at lower frequencies.

Moreover, C

determines the speed with which the amplifier turns ON. In order to reach near zero pop

b

and click, the equivalent input constant time is:

must not reach the τ

Figure 68: τ

max. versus bypass capacitor

in

tin=(Rin+2kΩ)xCin (s) with R

maximum value as indicated in the graph below in Figure 68.

in

Tamb=25°C

160

Vcc=3.3V

120

Vcc=2.6V

≥ 5kΩ

in

and the bias voltage bypass

in

b

80

in max. (ms)

40

0

1234

Bypass Capacitor Cb ( F)

Vcc=5V

By following previous rules, the TS4984 can reach near zero pop and click even with high gains such as

20 dB.

Example calculation

With R

value which gives a lower cut-off frequency equal to 18.5 Hz. In this case, (R

When referring to the previous graph, if C

=22kΩ and a 20 Hz, -3 db low cut-off frequency, Cin= 361 nF. So, Cin=390 nF with standard

in

+2kΩ)xCin=9.36ms.

in

=1 µF and Vcc = 5 V, we read 20 ms max. This value is twice

b

as high as our current value, thus we can state that pop and click will be reduced to its lowest value.

Minimizing both C

and the gain benefits both the pop phenomena, and the cost and size of the

in

application.

23/29

TS4984 Application Information

R1LCinL

R2L

VCC

+

Cs

+

Cb

Neg. Input LEFT

8 Ohms

LEFT Spe ake r

8 Ohms

RIGHT Spea ker

R1R

CinR

R2R

Neg. Inpu t RI GHT

StandBy

Control

R1LCinL

Pos. Input LEFT

R1R

CinR

Pos. Input RIGHT

R2L

R2R

Bias

StandBy

VCC1GND1

Bypas sL

GND2 VCC2

VO-L

VO+L

VO-R

VO+R

IN-L

IN+L

IN+R

IN-R

+

-

+

-

+

-

AV = -1

+

-

AV = -1

BypassR

TS49 84

4.9 Application example: Differential-input BTL power stereo amplifier

The schematic in Figure 69 shows how to design the TS4984 to work in differential-input mode. For this

discussion, only the left-channel amplifier will be referred to.

Let:

R

1R=R2L=R1

C

= C

inR

The gain of the amplifier is:

, R2R=R2L=R

inL=Cin

2

R2

Gvdif = 2

-------

×

R1

In order to reach the optimal performance of the differential function, R

maximum.

Figure 69: Differential input amplifier configuration

and R2 should be matched at 1%

1

24/29

Application Information TS4984

The value of the input capacitor CIN can be calculated with the following formula, using the -3dB lower

frequency required (where F

is the lower frequency required):

L

C

IN

1

≈

FR2

π

L1

)F(

Note:

This formula is true only if:

=

F

CB

is 5 times lower than F

1

+π

C)RR(2

.

L

)Hz(

B21

The following bill of materials is provided as an example of a differential amplifier with a gain of 2 and a

-3 dB lower cut-off frequency of about 80 Hz.

Table 7: Example of a bill of material

Designator Part Type

= R

R

1L

1R

R

= R

2L

2R

C

= C

inR

inL

C

b=CS

U1 TS4984

20kΩ / 1%

20kΩ / 1%

100nF

1µF

25/29

TS4984 Application Information

4.10 Demoboard

A demoboard for the TS4984 is available.

For more information about this demoboard, please refer to Application Note AN2049, which can be

found on www.st.com.

Figure 70 shows the schematic of the demoboard. Figure 71, Figure 72 and Figure 73 show the

component locations, top layer and bottom layer respectively.

Figure 70: Demoboard schematic

C1

R1

Neg. Inp ut L

Pos. Input L

Pos. Input R

Neg. Inp ut R

Vcc

GND

Cn1

C2

GND

Cn2

GND

Cn3

Jumper J 1

GND

Cn5

GND

Cn6

R2

C3

R3

VCC

Cn8

1

2

3

+

C8

1u

C4

R5

C5

R6

IN-L

1

IN+L

2

R4

Standby

12

Bypass L

3

R7

IN+R

10

IN-R

9

Bypass R

11

C6

R8

VCC

+

C7

C9

1u

100n F

145

VCC1

-

+

Bias

+

-

-

AV = -1

+

-

AV = -1

+

GND1

GND2 VCC2

6 13

VO-L

VO+L

VO-R

VO+R

U1

16

Cn4

Cn7

Neg. Outp ut L

Pos. Output L

Neg. Outp ut R

Pos. Output R

15

8

7

*

26/29

Application Information TS4984

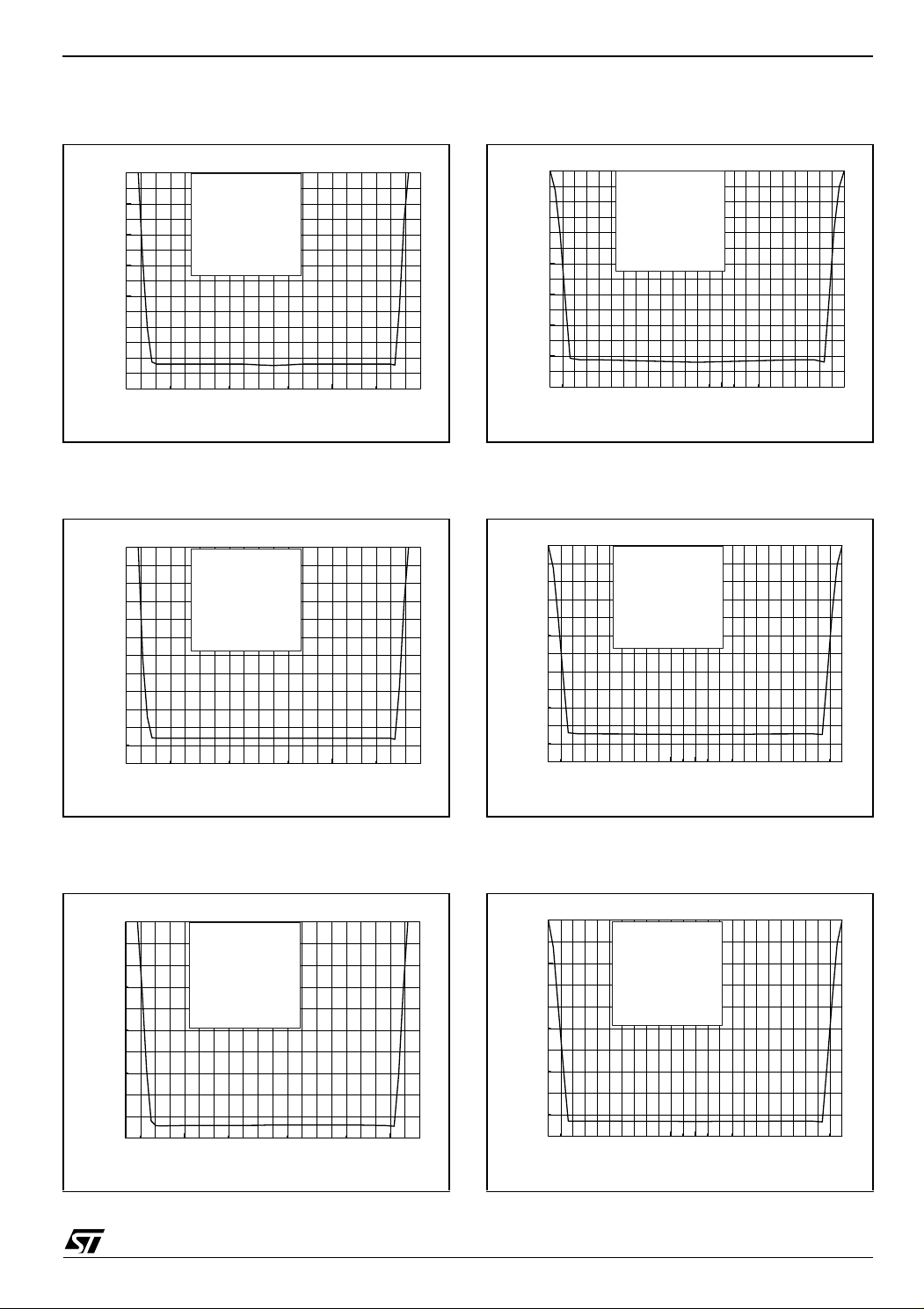

Figure 71: Components location Figure 72: Top layer

Figure 73: Bottom layer

27/29

TS4984 Package Mechanical Data

5 Package Mechanical Data

5.1 Dimensions of QFN16 package

DIMENSIONS

DIMENSIONS

DIMENSIONS

DIMENSIONS

mm

mm

mm

mm

MAX.

MAX.

MAX.

MAX.

0.9 1.00.8

0.9 1.00.8

0.9 1.00.8

0.02 0.05

0.02 0.05

0.02 0.05

0.20

0.20

0.20

0.25 0.300.18

0.25 0.300.18

0.25 0.300.18

4.0

4.0

4.0

4.0

4.0

4.0

0.50

0.50

0.50

0.40 0.500.30

0.40 0.500.30

0.40 0.500.30

4.15

4.15

2.62.1

2.62.1

2.62.1

4.15

4.15

2.62.1

2.62.1

2.62.1

*

*

* The Exposed Pad is connected to Ground.

* The Exposed Pad is connected to Ground.

REF

REF

REF

REF

A

A

A

A1

A1

A1

A3

A3

A3

b

b

b

D

D

D

D2

D2

D2

E

E

E

E2

E2

E2

e

e

e

K

K

K

L

L

L

r

r

r

MIN. TYP.

MIN. TYP.

MIN. TYP.

MIN. TYP.

3.85

3.85

3.85

3.85

0.2

0.2

0.2

0.11

0.11

5.2 Footprint recommended data

A

A

F

B

B

F

G

G

C

C

FOOTPRINT DATA

FOOTPRINT DATA

mm

mm

E

E

A

A

B

B

C

C

D

D

D

D

E

E

F

F

G0.22

G0.22

5.0

5.0

5.0

5.0

0.5

0.5

0.35

0.35

0.45

0.45

2.70

2.70

28/29

TS4984 Revision History

6 Revision History

Date Revision Description of Changes

01 Jan 2005 1 First Release

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

The ST logo is a registered trademark of STMicroelectronics

All other names are the property of their respective owners

All other names are the property of their respective owners

© 2004 STMicroelectronics - All rights reserved

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

STMicroelectronics group of companies

www.st.com

www.st.com

29/29

Loading...

Loading...