AM/FM car radio tuner IC with stereo decoder and

Features

FM-part

■ RF AGC generation by RF and IF detection

■ I/Q mixer for 1st FM IF 10.7MHz with image

rejection

■ Mixer for 2nd IF 450kHz

■ Internal 450KHz bandpass filter with bandwidth

control by ISS

■ Fully integrated FM-demodulator with spike

cancellation

AM-part

■ Wide and narrow AGC generation

■ Mixer for 1st IF 10.7MHz, AM upconversion

■ Mixer for 2nd IF 450kHz, AM downconversion

■ Integrated AM-demodulator

■ AM IF- and audio noise blanking

Stereodecoder

■ PLL with adjustment free, fully integrated VCO

■ Automatic pilot dependent mono/stereo

switching

■ Programmable ROLL-OFF compensation

■ High cut and stereo blend-characteristics

programmable

■ Dedicated RDS-mute

■ Internal noise blanker with several threshold

controls

Table 1. Device summary

TDA7540N

intelligent selectivity system (ISS)

LQFP80

Additional features

■ VCO for world tuning range

■ High performance fast PLL for RDS-System

■ IF counter for FM and AM with search stop

signal

■ Quality detector for level, deviation, adjacent

channel and multipath

■ ISS (intelligent selectivity system) for

cancellation of adjacent channel and noise

influences

■ Adjacent channel mute

■ Fully electronic alignment

■ All functions I

Description

The TDA7540N is a high performance tuner

circuit for AM/FM car radio. It contains mixer, IF

amplifier, demodulator for AM and FM,

stereodecoder, quality detection, ISS filter and

PLL synthesizer with IF counter on a single chip.

Use of BICMOS technology allows the

implementation of several tuning functions and a

minimum of external components.

2

C-Bus controlled

Order code Temp range, °CPackage Packing

TDA7540N -40 to 85°C LQFP80 (14x14x1.4mm) Tube

TDA7540NTR -40 to 85°C LQFP80 (14x14x1.4mm) Tape and reel

November 2007 Rev 1 1/76

www.st.com

1

Contents TDA7540N

Contents

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2 Pins description and connection diagrams . . . . . . . . . . . . . . . . . . . . . . 8

2.1 LQFP80 pins connection diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3.1 Globals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3.2 FM section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3.3 AM section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.3.4 Stereodecoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.3.5 PLL Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1 FM section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.1 Mixer1, AGC and 1.IF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.2 Mixer2, limiter and demodulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.3 Quality detection and ISS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.4 Soft mute control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.2 AM section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3 Stereodecoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3.1 Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3.2 Functional description of the noise blanker . . . . . . . . . . . . . . . . . . . . . . 32

4.3.3 Functional description of the multipath-detector . . . . . . . . . . . . . . . . . . 33

4.3.4 Quality detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

4.3.5 AFS control and stereo decoder mute . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.4 PLL and IF counter section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.4.1 PLL frequency synthesizer block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.4.2 IF counter block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.5 I2C-Bus interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

2/76

TDA7540N Contents

5 Software specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.1 Address organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.2 Control register function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.2.1 Data byte specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

6 Appendix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7 Part list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

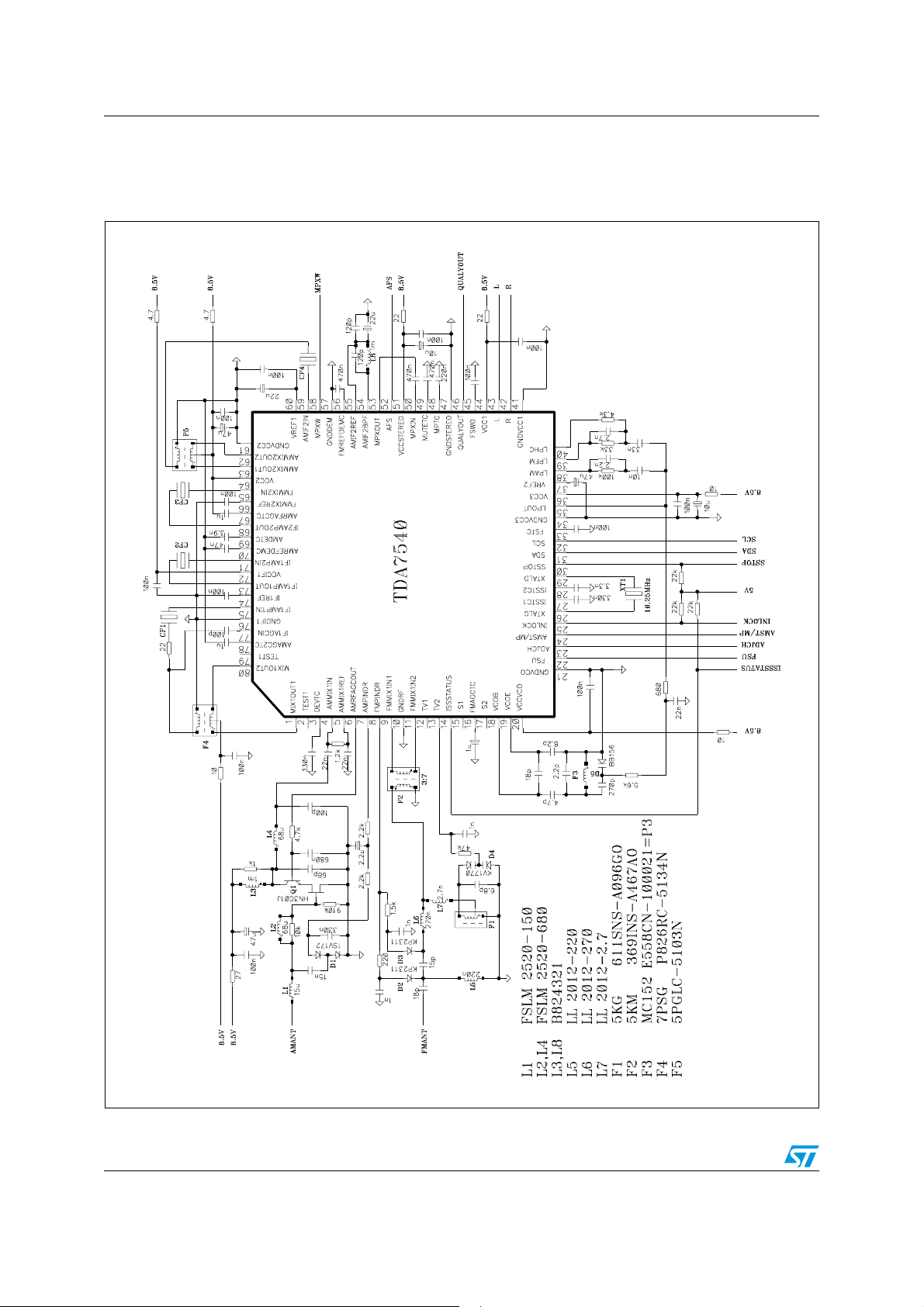

8 Application circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

9 Application notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

10 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

11 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3/76

List of tables TDA7540N

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

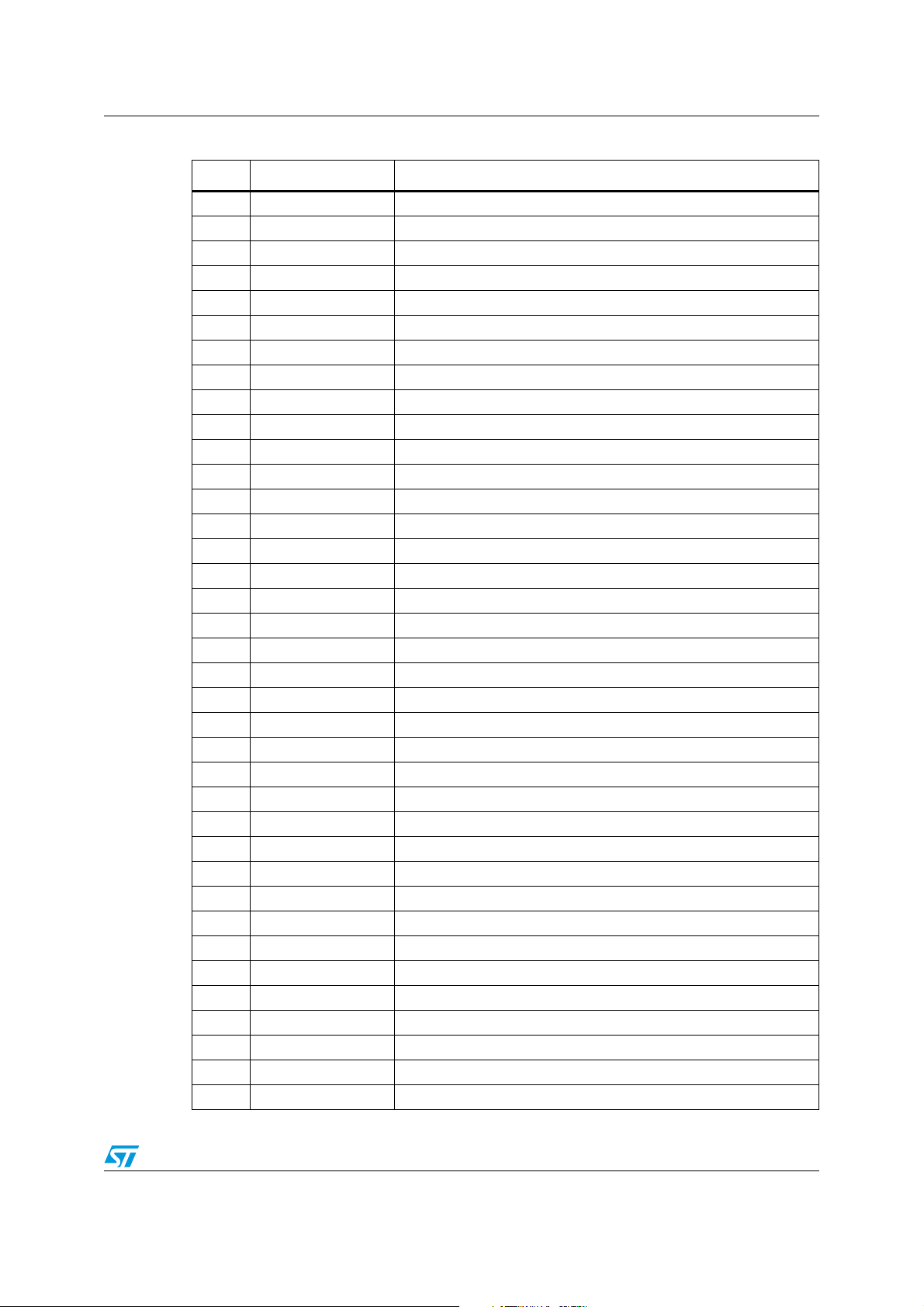

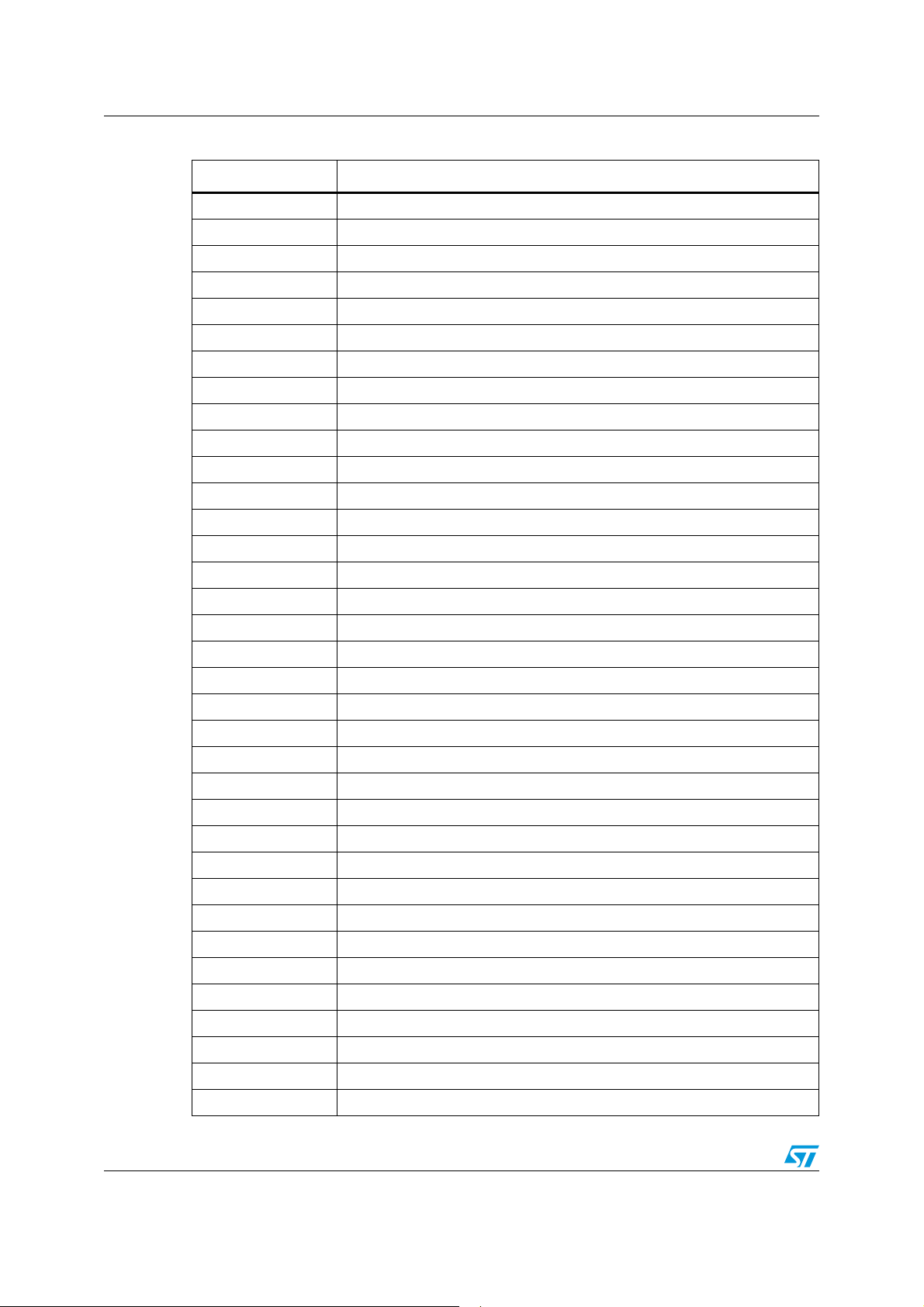

Table 2. Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 3. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 4. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 5. Globals electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 6. FM section electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 7. AM section electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 8. Stereodecoder electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 9. PLL electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 10. Address organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 11. Control register function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 12. Subaddress. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 13. Addr 0 Charge Pump Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 14. Addr 1 PLL counter 1 (LSB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 15. Addr 2 PLL counter 2 (MSB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 16. Addr 3,4 TV1,2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 17. Addr 5 IF counter control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 18. Addr 6 IF counter control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 19. Addr 7 AM control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 20. Addr 8 quality ISS filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 21. Addr 9 quality detection adjacent channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 22. Addr 10 quality detection multipath. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 23. Addr 11 quality deviation detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 24. Addr 12 softmute control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 25. Addr 13 softmute control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 26. Addr 14 VCODIV/PLLREF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 27. Addr 15 FM AGC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 28. Addr 16 AM AGC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 29. Addr 17 FM demodulator fine adjust. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 30. Addr 18 S-meter slider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 31. Addr 19 IF GAIN/XTAL adjust. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 32. Tank adjust . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 33. Addr 21 I/Q FM mixer1 adjust . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 34. Addr 22 AM IF noise blanker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 35. Addr 23 switch control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 36. Addr 24 stereodecoder 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 37. Addr 25 stereodecoder 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 38. Addr 26 stereodecoder 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 39. Addr 27 stereodecoder 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 40. Addr 28 stereodecoder 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 41. Addr 29 stereodecoder 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 42. Addr 30 stereodecoder 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 43. Addr 31 stereodecoder 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 44. Addr 32 stereodecoder 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 45. Addr 33 test tuner control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 46. Addr 34 test tuner control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 47. Addr 35 test tuner control 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 48. Addr 36 test tuner control 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4/76

TDA7540N List of tables

Table 49. Addr 37 test tuner control 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 50. Addr 38 test stereodecoder control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 51. Addr39 test FM demodulator spike blanker and stereo decoder . . . . . . . . . . . . . . . . . . . . 63

Table 52. Block diagram quality detection principle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 53. Functional mode quality detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 54. Part list (application- and measurment circuit) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 55. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5/76

List of figures TDA7540N

List of figures

Figure 1. Block circuit diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 2. LQFP80 pins connection (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 3. Trigger threshold vs. V

Figure 4. Deviation controlled trigger adjustment

Figure 5. Field strength controlled trigger adjustment

Figure 6. Relation between internal and external level-voltagees and setup of stereoblend. . . . . . . 31

Figure 7. Highcut characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 8. Block diagram I/Q mixer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 9. Block diagram VCO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 10. Block diagram keying AGC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 11. Block diagram ISS function. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 12. Block diagram AM part . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 13. Block diagram AM IF noise blanker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 14. Block diagram stereodecoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 15. Block diagram audio noise blanker. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 16. Block diagram multipath detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 17. Block diagram AFS function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 18. Application circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 19. LQFP80 (14x14x1.40mm) mechanical data and package dimensions. . . . . . . . . . . . . . . . 74

PEAK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

6/76

TDA7540N Block diagram

1 Block diagram

Figure 1. Block circuit diagram

7/76

Pins description and connection diagrams TDA7540N

2 Pins description and connection diagrams

2.1 LQFP80 pins connection diagram

Figure 2. LQFP80 pins connection (top view)

IF1AMP1IN

IF1REF

IF1AMP1OUT

VCCIF1

IF1AMP2IN

AMDETC

IF1AMP2OUT

AMRFAGCTC

FMM1X2REF

FMM1X2IN

VCC2

AMMIX2OUT1

AMMIX2OUT2

GNDVCC2

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

VREF1

AMIF2IN

MPXW

GNDDEM

FMREFDEMC

AMIF2REF

AMIF2BPF

MPXOUT

AFS

VCCSTEREO

MPXIN

MUTETC

MPTC

GNDSTEREO

QUALYOUT

FSWO

VCC1

L

R

GNDVCC1

MIX1 OUT1

TEST1

DEVTC

AMMIX1IN

AMMIX1REF

AMRFAGCOUT

AMPINDR

FMPINDR

FMMIX1IN1

GNDRF

FMMIX1IN2

TV1

TV2

ISSSTATUS

FMAGCTC

VCOB

VCOE

VCCVCO

S1

S2

TEST2

MIX1OUT2

79

80

1

2

3

4

5

6

7

8

9

10

12

13

14

15

16

17

18

19

20

21 22 23 24 25

GNDIF1

IF1AGCIN

AMAGC2TC

75 74 73 727071 69 68 67 66 65

76

77

78

26 27 28 29 30

AMREFDEMC

311132 33 34 35 36

64 63 62 61

37 38 39 40

2.2 Pin description

Table 2. Pin description

Pin # Pin name Function

1 MIX1OUT1 Mixer tank 10.7MHz

2 TEST1 Testing I/O pin

3 DEVTC Deviation detector time constant

4 AMMIX1IN AM mixer1 input

5 AMMIX1REF AM mixer1 reference

6 AMRFAGCOUT Output AM RF AGC

7 AMPINDR AM pin diode driver output

8 FMPINDR FM pin diode driver output

9 FMMIX1IN1 FM mixer1 input1

FSU

GNDVCO

ADJCH

AMST/MP

XTALG

STEREO

ISSTC1

ISSTC2

XTALD

SDA

SSTOP

SCL

FSTC

LPOUT

GNDVCC3

VCC3

VREF2

LPAM

LPFM

LPHC

D06AU1653

8/76

TDA7540N Pins description and connection diagrams

Table 2. Pin description (continued)

Pin # Pin name Function

10 GNDRF RF ground

11 FMMIX1IN2 FM mixer1 input2

12 TV1 Tuning voltage preselection1

13 TV2 Tuning voltage preselection2

14 ISSSTATUS ISS filter status output

15 S1 Free programmable switching output

16 FMAGCTC FM AGC time constant

17 S2 Free programmable switching output

18 VCOB VCO input base

19 VCOE VCO output emitter

20 VCCVCO VCO supply

21 GNDVCO VCO ground

22 FSU Unweighted fieldstrength output

23 ADJCH Ident. adjacent channel output

24 AMST/MP AM stereo output / ident. multipath output

25 STEREO Stereo information indication output

26 XTALG Xtal oscillator to MOS gate

27 ISSTC1 Time constant1 ISS filter switch

28 ISSTC2 Time constant2 ISS filter switch

29 XTALD Xtal oscillator to MOS drain

30 SSTOP Search stop output

31 SDA I

32 SCL I

33 FSTC S-meter filtering capacitor

34 GNDVCC3 VCC3 ground

35 LPOUT Op amp output to PLL loop filters

36 VCC3 Supply tuning voltage

37 VREF2 Voltage reference for PLL op amp

38 LPAM Op amp input to PLL loop filters AM

39 LPFM Op amp input to PLL loop filters FM

40 LPHC High current PLL loop filter input

41 GNDVCC1 Digital ground

42 R Stereodecoder output right

43 L Stereodecoder output left

44 VCC1 Digital supply

45 FSWO Weighted fieldstrength output with programmable DC offset

46 Qualyout Stereodecoder quality output

2

C-Bus data

2

C-Bus clock

9/76

Pins description and connection diagrams TDA7540N

Table 2. Pin description (continued)

Pin # Pin name Function

47 GNDSTEREO Strereodecoder ground

48 MPTC Multipath time constant

49 MUTETC Weak signal mute time constant

50 MPXIN Stereodecoder Input

51 VCCSTEREO Stereodecoder supply

52 AFS Alternative frequency search drive

53 MPX/AFAM MPX output / AM AF output

54 AMIF2BPF AM IF2 bandpass filter

55 AMIF2REF Reference voltage AM IF2 amplifier

56 FMREFDEMC FM demodulator reference

57 GNDDEM Ground FM demodulator

58 MPXW MPX Output without ISS filtering

59 AMIF2IN Input AM IF2

60 VREF1 Reference 5V

61 GNDVCC2 Analog ground

62 AMMIX2OUT2 AM Tank 450kHz

63 AMMIX2OUT1 AM Tank 450kHz

64 VCC2 Analog supply

65 FMMIX2IN FM IF1 mixer2 input

66 FMMIX2REF FM IF1 mixer2 reference

67 AMRFAGCTC AM RF AGC time constant

68 IF1AMP2OUT IF1 amplifier2 output

69 AMDETC AM detector capacitor

70 AMREFDEMC AM demodulator reference

71 IF1AMP2IN IF1 amplifier2 input

72 VCCIF1 IF1 supply

73 IF1AMP1OUT IF1 amplifier1 output

74 IF1REF IF1 amplifier reference

75 IF1AMP1IN IF1 amplifier1 input

76 GNDIF1 IF1 ground

77 IF1AGCIN IF1 AGC input

78 AMAGC2TC AM AGC2 time constant

79 TEST2 Testing I/O pin

80 MIX1OUT2 Mixer tank 10.7MHz

10/76

TDA7540N Electrical specifications

3 Electrical specifications

3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

Symbol Parameter Value Units

T

V

amb

T

Supply voltage 9.5 V

S

Ambient temperature -40 to 85 °C

Storage temperature -55 to 150 °C

stg

3.2 Thermal data

Table 4. Thermal data

Symbol Parameter Value Unit

Thermal resistance junction to ambient Max. 55 °C/W

R

th(j-amb)

3.3 Electrical characteristics

3.3.1 Globals

Table 5. Globals electrical characteristics

Symbol Parameter Test conditions Min. Typ. Max. Unit

(T

= 25°C, V

amb

f

= 10.25MHz, in application circuit, unless otherwise specified).

Xtal

CC1

= V

CC2

= V

CC3

= V

CCST

= V

CCVCO

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

=8.5V,

Supply

V

CC1

V

CC2

V

CC3

V

CCVCO

V

CCMIX1

V

CCMIX2

V

CCIF1

V

CCST

I

CC1

I

CC1

I

CC2

I

CC2

Digital supply voltage 7.7 8.5 9 V

Analog supply voltage 7.7 8.5 9 V

Analog tuning voltage 7.7 8.5 9 V

VCO supply voltage 7.7 8.5 9 V

MIX1 supply voltage 7.7 8.5 9 V

MIX2 supply voltage 7.7 8.5 9 V

IF1 supply voltage 7.7 8.5 9 V

Stereo supply voltage 7.7 8.5 9 V

Supply current FM ON 10 12 mA

Supply current AM ON 10 12 mA

Supply current FM ON / VCO:3 65 78 mA

Supply current AM ON 75 90 mA

11/76

Electrical specifications TDA7540N

Table 5. Globals electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 10.25MHz, in application circuit, unless otherwise specified).

Xtal

Symbol Parameter Test conditions Min. Typ. Max. Unit

CC1

= V

CC2

= V

CC3

= V

CCST

= V

CCVCO

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

=8.5V,

I

CC3

I

CCVCO

I

CCMIX1

I

CCMIX1

I

CCMIX2

I

CCIF1

I

CCST

Supply current 2 3 mA

Supply current 8 10 mA

Supply current FM ON 8 10 mA

Supply current AM ON 7 8.5 mA

Supply current AM ON 7 8.5 mA

Supply current 5 6.5 mA

Supply current 12 13.5 mA

Reference voltages

V

REF1

V

REF2

2

C-Bus interface

I

f

SCL

V

V

I

IN

V

Internal reference voltage I

Internal reference voltage I

Clock frequency 400 kHz

Input low voltage 1 V

IL

Input high voltage 3 5 V

IH

Input current -5 5 μA

Output acknowledge voltage IO = 1.6mA 0.4 V

O

= 0mA 4.8 5 5.2 V

REF1

= 0mA 2.4 2.5 2.6 V

REF2

3.3.2 FM section

Table 6. FM section electrical characteristics

Symbol Parameter Test conditions Min. Typ. Max. Unit

Wide band RF AGC

V

9-11

V

9-11

Narrow band IF & keying AGC

V

V

V

(T

amb

f

= 98MHz, dev= 40kHz, f

RF

otherwise specified).

Lower threshold start V16 = 2.5V 83 85 87 dBμV

Upper threshold start V16 = 2.5V 94 96 98 dBμV

77

77

77

Lower threshold start KAGC = off, V

Upper threshold start KAGC = off, V

Lower threshold start with

KAGC

= 25°C, V

CC1

= V

= V

CC2

MOD

KAGC = max,

V

ΔfIF=300KHz

= V

CC3

= 1kHz, f

= 0mV

9-11

= V

CCST

RMS,

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= 0mV

9-11

= 0mV

9-11

RMS

RMS

= V

CCMIX1

= V

CCMIX2

84 86 88 dBμV

96 98 100 dBμV

96 98 100 dBμV

= V

CCIF1

= 8.5V,

12/76

TDA7540N Electrical specifications

Table 6. FM section electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, dev= 40kHz, f

RF

CC1

= V

CC2

= V

MOD

= V

CC3

= 1kHz, f

= V

CCST

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

KAGC = max,

V

= 0mV

V

22

Startpoint KAGC

Δ Control range KAGC ΔV

R

IN

C

IN

Input resistance 10 13 16 kΩ

Input capacitance 2.5 pF

AGC time constant output

V

16

V

16

I

16

I

16

Max. AGC output voltage V

Min. AGC output voltage V

Min. AGC charge current V

Max. AGC discharge current V

AGC pin diode driver output

9-11

ΔfIF=300KHz

f

generates FS level at V

IF1

= +0.8V 16 dB

22

9-11

9-11

9-11

9-11

= 0mV

= 50mV

= 0mV

= 50mV

RMS,

RMS

RMS

RMS,V16

RMS,V16

2.2 V

22

V

REF1

+V

BE

V

0.5 V

= 2.5V -16.5 -12.5 -8.5 μA

= 2.5V 0.8 1.25 1.68 mA

I

8

I

8

AGC OUT, current min. V

AGC OUT, current max. V

9-11

9-11

= 0mV

= 50 mV

, V8 = 2.5V 12 μA

RMS

, V8 = 2.5V -22 -17 -12 mA

RMS

I/Q Mixer1 (10.7MHz)

R

V

R

C

OUT

9,11

g

IN

IN

m

Input resistance differential 10 kΩ

Input capacitance differential 4 pF

Output resistance differential 100 kΩ

Input DC bias 2.2 2.5 2.8 V

Conversion

transconductance

17 ms

F Noise figure 400Ω generator resistance 3 dB

CP

1dB

1dB compression point referred to diff. mixer input 100 dBμV

IIP3 3rd order intermodulation 122 dBμV

IQP I/Q phase adjust PH -7 +8 °

IRR Image rejection ratio ratio wanted/image 30 40 dB

IRR Image rejection ratio with phase adjust 40 46 dB

IF1 Amplifier1 +2 (10.7MHz)

G2 Gain 5 6 7 dB

G1

G1

min

max

Min. gain IFG1 7.5 9 10.5 dB

Max. gain IFG1 16 18 20 dB

13/76

Electrical specifications TDA7540N

Table 6. FM section electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, dev= 40kHz, f

RF

CC1

= V

CC2

= V

MOD

= V

CC3

= 1kHz, f

= V

CCST

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

R

IN

R

OUT

CP

1dB

IIP3 3rd order Intermodulation ref. to 330Ω

Input resistance 260 330 400 W

Output resistance 260 330 400 W

1dB compression point referred to 330Ω input 105 dBμV

input, 9dB gain 126 dBμV

Mixer2 (450kHz)

R

IN

V

65

V

65

Input impedance 260 330 400 Ω

Max. input voltage 119 dBμV

Limiting sensitivity S/N = 20dB 28 dBμV

G Mixer gain 18 dB

Limiter 1 (450kHz)

G

Limiter

Gain 80 dB

Demodulator, audio output

THD

V

R

|ΔV|

|ΔV|

S/N

V

MPXW

MPX

OUT

min

max

MPX output signal Dev.= 75kHz 400 500 600 mV

Output impedance 50 Ω

DC offset fine adjust DEM, MENA=1 8.5 mV

DC offset fine adjust DEM, MENA=1 264 mV

MPXW output signal Dev.= 75kHz 280 350 420 mV

Dev.= 75kHz, V65= 10mV

Dev.= 40kHz,V65 = 10mV

RMS

RMS

76 dB

Quality detection

0.1 %

RMS

RMS

S-meter, unweighted fieldstrength

ΔV

ΔV

ΔV

R

V

V

V

OUT

T

65

22

22

K

Min. input voltage MIX2 30 dBμV

Fieldstrength output V65 = 20dBµV 0.1 V

Fieldstrength output V65 = 80dBµV, SMSL = 0 2.2 2.6 3.0 V

Voltage per decade SMSL = 0 0.8 1 1.2 V

22

Voltage per decade SMSL = 1 1.2 1.5 1.8 V

22

S-meter offset SL, SMSL=1 -15 15 dB

22

Output impedance 280 400 520 Ω

Coefficient temperature 0 ppm/K

14/76

TDA7540N Electrical specifications

Table 6. FM section electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, dev= 40kHz, f

RF

CC1

= V

CC2

= V

MOD

= V

CC3

= 1kHz, f

= V

CCST

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

Adjacent channel gain

G

min

G

max

Gain minimum ACG=0 32 dB

Gain maximum ACG=1 38 dB

Adjacent channel filter

f

HP

f

BP

f

-20dB

-3dB frequency highpass ACF=0 100 kHz

Centre frequency ACF=1 100 kHz

Attenuation 20dB 70 kHz

Adjacent channel output

R

V

V

OUT

23

23

Output voltage low 0.1 V

Output voltage high 4.9 V

Output resistance 3.5 4.5 5.5 kΩ

Multipath channel gain

G

min

G

max

Gain minimum MPG=0 12 dB

Gain maximum MPG=1 23 dB

Multipath bandpass filter

f

BP19

f

BP31

Centre frequency MPF=0 19 kHz

Centre frequency MPF=1 31 kHz

Q Quality factor 5 8 10

Multipath output

Output voltage low 0.1 V

Output voltage high 4.9 V

Output resistance 3 kΩ

R

V

V

OUT

24

24

ISS (intelligent Selectivity System)

Filter 450kHz

f

centre

Centre frequency f

REF_intern

= 450kHz 450 kHz

BW 3dB Bandwidth, -3dB ISS80 = 1 70 80 90 kHz

BW 20dB Bandwidth, -20dB ISS80 = 1 132 150 168 kHz

BW 3dB Bandwidth, -3dB ISS80 = 0 106 120 135 kHz

BW 20dB Bandwidth, -20dB ISS80 = 0 220 250 280 kHz

BW 3dB Bandwidth weather band ISS30 = 1 20 30 40 kHz

BW 20dB -20dB weather band ISS30 = 1 56 80 104 kHz

15/76

Electrical specifications TDA7540N

Table 6. FM section electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, dev= 40kHz, f

RF

CC1

= V

CC2

= V

MOD

= V

CC3

= 1kHz, f

= V

CCST

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

Adjacent channel ISS filter threshold

V

NTH

V

NTH

V

WTH

V

WTH

V

THMP

V

THMP

I

27,I28

I

27,I28

I

27,I28

I

27,I28

I

27,I28

I

27,I28

V

27,V28

V

27,V28

Internal low threshold ACNTH 0 V

Internal high threshold ACNTH 0.24 0.3 0.36 V

Internal low threshold ACWTH 0.2 0.25 0.3 V

Internal high threshold ACWTH 0.76 0.95 1.14 V

Multipath threshold

Internal low threshold MPTH 0.40 0.50 0.60 V

Internal high threshold MPTH 1.0 1.25 1.5 V

ISS filter time constant

Charge current low mid TISS, ISSCTL = 1 -96 -74 -54 μA

Charge current high mid TISS, ISSCTL = 1 -60 μA

Charge current low narrow TISS, ISSCTL = 1 -165 -124 -87 μA

Charge current high narrow

TISS, ISSCTL = 1 -110 μA

Discharge current low TISS, ISSCTL = 0 -0.4 1 2.0 μA

Discharge current high TISS, ISSCTL = 0 10 15 20 μA

Low voltage ISSCTL = 0 0.1 0.2 V

High voltage ISSCTL = 1 4.6 4.9 V

ISS filter switch threshold

V

27,V28

V

27,V28

V

27,V28

V

27,V28

I

I

I

I

DEV

DEV

RATIO

RATIO

3

3

3

3

Threshold ISS on ISSCTL = 0 3 V

Threshold ISS off ISSCTL = 0 1 V

Threshold ISS narrow on ISSCTL = 0 4 V

Threshold ISS narrow off ISSCTL = 0 2 V

Charge current low TDEV -20 -32 -40 μA

Charge current high TDEV -30 -39 -48 μA

Discharge current low TDEV 0.5 1 1.5 μA

Discharge current high TDEV 5.5 8 10.5 μA

Internal low threshold DWTH 30 kHz

WTH

Internal high threshold DWTH 75 kHz

WTH

Referred to threshold DTH 1

min

Referred to threshold DTH 1.5

max

16/76

TDA7540N Electrical specifications

Table 6. FM section electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, dev= 40kHz, f

RF

CC1

= V

CC2

= V

MOD

= V

CC3

= 1kHz, f

= V

CCST

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

Softmute

V

ANT

V

ANT

a

SMmin

a

SMmax

a

SMTHISS

V

ACTH

a

SMAC

I

49

I

49

Upper startpoint SMTH, SMD, SLOPE = 0 10 dBμV

lower startpoint SMTH, SMD, SLOPE = 0 3 dBμV

Min. softmute depth

Max. softmute depth

Mute depth threshold for ISS

filter on

SMD, SLOPE = 0, SMTH

SMD, SLOPE = 0, SMTH

SMCTH 0.2 1 2 dB

Internal AC mute threshold ACM 60 340 mV

AC mute depth ACMD 4 10 dB

Charge current -65 -47.5 -30 μA

Discharge current 1.5 2.5 4.0 μA

S/N MPX

V

= 60dBμV,

ANT

(S+N)/N

dev.= 40kHz,LP=15KHz

deemphasis t = 50

3.3.3 AM section

Table 7. AM section electrical characteristics

(T

= 25°C, V

amb

f

= 98MHz, m= 30%, f

RF

CC1

otherwise specified).

= V

CC2

MOD

= V

= V

CC3

= 400kHz, f

Upper

Upper

18 dB

36 dB

66 69 dB

μs

= V

CCST

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

Symbol Parameter Test conditions Min. Typ. Max. Unit

Global

V

(S+N)/N Signal to Noise Ratio Ref.: V

Usable sensitivity (S+N)/N = 26 dB 25 19 dBµV

ANT_us

ΔV

ANT

a

IF

f

AF

THD Total Harmonic Distortion

V

53

IF2 AGC Range Ref.: V

IF rejection

Frequency response

Ref: V

IF = 10.7MHz

Ref.: V

ΔV

= -3 dB

AF

V

INRF

m = 0.3

V

INRF

m = 0.3

AF output level V

INRF

= 60dBμV, 50 52 dB

INRF

= 60dBμV5055 dB

INRF

= 60dBµV,

INRF

= 60dBµV,

INRF

= 60dBµV, m = 0.8

70 80 dB

3.6 kHz

0.5

0.3

= 120dBµV, m = 0.8

1.0

0.3

= 60dBµV 160 180 200 mV

17/76

%

RMS

Electrical specifications TDA7540N

Table 7. AM section electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, m= 30%, f

RF

CC1

= V

CC2

MOD

= V

= V

CC3

CCST

= 400kHz, f

= V

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

V

V

|I

78max

24

V

71

71

IF output level V

Min. RF AGC threshold

4

Max. RF AGC threshold

Min. IF AGC threshold

Max. IF AGC threshold

Min. DAGC threshold

Max. DAGC threshold

= 60dBµV, m=off 190 mV

INRF

WAGC

WAGC

DAGC

97

109

96.5

109

74

96

| AGC2 charge current seek 80 100 120 μA

CCR Charge current ratio seek/seek off 30

AGC voltage driver output

V

V

| I

6

Max. AGC output voltage 3.5 V

6

Min. AGC output voltage 0.5 V

6

| AGC current 100 μA

AGC pin diode driver output

I

7

AGC driver current -2.6 -2 -1.4 mA

AM Mixer1 (10.7MHz)

R

CP

R

C

OUT

IN

IN

1dB

Input resistance differential 100 kΩ

Input capacitance differential 4 pF

Output impedance differential 100 kΩ

1dB compression point referred to diff. mixer input 112 dBμV

IIP3 3rd order intermodulation 132 dB

F Noise figure 8 dB

AGain 26 dB

RMS

dBμV

dBμV

dBμV

dBμV

dBμV

dBμV

μV

C

min

C

max

C

1-80

Min. capacitance step IF1T 0.55 pF

Max. capacitance IF1T 8.25 pF

IF1T 2 pF

AM Mixer2 (450kHz)

CP

R

71

C

71

1dB

Input resistance 260 330 400 W

Input capacitance 2.5 pF

1dB compression point referred to diff. mixer input 120 dBμV

IIP3 3rd order intermodulation 132 dBμV

F Noise figure 12 dB

18/76

TDA7540N Electrical specifications

Table 7. AM section electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, m= 30%, f

RF

CC1

= V

CC2

MOD

= V

= V

CC3

CCST

= 400kHz, f

= V

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

A Max. gain Mixer2 tank output 34 dB

ΔA Gain control range 20 dB

C

min

C

max

C

62-63

IF noise blanking

Min. cap step IF2T 1.6 pF

Max. cap IF2T 24 pF

IF2T 2 pF

V

V

V

thstep

V

V

t

bl

t

bl

th

th

desth

desth

Min. blanking time 8 μs

Max. blanking time 17 μs

Min internal threshold 10 12.5 15 mV

Max. internal threshold 150 187.5 225 mV

Threshold step 10 12.5 15 mV

Min. desensitivity threshold 2.9 3.2 3.5 V

Max. desensitivity threshold 3.6 4 4.4 V

3.3.4 Stereodecoder

Table 8. Stereodecoder electrical characteristics

Symbol Parameter Test conditions Min. Typ. Max. Unit

Stereodecoder

V

R

G

min

G

max

G

step

SVRR Supply voltage ripple rejection V

a Max. channel separation

(T

V

amb

MPX

= 25°C, V

= 500mV

= V

CC1

mono, f = 1kHz, deemphasis = 50µs, f

rms

circuit, unless otherwise specified).

in

in

MPX input level STD Gain = 2.5 dB 0.5 0.93 V

Input resistance 70 100 130 kΩ

Min. Stereodecoder gain -0.5 0 0.5 dB

Max. Stereodecoder gain 3.15 3.75 4.35 dB

Stereodecoder gain step

resolution

CC2

= V

V

only L/R

CC3

= V

CCST

= V

CCVCO

= V

= V

CCMIX1

= 10.25MHz, in application

Xtal

CCMIX2

= V

1 1.25 1.5 dB

= 100mV, f = 1kHz 54 60 dB

ripple

= 500mV

MPX

rms

stereo

50 dB

CCIF1

= 8.5V,

rms

THD Total harmonic distortion 0.02 0.3 %

(S+N)/N

Signal plus Noise to Noise

ratio

A-weighted, 19kHz notch 85 dB

19/76

Electrical specifications TDA7540N

Table 8. Stereodecoder electrical characteristics (continued)

(T

V

amb

MPX

= 25°C, V

= 500mV

= V

CC1

mono, f = 1kHz, deemphasis = 50µs, f

rms

CC2

= V

CC3

= V

CCST

= V

CCVCO

= V

= V

CCMIX1

= 10.25MHz, in application

Xtal

CCMIX2

= V

CCIF1

= 8.5V,

circuit, unless otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

R

V

V

puafs

puafs

TH1

TH2

Pull up voltage for AFS pin 3.1 3.3 3.5 V

Pull up resistor for AFS pin 25 kΩ

1. threshold for AFS PIN 2.2 2.4 2.6 V

2. threshold for AFS PIN 0.6 0.8 1.0 V

Mono/stereo-switch

V

PTHST1

V

PTHST0

V

PTHMO1

V

PTHMO0

Pilot threshold voltage for Mono->Stereo, PTH = 1 6 10 15 mV

Pilot threshold voltage for Mono->Stereo, PTH = 0 10 14 19 mV

Pilot threshold voltage for Stereo->Mono, PTH = 1 4 8 12 mV

Pilot threshold voltage for Stereo->Mono, PTH = 0 7 12 16 mV

19kHz PLL

f

lock

PLL lock range

Pilot magnitude

20 mV

rms

= 4%

18.9 19.1 kHz

DP Pilot deviation Pilot frequency 19kHz 4 30 %

Deemphasis- and highcut

t

HC50

t

HC75

t

HC25

t

HC37

t

HC50

t

HC75

F

AMCMin

F

AMCMin

Deemphasis time constant

Deemphasis time constant

Deemphasis time constant

Deemphasis time constant

Highcut time constant

Highcut time constant

Min. AM corner frequency

Max. AM corner frequency

DEEMP = 0, DESFT = 1

>> V

V

LEVEL

HCH

DEEMP = 1, DESFT = 1

>> V

V

LEVEL

HCH

DEEMP = 0, DESFT = 0

>> V

V

LEVEL

HCH

DEEMP = 1, DESFT = 0

>> V

V

LEVEL

HCH

DEEMP = 0, DESFT = 1

<< V

V

LEVEL

HCL

DEEMP= 1, DESFT = 1

<< V

V

LEVEL

HCL

DEEMP = 0, DESFT = 1

AMCF

DEEMP = 0, DESFT = 1

AMCF

50 μs

75 μs

25 μs

37.5 μs

150 μs

225 μs

1.06 kHz

3.18 kHz

rms

rms

rms

rms

Stereoblend- and highcut-control

L

L

Gmax

L

Gstep

Gmin

Min. level gain LG -0.5 0 0.5 dB

Max. level gain LG 4.0 4.7 5.2 dB

Level gain step resolution LG 0.4 0.67 0.9 dB

20/76

TDA7540N Electrical specifications

Table 8. Stereodecoder electrical characteristics (continued)

(T

V

amb

MPX

= 25°C, V

= 500mV

= V

CC1

mono, f = 1kHz, deemphasis = 50µs, f

rms

CC2

= V

CC3

= V

CCST

= V

CCVCO

= V

= V

CCMIX1

= 10.25MHz, in application

Xtal

CCMIX2

= V

CCIF1

= 8.5V,

circuit, unless otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

VSBL

VSBL

VSBL

VHCH

VHCH

VHCH

VHCL

VHCL

VHCL

Min. voltage for mono SBC 29 33 %V

min

Max. voltage for mono SBC 54 58 %V

max

Step resolution SBC 4.2 %V

step

Min. voltage for no highcut VHCH 42 46 %V

min

Max. Voltage for no highcut VHCH 61 66 %V

max

Step resolution VHCH 8 %V

step

Min. voltage for full high cut VHCL, MAXHC = 11 11 15 %VHCH

min

Max. voltage for full high cut VHCL, MAXHC = 11 31 33 %VHCH

max

Step resolution VHCL, MAXHC = 11 7.3 %VHCH

step

Carrier and harmonic suppression at the output

a19 Pilot signal f=19kHz V

= 50mV

pilot

rms

50 dB

a38 Subcarrier f=38kHz 75 dB

a57 Subcarrier f=57kHz 62 dB

a76 Subcarrier f=76kHz 90 dB

(2)

(1)

=10kHz, f

mod

=13kHz, f

mod

=1kHz 65 dB

spur

=1kHz 75 dB

spur

Intermodulation

a2 f

a3 f

Traffic radio

REF1

REF1

REF1

REF1

REF1

REF1

a57 Signal f=57kHz 70 dB

SCA - Subsidiary communications authorization

(3)

a67 Signal f=67kHz 75 dB

ACI - adjacent channel interference

(4)

a114 Signal f=114kHz 95 dB

a190 Signal f=190kHz 84 dB

FM noise blanker

(5)

(5)

(5)

0)

V

=0.8V, NBLTH 147 mV

PEAK

V

=0.8V, NBLTH 280 mV

PEAK

19 mV

V

=1.5V, NBCTH 450 mV

PEAK

V

=1.5V, NBCTH 1200 mV

PEAK

V

TRMIN

V

TRMAX

V

TRSTEP

V

TRNOISE

V

TRNOISE

Min. trigger threshold

Max. trigger threshold

Trigger threshold step

Min. noise controlled trigger

threshold

(5)

Max. noise controlled

trigger threshold

21/76

OP

OP

OP

OP

OP

Electrical specifications TDA7540N

Table 8. Stereodecoder electrical characteristics (continued)

(T

V

amb

MPX

= 25°C, V

= 500mV

= V

CC1

mono, f = 1kHz, deemphasis = 50µs, f

rms

CC2

= V

CC3

= V

CCST

= V

CCVCO

= V

= V

CCMIX1

= 10.25MHz, in application

Xtal

CCMIX2

= V

CCIF1

= 8.5V,

circuit, unless otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

PEAK

V

PEAK

V

PEAK

V

PEAKDEV

V

PEAKDEV

V

PEAKFS

V

PEAKFS

T

S

T

S

SR

PEAK

SR

PEAK

V

RECTADJ

Peak voltage NBRR = 00, V

Peak voltage V

Peak voltage V

Min. deviation dependent

peak voltage

Max. deviation dependent

peak voltage

Min. fieldstrength controlled

peak voltage

Max. fieldstrength controlled

peak voltage

Min. blanking time

Max. blanking time

Noise rectifier charge

Noise rectifier charge

Noise rectifier discharge

adjustment

=50mV, f=150kHz 1.6 1.9 2.1 V

MPX

=200mV, f=150kHz 2.2 2.5 2.7 V

MPX

V

=500mV, NBDTH = 11 0.5 0.8 (off) 1.0 V

MPX

V

=500mV, NBDTH= 00 1.7 2.0 2.2 V

MPX

V

=0mV, V

MPX

(fully mono), NBFS = 11

V

=0mV, V

MPX

(fully mono), NBFS = 00

Signal HOLDN in testmode,

NBT

Signal HOLDN in testmode,

NBT

Signal PEAK in testmode,

NBPC=0

Signal PEAK in testmode,

NBPC=1

Signal PEAK in testmode,

NBRR=00, NBSMP=0,

MPPC=0

=0mV 0.5 0.8 1.0 V

MPX

<< V

LEVEL

LEVEL

<< V

SBL

SBL

0.5 0.8 (off) 1.0 V

1.7 2.0 2.2 V

22 μs

38 μs

10 mV/μs

20 mV/μs

0.3 V/ms

OP

OP

Signal PEAK in testmode,

NBRR=01, NBSMP=0,

MPPC=0

Signal PEAK in testmode,

NBRR=10, NBSMP=0,

MPPC=0

Signal PEAK in testmode,

NBRR=11, NBSMP=0,

MPPC=0

Signal PEAK in testmode,

=1V, NBSMP=0,

V

MPTC

MPPC=1, NBRR=01

Signal PEAK in testmode,

=1V,, NBSMP=1,

V

MPTC

MPPC=0, NBRR=01

Signal PEAK in testmode,

V

=1V,, NBSMP=1,

MPTC

MPPC=1A, NBRR=01

V

RECTADJ

V

RECTADJ

V

RECTADJ

V

ADJMP

V

ADJMP

V

ADJMP

Noise rectifier discharge

adjustment

Noise rectifier discharge

adjustment

Noise rectifier discharge

adjustment

Noise rectifier adjustment by

multipath

Noise rectifier adjustment by

strong multipath influence

Noise rectifier adjustment by

multipath and strong multipath

influence

22/76

0.8 V/ms

1.3 V/ms

2.0 V/ms

2.5 V/ms

3.3 V/ms

4.5 V/ms

TDA7540N Electrical specifications

Table 8. Stereodecoder electrical characteristics (continued)

(T

V

amb

MPX

= 25°C, V

= 500mV

= V

CC1

mono, f = 1kHz, deemphasis = 50µs, f

rms

CC2

= V

CC3

= V

CCST

= V

CCVCO

= V

= V

CCMIX1

= 10.25MHz, in application

Xtal

CCMIX2

= V

CCIF1

= 8.5V,

circuit, unless otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

G

AMdelay

AM delay filter attenuation f = 2.2kHz 2.0 dB

Multipath detector

f

CMP

G

BPMP

G

BPMP

G

RECTMP

G

RECTMP

I

CHMP

I

CHMP

I

DISMP

Center frequency of multipathbandpass

Min. band pass gain MPBPG 4 6 8 dB

Max. band pass gain MPBPG 10 12 14 dB

Min. rectifier gain MPRG -1 0 1 dB

Max. rectifier gain MPRG 4.5 7.6 9.5 dB

Rectifier charge current MPCC = 0 0.5 0.8 1.2 μA

Rectifier charge current MPCC = 1 0.2 0.4 0.6 μA

Rectifier discharge current 0.3 0.6 0.8 mA

stereo decoder locked on pilot

tone

19 kHz

Quality detector

a Min. MP influence factor QDC 0.5 0.6 0.7

aMax. MP

influence factor QDC 0.9 1.05 1.2

A Min. noise influence factor QNG 6 dB

A Max. noise influence factor QNG 15 dB

1. Intermodulation Suppression

2 = VO(signal,@1KHz) / VO(spurious, @1KHz) ; fs = (2x10KHz) - 19KHz

a

a

3 = VO(signal,@1KHz) / VO(spurious, @1KHz) ; fs = (3x13KHz) - 38KHz

measured with: 91% stereo signal; 9% pilot signal; fm = 10kHz or 13kHz.

2. Traffic Radio (V.F.) Suppression

57(V,W,F) = VO(signal,@1KHz) / VO(spurious, @1KHz+/-23KHz)

a

measured with: 91% stereo signal; 9% pilot signal; fm=1kHz; 5% sub carrier (f=57kHz, fm=23Hz AM, m=60%)

3. SCA ( Subsidiary Communications Authorization )

67 = VO(signal,@1KHz) / VO(spurious, @9KHz) ; fs = (2x38KHz) - 67KHz

a

measured with: 81% mono signal; 9% pilot signal; fm=1kHz; 10%SCA – sub carrier ( fS = 67kHz, unmodulated ).

4. ACI (Adjacent Channel Interference )

114 = VO(signal,@1KHz) / VO(spurious, @4KHz) ; fs = 110KHz - (3x38KHz)

a

a

190 = VO(signal,@1KHz) / VO(spurious, @4KHz) ; fs = 186KHz - (5x38KHz)

measured with: 90% mono signal; 9% pilot signal; fm=1kHz; 1% spurious signal ( fS = 110kHz or 186kHz, unmodulated).

5. All thresholds are measured inTestmode at the quality output. The thresholds are calculated by

V

- V

V

NBTH

PEAK

PEAK

is adjusted by applying a 150kHz sinewave at MPXIN.

23/76

Electrical specifications TDA7540N

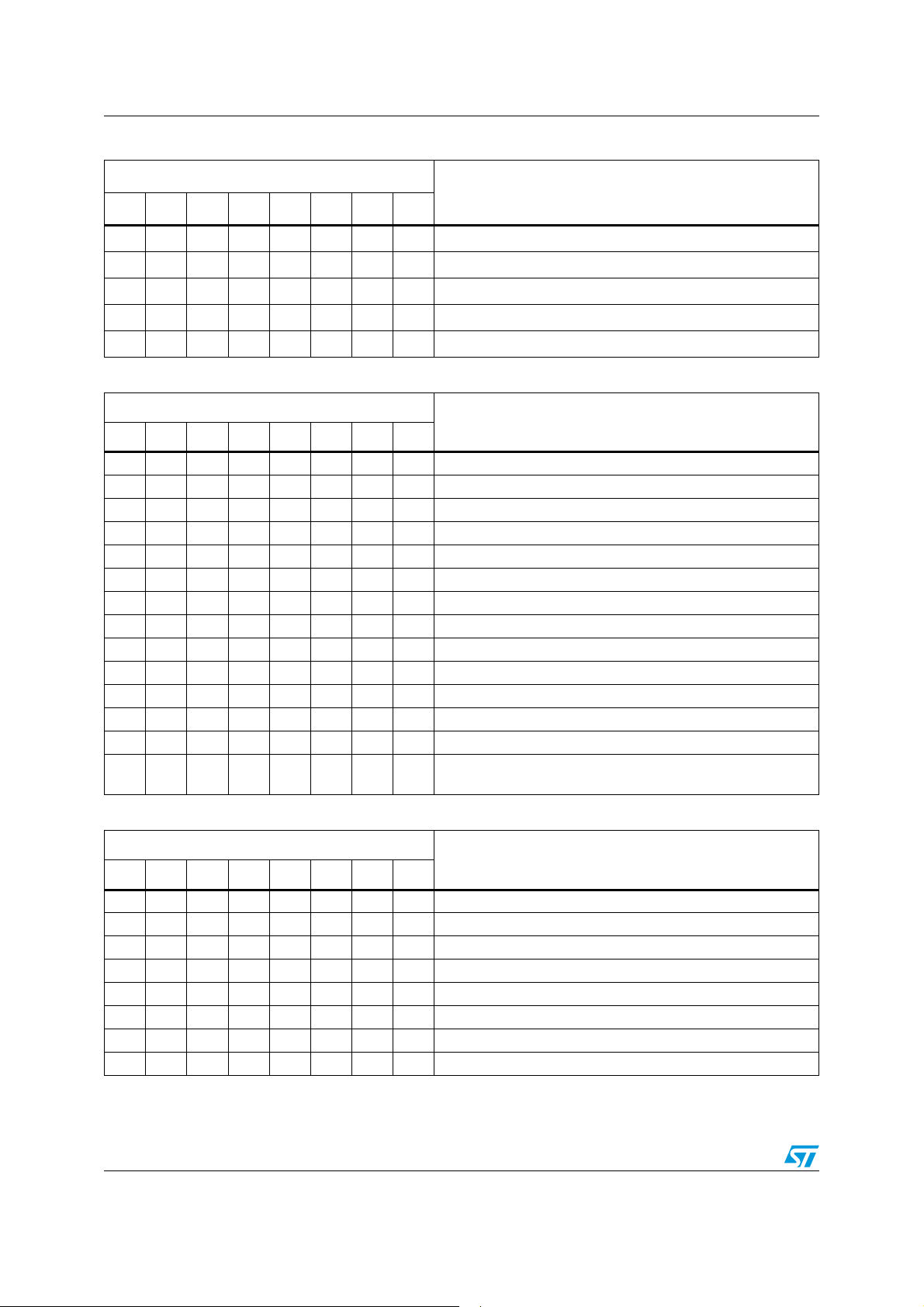

Figure 3. Trigger threshold vs. V

VTH

Min. Trig. T hreshold

280 mV

8 STEPS

147 mV

0.8 V

PEAK

Figure 4. Deviation controlled trigger adjustment

V

PEAK

[V ]

OP

Noise Controlled Tr ig. Threshold

1200 mV (00)

950 mV (01)

700 mV (10)

450 mV (11)

V

Peak1.5 V

00

2.0

01

1.5

10

1.0

0.8

11

20 32.5 45 75

Figure 5. Field strength controlled trigger adjustment

V

PEAK

MONO STER EO

≈

3V

2.0V (00 )

1.6V(01)

NOIS E

ATC_SB OFF (11)

1.4V(10)

Detector off

DEVIATION [KHz]

0.8V

noisy sig nal go od signa l

24/76

E'

TDA7540N Electrical specifications

3.3.5 PLL Section

Table 9. PLL electrical characteristics

(T

= 25°C, V

amb

f

= 98MHz, dev. = 40kHz, f

RF

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

Output of tuning voltages (TV1,TV2)

CC1

= V

CC2

= V

CC3

MOD

= V

CCST

= 1kHz, f

= V

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

R

R

V

OUT

OUT

OUT

Output voltage TVO 0.5 V

-0.5 V

CC3

Output impedance TVMODE=0 32 40 48 kΩ

Output impedance TVMODE=1 16 20 24 kΩ

Xtal reference oscillator

f

LO

C

Step

C

max

Δf/f Deviation versus VCC2

Reference frequency C

= 15pF 10.25 MHz

Load

Min. cap step XTAL 0.75 pF

Max. cap XTAL 23.25 pF

ΔV

= 1V 1.5 ppm/V

CC2

Δf/f Deviation versus temp -40°C < T < +85°C 0.2 ppm/K

Loop filter input/output

-I

I

V

V

I

OUT

I

OUT

IN

IN

OL

OH

Input leakage current VIN = GND, PD

V

= VREF1

Input leakage current

Output voltage Low I

Output voltage High I

Output current, sink V

Output current, source V

IN

PD

= Tristate

OUT

= -0.2mA 0.05 0.5 V

OUT

= 0.2mA

OUT

= 1V to V

OUT

= 1V to V

OUT

= Tristate -0.1 0.1 μA

OUT

-0.1 0.1 μA

V

-

V

CC3

0.5

-1V 10 mA

CC3

-1V -10 mA

CC3

CC3

0.05

-

Voltage controlled oscillator (VCO)

V

f

VCOmin

f

VCOmax

C/N Carrier to Noise

Minimum VCO frequency 50 MHz

Maximum VCO frequency 260 MHz

f

= 200MHz, Δf=1KHz,

VCO

B=1Hz, closed loop

80 dBc

SSTOP, INLOCK, ISSSTATUS outputs (open collector)

V Output voltage low I = -200

μA0.20.5V

V Output voltage high 5 V

-I Output leakage current V = 5V -0.1 0.1 μA

I Output current, sink V = 0.5V-5V 1 mA

Switching outputs S1, S2 (open collector SMODE=1)

V Output voltage low I = -5mA 0.2 0.5 V

25/76

Electrical specifications TDA7540N

Table 9. PLL electrical characteristics (continued)

(T

= 25°C, V

amb

f

= 98MHz, dev. = 40kHz, f

RF

CC1

= V

CC2

= V

CC3

MOD

= V

CCST

= 1kHz, f

= V

CCVCO

= 10.25MHz, in application circuit, unless

Xtal

= V

CCMIX1

= V

CCMIX2

= V

CCIF1

= 8.5V,

otherwise specified).

Symbol Parameter Test conditions Min. Typ. Max. Unit

V Output voltage high V

CC1

V

-I Output leakage current V = 5V -0.5 0.5 μA

I Output current, sink V = 0.5V-V

CC

7mA

Switching outputs S1, S2 (Open emitter SMODE=0)

V Output voltage low I = 0μA0.10.3V

V Output voltage high I = 1mA

V

CC1

-1

V

I Output current, sink V = 5V 7 mA

26/76

TDA7540N Functional description

4 Functional description

4.1 FM section

4.1.1 Mixer1, AGC and 1.IF

FM quadrature I/Q-mixer converts FM RF to IF1 of 10.7MHz. The mixer provides inherent

image rejection and wide dynamic range with low noise and large input signal performance.

The mixer1 tank can be adjusted by software (IF1T). For accurate image rejection the

phase-error of I/Q can be compensated by software (PH)

It is capable of tuning the US FM, US weather, Europe FM, Japan FM and East Europe FM

bands

– US FM = 87.9 to 107.9 MHz

– US weather = 162.4 to 162.55 MHz

– Europe FM = 87.5 to 108 MHz

– Japan FM = 76 to 91 MHz

– East Europe FM = 65.8 to 74 MHz

The AGC operates on different sensitivities and bandwidths in order to improve the input

sensitivity and dynamic range. AGC thresholds are programmable by software

(RFAGC,IFAGC,KAGC). The output signal is a controlled current for pin diode attenuator.

A 10.7MHz programmable amplifier (IFG1) correct the IF ceramic insertion loss and the

costumer level plan application.

4.1.2 Mixer2, limiter and demodulator

In this 2nd mixer stage the first 10.7MHz IF is converted into the second 450kHz IF. A multistage limiter generates signals for the complete integrated demodulator including spike

cancellation (DNB). MPX output DC offset versus noise DC level is correctable by software

(DEM), if tuner softmute is activated.

4.1.3 Quality detection and ISS

Fieldstrength

Parallel to mixer2 input a 10.7MHz limiter generates a signal for digital IF counter and a

fieldstrength output signal. This internal unweighted fieldstrength is used for keying AGC,

adjacent channel and multipath detection and is available at PIN22 (FSU) after +6dB buffer

stage. It is possible to combinate the IF counter result with this FSU via programmable

comparator (SSTH). The behaviour of FSU signal can be corrected for DC offset (SL) and

slope (SMSL). The generated unweighted fieldstrength is externally filtered and used for

softmute function and generation of ISS filter switching signal for weak input level (sm).

Adjacent channel detector

The input of the adjacent channel detector is AC coupled from internal unweighted

fieldstrength. A programmable highpass or bandpass (ACF) and amplifier (ACG) as well as

rectifier determines the influences. This voltage is compared with adjustable comparator1

thresholds (ACWTH, ACNTH). The output signal of this comparator generates a DC level at

PIN27 by programmable time constant. Time control (TISS) for a present adjacent channel

27/76

Functional description TDA7540N

is made by charge and discharge current after comparator1 in an external capacitance. The

charge current is fixed and the discharge current is controlled by I

produces digital signals (ac, ac+) in an additional comparator4. The adjacent channel

information is available as analog output signal after rectifier and +8dB output buffer.

2

C Bus. This level

Multipath detector

The input of the multipath detector is AC coupled from internal unweighted fieldstrength. A

programmable bandpass (MPF) and amplifier (MPG) as well as rectifier determines the

influences. This voltage is compared with an adjustable comparator2 thresholds (MPTH).

The output signal of this comparator2 is used for the "Milano" effect. In this case the

adjacent channel detection is switched off. The "Milano" effect is selectable by I

(MPOFF). The multipath information is available as analog output signal after rectifier and

+8dB output buffer.

2

C Bus

450kHz IF narrow bandpass filter (ISS filter)

The device gets an additional 450KHz IF narrow bandpass filter for suppression of noise

and adjacent channel signal influences. This narrow filter has three switchable bandwidthes,

narrow range of 80kHz, mid range of 120kHz and 30KHz for weather band information.

Without ISS filter the IF bandwidth (wide range) is defined only by ceramic filter chain. The

filter is located between mixer2 and 450kHz limiter stage. The centre frequency is matched

to the demodulator center frequency.

Deviation detector

In order to avoid distortion in audio output signal the narrow ISS filter is switched OFF for

present overdeviation. Hence the demodulator output signal is detected. A lowpass filtering

and peak rectifier generates a signal that is defined by software controlled current (TDEV) in

an external capacitance.

This value is compared with a programmable comparator3 thresholds (DWTH, DTH) and

generates two digital signals (dev, dev+). For weak signal condition deviation threshold is

dependent on FSWO.

ISS switch logic

All digital signals coming from adjacent channel detector, deviation detector and softmute

are acting via switching matrix on ISS filter switch. The IF bandpass switch mode is

controlled by software (ISSON, ISS30, ISS80, CTLOFF). The switch ON of the IF bandpass

is also available by external manipulation of voltage at PIN27. Two application modes are

available (APPM).

The conditions are described in Ta bl e 5 2 .

4.1.4 Soft mute control

The filtered fieldstrength (FSWO) signal is the reference for mute control. The startpoint and

mute depth are programmable (SMTH, SMD) in a wide range. The time constant is defined

by external capacitance. Additional adjacent channel mute function is supported. A

highpass filter with -3dB threshold frequency of 100kHz, amplifier and peak rectifier

generates an adjacent noise signal from MPX output with the same time constant for

softmute. This value is compared with comparator5 thresholds (ACM). For present strong

adjacent channel the MPX signal is additional attenuated (ACMD).

28/76

TDA7540N Functional description

4.2 AM section

The up/down conversion is combined with gain control circuit sensing three input signals,

narrow band information at PIN 54, upconversion signal (IF2AGC) at PIN 71and wide band

information (RFAGC) at PIN 4.This gain control gives two output signals. The first one is a

current for pin diode attenuator and the second one is a voltage for preamplifier. Time

constant of RF- and IF-AGC is defined by internal 100k resistor and external capacitor at

PIN 67. The intervention points for AGC (DAGC,WAGC) are programmable by software.

In order to avoid a misbehaviour of AGC intervention point it is important to know that the

DAGC threshold has to be lower than WAGC threshold !

The oscillator frequency for upconversion-mixer1 is generated by dividing the VCO

frequency after VCO divider (VCOD) and AM predivider(AMD).

Two 10,7MHz ceramic filters before mixer2 input increases 900KHz attenuation.In mixer2

the IF1 is down converted into the IF2 450kHz. After filtering by ceramic filter a 450kHz

amplifier is included with an additional gain control of IF2 below DAGC threshold. Time

constant is defined by capacitance at PIN 78.

Mixer1 and mixer2 tanks are software controlled adjustable (IF1T, IF2T).

The demodulator is a peak detector to generate the audio output signal.

A separate output is available for AMIF stereo (AMST).

AM IF noise blanker

In order to remove in AM short spikes a noise cancellation conception is used in 450KHz IF

AM level. The advantage is to avoid long narrow AGC- and demodulator- time constants,

wich enlarge spike influences on audio signal and makes difficult to remove it in audio path.

The 10.7MHz AM IF signal generates before 10.7 MHz ceramic filter via limitation an

unweighted fieldstrenght signal including slope of noise spike. The comparison of these

detected slope between fast and slow rectifier ignores audio modulation whereby the

threshold of slow rectifier is programmable (AINBT). A comparator activates a pulse

generator.

The duration of this pulse is software programmable (AINT) and is smooth blanking out the

spikes in 450KHz AM mixer2. Additionally this funtionality is controlled by narrow AM

fieldstrenght (AINBD).

4.3 Stereodecoder

4.3.1 Decoder

The stereo decoder-part of the TDA7540N (see Figure 14) contains all functions necessary

to demodulate the MPX-signal like pilot tone-dependent MONO/STEREO-switching as well

as "stereoblend" and "highcut". Adaptations like programmable input gain, roll-off

compensation, selectable deemphasis time constant and a programmable field strength

input allow easy adaption to different applications.

th

The 4

and noise and acts as an anti-aliasing filter for the following switch capacitor filters.

order input filter has a corner frequency of 80kHz and is used to attenuate spikes

29/76

Functional description TDA7540N

Demodulator

In the demodulator block the left and the right channel are separated from the MPX-signal.

In this stage also the 19-kHz pilot tone is canceled. For reaching a high channel separation

the TDA7540 offers an I2C-bus programmable roll-off adjustment, which is able to

compensate the low pass behavior of the tuner section. Within the compensation range an

adjustment to obtain at least 40dB channel separation is possible. The bits for this

adjustment are located together with the level gain adjustment in one byte. This gives the

possibility to perform an optimization step during the production of the car radio where the

channel separation and the header are trimmed.

In addition to that the FM signal can be inverted.

Deemphasis and highcut

The deemphasis low pass allows to choose between a time constant of 50µs/ 75μs

(DEEMP) and 25μs/37.5μs (DESFT). The highcut control range will be in both cases τ

2xτ

. Inside the highcut control range (between VHCH and VHCL) the LEVEL signal is

Deemp

converted into a 5-bit word, which controls the low pass time constant between

τ

Deemp

...3xτ

. Thereby the resolution will remain always 5 bits independently of the

Deemp

absolute voltage range between the VHCH- and VHCL-values.

The highcut function can be switched off by I

2

C-bus .

HC

=

In AM mode (AMON = 1) the bits DEEMP and DESFT together with the AM corner

frequency bits (AMCF1...5) can be used as programmable AM frequency response. The

maximum corner frequency is defined by τ

, the minimum is defined by 3xτ

Deemp

Deemp

19kHz PLL and pilot tone detector

The PLL has the task to lock on the 19kHz pilot tone during a stereo-transmission to allow a

correct demodulation. The included pilot tone-detector enables the demodulation if the pilot

tone reaches the selected pilot tone threshold V

. Two different thresholds are

PTHST

available. The status of the detector output can be checked by reading the status byte of the

TDA7540N via I

2

C-bus or by reading the STEREO pin (pin 25).

Field strength control

The field strength input is used to control the highcut- and the stereoblend-function. In

addition the signal can be also used to control the noise blanker thresholds and as input for

the multipath detector.

Level-input and -gain

As level input for the stereo decoder is used the FSU voltage (pin22). Appling a capacitor at

FSTC (pin33) a desired time constant can by reached together with the internal resistor of

10k between FSU pin and FSTC pin.

In addition to that the LEVEL signal is low pass filtered internally in order to suppress

undesired high frequency modulation on the highcut- and stereoblend-function . The filter is

a combination of a 1

order switched capacitor low pass at 2.2kHz. The second stage is a programmable gain

stage to adapt the LEVEL signal internally . The gain is widely programmable in 8 steps

from 0dB to 4,7dB (step=0.67dB). These 3bits are located together with the Roll-Off bits in

the "Stereo decoder 8"-byte to simplify a possible adaptation during the production of the

car radio.

st

-order RC-low pass at 53kHz (working as anti-aliasing filter) and a 1st-

30/76

TDA7540N Functional description

L

t

r

τ

Stereoblend control

The stereoblend control block converts the internal LEVEL-voltage into a demodulator

compatible analog signal, which is used to control the channel separation between 0dB and

the maximum separation. Internally this control range has a fixed upper limit, which is the

internal reference voltage

V

in 4% steps (see Figure 6).

REF1

To adjust the external LEVEL-voltage to the internal range two values must be defined: the

LEVEL gain L

and VSBL. To adjust the voltage where the full channel separation is

G

reached (VST) the LEVEL gain L

estimate the gain:

The MONO-voltage VMO (0dB channel separation) can be chosen selecting VSBL.

Figure 6. Relation between internal and external level-voltagees and setup of

stereoblend

V

. The lower limit can be programmed between 29 and 58% of

REF1

has to be defined. The following equation can be used to

G

L

G

= V

/FSU@full stereo

REF1

The stereo blend function can be switched ON/OFF using bit Addr25<d2>. Please note that

in AM it must be switched in forced mono!

Highcut control

The highcut control set-up is similar to the stereoblend control set-up: the starting point

VHCH can be set with 2 bits to be 42, 50, 58 or 66% of V

to be 11, 18.3, 25.7 or 33% of VHCH (see Figure 7).

Figure 7. Highcut characteristics

owpass

ime con stant

3

•

Deem p

Deem p

VHCL VHC

whereas the range can be set

REF1

HFieldst

ength

31/76

Functional description TDA7540N

4.3.2 Functional description of the noise blanker

In the automotive environment spikes produced by the ignition or for example the wipermotor disturb the MPX-signal. The aim of the noise blanker part is to cancel the audible

influence of the spikes. Therefore the output of the stereo decoder is held at the actual

voltage for a time between 22

blanker is given inFigure 15.

In a first stage the spikes must be detected but to avoid a wrong triggering on high

frequency (white) noise a complex trigger control is implemented. Behind the trigger stage a

pulse former generates the "blanking"-pulse. An own biasing circuit supplies the noise

blanker in order to avoid any cross talk to the signal path.

Trigg er pa th

The incoming MPX signal is high pass filtered, amplified and rectified. This second order

high pass filter has a corner-frequency of 140kHz. The rectified signal, RECT, is low pass

filtered to generate a signal called PEAK. Also noise with a frequency 140kHz increases the

PEAK voltage. The resulting voltage can be adjusted by use of the noise rectifier discharge

current. The PEAK voltage is fed to a threshold generator, which adds to the PEAK-voltage

a DC-dependent threshold VTH. Both signals, RECT and PEAK+VTH are fed to a

comparator, which triggers a re-triggerable monoflop. The monoflop's output activates the

sample-and-hold circuits in the signal path for the selected duration.

μs and 38μs (programmable). The block diagram of the noise

Automatic noise controlled threshold adjustment (Figure 3)

There are mainly two independent possibilities for programming the trigger threshold:

1. the low threshold in 8 steps (NBLTH)

2. and the noise adjusted threshold in 4 steps (NBCTH).

The low threshold is active in combination with a good MPX signal without any noise; the

PEAK voltage is less than 1V. The sensitivity in this operation is high.

If the MPX signal is noisy (low fieldstrength) the PEAK voltage increases due to the higher

noise, which is also rectified. With increasing of the PEAK voltage the trigger threshold

increases, too. This particular gain is programmable in 4 steps (NBCTH).

Automatic threshold control by the stereoblend voltage (Figure 5)

Besides the noise controlled threshold adjustment there is an additional possibility for

influencing the noise blanker trigger threshold using the bits NBFS. This influence depends

on the stereoblend control.

The point where the MPX signal starts to become noisy is fixed by the RF part. This point is

also the starting point of the normal noise-controlled trigger adjustment. But in some cases

the noise blanker can create a wrong triggering, which create distortion, already in the

region of mono/stereo transition. Therefore a opportunity to control the PEAK voltage by the

stereo blend function it is implemented.

Over deviation detector (Figure 4)

If the system is tuned to stations with a high deviation the noise blanker can trigger on the

higher frequencies of the modulation. To avoid this wrong behavior, which causes noise in

the output signal, the noise blanker offers a deviation-dependent threshold adjustment. By

rectifying the MPX signal a further signal representing the actual deviation is obtained. It is

32/76

TDA7540N Functional description

used to increase the PEAK voltage. Offset and gain of this circuit are programmable in 3

steps (NBDTH) of the stereo decoder-byte (the first step turns off the detector).

Multipath-level

To react on high repetitive spikes caused by a Multipath-situation, the discharge-time of the

PEAK voltage can be decreased depending on the voltage-level at Pin MPout. There are

two ways to do this. One way is to switch on the linear influence of the Multipath-Level on the

PEAK-signal . In this case the discharge slew rate is 1V/ms

1)

. The second possibility is to

activate a function, which switches to the 18k discharge if the Multipath-Level is below 2.5V.

If multipath influence on noise blanker is switched ON than MPF bit has to be set to 0.

1)

The slew rate is measured with R

Discharge

=infinite and V

MPout

=2.5V

AM Mode of Noise Blanker

The TDA7540N offers an AM audio noise blanker too.

If the AM noise blanker is used the AM audio delay filter and the AM audio filter must be

switched on. It is not recommented to use the AM noise blanker without to use the AMIF

noiseblanker inside the tuner.

The noise blanker is activated if the spike is bigger than a fixed threshold

In order to blank the whole spike in AM mode the hold time of the S&H circuit is much longer

than in FM mode (640µs -1.2ms).

4.3.3 Functional description of the multipath-detector

Using the internal Multipath-Detector the audible effects of a multipath condition can be

minimized. A multipath-condition is detected by rectifying the 19kHz spectrum in the