Features

■ Voltage monitored on separate sense

input V

■

Factory-trimmed voltage thresholds in 100 mV

increments from 1.6 V to 5.7 V

■ ±2% voltage threshold accuracy

■ Operating voltage 1.6 V to 6.0 V

■ Open drain output

■ Low supply current of 0.8 µA (typ.)

■ Time delay programmable by external

capacitor

■ Power supply transient immunity

■ Available in SOT23-5 package

■ Operating temperature –40 to 85 °C

SEN

STM1831

Voltage detector with sense input

and external delay capacitor

SOT23-5

Applications

■ Microprocessor reset circuitry

■ Charge voltage monitors

■ Memory battery backup switch circuits

■ Power failure detection circuits

November 2010 Doc ID 18180 Rev 1 1/24

www.st.com

1

Contents STM1831

Contents

1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1 Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3 Typical operating characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

4 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5 DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

6 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7 Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

8 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2/24 Doc ID 18180 Rev 1

STM1831 List of tables

List of tables

Table 1. Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 2. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 3. Operating and AC measurement conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 4. DC and AC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 5. SOT23-5 - 5-lead small outline transistor package mechanical data . . . . . . . . . . . . . . . . . 21

Table 6. STM1831 ordering information scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 7. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Doc ID 18180 Rev 1 3/24

List of figures STM1831

List of figures

Figure 1. Logic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. SOT23-5 pin connections (top view). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 3. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 4. Application hookup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 5. Timing waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 6. Supply current vs. sense voltage, V

Figure 7. Supply current vs. input voltage, V

Figure 8. Detect voltage vs. ambient temperature, V

Figure 9. Detect voltage vs. supply voltage, V

Figure 10. Hysteresis voltage vs. ambient temperature, V

Figure 11. C

pin sink current vs. supply voltage, V

D

Figure 12. Output voltage vs. sense voltage, V

on RST

is 100 kΩ, CD pin open . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 13. Output voltage vs. supply voltage, V

on RST

is 100 kΩ, CD pin open . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 14. Output current vs. supply voltage, V

Figure 15. Relative delay resistance vs. ambient temperature, V

Figure 16. Release delay time vs. delay capacitance, T

Figure 17. Detect delay time vs. delay capacitance, T

Figure 18. RST

Figure 19. RST

output leakage current vs. ambient temperature,

V

CC

= V

SEN

= V

= 6.0 V, CD pin open . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

OUT

output leakage current vs. output voltage, VCC = V

T

= 85 °C, CD pin open . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

A

Figure 20. Sense current vs. supply voltage, V

Figure 21. Sense current vs. ambient temperature, V

Figure 22. AC testing input/output waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 23. SOT23-5 - 5-lead small outline transistor package mechanical drawing . . . . . . . . . . . . . . 21

= 3.0 V, V

CC

= 1.9 V (RST asserted) . . . . . . . . . . . . . . . . . . . . . . 9

SEN

DET

= 2.4 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

DET

= 0 V, VCD = 0.5 V . . . . . . . . . . . . . . . . . . . . 11

SEN

= 2.4 V, TA = 25 °C, external pull-up resistor

DET

= VCC, external pull-up resistor

SEN

= 0 V, V

SEN

= 25 °C. . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

A

= 25 °C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

A

= 1.9 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

SEN

CC

= V

= 2.0 V . . . . . . . . . . . . . . . . . . . . . . . 9

DET

= 2.4 V . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

= 2.4 V . . . . . . . . . . . . . . . . . . . . . . . . 11

DET

= 0.5 V. . . . . . . . . . . . . . . . . . . . . . . 13

RST

SEN

= 5 V, V

CC

SEN

= 6.0 V,

= 6 V, VCD = 0 V . . 13

SEN

= 5 V . . . . . . . . . . . . . . . . . . . . . . . . 16

4/24 Doc ID 18180 Rev 1

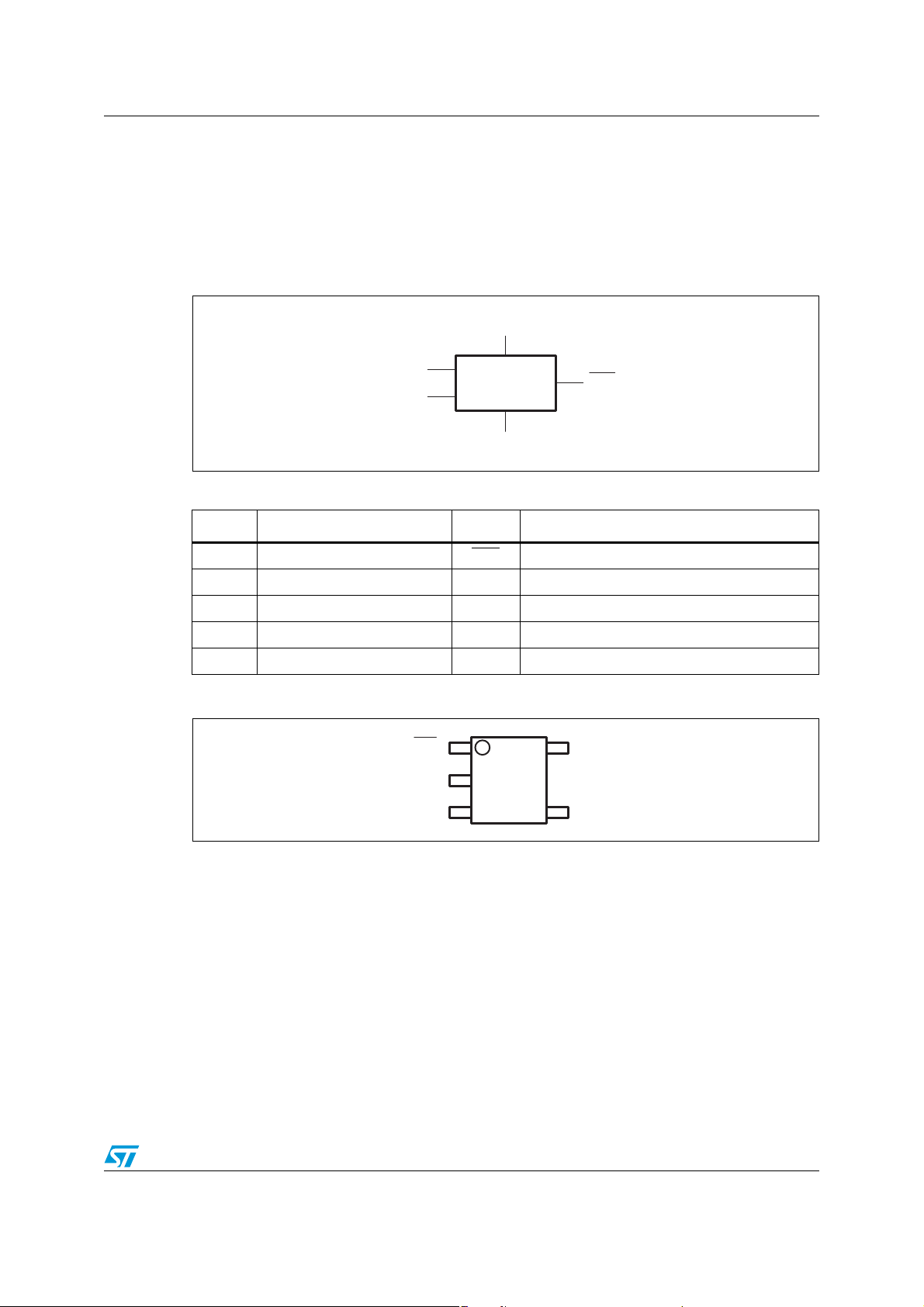

STM1831 Description

1 Description

The STM1831 is a voltage detector with very low current consumption. It monitors a voltage

on a separate input pin (V

down to 0 V. In addition, the delay of the output can be adjusted by an external capacitor.

Figure 1. Logic diagram

.

Table 1. Pin descriptions

Pin Type Name Function

), which is fully functional even if the monitored voltage goes

SEN

V

CC

V

SEN

C

STM1831

D

V

SS

RST

AM00700

1 Output open drain RST

2Power V

3Power V

4 Input V

5I/O C

Active-low reset output

Ground

SS

Supply voltage

CC

Sense voltage

SEN

Delay capacitor

D

Figure 2. SOT23-5 pin connections (top view)

RST

V

SS

V

CC

1

2

34

5

C

V

D

SEN

AM00852

Doc ID 18180 Rev 1 5/24

Description STM1831

1.1 Pin descriptions

See Figure 1 and Ta bl e 1 for a brief overview of the signals available on this device.

Power supply (VCC)

This pin is used to provide power to the device. A 0.1 µF decoupling ceramic capacitor is

recommended to be connected between the V

device as possible.

and VSS pins, as close to the STM1831

CC

Sense voltage input (V

Input voltage on this pin is monitored. When it drops below the threshold (V

output (RST

from V

) is asserted. If VCC is close to 0 V, internal logic disconnects the voltage divider

input in order to minimize I

SEN

SEN

)

), reset

DET

current (see Figure 3 and Figure 20).

SEN

Reset output (RST)

Reset output is asserted when the voltage on the V

(V

).

DET

The STM1831 has an open drain, active-low output which sinks current when the output is

asserted. Connect a pull-up resistor from RST

to any supply voltage up to 6 V (see

Figure 4). Select a resistor value large enough to register a logic low, and small enough to

register a logic high, while all of the input current and leakage paths connected to the reset

output line are being supplied. A 10 kΩ pull-up is sufficient in most applications.

The advantages of open drain output include the ability to connect more open drain outputs

in parallel (wired OR connections) as well as connecting the output to a power supply

voltage other than V

CC

.

input pin drops below the threshold

SEN

Delay capacitor (CD)

Capacitor CD determines the delay (tCD) between reset deassertion and the moment when

V

voltage exceeds the V

SEN

Any external leakage due to poor quality timing capacitors or excessive humidity may cause

a significant leakage current which extends the t

tracks between the C

pin and its respective timing capacitor should be as short as

D

possible, properly covered with solder mask and isolated from other tracks (especially V

by as great a distance as possible. Low-leakage timing capacitors (ceramic or film capacitor)

should be used.

threshold (see Figure 5 with calculations for more details).

DET

timing. To minimize this effect, the PCB

CD

SS

)

Leave C

6/24 Doc ID 18180 Rev 1

pin open if unused (i.e. tCD = 0 ms).

D

STM1831 Description

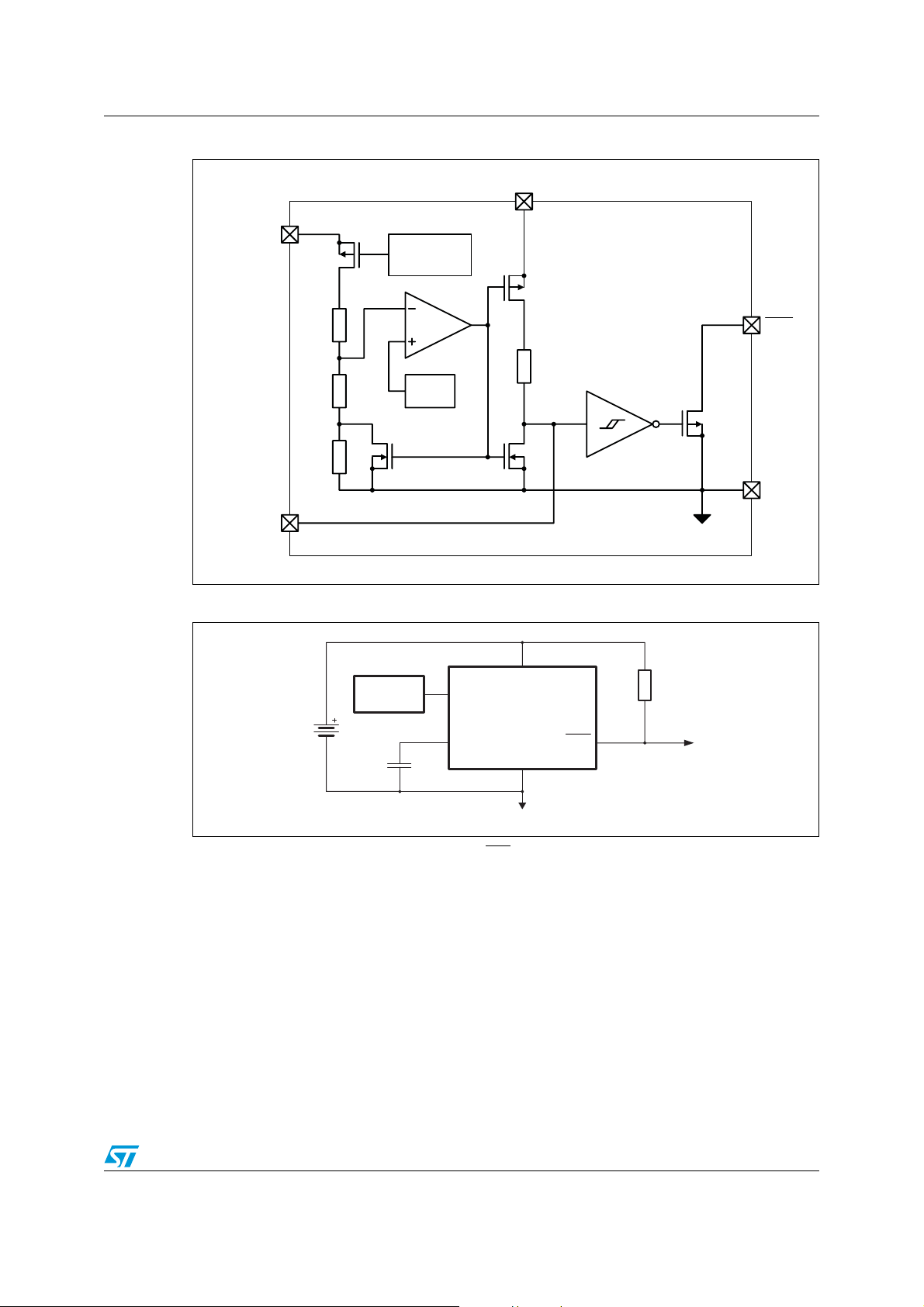

Figure 3. Block diagram

V

CC

V

SEN

Logic

R

1

R

2

R

3

C

D

Figure 4. Application hookup

Monitored

voltage

C

D

RST

R

CD

V

REF

V

SS

AM00853

V

SEN

V

CC

(1)

R

STM1831

C

D

V

RST

SS

1. External pull-up resistor is needed for open drain RST output. A 10 kΩ is sufficient in most applications.

Doc ID 18180 Rev 1 7/24

AM00699

Operation STM1831

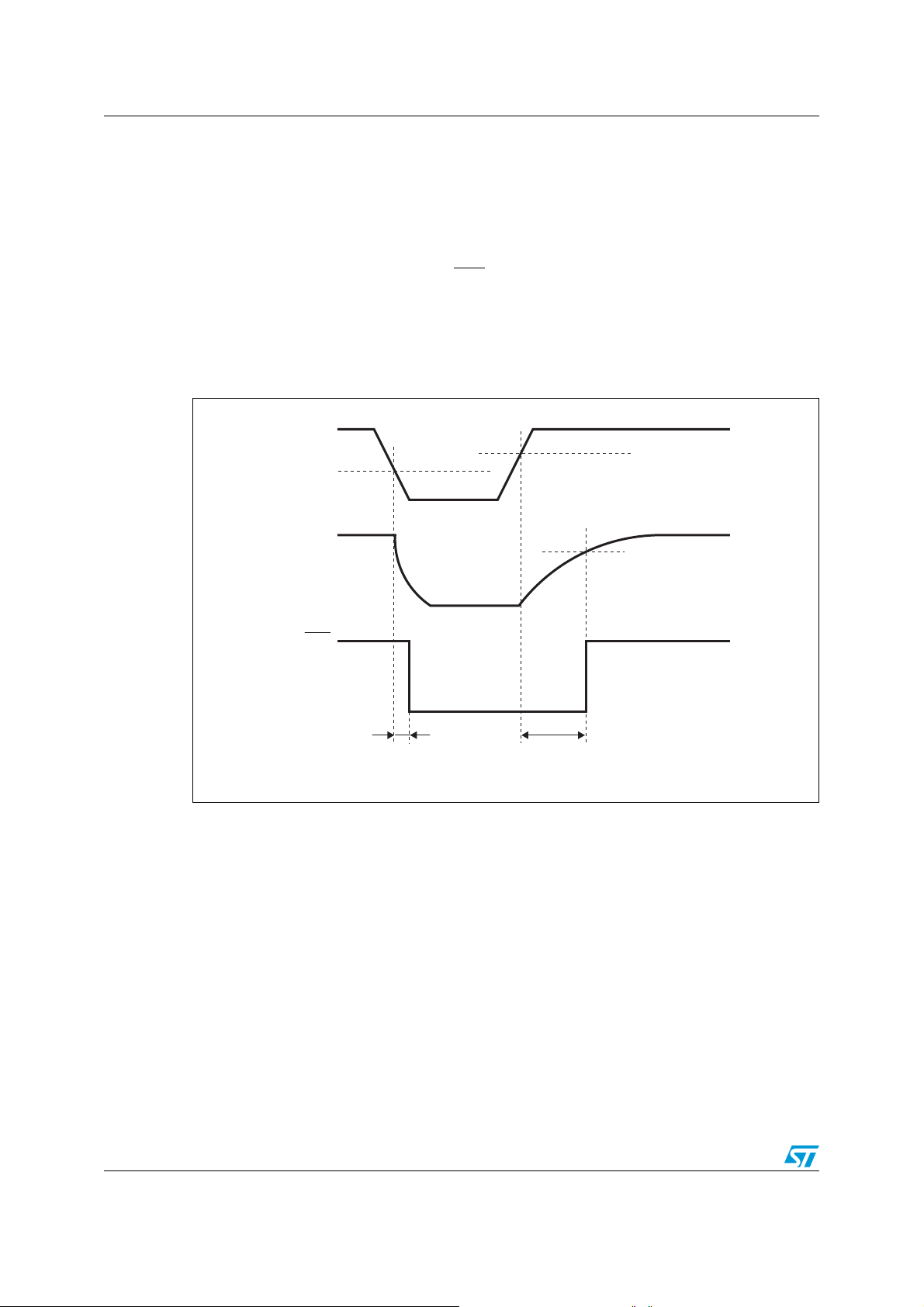

2 Operation

The STM1831 voltage detector monitors system voltages from 1.6 V to 5.7 V in 100 mV

increments, has a voltage hysteresis (V

capacitor C

.

D

The STM1831 asserts a reset output (RST

(V

). The reset output stays asserted until VCC goes above the detect voltage with

DET

hysteresis (V

DET

+ V

). If the external capacitor is connected to the CD pin, the reset

HYS

output deassertion is adequately delayed (see Figure 5 with calculations below for more

details). Leave the C

pin open if unused (i.e. tCD = 0 ms).

D

Figure 5. Timing waveforms

V

SEN

V

DET

C

D

) and an output delay programmable by external

HYS

) whenever VCC goes below the detect voltage

V

+ V

DET

V

HYST

TCD

RST

t

t

t

The t

detect delay time

DET

release delay time (measured when external capacitor CD is disconnected)

REL

delay by external capacitor CD.

CD

delay can be calculated based on Equation 1:

CD

Equation 1

and considering R

Equation 2

t

DET

t

CD

= 2 MΩ (typ.) and V

CD

t

CD

R–

CDCD

TCD

1.39 106CD×× sF,()≅

t

+ t

REL

CD

V

TCD

⎛⎞

In 1

××=

--------------–

⎝⎠

V

CC

= 1.5 V (typ.) at VCC = 3.0 V:

AM00854

8/24 Doc ID 18180 Rev 1

STM1831 Typical operating characteristics

3 Typical operating characteristics

Figure 6. Supply current vs. sense voltage, VCC = 3.0 V, V

1.0

0.9

0.8

(µA)

0.7

CC

0.6

0.5

0.4

0.3

0.2

Supply current, I

0.1

0

0123456

Sense voltage, V

Figure 7. Supply current vs. input voltage, V

SEN

(V)

SEN

= 1.9 V (RST asserted)

DET

= 2.0 V

TA = –40 °C

TA = 25 °C

TA = 85 °C

AM04965v1

2.0

1.8

1.6

1.4

(µA)

CC

1.2

1.0

0.8

0.6

Supply current, I

0.4

0.2

0

012345

Supply voltage, VCC (V)

TA = -40°C

TA = 25°C

TA = 85°C

6

AM04966v1

Doc ID 18180 Rev 1 9/24

Typical operating characteristics STM1831

Figure 8. Detect voltage vs. ambient temperature, V

2.50

2.45

(V)

DET

2.40

2.35

VCC = 6.0 V

Detect voltage, V

2.30

-40-20 0 20406080

Ambient temperature, TA (°C)

Figure 9. Detect voltage vs. supply voltage, V

DET

= 2.4 V

= 2.4 V

DET

VCC = 1.6 V

AM04967v1

2.50

(V)

2.45

DET

2.40

2.35

Detect voltage, V

2.30

TA = 85 °C

TA = 25 °C

TA = -40 °C

123456

Supply voltage, VCC (V)

AM04968v1

10/24 Doc ID 18180 Rev 1

STM1831 Typical operating characteristics

Figure 10. Hysteresis voltage vs. ambient temperature, V

300

250

(V)

HYS

200

150

100

50

Hysteresis voltage, V

0

-40 -20 0 20 40 60 80

VCC = 6.0 V

VCC = 1.6 V

Ambient Temperature, TA (°C)

Figure 11. C

pin sink current vs. supply voltage, V

D

= 0 V, VCD = 0.5 V

SEN

DET

= 2.4 V

AM04969v1

8

7

(mA)

6

CD

5

4

3

TA = -40 °C

2

pin sink current, I

D

1

C

TA = 25 °C

TA = 85 °C

0

0123456

Supply voltage, VCC (V)

AM04970v1

Doc ID 18180 Rev 1 11/24

Typical operating characteristics STM1831

Figure 12. Output voltage vs. sense voltage, V

resistor on RST

7

6

(V)

5

RST

4

3

2

Reset output voltage, V

1

0

0123456

is 100 kΩ, CD pin open

Sense voltage, V

Figure 13. Output voltage vs. supply voltage, V

on RST

is 100 kΩ, CD pin open

= 2.4 V, TA = 25 °C, external pull-up

DET

Vcc = 6.0 V

Vcc = 4.5 V

Vcc = 3.0 V

(V)

SEN

= VCC, external pull-up resistor

SEN

AM04971v1

3.0

(V)

2.5

RST

2.0

1.5

1.0

0.5

Reset output voltage, V

TA = -40 °C

TA = 25 °C

TA = 85 °C

0

00.511.5 22.5

Supply voltage, VCC (V)

AM04972v1

12/24 Doc ID 18180 Rev 1

STM1831 Typical operating characteristics

Figure 14. Output current vs. supply voltage, V

SEN

= 0 V, V

RST

= 0.5 V

40

RST

35

30

25

20

(mA)

15

10

5

Output current on RST pin, I

0

0123456

Supply voltage, VCC (V)

Figure 15. Relative delay resistance vs. ambient temperature, V

V

= 0 V

CD

TA = -40 °C

TA = 25 °C

TA = 85 °C

= 5 V, V

CC

SEN

AM04973v1

= 6 V,

CD-TYP

/ R

CD

Relative delay resistance, R

1.30

1.20

1.10

1.00

(-)

0.90

0.80

0.70

-40 -20 0 20 40 60 80

Ambient temperature, TA (°C)

AM04974v1

Doc ID 18180 Rev 1 13/24

Typical operating characteristics STM1831

Figure 16. Release delay time vs. delay capacitance, TA = 25 °C

10000

V

= 1.6 V

(ms)

CD

+ t

DET

1000

100

cc

V

= 3 V

cc

V

= 6 V

cc

10

1

Release delay, t

0.1

0.0001 0.001 0.01 0.1 1

External delay capacitor, CD (µF)

Figure 17. Detect delay time vs. delay capacitance, T

10000

V

= 1.6 V

1000

cc

V

= 3 V

cc

V

= 6 V

cc

(µs)

100

DET

10

Detect delay, t

1

0.0001 0.001 0.01 0.1 1

External delay capacitor, CD (µF)

= 25 °C

A

AM04975v1

AM04976v1

14/24 Doc ID 18180 Rev 1

STM1831 Typical operating characteristics

Figure 18. RST output leakage current vs. ambient temperature,

V

= V

CC

1.0

0.9

(nA)

0.8

RST

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

Reset leakage current, I

-40 -20 0 20 40 60 80

SEN

= V

= 6.0 V, CD pin open

OUT

Figure 19. RST

T

= 85 °C, CD pin open

A

0.6

(nA)

0.5

RST

0.4

0.3

0.2

0.1

0

Reset leakage current, I

Ambient temperature, TA (°C)

output leakage current vs. output voltage, VCC = V

0123456

Reset output voltage, V

RST

(V)

SEN

= 6.0 V,

AM04977v1

AM04978v1

Doc ID 18180 Rev 1 15/24

Typical operating characteristics STM1831

Figure 20. Sense current vs. supply voltage, V

0.14

0.12

0.10

(nA)

SEN

0.08

0.06

0.04

Sense current, I

0.02

0.00

0123456

SEN

= 1.9 V

Supply voltage, VCC (V)

Figure 21. Sense current vs. ambient temperature, V

CC

= V

SEN

TA = -40 °C

TA = 25 °C

TA = 85 °C

AM04979v1

= 5 V

(nA)

SEN

Sense current, I

500

450

400

350

300

250

200

150

100

50

0

-40 -20 0 20 40 60 80

Ambient temperature, TA (°C)

AM04980v1

16/24 Doc ID 18180 Rev 1

STM1831 Maximum ratings

4 Maximum ratings

Stressing the device above the ratings listed in Ta bl e 2 may cause permanent damage to

the device. These are stress ratings only and operation of the device at these or any other

conditions above those indicated in the operating sections of this specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device

reliability.

Table 2. Absolute maximum ratings

Symbol Parameter Value Unit

T

T

SLD

V

V

V

STG

T

J

CC

CD

RST

(1)

Storage temperature (VCC off) –55 to 150 °C

Lead solder temperature for 10 seconds 260 °C

Maximum junction temperature 125 °C

Supply voltage –0.3 to 7.0 V

Delay capacitor pin voltage –0.3 to VCC + 0.3 V

Reset output voltage

– N-channel open drain –0.3 to 7.0

ESD voltage

V

ESD

1. Reflow at peak temperature of 260 °C. The time above 255 °C must not exceed 30 seconds.

– Human body model (MIL-STD-883, Method 3015)

– Machine model

2000

200

V

V

Doc ID 18180 Rev 1 17/24

DC and AC parameters STM1831

5 DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC

characteristics of the device. The parameters in Ta b le 4 that follow, are derived from tests

performed under the measurement conditions summarized in Ta b le 3 and Figure 5 with

measurement conditions for t

conditions in their circuit match the operating conditions when relying on the quoted

parameters.

Table 3. Operating and AC measurement conditions

Parameter Value Unit

DET

and t

. Designers should check that the operating

REL

Supply voltage (V

Ambient operating temperature (T

Input rise and fall times ≤

Input pulse voltages 0.2 to 0.8 V

Input and output timing ref. voltages 0.3 to 0.7 V

) 1.6 to 6.0 V

CC

) –40 to 85 °C

A

5ns

Figure 22. AC testing input/output waveforms

0.8 V

CC

0.2 V

CC

CC

CC

0.7 V

0.3 V

V

V

CC

CC

AI02568

18/24 Doc ID 18180 Rev 1

STM1831 DC and AC parameters

Table 4. DC and AC characteristics

Symbol Parameter Conditions

Operating

voltage

Detect voltage

(2)

Hysteresis

voltage

Supply current

Output current

Output leakage

current

Temperature

)

variation

Sense current

Delay resistance

V

SEN

V

RST

VCC = 6.0 V, V

V

V

CC

V

SEN

ΔV

/ (ΔTA • V

DET

V

CC

V

DET

V

HYS

I

CC

I

RST

I

LEAK

I

SEN

R

CD

DET

Delay

I

CD

capacitance pin

V

CD

sink current

V

SEN

SEN

V

SEN

VCC = 6.0 V, V

VCC = 6.0 V, V

V

t

t

TCD

DET

REL

Delay

capacitance pin

threshold voltage

Detect delay

time

Release delay

time

–40 °C < T

(1)

< 85 °C 1.6 — 6.0 V

A

= 1.6 V — 0.70 1.20

V

CC

= 3.0 V — 0.80 1.40

CC

= 6.0 V — 1.20 2.00

V

CC

Min. Typ. Max. Units

V

DET

0.02 V

–2% V

DET

DETVDET

0.05

V

DET

+ 2% V

0.08 V

DET

VCC = 1.6 V 0.8 7.0 —

= 2.0 V 5.0 14.0 —

V

CC

= 3.0 V 10.0 22.0 —

V

= 0 V,

= 0.5 V

= 6.0 V, CD: open

RST

–40 °C < T

V

> 1.6 V, V

= 6.0 V, VCC = 5.0 V,

VCD = 0 V

CC

V

= 4.0 V 15.0 28.0 —

CC

= 5.0 V 17.0 32.0 —

V

CC

= 6.0 V 20.0 35.0 —

V

CC

= 6.0 V,

SEN

< 85 °C — ±100 — ppm/ °C

A

= 0 V — 10 —

CC

= 5.0 V — 300 500

SEN

— — 400 nA

1.4 2.0 2.6 MΩ

= 0.5 V, VCC = 1.6 V 0.2 1.4 — mA

= 6.0 V, VCC = 1.6 V 0.70 0.85 1.00

= 6.0 V, VCC = 3.0 V 1.25 1.50 1.70

= 6.0 V, VCC = 6.0 V 2.45 2.65 2.85

= 6.0 V→

SEN

: open

0 V, C

D

SEN

V, CD: open

= 0 V→ 6

—4075 µs

— 55 170 µs

V

µAV

mA

nA

V V

1. Valid for ambient operating temperature: TA = 25 °C; VCC = 1.6 V to 6.0 V (except where noted).

2. Factory-trimmed voltage thresholds in 100 mV increments from 1.6 V to 5.7 V.

Doc ID 18180 Rev 1 19/24

Package mechanical data STM1831

6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK

The maximum ratings related to soldering conditions are also marked on the inner box label.

®

packages, depending on their level of environmental compliance. ECOPACK®

®

is an ST trademark.

20/24 Doc ID 18180 Rev 1

STM1831 Package mechanical data

Figure 23. SOT23-5 - 5-lead small outline transistor package mechanical drawing

1

e

5 x b

C

T

Note: Drawing is not to scale.

Table 5. SOT23-5 - 5-lead small outline transistor package mechanical data

E

E1 L

e1

A1

D

5x

0.10 C

A2

A

0133778_C

Millimeters Inches

Symbol

Typ. Min. Max. Typ. Min. Max.

A 1.45 0.057

A1 0.00 0.15 0.00 0.006

A2 1.15 0.90 1.30 0.045 0.035 0.051

b 0.30 0.50 0.012 0.020

c 0.08 0.22 0.003 0.009

D2.90 0.114

E2.80 0.110

E1 1.60 0.063

e0.95 0.037

e1 1.90 0.075

L 0.45 0.30 0.60 0.018 0.012 0.024

θ 4 0 8 4 0 8 Degrees

N5 5

Note

Doc ID 18180 Rev 1 21/24

Part numbering STM1831

7 Part numbering

Table 6. STM1831 ordering information scheme

Example: STM1831 L 24 WY 6 F

Device type

STM1831

Reset output polarity

L: active-low

Detector threshold

(1)

24: 2.4 V typ.

(100 mV steps from 1.6 V to 5.7 V available)

Package

WY: SOT23-5

Temperature range

6: –40 °C to +85 °C

Shipping method

®

F: Lead-free ECOPACK

1. Other detector thresholds are offered. Minimum order quantities may apply. Contact local ST sales

office for availability.

package, tape and reel

22/24 Doc ID 18180 Rev 1

STM1831 Revision history

8 Revision history

Table 7. Document revision history

Date Revision Changes

16-Nov-2010 1 Initial release.

Doc ID 18180 Rev 1 23/24

STM1831

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

24/24 Doc ID 18180 Rev 1

Loading...

Loading...