ST SPC560B40L5, SPC560B50L5, SPC560B40L3, SPC560C40L3, SPC560B50L3 User Manual

...

Features

SPC560B40x, SPC560B50x

SPC560C40x, SPC560C50x

32-bit MCU family built on the Power Architecture

for automotive body electronics applications

®

■ High-performance 64 MHz e200z0h CPU

– 32-bit Power Architecture

®

technology

– Up to 60 DMIPs operation

– Variable length encoding (VLE)

■ Memory

– Up to 512 Kbytes Code Flash, with ECC

– 64 Kbytes Data Flash, with ECC

– Up to 48 Kbytes SRAM, with ECC

– 8-entry memory protection unit (MPU)

■ Interrupts

– 16 priority levels

– Non-maskable interrupt (NMI)

– Up to 34 ext. int. including 18 wakeup lines

■ GPIO: LQFP64/45, LQFP100/75,

LQFP144/123

■ Timer units

– 6-channel 32-bit periodic interrupt timers

– 4-channel 32-bit system timer module

– System watchdog timer

– Real-time clock timer

■ 16-bit counter time-triggered I/Os

– Up to 56 channels with PWM/MC/IC/OC

– ADC diagnostic via CTU

■ Communications interface

– Up to 6 FlexCAN interfaces (2.0B active)

with 64-message objects each

– Up to 4 LINFlex/UART

– 3 DSPI / I

2

C

LQFP100 (14 x 14 x 1.4 mm)

LQFP144 (20 x 20 x 1.4 mm)

■ 10-bit A/D converter with up to 36 channels

LQFP64 (10 x 10 x 1.4 mm)

– Up to 64 channels via external multiplexing

– Individual conversion registers

– Cross triggering unit

■ Dedicated diagnostic module for lighting

– Advanced PWM generation

– Time-triggered diagnostic

– PWM-synchronized ADC measurements

■ Clock generation

– 4 to 16 MHz fast external crystal oscillator

– 32 KHz slow external crystal oscillator

– 16 MHz fast internal RC oscillator

– 128 kHz slow internal RC oscillator

– Software-controlled FMPLL

– Clock monitoring unit

■ Exhaustive debugging capability

– Nexus1 on all devices

– Nexus2+ available on emulation package

■ Low power capabilities

– Ultra-low power standby with RTC, SRAM

and CAN monitoring

– Fast wakeup schemes

■ Operating temp. range up to -40 to 125 °C

■ Single 5 V or 3.3 V supply

Table 1. Device summary

Package

LQFP144 SPC560B40L5 — SPC560B50L5 —

LQFP100 SPC560B40L3 SPC560C40L3 SPC560B50L3 SPC560C50L3

LQFP64

1. All LQFP64 information is indicative and must be confirmed during silicon validation.

October 2011 Doc ID 14619 Rev 9 1/117

(1)

256 KB code Flash memory 512 KB code Flash memory

SPC560B40L1 SPC560C40L1 SPC560B50L1 SPC560C50L1

Part number

www.st.com

1

Contents SPC560B40x/50x, SPC560C40x/50x

Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.1 Document overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

1.2 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 Package pinouts and signal descriptions . . . . . . . . . . . . . . . . . . . . . . . 14

3.1 Package pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2 Pad configuration during reset phases . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.3 Voltage supply pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.4 Pad types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.5 System pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.6 Functional ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.7 Nexus 2+ pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.2 Parameter classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

4.3 NVUSRO register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.3.1 NVUSRO[PAD3V5V] field description . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.3.2 NVUSRO[OSCILLATOR_MARGIN] field description . . . . . . . . . . . . . . . 44

4.3.3 NVUSRO[WATCHDOG_EN] field description . . . . . . . . . . . . . . . . . . . . 44

4.4 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.5 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4.6 Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.6.1 Package thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.6.2 Power considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4.7 I/O pad electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.7.1 I/O pad types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.7.2 I/O input DC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.7.3 I/O output DC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.7.4 Output pin transition times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.7.5 I/O pad current specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

2/117 Doc ID 14619 Rev 9

SPC560B40x/50x, SPC560C40x/50x Contents

4.8 RESET electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

4.9 Power management electrical characteristics . . . . . . . . . . . . . . . . . . . . . 63

4.9.1 Voltage regulator electrical characteristics . . . . . . . . . . . . . . . . . . . . . . 63

4.9.2 Low voltage detector electrical characteristics . . . . . . . . . . . . . . . . . . . . 68

4.10 Power consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

4.11 Flash memory electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.11.1 Program/Erase characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.11.2 Flash power supply DC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 72

4.11.3 Start-up/Switch-off timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.12 Electromagnetic compatibility (EMC) characteristics . . . . . . . . . . . . . . . . 73

4.12.1 Designing hardened software to avoid noise problems . . . . . . . . . . . . . 73

4.12.2 Electromagnetic interference (EMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.12.3 Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . . 74

4.13 Fast external crystal oscillator (4 to 16 MHz) electrical characteristics . . 75

4.14 Slow external crystal oscillator (32 kHz) electrical characteristics . . . . . . 78

4.15 FMPLL electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.16 Fast internal RC oscillator (16 MHz) electrical characteristics . . . . . . . . . 81

4.17 Slow internal RC oscillator (128 kHz) electrical characteristics . . . . . . . . 82

4.18 ADC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.18.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.18.2 Input impedance and ADC accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.18.3 ADC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.19 On-chip peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.19.1 Current consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.19.2 DSPI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

4.19.3 Nexus characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.19.4 JTAG characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5 Package characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.1 ECOPACK

5.2 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.2.1 LQFP64 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

® . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.2.2 LQFP100 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

5.2.3 LQFP144 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

5.2.4 LBGA208 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Doc ID 14619 Rev 9 3/117

Contents SPC560B40x/50x, SPC560C40x/50x

6 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Appendix A Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

4/117 Doc ID 14619 Rev 9

SPC560B40x/50x, SPC560C40x/50x List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. SPC560B40x/50x and SPC560C40x/50x device comparison . . . . . . . . . . . . . . . . . . . . . . . 9

Table 3. SPC560B40x/50x and SPC560C40x/50x series block summary . . . . . . . . . . . . . . . . . . . . 12

Table 4. Voltage supply pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 5. System pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 6. Functional port pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 7. Nexus 2+ pin descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 8. Parameter classifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 9. PAD3V5V field description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 10. OSCILLATOR_MARGIN field description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 11. WATCHDOG_EN field description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 12. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 13. Recommended operating conditions (3.3 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 14. Recommended operating conditions (5.0 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 15. LQFP thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 16. I/O input DC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 17. I/O pull-up/pull-down DC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 18. SLOW configuration output buffer electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 19. MEDIUM configuration output buffer electrical characteristics . . . . . . . . . . . . . . . . . . . . . . 52

Table 20. FAST configuration output buffer electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 21. Output pin transition times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 22. I/O supply segment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 23. I/O consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 24. I/O weight . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 25. Reset electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 26. Voltage regulator electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 27. Low voltage detector electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 28. Power consumption on VDD_BV and VDD_HV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 29. Program and erase specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 30. Flash module life. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 31. Flash read access timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 32. Flash memory power supply DC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 33. Start-up time/Switch-off time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 34. EMI radiated emission measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 35. ESD absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 36. Latch-up results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Table 37. Crystal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 38. Fast external crystal oscillator (4 to 16 MHz) electrical characteristics. . . . . . . . . . . . . . . . 77

Table 39. Crystal motional characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 40. Slow external crystal oscillator (32 kHz) electrical characteristics . . . . . . . . . . . . . . . . . . . 80

Table 41. FMPLL electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 42. Fast internal RC oscillator (16 MHz) electrical characteristics . . . . . . . . . . . . . . . . . . . . . . 81

Table 43. Slow internal RC oscillator (128 kHz) electrical characteristics . . . . . . . . . . . . . . . . . . . . . 82

Table 44. ADC input leakage current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 45. ADC conversion characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 46. On-chip peripherals current consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 47. DSPI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 48. Nexus characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Doc ID 14619 Rev 9 5/117

List of tables SPC560B40x/50x, SPC560C40x/50x

Table 49. JTAG characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 50. LQFP64 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 51. LQFP100 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 52. LQFP144 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 53. LBGA208 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 54. Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 55. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

6/117 Doc ID 14619 Rev 9

SPC560B40x/50x, SPC560C40x/50x List of figures

List of figures

Figure 1. SPC560B40x/50x and SPC560C40x/50x block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 11

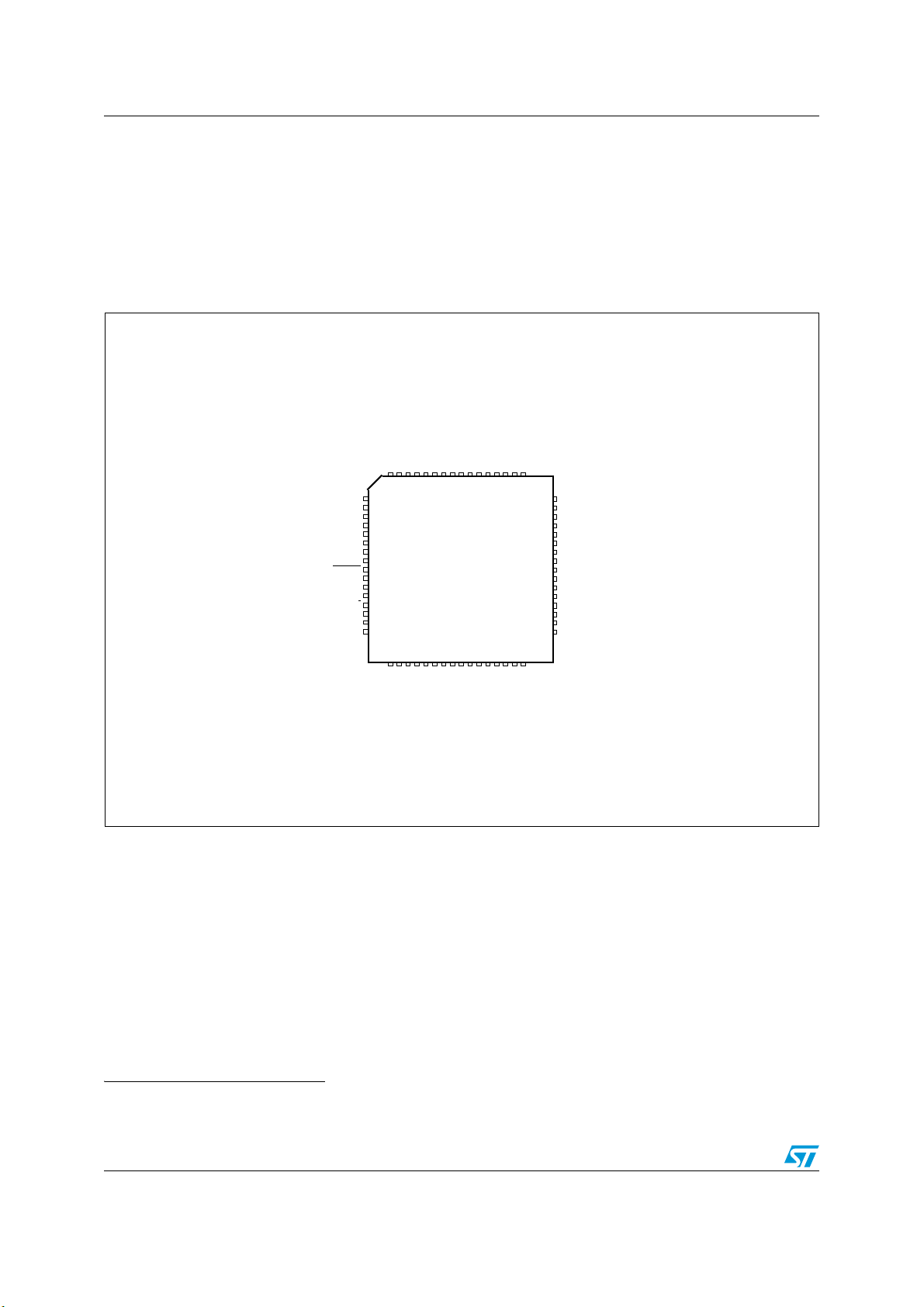

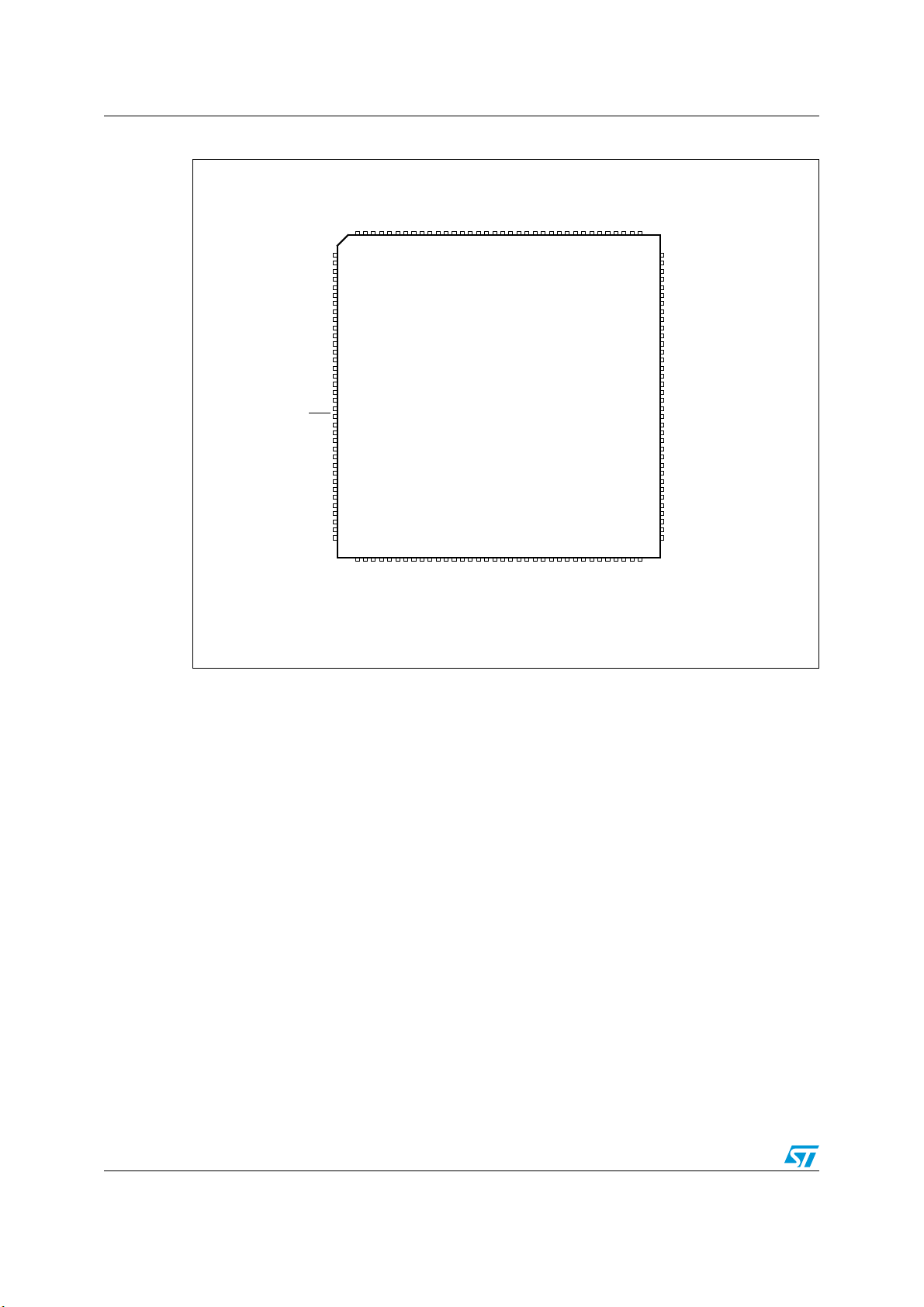

Figure 2. LQFP 64-pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

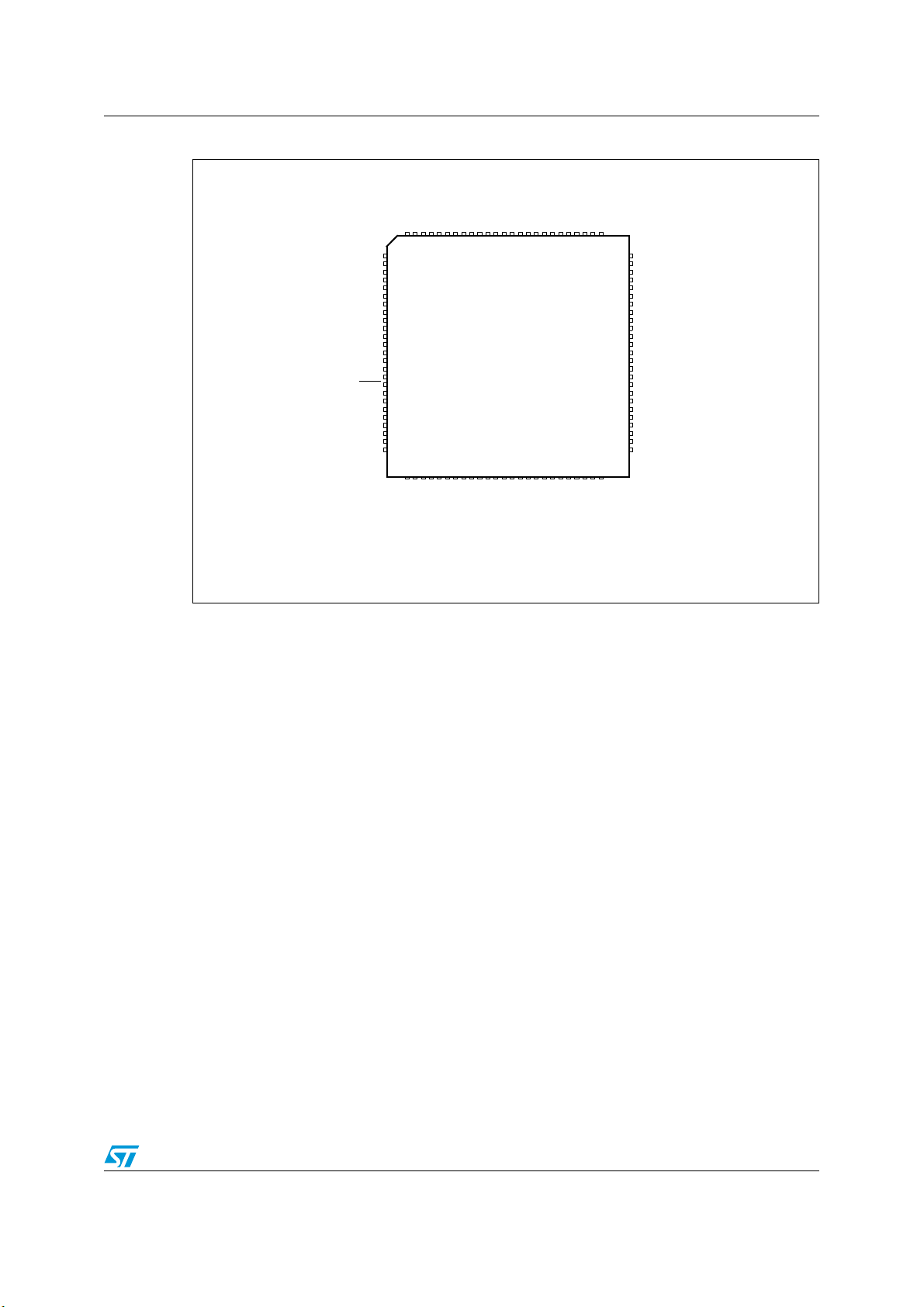

Figure 3. LQFP 100-pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 4. LQFP 144-pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

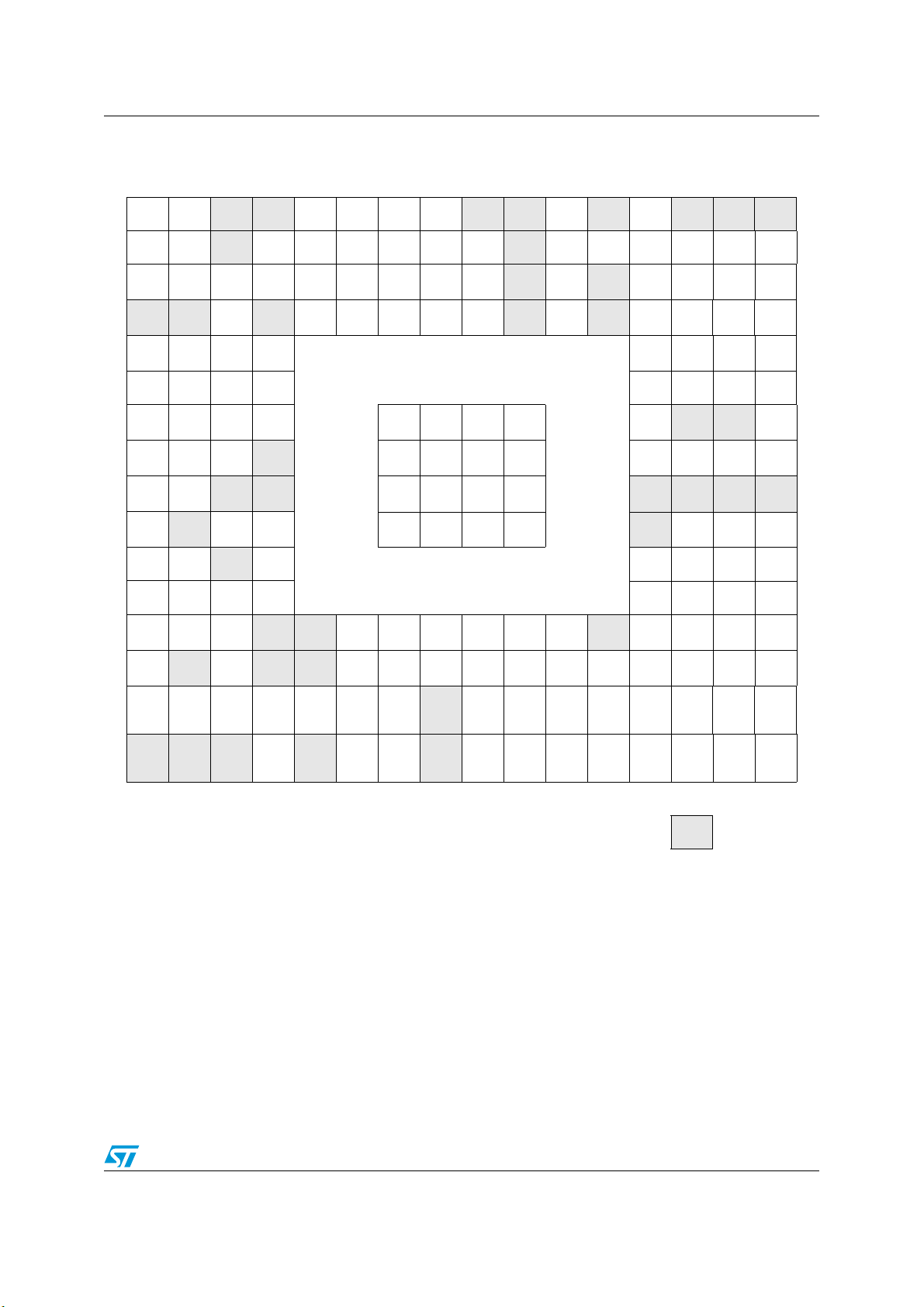

Figure 5. LBGA208 confguration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 6. I/O input DC electrical characteristics definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 7. Start-up reset requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 8. Noise filtering on reset signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 9. Voltage regulator capacitance connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 10. VDD and VDD_BV maximum slope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 11. VDD and VDD_BV supply constraints during STANDBY mode exit. . . . . . . . . . . . . . . . . . 65

Figure 12. Low voltage detector vs reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 13. Crystal oscillator and resonator connection scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 14. Fast external crystal oscillator (4 to 16 MHz) timing diagram . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 15. Crystal oscillator and resonator connection scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure 16. Equivalent circuit of a quartz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 17. Slow external crystal oscillator (32 kHz) timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 18. ADC characteristic and error definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Figure 19. Input equivalent circuit (precise channels) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 20. Input equivalent circuit (extended channels) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 21. Transient behavior during sampling phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 22. Spectral representation of input signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 23. DSPI classic SPI timing – master, CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 24. DSPI classic SPI timing – master, CPHA = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 25. DSPI classic SPI timing – slave, CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 26. DSPI classic SPI timing – slave, CPHA = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 27. DSPI modified transfer format timing – master, CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 28. DSPI modified transfer format timing – master, CPHA = 1 . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 29. DSPI modified transfer format timing – slave, CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 30. DSPI modified transfer format timing – slave, CPHA = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 31. DSPI PCS strobe (PCSS) timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 32. Nexus TDI, TMS, TDO timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 33. Timing diagram – JTAG boundary scan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Figure 34. LQFP64 package mechanical drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Figure 35. LQFP100 package mechanical drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 36. LQFP144 package mechanical drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 37. LBGA208 package mechanical drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 38. Ordering information scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Doc ID 14619 Rev 9 7/117

Introduction SPC560B40x/50x, SPC560C40x/50x

1 Introduction

1.1 Document overview

This document describes the features of the family and options available within the family

members, and highlights important electrical and physical characteristics of the device. To

ensure a complete understanding of the device functionality, refer also to the device

reference manual and errata sheet.

1.2 Description

The SPC560B40x/50x and SPC560C40x/50x is a family of next generation microcontrollers

built on the Power Architecture embedded category.

The SPC560B40x/50x and SPC560C40x/50x family of 32-bit microcontrollers is the latest

achievement in integrated automotive application controllers. It belongs to an expanding

family of automotive-focused products designed to address the next wave of body

electronics applications within the vehicle. The advanced and cost-efficient host processor

core of this automotive controller family complies with the Power Architecture embedded

category and only implements the VLE (variable-length encoding) APU, providing improved

code density. It operates at speeds of up to 64 MHz and offers high performance processing

optimized for low power consumption. It capitalizes on the available development

infrastructure of current Power Architecture devices and is supported with software drivers,

operating systems and configuration code to assist with users implementations.

8/117 Doc ID 14619 Rev 9

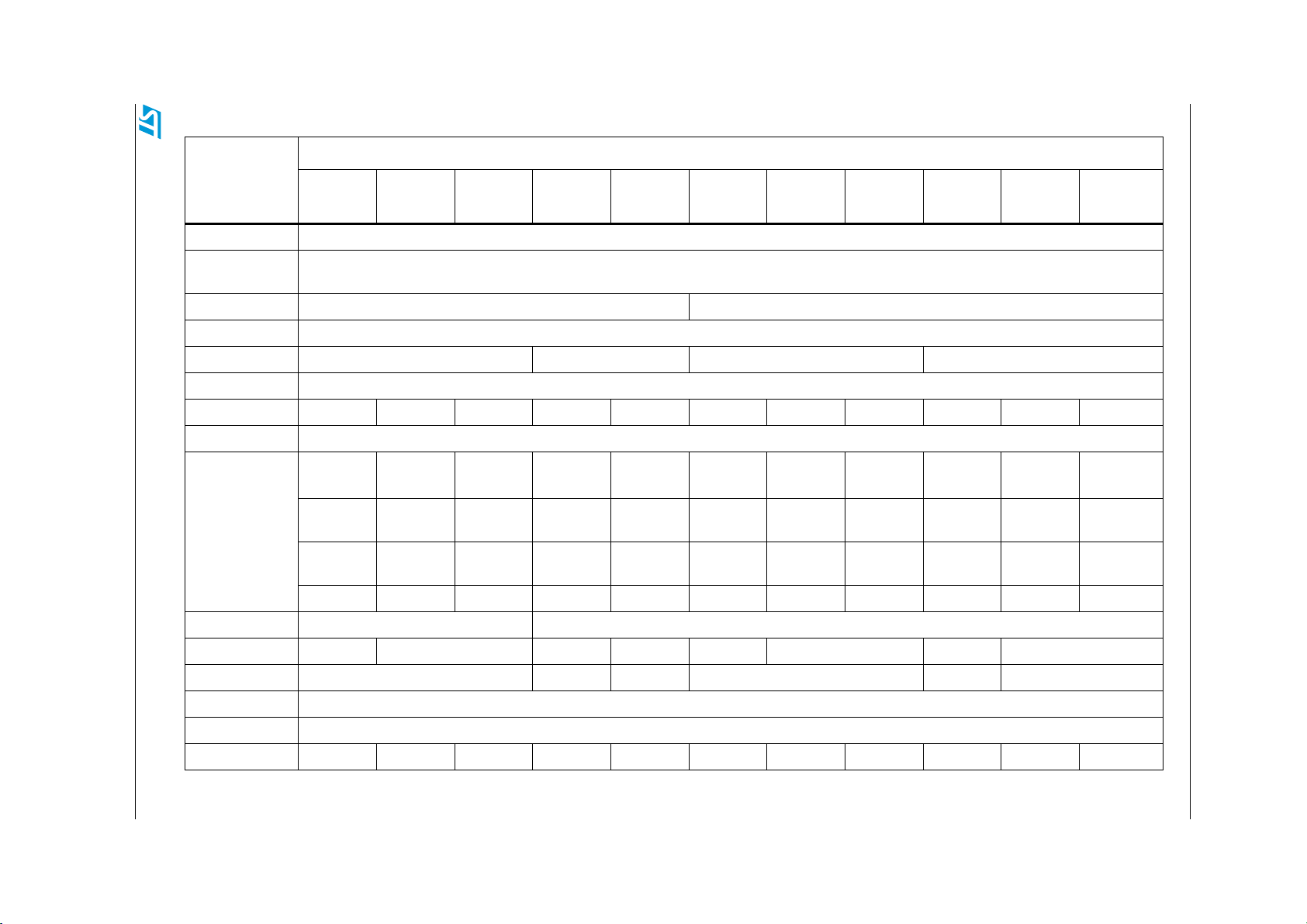

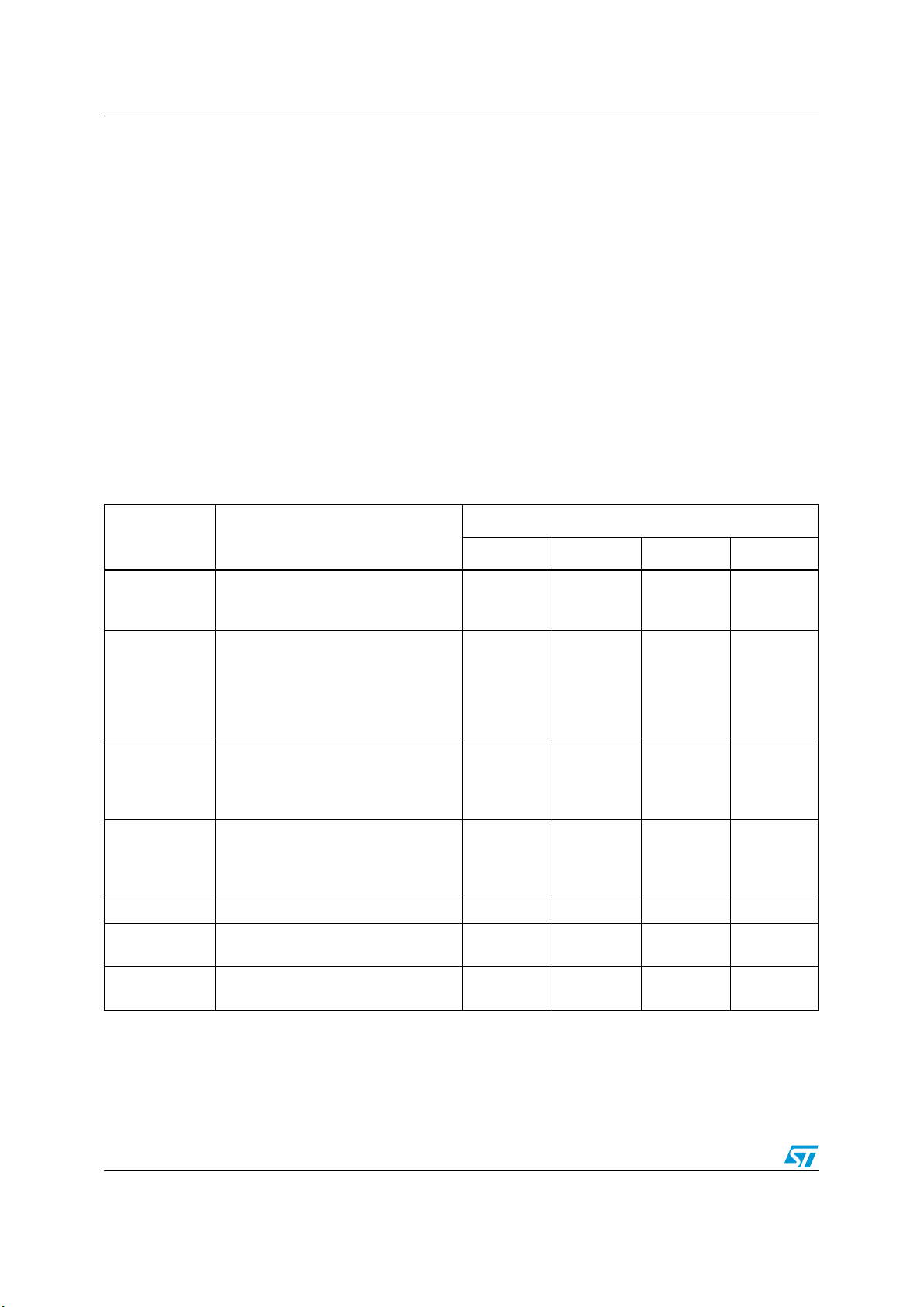

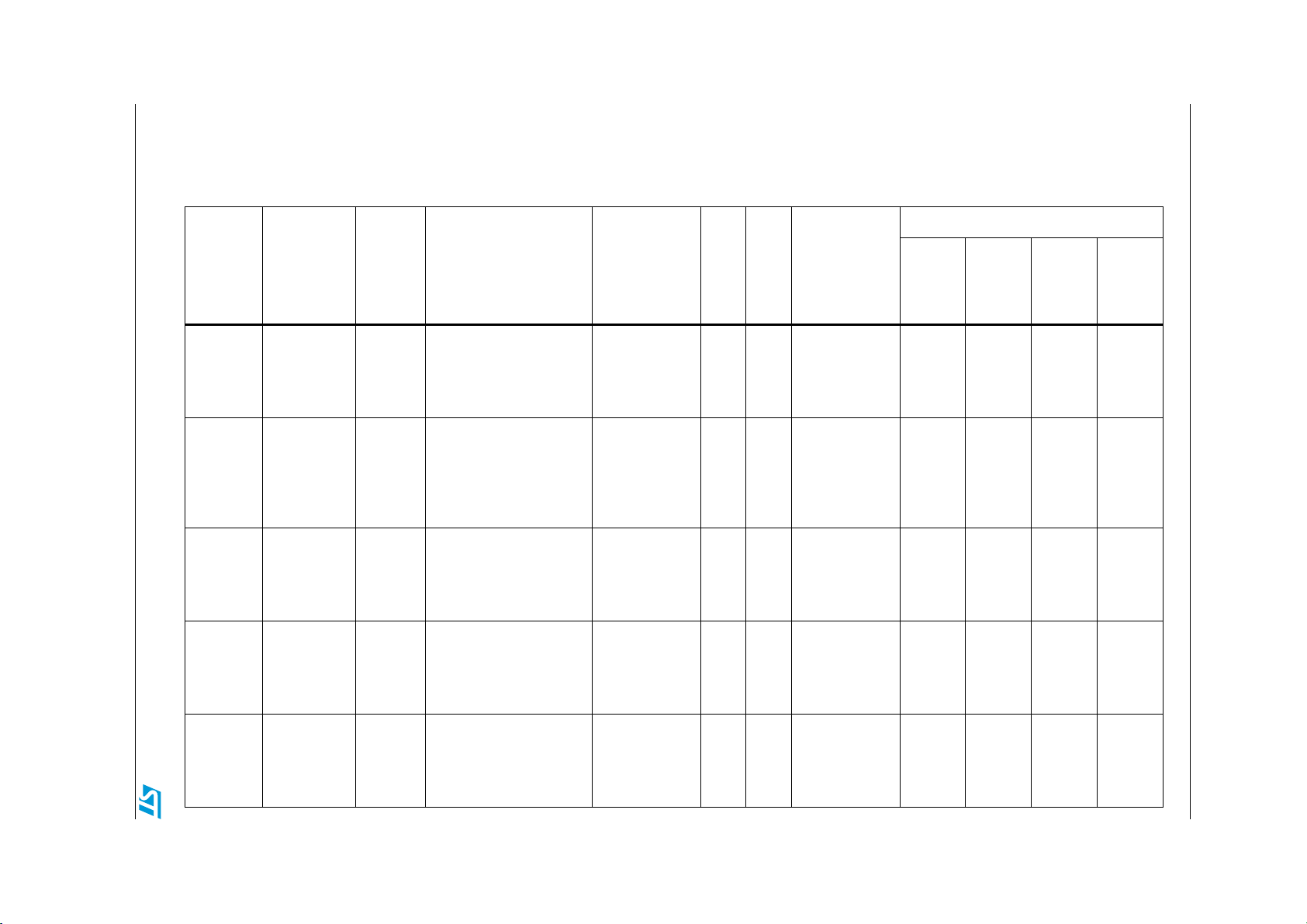

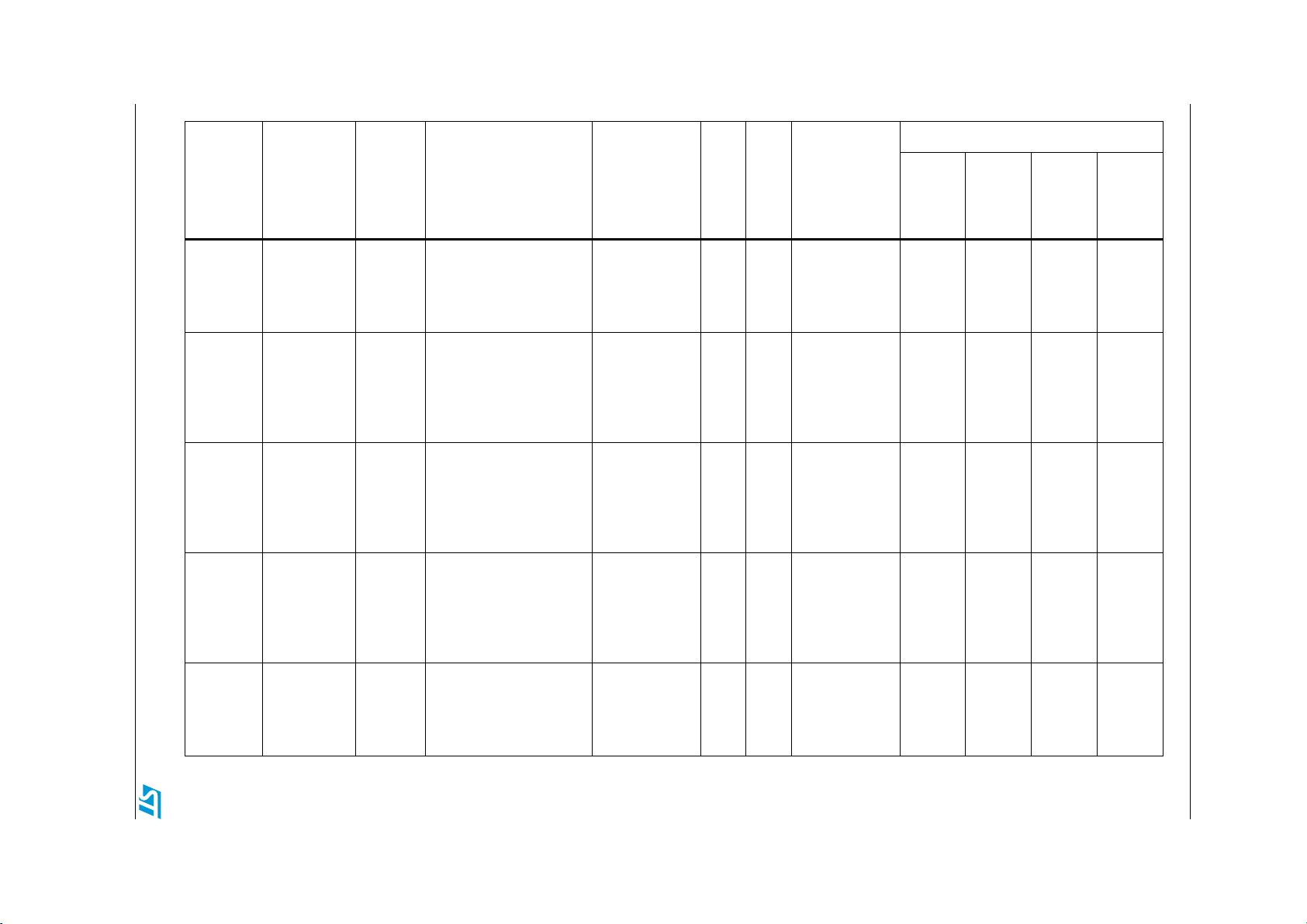

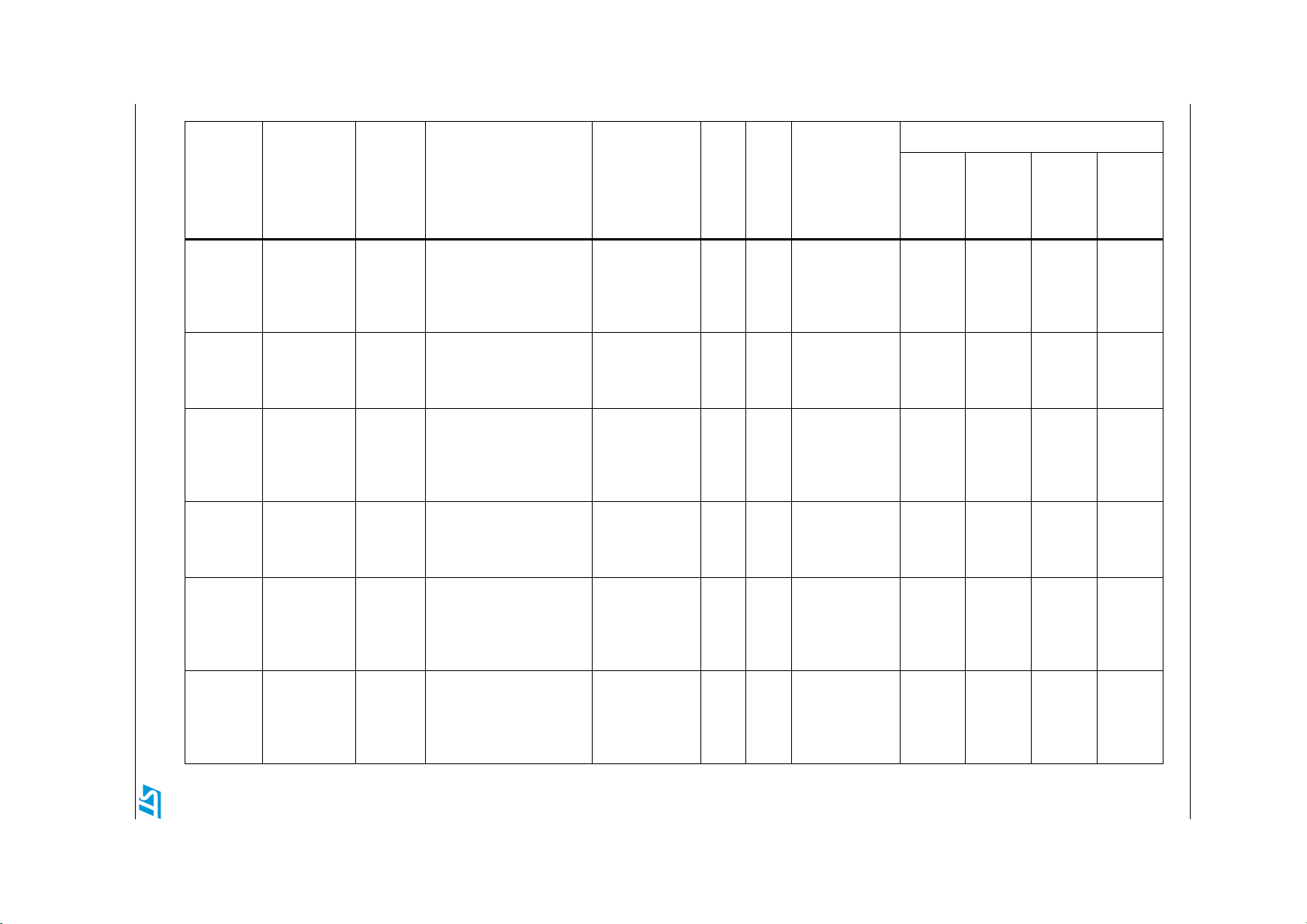

Table 2. SPC560B40x/50x and SPC560C40x/50x device comparison

SPC560B40x/50x, SPC560C40x/50x Introduction

(1)

Device

Doc ID 14619 Rev 9 9/117

Feature

SPC560B

40L1

SPC560B

40L3

SPC560B

40L5

SPC560C

40L1

SPC560C

40L3

SPC560B

50L1

SPC560B

50L3

SPC560B

50L5

SPC560C

50L1

SPC560C

50L3

SPC560B

50B2

CPU e200z0h

Execution

(2)

speed

Static – up to 64 MHz

Code Flash 256 KB 512 KB

Data Flash 64 KB (4 × 16 KB)

RAM 24KB 32KB 32KB 48 KB

MPU 8-entry

ADC (10-bit) 12 ch 28 ch 36 ch 8 ch 28 ch 12 ch 28 ch 36 ch 8 ch 28 ch 36 ch

CTU Ye s

(3)

Total timer I/O

eMIOS

– PWM + MC +

– PWM +

–IC/OC

IC/OC

IC/OC

(4)

(4)

(4)

12 ch,

16-bit

2 ch 5 ch 10 ch 2 ch 5 ch 2 ch 5 ch 10 ch 2 ch 5 ch 10 ch

10 ch 20 ch 40 ch 10 ch 20 ch 10 ch 20 ch 40 ch 10 ch 20 ch 40 ch

— 3 ch 6 ch — 3 ch — 3 ch 6 ch — 3 ch 6 ch

SCI (LINFlex) 3

28 ch,

16-bit

(5)

56 ch,

16-bit

12 ch,

16-bit

28 ch,

16-bit

12 ch,

16-bit

28 ch,

16-bit

4

56 ch,

16-bit

12 ch,

16-bit

28 ch,

16-bit

56 ch,

16-bit

SPI (DSPI) 2 3 2 3 2 3 2 3

CAN (FlexCAN) 2

2

C 1

I

(6)

56 3

(7)

56

32 kHz oscillator Yes

(8)

GPIO

45 79 123 45 79 45 79 123 45 79 123

10/117 Doc ID 14619 Rev 9

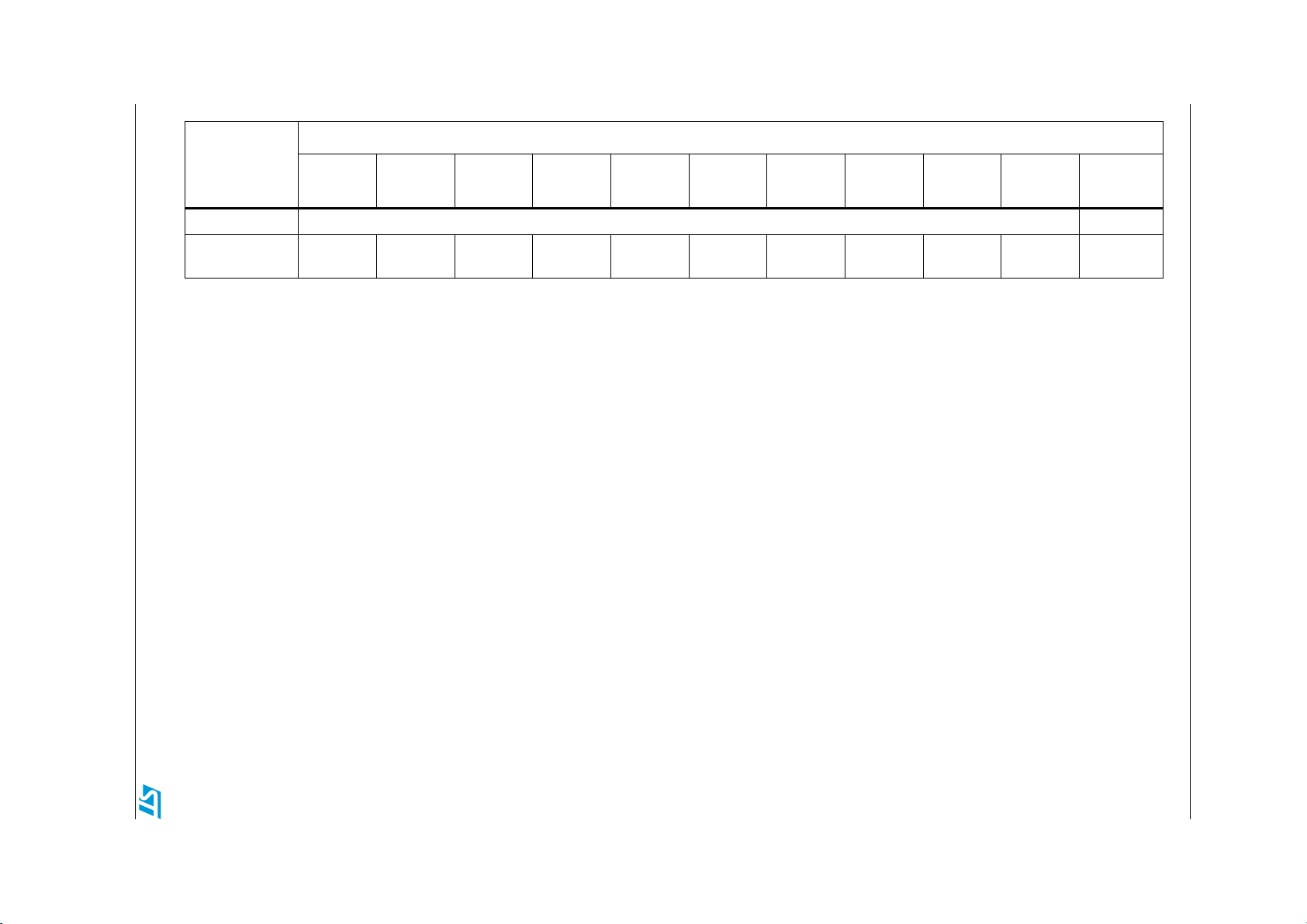

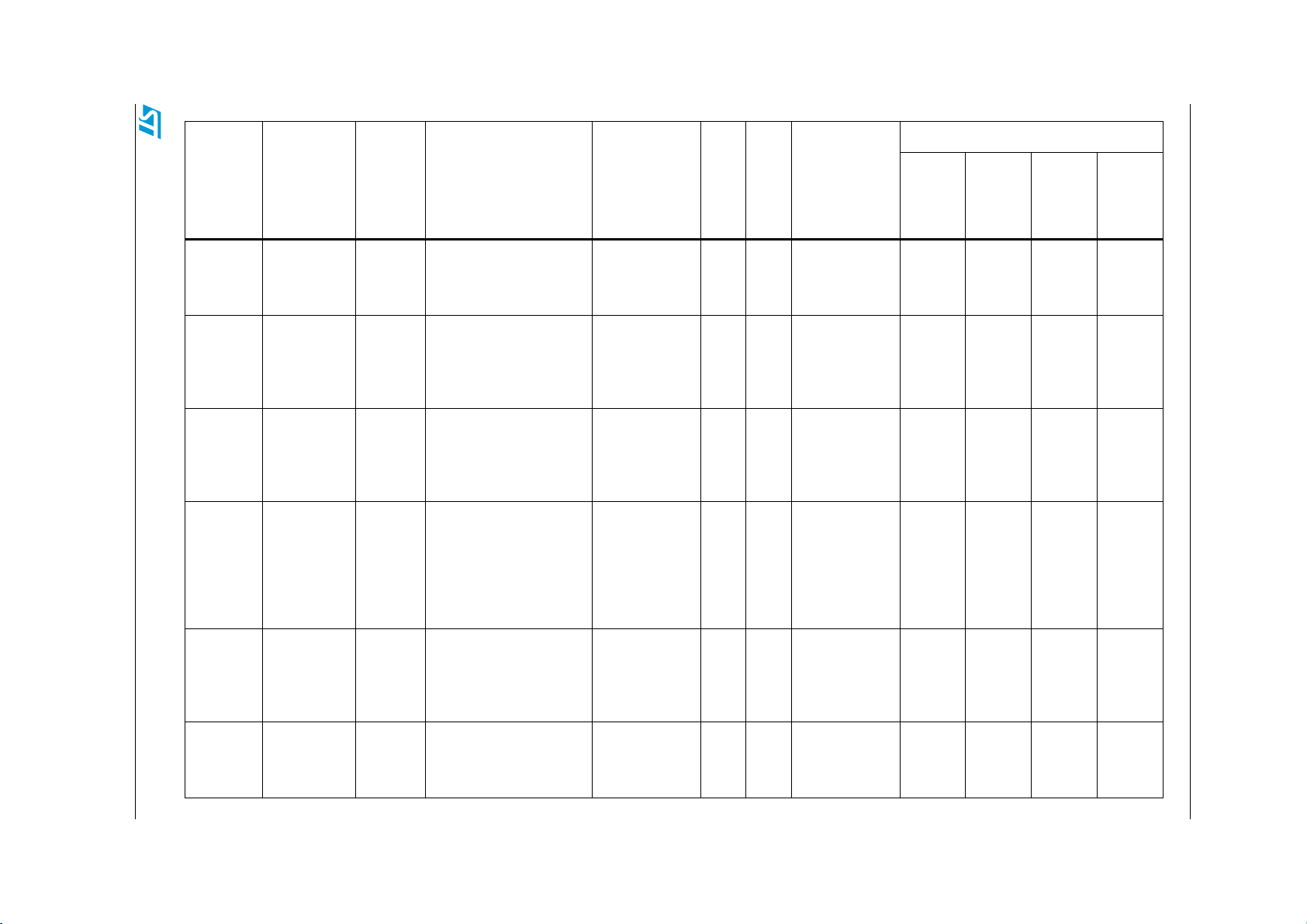

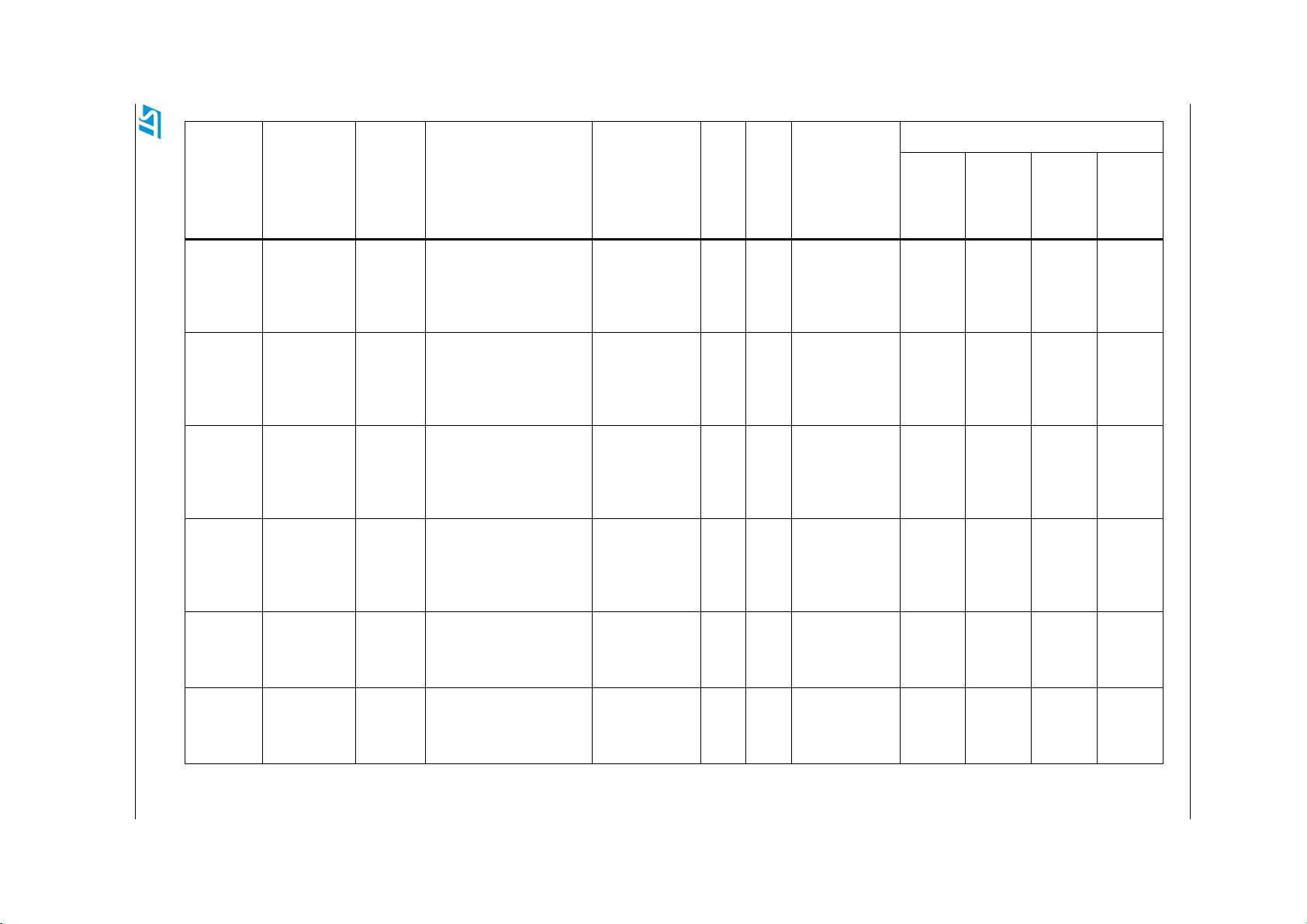

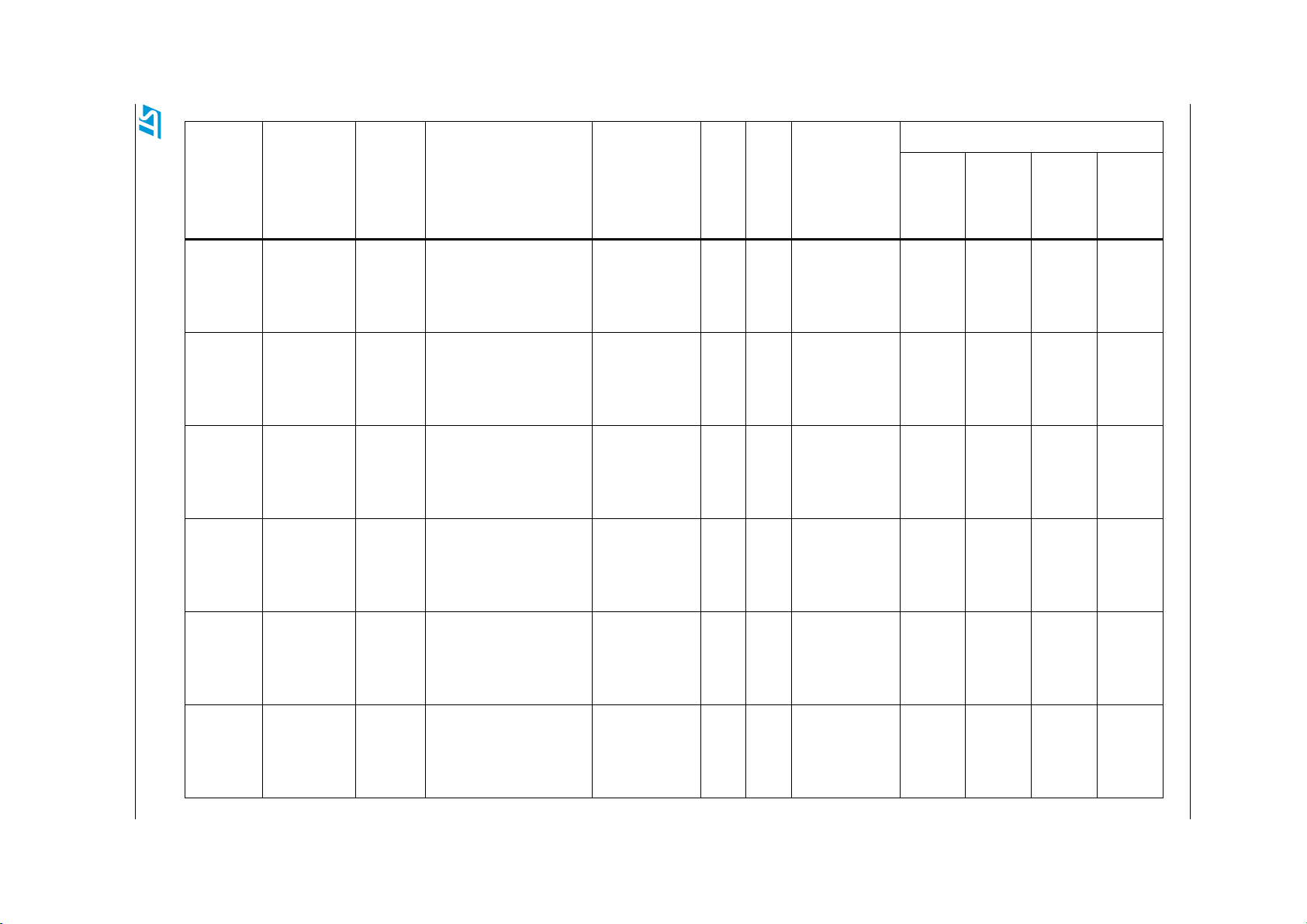

Table 2. SPC560B40x/50x and SPC560C40x/50x device comparison

(1)

(continued)

Device

Introduction SPC560B40x/50x, SPC560C40x/50x

Feature

SPC560B

40L1

SPC560B

40L3

SPC560B

40L5

SPC560C

40L1

SPC560C

40L3

SPC560B

50L1

SPC560B

50L3

SPC560B

50L5

SPC560C

50L1

SPC560C

50L3

SPC560B

50B2

Debug JTAG Nexus2+

Package LQFP64

1. Feature set dependent on selected peripheral multiplexing—table shows example implementation

2. Based on 125 °C ambient operating temperature

3. See the eMIOS section of the device reference manual for information on the channel configuration and functions.

4. IC – Input Capture; OC – Output Compare; PWM – Pulse Width Modulation; MC – Modulus counter

5. SCI0, SCI1 and SCI2 are available. SCI3 is not available.

6. CAN0, CAN1 are available. CAN2, CAN3, CAN4 and CAN5 are not available.

7. CAN0, CAN1 and CAN2 are available. CAN3, CAN4 and CAN5 are not available.

8. I/O count based on multiplexing with peripherals

9. All LQFP64 information is indicative and must be confirmed during silicon validation.

10. LBGA208 available only as development package for Nexus2+

(9)

LQFP100 LQFP144 LQFP64

(9)

LQFP100 LQFP64

(9)

LQFP100 LQFP144 LQFP64

(9)

LQFP100

LBGA208

(10)

SPC560B40x/50x, SPC560C40x/50x Block diagram

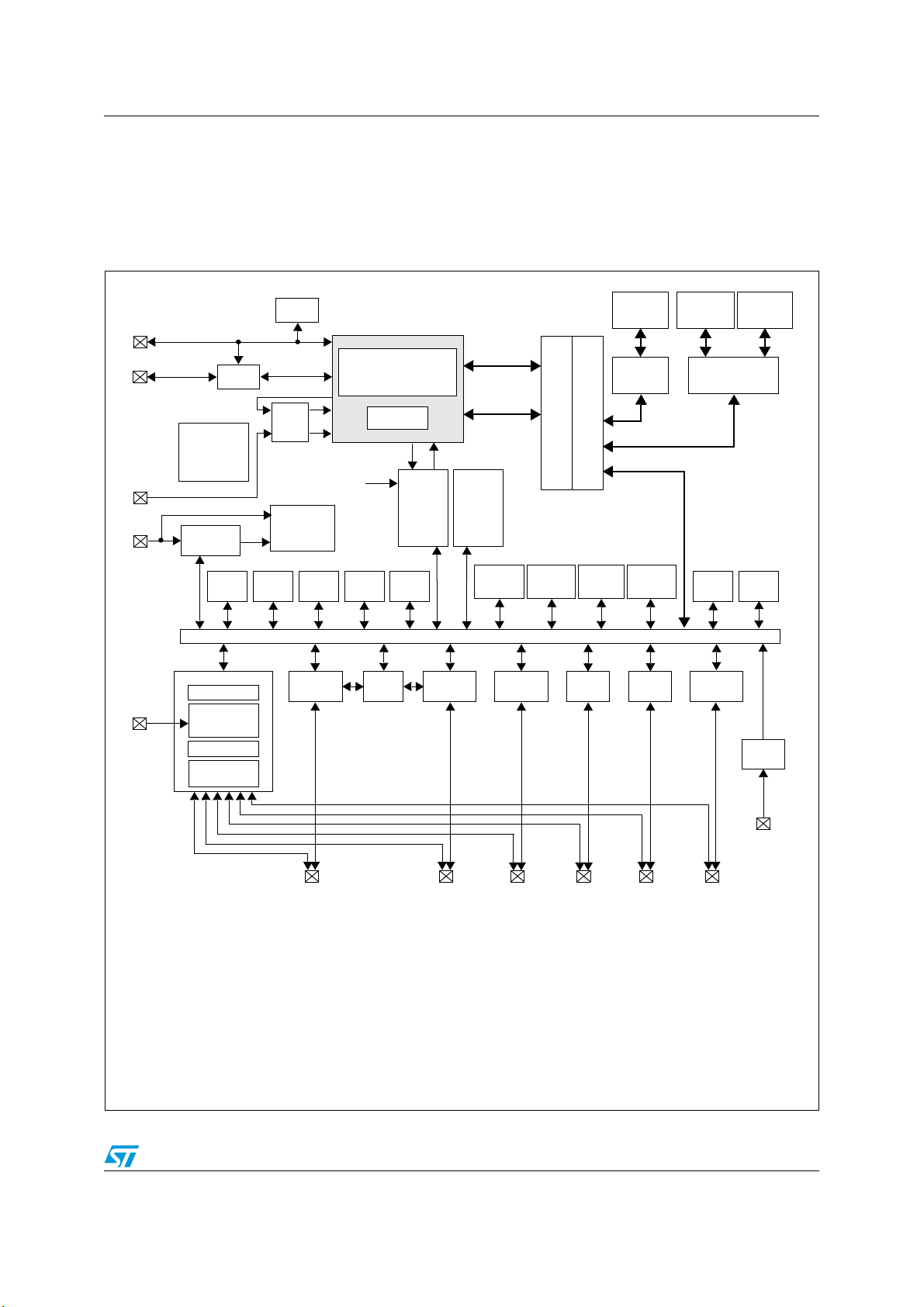

2 Block diagram

Figure 1 shows a top-level block diagram of the SPC560B40x/50x and SPC560C40x/50x

device series.

Figure 1. SPC560B40x/50x and SPC560C40x/50x block diagram

JTAG port

Nexus port

NMI

Clocks

Interrupt

request

Nexus

Vol ta ge

regulator

FMPLL

RTC

SIUL

Reset control

External

interrupt

request

IMUX

GPIO and

pad control

JTAG

NMI

SIUL

Interrupt requests

from peripheral

blocks

CMU

SWT

36 Ch.

ADC

ECSM

e200z0h

Nexus 2+

CTU

PITSTM

INTC

eMIOS

Instructions

(Master)

Data

(Master)

MPU

registers

Peripheral bridge

2 x

4 x

LINFlex

64-bit 2 x 3 Crossbar Switch

3 x

DSPI

MPU

SRAM

48 KB

SRAM

controller

(Slave)

MC_PCUMC_MEMC_CGMMC_RGM

I2C

Code Flash

512 KB

controller

(Slave)

BAM

6 x

FlexCAN

Data Flash

64 KB

Flash

(Slave)

SSCM

WKPU

I/O

Legend:

ADC Analog-to-Digital Converter

BAM Boot Assist Module

FlexCAN Controller Area Network

CMU Clock Monitor Unit

CTU Cross Triggering Unit

DSPI Deserial Serial Peripheral Interface

eMIOS Enhanced Modular Input Output System

FMPLL Frequency-Modulated Phase-Locked Loop

2

C Inter-integrated Circuit Bus

I

IMUX Internal Multiplexer

INTC Interrupt Controller

JTAG JTAG controller

LINFlex Serial Communication Interface (LIN support)

ECSM Error Correction Status Module

. . .

Doc ID 14619 Rev 9 11/117

. . .

MC_CGM Clock Generation Module

MC_ME Mode Entry Module

MC_PCU Power Control Unit

MC_RGM Reset Generation Module

MPU Memory Protection Unit

Nexus Nexus Development Interface (NDI) Level

NMI Non-Maskable Interrupt

PIT Periodic Interrupt Timer

RTC Real-Time Clock

SIUL System Integration Unit Lite

SRAM Static Random-Access Memory

SSCM System Status Configuration Module

STM System Timer Module

SWT Software Watchdog Timer

WKPU Wakeup Unit

. . .

. . .

. . .

Interrupt

request with

wakeup

functionality

Block diagram SPC560B40x/50x, SPC560C40x/50x

Ta bl e 3 summarizes the functions of all blocks present in the SPC560B40x/50x and

SPC560C40x/50x series of microcontrollers. Please note that the presence and number of

blocks vary by device and package.

Table 3. SPC560B40x/50x and SPC560C40x/50x series block summary

Analog-to-digital converter (ADC) Multi-channel, 10-bit analog-to-digital converter

Boot assist module (BAM)

Clock monitor unit (CMU) Monitors clock source (internal and external) integrity

Cross triggering unit (CTU)

Deserial serial peripheral

interface (DSPI)

Error Correction Status Module

(ECSM)

Enhanced Direct Memory Access

(eDMA)

Enhanced modular input output

system (eMIOS)

Block Function

A block of read-only memory containing VLE code which is executed according

to the boot mode of the device

Enables synchronization of ADC conversions with a timer event from the eMIOS

or from the PIT

Provides a synchronous serial interface for communication with external

devices

Provides a myriad of miscellaneous control functions for the device including

program-visible information about configuration and revision levels, a reset

status register, wakeup control for exiting sleep modes, and optional features

such as information on memory errors reported by error-correcting codes

Performs complex data transfers with minimal intervention from a host

processor via “n” programmable channels.

Provides the functionality to generate or measure events

Flash memory Provides non-volatile storage for program code, constants and variables

FlexCAN (controller area

network)

Frequency-modulated phaselocked loop (FMPLL)

Internal multiplexer (IMUX) SIU

subblock

2

Inter-integrated circuit (I

C™) bus

Supports the standard CAN communications protocol

Generates high-speed system clocks and supports programmable frequency

modulation

Allows flexible mapping of peripheral interface on the different pins of the device

A two wire bidirectional serial bus that provides a simple and efficient method of

data exchange between devices

Interrupt controller (INTC) Provides priority-based preemptive scheduling of interrupt requests

JTAG controller

LINFlex controller

Clock generation module

(MC_CGM)

Provides the means to test chip functionality and connectivity while remaining

transparent to system logic when not in test mode

Manages a high number of LIN (Local Interconnect Network protocol)

messages efficiently with a minimum of CPU load

Provides logic and control required for the generation of system and peripheral

clocks

Provides a mechanism for controlling the device operational mode and mode

Mode entry module (MC_ME)

transition sequences in all functional states; also manages the power control

unit, reset generation module and clock generation module, and holds the

configuration, control and status registers accessible for applications

12/117 Doc ID 14619 Rev 9

SPC560B40x/50x, SPC560C40x/50x Block diagram

Table 3. SPC560B40x/50x and SPC560C40x/50x series block summary (continued)

Block Function

Reduces the overall power consumption by disconnecting parts of the device

Power control unit (MC_PCU)

Reset generation module

(MC_RGM)

Memory protection unit (MPU)

from the power supply via a power switching device; device components are

grouped into sections called “power domains” which are controlled by the PCU

Centralizes reset sources and manages the device reset sequence of the

device

Provides hardware access control for all memory references generated in a

device

Nexus development interface

(NDI)

Periodic interrupt timer (PIT) Produces periodic interrupts and triggers

Real-time counter (RTC)

System integration unit (SIU)

Static random-access memory

(SRAM)

System status configuration

module (SSCM)

System timer module (STM)

System watchdog timer (SWT) Provides protection from runaway code

Wakeup unit (WKPU)

Crossbar (XBAR) switch

Provides real-time development support capabilities in compliance with the

IEEE-ISTO 5001-2003 standard

A free running counter used for time keeping applications, the RTC can be

configured to generate an interrupt at a predefined interval independent of the

mode of operation (run mode or low-power mode)

Provides control over all the electrical pad controls and up 32 ports with 16 bits

of bidirectional, general-purpose input and output signals and supports up to 32

external interrupts with trigger event configuration

Provides storage for program code, constants, and variables

Provides system configuration and status data (such as memory size and

status, device mode and security status), device identification data, debug

status port enable and selection, and bus and peripheral abort enable/disable

Provides a set of output compare events to support AUTOSAR and operating

system tasks

The wakeup unit supports up to 18 external sources that can generate

interrupts or wakeup events, of which 1 can cause non-maskable interrupt

requests or wakeup events.

Supports simultaneous connections between two master ports and three slave

ports. The crossbar supports a 32-bit address bus width and a 64-bit data bus

width.

Doc ID 14619 Rev 9 13/117

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

3 Package pinouts and signal descriptions

3.1 Package pinouts

The available LQFP pinouts and the LBGA208 ballmap are provided in the following figures.

For pin signal descriptions, please refer to the device reference manual (RM0017).

Figure 2. LQFP 64-pin configuration

PB[3]

1

PC[9]

2

PA[ 2 ]

3

PA[ 1 ]

4

PA[ 0 ]

5

VSS_HV

6

VDD_HV

7

VSS_HV

8

RESET

9

VSS_LV

10

VDD_LV

11

VDD_BV

12

PC[10]

13

PB[0]

14

PB[1]

15

PC[6]

16

(a)

PB[2]

PC[8]

PC[4]

PC[5]

PH[9]

PC[0]

VSS_LV

VDD_LV

VDD_HV

VSS_HV

PC[1]

PH[10]

PA[ 6 ]

646362616059585756555453525150

LQFP64 Top view

171819202122232425

PA[ 4 ]

PC[7]

PA[ 1 5 ]

PA[ 1 4 ]

PA[ 1 3 ]

PA[ 1 2 ]

VDD_LV

26272829303132

XTAL

EXTAL

VSS_LV

VSS_HV

PB[9]

VDD_HV

PA[ 5 ]

PC[2]

PC[3]

49

PA[ 1 1 ]

48

PA[ 1 0 ]

47

PA[ 9 ]

46

PA[ 8 ]

45

PA[ 7 ]

44

PA[ 3 ]

43

PB[15]

42

PB[14]

41

PB[13]

40

PB[12]

39

PB[11]

38

PB[7]

37

PB[6]

36

PB[5]

35

VDD_HV_ADC

34

VSS_HV_ADC

33

PB[8]

PB[4]

PB[10]

a. All LQFP64 information is indicative and must be confirmed during silicon validation.

14/117 Doc ID 14619 Rev 9

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

Figure 3. LQFP 100-pin configuration

PB[2]

PC[8]

PC[13]

PC[12]

PE[7]

PE[6]

PE[5]

PE[4]

PC[4]

PC[5]

PE[3]

PE[2]

PH[9]

PC[0]

VSS_LV

VDD_LV

VDD_HV

VSS_HV

PC[1]

PH[10]

PA[ 6 ]

PA[ 5 ]

PC[2]

PC[3]

PE[12]

PB[3]

PC[9]

PC[14]

PC[15]

PA[ 2 ]

PE[0]

PA[ 1 ]

PE[1]

PE[8]

PE[9]

PE[10]

PA[ 0 ]

PE[11]

VSS_HV

VDD_HV

VSS_HV

RESET

VSS_LV

VDD_LV

VDD_BV

PC[11]

PC[10]

PB[0]

PB[1]

PC[6]

9998979695949392919089888786858483828180797877

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26272829303132333435363738394041424344454647484950

PC[7]

PA[ 1 5 ]

PA[ 1 4 ]

LQFP100

PA[ 4 ]

PA[ 1 3 ]

PA[ 1 2 ]

VDD_LV

Top view

XTAL

EXTAL

VSS_LV

VSS_HV

PB[9]

PB[8]

PD[0]

PD[1]

PD[2]

PD[3]

PB[10]

VDD_HV

76

PA[11]

75

PA[10]

74

PA[ 9 ]

73

PA[ 8 ]

72

PA[ 7 ]

71

VDD_HV

70

VSS_HV

69

PA[ 3 ]

68

PB[15]

67

PD[15]

66

PB[14]

65

PD[14]

64

PB[13]

63

PD[13]

62

PB[12]

61

PD[12]

60

PB[11]

59

PD[11]

58

PD[10]

57

PD[9]

56

PB[7]

55

PB[6]

54

PB[5]

53

VDD_HV_ADC

52

VSS_HV_ADC

51

PB[4]

PD[4]

PD[5]

PD[6]

PD[7]

PD[8]

Note:

Availability of port pin alternate functions depends on product selection.

Doc ID 14619 Rev 9 15/117

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

Figure 4. LQFP 144-pin configuration

PB[2]

PC[8]

PC[13]

PC[12]

PE[7]

PE[6]

PH[8]

PH[7]

PH[6]

PH[5]

PH[4]

PE[5]

PE[4]

PC[4]

PC[5]

PE[3]

PE[2]

PH[9]

PC[0]

VSS_LV

VDD_LV

VDD_HV

VSS_HV

PC[1]

PH[10]

PA[ 6 ]

PA[ 5 ]

PC[2]

PC[3]

PG[11]

PG[10]

PE[15]

PE[14]

PG[15]

PG[14]

PE[12]

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

PB[3]

PC[9]

PC[14]

PC[15]

PG[5]

PG[4]

PG[3]

PG[2]

PA[ 2 ]

PE[0]

PA[ 1 ]

PE[1]

PE[8]

PE[9]

PE[10]

PA[ 0 ]

PE[11]

VSS_HV

VDD_HV

VSS_HV

RESET

VSS_LV

VDD_LV

VDD_BV

PG[9]

PG[8]

PC[11]

PC[10]

PG[7]

PG[6]

PB[0]

PB[1]

PF[9]

PF[8]

PF[12]

PC[6]

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

LQFP144

To p v i ew

3738394041424344454647484950515253545556575859606162636465666768697071

109

108

107

106

105

104

103

102

101

100

72

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

PA[ 11 ]

PA[ 10 ]

PA[ 9]

PA[ 8]

PA[ 7]

PE[13]

PF[14]

PF[15]

VDD_HV

VSS_HV

PG[0]

PG[1]

PH[3]

PH[2]

PH[1]

PH[0]

PG[12]

PG[13]

PA[ 3]

PB[15]

PD[15]

PB[14]

PD[14]

PB[13]

PD[13]

PB[12]

PD[12]

PB[11]

PD[11]

PD[10]

PD[9]

PB[7]

PB[6]

PB[5]

VDD_HV_ADC

VSS_HV_ADC

PA[ 4 ]

PC[7]

PA[ 1 5]

PA[ 1 4]

PF[10]

PF[11]

PF[13]

XTAL

PA[ 1 3]

PA[ 1 2]

VSS_LV

VDD_LV

VSS_HV

PF[0]

PF[1]

PF[2]

PF[3]

PF[4]

PF[5]

PF[6]

PB[9]

PB[8]

PB[10]

EXTAL

VDD_HV

PF[7]

PD[0]

PD[1]

PD[2]

PD[3]

PB[4]

PD[4]

PD[5]

PD[6]

PD[7]

PD[8]

Note:

Availability of port pin alternate functions depends on product selection.

16/117 Doc ID 14619 Rev 9

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

Figure 5. LBGA208 confguration

12345678910111213141516

A PC[8] PC[13]

BPC[9]PB[2]

CPC[14]

D

E PG[4] PG[5] PG[3] PG[2] PG[1] PG[0] PF[15]

F PE[0] PA[2] PA[1] PE[1] PH[0] PH[1] PH[3] PH[2] F

G PE[9] PE[8] PE[10] PA[0]

H

J RESET

K EVTI

L PG[9] PG[8]

M PG[7] PG[6] PC[10] PC[11] PB[13] PD[13] PD[12] PB[12] M

N PB[1] PF[9] PB[0]

PPF[8]

R PF[12] PC[6] PF[10] PF[11]

VDD_H

NC NC PC[15] NC PH[6] PE[4] PE[2]

VSS_H

PE[11]

V

VSS_L

NC NC PH[8] PH[4] PC[5] PC[0] NC NC PC[2] NC PE[15] NC NC NC A

NC PC[12] PE[6] PH[5] PC[4] PH[9] PH[10] NC PC[3] PG[11] PG[15] PG[14] PA[11] PA[10] B

VSS_L

PB[3] PE[7] PH[7] PE[5] PE[3]

V

VSS_HVVSS_HVVSS_HVVSS_H

VDD_H

V

VDD_BVVDD_L

NC

NC PC[7] NC NC PA[14]

NC

V

NC NC

V

NC EVTO PB[15] PD[15] PD[14] PB[14] L

NC NC PA[4]

VDD_H

V

VSS_HVVSS_HVVSS_HVVSS_H

VSS_HVVSS_HVVSS_HVVSS_H

VSS_HVVSS_HVVSS_HVVSS_H

VSS_L

V

VDD_L

V

PA [1 5 ] PA [ 13 ]

PC[1]

V

VDD_LVVDD_H

VDD_H

EXTAL

XTAL PB[10] PF[1] PF[5] PD[0] PD[3]

OSC32

NC

K_XTALPF[3] PF[7] PD[2] PD[4] PD[7]

NC PA[5] NC PE[14] PE[12] PA[9] PA[8] C

NC PA[6] NC PG[10] PF[14] PE[13] PA[7] D

V

V

V

V

V

PF[0] PF[4] NC PB[11] PD[10] PD[9] PD[11] N

V

VDD_H

MDO3 MDO2 MDO0 MDO1 H

NC NC NC NC J

NC PG[12] PA[3] PG[13] K

NC NC MSEO G

V

VDD_H

V_ADC

VSS_H

V_ADC

VDD_H

V

PB[6] PB[7] P

PB[5] R

E

NC NC NC MCKO NC PF[13] PA[12] NC

T

12345678910111213141516

Note: LBGA208 available only as development package for Nexus 2+.

OSC32

K_EXTALPF[2] PF[6] PD[1] PD[5] PD[6] PD[8] PB[4] T

= Not connected

NC

3.2 Pad configuration during reset phases

All pads have a fixed configuration under reset.

During the power-up phase, all pads are forced to tristate.

Doc ID 14619 Rev 9 17/117

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

After power-up phase, all pads are forced to tristate with the following exceptions:

● PA[9] (FAB) is pull-down. Without external strong pull-up the device starts fetching from

flash.

● PA[8] (ABS[0]) is pull-up.

● RESET pad is driven low. This is pull-up only after PHASE2 reset completion.

● JTAG pads (TCK, TMS and TDI) are pull-up whilst TDO remains tristate.

● Precise ADC pads (PB[7:4] and PD[11:0]) are left tristate (no output buffer available).

● Main oscillator pads (EXTAL, XTAL) are tristate.

● Nexus output pads (MDO[n], MCKO, EVTO, MSEO) are forced to output.

3.3 Voltage supply pins

Voltage supply pins are used to provide power to the device. Three dedicated

VDD_LV/VSS_LV supply pairs are used for 1.2 V regulator stabilization.

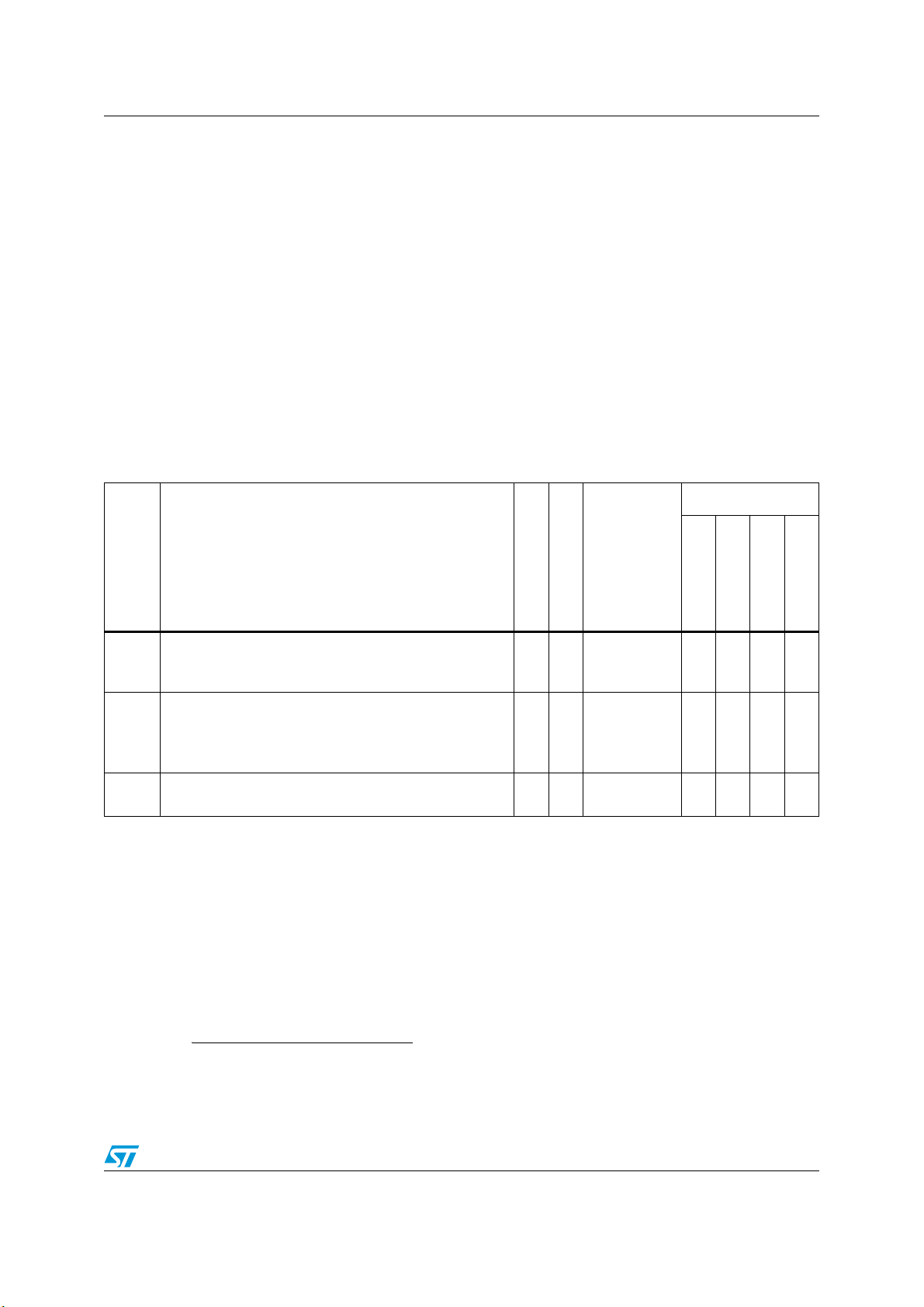

Table 4. Voltage supply pin descriptions

Port pin Function

Pin number

LQFP64 LQFP100 LQFP144 LBGA208

(1)

C2, D9, E16,

G13, H3,

N9, R5

VDD_HV Digital supply voltage 7, 28, 56

15, 37, 70, 8419, 51, 100,

123

G7, G8, G9,

G10, H1,

VSS_HV Digital ground 6, 8, 26, 55

14, 16, 35,

69, 83

18, 20, 49,

99, 122

H7, H8, H9,

H10, J7, J8,

J9, J10, K7,

K8, K9, K10

1.2V decoupling pins. Decoupling

VDD_LV

capacitor must be connected between

these pins and the nearest V

(2)

pin.

SS_LV

11, 23, 57 19, 32, 85 23, 46, 124 D8, K4, P7

1.2V decoupling pins. Decoupling

VSS_LV

capacitor must be connected between

these pins and the nearest V

(2)

pin.

DD_LV

10, 24, 58 18, 33, 86 22, 47, 125 C8, J2, N7

VDD_BV Internal regulator supply voltage 12 20 24 K3

VSS_HV_ADC

VDD_HV_ADC

1. LBGA208 available only as development package for Nexus2+.

2. A decoupling capacitor must be placed between each of the three VDD_LV/VSS_LV supply pairs to ensure stable voltage

(see the recommended operating conditions in the device datasheet for details).

Reference ground and analog ground

for the ADC

Reference voltage and analog supply

for the ADC

33 51 73 R15

34 52 74 P14

18/117 Doc ID 14619 Rev 9

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

3.4 Pad types

In the device the following types of pads are available for system pins and functional port

pins:

S = Slow

M = Medium

F = Fast

I = Input only with analog feature

(b)

(b)(c)

(b)(c)

(b)

J = Input/Output (‘S’ pad) with analog feature

X = Oscillator

3.5 System pins

The system pins are listed in Ta bl e 5 .

Table 5. System pin descriptions

Pin number

Function

System pin

RESET

Bidirectional reset with Schmitt-Trigger characteristics

and noise filter.

Analog output of the oscillator amplifier circuit, when the

EXTAL

XTAL

1. LBGA208 available only as development package for Nexus2+.

2. See the relevant section of the datasheet .

oscillator is not in bypass mode.

Analog input for the clock generator when the oscillator

is in bypass mode.

(2)

Analog input of the oscillator amplifier circuit. Needs to

be grounded if oscillator is used in bypass mode.

(2)

Pad type

I/O direction

LQFP64

LQFP100

LQFP144

RESET configuration

Input, weak

I/O M

pull-up only

91721J1

after PHASE2

I/O X Tristate 27 36 50 N8

I X Tristate 25 34 48 P8

(1)

LBGA208

b. See the I/O pad electrical characteristics in the device datasheet for details.

c. All medium and fast pads are in slow configuration by default at reset and can be configured as fast or medium

(see PCR.SRC in section Pad Configuration Registers (PCR0–PCR122) in the device reference manual).

Doc ID 14619 Rev 9 19/117

20/117 Doc ID 14619 Rev 9

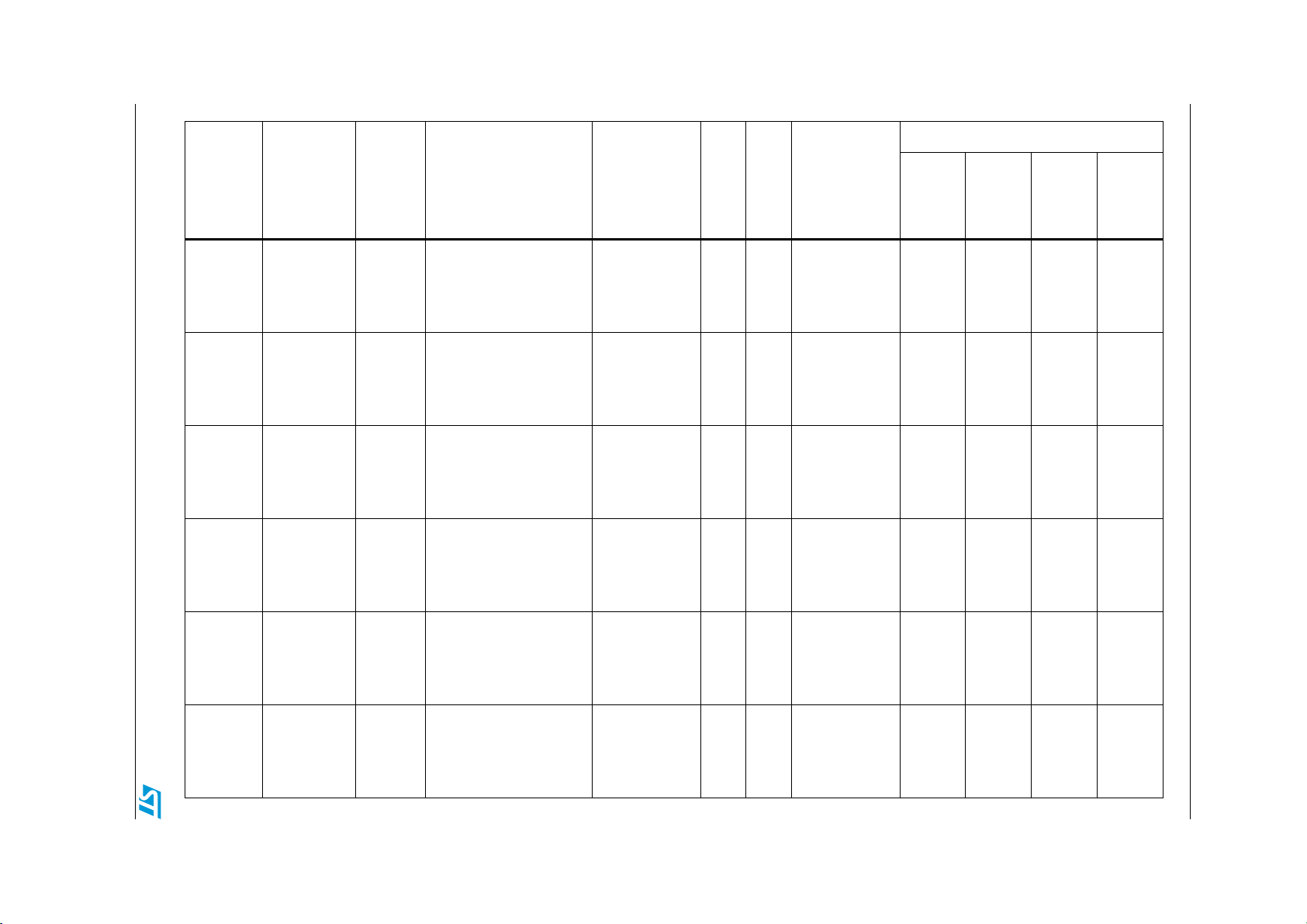

3.6 Functional ports

The functional port pins are listed in Ta bl e 6 .

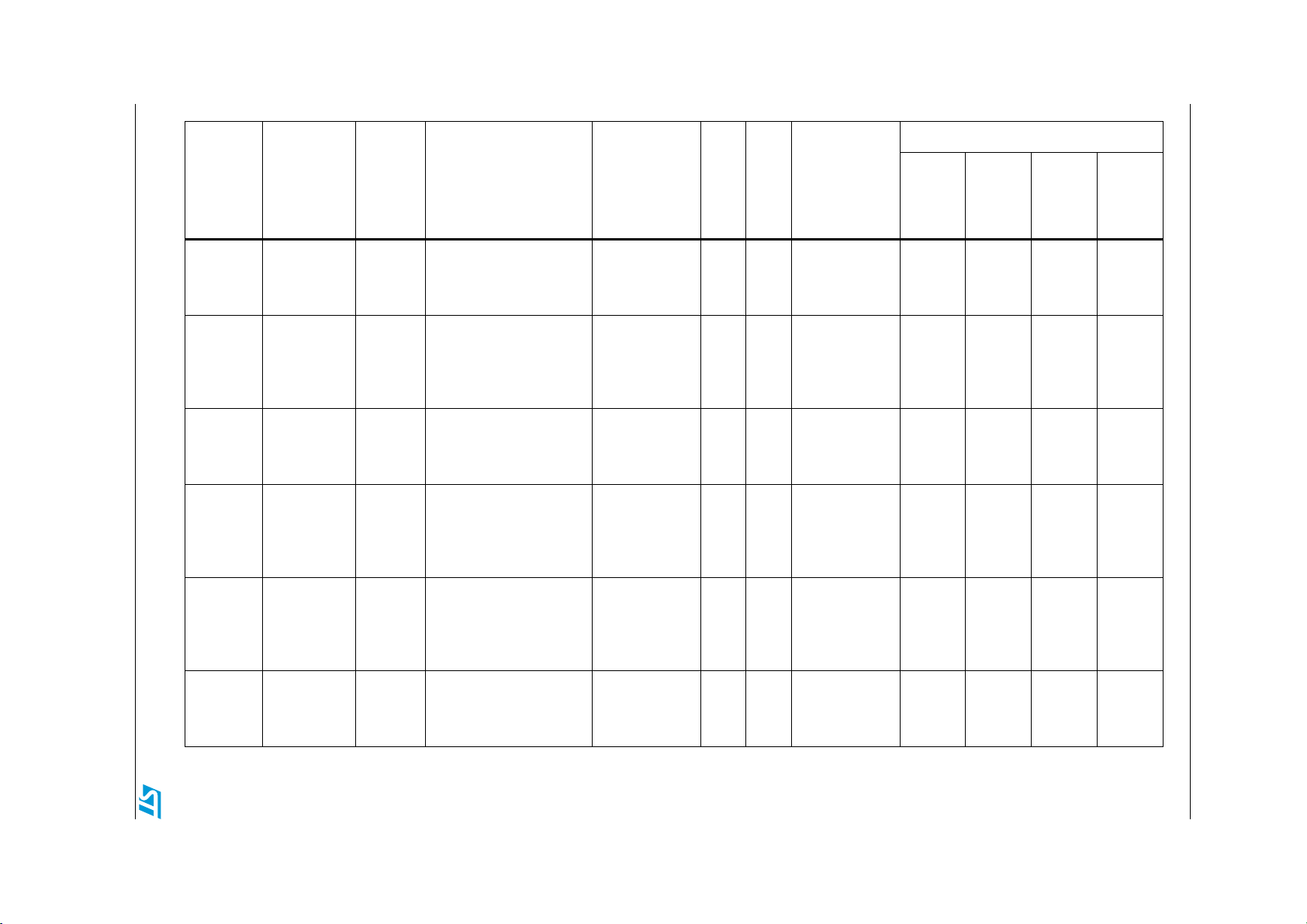

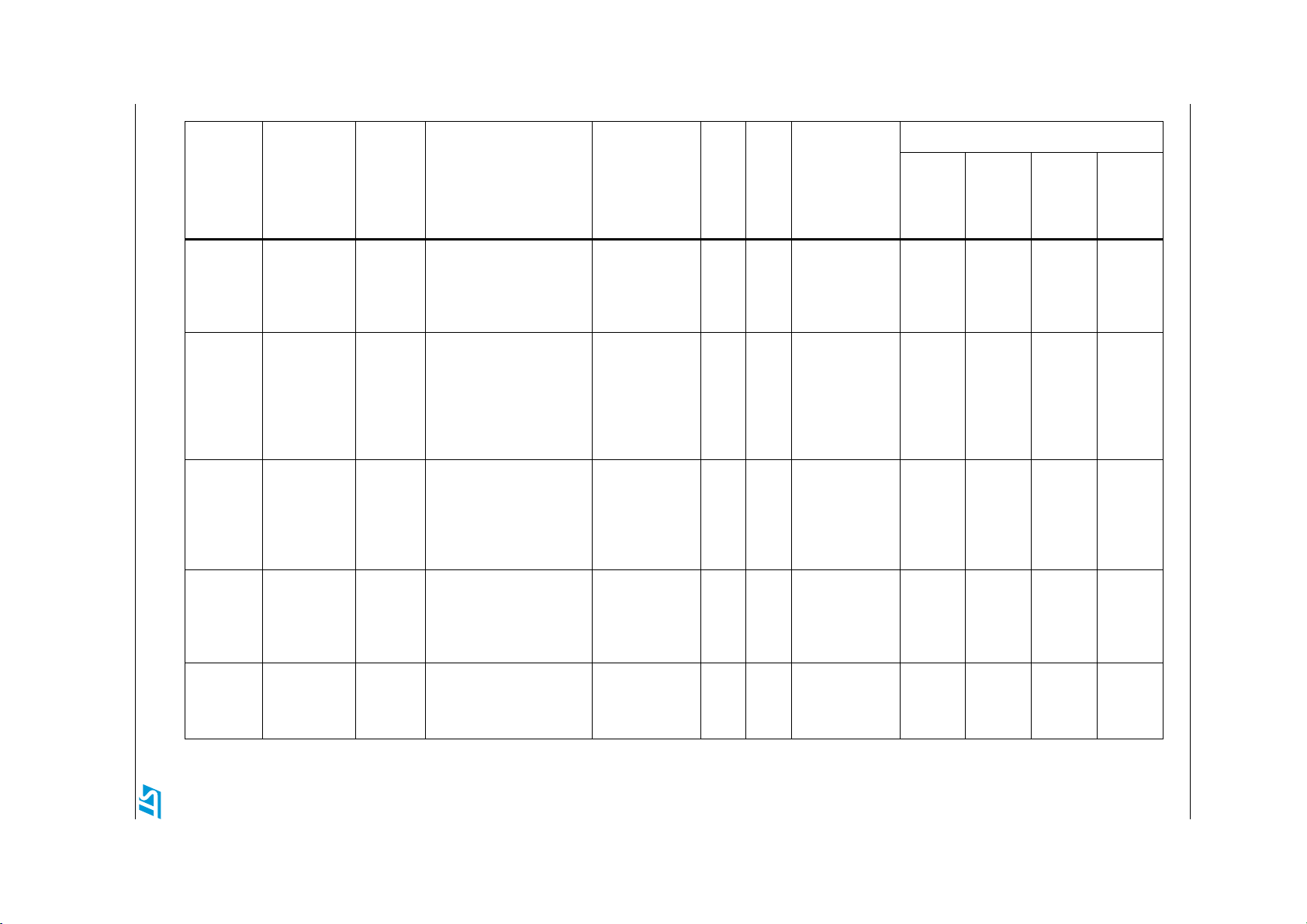

Table 6. Functional port pin descriptions

(1)

Port pin

PA[0] PCR[0] AF0

PA[1] PCR[1] AF0

PA[2] PCR[2] AF0

PA[3] PCR[3] AF0

PA[4] PCR[4] AF0

PCR

Alternate

AF1

AF2

AF3

—

AF1

AF2

AF3

—

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

function

Function

GPIO[0]

E0UC[0]

CLKOUT

—

WKPU[19]

GPIO[1]

E0UC[1]

—

—

(5)

NMI

WKPU[2]

GPIO[2]

E0UC[2]

—

—

WKPU[3]

GPIO[3]

E0UC[3]

—

—

EIRQ[0]

GPIO[4]

E0UC[4]

—

—

WKPU[9]

(4)

(4)

(4)

(4)

Peripheral

SIUL

eMIOS_0

CGL

—

WKPU

SIUL

eMIOS_0

—

—

WKPU

WKPU

SIUL

eMIOS_0

—

—

WKPU

SIUL

eMIOS_0

—

—

SIUL

SIUL

eMIOS_0

—

—

WKPU

I/O

I/O

O

—

I/O

I/O

—

—

I/O

I/O

—

—

I/O

I/O

—

—

I/O

I/O

—

—

(2)

I/O direction

Pad type

RESET

configuration

LQFP64

Pin number

LQFP100

LQFP144

M Tristate 5 12 16 G4

I

S Tristate 4 7 11 F3

I

I

STristate 359F2

I

STristate 436890K15

I

S Tristate 20 29 43 N6

I

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

(3)

LBGA208

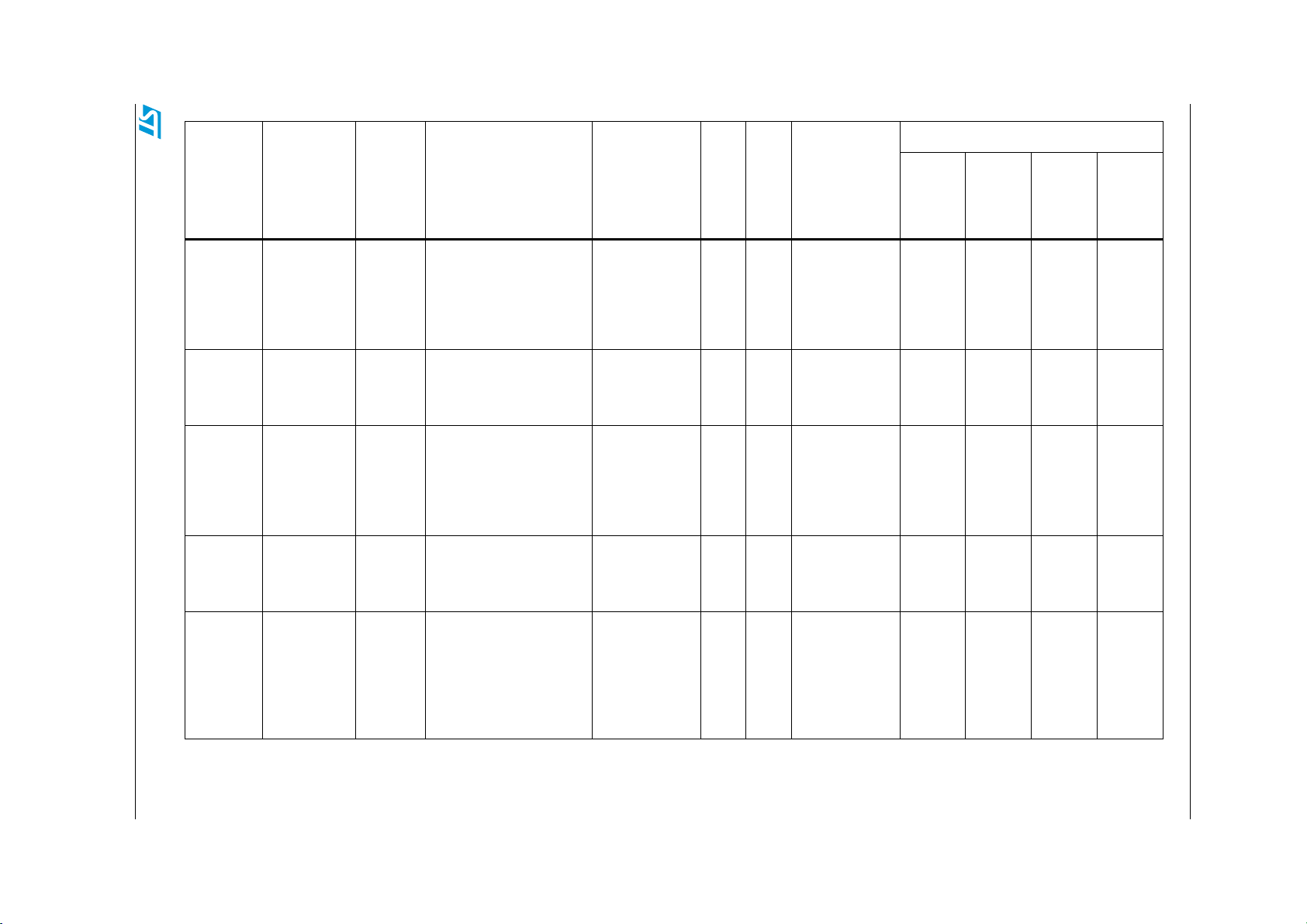

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PA[5] PCR[5] AF0

PA[6] PCR[6] AF0

Doc ID 14619 Rev 9 21/117

PA[7] PCR[7] AF0

PA[8] PCR[8] AF0

PA[9] PCR[9] AF0

PA[10] PCR[10] AF0

PCR

Alternate

AF1

AF2

AF3

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

N/A

—

AF1

AF2

AF3

N/A

AF1

AF2

AF3

function

(6)

(6)

GPIO[5]

E0UC[5]

GPIO[6]

E0UC[6]

EIRQ[1]

GPIO[7]

E0UC[7]

LIN3TX

EIRQ[2]

GPIO[8]

E0UC[8]

EIRQ[3]

ABS[0]

LIN3RX

GPIO[9]

E0UC[9]

FAB

GPIO[10]

E0UC[10]

SDA

—

—

—

—

—

—

—

—

—

—

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

(2)

Function

Peripheral

Pad type

I/O direction

SIUL

eMIOS_0

—

—

SIUL

eMIOS_0

—

—

SIUL

SIUL

eMIOS_0

LINFlex_3

—

SIUL

SIUL

eMIOS_0

—

—

SIUL

BAM

LINFlex_3

SIUL

eMIOS_0

—

—

BAM

SIUL

eMIOS_0

I2C_0

—

I/O

I/O

—

—

I/O

I/O

—

—

I/O

I/O

O

—

I/O

I/O

—

—

I/O

I/O

—

—

I/O

I/O

I/O

—

M Tristate 51 79 118 C11

S Tristate 52 80 119 D11

I

S Tristate 44 71 104 D16

I

S Input, weak

I

I

I

S Pull-down 46 73 106 C15

I

S Tristate 47 74 107 B16

RESET

pull-up

configuration

LQFP64

45 72 105 C16

Pin number

LQFP100

(3)

LQFP144

LBGA208

22/117 Doc ID 14619 Rev 9

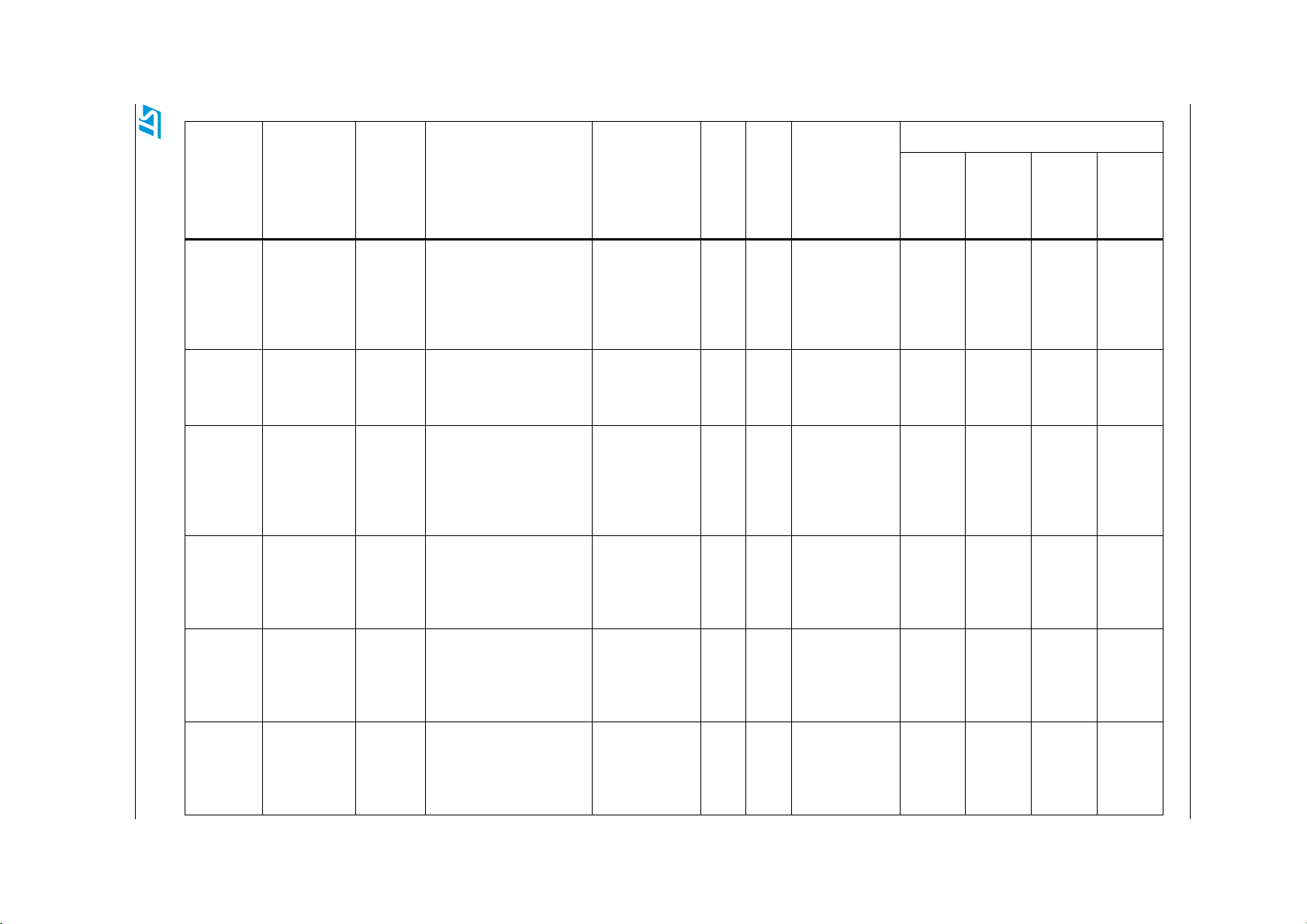

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PA[11] PCR[11] AF0

PCR

Alternate

AF1

AF2

function

GPIO[11]

E0UC[11]

SCL

AF3

PA[12] PCR[12] AF0

GPIO[12]

AF1

AF2

AF3

—

PA[13] PCR[13] AF0

AF1

SIN_0

GPIO[13]

SOUT_0

AF2

AF3

PA[14] PCR[14] AF0

AF1

AF2

GPIO[14]

SCK_0

CS0_0

AF3

—

PA[15] PCR[15] AF0

AF1

AF2

EIRQ[4]

GPIO[15]

CS0_0

SCK_0

AF3

—

PB[0] PCR[16] AF0

AF1

WKPU[10]

GPIO[16]

CAN0TX

AF2

AF3

—

—

—

—

—

—

—

—

—

—

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

(2)

Function

Peripheral

Pad type

I/O direction

(4)

SIUL

eMIOS_0

I2C_0

—

SIUL

—

—

—

DSPI0

SIUL

DSPI_0

—

—

SIUL

DSPI_0

DSPI_0

—

SIUL

SIUL

DSPI_0

DSPI_0

—

WKPU

SIUL

FlexCAN_0

—

—

I/O

I/O

I/O

—

I/O

—

—

—

I/O

O

—

—

I/O

I/O

I/O

—

I/O

I/O

I/O

—

I/O

O

—

—

S Tristate 48 75 108 B15

S Tristate 22 31 45 T7

I

M Tristate 21 30 44 R7

M Tristate 19 28 42 P6

I

M Tristate 18 27 40 R6

I

M Tristate 14 23 31 N3

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PB[1] PCR[17] AF0

PB[2] PCR[18] AF0

Doc ID 14619 Rev 9 23/117

PB[3] PCR[19] AF0

PB[4] PCR[20] AF0

PB[5] PCR[21] AF0

PB[6] PCR[22] AF0

PCR

Alternate

AF1

AF2

AF3

—

—

AF1

AF2

AF3

AF1

AF2

AF3

—

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

function

GPIO[17]

WKPU[4]

CAN0RX

GPIO[18]

LIN0TX

SDA

GPIO[19]

SCL

WKPU[11]

LIN0RX

GPIO[20]

GPI[0]

GPIO[21]

GPI[1]

GPIO[22]

GPI[2]

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

(2)

Function

Peripheral

Pad type

I/O direction

(4)

(4)

SIUL

—

—

—

WKPU

FlexCAN_0

SIUL

LINFlex_0

I2C_0

—

SIUL

—

I2C_0

—

WKPU

LINFlex_0

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

I/O

—

—

—

I/O

O

I/O

—

I/O

—

I/O

—

—

—

—

—

—

—

—

—

—

S Tristate 15 24 32 N1

I

I

M Tristate 64 100 144 B2

STristate 111C3

I

I

I

ITristate 325072T16

I

I

I Tristate 35 53 75 R16

I

I

ITristate 365476P15

I

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

24/117 Doc ID 14619 Rev 9

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PB[7] PCR[23] AF0

PCR

Alternate

function

GPIO[23]

AF1

AF2

AF3

—

PB[8] PCR[24] AF0

GPI[3]

GPIO[24]

AF1

AF2

AF3

—

—

PB[9] PCR[25] AF0

ANS[0]

OSC32K_XTAL

GPIO[25]

AF1

AF2

AF3

—

—

PB[10] PCR[26] AF0

ANS[1]

OSC32K_EXTAL

GPIO[26]

AF1

AF2

AF3

PB[11]

(8)

PCR[27] AF0

—

—

AF1

ANS[2]

WKPU[8]

GPIO[27]

E0UC[3]

AF2

AF3

—

CS0_0

ANS[3]

—

—

—

—

—

—

—

—

—

—

—

—

—

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

(2)

Function

Peripheral

Pad type

I/O direction

(4)

(7)

(7)

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SXOSC

SIUL

—

—

—

ADC

SXOSC

SIUL

—

—

—

ADC

WKPU

SIUL

eMIOS_0

—

DSPI_0

ADC

—

—

—

—

—

—

I/O

—

—

—

I/O

I/O

—

—

—

I/O

I/O

—

I/O

I

ITristate 375577P16

I

I

I Tristate 30 39 53 R9

I

I

I Tristate 29 38 52 T9

I

J Tristate 31 40 54 P9

I

I

J Tristate 38 59 81 N13

I

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

Table 6. Functional port pin descriptions (continued)

(1)

PCR

Alternate

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

PCR[32] AF0

AF1

AF2

AF3

PCR[33] AF0

AF1

AF2

AF3

function

GPIO[28]

E0UC[4]

CS1_0

ANX[0]

GPIO[29]

E0UC[5]

CS2_0

ANX[1]

GPIO[30]

E0UC[6]

CS3_0

ANX[2]

GPIO[31]

E0UC[7]

CS4_0

ANX[3]

GPIO[32]

GPIO[33]

TDO

Doc ID 14619 Rev 9 25/117

Port pin

PB[12] PCR[28] AF0

PB[13] PCR[29] AF0

PB[14] PCR[30] AF0

PB[15] PCR[31] AF0

(9)

PC[0]

(9)

PC[1]

—

—

—

—

—

TDI

—

—

—

Function

(10)

Peripheral

SIUL

eMIOS_0

—

DSPI_0

ADC

SIUL

eMIOS_0

—

DSPI_0

ADC

SIUL

eMIOS_0

—

DSPI_0

ADC

SIUL

eMIOS_0

—

DSPI_0

ADC

SIUL

—

JTAGC

—

SIUL

—

JTAGC

—

I/O

I/O

—

O

I/O

I/O

—

O

I/O

I/O

—

O

I/O

I/O

—

O

I/O

—

—

I/O

—

O

—

(2)

Pad type

I/O direction

RESET

configuration

LQFP64

Pin number

LQFP100

LQFP144

JTristate 396183M16

I

JTristate 406385M13

I

J Tristate 41 65 87 L16

I

J Tristate 42 67 89 L13

I

M Input, weak

59 87 126 A8

pull-up

I

MTristate 54 82121C9

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

(3)

LBGA208

26/117 Doc ID 14619 Rev 9

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PC[2] PCR[34] AF0

PCR

Alternate

AF1

AF2

function

GPIO[34]

SCK_1

CAN4TX

AF3

—

PC[3] PCR[35] AF0

AF1

AF2

EIRQ[5]

GPIO[35]

CS0_1

MA[0]

AF3

—

—

—

PC[4] PCR[36] AF0

CAN1RX

CAN4RX

EIRQ[6]

GPIO[36]

AF1

AF2

AF3

—

—

PC[5] PCR[37] AF0

AF1

AF2

SIN_1

CAN3RX

GPIO[37]

SOUT_1

CAN3TX

AF3

—

PC[6] PCR[38] AF0

AF1

EIRQ[7]

GPIO[38]

LIN1TX

AF2

AF3

—

—

—

—

—

—

—

—

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

(2)

Function

Peripheral

Pad type

I/O direction

(11)

(11)

(11)

(11)

SIUL

DSPI_1

FlexCAN_4

—

SIUL

SIUL

DSPI_1

ADC

—

FlexCAN_1

FlexCAN_4

SIUL

SIUL

—

—

—

DSPI_1

FlexCAN_3

SIUL

DSPI1

FlexCAN_3

—

SIUL

SIUL

LINFlex_1

—

—

I/O

I/O

O

—

I/O

I/O

O

—

I/O

—

—

—

I/O

O

O

—

I/O

O

—

—

M Tristate 50 78 117 A11

I

S Tristate 49 77 116 B11

I

I

I

MTristate 62 92131B7

I

I

MTristate 61 91130A7

I

S Tristate 16 25 36 R2

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PC[7] PCR[39] AF0

PC[8] PCR[40] AF0

Doc ID 14619 Rev 9 27/117

PC[9] PCR[41] AF0

PC[10] PCR[42] AF0

PC[11] PCR[43] AF0

PCR

Alternate

AF1

AF2

AF3

—

—

AF1

AF2

AF3

AF1

AF2

AF3

—

—

AF1

AF2

AF3

AF1

AF2

AF3

—

—

—

function

GPIO[39]

LIN1RX

WKPU[12]

GPIO[40]

LIN2TX

GPIO[41]

LIN2RX

WKPU[13]

GPIO[42]

CAN1TX

CAN4TX

MA[1]

GPIO[43]

CAN1RX

CAN4RX

WKPU[5]

—

—

—

—

—

—

—

—

—

—

—

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

(2)

Function

Peripheral

Pad type

I/O direction

(11)

(11)

(4)

(4)

(4)

SIUL

—

—

—

LINFlex_1

WKPU

SIUL

LINFlex_2

—

—

SIUL

—

—

—

LINFlex_2

WKPU

SIUL

FlexCAN_1

FlexCAN_4

ADC

SIUL

—

—

—

FlexCAN_1

FlexCAN_4

WKPU

I/O

—

—

—

I/O

O

—

—

I/O

—

—

—

I/O

O

O

O

I/O

—

—

—

S Tristate 17 26 37 P3

I

I

STristate 6399143A1

STristate 222B1

I

I

M Tristate 13 22 28 M3

S Tristate — 21 27 M4

I

I

I

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

28/117 Doc ID 14619 Rev 9

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PC[12] PCR[44] AF0

PCR

Alternate

AF1

function

GPIO[44]

E0UC[12]

AF2

AF3

—

PC[13] PCR[45] AF0

AF1

AF2

SIN_2

GPIO[45]

E0UC[13]

SOUT_2

AF3

PC[14] PCR[46] AF0

AF1

AF2

GPIO[46]

E0UC[14]

SCK_2

AF3

—

PC[15] PCR[47] AF0

AF1

AF2

EIRQ[8]

GPIO[47]

E0UC[15]

CS0_2

AF3

PD[0] PCR[48] AF0

GPIO[48]

AF1

AF2

AF3

—

PD[1] PCR[49] AF0

GPI[4]

GPIO[49]

AF1

AF2

AF3

—

GPI[5]

—

—

—

—

—

—

—

—

—

—

—

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

(2)

Function

Peripheral

Pad type

I/O direction

SIUL

eMIOS_0

—

—

DSPI_2

SIUL

eMIOS_0

DSPI_2

—

SIUL

eMIOS_0

DSPI_2

—

SIUL

SIUL

eMIOS_0

DSPI_2

—

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

I/O

I/O

—

—

I/O

I/O

O

—

I/O

I/O

I/O

—

I/O

I/O

I/O

—

—

—

—

—

—

—

M Tristate — 97 141 B4

I

S Tristate — 98 142 A2

STristate — 3 3 C1

I

MTristate — 4 4 D3

I

I Tristate — 41 63 P12

I

I

I Tristate — 42 64 T12

I

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PD[2] PCR[50] AF0

PD[3] PCR[51] AF0

Doc ID 14619 Rev 9 29/117

PD[4] PCR[52] AF0

PD[5] PCR[53] AF0

PD[6] PCR[54] AF0

PD[7] PCR[55] AF0

PCR

Alternate

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

AF1

AF2

AF3

—

function

GPIO[50]

GPI[6]

GPIO[51]

GPI[7]

GPIO[52]

GPI[8]

GPIO[53]

GPI[9]

GPIO[54]

GPI[10]

GPIO[55]

GPI[11]

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

SPC560B40x/50x, SPC560C40x/50x Package pinouts and signal descriptions

(2)

Function

Peripheral

Pad type

I/O direction

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

I

I Tristate — 43 65 R12

I

I

I Tristate — 44 66 P13

I

I

I Tristate — 45 67 R13

I

I

I Tristate — 46 68 T13

I

I Tristate — 47 69 T14

I

I

I

I Tristate — 48 70 R14

I

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

30/117 Doc ID 14619 Rev 9

Table 6. Functional port pin descriptions (continued)

(1)

Port pin

PD[8] PCR[56] AF0

PCR

Alternate

function

GPIO[56]

AF1

AF2

AF3

—

PD[9] PCR[57] AF0

GPI[12]

GPIO[57]

AF1

AF2

AF3

—

PD[10] PCR[58] AF0

GPI[13]

GPIO[58]

AF1

AF2

AF3

—

PD[11] PCR[59] AF0

GPI[14]

GPIO[59]

AF1

AF2

AF3

PD[12]

(8)

PCR[60] AF0

—

AF1

AF2

GPI[15]

GPIO[60]

CS5_0

E0UC[24]

AF3

—

PD[13] PCR[61] AF0

AF1

AF2

ANS[4]

GPIO[61]

CS0_1

E0UC[25]

AF3

—

ANS[5]

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Package pinouts and signal descriptions SPC560B40x/50x, SPC560C40x/50x

(2)

Function

Peripheral

Pad type

I/O direction

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

—

—

—

ADC

SIUL

DSPI_0

eMIOS_0

—

ADC

SIUL

DSPI_1

eMIOS_0

—

ADC

—

—

—

—

—

—

—

—

—

—

—

—

I/O

O

I/O

—

I/O

I/O

I/O

—

I

I Tristate — 49 71 T15

I

I

I Tristate — 56 78 N15

I

I

I Tristate — 57 79 N14

I

I

I Tristate — 58 80 N16

I

J Tristate — 60 82 M15

I

J Tristate — 62 84 M14

I

RESET

configuration

LQFP64

Pin number

LQFP100

(3)

LQFP144

LBGA208

Loading...

Loading...