M24LR64E-R

SO8 (MN)

150 mils width

UFDFPN8 (MC)

2 x 3 mm

TSSOP8 (DW)

Sawn wafer on UV tape

64-Kbit EEPROM with password protection, dual interface & energy

harvesting: 400 kHz I²C bus & ISO 15693 RF protocol at 13.56 MHz

Datasheet − production data

Features

I2C interface

■ Two-wire I

400 kHz protocol

■ Single supply voltage:

– 1.8 V to 5.5 V

■ Byte and Page Write (up to 4 bytes)

■ Random and Sequential read modes

■ Self-timed programming cycle

■ Automatic address incrementing

■ Enhanced ESD/latch-up protection

■ I²C timeout

2

C serial interface supports

Contactless interface

■ ISO 15693 and ISO 18000-3 mode 1

compatible

■ 13.56 MHz ± 7 kHz carrier frequency

■ To tag: 10% or 100% ASK modulation using

1/4 (26 Kbit/s) or 1/256 (1.6 Kbit/s) pulse

position coding

■ From tag: load modulation using Manchester

coding with 423 kHz and 484 kHz subcarriers

in low (6.6 kbit/s) or high (26 kbit/s) data rate

mode. Supports the 53 kbit/s data rate with

Fast commands

■ Internal tuning capacitance: 27.5 pF

■ 64-bit unique identifier (UID)

■ Read Block & Write (32-bit blocks)

Digital output pin

■ User configurable pin: RF write in progress or

RF busy mode

Energy harvesting

■ Analog pin for energy harvesting

■ 4 sink current configurable ranges

Memory

■ 64-Kbit EEPROM organized into:

– 8192 bytes in I

– 2048 blocks of 32 bits in RF mode

■ Write time

2

–I

C: 5 ms (max.)

– RF: 5.75 ms including the internal Verify

time

■ More than 1 million write cycles

■ More than 40-year data retention

■ Multiple password protection in RF mode

■ Single password protection in I

■ Package

– ECOPACK2

Halogen-free)

2

C mode

2

C mode

®

(RoHS compliant and

June 2012 Doc ID 022712 Rev 3 1/140

This is information on a product in full production.

www.st.com

1

Contents M24LR64E-R

Contents

1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2 Signal descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.1 Serial clock (SCL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.2 Serial data (SDA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3 RF Write in progress / RF Busy (RF WIP/BUSY) . . . . . . . . . . . . . . . . . . . 15

2.4 Energy harvesting analog output (Vout) . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.5 Antenna coil (AC0, AC1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.5.1 Device reset in RF mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.6 VSS ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.7 Supply voltage (V

2.7.1 Operating supply voltage V

2.7.2 Power-up conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.7.3 Device reset in I²C mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.7.4 Power-down conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

CC

CC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3 User memory organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4 System memory area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.1 M24LR64E-R block security in RF mode . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.1.1 Example of the M24LR64E-R security protection in RF mode . . . . . . . 26

4.2 M24LR64E-R block security in I²C mode (I2C_Write_Lock bit area) . . . . 27

4.3 Configuration byte and Control register . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.3.1 RF WIP/BUSY pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.3.2 Energy harvesting configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.3.3 FIELD_ON indicator bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

4.3.4 Configuration byte access in I²C and RF modes . . . . . . . . . . . . . . . . . . 30

4.3.5 Control register access in I²C or RF mode . . . . . . . . . . . . . . . . . . . . . . 30

4.4 ISO 15693 system parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5I

2

C device operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.1 Start condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.2 Stop condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2/140 Doc ID 022712 Rev 3

M24LR64E-R Contents

5.3 Acknowledge bit (ACK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.4 Data input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.5 I²C timeout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.5.1 I²C timeout on Start condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.5.2 I²C timeout on clock period . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.6 Memory addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.7 Write operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.8 Byte write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5.9 Page write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5.10 Minimizing system delays by polling on ACK . . . . . . . . . . . . . . . . . . . . . . 36

5.11 Read operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.12 Random Address Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.13 Current Address Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.14 Sequential Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.15 Acknowledge in Read mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.16 M24LR64E-R I

5.16.1 I2C present password command description . . . . . . . . . . . . . . . . . . . . . 39

5.16.2 I

2

C password security . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2

C write password command description . . . . . . . . . . . . . . . . . . . . . . . 40

6 M24LR64E-R memory initial state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

7 RF device operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.1 RF communication and energy harvesting . . . . . . . . . . . . . . . . . . . . . . . . 42

7.2 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

7.3 Initial dialog for vicinity cards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

7.3.1 Power transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

7.3.2 Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

7.3.3 Operating field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

8 Communication signal from VCD to M24LR64E-R . . . . . . . . . . . . . . . . 45

9 Data rate and data coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9.1 Data coding mode: 1 out of 256 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9.2 Data coding mode: 1 out of 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

9.3 VCD to M24LR64E-R frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Doc ID 022712 Rev 3 3/140

Contents M24LR64E-R

9.4 Start of frame (SOF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

10 Communication signal from M24LR64E-R to VCD . . . . . . . . . . . . . . . . 52

10.1 Load modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

10.2 Subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

10.3 Data rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

11 Bit representation and coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.1 Bit coding using one subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.1.1 High data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.1.2 Low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

11.2 Bit coding using two subcarriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

11.2.1 High data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

11.2.2 Low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

12 M24LR64E-R to VCD frames . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.1 SOF when using one subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.1.1 High data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.1.2 Low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.2 SOF when using two subcarriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.2.1 High data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.2.2 Low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.3 EOF when using one subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

12.3.1 High data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

12.3.2 Low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

12.4 EOF when using two subcarriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

12.4.1 High data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

12.4.2 Low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

13 Unique identifier (UID) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

14 Application family identifier (AFI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

15 Data storage format identifier (DSFID) . . . . . . . . . . . . . . . . . . . . . . . . . 62

15.1 CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

16 M24LR64E-R protocol description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4/140 Doc ID 022712 Rev 3

M24LR64E-R Contents

17 M24LR64E-R states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

17.1 Power-off state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

17.2 Ready state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

17.3 Quiet state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

17.4 Selected state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

18 Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

18.1 Addressed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

18.2 Non-addressed mode (general request) . . . . . . . . . . . . . . . . . . . . . . . . . 67

18.3 Select mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

19 Request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

19.1 Request flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

20 Response format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

20.1 Response flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

20.2 Response error code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

21 Anticollision . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

21.1 Request parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

22 Request processing by the M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . . 74

23 Explanation of the possible cases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

24 Inventory Initiated command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

25 Timing definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

25.1 t1: M24LR64E-R response delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

25.2 t2: VCD new request delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

25.3 t

: VCD new request delay when no response is received

3

from the M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

26 Command codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

26.1 Inventory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

26.2 Stay Quiet . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Doc ID 022712 Rev 3 5/140

Contents M24LR64E-R

26.3 Read Single Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

26.4 Write Single Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

26.5 Read Multiple Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

26.6 Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

26.7 Reset to Ready . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

26.8 Write AFI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

26.9 Lock AFI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

26.10 Write DSFID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

26.11 Lock DSFID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

26.12 Get System Info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

26.13 Get Multiple Block Security Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

26.14 Write-sector Password . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

26.15 Lock-sector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

26.16 Present-sector Password . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

26.17 Fast Read Single Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

26.18 Fast Inventory Initiated . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

26.19 Fast Initiate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

26.20 Fast Read Multiple Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

26.21 Inventory Initiated . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

26.22 Initiate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

26.23 ReadCfg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

26.24 WriteEHCfg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

26.25 WriteDOCfg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

26.26 SetRstEHEn . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

26.27 CheckEHEn . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

27 Maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

28 I2C DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

29 RF electrical parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

30 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

31 Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

6/140 Doc ID 022712 Rev 3

M24LR64E-R Contents

Appendix A Anticollision algorithm (informative) . . . . . . . . . . . . . . . . . . . . . . . 135

A.1 Algorithm for pulsed slots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Appendix B CRC (informative) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

B.1 CRC error detection method . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

B.2 CRC calculation example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Appendix C Application family identifier (AFI) (informative) . . . . . . . . . . . . . . 138

32 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Doc ID 022712 Rev 3 7/140

List of tables M24LR64E-R

List of tables

Table 1. Signal names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 2. Device select code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 3. Address most significant byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 4. Address least significant byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 5. Sector details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 6. Sector security status byte area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 7. Sector security status byte organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 8. Read/Write protection bit setting. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 9. Password control bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 10. Password system area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 11. M24LR64E-R sector security protection after power-up. . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 12. M24LR64E-R sector security protection after a valid presentation of password 1 . . . . . . . 26

Table 13. I2C_Write_Lock bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 14. Configuration byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 15. Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 16. EH_enable bit value after power-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 17. System parameter sector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 18. Operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 19. 10% modulation parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 20. Response data rates. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 21. UID format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 22. CRC transmission rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 23. VCD request frame format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 24. M24LR64E-R Response frame format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 25. M24LR64E-R response depending on Request_flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 26. General request format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 27. Definition of request flags 1 to 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 28. Request flags 5 to 8 when Bit 3 = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 29. Request flags 5 to 8 when Bit 3 = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 30. General response format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 31. Definitions of response flags 1 to 8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 32. Response error code definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 33. Inventory request format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 34. Example of the addition of 0-bits to an 11-bit mask value . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 35. Timing values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 36. Command codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 37. Inventory request format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 38. Inventory response format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 39. Stay Quiet request format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 40. Read Single Block request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 41. Read Single Block response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . 83

Table 42. Sector security status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 43. Read Single Block response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 44. Write Single Block request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 45. Write Single Block response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . 84

Table 46. Write Single Block response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 47. Read Multiple Block request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 48. Read Multiple Block response format when Error_flag is NOT set. . . . . . . . . . . . . . . . . . . 88

8/140 Doc ID 022712 Rev 3

M24LR64E-R List of tables

Table 49. Sector security status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 50. Read Multiple Block response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . 89

Table 51. Select request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 52. Select Block response format when Error_flag is NOT set. . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 53. Select response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 54. Reset to Ready request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 55. Reset to Ready response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . 91

Table 56. Reset to ready response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 57. Write AFI request format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 58. Write AFI response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 59. Write AFI response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 60. Lock AFI request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 61. Lock AFI response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 62. Lock AFI response format when Error_flag is set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 63. Write DSFID request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 64. Write DSFID response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 65. Write DSFID response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 66. Lock DSFID request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 67. Lock DSFID response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 68. Lock DSFID response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 69. Get System Info request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 70. Get System Info response format when Protocol_extension_flag = 0 and

Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 71. Get System Info response format when Protocol_extension_flag = 1 and

Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 72. Get System Info response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 73. Get Multiple Block Security Status request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 74. Get Multiple Block Security Status response format when Error_flag is NOT set . . . . . . 100

Table 75. Sector security status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 76. Get Multiple Block Security Status response format when Error_flag is set . . . . . . . . . . . 100

Table 77. Write-sector Password request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 78. Write-sector Password response format when Error_flag is NOT set . . . . . . . . . . . . . . . 101

Table 79. Write-sector Password response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . 101

Table 80. Lock-sector request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 81. Sector security status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 82. Lock-sector response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 83. Lock-sector response format when Error_flag is set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 84. Present-sector Password request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 85. Present-sector Password response format when Error_flag is NOT set . . . . . . . . . . . . . 104

Table 86. Present-sector Password response format when Error_flag is set . . . . . . . . . . . . . . . . . . 104

Table 87. Fast Read Single Block request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 88. Fast Read Single Block response format when Error_flag is NOT set . . . . . . . . . . . . . . . 106

Table 89. Sector security status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 90. Fast Read Single Block response format when Error_flag is set . . . . . . . . . . . . . . . . . . . 106

Table 91. Fast Inventory Initiated request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 92. Fast Inventory Initiated response format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 93. Fast Initiate request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 94. Fast Initiate response format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 95. Fast Read Multiple Block request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 96. Fast Read Multiple Block response format when Error_flag is NOT set. . . . . . . . . . . . . . 110

Table 97. Sector security status if Option_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 98. Fast Read Multiple Block response format when Error_flag is set . . . . . . . . . . . . . . . . . . 110

Doc ID 022712 Rev 3 9/140

List of tables M24LR64E-R

Table 99. Inventory Initiated request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 100. Inventory Initiated response format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 101. Initiate request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 102. Initiate response format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 103. ReadCfg request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 104. ReadCfg response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 105. ReadCfg response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Table 106. WriteEHCfg request format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 107. WriteEHCfg response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 108. WriteEHCfg response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 109. WriteDOCfg request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 110. WriteDOCfg response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 111. WriteDOCfg response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 112. SetRstEHEn request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 113. SetRstEHEn response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . 117

Table 114. SetRstEHEn response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 115. CheckEHEn request format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 116. CheckEHEn response format when Error_flag is NOT set . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 117. CheckEHEn response format when Error_flag is set . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 118. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 119. I

2

C operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 120. AC test measurement conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 121. Input parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 122. I

Table 123. I

2

C DC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

2

C AC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 124. RF characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Table 125. Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Table 126. Energy harvesting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Table 127. SO8N – 8-lead plastic small outline, 150 mils body width, package data. . . . . . . . . . . . . 131

Table 128. UFDFPN8 (MLP8) 8-lead ultra thin fine pitch dual flat package no lead

2 x 3 mm, data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 129. TSSOP8 – 8-lead thin shrink small outline, package mechanical data. . . . . . . . . . . . . . . 133

Table 130. Ordering information scheme for packaged devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 131. CRC definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 132. AFI coding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Table 133. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

10/140 Doc ID 022712 Rev 3

M24LR64E-R List of figures

List of figures

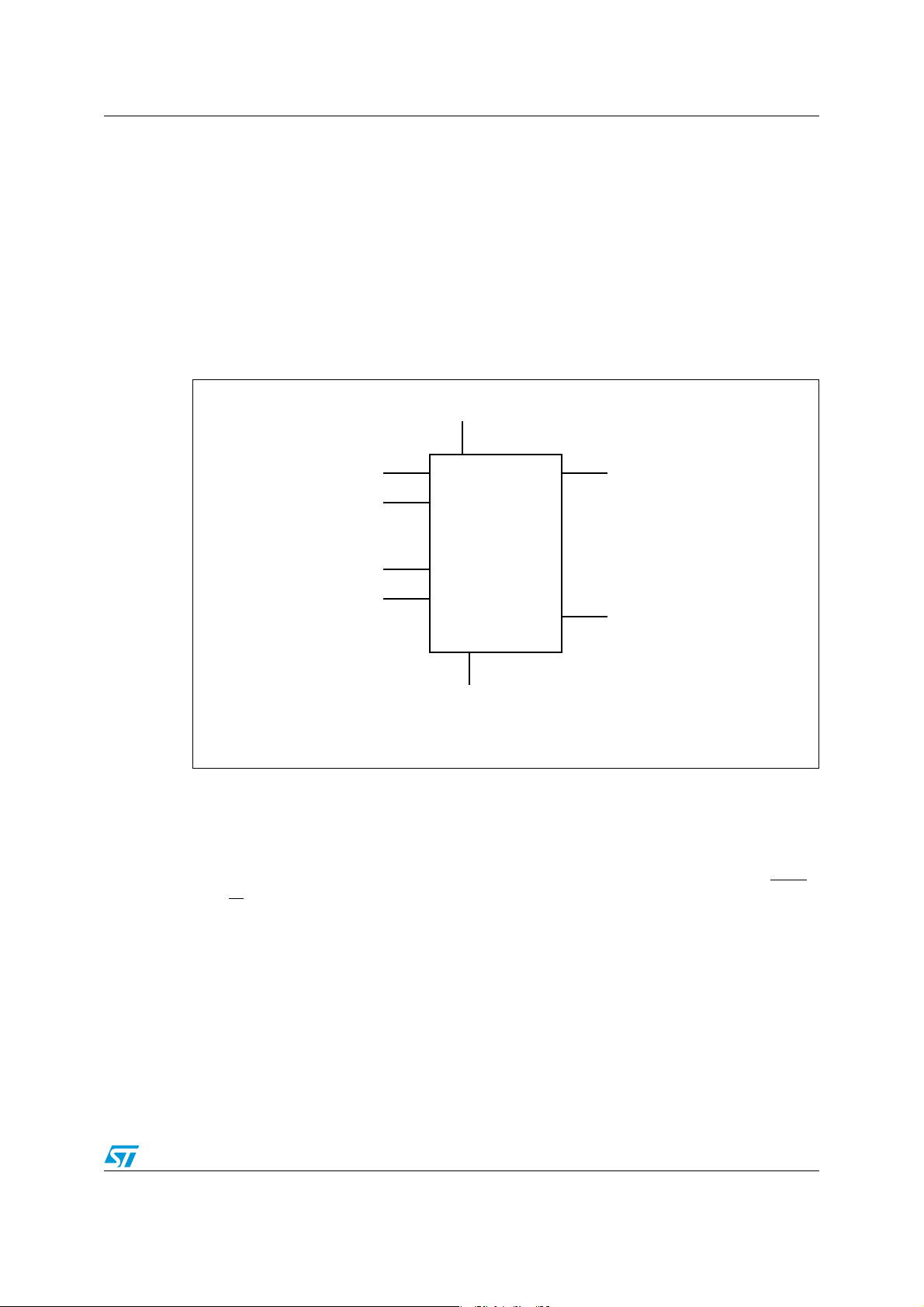

Figure 1. Logic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 2. 8-pin package connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 3. I

Figure 4. I

Figure 5. Circuit diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 6. Memory sector organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 7. I²C timeout on Start condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 8. Write mode sequences with I2C_Write_Lock bit = 1 (data write inhibited). . . . . . . . . . . . . 34

Figure 9. Write mode sequences with I2C_Write_Lock bit = 0 (data write enabled) . . . . . . . . . . . . . 35

Figure 10. Write cycle polling flowchart using ACK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 11. Read mode sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 12. I

Figure 13. I

Figure 14. 100% modulation waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 15. 10% modulation waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 16. 1 out of 256 coding mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 17. Detail of a time period. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 18. 1 out of 4 coding mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 19. 1 out of 4 coding example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 20. SOF to select 1 out of 256 data coding mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 21. SOF to select 1 out of 4 data coding mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 22. EOF for either data coding mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 23. Logic 0, high data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 24. Logic 0, high data rate, fast commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 25. Logic 1, high data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 26. Logic 1, high data rate, fast commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 27. Logic 0, low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 28. Logic 0, low data rate, fast commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 29. Logic 1, low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 30. Logic 1, low data rate, fast commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 31. Logic 0, high data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 32. Logic 1, high data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 33. Logic 0, low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 34. Logic 1, low data rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 35. Start of frame, high data rate, one subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 36. Start of frame, high data rate, one subcarrier, fast commands. . . . . . . . . . . . . . . . . . . . . . 56

Figure 37. Start of frame, low data rate, one subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 38. Start of frame, low data rate, one subcarrier, fast commands . . . . . . . . . . . . . . . . . . . . . . 57

Figure 39. Start of frame, high data rate, two subcarriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 40. Start of frame, low data rate, two subcarriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 41. End of frame, high data rate, one subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 42. End of frame, high data rate, one subcarrier, fast commands . . . . . . . . . . . . . . . . . . . . . . 58

Figure 43. End of frame, low data rate, one subcarrier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 44. End of frame, low data rate, one subcarrier, Fast commands . . . . . . . . . . . . . . . . . . . . . . 58

Figure 45. End of frame, high data rate, two subcarriers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 46. End of frame, low data rate, two subcarriers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 47. M24LR64E-R decision tree for AFI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

2

C Fast mode (fC = 400 kHz): maximum R

capacitance (C

2

C bus protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2

C present password command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2

C write password command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

bus

value versus bus parasitic

bus

Doc ID 022712 Rev 3 11/140

List of figures M24LR64E-R

Figure 48. M24LR64E-R protocol timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 49. M24LR64E-R state transition diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 50. Principle of comparison between the mask, the slot number and the UID . . . . . . . . . . . . . 73

Figure 51. Description of a possible anticollision sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 52. M24LR64E RF-Busy management following Inventory command . . . . . . . . . . . . . . . . . . . 81

Figure 53. Stay Quiet frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . 82

Figure 54. Read Single Block frame exchange between VCD and M24LR64E-R. . . . . . . . . . . . . . . . 84

Figure 55. Write Single Block frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . 85

Figure 56. M24LR64E RF-Busy management following Write command . . . . . . . . . . . . . . . . . . . . . . 86

Figure 57. M24LR64E RF-Wip management following Write command . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 58. Read Multiple Block frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . 89

Figure 59. Select frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 60. Reset to Ready frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . 91

Figure 61. Write AFI frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 62. Lock AFI frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 63. Write DSFID frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . 96

Figure 64. Lock DSFID frame exchange between VCD and M24LR64E-R. . . . . . . . . . . . . . . . . . . . . 97

Figure 65. Get System Info frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . 99

Figure 66. Get Multiple Block Security Status frame exchange between VCD and M24LR64E-R . . 100

Figure 67. Write-sector Password frame exchange between VCD and M24LR64E-R . . . . . . . . . . . 102

Figure 68. Lock-sector frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . 103

Figure 69. Present-sector Password frame exchange between VCD and M24LR64E-R . . . . . . . . . 105

Figure 70. Fast Read Single Block frame exchange between VCD and M24LR64E-R. . . . . . . . . . . 106

Figure 71. Fast Initiate frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . 109

Figure 72. Fast Read Multiple Block frame exchange between VCD and M24LR64E-R . . . . . . . . . 110

Figure 73. Initiate frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . . . 112

Figure 74. ReadCfg frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . . . . 114

Figure 75. WriteEHCfg frame exchange between VCD and M24LR64E-R. . . . . . . . . . . . . . . . . . . . 115

Figure 76. WriteDOCfg frame exchange between VCD and M24LR64E-R. . . . . . . . . . . . . . . . . . . . 116

Figure 77. SetRstEHEn frame exchange between VCD and M24LR64E-R . . . . . . . . . . . . . . . . . . . 118

Figure 78. CheckEHEn frame exchange between VCD and M24LR64E-R. . . . . . . . . . . . . . . . . . . . 119

Figure 79. AC test measurement I/O waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Figure 80. I

2

C AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 81. ASK modulated signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Figure 82. Energy harvesting: Vout min vs. Isink. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 83. Energy harvesting: working domain range 11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Figure 84. Energy harvesting: working domain range 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 85. Energy harvesting: working domain range 01 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 86. Energy harvesting: working domain range 00 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Figure 87. SO8N – 8-lead plastic small outline, 150 mils body width, package outline. . . . . . . . . . . 131

Figure 88. UFDFPN8 (MLP8) – 8-lead ultra thin fine pitch dual flat package no lead

2 × 3mm, package outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Figure 89. TSSOP8 – 8-lead thin shrink small outline, package outline . . . . . . . . . . . . . . . . . . . . . . 133

12/140 Doc ID 022712 Rev 3

M24LR64E-R Description

1 Description

The M24LR64E-R device is a dual-interface, electrically erasable programmable memory

(EEPROM). It features an I

also a contactless memory powered by the received carrier electromagnetic wave. The

M24LR64E-R is organized as 8192 × 8 bits in the I

15693 and ISO 18000-3 mode 1 RF mode.

The M24LR64E-R also features an energy harvesting analog output, as well as a userconfigurable digital output pin toggling during either RF write in progress or RF busy mode.

Figure 1. Logic diagram

2

C interface and can be operated from a VCC power supply. It is

2

C mode and as 2048 × 32 bits in the ISO

V

CC

SCL

Vout

SDA

AC0

M24LR64E-R

AC1

RF WIP/

#64:

V

SS

MS19740V1

2

I

C uses a two-wire serial interface, comprising a bidirectional data line and a clock line. The

devices carry a built-in 4-bit device type identifier code (1010) in accordance with the I

bus definition.

The device behaves as a slave in the I

by the serial clock. Read and Write operations are initiated by a Start condition, generated

by the bus master. The Start condition is followed by a device select code and Read/Write

bit (RW

When writing data to the memory, the device inserts an acknowledge bit during the 9

time, following the bus master’s 8-bit transmission. When data is read by the bus master, the

bus master acknowledges the receipt of the data byte in the same way. Data transfers are

terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.

In the ISO15693/ISO18000-3 mode 1 RF mode, the M24LR64E-R is accessed via the

13.56 MHz carrier electromagnetic wave on which incoming data is demodulated from the

received signal amplitude modulation (ASK: amplitude shift keying). When connected to an

antenna, the operating power is derived from the RF energy and no external power supply is

required. The received ASK wave is 10% or 100% modulated with a data rate of 1.6 Kbit/s

) (as described in Ta bl e 2 ), terminated by an acknowledge bit.

2

C protocol, with all memory operations synchronized

th

2

C

bit

Doc ID 022712 Rev 3 13/140

Description M24LR64E-R

SDAV

SS

SCL

RF WIP/BUSYAC0

Vout V

CC

MS19742V1

1

2

3

4

8

7

6

5

AC1

using the 1/256 pulse coding mode or a data rate of 26 Kbit/s using the 1/4 pulse coding

mode.

Outgoing data is generated by the M24LR64E-R load variation using Manchester coding

with one or two subcarrier frequencies at 423 kHz and 484 kHz. Data is transferred from the

M24LR64E-R at 6.6 Kbit/s in low data rate mode and 26 Kbit/s in high data rate mode. The

M24LR64E-R supports the 53 Kbit/s fast mode in high data rate mode using one subcarrier

frequency at 423 kHz.

The M24LR64E-R follows the ISO 15693 and ISO 18000-3 mode 1 recommendation for

radio-frequency power and signal interface.

The M24LR64E-R provides an Energy harvesting mode on the analog output pin Vout.

When the Energy harvesting mode is activated, the M24LR64E-R can output the excess

energy coming from the RF field on the Vout analog pin. In case the RF field strength is

insufficient or when Energy harvesting mode is disabled, the analog output pin Vout goes

into high-Z state and Energy harvesting mode is automatically stopped.

The M24LR64E-R features a user configurable digital out pin RF WIP/BUSY that can be

used to drive a microcontroller interrupt input pin (available only when the M24LR64E-R is

correctly powered on the Vcc pin).

When configured in the RF write in progress mode (RF WIP mode), the RF WIP/BUSY pin is

driven low for the entire duration of the RF internal write operation. When configured in the

RF busy mode (RF BUSY mode), the RF WIP/BUSY pin is driven low for the entire duration

of the RF command progress.

The RF WIP/BUSY pin is an open drain output and must be connected to a pull-up resistor.

Table 1. Signal names

Signal name Function Direction

Vout Energy harvesting Output Analog output

SDA Serial Data I/O

SCL Serial Clock Input

AC0, AC1 Antenna coils I/O

V

CC

RF WIP/BUSY Digital signal Digital output

V

SS

Supply voltage

Ground

Figure 2. 8-pin package connections

1. See Section 30 for package dimensions, and how to identify pin 1.

14/140 Doc ID 022712 Rev 3

M24LR64E-R Signal descriptions

2 Signal descriptions

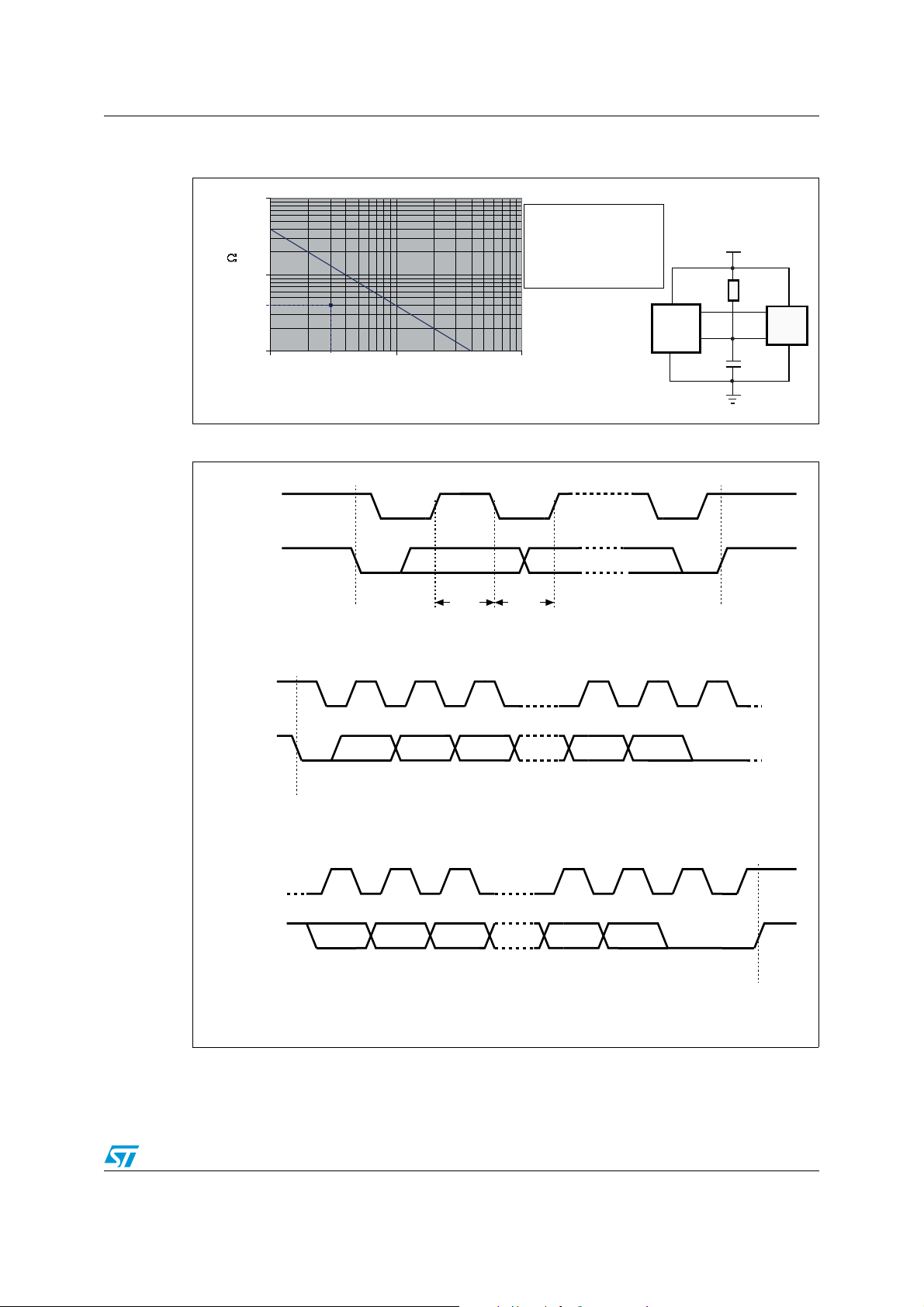

2.1 Serial clock (SCL)

This input signal is used to strobe all data in and out of the device. In applications where this

signal is used by slave devices to synchronize the bus to a slower clock, the bus master

must have an open drain output, and a pull-up resistor must be connected from Serial Clock

(SCL) to V

most applications, though, this method of synchronization is not employed, and so the pullup resistor is not necessary, provided that the bus master has a push-pull (rather than open

drain) output.

2.2 Serial data (SDA)

This bidirectional signal is used to transfer data in or out of the device. It is an open drain

output that may be wire-OR’ed with other open drain or open collector signals on the bus. A

pull-up resistor must be connected from Serial Data (SDA) to V

the value of the pull-up resistor can be calculated).

. (Figure 3 indicates how the value of the pull-up resistor can be calculated). In

CC

. (Figure 3 indicates how

CC

2.3 RF Write in progress / RF Busy (RF WIP/BUSY)

This configurable output signal is used either to indicate that the M24LR64E-R is executing

an internal write cycle from the RF channel or that an RF command is in progress. RF WIP

and signals are available only when the M24LR64E-R is powered by the Vcc pin. It is an

open drain output and a pull-up resistor must be connected from RF WIP/BUSY to V

2.4 Energy harvesting analog output (Vout)

This analog output pin is used to deliver the analog voltage Vout available when the Energy

harvesting mode is enabled and the RF field strength is sufficient. When the Energy

harvesting mode is disabled or the RF field strength is not sufficient, the energy harvesting

analog voltage output Vout is in High-Z state.

2.5 Antenna coil (AC0, AC1)

These inputs are used to connect the device to an external coil exclusively. It is advised not

to connect any other DC or AC path to AC0 or AC1.

When correctly tuned, the coil is used to power and access the device using the ISO 15693

and ISO 18000-3 mode 1 protocols.

2.5.1 Device reset in RF mode

CC

.

To ensure a proper reset of the RF circuitry, the RF field must be turned off (100%

modulation) for a minimum t

RF_OFF

period of time.

Doc ID 022712 Rev 3 15/140

Signal descriptions M24LR64E-R

2.6 VSS ground

VSS is the reference for the VCC supply voltage and Vout analog output voltage.

2.7 Supply voltage (VCC)

This pin can be connected to an external DC supply voltage.

Note: An internal voltage regulator allows the external voltage applied on V

M24LR64E-R, while preventing the internal power supply (rectified RF waveforms) to output

a DC voltage on the V

2.7.1 Operating supply voltage V

CC

pin.

CC

Prior to selecting the memory and issuing instructions to it, a valid and stable VCC voltage

within the specified [V

(min), VCC(max)] range must be applied (see Tab l e 1 19 ). To

CC

maintain a stable DC supply voltage, it is recommended to decouple the V

suitable capacitor (usually around 10 nF) close to the V

CC/VSS

package pins.

This voltage must remain stable and valid until the end of the transmission of the instruction

and, for a Write instruction, until the completion of the internal I²C write cycle (t

2.7.2 Power-up conditions

When the power supply is turned on, VCC rises from VSS to VCC. The VCC rise time must not

vary faster than 1V/µs.

2.7.3 Device reset in I²C mode

In order to prevent inadvertent write operations during power-up, a power-on reset (POR)

circuit is included. At power-up (continuous rise of V

I²C instruction until V

lower than the minimum V

has reached the power-on reset threshold voltage (this threshold is

CC

operating voltage defined in Ta bl e 1 19 ). When VCC passes

CC

over the POR threshold, the device is reset and enters the Standby power mode. However,

the device must not be accessed until V

within the specified [V

(min), VCC(max)] range.

CC

has reached a valid and stable VCC voltage

CC

In a similar way, during power-down (continuous decrease in V

below the power-on reset threshold voltage, the device stops responding to any instruction

sent to it.

), the device does not respond to any

CC

), as soon as VCC drops

CC

to supply the

CC

line with a

CC

).

W

2.7.4 Power-down conditions

During power-down (continuous decay of VCC), the device must be in Standby power mode

(mode reached after decoding a Stop condition, assuming that there is no internal write

cycle in progress).

16/140 Doc ID 022712 Rev 3

M24LR64E-R Signal descriptions

1

10

100

10 100 1000

Bus line capacitor (pF)

Bus line pull-up resistor

(k

)

When t

LOW

= 1.3 µs (min value for

f

C

= 400 kHz), the R

bus

× C

bus

time constant must be below the

400 ns time constant line

represented on the left.

I²C bus

master

M24xxx

R

bus

V

CC

C

bus

SCL

SDA

ai14796b

R

bus

× C

bus

= 400 ns

Here R

bus

× C

bus

= 120 ns

4 kΩ

30 pF

SCL

SDA

SCL

SDA

SDA

Start

Condition

SDA

Input

SDA

Change

AI00792B

Stop

Condition

1 23 7 89

MSB

ACK

Start

Condition

SCL

1 23 7 89

MSB ACK

Stop

Condition

Figure 3. I2C Fast mode (fC = 400 kHz): maximum R

Figure 4. I

capacitance (C

2

C bus protocol

bus

)

value versus bus parasitic

bus

Doc ID 022712 Rev 3 17/140

Signal descriptions M24LR64E-R

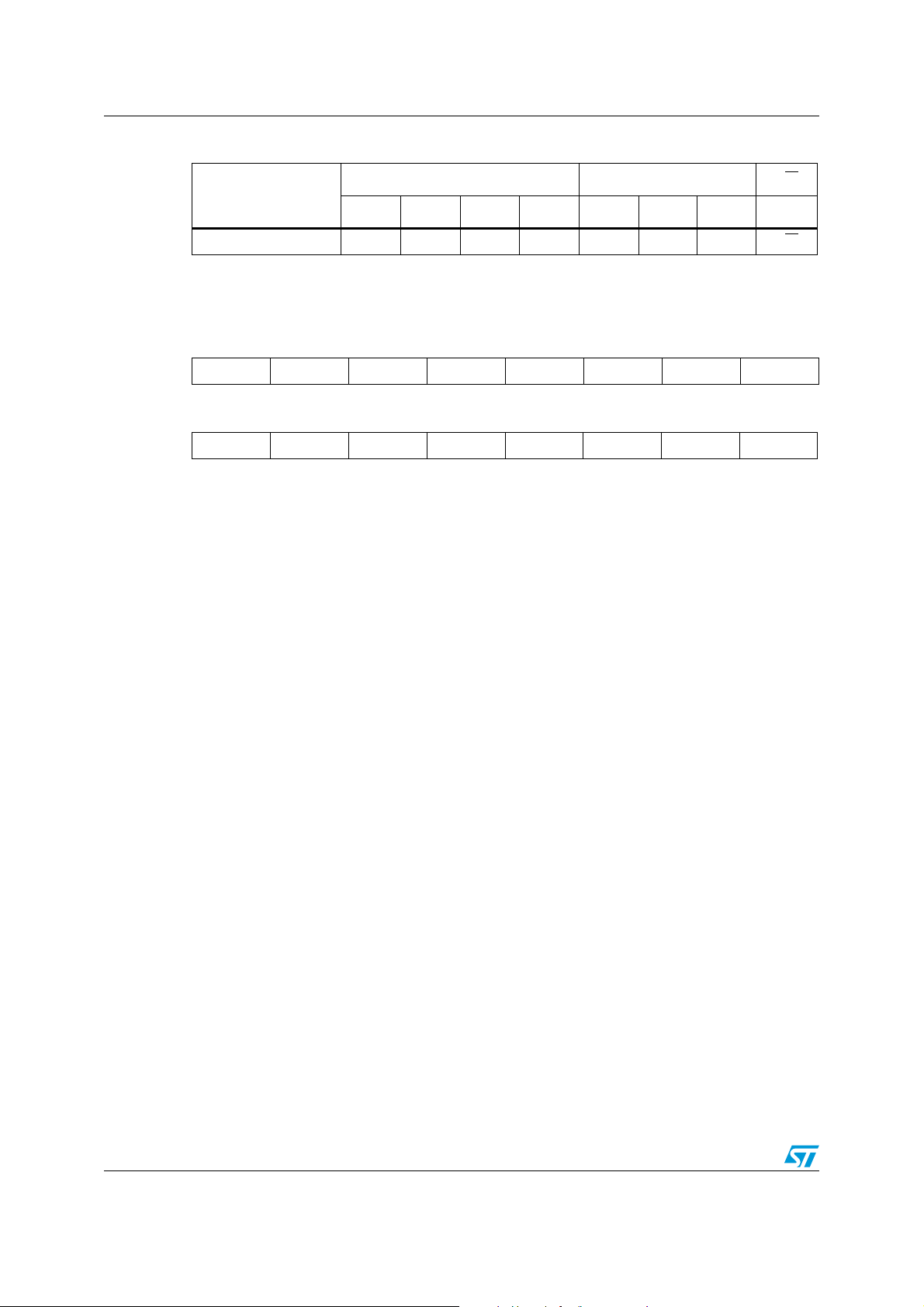

Table 2. Device select code

Device type identifier

b7 b6 b5 b4 b3 b2 b1 b0

Device select code1010E2

1. The most significant bit, b7, is sent first.

2. E2 is not connected to any external pin. It is however used to address the M24LR64E-R as described in

Section 3 and Section 4.

Table 3. Address most significant byte

b15 b14 b13 b12 b11 b10 b9 b8

Table 4. Address least significant byte

b7 b6 b5 b4 b3 b2 b1 b0

(1)

Chip Enable address RW

(2)

11RW

18/140 Doc ID 022712 Rev 3

M24LR64E-R User memory organization

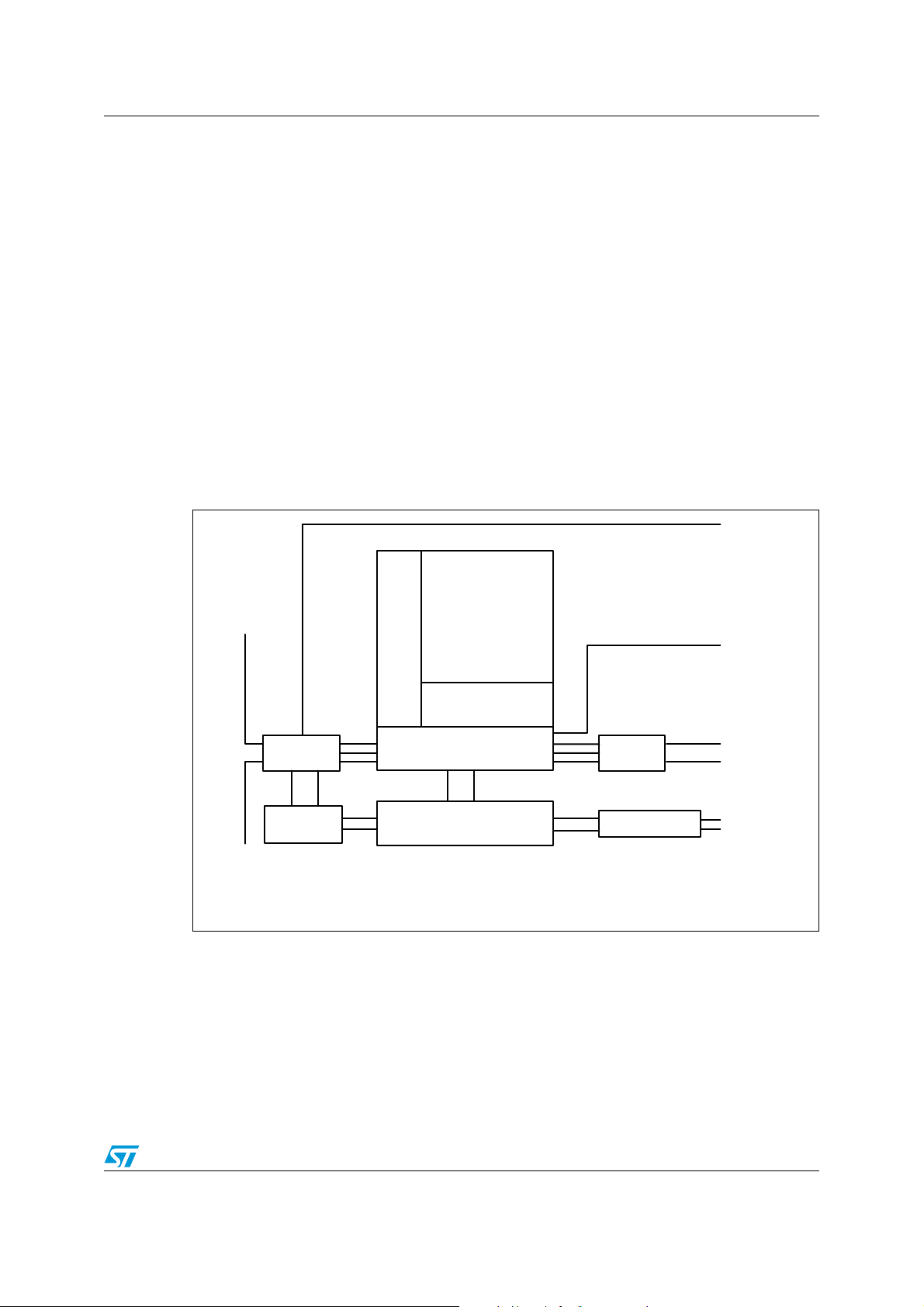

MS19780V1

RF V

CC

AC0

AC1

RF

Power management

Vout

RF WIP/BUSY

Logic

EEPROM

Latch

I

2

C

Contact V

CC

SCL

SDA

V

CC

V

SS

Row decoder

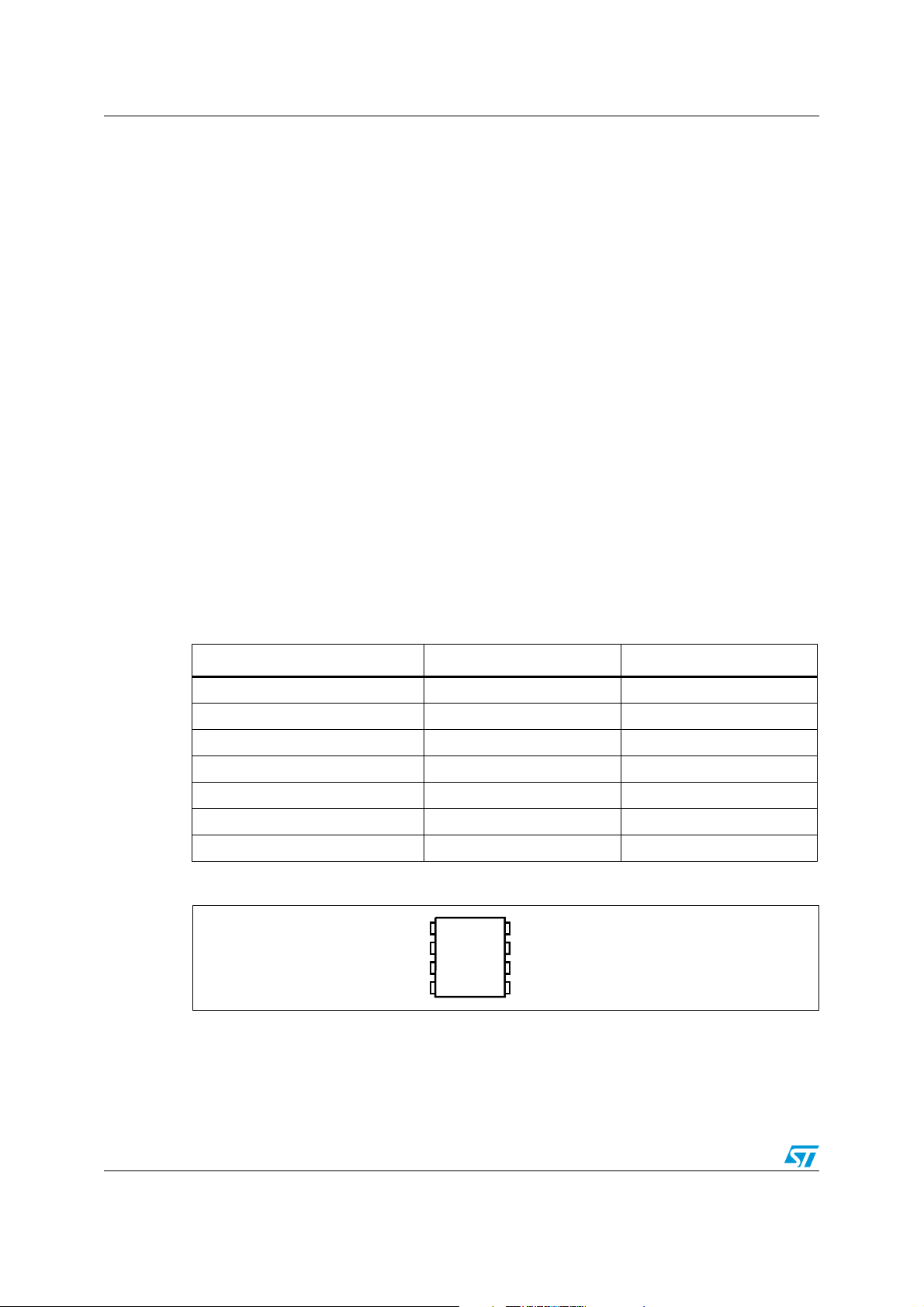

3 User memory organization

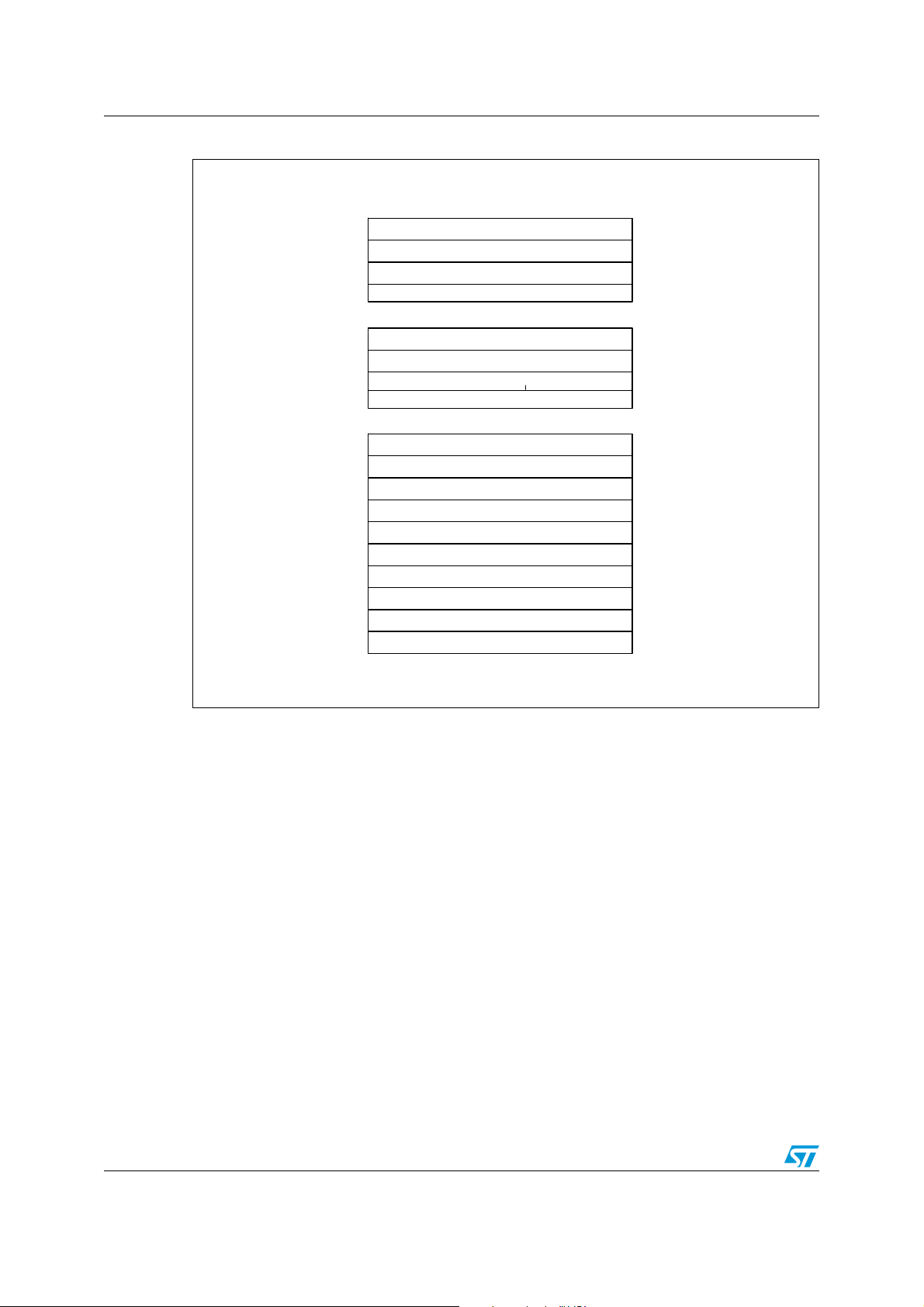

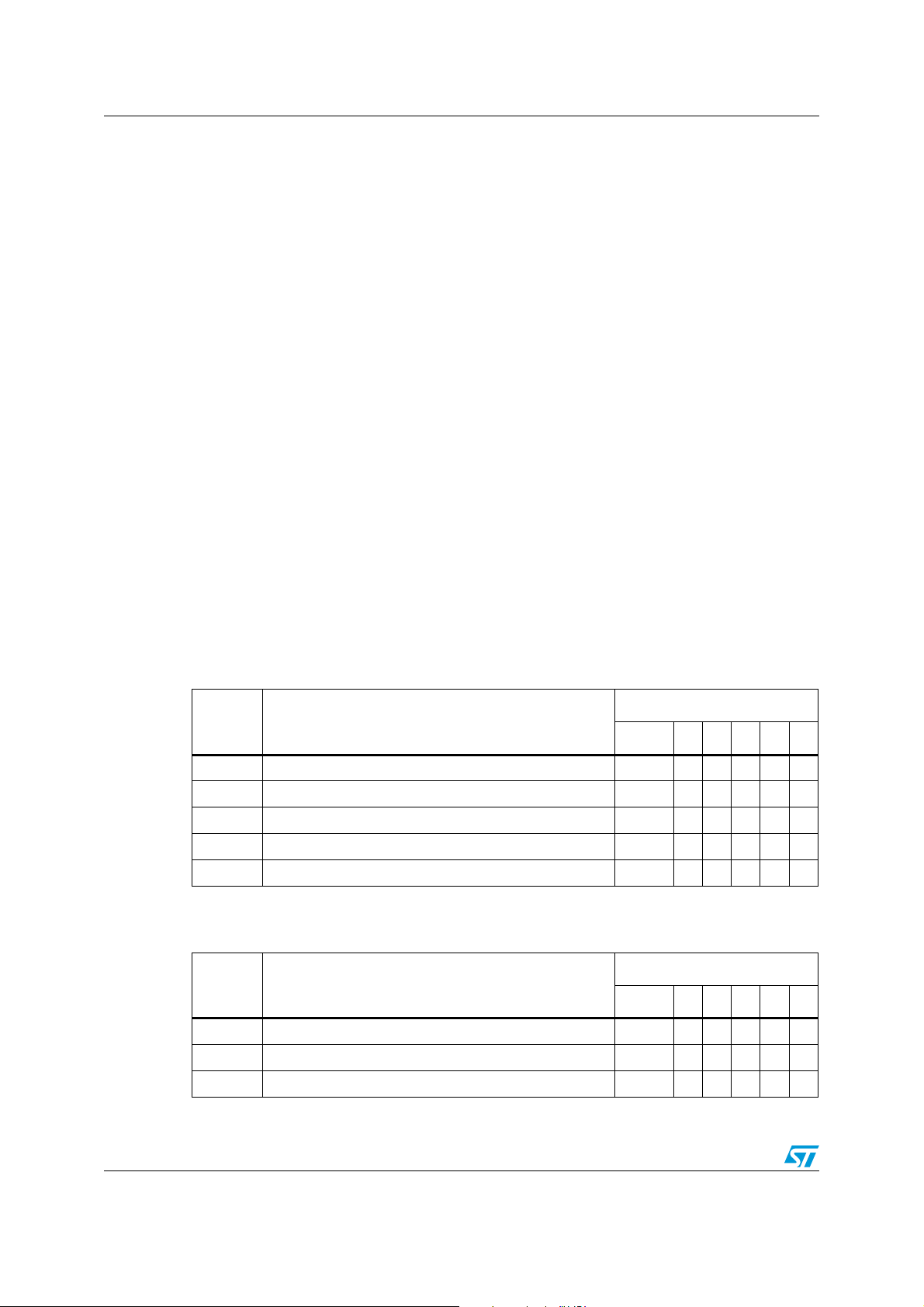

The M24LR64E-R is divided into 16 sectors of 32 blocks of 32 bits, as shown in Ta bl e 5 .

Figure 6 shows the memory sector organization. Each sector can be individually read-

and/or write-protected using a specific password command. Read and write operations are

possible if the addressed data is not in a protected sector.

The M24LR64E-R also has a 64-bit block that is used to store the 64-bit unique identifier

(UID). The UID is compliant with the ISO 15963 description, and its value is used during the

anticollision sequence (Inventory). This block is not accessible by the user and its value is

written by ST on the production line.

The M24LR64E-R includes an AFI register that stores the application family identifier, and a

DSFID register that stores the data storage family identifier used in the anticollision

algorithm.

The M24LR64E-R has four 32-bit blocks that store an I

codes.

Figure 5. Circuit diagram

2

C password plus three RF password

Doc ID 022712 Rev 3 19/140

User memory organization M24LR64E-R

MS19741V1

1 Kbit EEPROM sector

1 Kbit EEPROM sector

1 Kbit EEPROM sector

1 Kbit EEPROM sector

Sector

Area

Sector security

status

1 Kbit EEPROM sector

1 Kbit EEPROM sector

1 Kbit EEPROM sector

1 Kbit EEPROM sector

I²C password

RF password 1

RF password 2

RF password 3

8-bit DSFID

8-bit AFI

8-bit configuration

16-bit I²C Write Lock_bit

64-bit UID

0

1

2

3

12

13

14

15

5 bits

5 bits

5 bits

5 bits

5 bits

5 bits

5 bits

5 bits

System

System

System

System

System

System

System

System

80-bit SSS

System

Figure 6. Memory sector organization

Sector details

The M24LR64E-R user memory is divided into 16 sectors. Each sector contains 1024 bits.

20/140 Doc ID 022712 Rev 3

The protection scheme is described in Section 4: System memory area.

In RF mode, a sector provides 32 blocks of 32 bits. Each read and write access is done by

block. Read and write block accesses are controlled by a Sector Security Status byte that

defines the access rights to the 32 blocks contained in the sector. If the sector is not

protected, a Write command updates the complete 32 bits of the selected block.

2

In I

C mode, a sector provides 128 bytes that can be individually accessed in Read and

Write modes. When protected by the corresponding I2C_Write_Lock bit, the entire sector is

write-protected. To access the user memory, the device select code used for any I

command must have the E2 Chip Enable address at 0.

2

C

M24LR64E-R User memory organization

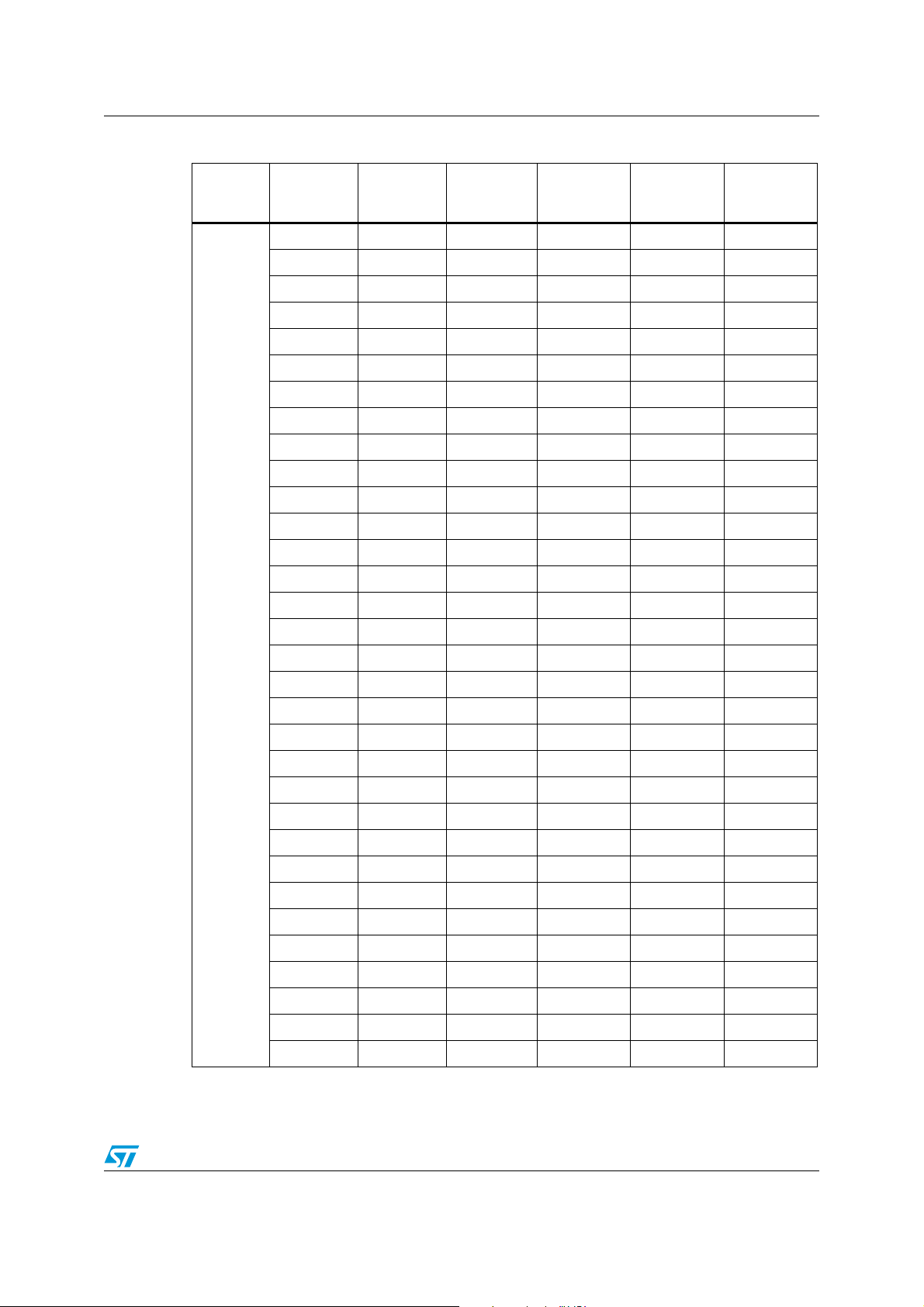

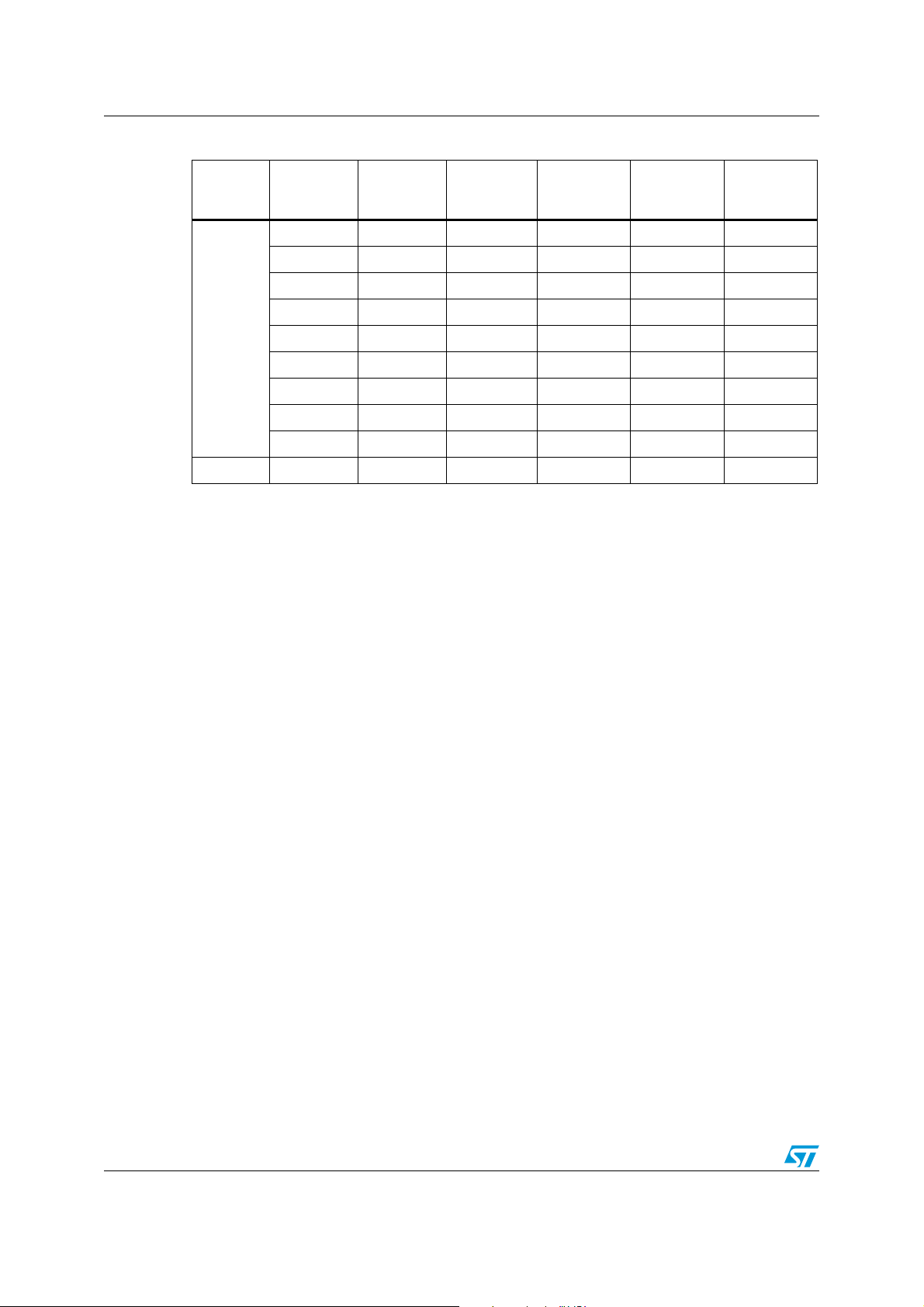

Table 5. Sector details

Sector

number

0

RF block

address

I2C byte

address

Bits [31:24] Bits [23:16] Bits [15:8] Bits [7:0]

0 0 user user user user

1 4 user user user user

2 8 user user user user

3 12 user user user user

4 16 user user user user

5 20 user user user user

6 24 user user user user

7 28 user user user user

8 32 user user user user

9 36 user user user user

10 40 user user user user

11 44 user user user user

12 48 user user user user

13 52 user user user user

14 56 user user user user

15 60 user user user user

16 64 user user user user

17 68 user user user user

18 72 user user user user

19 76 user user user user

20 80 user user user user

21 84 user user user user

22 88 user user user user

23 92 user user user user

24 96 user user user user

25 100 user user user user

26 104 user user user user

27 108 user user user user

28 112 user user user user

29 116 user user user user

30 120 user user user user

31 124 user user user user

Doc ID 022712 Rev 3 21/140

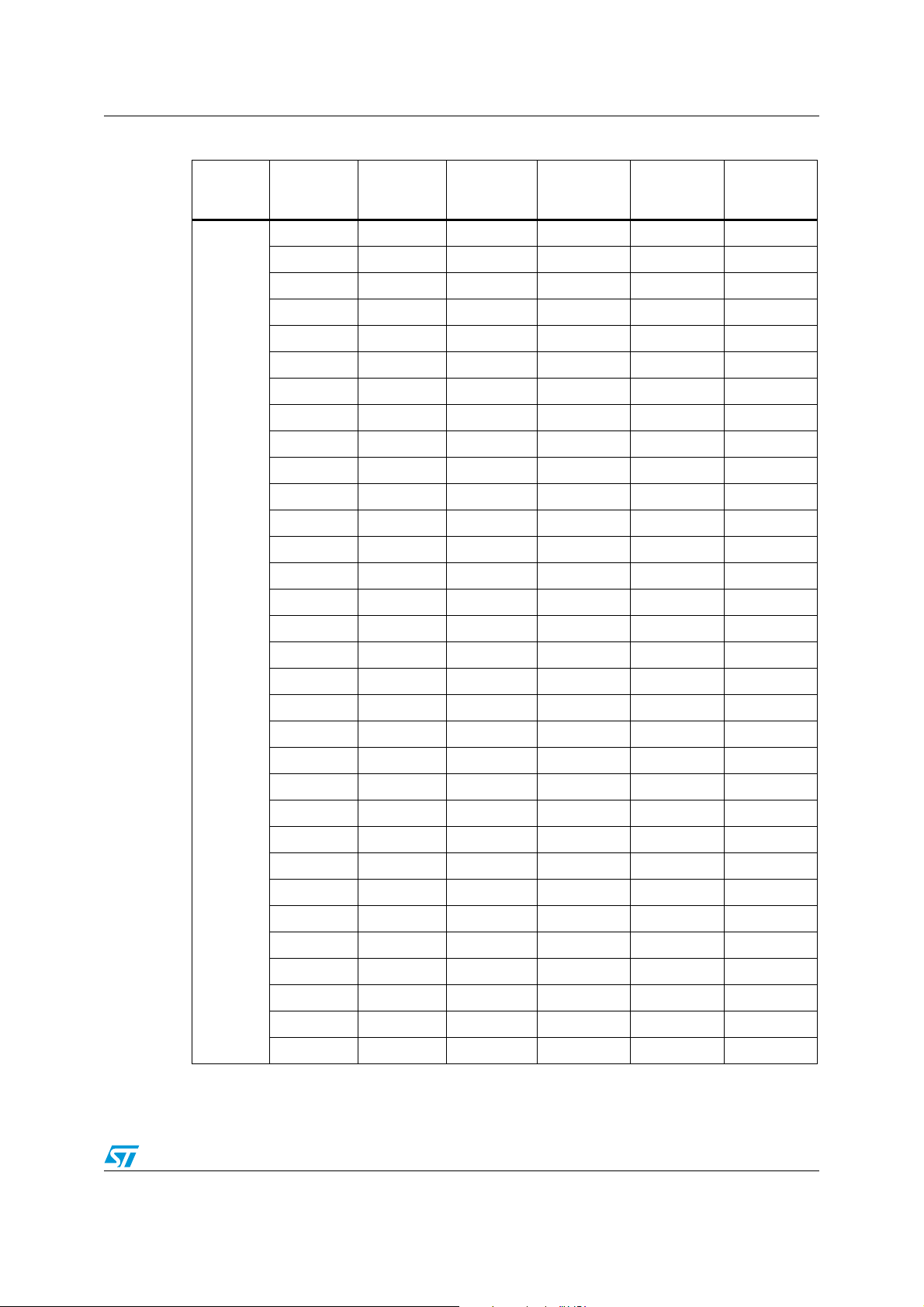

User memory organization M24LR64E-R

Table 5. Sector details (continued)

Sector

number

1

... ... ... ... ... ... ...

RF block

address

32 128 user user user user

33 132 user user user user

34 136 user user user user

35 140 user user user user

36 144 user user user user

37 148 user user user user

38 152 user user user user

39 156 user user user user

... ... ... ... ... ...

I2C byte

address

Bits [31:24] Bits [23:16] Bits [15:8] Bits [7:0]

22/140 Doc ID 022712 Rev 3

M24LR64E-R User memory organization

Table 5. Sector details (continued)

Sector

number

63

RF block

address

2016 8064 user user user user

2017 8068 user user user user

2018 8072 user user user user

2019 8076 user user user user

2020 8080 user user user user

2021 8084 user user user user

2022 8088 user user user user

2023 8092 user user user user

2024 8096 user user user user

2025 8100 user user user user

2026 8104 user user user user

2027 8108 user user user user

2028 8112 user user user user

2029 8116 user user user user

2030 8120 user user user user

2031 8124 user user user user

2032 8128 user user user user

I2C byte

address

Bits [31:24] Bits [23:16] Bits [15:8] Bits [7:0]

2033 8132 user user user user

2034 8136 user user user user

2035 8140 user user user user

2036 8144 user user user user

2037 8148 user user user user

2038 8152 user user user user

2039 8156 user user user user

2040 8160 user user user user

2041 8164 user user user user

2042 8168 user user user user

2043 8172 user user user user

2044 8176 user user user user

2045 8180 user user user user

2046 8184 user user user user

2047 8188 user user user user

Doc ID 022712 Rev 3 23/140

System memory area M24LR64E-R

4 System memory area

4.1 M24LR64E-R block security in RF mode

The M24LR64E-R provides a special protection mechanism based on passwords. In RF

mode, each memory sector of the M24LR64E-R can be individually protected by one out of

three available passwords, and each sector can also have Read/Write access conditions

set.

Each memory sector of the M24LR64E-R is assigned with a Sector security status byte

including a Sector Lock bit, two Password Control bits and two Read/Write protection bits,

as shown in Ta bl e 7 .

Ta bl e 6 describes the organization of the Sector security status byte, which can be read

using the Read Single Block and Read Multiple Block commands with the Option_flag set

to 1.

On delivery, the default value of the SSS bytes is set to 00h.

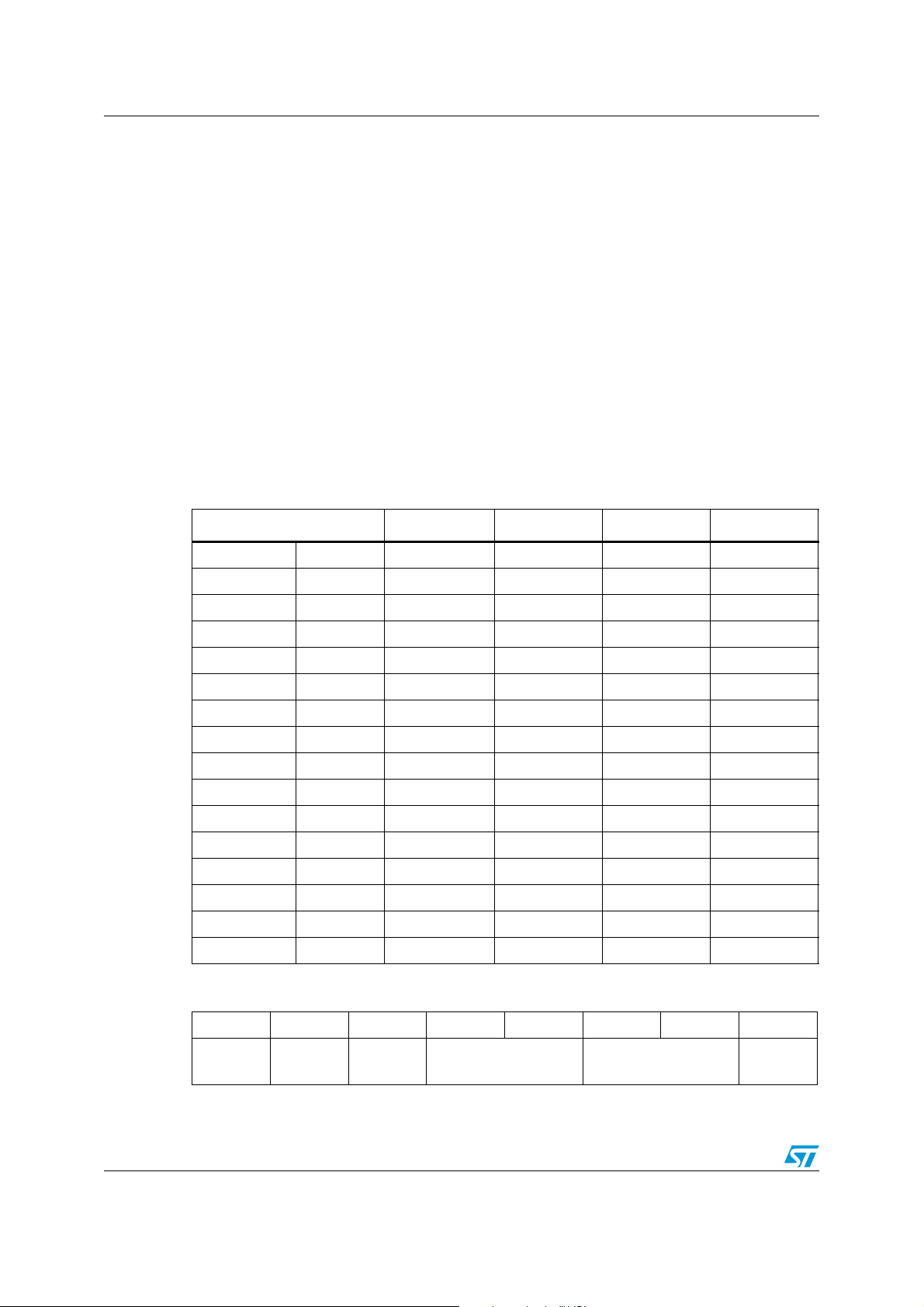

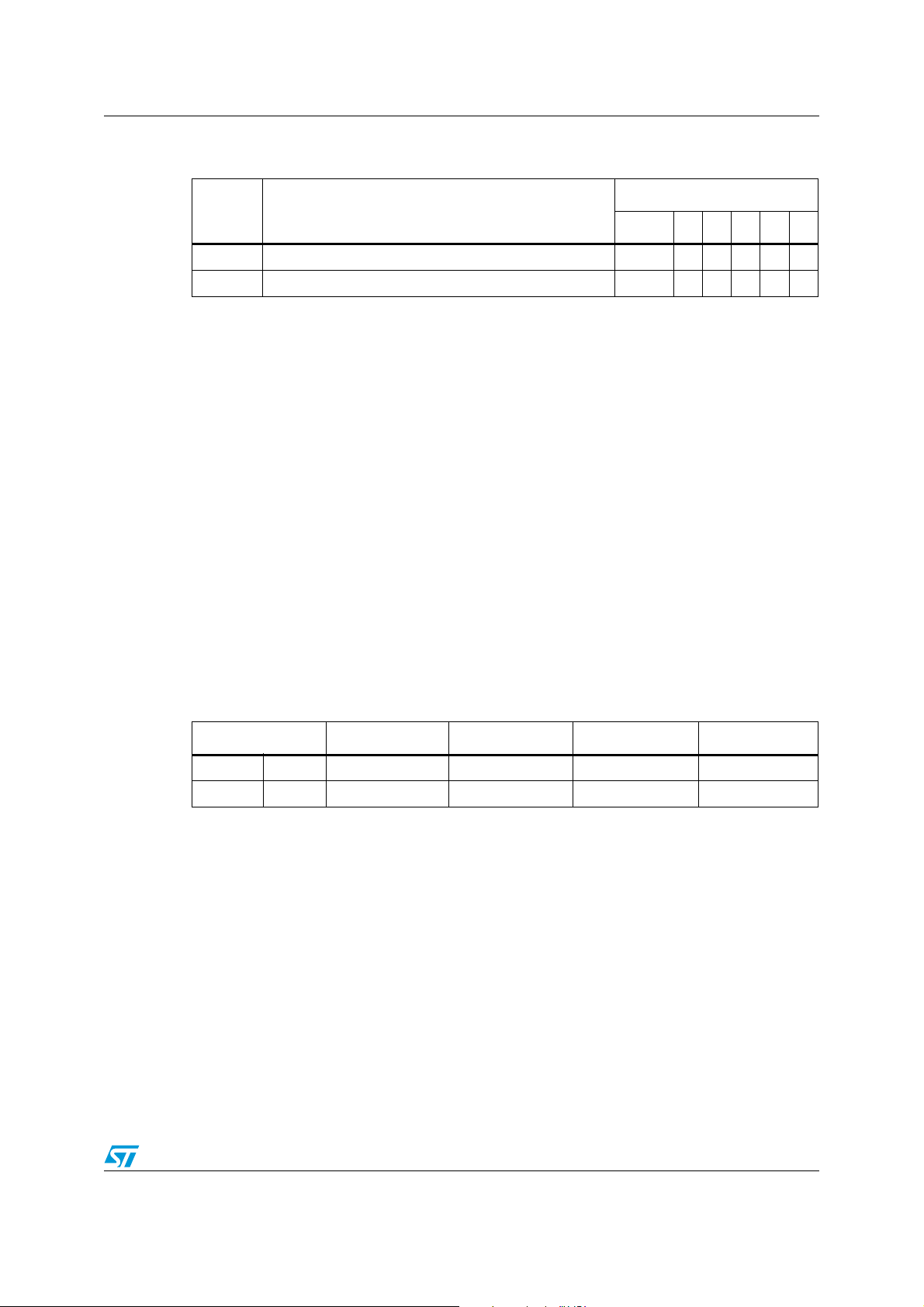

Table 6. Sector security status byte area

I2C byte address Bits [31:24] Bits [23:16] Bits [15:8] Bits [7:0]

E2 = 1 0 SSS 3 SSS 2 SSS 1 SSS 0

E2 = 1 4 SSS 7 SSS 6 SSS 5 SSS 4

E2 = 1 8 SSS 11 SSS 10 SSS 9 SSS 8

E2 = 1 12 SSS 15 SSS 14 SSS 13 SSS 12

E2 = 1 16 SSS 19 SSS 18 SSS 17 SSS 16

E2 = 1 20 SSS 23 SSS 22 SSS 21 SSS 20

E2 = 1 24 SSS 27 SSS 26 SSS 25 SSS 24

E2 = 1 28 SSS 31 SSS 30 SSS 29 SSS 28

E2 = 1 32 SSS 35 SSS 34 SSS 33 SSS 32

E2 = 1 36 SSS 39 SSS 38 SSS 37 SSS 36

E2 = 1 40 SSS 43 SSS 42 SSS 41 SSS 40

E2 = 1 44 SSS 47 SSS 46 SSS 45 SSS 44

E2 = 1 48 SSS 51 SSS 50 SSS 49 SSS 48

E2 = 1 52 SSS 55 SSS 54 SSS 53 SSS 52

E2 = 1 56 SSS 59 SSS 58 SSS 57 SSS 56

E2 = 1 60 SSS 63 SSS 62 SSS 61 SSS 60

Table 7. Sector security status byte organization

b

7

0 0 0 Password control bits

b

6

b

5

b

4

b

3

b

2

b

1

Read / Write

protection bits

b

0

Sector

Lock

24/140 Doc ID 022712 Rev 3

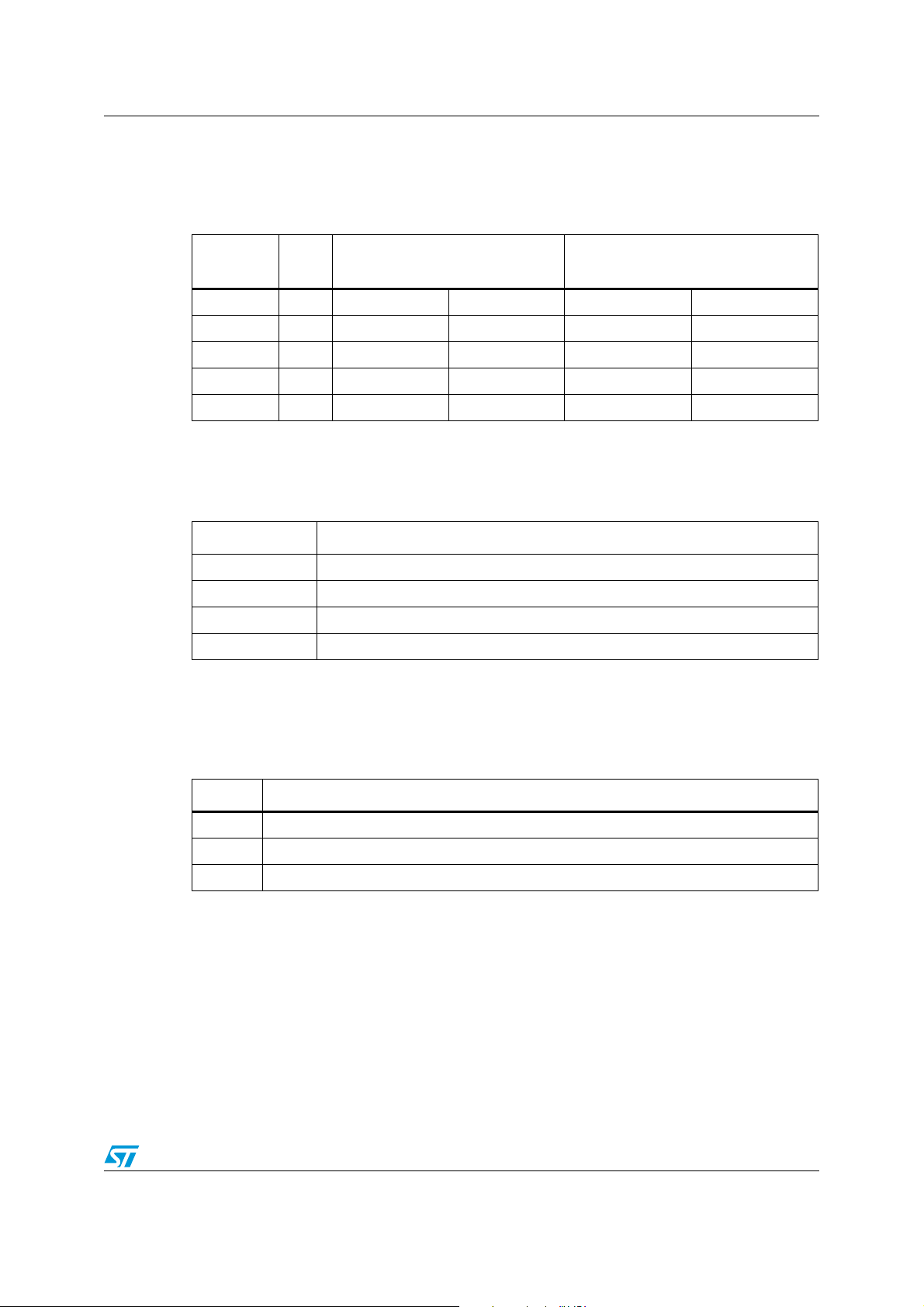

M24LR64E-R System memory area

When the Sector Lock bit is set to 1, for instance by issuing a Lock-sector command, the two

Read/Write protection bits (b

, b2) are used to set the Read/Write access of the sector as

1

described in Ta b le 8 .

Table 8. Read/Write protection bit setting

Sector

Lock

, b

b

2

1

Sector access

when password presented

when password not presented

Sector access

0 xx Read Write Read Write

1 00 Read Write Read No Write

1 01 Read Write Read Write

1 10 Read Write No Read No Write

1 11 Read No Write No Read No Write

The next two bits of the Sector security status byte (b3, b4) are the password control bits.

The value of these two bits is used to link a password to the sector, as defined in Ta bl e 9 .

Table 9. Password control bits

b4, b

3

Password

00 The sector is not protected by a password.

01 The sector is protected by password 1.

10 The sector is protected by password 2.

11 The sector is protected by password 3.

The M24LR64E-R password protection is organized around a dedicated set of commands,

plus a system area of three password blocks where the password values are stored. This

system area is described in Ta bl e 1 0.

Table 10. Password system area

Add

1 Password 1

2 Password 2

3 Password 3

The dedicated commands for protection in RF mode are:

● Write-sector password:

The Write-sector password command is used to write a 32-bit block into the password

system area. This command must be used to update password values. After the write

cycle, the new password value is automatically activated. It is possible to modify a

password value after issuing a valid Present-sector password command. On delivery,

the three default password values are set to 0000 0000h and are activated.

● Lock-sector:

The Lock-sector command is used to set the sector security status byte of the selected

sector. Bits b

to b1 of the sector security status byte are affected by the Lock-sector

4

Doc ID 022712 Rev 3 25/140

System memory area M24LR64E-R

command. The sector lock bit, b0, is set to 1 automatically. After issuing a Lock-sector

command, the protection settings of the selected sector are activated. The protection of

a locked block cannot be changed in RF mode. A Lock-sector command sent to a

locked sector returns an error code.

● Present-sector password:

The Present-sector password command is used to present one of the three passwords

to the M24LR64E-R in order to modify the access rights of all the memory sectors

linked to that password (Ta b le 8 ) including the password itself. If the presented

password is correct, the access rights remain activated until the tag is powered off or

until a new Present-sector password command is issued. If the presented password

value is not correct, all the access rights of all the memory sectors are deactivated.

● Sector security status byte area access conditions in I

2

In I

C mode, read access to the sector security status byte area is always allowed.

Write access depends on the correct presentation of the I

2

C mode:

2

C password (see

Section 5.16.1: I2C present password command description).

To access the Sector security status byte area, the device select code used for any I

2

C

command must have the E2 Chip Enable address at 1.

2

An I

C write access to a sector security status byte re-initializes the RF access

condition to the given memory sector.

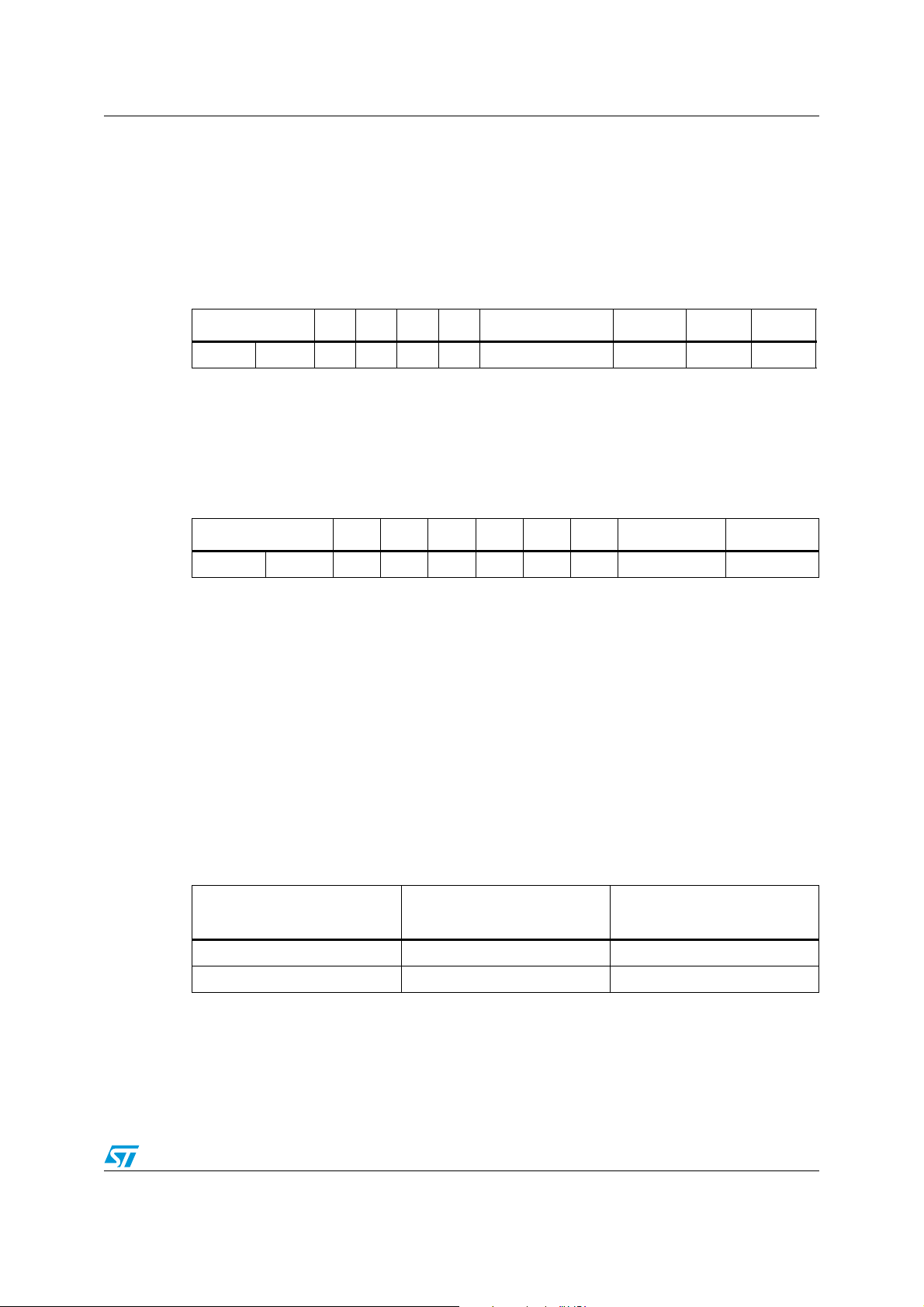

4.1.1 Example of the M24LR64E-R security protection in RF mode

Ta bl e 1 1 and Ta bl e 1 2 show the sector security protections before and after a valid Present-

sector password command. Tab le 1 1 shows the sector access rights of an M24LR64E-R

after power-up. After a valid Present-sector password command with password 1, the

memory sector access is changed as shown in Ta bl e 1 2.

Table 11. M24LR64E-R sector security protection after power-up

Sector

address

0 Protection: standard Read No Write xxx 00001

1 Protection: pswd 1 Read No Write xxx 01001

2 Protection: pswd 1 Read Write xxx 01011

3 Protection: pswd 1 No Read No Write xxx 01101

4 Protection: pswd 1 No Read No Write xxx 01111

Table 12. M24LR64E-R sector security protection after a valid presentation of

password 1

Sector

address

0 Protection: standard Read No Write xxx 00001

Sector security status byte

b

7b6b5b4b3b2b1b0

Sector security status byte

b7b6b5b4b3b2b1b

0

1 Protection: pswd 1 Read Write xxx 01001

2 Protection: pswd 1 Read Write xxx 01011

26/140 Doc ID 022712 Rev 3

M24LR64E-R System memory area

Table 12. M24LR64E-R sector security protection after a valid presentation of

password 1

Sector

address

3 Protection: pswd 1 Read Write xxx 01101

4 Protection: pswd 1 Read No Write xxx 01111

Sector security status byte

b7b6b5b4b3b2b1b

0

4.2 M24LR64E-R block security in I²C mode (I2C_Write_Lock bit area)

In the I2C mode only, it is possible to protect individual sectors against Write operations.

This feature is controlled by the I2C_Write_Lock bits stored in the 2 bytes of the

I2C_Write_Lock bit area. I2C_Write_Lock bit area starts from location 8192 (see Ta bl e 1 3 ).

To access the I2C_Write_Lock bit area, the device select code used for any I

must have the E2 Chip Enable address at 1.

Using these 16 bits, it is possible to write-protect all the 16 sectors of the M24LR64E-R

memory. Each bit controls the I

is always possible to unprotect a sector in the I

2

C write access to a specific sector as shown in Ta bl e 1 3 . It

2

C mode. When an I2C_Write_Lock bit is

reset to 0, the corresponding sector is unprotected. When the bit is set to 1, the

corresponding sector is write-protected.

2

In I

C mode, read access to the I2C_Write_Lock bit area is always allowed. Write access

depends on the correct presentation of the I

2

C password.

2

C command

On delivery, the default value of the eight bytes of the I2C_Write_Lock bit area is reset to

00h.

m

Table 13. I2C_Write_Lock bit

I2C byte address Bits [31:24] Bits [23:16] Bits [15:8] Bits [7:0]

E2 = 1 2048 sectors 31-24 sectors 23-16 sectors 15-8 sectors 7-0

E2 = 1 2052 sectors 63-56 sectors 55-48 sectors 47-40 sectors 39-32

4.3 Configuration byte and Control register

The M24LR64E-R offers an 8-bit non-volatile Configuration byte located at I²C location 2320

of the system area used to store the RF WIP/BUSY pin and the energy harvesting

configuration (see Ta b le 1 4 ).

The M24LR64E-R also offers an 8-bit volatile Control register located at I²C location 2336 of

the system area used to store the energy harvesting enable bit as well as a FIELD_ON bit

indicator (see Tab le 1 5 ).

Doc ID 022712 Rev 3 27/140

System memory area M24LR64E-R

4.3.1 RF WIP/BUSY pin configuration

The M24LR64E-R features a configurable open drain output RF WIP/BUSY pin used to

provide RF activity information to an external device.

The RF WIP/BUSY pin functionality depends on the value of bit 3 of the Configuration byte.

● RF busy mode

When bit 3 of the Configuration byte is set to 0, the RF WIP/BUSY pin is configured in RF

busy mode.

The purpose of this mode is to indicate to the I²C bus master whether the M24LR64E-R is

busy in RF mode or not.

In this mode, the RF WIP/BUSY pin is tied to 0 from the RF command Start Of Frame (SOF)

until the end of the command execution.

If a bad RF command is received, the RF WIP/BUSY pin is tied to 0 from the RF command

SOF until the reception of the RF command CRC. Otherwise, the RF WIP/BUSY pin is in

high-Z state.

When tied to 0, the RF WIP/BUSY signal returns to High-Z state if the RF field is cut-off.

During the execution of I²C commands, the RF WIP/BUSY pin remains in high-Z state.

● RF Write in progress

When bit 3 of the Configuration byte is set to 1, the RF WIP/BUSY pin is configured in RF

Write in progress mode.

The purpose of this mode is to indicate to the I²C bus master that some data has been

changed in RF mode.

In this mode, the RF WIP/BUSY pin is tied to 0 for the duration of an internal write operation

(i.e. between the end of a valid RF write command and the beginning of the RF answer).

During the execution of I²C write operations, the RF WIP/BUSY pin remains in high-Z state.

4.3.2 Energy harvesting configuration