LD39100XX12, LD39100XX25

1 A, low quiescent current, low noise voltage regulator

Features

■ Input voltage from 1.5 to 5.5 V

■ Ultra low dropout voltage (200 mV typ. at 1 A

load)

■ Very low quiescent current (20 µA typ. at no

load, 200 µA typ. at 1 A load, 1 µA max in off

mode)

■ Very low noise with no bypass capacitor

(30 µV

■ Output voltage tolerance: ± 2.0 % @ 25 °C

■ 1 A guaranteed output current

■ Wide range of output voltages available on

request: 0.8 V to 4.5 V with 100 mV step and

adjustable from 0.8 V

■ Logic-controlled electronic shutdown

■ Stabilized with ceramic capacitors C

■ Internal current and thermal limit

■ DFN6 (3 x 3 mm) package

■ Temperature range: - 40 °C to 125 °C

Applications

■ Printers

■ Personal digital assistants (PDAs)

■ Cordless phones

■ Consumer applications

RMS

at V

OUT

= 0.8 V)

OUT

= 1 µF

LD39100XX

DFN6 (3 x 3 mm)

with a typical dropout voltage of 200 mV. The

device is stable due to the use of ceramic

capacitors on the input and output. The ultra low

drop-voltage, low quiescent current and low noise

features make it suitable for low power battery

powered applications. Power supply rejection is

65 dB at low frequencies and starts to roll off at 10

kHz. An enable logic control function puts the

LD39100xx in shutdown mode, allowing a total

current consumption lower than 1 µA. The device

also includes short-circuit constant current limiting

and thermal protection.

Description

The LD39100xx provides 1 A maximum current

from an input voltage ranging from 1.5 V to 5.5 V

Table 1. Device summary

October 2011 Doc ID 15676 Rev 3 1/23

Part numbers Order codes Output voltages

LD39100XX LD39100PUR Adj. from 0.8 V

LD39100XX12 LD39100PU12R 1.2 V

LD39100XX25 LD39100PU25R 2.5 V

www.st.com

23

Contents LD39100XX, LD39100XX12, LD39100XX25

Contents

1 Circuit schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

5 Typical performance characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

6 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

6.1 Power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

6.2 Enable function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

6.3 Power Good function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

7 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

8 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2/23 Doc ID 15676 Rev 3

LD39100XX, LD39100XX12, LD39100XX25 Circuit schematics

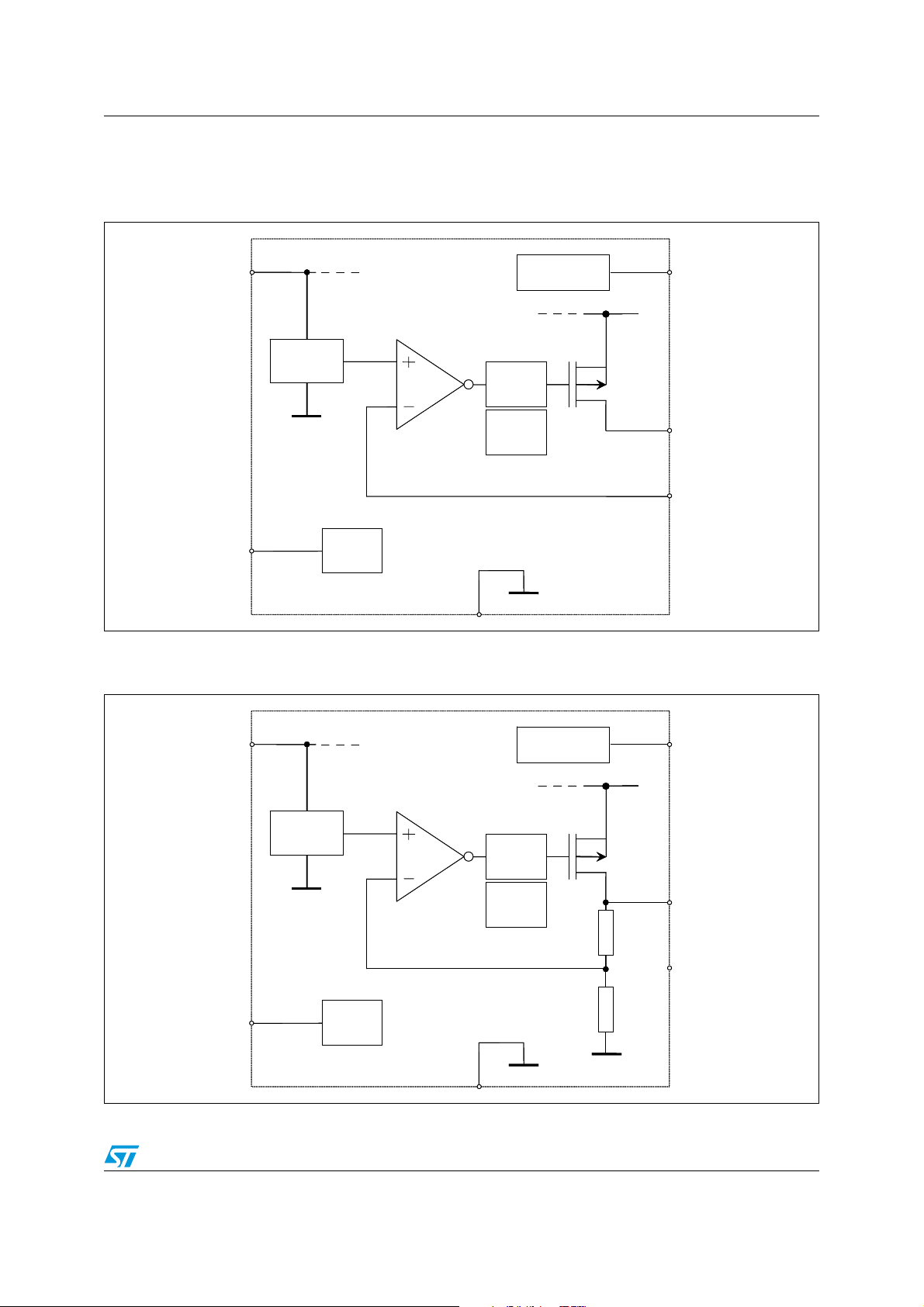

1 Circuit schematics

Figure 1. Schematic diagram for the LD39100PU

IN

IN

BandGap

BandGap

reference

reference

OpAmp

OpAmp

EN

EN

Figure 2. Schematic diagram for the LD39100PUxx

Internal

Internal

enable

enable

GND

GND

Power-good

Power-good

Current

Current

limit

limit

Thermal

Thermal

protection

protection

signal

signal

PG

PG

IN

ININ

OUT

OUT

ADJ

ADJ

IN

IN

BandGap

BandGap

reference

reference

OpAmp

OpAmp

EN

EN

Internal

Internal

enable

enable

GND

GND

Power-good

Power-good

Current

Current

limit

limit

Thermal

Thermal

protection

protection

signal

signal

PG

PG

IN

ININ

OUT

OUT

R

R

1

1

NC

NC

R

R

2

2

Doc ID 15676 Rev 3 3/23

Pin configuration LD39100XX, LD39100XX12, LD39100XX25

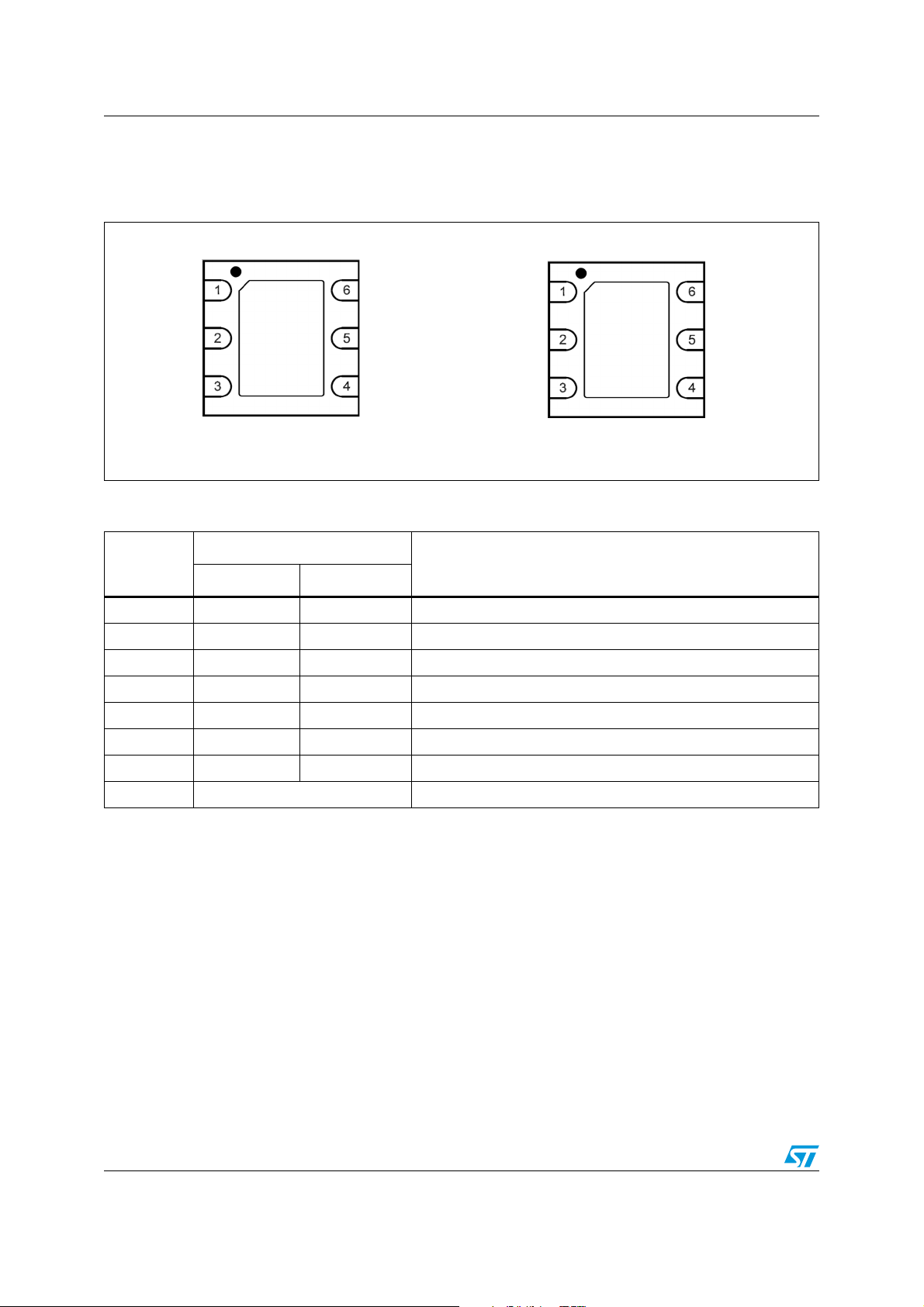

2 Pin configuration

Figure 3. Pin connection (top view)

EN

GND

PG

LD39100PUxx

V

NC

V

IN

OUT

EN

GND

PG

LD39100PU

Table 2. Pin description

Pin n°

Symbol

LD39100PU LD39100PUxx

EN 1 1 Enable pin logic input: Low = shutdown, High = active

GND 2 2 Common ground

PG 3 3 Power Good

V

OUT

4 4 Output voltage

ADJ 5 - Adjust pin

V

IN

6 6 Input voltage of the LDO

NC - 5 Not connected

GND EXP pad Exposed pad must be connected to GND

Function

V

IN

ADJ

V

OUT

4/23 Doc ID 15676 Rev 3

LD39100XX, LD39100XX12, LD39100XX25 Maximum ratings

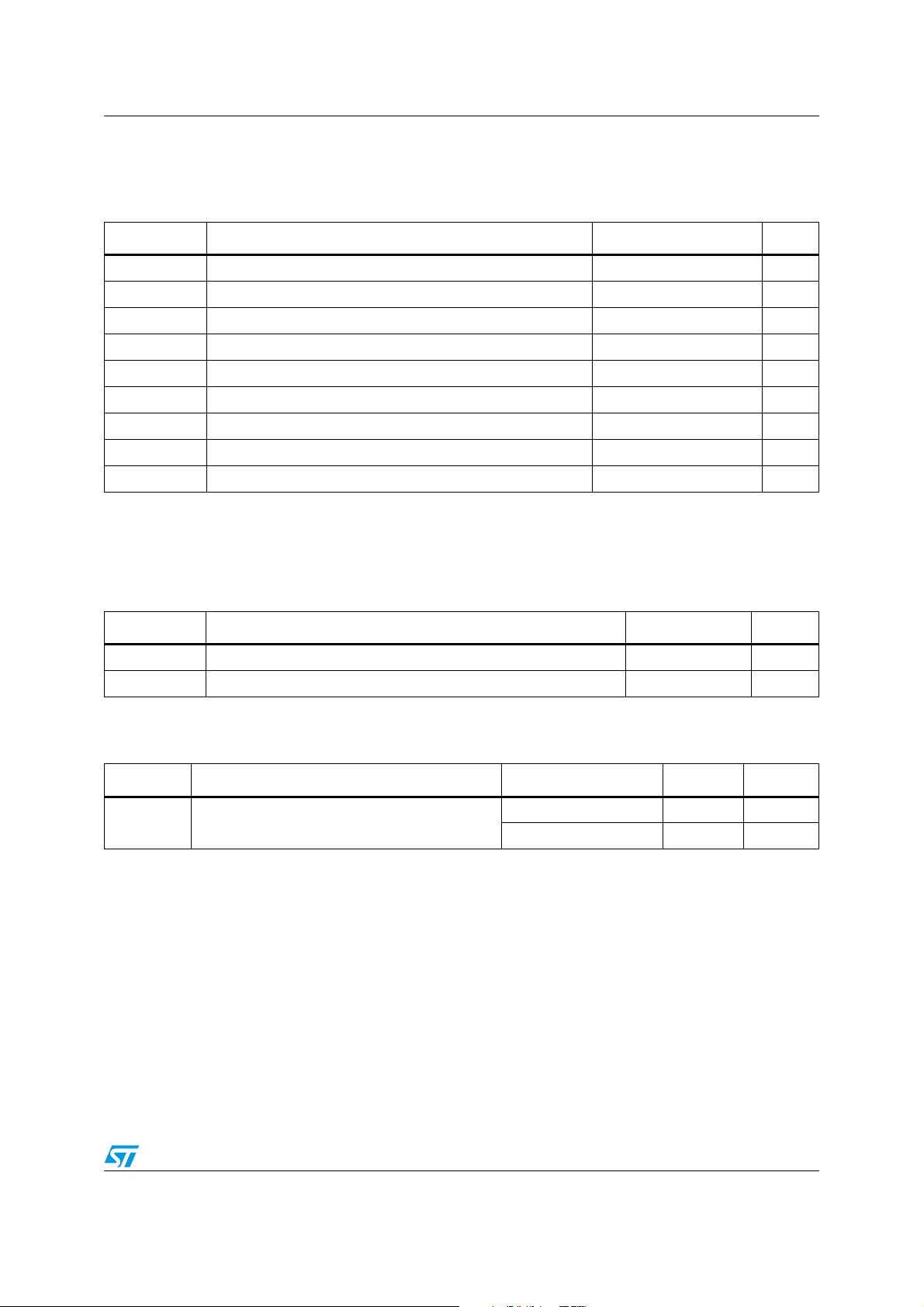

3 Maximum ratings

Table 3. Absolute maximum ratings

Symbol Parameter Value Unit

V

IN

V

OUT

EN Enable pin -0.3 to V

DC input voltage -0.3 to 7 V

DC output voltage -0.3 to VIN + 0.3 (7 V max) V

+ 0.3 (7 V max) V

IN

PG Power Good pin -0.3 to 7 V

ADJ Adjust pin 4 V

I

T

T

OUT

P

D

STG

OP

Output current Internally limited

Power dissipation Internally limited

Storage temperature range - 65 to 150 °C

Operating junction temperature range - 40 to 125 °C

Note: Absolute maximum ratings are those values beyond which damage to the device may occur.

Functional operation under these conditions is not implied. All values are referred to GND.

Table 4. Thermal data

Symbol Parameter Value Unit

R

R

thJA

thJC

Thermal resistance junction-ambient 55 °C/W

Thermal resistance junction-case 10 °C/W

Table 5. ESD performance

Symbol Parameter Test conditions Value Unit

ESD ESD protection voltage

HBM 4 kV

MM 0.4 kV

Doc ID 15676 Rev 3 5/23

Electrical characteristics LD39100XX, LD39100XX12, LD39100XX25

4 Electrical characteristics

TJ = 25 °C, V

= 1.8 V, CIN = C

IN

OUT

= 1 µF, I

= 100 mA, VEN = VIN, unless otherwise

OUT

specified.

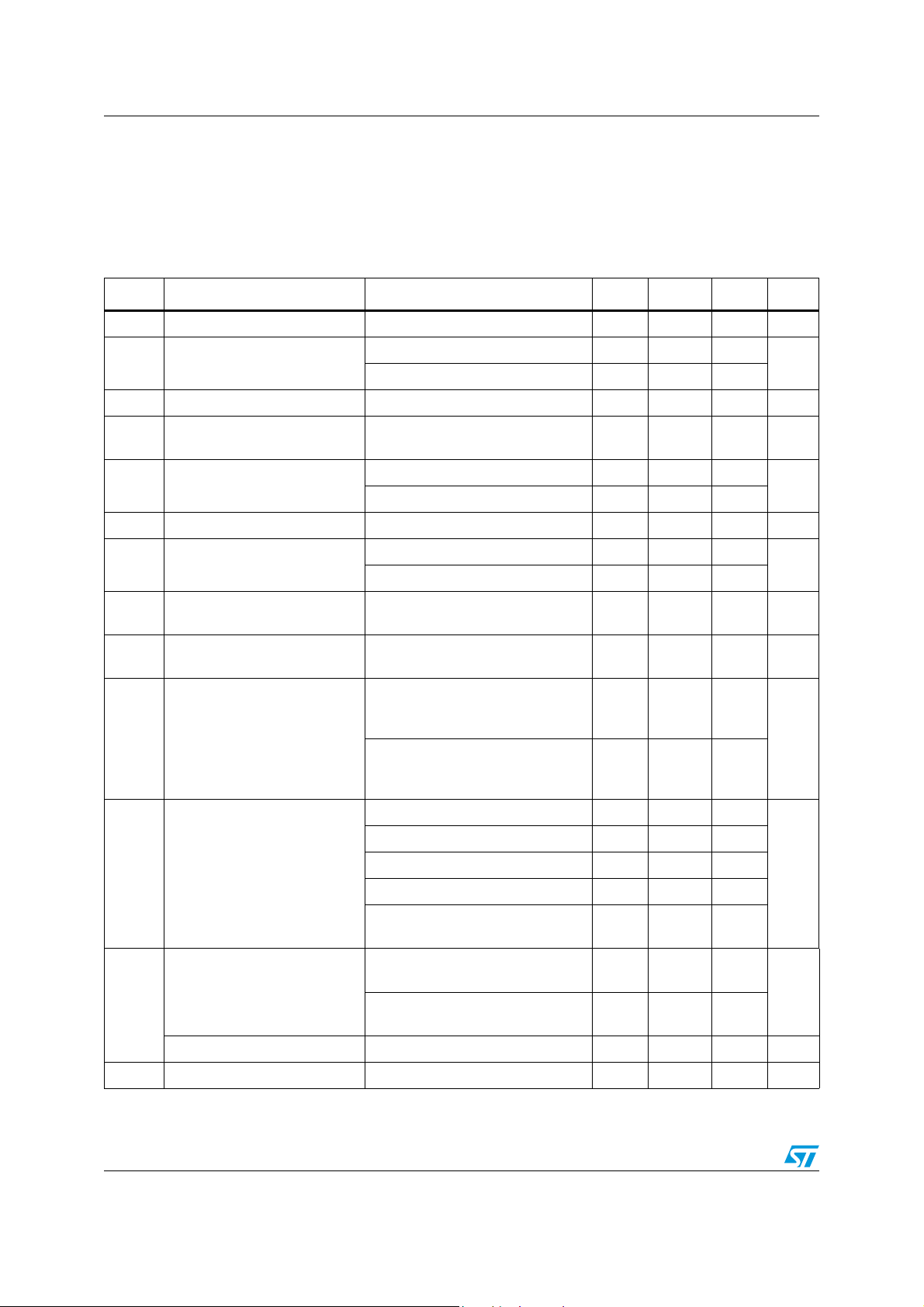

Table 6. Electrical characteristics for the LD39100PU

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

IN

V

ADJVADJ

I

ADJ

ΔV

OUT

ΔV

OUT

ΔV

OUT

ΔV

OUT

V

DROP

e

N

SVR

I

Q

PG

I

SC

Operating input voltage 1.5 5.5 V

I

=10mA, TJ = 25°C 784 800 816

accuracy

OUT

=10mA, -40°C<TJ<125°C 776 800 824

I

OUT

Adjust pin current 1µA

+1 V ≤ VIN ≤ 5.5 V,

V

Static line regulation

Transient line regulation

(1)

Static load regulation I

Transient load regulation

Dropout voltage

(2)

(1)

Output noise voltage

Supply voltage rejection

= 0.8 V

V

O

Quiescent current

Power good output threshold

OUT

=100mA

I

OUT

ΔVIN=500mV, I

=500mV, I

ΔV

IN

=10mA to 1A 0.002 %/mA

OUT

I

=10mA to 1A, tR=5µs 40

OUT

=1A to 10mA, tF=5µs 40

I

OUT

I

=1A, VO fixed to 1.5V

OUT

=100mA, tR=5µs 10

OUT

=100mA, tF=5µs 10

OUT

-40°C<TJ<125°C

10Hz to 100kHz, I

V

=0.8V

OUT

VIN=1.8V+/-V

V

RIPPLE

I

=10mA

OUT

=1.8V+/-V

V

IN

V

RIPPLE

I

=100mA

OUT

=0mA 20

I

OUT

I

=0mA, -40°C<TJ<125°C 50

OUT

=0 to 1A 200

I

OUT

=0 to 1A, -40°C<TJ<125°C 300

I

OUT

V

input current in off mode:

IN

VEN=GND

RIPPLE

=0.25V, freq. = 1kHz

RIPPLE

=0.25V, freq.=10kHz

(3)

OUT

=100mA,

Rising edge

Falling edge

0.01 %/V

200 400 mV

30 µV

65

62

0.001 1

0.92*

V

OUT

0.8*

V

OUT

Power good output voltage low Isink=6mA open drain output 0.4 V

Short-circuit current RL=0 1.5 A

mV

mVpp

mVpp

RMS

dB

µA

V

6/23 Doc ID 15676 Rev 3

LD39100XX, LD39100XX12, LD39100XX25 Electrical characteristics

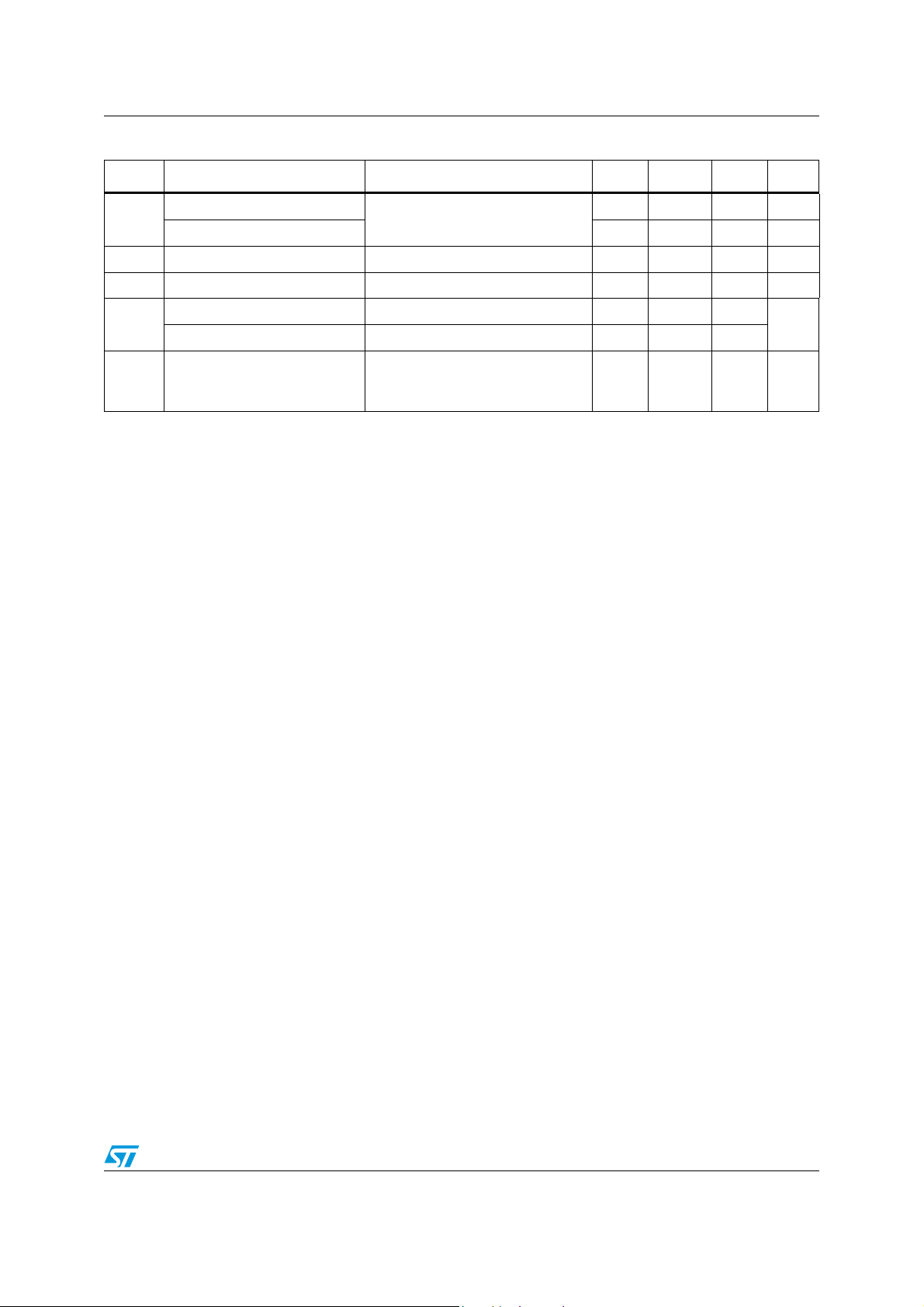

Table 6. Electrical characteristics for the LD39100PU (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

EN

Enable input logic high 0.9 V

I

Enable pin input current VEN= V

EN

t

ON

Turn-on time

(4)

=1.5V to 5.5V, -40°C<TJ<125°C

V

IN

IN

0.1 100 nA

30 µs

Enable input logic low

0.4 V

Thermal shutdown 160

T

SHDN

Hysteresis 20

°C

Capacitance (see typical

C

Output capacitor

OUT

performance characteristics for

122µF

stability)

1. All transient values are guaranteed by design, not production tested

2. Dropout voltage is the input-to-output voltage difference at which the output voltage is 100 mV below its nominal value. This

specification does not apply for output voltages below 1.5 V

3. PG pin floating

4. Turn-on time is time measured between the enable input just exceeding V

reaching 95% of its nominal value

high value and the output voltage just

EN

Doc ID 15676 Rev 3 7/23

Loading...

Loading...