Sony Z40HR Schematics

5

4

3

2

1

http://laptopblue.vn/

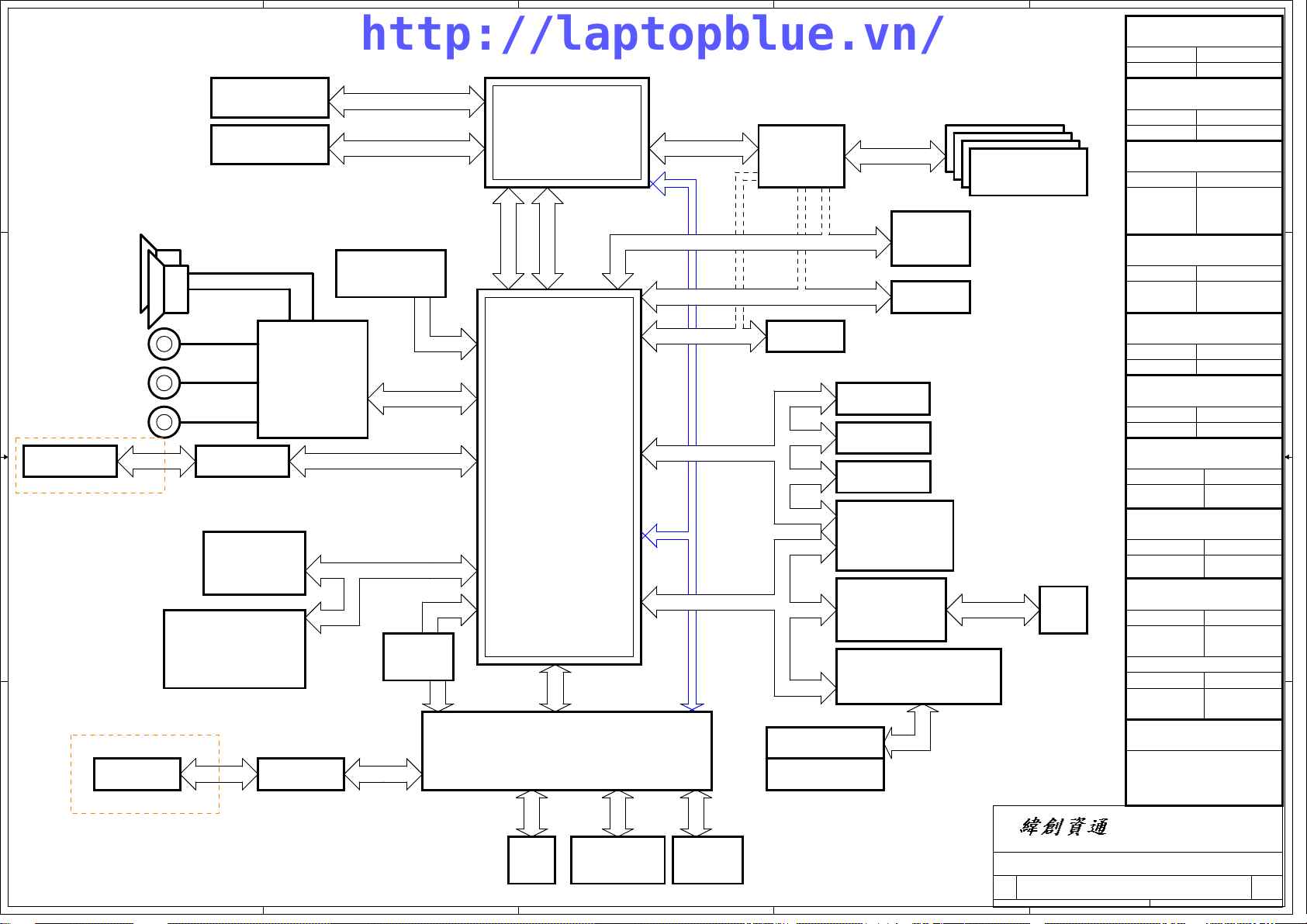

Z50-HR(S204-SC) Schematics Document

D D

Intel PCH

2011-02-14

REV :-1

C C

Sandy Bridge

B B

A A

5

4

3

2

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cover Page

Cover Page

Cover Page

Taipei Hsien 221, Taiwan, R.O.C.

1 74

1 74

1 74

1

-1

-1

-1

5

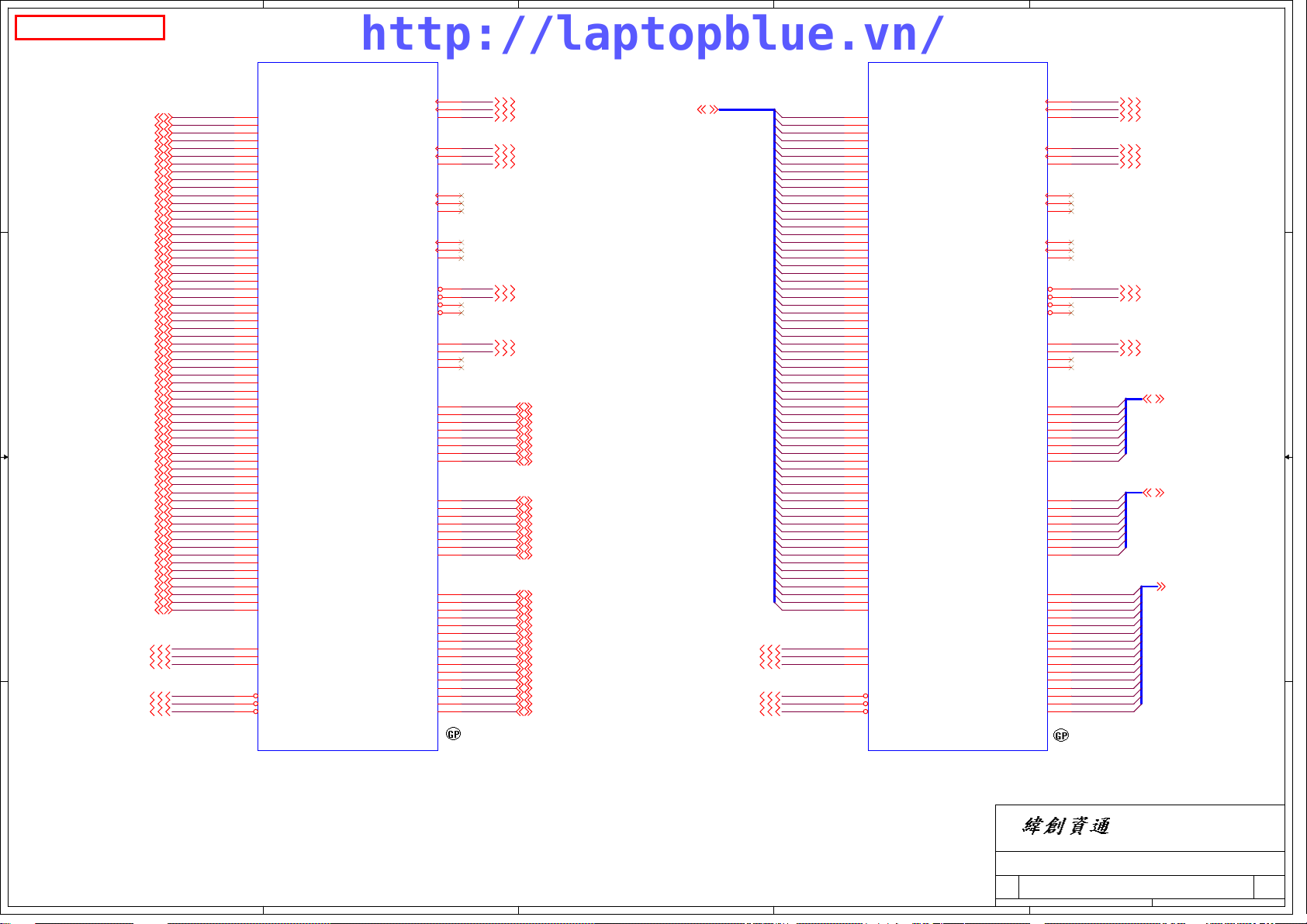

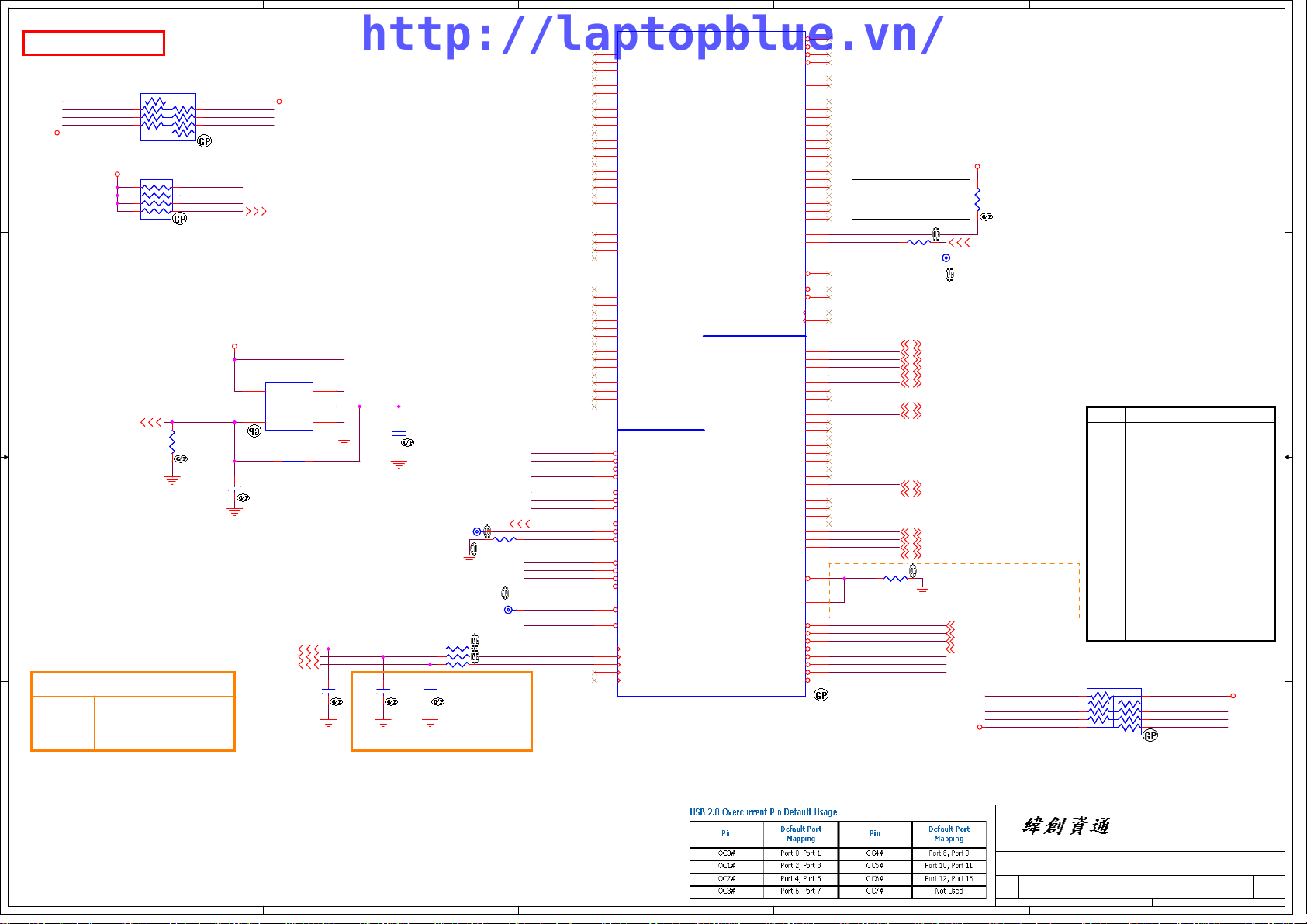

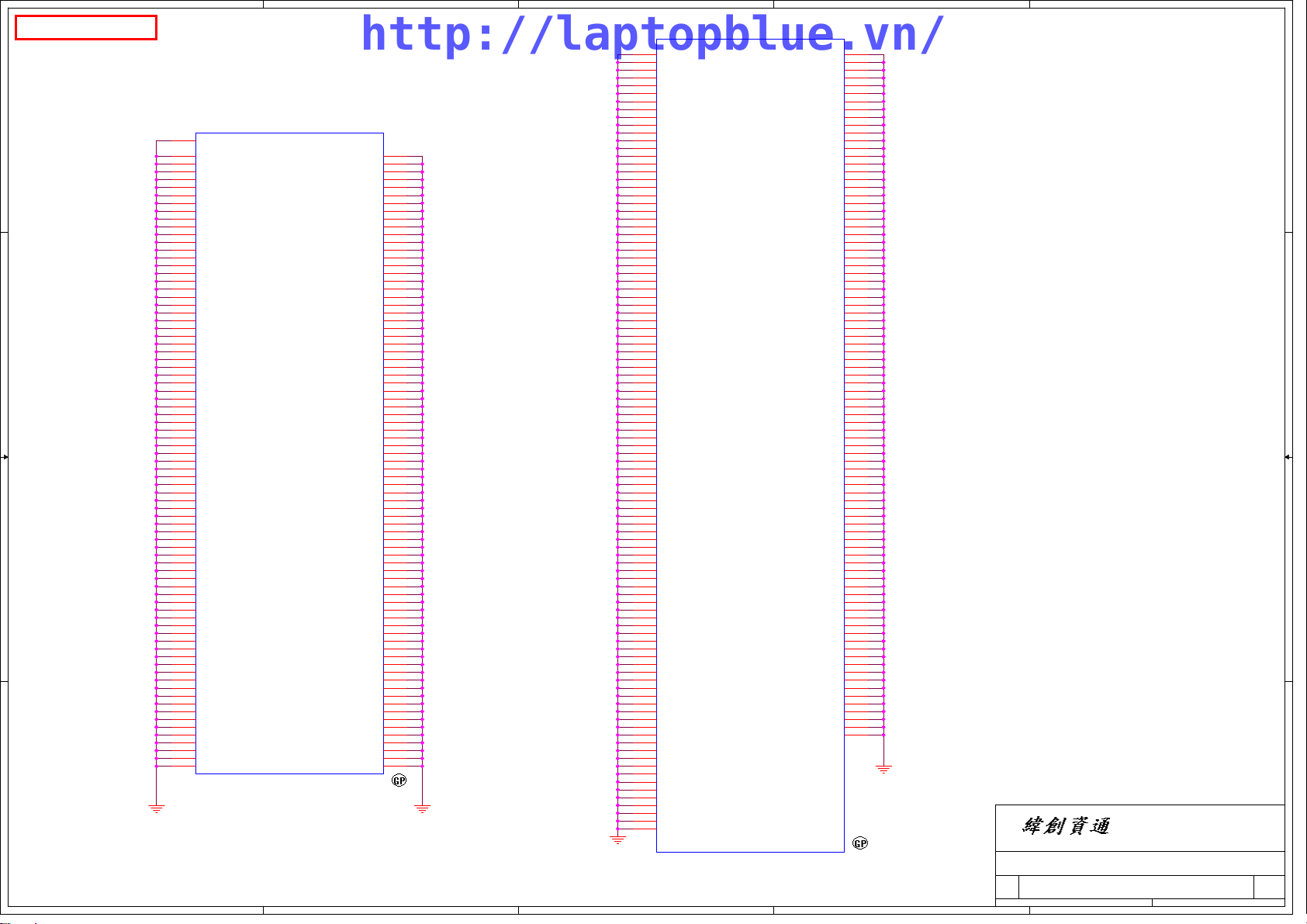

Slot 0DDRIII

Slot 1

11

12

D D

1067/1333

DDRIII

1067/1333

SPEAKER

CR2032_220mA

(Non Rechargeable)

INTERNAL MIC

C C

Headphone

External MIC

USB 2.0 x3

i/o Connector

59

USB Board

HDD 2.5'' SATA

B B

(SATA0)

Blu-ray

BD Combo

Super-Multi

(SATA4)

LED&Switch Board

59

Switch x 4

LEDx 4

A A

AUDIO CODEC

Conexant

CX20671-21Z

25,28,46

USB2.0

45

45

59

i/o Connector

4

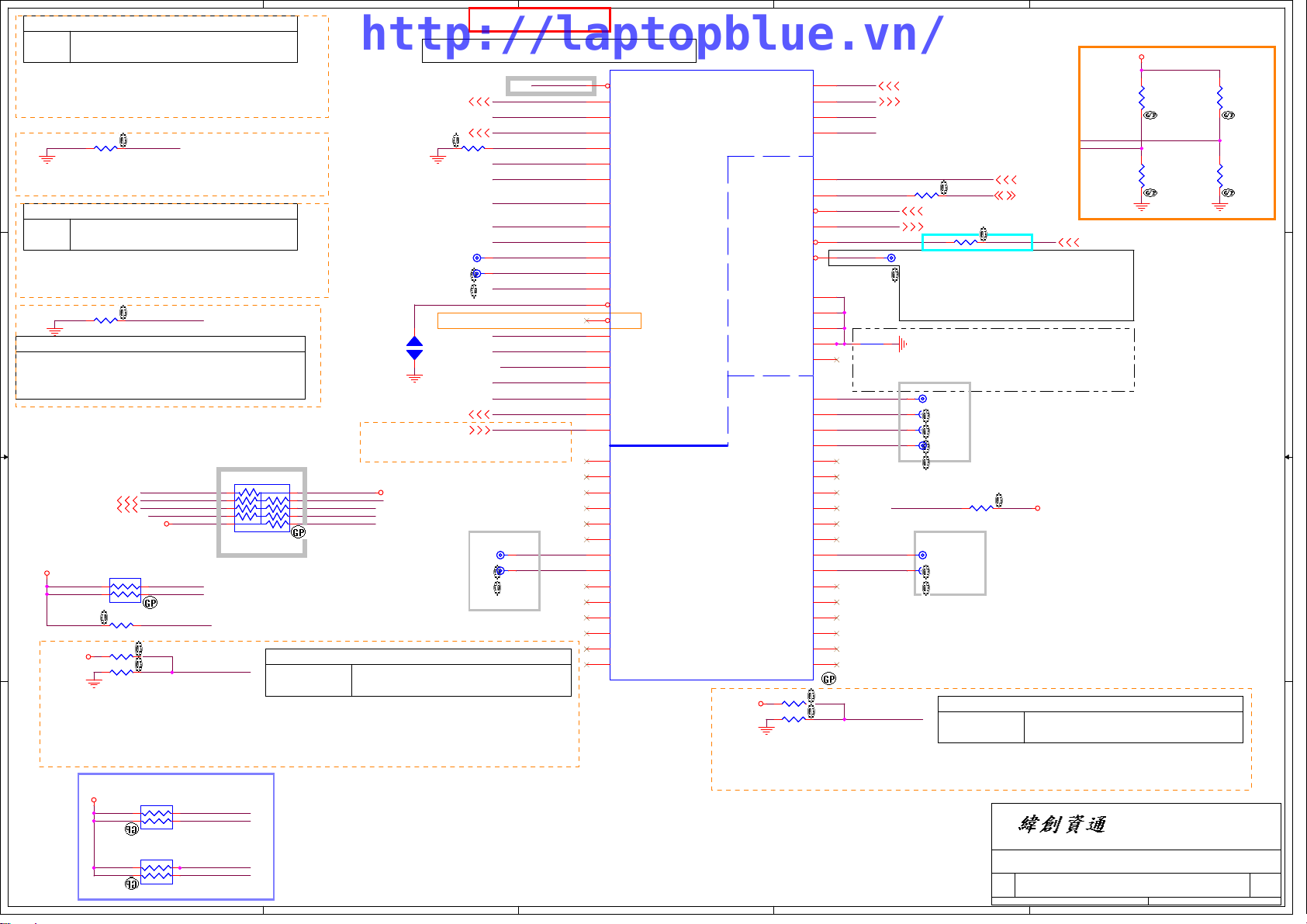

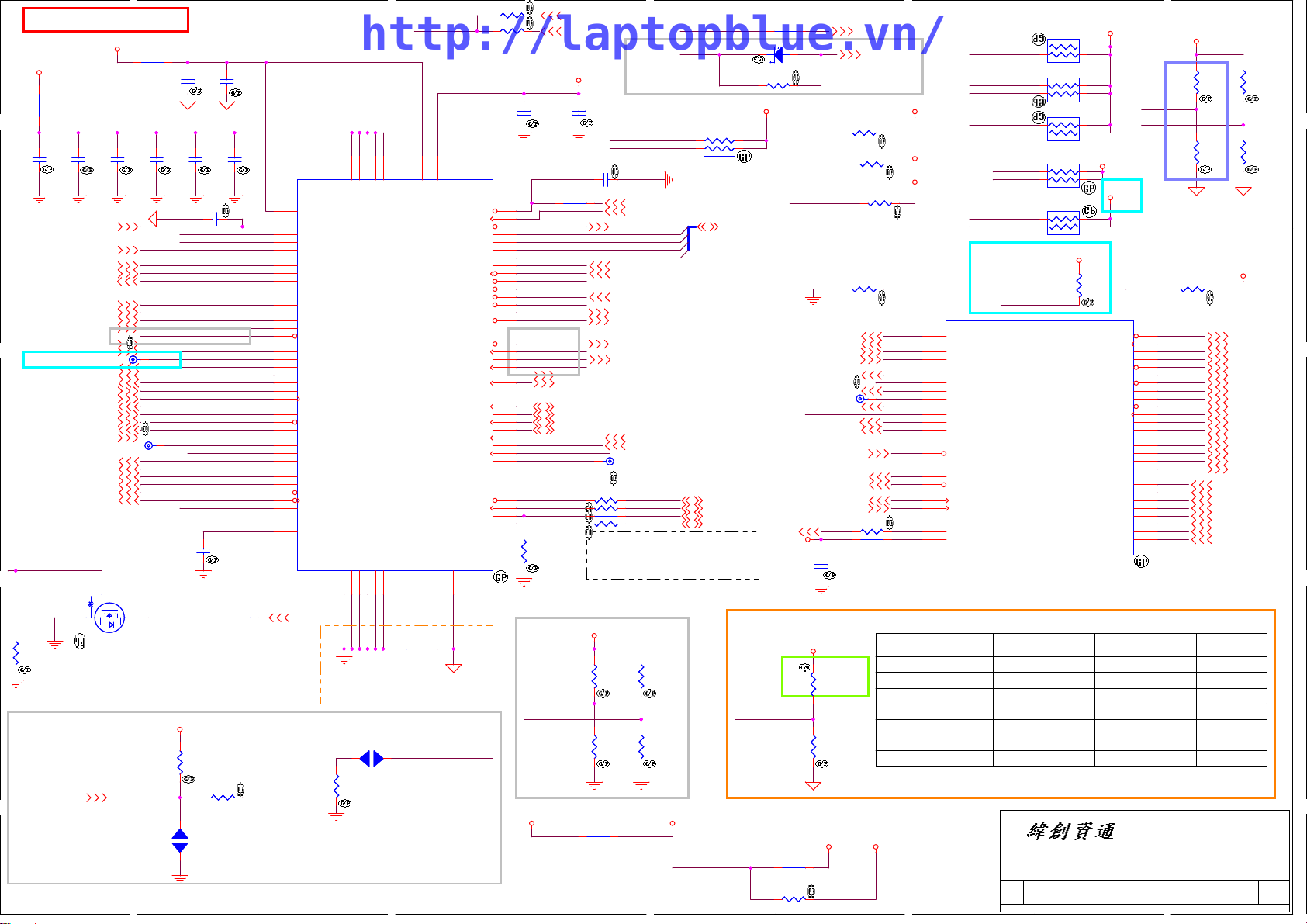

Z50-HR Block Diagram

http://laptopblue.vn/

DDRIII 1067/1333 Channel A

Intel CPU

DDRIII 1067/1333 Channel B

Sandy Bridge DC

FSB: 1066 MHz

FDI

4,5,6,7,8,9,10

DMI

at 5G

3

PCI EXPRESS GRAPHIC

Nvidia

N12M-GS

60,61,62,63,64

LVDS

2

DDR3

800MHz

VRAM x 4

15" LCD

1366x768

RTC

48

HDMI

HDMI

INTEL

RTC

PCH

RGB CRT

CRT

43

Cougar Point

HD Audio (Azalia)

SATA II

SPI

Flash

4 MB

SPI

14 USB 2.0/1.1 ports

ETHERNET

High Definition Audio

Serial Peripheral I/F(dual output)

ACPI 1.1

LPC I/F

6 SATA

(10/100/1000Mb)

USB2.0

NC

PCIE

PCI Express

13,14,15,16,17,18,19,20,21

48

KBC

LPC Bus

MS&SD Connector

23

LED&RF SW

SPI

NPEC795P

USB 2.0 x1

CAMERA

BlueTooth

Mini-Card

WLAN/WiMAX

Intel Kilmar Peak 2x2

Atheros LAN

AR8151

10/100/1000

WOL from S3

Memory Card

Controller Chip

RTS5209

56

52

1

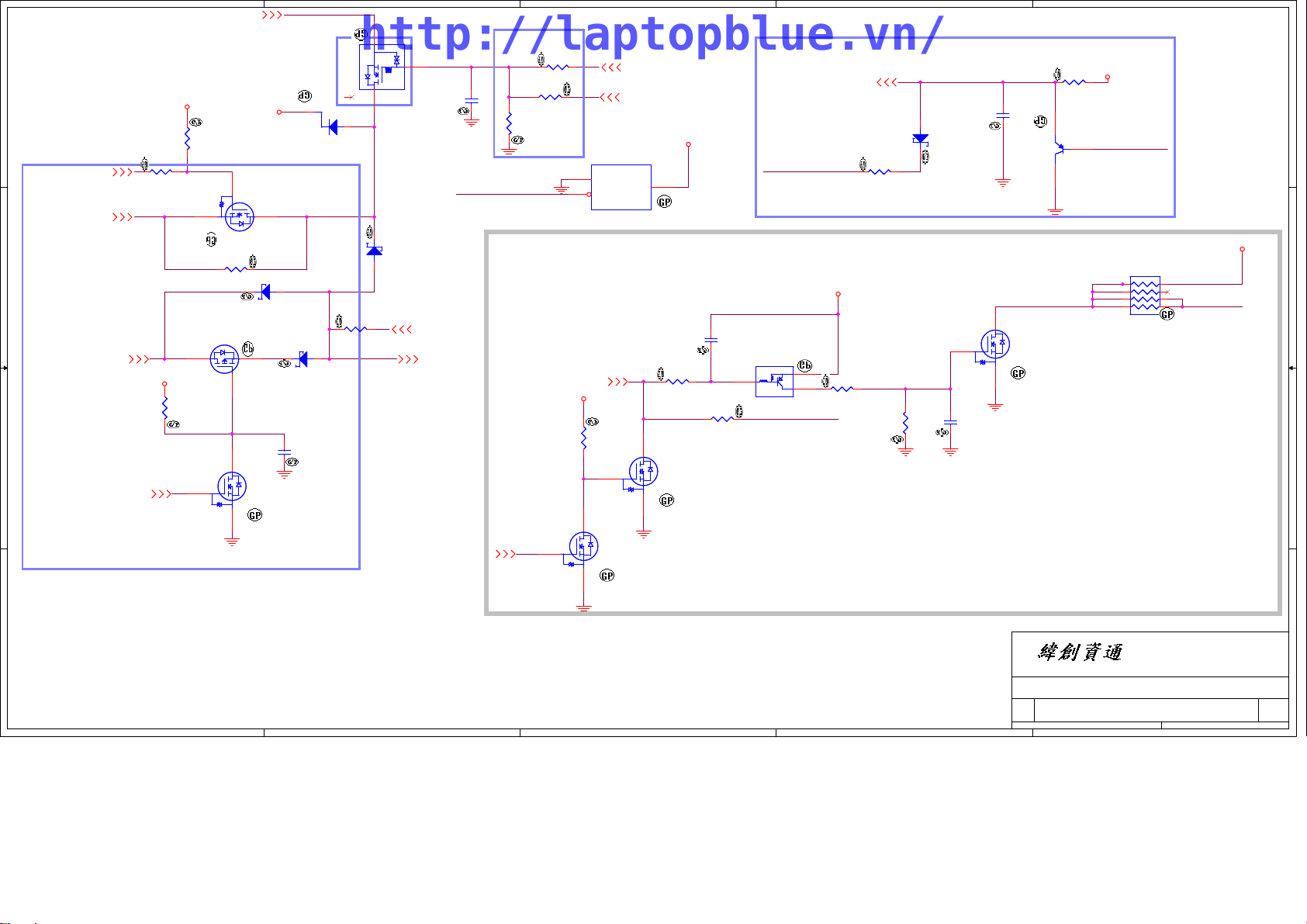

CPU DC/DC

ISL95831

INPUTS

DCBATOUT

SYSTEM DC/DC

TPS51218D

INPUTS

DCBATOUT

SYSTEM DC/DC

VRAM

1GB/512MB

42

44

65,66

RT8223

INPUTS

DCBATOUT 5V_S5

SYSTEM DC/DC

RT8207

INPUTS

DCBATOUT

SYSTEM DC/DC

ISL95831HRTZ

INPUTS

DCBATOUT

49

42

RT8208A

INPUTS

DCBATOUT

TI CHARGER

BQ24725

50

INPUTS

+DC_IN_S5

26

SYSTEM DC/DC

RT9025

INPUTS

51

3D3V_S0

SYSTEM DC/DC

RJ45

26

27

47

APL5916KAI-TRL-GP

INPUTS

26

3D3V_S0 0D85V_S0

Switches

INPUTS OUTPUTS

1D5V_S3

5V_S5

OUTPUTS

VCC_CORE

OUTPUTS

1D05V_VTT

OUTPUTS

5V_AUX_S5

3D3V_AUX_S5

3D3V_S5

OUTPUTS

1D5V_S3

0D75V_S0

DDR_VREF_S3

OUTPUTS

VCC_GFXCORE

VGA

OUTPUTS

VGA_CORE

OUTPUTS

OUTPUTS

OUTPUTS

35,36,37

DCBATOUT+PBATT

1D8V_S0

1D5V_S0

5V_S0

3D3V_S03D3V_S5

38

34

39

37

67

33

40

41

29

PCB LAYER

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

L1:Top

L2:VCC

L3:Signal

L4:Signal

L5:GND

L6:Bottom

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

2 74

2 74

2 74

1

-1

-1

-1

2453

3

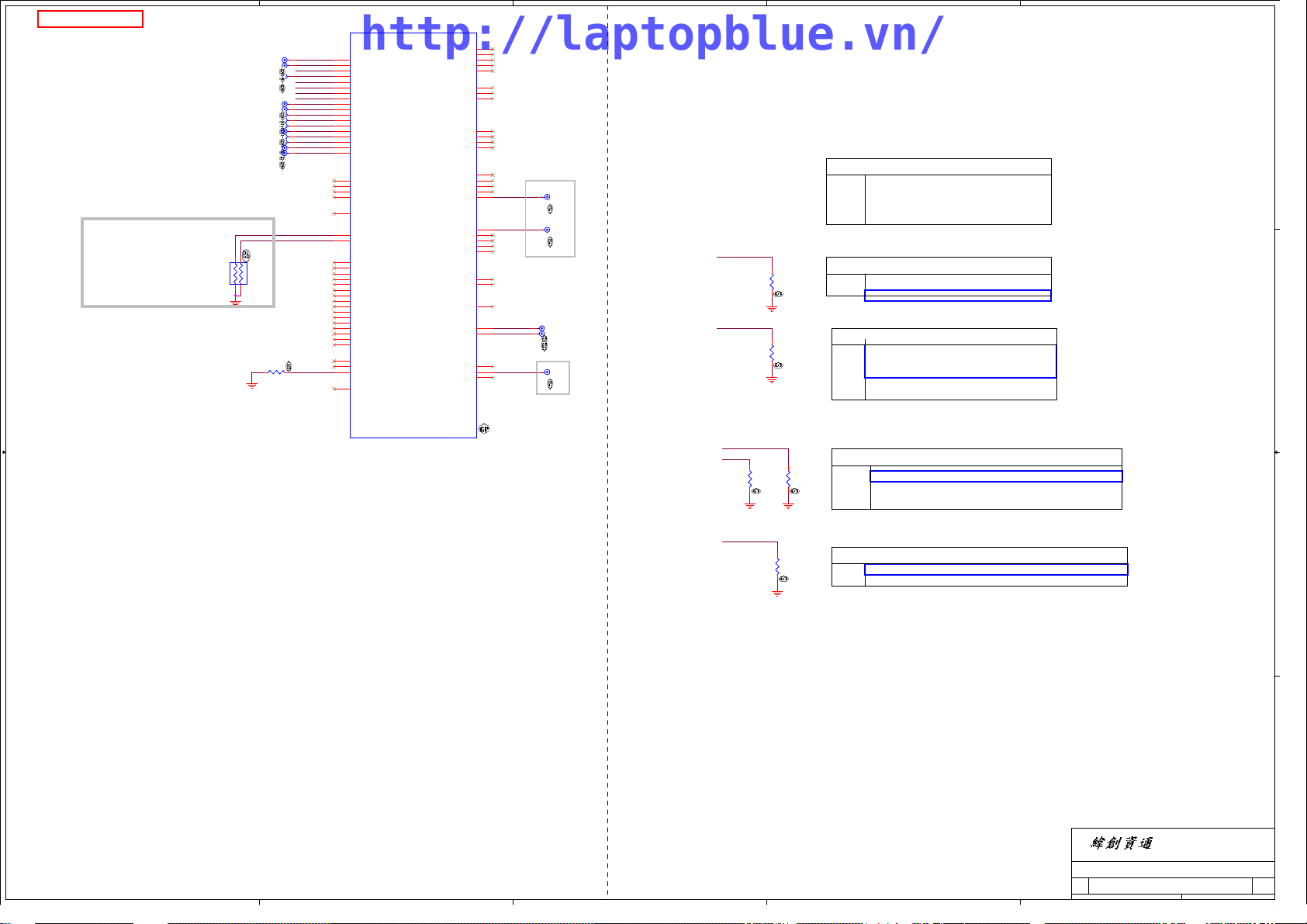

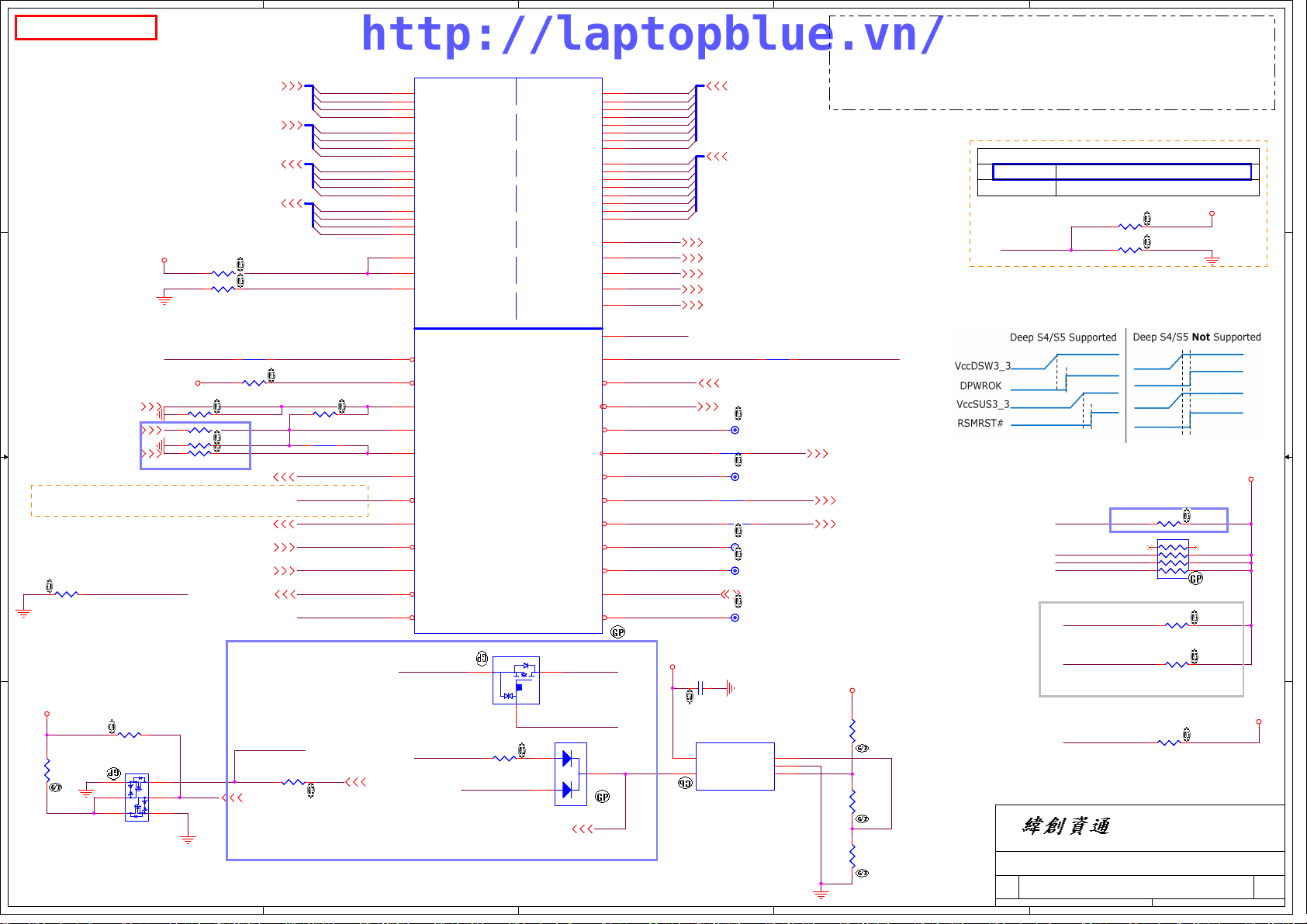

Lid switch

Title

Title

Title

54

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

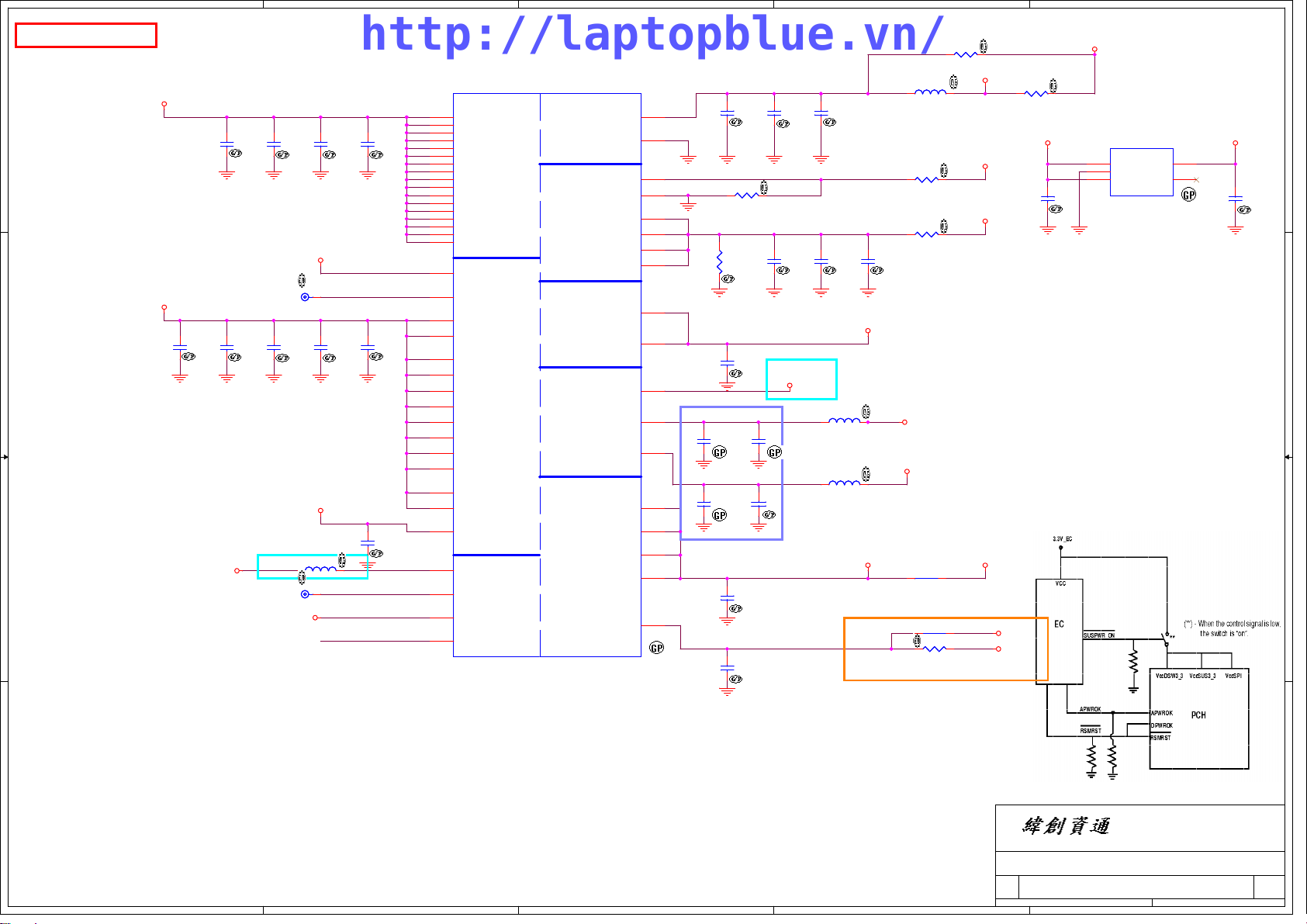

Block Diagram

Block Diagram

Block Diagram

Touch

Pad

5

4

Thermal Sensor

P2800

A

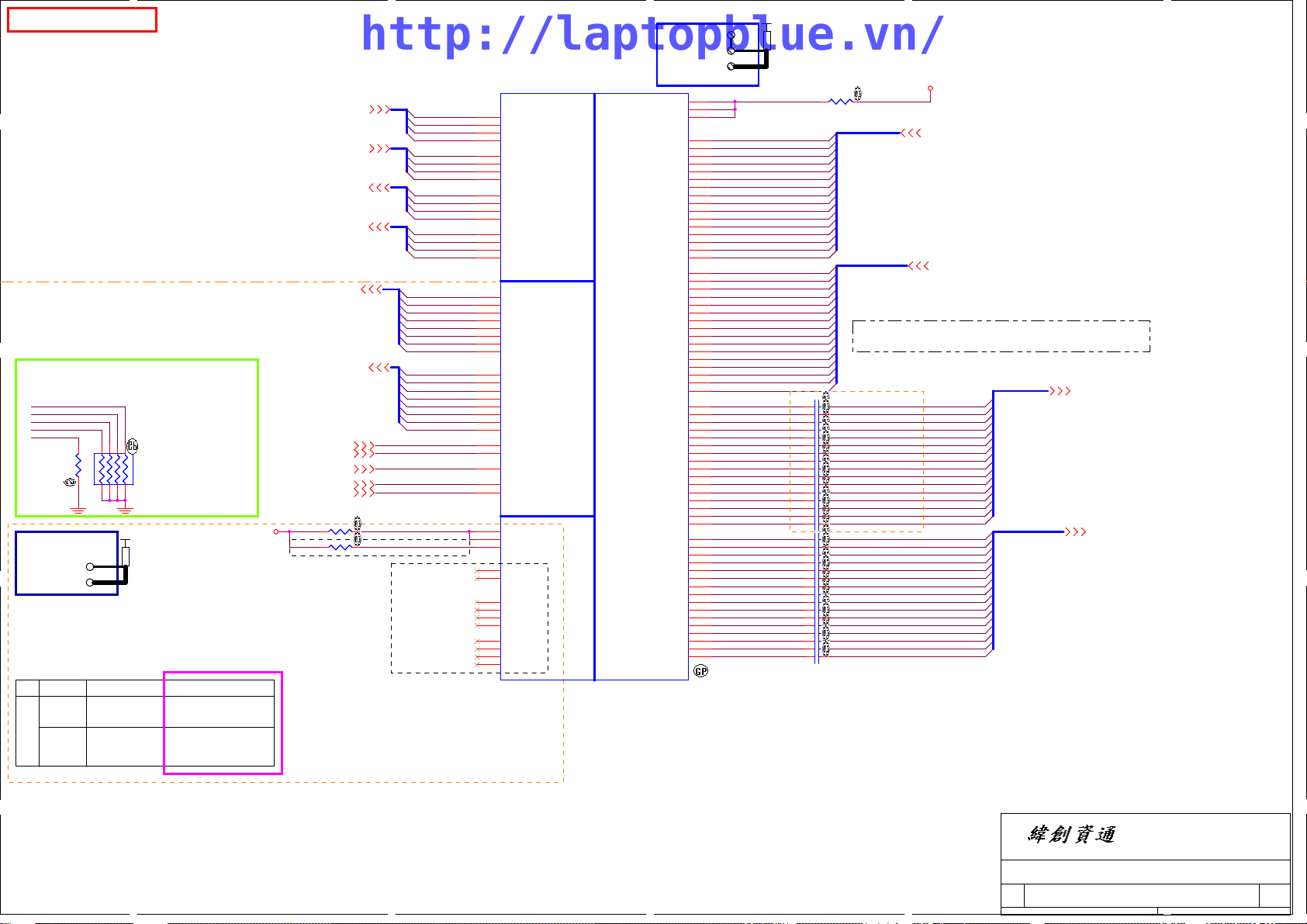

PCH Strapping

Name Schematics Notes

SPKR

INIT3_3V#

GNT3#/GPIO55

4 4

GNT2#/GPIO53

GNT1#/GPIO51

SPI_MOSI

NV_ALE

NC_CLE

HAD_DOCK_EN#

/GPIO[33]

3 3

Reboot option at power-up

Internal weak Pull-down.

Default Mode:

Connect to Vcc3_3 with 8.2-kΩ

No Reboot Mode with TCO Disabled:

- 10-kΩ weak pull-up resistor.

Weak internal pull-up. Leave as "No Connect".

GNT[3:0]# functionality is not available on Mobile.

Mobile: Used as GPIO only

Pull-up resistors are not required on these signals.

If pull-ups are used, they should be tied to the Vcc3_3power rail.

Enable Danbury:

Disable Danbury:

Enable Danbury:

Disable Danbury:

DMI termination voltage. Weak internal pull-up. Do not pull low.

Low (0) - Flash Descriptor Security will be overridden. Also,

when this signals is sampled on the rising edge of PWROK

then it will also disable Intel ME and its features.

High (1) - Security measure defined in the Flash Descriptor will be enabled.

Platform design should provide appropriate pull-up or pull-down depending on

the desired settings. If a jumper option is used to tie this signal to GND as

required by the functional strap, the signal should be pulled low through a weak

pull-down in order to avoid asserting HDA_DOCK_EN# inadvertently.

Note: CRB recommends 1-kohm pull-down for FD Override. There is an internal

pull-up of 20 kohm for DA_DOCK_EN# which is only enabled at boot/reset for

strapping functions.

Huron River Schematic Checklist Rev.0_7

Connect to Vcc3_3 with 8.2-k? weak pull-up resistor.

Left floating, no pull-down required.

Connect to +NVRAM_VCCQ with 8.2-kohm

weak pull-up resistor [CRB has it pulled up

with 1-kohm no-stuff resistor]

Leave floating (internal pull-down)

B

http://laptopblue.vn/

C

Processor Strapping

Pin Name Strap Description Configuration (Default value for each bit is

CFG[2]

CFG[4]

CFG[6:5]

CFG[7]

PCI-Express Static

Lane Reversal

PCI-Express

Port Bifurcation

Straps

PEG DEFER TRAINING

1 unless specified otherwise)

1:

Normal Operation.

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

0:

Disabled - No Physical Display Port attached to

1:

Embedded DisplayPort.

Enabled - An external Display Port device is

0:

connectd to the EMBEDDED display Port

11 : x16 - Device 1 functions 1 and 2 disabled

10 : x8, x8 - Device 1 function 1 enabled ;

function 2 disabled

01 : Reserved - (Device 1 function 1 disabled ;

function 2 enabled)

00 : x8, x4, x4 - Device 1 functions 1 and 2

enabled

1:

PEG Train immediately following xxRESETB de assertion

PEG Wait for BIOS for training

0:

D

Huron River Schematic Checklist Rev.0_7

Default

Value

1

0

11

1

E

HDA_SDO

HDA_SYNC

GPIO15

GPIO8

2 2

GPIO27

Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

Weak internal pull-down. Do not pull high. Sampled at rising edge of RSMRST#.

Low (1) - Intel ME Crypto Transport Layer Security (TLS) cipher suite with no

confidentiality High (1) - Intel ME Crypto Transport Layer Security (TLS) cipher

suite with confidentiality

Note : This is an un-muxed signal.

This signal has a weak internal pull-down of 20 kohm which is enabled when PWROK is low.

Sampled at rising edge of RSMRST#.

CRB has a 1-kohm pull-up on this signal to +3.3VA rail.

GPIO8 on PCH is the Integrated Clock Enable strap and is required to be pulled-down

using a 1k +/- 5% resistor. When this signal is sampled high at the rising edge of

RSMRST#, Integrated Clocking is enabled, When sampled low, Buffer Through Mode is

enabled.

Default = Do not connect (floating)

High(1) = Enables the internal VccVRM to have a clean supply for

analog rails. No need to use on-board filter circuit.

Low (0) = Disables the VccVRM. Need to use on-board filter

circuits for analog rails.

USB Table

Pair

PCIE Routing

LANE1

LANE2

LANE3

LANE4

1 1

LANE5

LANE6

LANE7

LANE8

Mini Card1(WLAN)

Card Reader

N/A

GIGA LAN

N/A

N/A

N/A

N/A

SATA Table

SATA

Pair

0

1

2

3

4

5

Device

HDD1

N/A

N/A

N/A

ODD

N/A

0

1

2

3

4

5

6

7

8

9

10

11

12

13

Device

USB Ext. port 2

USB Ext. port 1

USB Ext. port 4

USB Ext. port 3

X

X

X

X

CAMERA

X

X

Mini Card1 (WLAN)

BLUETOOTH

OC#0

OC#1

OC#2

OC#3

OC#5

OC#7

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

Table of Content

Table of Content

Table of Content

Taipei Hsien 221, Taiwan, R.O.C.

3 74

3 74

3 74

-1

-1

-1

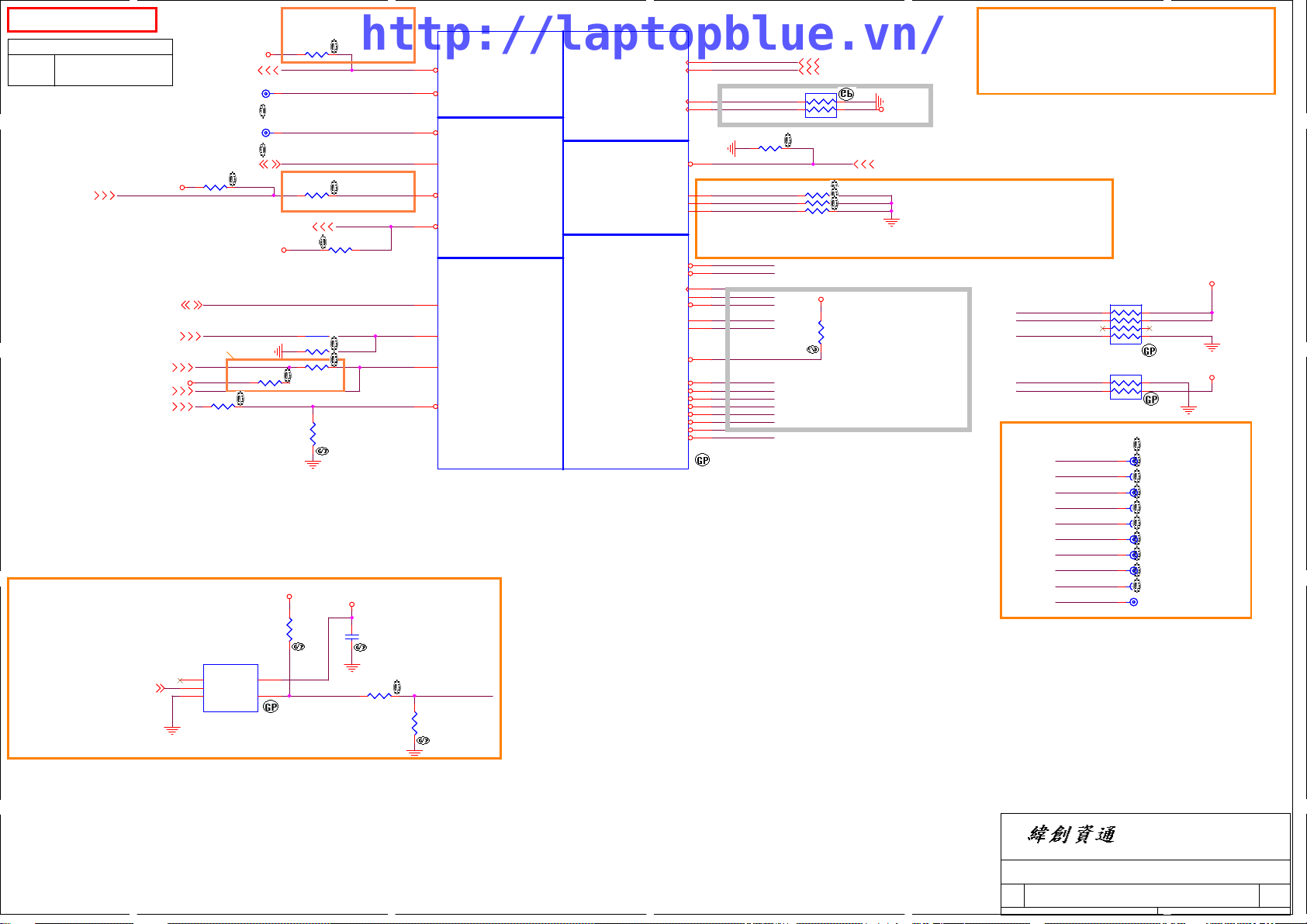

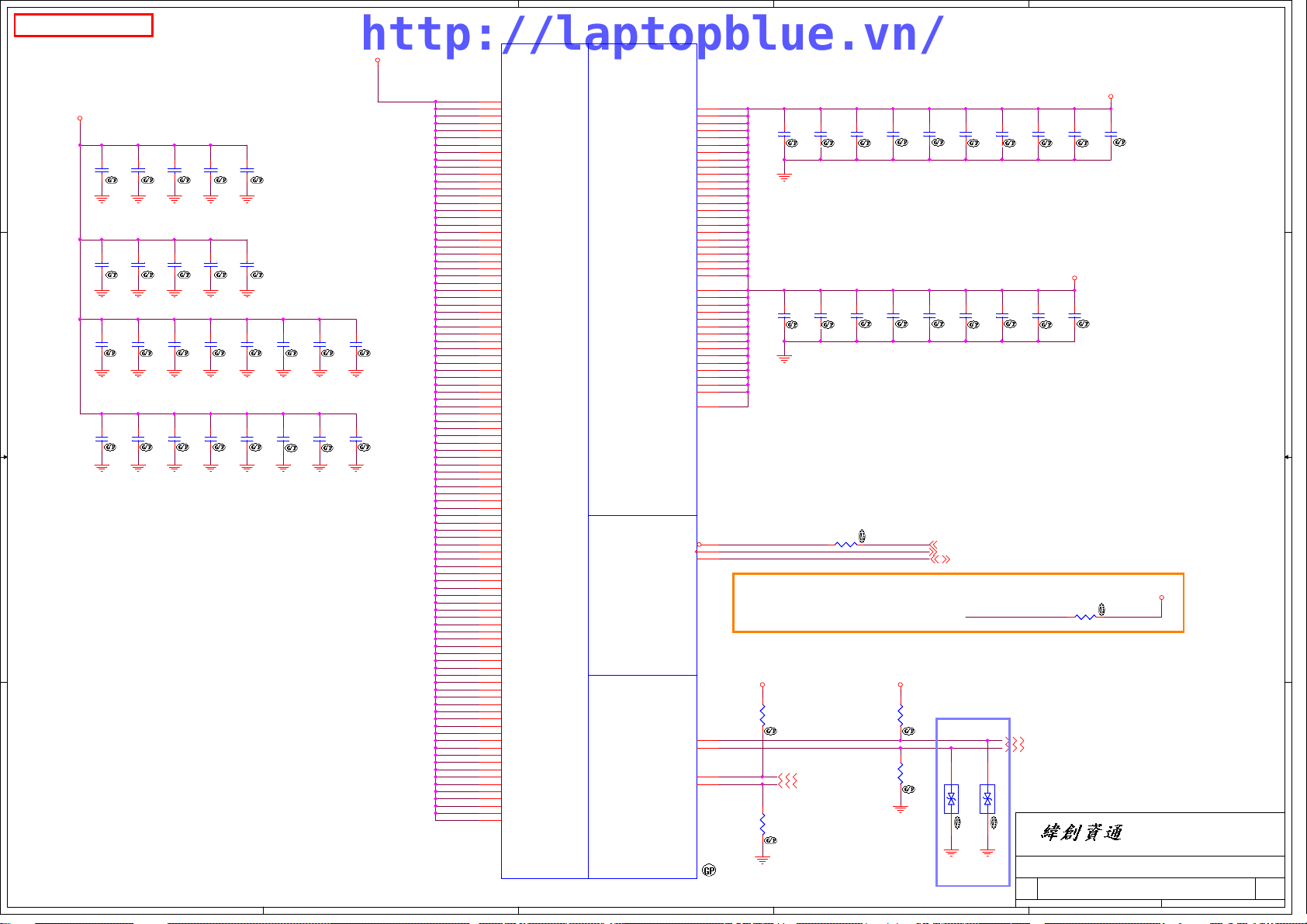

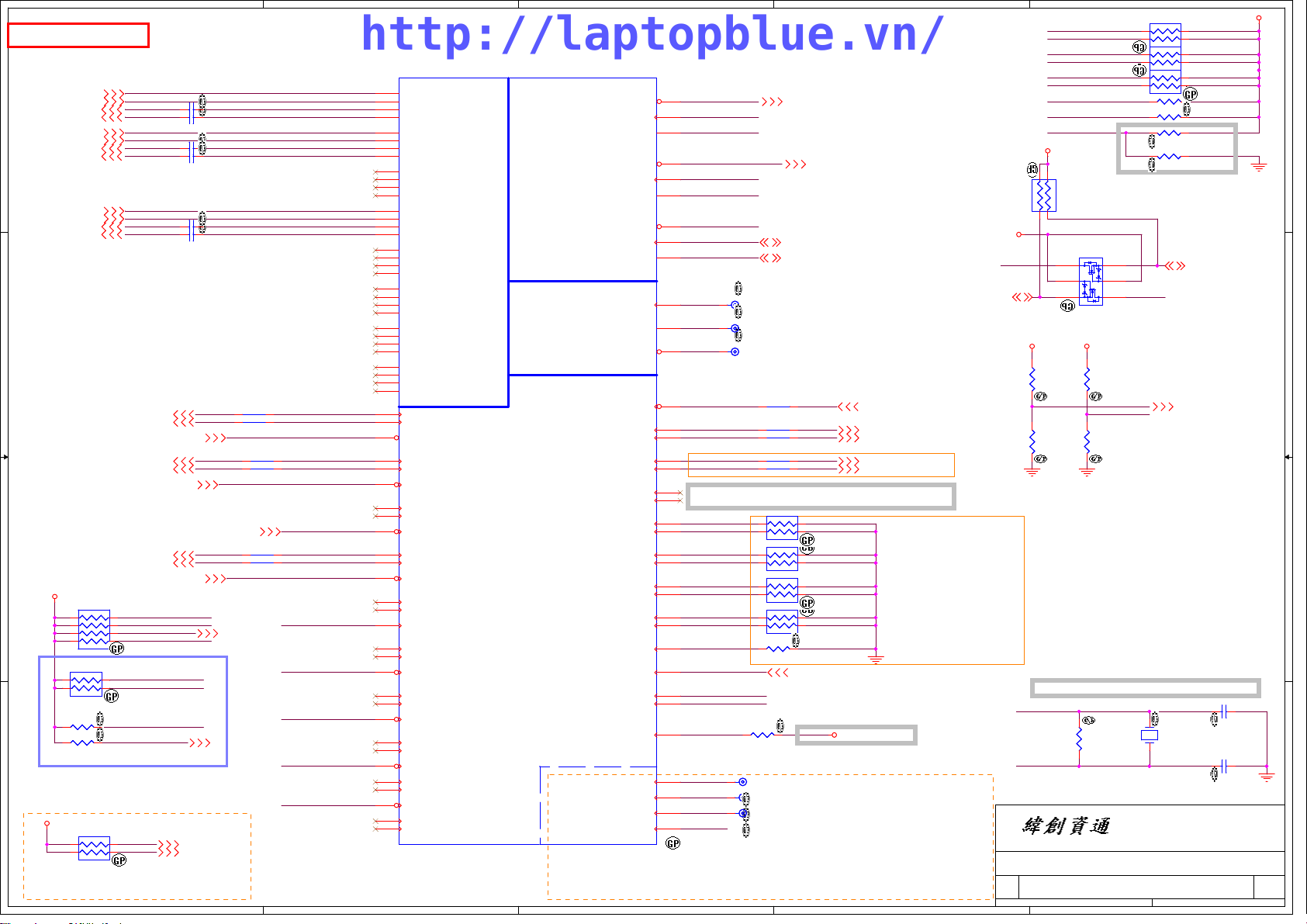

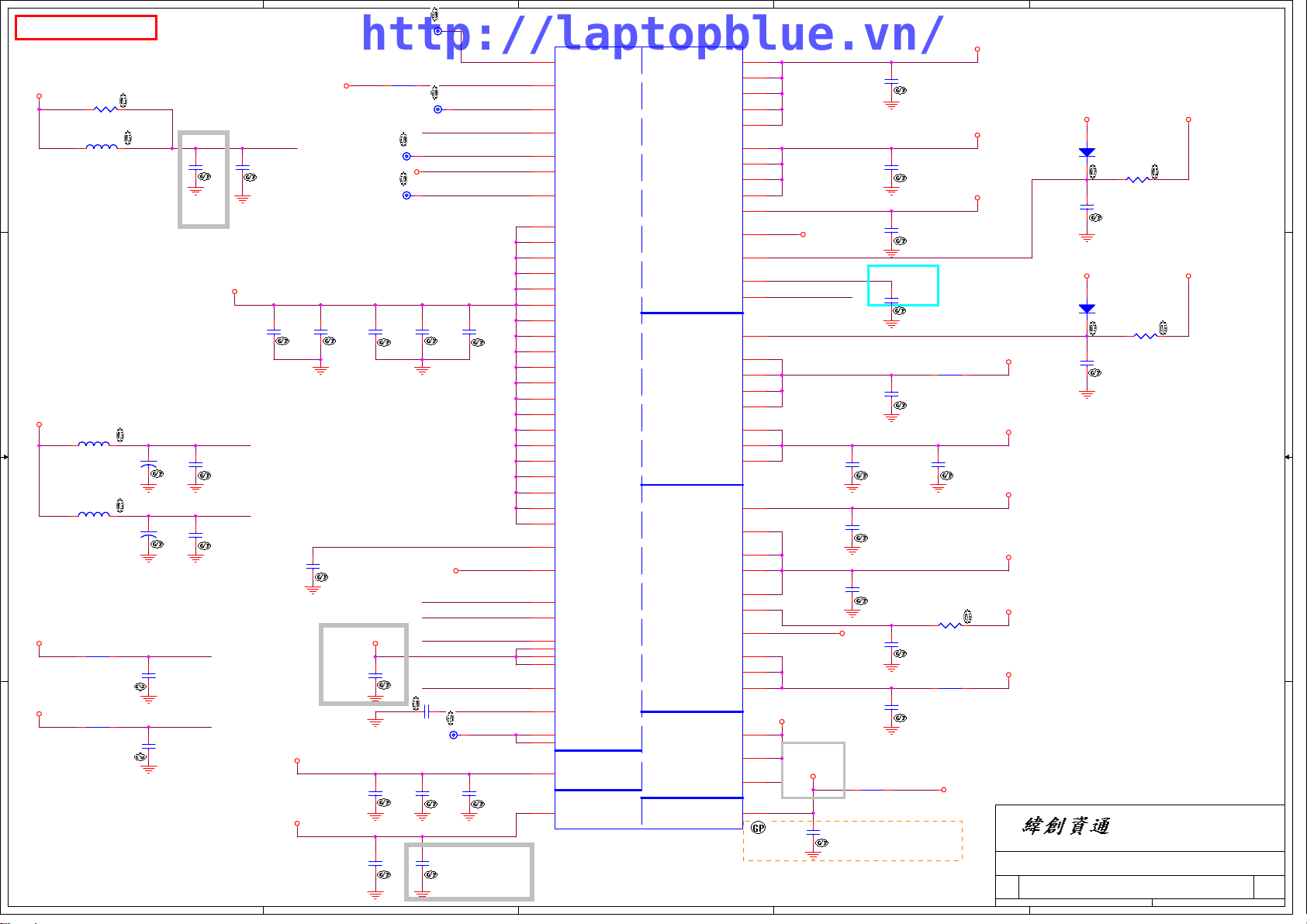

SSID = CPU

5

Note:

Intel DMI supports both Lane

D D

Reversal and polarity inversion

but only at PCH side. This is

enabled via a soft strap.

Note:

Intel FDI supports both Lane Reversal and polarity

inversion but only at PCH side. This is enabled via a

soft strap.

Lane reversal does not apply to FDI sideband signals.

C C

If left as no connect, there is no

functional impact, but power (~15 mW)

may be wasted.

FDI_LSYNC0

FDI_FSYNC0

FDI_LSYNC1

FDI_FSYNC1

FDI_INT

12

R404

R404

1KR2J-1-GP

1KR2J-1-GP

DIS

DIS

EDP_COMPIO

B B

EDP_ICOMPO

【

Signal Routing Guideline:

EDP_ICOMPO keep W/S=12/15 mils and routing

length less than 500 mils.

EDP_COMPIO keep W/S=4/15 mils and routing

length less than 500 mils.

Port

DG 0.9 P.54

Strap Enable Disable

CFG[4]

eDP

EDP_HDP

678

RN401

RN401

SRN1KJ-4-GP

SRN1KJ-4-GP

DIS

DIS

66.10236.08L

66.10236.08L

123

4 5

VCCIO

24.9R

4mil

12mil

】

Pull down to GND

through a 1K ±

5% resistor

Pull down to GND

through a 1K ±

5% resistor

1D05V_VTT

No Connect

Pull high to CPU VCCIO

through a 10K ±

5% resistor

DMI_TXN[3:0]15

DMI_TXP[3:0]15

DMI_RXN[3:0]15

DMI_RXP[3:0]15

FDI_TXN[7:0]15

FDI_TXP[7:0]15

FDI_FSYNC015

FDI_FSYNC115

FDI_INT15

FDI_LSYNC015

FDI_LSYNC115

R402 24D9R2F-L-GPR402 24D9R2F-L-GP

1 2

R403

R403

1 2

4

http://laptopblue.vn/

CPU1A

CPU1A

SANDY

DMI_RX#0

DMI_RX#1

DMI_RX#2

DMI_RX#3

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

DMI_TX#0

DMI_TX#1

DMI_TX#2

DMI_TX#3

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

FDI0_TX#0

FDI0_TX#1

FDI0_TX#2

FDI0_TX#3

FDI1_TX#0

FDI1_TX#1

FDI1_TX#2

FDI1_TX#3

FDI0_TX0

FDI0_TX1

FDI0_TX2

FDI0_TX3

FDI1_TX0

FDI1_TX1

FDI1_TX2

FDI1_TX3

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

EDP_COMPIO

EDP_ICOMPO

EDP_HPD

EDP_AUX

EDP_AUX#

EDP_TX0

EDP_TX1

EDP_TX2

EDP_TX3

EDP_TX#0

EDP_TX#1

EDP_TX#2

EDP_TX#3

SANDY

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

10KR2J-3-GP

10KR2J-3-GP

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

DP_COMP

eDP_HPD

eDP

Disable

B27

B25

A25

B24

B28

B26

A24

B23

G21

E22

F21

D21

G22

D22

F20

C21

A21

H19

E19

F18

B21

C20

D18

E17

A22

G19

E20

G18

B20

C19

D19

F17

H20

H17

A18

A17

B16

C15

D15

C17

F16

C16

G15

C18

E16

D16

F15

J18

J17

J19

ARRAN

ARRAN

3

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

【

DG 0.9 P.32

PEG_RCOMPO

PEG_ICOMPI

PEG_ICOMPO

1 OF 9

1 OF 9

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

】

VCCIO

4mil

12mil

PEG_IRCOMP_R

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

PEG_C_TXN15

PEG_C_TXN14

PEG_C_TXN13

PEG_C_TXN12

PEG_C_TXN11

PEG_C_TXN10

PEG_C_TXN9

PEG_C_TXN8

PEG_C_TXN7

PEG_C_TXN6

PEG_C_TXN5

PEG_C_TXN4

PEG_C_TXN3

PEG_C_TXN2

PEG_C_TXN1

PEG_C_TXN0

PEG_C_TXP15

PEG_C_TXP14

PEG_C_TXP13

PEG_C_TXP12

PEG_C_TXP11

PEG_C_TXP10

PEG_C_TXP9

PEG_C_TXP8

PEG_C_TXP7

PEG_C_TXP6

PEG_C_TXP5

PEG_C_TXP4

PEG_C_TXP3

PEG_C_TXP2

PEG_C_TXP1

PEG_C_TXP0

Signal Routing Guideline:

PEG_ICOMPO keep W/S=12/15 mils and routing length less than 500 mils.

24.9R

PEG_ICOMPI & PEG_RCOMPO keep W/S=4/15 mils and routing length less than 500 mils.

R401 24D9R2F-L-GPR401 24D9R2F-L-GP

1 2

PEG_RXN[0..15]

PEG_RXP[0..15]

2

1D05V_VTT

PEG_RXN[0..15] 60

NOTE.

If PEG is not implemented, the RX&TX pairs can be left as No Connect

PEG Static Lane Reversal

close to the processor

C421 SCD22U10V2KX-1GP

C421 SCD22U10V2KX-1GP

1 2

DIS

DIS

C422 SCD22U10V2KX-1GP

C422 SCD22U10V2KX-1GP

1 2

DIS

DIS

C423 SCD22U10V2KX-1GP

C423 SCD22U10V2KX-1GP

1 2

DIS

DIS

C424 SCD22U10V2KX-1GP

C424 SCD22U10V2KX-1GP

1 2

DIS

DIS

C425 SCD22U10V2KX-1GP

C425 SCD22U10V2KX-1GP

1 2

DIS

DIS

C426 SCD22U10V2KX-1GP

C426 SCD22U10V2KX-1GP

1 2

DIS

DIS

C427 SCD22U10V2KX-1GP

C427 SCD22U10V2KX-1GP

1 2

DIS

DIS

C428 SCD22U10V2KX-1GP

C428 SCD22U10V2KX-1GP

1 2

DIS

DIS

C429 SCD22U10V2KX-1GP

C429 SCD22U10V2KX-1GP

1 2

DIS

DIS

C430 SCD22U10V2KX-1GP

C430 SCD22U10V2KX-1GP

1 2

DIS

DIS

C431 SCD22U10V2KX-1GP

C431 SCD22U10V2KX-1GP

1 2

DIS

DIS

C432 SCD22U10V2KX-1GP

C432 SCD22U10V2KX-1GP

1 2

DIS

DIS

C433 SCD22U10V2KX-1GP

C433 SCD22U10V2KX-1GP

1 2

DIS

DIS

C434 SCD22U10V2KX-1GP

C434 SCD22U10V2KX-1GP

1 2

DIS

DIS

C435 SCD22U10V2KX-1GP

C435 SCD22U10V2KX-1GP

1 2

DIS

DIS

C436 SCD22U10V2KX-1GP

C436 SCD22U10V2KX-1GP

1 2

DIS

DIS

C437 SCD22U10V2KX-1GP

C437 SCD22U10V2KX-1GP

1 2

DIS

DIS

C438 SCD22U10V2KX-1GP

C438 SCD22U10V2KX-1GP

1 2

DIS

DIS

C439 SCD22U10V2KX-1GP

C439 SCD22U10V2KX-1GP

1 2

DIS

DIS

C440 SCD22U10V2KX-1GP

C440 SCD22U10V2KX-1GP

1 2

DIS

DIS

C441 SCD22U10V2KX-1GP

C441 SCD22U10V2KX-1GP

1 2

DIS

DIS

C442 SCD22U10V2KX-1GP

C442 SCD22U10V2KX-1GP

1 2

DIS

DIS

C443 SCD22U10V2KX-1GP

C443 SCD22U10V2KX-1GP

1 2

DIS

DIS

C444 SCD22U10V2KX-1GP

C444 SCD22U10V2KX-1GP

1 2

DIS

DIS

C445 SCD22U10V2KX-1GP

C445 SCD22U10V2KX-1GP

1 2

DIS

DIS

C446 SCD22U10V2KX-1GP

C446 SCD22U10V2KX-1GP

1 2

DIS

DIS

C447 SCD22U10V2KX-1GP

C447 SCD22U10V2KX-1GP

1 2

DIS

DIS

C448 SCD22U10V2KX-1GP

C448 SCD22U10V2KX-1GP

1 2

DIS

DIS

C449 SCD22U10V2KX-1GP

C449 SCD22U10V2KX-1GP

1 2

DIS

DIS

C450 SCD22U10V2KX-1GP

C450 SCD22U10V2KX-1GP

1 2

DIS

DIS

C451 SCD22U10V2KX-1GP

C451 SCD22U10V2KX-1GP

1 2

DIS

DIS

C452 SCD22U10V2KX-1GP

C452 SCD22U10V2KX-1GP

1 2

DIS

DIS

PEG_TXN15

PEG_TXN14

PEG_TXN13

PEG_TXN12

PEG_TXN11

PEG_TXN10

PEG_TXN9

PEG_TXN8

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP15

PEG_TXP14

PEG_TXP13

PEG_TXP12

PEG_TXP11

PEG_TXP10

PEG_TXP9

PEG_TXP8

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

PEG_RXP[0..15] 60

PEG_TXN[0..15]

PEG_TXP[0..15]

1

PEG_TXN[0..15] 60

PEG_TXP[0..15] 60

N12M GS2 HYN1GB

N12M GS2 HYN1GB

A A

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (PCIE/DMI/FDI)

CPU (PCIE/DMI/FDI)

CPU (PCIE/DMI/FDI)

Taipei Hsien 221, Taiwan, R.O.C.

4 74

4 74

4 74

-1

-1

-1

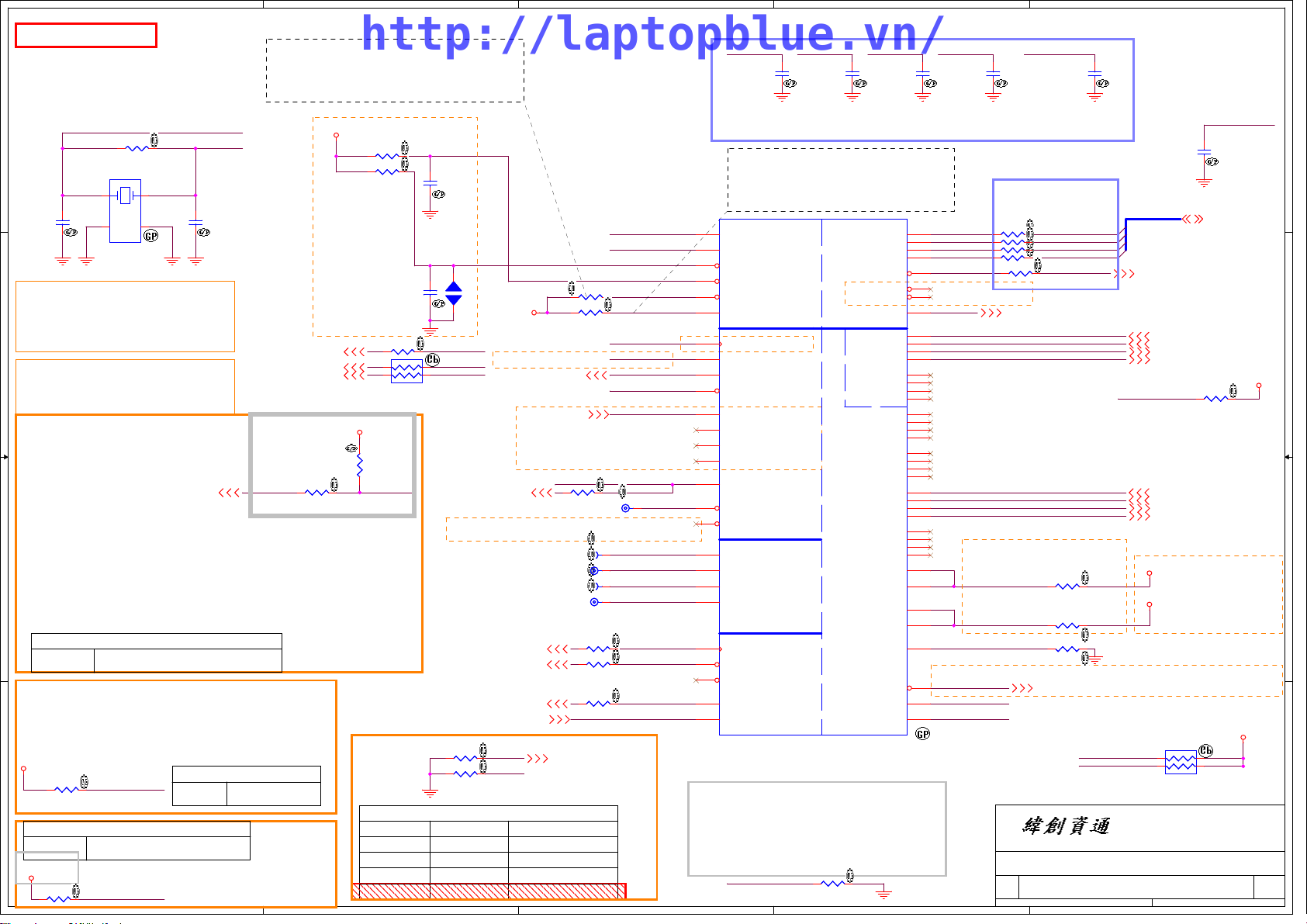

SSID = CPU

DMI & FDI Termination Voltage

NV_CLE

Set to Vss when LOW

Set to Vcc when HIGH

D D

H_PROCHOT#23,35

Connect EC to PROCHOT# through inverting OD buffer.

C C

B B

1D05V_VTT

H_PM_SYNC15

H_CPUPW RGD18,69

close to the processor

PM_DRAM_PWRGD15,30

VDDPWRGOOD30

1D05V_VTT

PLT_RST#14,22,23,26,27,51,55,60,69

Buffered reset to CPU

PLT_RST#14,22,23,26,27,51,55,60,69

+V_NVRAM_VCCQ

H_SNB_IVB#14

H_PECI18,23

R501

R501

1 2

62R2J-GP

62R2J-GP

NO_S3

NO_S3

R510

R510

1 2

1K5R2F-2-GP

1K5R2F-2-GP

U501

U501

NC#11VCC

2

A

3

GND

Do Not Stuff

Do Not Stuff

DY

DY

TP501Do Not Stuff TP501Do Not Stuff

TP502Do Not Stuff TP502Do Not Stuff

close to the processor

1 2

2K2R2J-2-GP

2K2R2J-2-GP

1

1

close to the processor

1 2

56R2J-4-GP

56R2J-4-GP

63.56034.1DL

63.56034.1DL

H_THERMTRIP#18,22

1D05V_VTT

1 2

Do Not Stuff

Do Not Stuff

R503

R503

1 2

10KR2J-3-GP

10KR2J-3-GP

1 2

NO_S3

NO_S3

Do Not Stuff

Do Not Stuff

R521

R521

1 2

Do Not Stuff

Do Not Stuff

1D05V_VTT

12

R514

R514

Do Not Stuff

Do Not Stuff

DY

DY

5

4

Y

R517

R517

R516

R516

R524

R524

R504

R504

12

R523

R523

56R2J-4-GP

56R2J-4-GP

R509

R509

750R2F-GP

750R2F-GP

3D3V_S0

Do Not Stuff

Do Not Stuff

5

4

CPU1B

CPU1B

SANDY

http://laptopblue.vn/

C26

SKTOCC#_R

H_CATERR#

H_PROCHOT#_R

12

H_CPUPW RGD_R

VDDPWRGOOD

BUF_CPU_RST#

12

C501

C501

DY

DY

R515

R515

1 2

DY

DY

Do Not Stuff

Do Not Stuff

AN34

AL33

AN33

AL32

AN32

AM34

AP33

V8

AR33

ARRAN

ARRAN

62.10055.321

62.10055.321

BUF_CPU_RST#BUFO_CPU_RST#

12

R512

R512

Do Not Stuff

Do Not Stuff

DY

DY

SANDY

SNB_IVB#

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

CLOCKS

CLOCKS

DDR3

DDR3

JTAG & BPM

JTAG & BPM

3

2 OF 9

2 OF 9

BCLK

BCLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

MISC

MISC

PRDY#

PREQ#

TRST#

DBR#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

2

A28

A27

CLK_DP_P_R

A16

CLK_DP_N_R

A15

R502

R502

1 2

R8

SM_RCOMP_0

AK1

SM_RCOMP_1

A5

SM_RCOMP_2

A4

Signal Routing Guideline:

SM_RCOMP[0,1] keep W/S=20/20 mils and routing length less than 500 mils.

SM_RCOMP[2] keep W/S=15/20 mils and routing length less than 500 mils.

XDP_PRDY#

AP29

XDP_PREQ#

AP27

XDP_TCLK

AR26

TCK

TMS

TDI

TDO

AR27

AP30

AR28

AP26

AL35

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_DBRESET#

R506 140R2F-GPR506 140R2F-GP

R507 25D5R2F-GPR507 25D5R2F-GP

R508 200R2F-L-GPR508 200R2F-L-GP

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_BPM4

XDP_BPM5

XDP_BPM6

XDP_BPM7

SRN1KJ-7-GP

SRN1KJ-7-GP

DIS

DIS

2 3

1

RN503

RN503

4K99R2F-L-GP

4K99R2F-L-GP

1 2

1 2

1 2

3D3V_S0

CLK_EXP_P 16

CLK_EXP_N 16

4

12

R513

R513

1KR2J-1-GP

1KR2J-1-GP

EVT

1D05V_VTT

SM_DRAMRST# 30

EVT

Disabling Guidelines:

If motherboard only supports external graphics:

Connect DPLL_REF_SSCLK on Processor to GND through

1K +/- 5% resistor.

Connect DPLL_REF_SSCLK# on Processor to VCCP

through 1K +/- 5% resistorpower (~15 mW) may be

wasted.

XDP_TDI

XDP_TMS

XDP_TCLK

XDP_TRST#

XDP_TDO

【

RN501

RN501

1

2

3

4 5

Do Not Stuff

Do Not Stuff

RN502

RN502

1

2 3

SRN51J-GP

SRN51J-GP

1

CHKLST 0.9 P.53

1D05V_VTT

DY

DY

8

7

6

4

1D05V_VTT

】

XDP Test Point

XDP_PRDY#

XDP_PREQ#

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_BPM4

XDP_BPM5

XDP_BPM6

XDP_BPM7

1

1

1

1

1

1

1

1

1

1

TP12 Do Not StuffTP12 Do Not Stuff

TP13 Do Not StuffTP13 Do Not Stuff

TP14 Do Not StuffTP14 Do Not Stuff

TP15 Do Not StuffTP15 Do Not Stuff

TP18 Do Not StuffTP18 Do Not Stuff

TP16 Do Not StuffTP16 Do Not Stuff

TP19 Do Not StuffTP19 Do Not Stuff

TP20 Do Not StuffTP20 Do Not Stuff

TP21 Do Not StuffTP21 Do Not Stuff

TP22 Do Not StuffTP22 Do Not Stuff

N12M GS2 HYN1GB

N12M GS2 HYN1GB

A A

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (THERMAL/CLOCK/PM )

CPU (THERMAL/CLOCK/PM )

CPU (THERMAL/CLOCK/PM )

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Taipei Hsien 221, Taiwan, R.O.C.

5 74

5 74

5 74

-1

-1

-1

5

4

3

2

1

SSID = CPU

CPU1C

CPU1C

SANDY

SANDY

D D

C C

B B

M_A_DQ011

M_A_DQ111

M_A_DQ211

M_A_DQ311

M_A_DQ411

M_A_DQ511

M_A_DQ611

M_A_DQ711

M_A_DQ811

M_A_DQ911

M_A_DQ1011

M_A_DQ1111

M_A_DQ1211

M_A_DQ1311

M_A_DQ1411

M_A_DQ1511

M_A_DQ1611

M_A_DQ1711

M_A_DQ1811

M_A_DQ1911

M_A_DQ2011

M_A_DQ2111

M_A_DQ2211

M_A_DQ2311

M_A_DQ2411

M_A_DQ2511

M_A_DQ2611

M_A_DQ2711

M_A_DQ2811

M_A_DQ2911

M_A_DQ3011

M_A_DQ3111

M_A_DQ3211

M_A_DQ3311

M_A_DQ3411

M_A_DQ3511

M_A_DQ3611

M_A_DQ3711

M_A_DQ3811

M_A_DQ3911

M_A_DQ4011

M_A_DQ4111

M_A_DQ4211

M_A_DQ4311

M_A_DQ4411

M_A_DQ4511

M_A_DQ4611

M_A_DQ4711

M_A_DQ4811

M_A_DQ4911

M_A_DQ5011

M_A_DQ5111

M_A_DQ5211

M_A_DQ5311

M_A_DQ5411

M_A_DQ5511

M_A_DQ5611

M_A_DQ5711

M_A_DQ5811

M_A_DQ5911

M_A_DQ6011

M_A_DQ6111

M_A_DQ6211

M_A_DQ6311

M_A_BS011

M_A_BS111

M_A_BS211

M_A_CAS#11

M_A_RAS#11

M_A_WE#11

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

AE8

AD9

AF9

C5

SA_DQ0

D5

SA_DQ1

D3

SA_DQ2

D2

SA_DQ3

D6

SA_DQ4

C6

SA_DQ5

C2

SA_DQ6

C3

SA_DQ7

F10

SA_DQ8

F8

SA_DQ9

SA_DQ10

G9

SA_DQ11

F9

SA_DQ12

F7

SA_DQ13

G8

SA_DQ14

G7

SA_DQ15

K4

SA_DQ16

K5

SA_DQ17

K1

SA_DQ18

J1

SA_DQ19

J5

SA_DQ20

J4

SA_DQ21

J2

SA_DQ22

K2

SA_DQ23

M8

SA_DQ24

SA_DQ25

N8

SA_DQ26

N7

SA_DQ27

SA_DQ28

M9

SA_DQ29

N9

SA_DQ30

M7

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

AJ5

SA_DQ38

AJ6

SA_DQ39

AJ8

SA_DQ40

SA_DQ41

AJ9

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

V6

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

http://laptopblue.vn/

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

3 OF 9

3 OF 9

SA_CLK0

SA_CLK#0

SA_CKE0

SA_CLK1

SA_CLK#1

SA_CKE1

SA_CLK2

SA_CLK#2

SA_CKE2

SA_CLK3

SA_CLK#3

SA_CKE3

SA_CS#0

SA_CS#1

SA_CS#2

SA_CS#3

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

M_A_DQS#0M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DIM0_CLK_DDR0 11

M_A_DIM0_CLK_DDR#0 11

M_A_DIM0_CKE0 11

M_A_DIM0_CLK_DDR1 11

M_A_DIM0_CLK_DDR#1 11

M_A_DIM0_CKE1 11

M_A_DIM0_CS#0 11

M_A_DIM0_CS#1 11

M_A_DIM0_ODT0 11

M_A_DIM0_ODT1 11

M_A_DQS#0 11

M_A_DQS#1 11

M_A_DQS#2 11

M_A_DQS#3 11

M_A_DQS#4 11

M_A_DQS#5 11

M_A_DQS#6 11

M_A_DQS#7 11

M_A_DQS0 11

M_A_DQS1 11

M_A_DQS2 11

M_A_DQS3 11

M_A_DQS4 11

M_A_DQS5 11

M_A_DQS6 11

M_A_DQS7 11

M_A_A0 11

M_A_A1 11

M_A_A2 11

M_A_A3 11

M_A_A4 11

M_A_A5 11

M_A_A6 11

M_A_A7 11

M_A_A8 11

M_A_A9 11

M_A_A10 11

M_A_A11 11

M_A_A12 11

M_A_A13 11

M_A_A14 11

M_A_A15 11

4 OF 9

CPU1D

CPU1D

SANDY

M_B_DQ[63:0]12

M_B_DQ[63:0]

M_B_BS012

M_B_BS112

M_B_BS212

M_B_CAS#12

M_B_RAS#12

M_B_WE#12

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

D10

K10

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

C9

SB_DQ0

A7

SB_DQ1

SB_DQ2

C8

SB_DQ3

A9

SB_DQ4

A8

SB_DQ5

D9

SB_DQ6

D8

SB_DQ7

G4

SB_DQ8

F4

SB_DQ9

F1

SB_DQ10

G1

SB_DQ11

G5

SB_DQ12

F5

SB_DQ13

F2

SB_DQ14

G2

SB_DQ15

J7

SB_DQ16

J8

SB_DQ17

SB_DQ18

K9

SB_DQ19

J9

SB_DQ20

J10

SB_DQ21

K8

SB_DQ22

K7

SB_DQ23

M5

SB_DQ24

N4

SB_DQ25

N2

SB_DQ26

N1

SB_DQ27

M4

SB_DQ28

N5

SB_DQ29

M2

SB_DQ30

M1

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_BS0

SB_BS1

R6

SB_BS2

SB_CAS#

SB_RAS#

SB_WE#

SANDY

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

4 OF 9

SB_CLK0

SB_CLK#0

SB_CKE0

SB_CLK1

SB_CLK#1

SB_CKE1

SB_CLK2

SB_CLK#2

SB_CKE2

SB_CLK3

SB_CLK#3

SB_CKE3

SB_CS#0

SB_CS#1

SB_CS#2

SB_CS#3

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

AE2

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DIM0_CLK_DDR0 12

M_B_DIM0_CLK_DDR#0 12

M_B_DIM0_CKE0 12

M_B_DIM0_CLK_DDR1 12

M_B_DIM0_CLK_DDR#1 12

M_B_DIM0_CKE1 12

M_B_DIM0_CS#0 12

M_B_DIM0_CS#1 12

M_B_DIM0_ODT0 12

M_B_DIM0_ODT1 12

M_B_DQS#[7:0] 12

M_B_DQS[7:0] 12

M_B_A[15:0] 12

ARRAN

ARRAN

A A

5

4

3

ARRAN

ARRAN

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (DDR)

CPU (DDR)

CPU (DDR)

Taipei Hsien 221, Taiwan, R.O.C.

6 74

6 74

6 74

1

-1

-1

-1

5

SSID = CPU

CFG0

AK28

1

TP713Do Not Stuff TP713Do Not Stuff

CFG1

AK29

1

TP701Do Not Stuff TP701Do Not Stuff

CFG2

AL26

CFG3

1

CFG4

CFG5

CFG6

CFG7

CFG8

1

CFG9

1

CFG10

1

CFG11

1

CFG12

1

CFG13

1

CFG14

1

CFG15

1

CFG16

1

CFG17

1

H_VCCP_SEL

AL27

AK26

AL29

AL30

AM31

AM32

AM30

AM28

AM26

AN28

AN31

AN26

AM27

AK31

AN29

AJ31

AH31

AJ33

AH33

AJ26

D1

F25

F24

F23

D24

G25

G24

E23

D23

C30

A31

B30

B29

D30

B31

A30

C29

J20

B18

A19

J15

TP702Do Not Stuff TP702Do Not Stuff

TP703Do Not Stuff TP703Do Not Stuff

TP704Do Not Stuff TP704Do Not Stuff

D D

TP705Do Not Stuff TP705Do Not Stuff

TP706Do Not Stuff TP706Do Not Stuff

TP707Do Not Stuff TP707Do Not Stuff

TP708Do Not Stuff TP708Do Not Stuff

TP709Do Not Stuff TP709Do Not Stuff

TP710Do Not Stuff TP710Do Not Stuff

TP711Do Not Stuff TP711Do Not Stuff

TP712Do Not Stuff TP712Do Not Stuff

M3 - Processor Generated SO-DIMM VREF_DQ

B4:VREF_DQ CHA

D1:VREF_DQ CHB

M_VREF_DQ_D IMM0_C

4

1

RN701

RN701

SRN1KJ-7-G P

SRN1KJ-7-G P

2 3

M_VREF_DQ_D IMM1_C

R710

R710

1 2

DY

DY

Do Not Stuff

Do Not Stuff

EVT

C C

4

5 OF 9

CPU1E

CPU1E

http://laptopblue.vn/

SANDY

SANDY

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

RSVD#AJ31

RSVD#AH31

RSVD#AJ33

RSVD#AH33

RSVD#AJ26

B4

RSVD#B4

RSVD#D1

RSVD#F25

RSVD#F24

RSVD#F23

RSVD#D24

RSVD#G25

RSVD#G24

RSVD#E23

RSVD#D23

RSVD#C30

RSVD#A31

RSVD#B30

RSVD#B29

RSVD#D30

RSVD#B31

RSVD#A30

RSVD#C29

RSVD#J20

RSVD#B18

RSVD#A19

RSVD#J15

ARRAN

ARRAN

5 OF 9

L7

RSVD#L7

AG7

RSVD#AG7

AE7

RSVD#AE7

AK2

RSVD#AK2

W8

RSVD#W8

AT26

RSVD#AT26

AM33

RSVD#AM33

AJ27

RSVD#AJ27

T8

RSVD#T8

J16

RSVD#J16

H16

RSVD#H16

G16

RSVD#G16

AR35

RSVD#AR35

AT34

RSVD#AT34

AT33

RSVD#AT33

AP35

RSVD#AP35

RSVD#AR34

RSVD#B34

RSVD#A33

RSVD#A34

RSVD#B35

RSVD#C35

RESERVED

RESERVED

RSVD#AJ32

RSVD#AK32

RSVD#AH27

RSVD#AN35

RSVD#AM35

RSVD#AT2

RSVD#AT1

RSVD#AR1

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AH27

AN35

AM35

AT2

AT1

AR1

CPU_CORN ER1

CPU_CORN ER2

CLK_XDP_ITP_P

CLK_XDP_ITP_N

CPU_CORN ER3

1

1

1

1

1

TP716 Do Not StuffTP716 Do Not Stuff

TP717 Do Not StuffTP717 Do Not Stuff

TP715 Do Not StuffTP715 Do Not Stuff

TP714 Do Not StuffTP714 Do Not Stuff

TP718 Do Not StuffTP718 Do Not Stuff

3

PEG Static Lane Reversal

CFG[0]

CFG2

CFG4

CFG5

CFG6

12

R703

R703

Do Not Stuff

Do Not Stuff

DY

DY

12

R701

R701

1KR2J-1-GP

1KR2J-1-GP

DIS

DIS

12

R702

R702

Do Not Stuff

Do Not Stuff

DY

DY

12

R704

R704

Do Not Stuff

Do Not Stuff

DY

DY

PEG Static Lane Reversal

CFG2

Display Port Presence Strap

CFG4

PCIE Port Bifurcation Straps

CFG[6:5]

2

Connect a series 1K ohm resistor on the

critical CFG[0] trace in a manner which does

not introduce any stubs to CFG[0] trace. Route

as needed from the opposite side of this series

isolation resistor to the debug port. ITP will

drive the net to GND.

1: Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

1: Disabled; No Physical Display Port

attached to Embedded Display Port

Can float on Processor if eDP interface is

disabled

0: Enabled; An external Display Port device is

connected to the Embedded Display Port

11: x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

1

CFG7

B B

A A

5

4

3

12

R705

R705

Do Not Stuff

Do Not Stuff

DY

DY

PEG DEFER TRAINING

1: PEG Train immediately following xxRESETB de assertion

CFG7

0: PEG Wait for BIOS for training

2

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

21F, 88, Sec.1, Hsin T ai Wu Rd ., Hsichih,

Taipei Hsie n 221, Taiwan, R.O. C.

Taipei Hsie n 221, Taiwan, R.O. C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A2

A2

A2

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesd ay, March 02, 2011

Wednesd ay, March 02, 2011

Wednesd ay, March 02, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsie n 221, Taiwan, R.O. C.

CPU (RESERVED)

CPU (RESERVED)

CPU (RESERVED)

7 74

7 74

1

7 74

-1

-1

-1

5

SSID = CPU

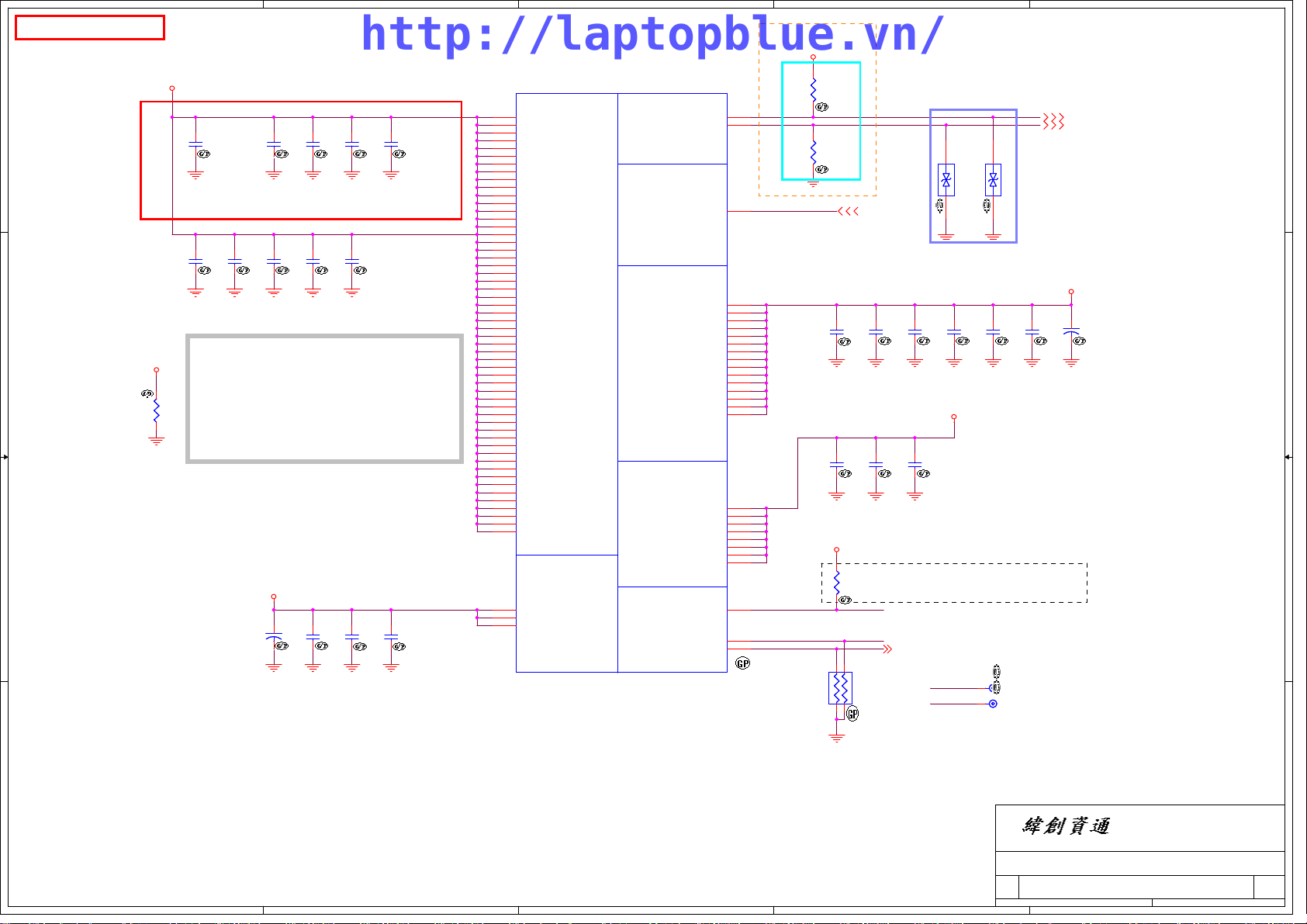

PROCESSOR CORE POWER

D D

C C

B B

A A

VCC_CORE

12

12

12

C802

C802

C801

C801

DY

DY

12

C820

C820

DY

DY

12

12

DY

DY

DY

DY

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

12

C819

C819

DY

DY

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

12

C821

C821

C816

C816

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C836

C836

C837

C837

Do Not Stuff

Do Not Stuff

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

5

12

C803

C803

DY

DY

Do Not Stuff

Do Not Stuff

12

C818

C818

DY

DY

Do Not Stuff

Do Not Stuff

12

C822

C822

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C835

C835

Do Not Stuff

Do Not Stuff

DY

DY

12

C804

C804

C811

C811

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

12

12

C817

C817

C815

C815

DY

DY

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

12

12

C823

C823

C824

C824

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C834

C834

C833

C833

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

DY

DY

12

C826

C826

C825

C825

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

12

C831

C831

C832

C832

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

4

POWER

CPU1F

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

CPU1F

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y35

VCC

Y34

VCC

Y33

VCC

Y32

VCC

Y31

VCC

Y30

VCC

Y29

VCC

Y28

VCC

Y27

VCC

Y26

VCC

V35

VCC

V34

VCC

V33

VCC

V32

VCC

V31

VCC

V30

VCC

V29

VCC

V28

VCC

V27

VCC

V26

VCC

U35

VCC

U34

VCC

U33

VCC

U32

VCC

U31

VCC

U30

VCC

U29

VCC

U28

VCC

U27

VCC

U26

VCC

R35

VCC

R34

VCC

R33

VCC

R32

VCC

R31

VCC

R30

VCC

R29

VCC

R28

VCC

R27

VCC

R26

VCC

P35

VCC

P34

VCC

P33

VCC

P32

VCC

P31

VCC

P30

VCC

P29

VCC

P28

VCC

P27

VCC

P26

VCC

ARRAN

ARRAN

http://laptopblue.vn/

VCC_CORE

53A

12

C827

C827

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C828

C828

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

4

POWER

SANDY

SANDY

CORE SUPPLY

CORE SUPPLY

SENSE LINES SVID

SENSE LINES SVID

3

PEG AND DDR

PEG AND DDR

VCC_SENSE

VCCIO_SENSE

VSSIO_SENSE

3

6 OF 9

6 OF 9

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VIDALERT#

VIDSCLK

VIDSOUT

VSS_SENSE

2

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

H_CPU_SVIDALRT#

AJ29

H_CPU_SVIDCLK

AJ30

H_CPU_SVIDDAT

AJ28

For CRB VIDSOUT need to pull high 130 ohm closr to CPU and IMVP7

For CRB VIDALERT# need to pull high 75 ohm close to CPU

1D05V_VTT

12

AJ35

AJ34

B10

A10

12

12

12

12

12

R804

R804

10R2F-L-GP

10R2F-L-GP

R805

R805

10R2F-L-GP

10R2F-L-GP

C806

C806

C805

C805

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

No-stuff sites outside the socket may be removed.

No-stuff sites inside the socket cavity need to remain.

12

C812

C812

C813

C813

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

R803 43R2J-GPR803 43R2J-GP

1 2

VCCIO_SENSE 38

VSSIO_SENSE 38

C807

C807

12

C814

C814

DY

DY

10R2F-L-GP

10R2F-L-GP

10R2F-L-GP

10R2F-L-GP

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

Do Not Stuff

Do Not Stuff

VCC_CORE

R801

R801

R802

R802

C808

C808

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C829

C829

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

2

12

C810

C810

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C842

C842

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

H_CPU_SVIDDAT

12

12

C838

C838

C839

C839

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

1D05V_VTT

12

12

C843

C843

C844

C844

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

R807 130R2F-1-GPR807 130R2F-1-GP

12

C809

C809

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C830

C830

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

VR_SVID_ALERT# 35

H_CPU_SVIDCLK 35

H_CPU_SVIDDAT 35

R801,R802 close to CPU

VCCSENSE 35

VSSSENSE 35

12

12

ED801

ED801

ED802

ED802

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

VARISTOR-5V-1-GP

VARISTOR-5V-1-GP

VARISTOR-5V-1-GP

VARISTOR-5V-1-GP

Title

Title

PVT

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

1D05V_VTT

12

12

12

1 2

C841

C841

C840

C840

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C845

C845

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

1

1D05V_VTT

1

8 74

8 74

8 74

-1

-1

-1

5

4

3

2

1

SSID = CPU

http://laptopblue.vn/

VCC_GFXCORE

D D

C C

B B

VCC_GFXCORE

Disabling Guidelines for External Graphics Designs:

Can connect to GND if motherboard only supports external

graphics and if GFX VR is not stuffed.

Can be left floating (Gfx VR keeps VAXG rail from floating)

if the VR is stuffed

R903

R903

0R3J-0-U-GP

0R3J-0-U-GP

DIS

DIS

1 2

12

UMA

UMA

12

UMA

UMA

C901

C901

C907

C907

20110117

PROCESSOR VAXG: 24A

12

12

C903

Do Not Stuff

Do Not Stuff

12

Do Not Stuff

Do Not Stuff

UMA

UMA

C903

Do Not Stuff

Do Not Stuff

UMA

UMA

UMA

UMA

12

C918

C918

C908

C908

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

DY

DY

EVT

20100910 Del R904,R905,R901

1D8V_S0

12

TC902

TC902

Do Not Stuff

Do Not Stuff

DY

DY

12

C904

C904

C905

C905

Do Not Stuff

Do Not Stuff

UMA

UMA

12

12

C919

C919

Do Not Stuff

Do Not Stuff

DY

DY

UMA

UMA

PROCESSOR VCCPLL: 1.2A

12

12

C923

C923

Do Not Stuff

Do Not Stuff

DY

DY

DY

DY

CPU1G

CPU1G

AT24

VAXG

AT23

VAXG

12

C906

C906

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

UMA

UMA

C920

C920

Do Not Stuff

Do Not Stuff

12

C922

C922

C924

C924

Do Not Stuff

Do Not Stuff

SC1U10V2KX-1GP

SC1U10V2KX-1GP

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

B6

VCCPLL

A6

VCCPLL

A2

VCCPLL

ARRAN

ARRAN

POWER

POWER

SANDY

SANDY

GRAPHICS

GRAPHICS

1.8V RAIL

1.8V RAIL

SENSE

SENSE

VREFMISC

VREFMISC

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

7 OF 9

7 OF 9

VAXG_SENSE

VSSAXG_SENSE

LINES

LINES

SM_VREF

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA_SENSE

FC_C22

VCCSA_VID1

R906,R907 close to CPU

VCC_GFXCORE

12

Do Not Stuff

Do Not Stuff

UMA

AK35

AK34

AL1

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

+V_SM_VREF_CNT

UMA

12

Do Not Stuff

Do Not Stuff

UMA

UMA

Routing Guideline:

Power from DDR_VREF_S3 and +V_SM_VREF_CNT

should have 10 mils trace width.

PROCESSOR VCCSA: 6A

M27

M26

L26

J26

J25

J24

H26

H25

H23

C22

C24

VCCSA_SENSE

H_FC_C22

VCCSA_SEL

RN901

RN901

SRN10KJ-5-GP

SRN10KJ-5-GP

0D85V_S0

R906

R906

DVT

R907

R907

+V_SM_VREF_CNT 30

PROCESSOR VDDQ: 10A

12

12

C909

C909

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

12

C916

C916

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

R902

R902

R902 need be close to pin H23.

10R2J-2-GP

10R2J-2-GP

1

23

4

Refer to the latest Huron River Mainstream PDG

(Doc# 436735) for more details on S3 power

reduction implementation.

+V_SM_VREF_CNT should have 10 mil trace width

VCC_AXG_SENSE 35

VSS_AXG_SENSE 35

PVT

12

ED902

ED902

VARISTOR-5V-1-GP

C912

C912

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1

1

VARISTOR-5V-1-GP

12

12

C913

C913

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

TP901 Do Not StuffTP901 Do Not Stuff

TP902 Do Not StuffTP902 Do Not Stuff

1D5V_DDR_S0

12

C914

C914

DY

DY

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

VARISTOR-5V-1-GP

VARISTOR-5V-1-GP

12

VCCSA Output Decoupling Recommendation:

1 x 330 uF

2 x 10 uF at Bottom Socket Cavity

1 x 10 uF at Bottom Socket Edge

12

C910

C910

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C915

C915

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

VCCSA_SEL 41

12

ED901

ED901

C911

C911

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

0D85V_S0

C917

C917

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

H_FC_C22

VCCSA_SENSE

TC901

TC901

Do Not Stuff

Do Not Stuff

A A

5

4

3

2

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (VCC_GFXCORE)

CPU (VCC_GFXCORE)

CPU (VCC_GFXCORE)

Taipei Hsien 221, Taiwan, R.O.C.

9 74

9 74

9 74

1

-1

-1

-1

5

4

3

2

1

SSID = CPU

CPU1H

CPU1H

AT35

VSS

AT32

VSS

AT29

VSS

AT27

VSS

AT25

VSS

AT22

VSS

D D

C C

B B

AT19

AT16

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

http://laptopblue.vn/

SANDY

SANDY

VSS

VSS

8 OF 9

8 OF 9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH26

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

M34

G35

G32

G29

G26

G23

G20

G17

G11

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

K35

K32

K29

K26

H33

H30

H27

H24

H21

H18

H15

H13

H10

F34

F31

F29

9 OF 9

CPU1I

CPU1I

T35

VSS

T34

VSS

T33

VSS

T32

VSS

T31

VSS

T30

VSS

T29

VSS

T28

VSS

T27

VSS

T26

VSS

P9

VSS

P8

VSS

P6

VSS

P5

VSS

P3

VSS

P2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L33

VSS

L30

VSS

L27

VSS

L9

VSS

L8

VSS

L6

VSS

L5

VSS

L4

VSS

L3

VSS

L2

VSS

L1

VSS

VSS

VSS

VSS

VSS

J34

VSS

J31

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H9

VSS

H8

VSS

H7

VSS

H6

VSS

H5

VSS

H4

VSS

H3

VSS

H2

VSS

H1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SANDY

SANDY

VSS

VSS

9 OF 9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

CPU_CORNER4

R1001 Do Not Stuff

R1001 Do Not Stuff

1 2

DY

DY

1

TP719 Do Not StuffTP719 Do Not Stuff

ARRAN

ARRAN

A A

5

4

3

ARRAN

ARRAN

N12M GS2 HYN1GB

N12M GS2 HYN1GB

N12M GS2 HYN1GB

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Z50-HR { Huron River Platform}

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Wednesday, March 02, 2011

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (VSS)

CPU (VSS)

CPU (VSS)

Taipei Hsien 221, Taiwan, R.O.C.

10 74

10 74

10 74

1

-1

-1

-1

5

DDR_VREF_S3

D D

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

C1425

C1425

DDR_VREF_S3

SCD1U10V2KX-5GP

Do Not Stuff

Do Not Stuff

12

12

C1423

C1423

DY

DY

C1424

C1424

EVT Del R1401

Do Not Stuff

Do Not Stuff

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

C1411

C1411

C C

0D75V_S0

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C1419

C1419

SA0_DIM0

SA1_DIM0

B B

A A

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

12

12

C1412

C1412

C1413

C1413

DY

DY

Do Not Stuff

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

Do Not Stuff

C1421

C1421

12

1

4

5

C1418

C1418

DY

DY

23

SRN10KJ-5-GP

SRN10KJ-5-GP

RN1401

RN1401

3D3V_S0

12

1D5V_S3

M_A_DIM0_CLK_DDR06

M_A_DIM0_CLK_DDR#06

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

Do Not Stuff

Do Not Stuff

12

12

C1401

C1401

C1402

C1402

DY

DY

4

SA0_DIM0

SA1_DIM0

4

DDR_VREF_S3

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ8

M_A_DQ9

M_A_DQS#1

M_A_DQS1

M_A_DQ10

M_A_DQ11

M_A_DQ16

M_A_DQ17

M_A_DQS#2

M_A_DQS2

M_A_DQ18

M_A_DQ19

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_BS2

M_A_A12

M_A_A9

M_A_A8

M_A_A5

M_A_A3

M_A_A1

M_A_A10

M_A_BS0

M_A_WE#

M_A_CAS#

M_A_A13

M_A_DQ32

M_A_DQ33

M_A_DQS#4

M_A_DQS4

M_A_DQ34

M_A_DQ35

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ48

M_A_DQ49

M_A_DQS#6

M_A_DQS6

M_A_DQ50

M_A_DQ51

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

0D75V_S0

http://laptopblue.vn/

M_A_DQ06

M_A_DQ16

M_A_DQ26

M_A_DQ36

M_A_DQ86

M_A_DQ96

M_A_DQS#16

M_A_DQS16

M_A_DQ106

M_A_DQ116

M_A_DQ166

M_A_DQ176

M_A_DQS#26

M_A_DQS26

M_A_DQ186

M_A_DQ196

M_A_DQ246

M_A_DQ256

M_A_DQ266

M_A_DQ276

M_A_DIM0_CKE06

M_A_BS26

M_A_A126

M_A_A96

M_A_A86

M_A_A56

M_A_A36

M_A_A16

M_A_A106

M_A_BS06

M_A_WE#6

M_A_CAS#6

M_A_A136

M_A_DIM0_CS#16

M_A_DQ326

M_A_DQ336

M_A_DQS#46

M_A_DQS46

M_A_DQ346

M_A_DQ356

M_A_DQ406

M_A_DQ416

M_A_DQ426

M_A_DQ436

M_A_DQ486

M_A_DQ496

M_A_DQS#66

M_A_DQS66

M_A_DQ506

M_A_DQ516

M_A_DQ566

M_A_DQ576

M_A_DQ586

M_A_DQ596

DM1

DM1

NP1

205

1

3

2

5

4

7

6

9

8

11

10

13

12

15

14

17

16

19

18

21

20

23

22

25

24

27

26

29

28

31

30

33

32

35

34

37

36

39

38

41

40

43

42

45

44

47

46

49

48

51

50

53

52

55

54

57

56

59

58

61

60

63

62

65

64

67

66

69

68

71

70

72

73

75