Sony LCX019AM Datasheet

Description

The LCX019AM is a 3.4cm diagonal active matrix

TFT-LCD panel addressed by polycrystalline silicon

super thin film transistors with built-in peripheral

driving circuit. This panel allows full-color

representation without color filters through the use of

a microlens.

This panel has an aspect ratio of 4:3 and supports

NTSC/PAL display.

This panel has a polysilicon TFT high-speed

scanner and built-in function to display images

up/down and/or right/left inverse. The built-in 5V

interface circuit leads to lower voltage of timing and

control signals.

Features

• The number of active dots: 576,000 (1.32-inch; 3.4cm in diagonal)

• Horizontal resolution: 600TV lines

• Effective aperture ratio: 70% (reference value)

• High contrast ratio with normally white mode: 200 (typ.)

• Built-in H and V drivers (built-in input level conversion circuit, 5V driving possible)

• Supports NTSC

(PAL mode also available through conversion of scanned dot numbers by an external IC)

• Up/down and/or right/left inverse display function

Element Structure

• Dots: 1199.5 (H) × 480 (V) = 575,760

• Built-in peripheral driver using polycrystalline silicon super thin film transistors.

Applications

Liquid crystal projectors, etc.

– 1 –

LCX019AM

E97106A94-PS

3.4cm (1.32-inch) LCD Panel (with microlens)

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

For the availability of this product, please contact the sales office.

– 2 –

LCX019AM

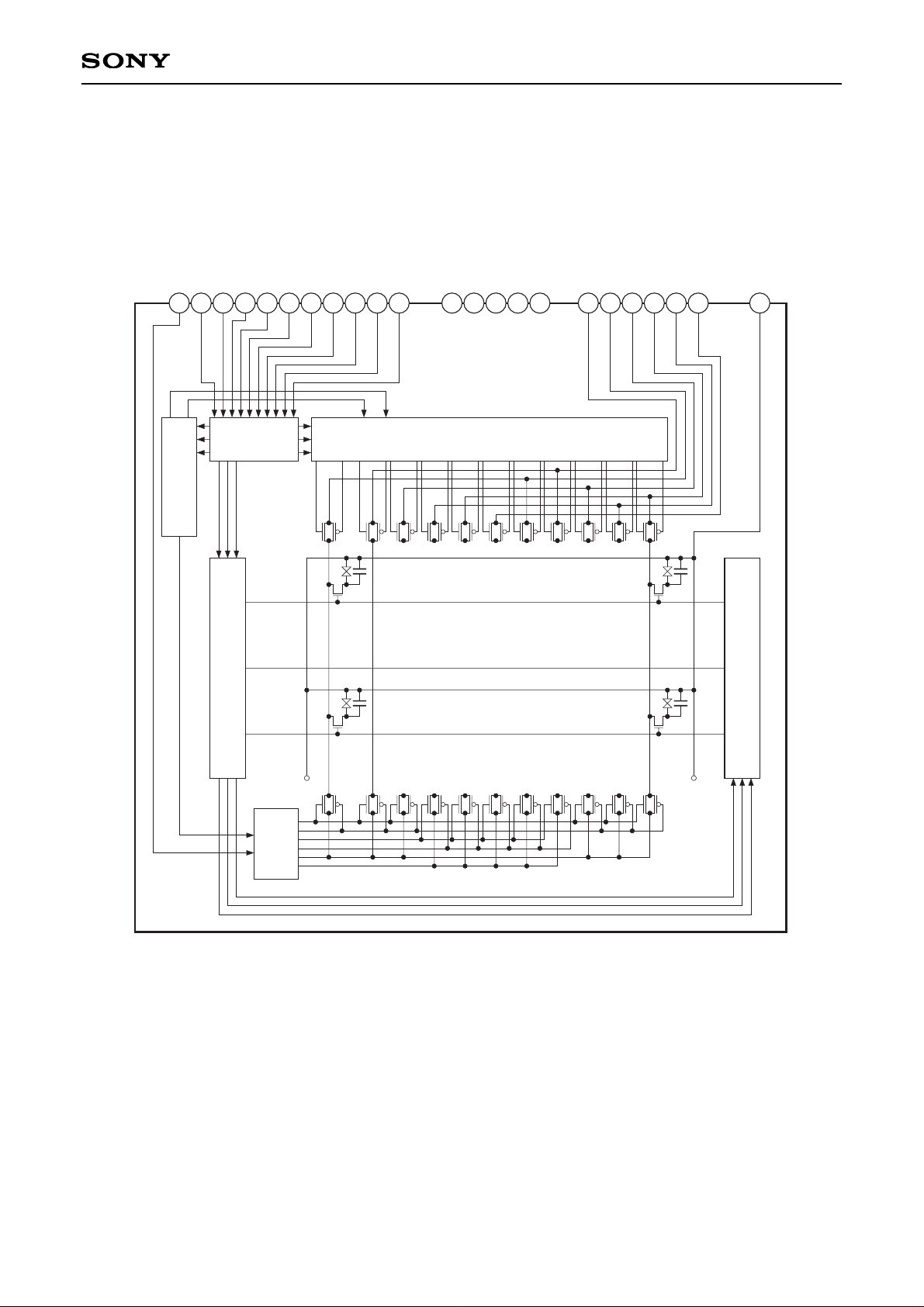

Block Diagram

Mode Controller

Level

Shifter

Bi-directional H Driver

Bi-directional V Driver

Bi-directional V Driver

2

3

4

5

6

7

8

9

10

11

12

13

14 15

16

17

18

19

20

21

22

23

1

VCOM

Precharge

Controller

PSIG

HST

HCK1

HCK2

N.C.

RGT

VST

VCK

PCG

DWN

ENB

AV

DD

HV

DD

VV

DD

V

SS

V

SS

G

SIG6 (B2)

SIG5 (R2)

SIG4 (G2)

SIG3 (B1)

SIG2 (R1)

SIG1 (G1)

COM

– 3 –

LCX019AM

Absolute Maximum Ratings (VSS = 0V)

• H driver supply voltage HVDD –1.0 to +20 V

• V driver supply voltage VVDD –1.0 to +20 V

• Analog block drive supply voltage AVDD –1.0 to +20 V

• Common pad voltage COM –1.0 to +17 V

• H shift register input pin voltage HST, HCK1, HCK2 –1.0 to +17 V

RGT

• V shift register input pin voltage VST, VCK, PCG –1.0 to +17 V

ENB, DWN

• Video signal input pin voltage SIG1, SIG2, SIG3, SIG4 –1.0 to +15 V

SIG5, SIG6, PSIG

• Operating temperature Topr –10 to +70 °C

• Storage temperature Tstg –30 to +85 °C

Operating Conditions (VSS = 0V)

• Supply voltage

HVDD 13.5 ± 0.3 V

VVDD 13.5 ± 0.3 V

AVDD 15.5 ± 0.3 V

• Input pulse voltage (Vp-p of all input pins except video signal and side black signal input pins)

Vin 5.0 ± 0.5 V

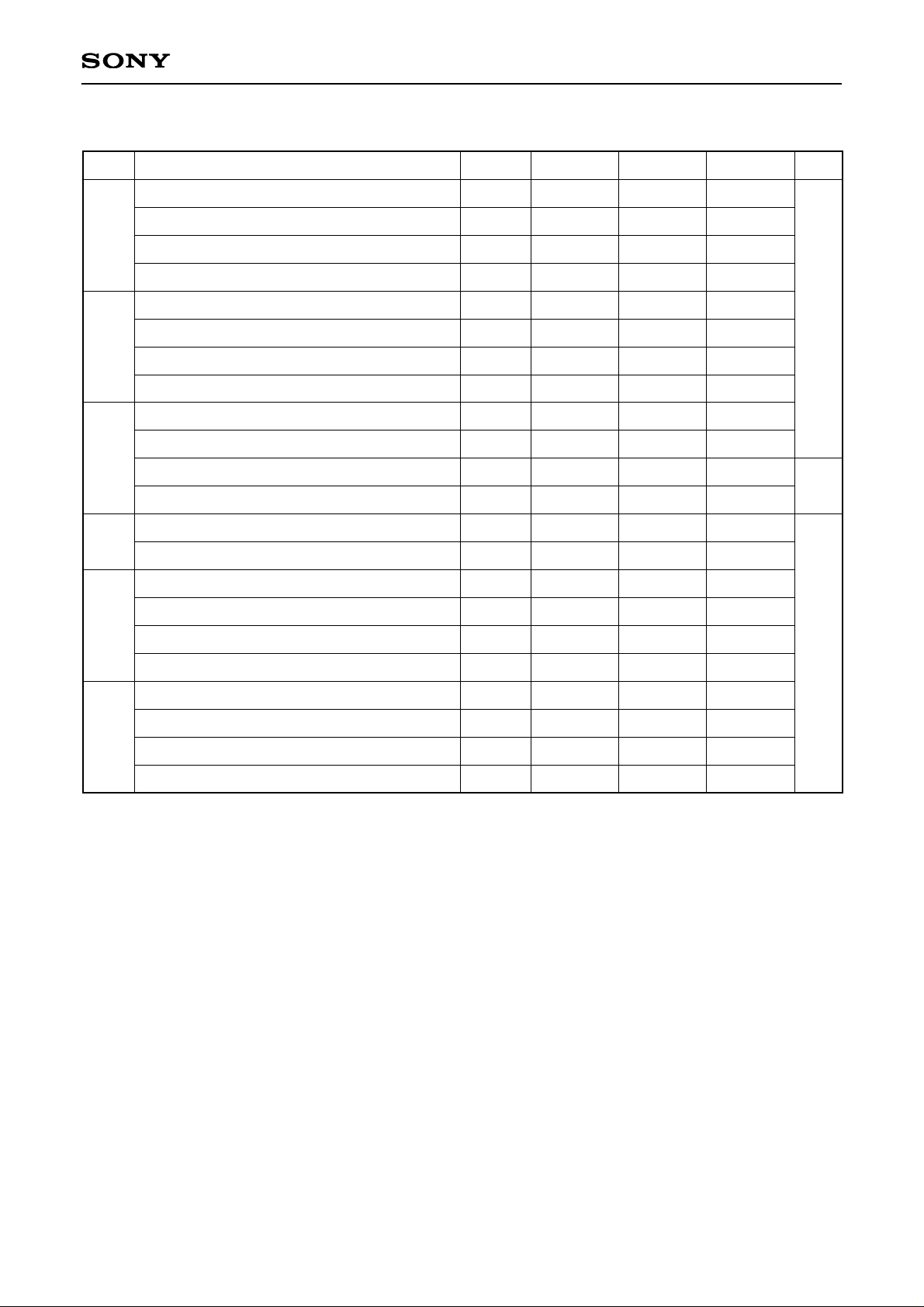

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

COM

VSSG

PSIG

SIG1 (G1)

SIG2 (R1)

SIG3 (B1)

SIG4 (G2)

SIG5 (R2)

SIG6 (B2)

AVDD

HVDD

N.C.

13

14

15

16

17

18

19

20

21

22

23

24

RGT

HST

HCK1

HCK2

VSS

ENB

VCK

VST

DWN

PCG

VVDD

TEST

Drive direction pulse for H shift

register (H: normal, L: reverse)

Start pulse for H shift register

drive

Clock pulse for H shift register

drive

Clock pulse for H shift register

drive

GND (H, V drivers)

Enable pulse for gate selection

Clock pulse for V shift register

drive

Start pulse for V shift register

drive

Drive direction pulse for V shift

register (H: normal, L: reverse)

Improvement pulse (2) for

uniformity

Power supply for V driver

Test; Open

Common voltage of panel

Analog block GND

Improvement pulse for uniformity

Video signal 1 (G) to panel

Video signal 2 (R) to panel

Video signal 3 (B) to panel

Video signal 4 (G) to panel

Video signal 5 (R) to panel

Video signal 6 (B) to panel

Analog block power supply

Power supply for H driver

Symbol Description

Pin

No.

Symbol Description

– 4 –

LCX019AM

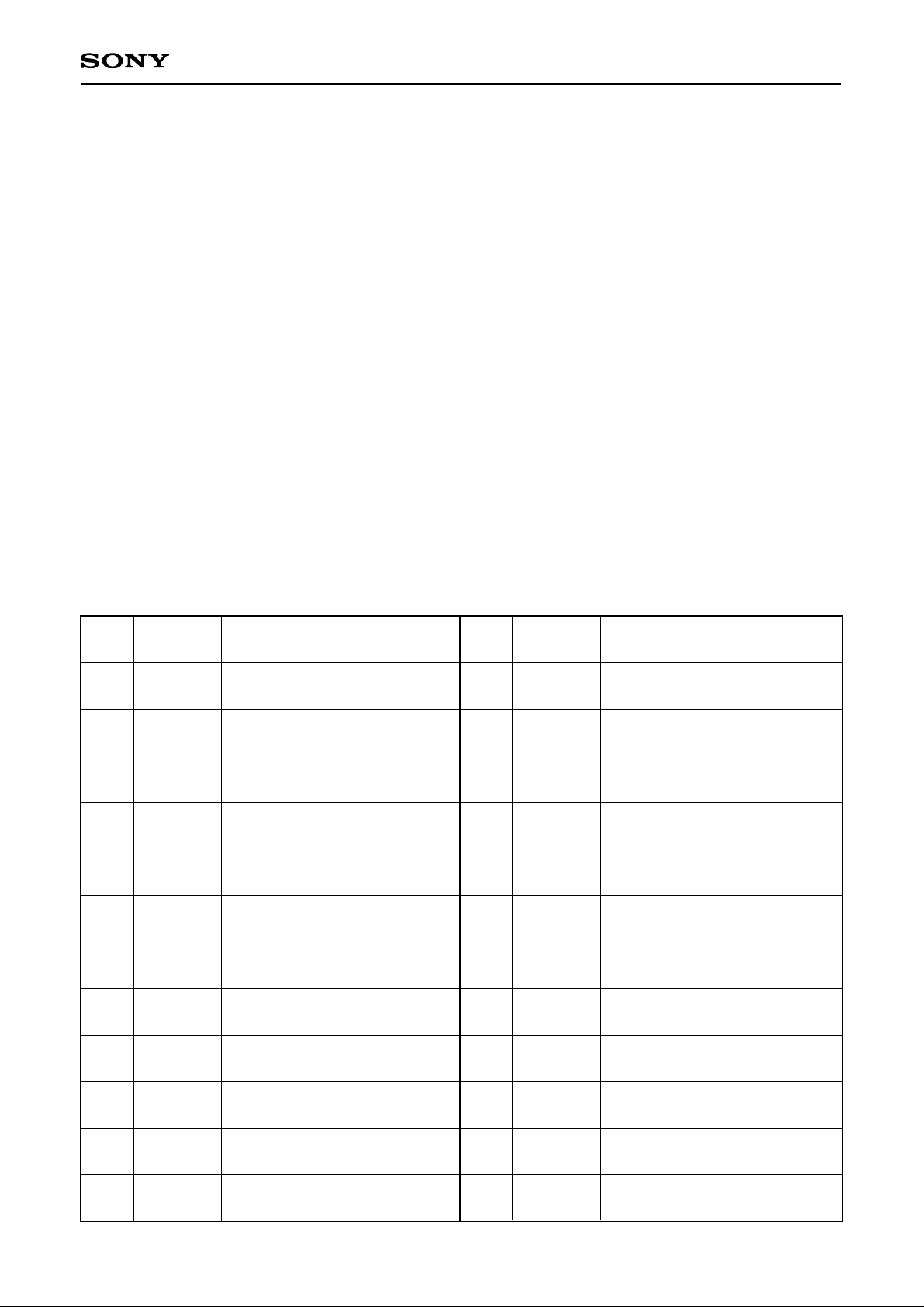

Input Equivalent Circuit

To prevent static charges, protective diodes are provided for each pin except the power supply. In addition,

protective resistors are added to all pins except video signal input. All pins are connected to VSS with a high

resistance of 1MΩ (typ.). The equivalent circuit of each input pin is shown below: (The resistor value: typ.)

Input

LC

Level conversion circuit

(single-phase input)

2.5kΩ2.5kΩ

VV

DD

Input

Level conversion circuit

(single-phase input)

250Ω250Ω

HV

DD

Input

Level conversion circuit

(single-phase input)

2.5kΩ2.5kΩ

HV

DD

Input

HV

DD

250Ω

250Ω

250Ω

250Ω

Level conversion circuit

(2-phase input)

Input

HV

DD

Signal line

(1) SIG1, SIG2, SIG3, SIG4, SIG5, SIG6, PSIG

(2) HCK1, HCK2

(3) RGT

(4) HST

(5) PCG, VCK

(6) VST, ENB, DWN

(7) COM

1MΩ

Input

1MΩ

1MΩ

1MΩ

1MΩ

Level conversion circuit

(single-phase input)

250Ω250Ω

VV

DD

Input

1MΩ

1MΩ

1MΩ

VVDD

VSS VSS

VSS

VSS

VSS

VSS

VSS

VSS

– 5 –

LCX019AM

Input Signals

1. Input signal voltage conditions (Vss = 0V)

Item

H driver input voltage

RGT, HST, HCK1, HCK2

(Low)

(High)

(Low)

(High)

VHIL

VHIH

VVIL

VVIH

VVC

Vsig

Vcom

Vpsig

–0.5

4.5

–0.5

4.5

6.8

VVC – 4.5

VVC – 0.3

VVC ± 3.4

0.0

5.0

0.0

5.0

7.0

—

VVC – 0.2

VVC ± 3.5

0.3

5.5

0.3

5.5

7.2

VVC + 4.5

VVC – 0.1

VVC ± 3.6

V

V

V

V

V

V

V

V

V driver input voltage

ENB, VCK, PCG, VST, DWN

Video signal center voltage

Video signal input range∗1(SIG1 to 6)

Common voltage of panel

∗2

Uniformity improvement signal input

(PSIG)

∗3

Symbol Min. Typ. Max. Unit

∗1

Video input signal shall be symmetrical to VVC.

∗2

Common voltage of the panel shall be adjusted to VVC – 0.2 V.

∗3

The uniformity improvement signal PSIG shall be input with the same polarity as video signals SIG1 to 6

and symmetrically with respect to VVC. Also, the PSIG rise and fall shall be synchronized with the PCG

pulse rise and the time between the rise trPSIG and fall tfPSIG shall be kept to 800ns or less. (See the

figure below.)

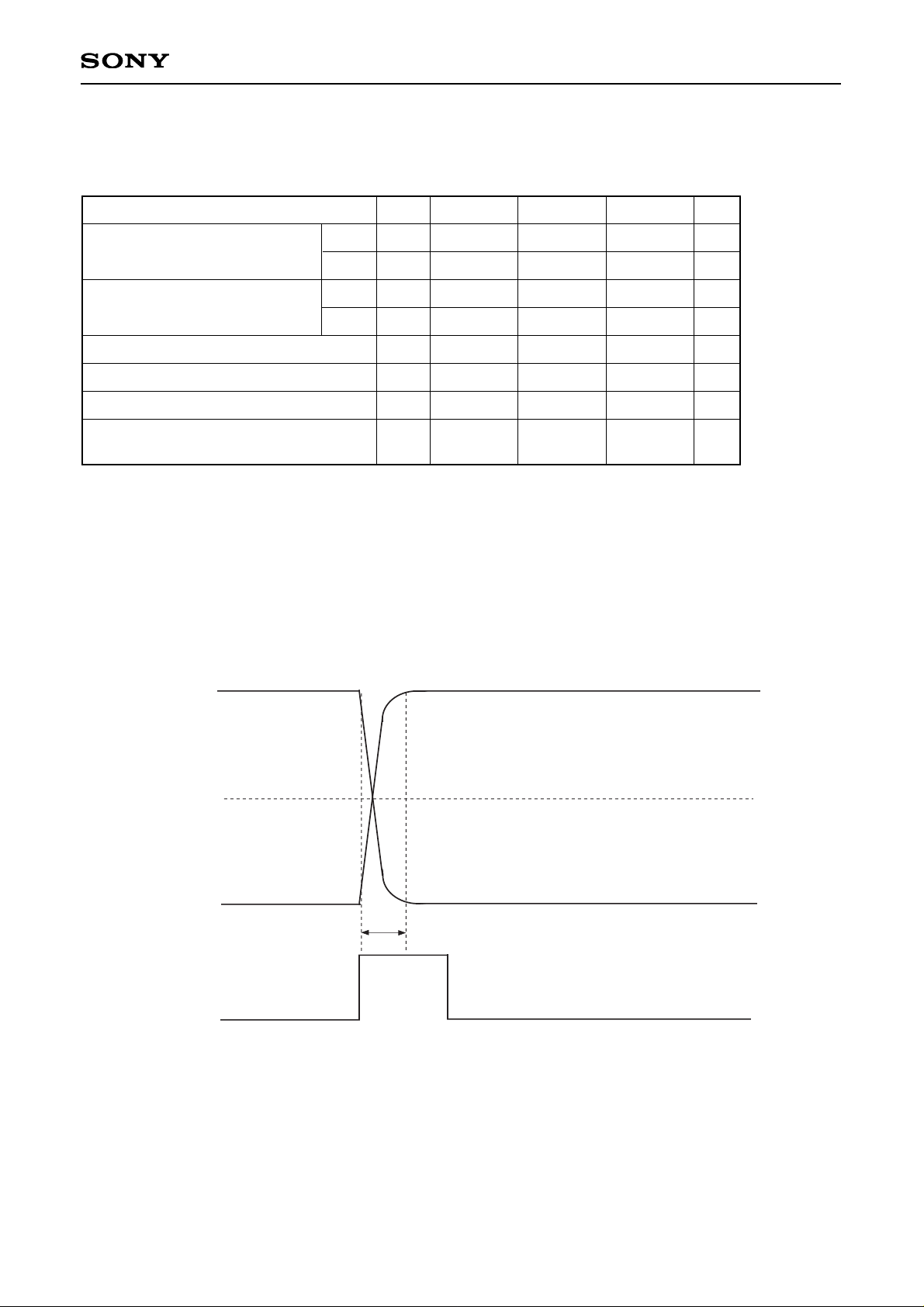

Uniformity Improvement Signal PSIG Input Waveform

Level Conversion Circuit

The LCX019AM has a built-in level conversion circuit in the clock input unit on the panel. The input signal level

increases to HVDD or VVDD. The VCC of external ICs are applicable to 5 ± 0.5V.

trPSIG

tfPSIG

VVC

PSIG

PCG

90%

10%

– 6 –

LCX019AM

2. Clock timing conditions (Ta = 25°C) (fHCKn = 3.82MHz, fVCK = 15.7kHz)

Hst rise time

Hst fall time

Hst data set-up time

Hst data hold time

Hckn∗4rise time

Hckn∗4fall time

Hck1 fall to Hck2 rise time

Hck1 rise to Hck2 fall time

Vst rise time

Vst fall time

Vst data set-up time

Vst data hold time

Vck rise time

Vck fall time

Enb rise time

Enb fall time

Vck rise/fall to Enb rise time

Enb pulse width

Pcg rise time

Pcg fall time

Pcg fall to Vck rise/fall time

Pcg pulse width

trHst

tfHst

tdHst

thHst

trHckn

tfHckn

to1Hck

to2Hck

trVst

tfVst

tdVst

thVst

trVck

tfVck

trEnb

tfEnb

tdEnb

twEnb

trPcg

tfPcg

toVck

twPcg

—

—

–15

116

—

—

–15

–15

—

—

5

5

—

—

—

—

350

3450

—

—

250

1750

—

—

0

131

—

—

0

0

—

—

15

15

—

—

—

—

400

3500

—

—

300

1800

30

30

15

146

30

30

15

15

100

100

25

25

100

100

100

100

450

3550

20

20

350

1850

ns

µs

ns

Item Symbol Min. Typ. Max. Unit

HST

HCK

VST

VCK

ENB

PCG

∗4

Hckn means Hck1 and Hck2.

– 7 –

LCX019AM

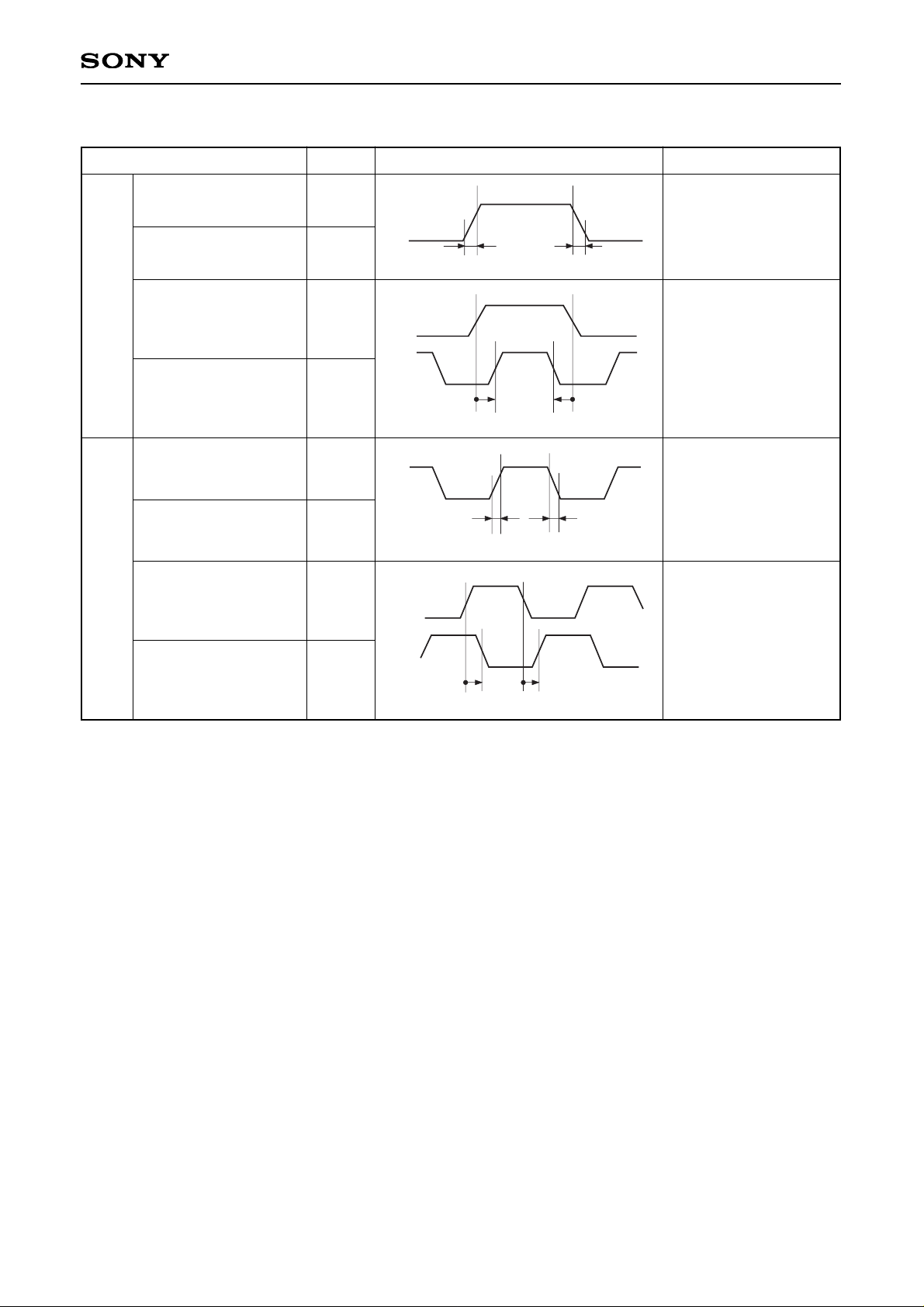

<Horizontal Shift Register Driving Waveform>

Hst rise time

HST

HCK

Hst fall time

Hst data set-up time

Hst data hold time

Hckn∗4rise time

Hckn∗4fall time

Hck1 fall to Hck2 rise

time

Hck1 rise to Hck2 fall

time

• Hckn

∗4

duty cycle 50%

to1Hck = 0ns

to2Hck = 0ns

• Hckn

∗4

duty cycle 50%

to1Hck = 0ns

to2Hck = 0ns

• Hckn

∗4

duty cycle 50%

to1Hck = 0ns

to2Hck = 0ns

trHst

tfHst

tdHst

thHst

trHckn

tfHckn

to1Hck

to2Hck

Item Symbol Waveform Conditions

90%

10%

10%

90%

Hst

trHst tfHst

50%

50%

∗

5

Hst

Hck1

tdHst thHst

50%

50%

∗

4

Hckn

10%

10%

90%

90%

trHckn tfHckn

50%

50%

∗

5

Hck1

to2Hck to1Hck

50%

50%

Hck2

Loading...

Loading...