SONY KDL-26P3000, KDL-32P3000, KDL-37P3000, KDL-40P3000, KDL-26P300H Service manual

...

HISTORY

Model Name :

SERVICE MANUAL

Click on Page Number to display detail of changes.

KDL-26/32/37/40P3000 & KDL-26/32/37/40P300H

Date Part Number Description of Revisions

Version

1.09-927-574-01 2007.10

Original Manual.

2.0

9-927-574-02 2007.11

Amendments to the exploded views

(P74-77) and

addition of full size schematic diagrams (Full).

- 1 -

SE2

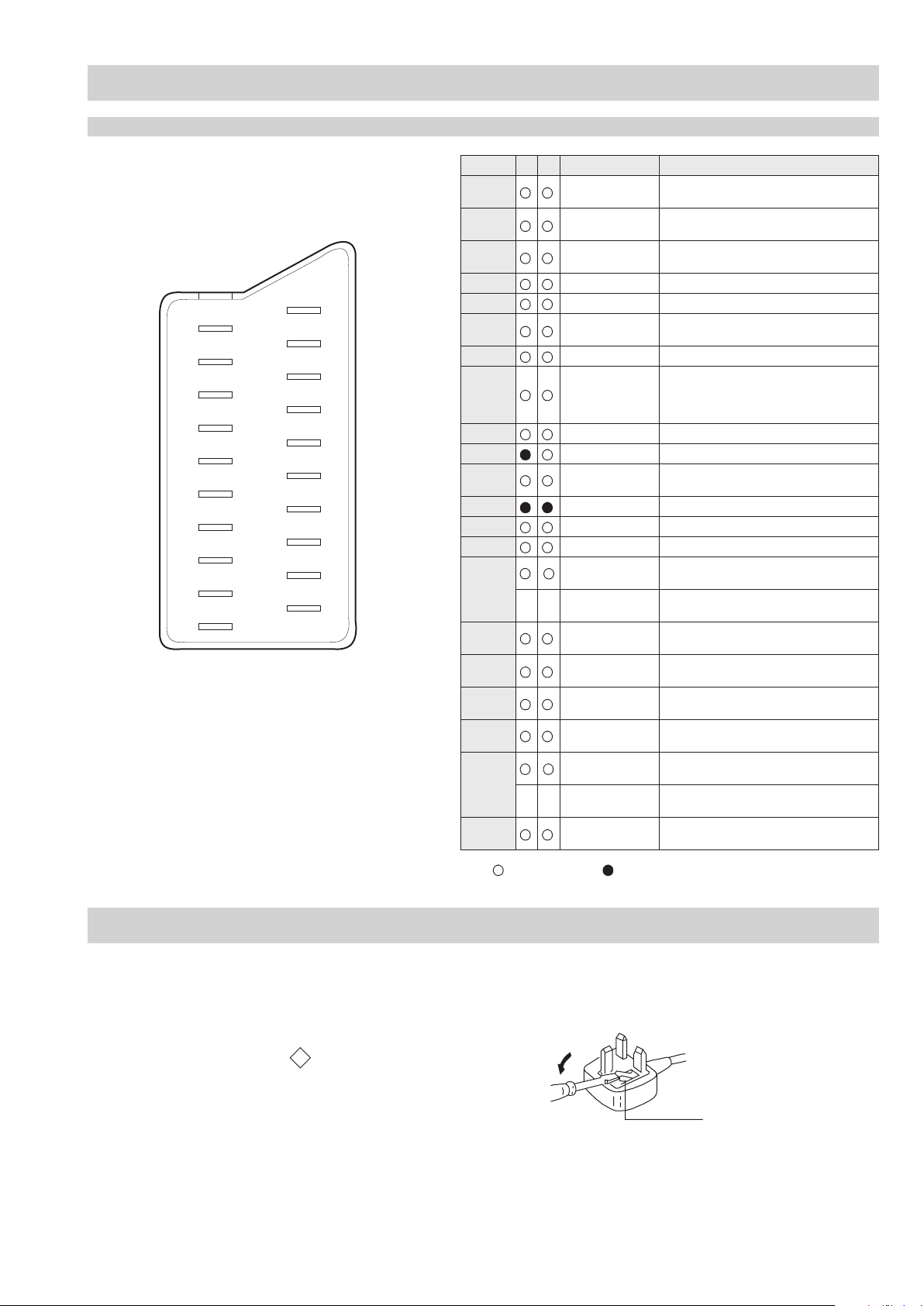

RM-ED009

SERVICE MANUAL

SE2

CHASSIS

MODEL

COMMANDER DEST

MODEL

COMMANDER DEST

KDL-26P3000

RM-ED009 UK

KDL-32P3000

RM-ED009 UK

KDL-37P3000

RM-ED009 UK

KDL-40P3000

RM-ED009 UK

KDL-26P300H

RM-ED009 UK

KDL-32P300H

RM-ED009 UK

KDL-37P300H

RM-ED009 UK

KDL-40P300H

RM-ED009 UK

RM-ED009

FLAT PANEL COLOR TV

KDL-26P3000 / KDL-32P3000 / KDL-37P3000 / KDL-40P3000

KDL-26P300H / KDL-32P300H / KDL-37P300H / KDL-40P300H

KDL-26P3000

RM-ED009 AEP

KDL-32P3000

RM-ED009 AEP

KDL-37P3000

RM-ED009 AEP

KDL-40P3000

RM-ED009 AEP

KDL-26P300H

RM-ED009 AEP

KDL-32P300H

RM-ED009 AEP

KDL-37P300H

RM-ED009 AEP

KDL-40P300H

RM-ED009 AEP

- 2 -

SE2

RM-ED009

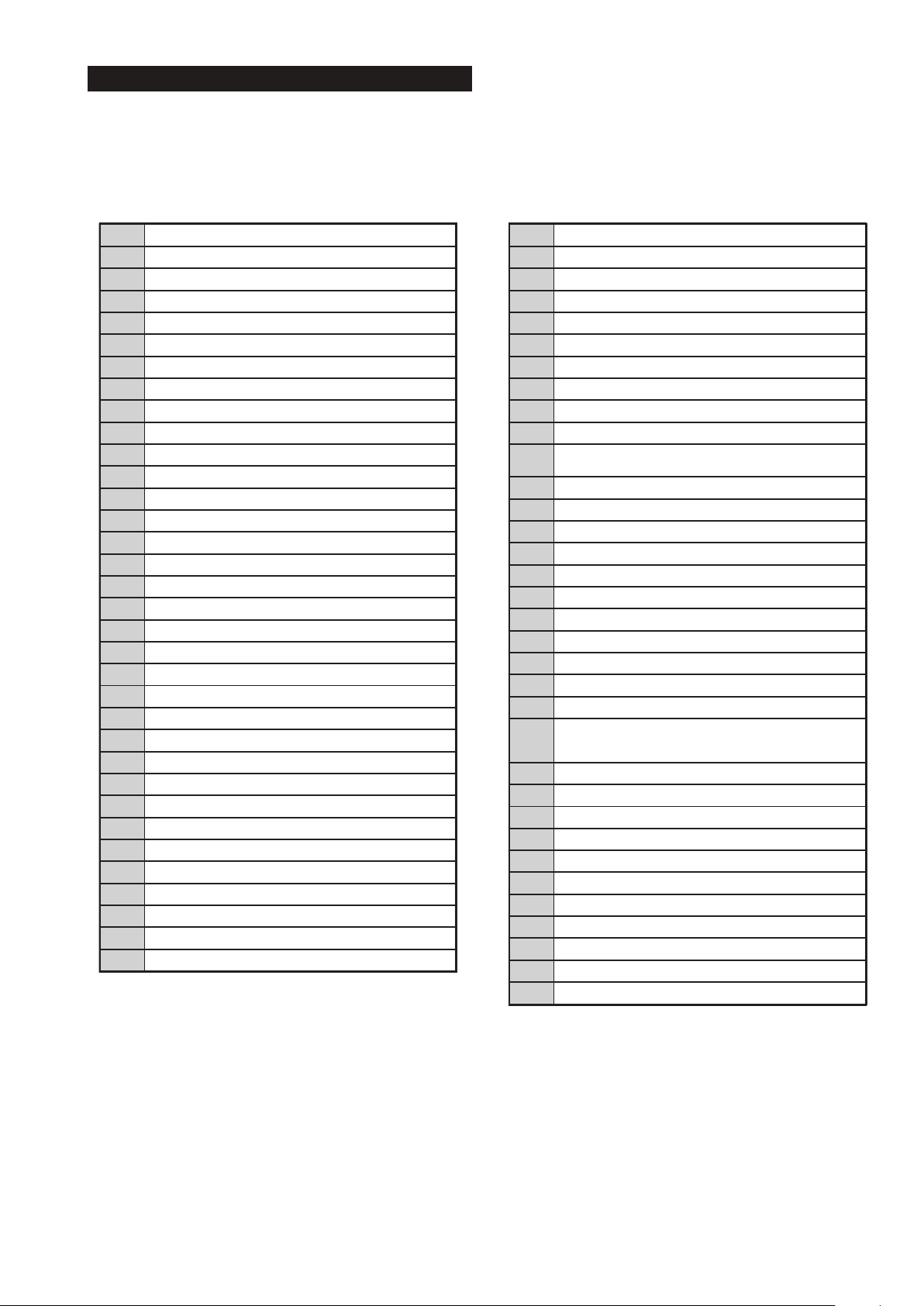

TABLE OF CONTENTS

Section Title Page Section Title Page

1. GENERAL ................................................................... 3

Caution ................................................................ 3

Specifications ...................................................... 5

Connectors .......................................................... 6

Self Diagnosis ..................................................... 8

2. DISASSEMBLY

2-1. Rear Cover Removal ........................................... 9

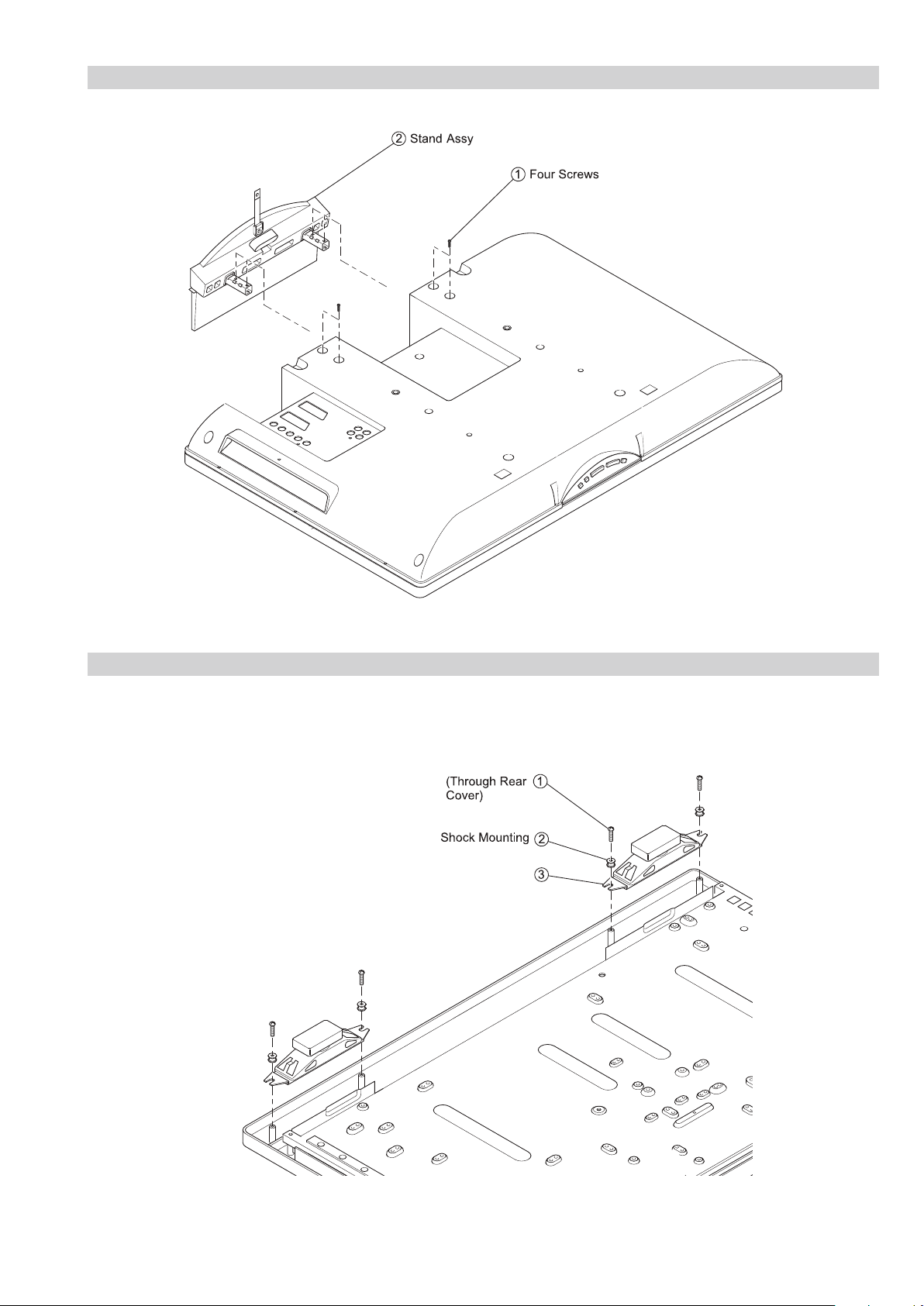

2-2. Stand Removal (26 & 32 inches) ........................ 9

2-3. Stand Removal (37 & 40 inches) ........................ 10

2-4. Loudspeaker Removal ........................................ 10

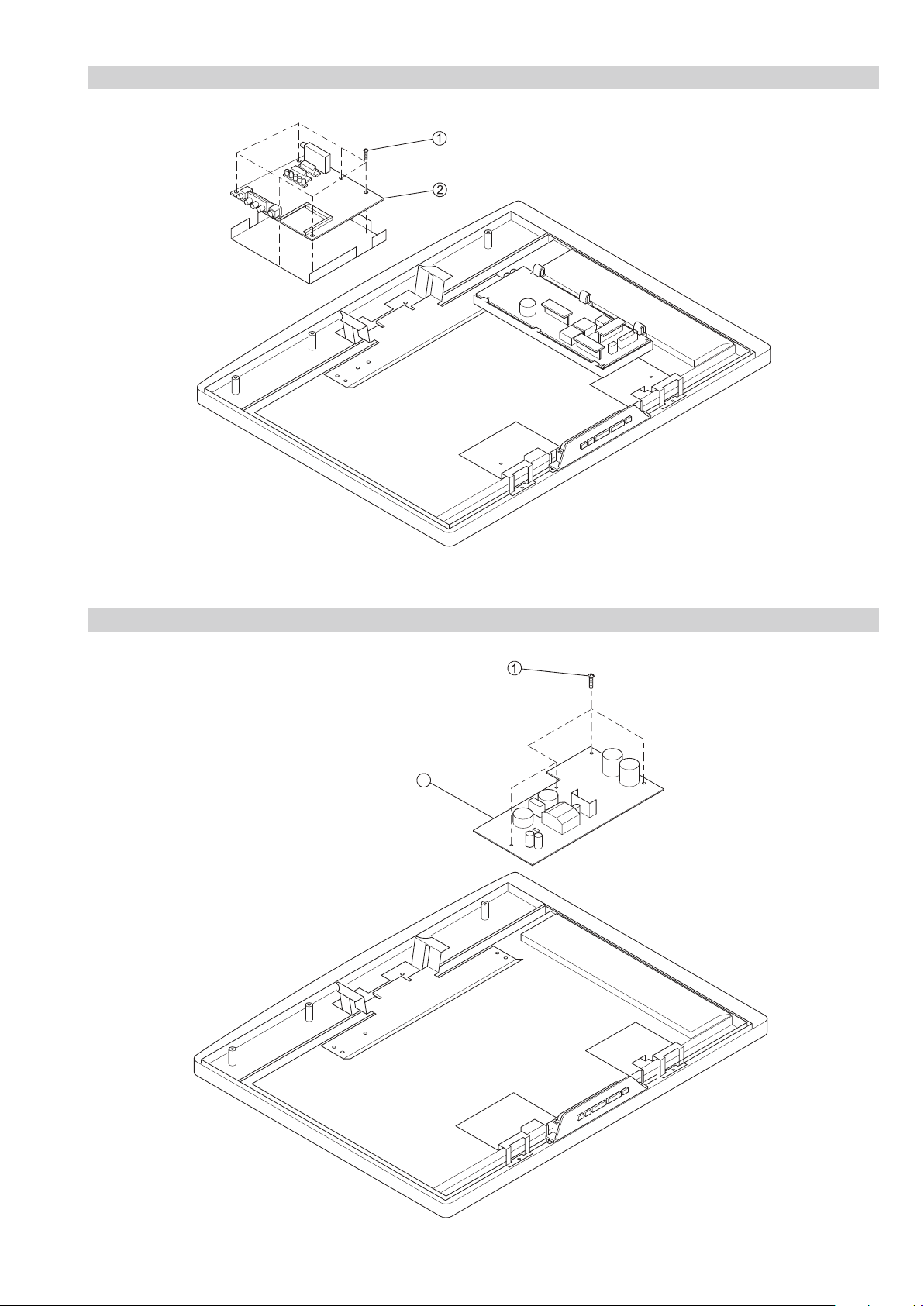

2-5. B1 Board Removal .............................................. 11

2-6. DS1 Board Removal (40 inches)........................ 11

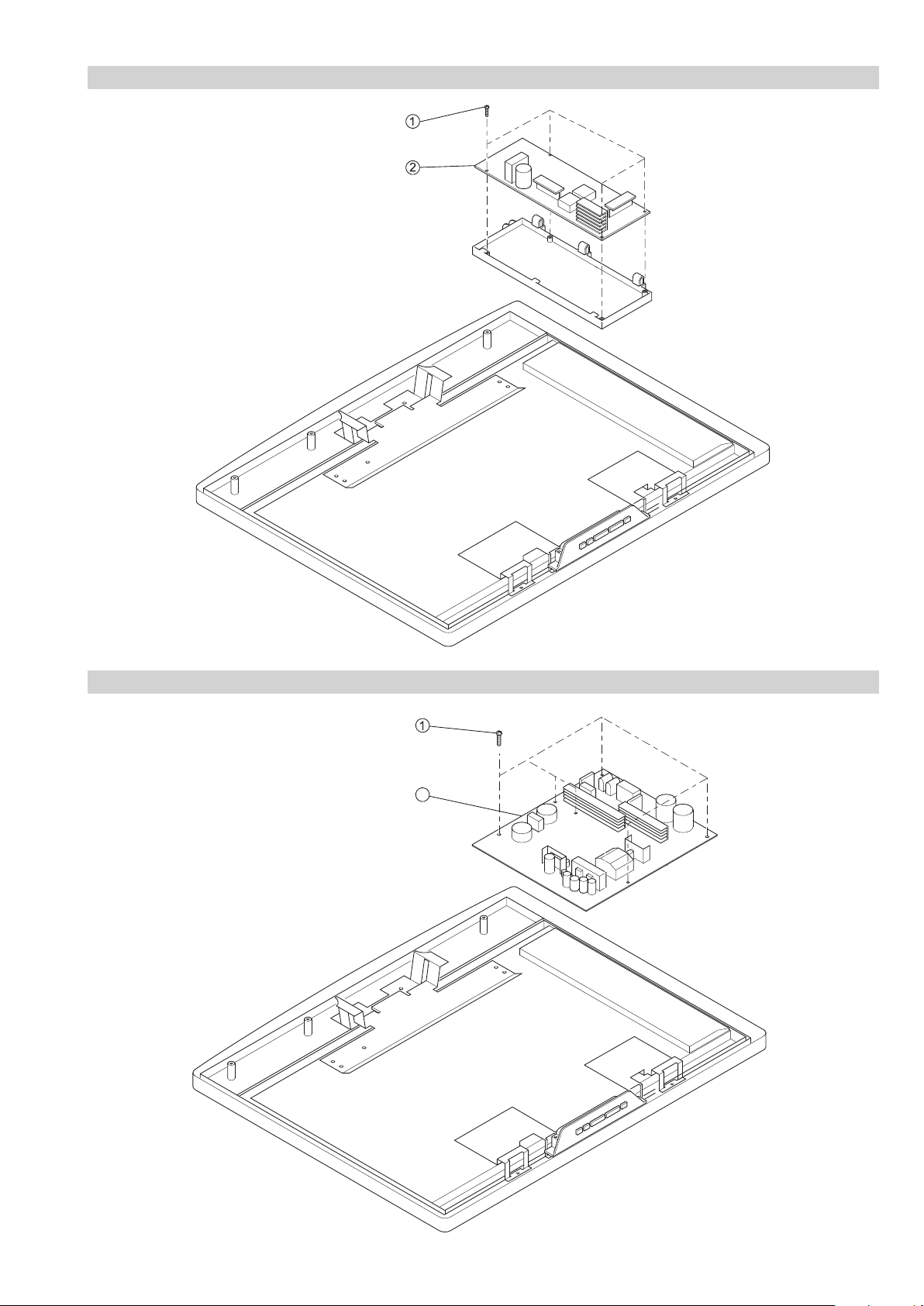

2-7. GS2 Board Removal (26 & 32 inches) ............... 12

2-8. GS3 (37 inches) or GS4 (40 inches)

Board Removal ................................................... 12

2-9. H1PS Board Removal ........................................ 13

2-10. H3PS Board Removal ........................................ 13

2-11. LCD Panel Removal ........................................... 14

3. CIRCUIT ADJUSTMENTS

3-1. Electrical Adjustments ....................................... 15

3-2. TT Mode ............................................................ 17

3-3. TT OSD Labels .................................................. 18

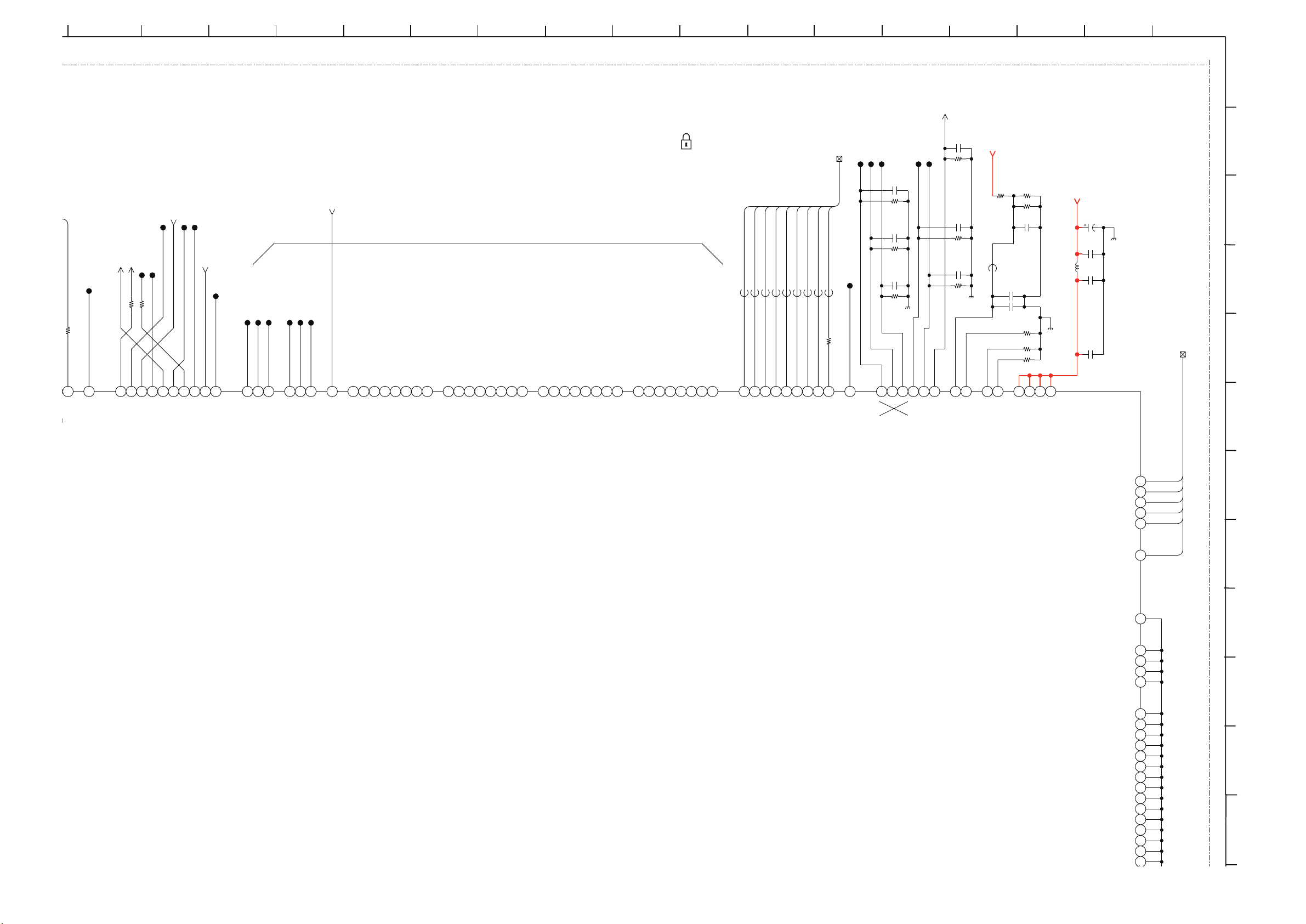

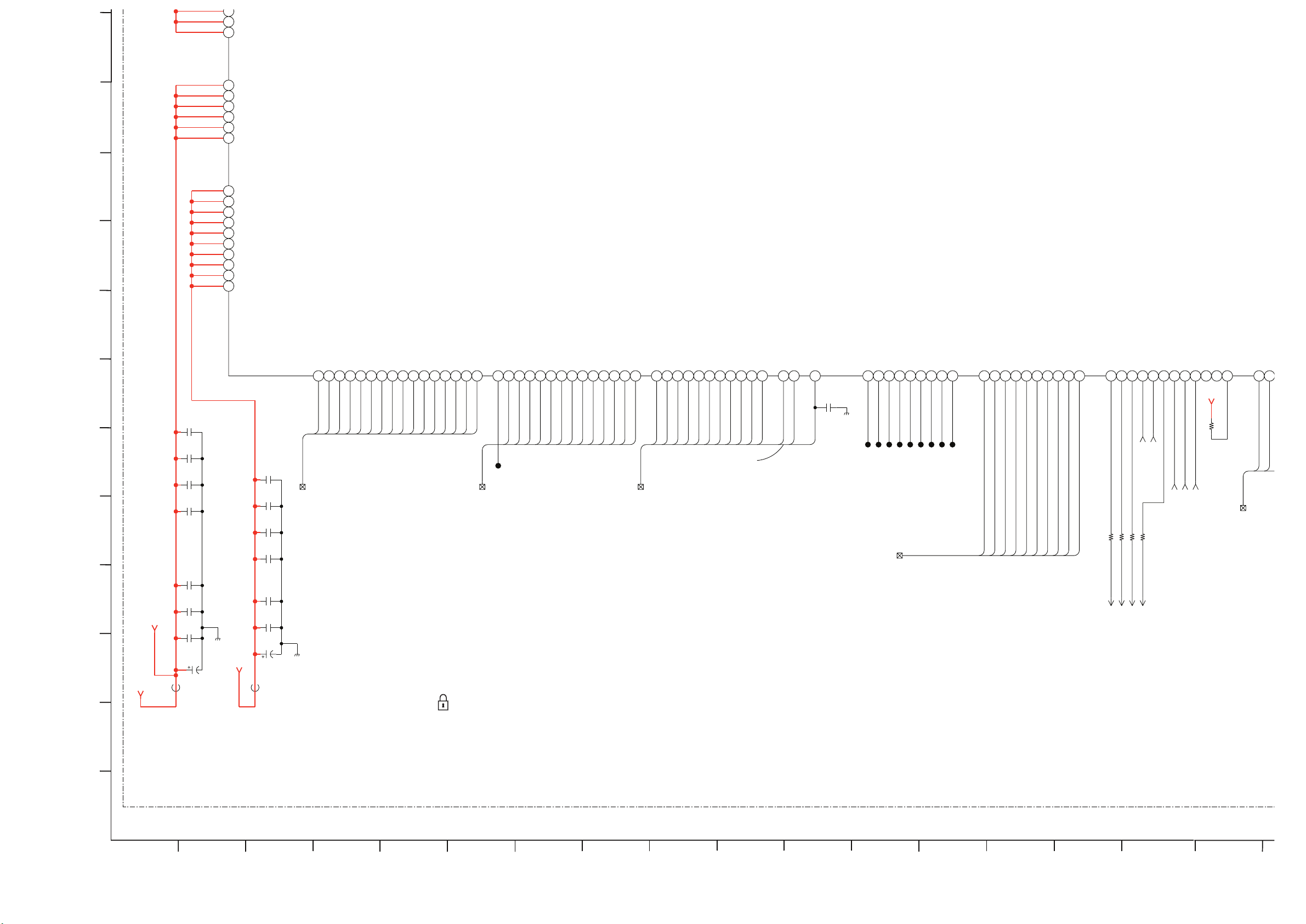

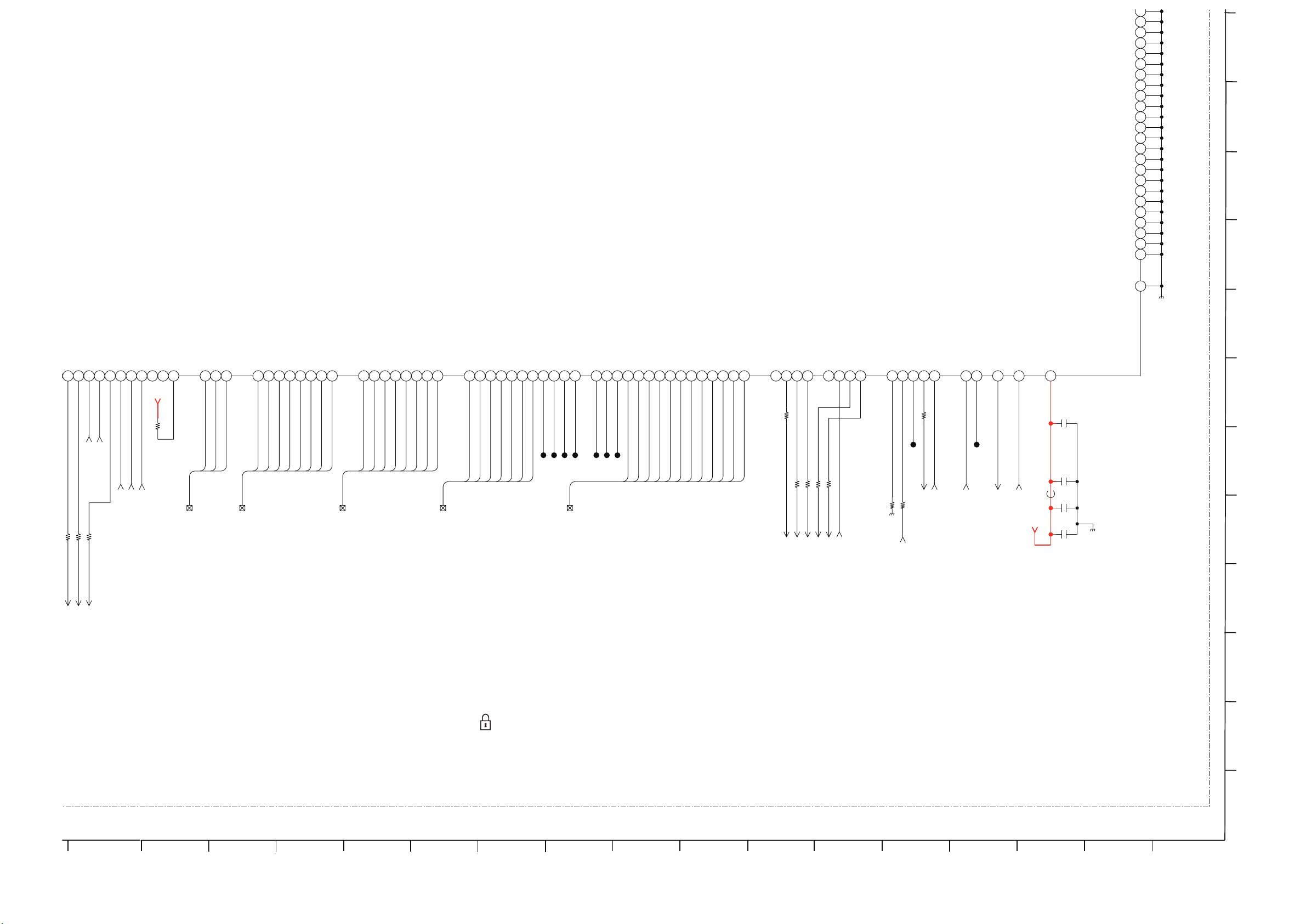

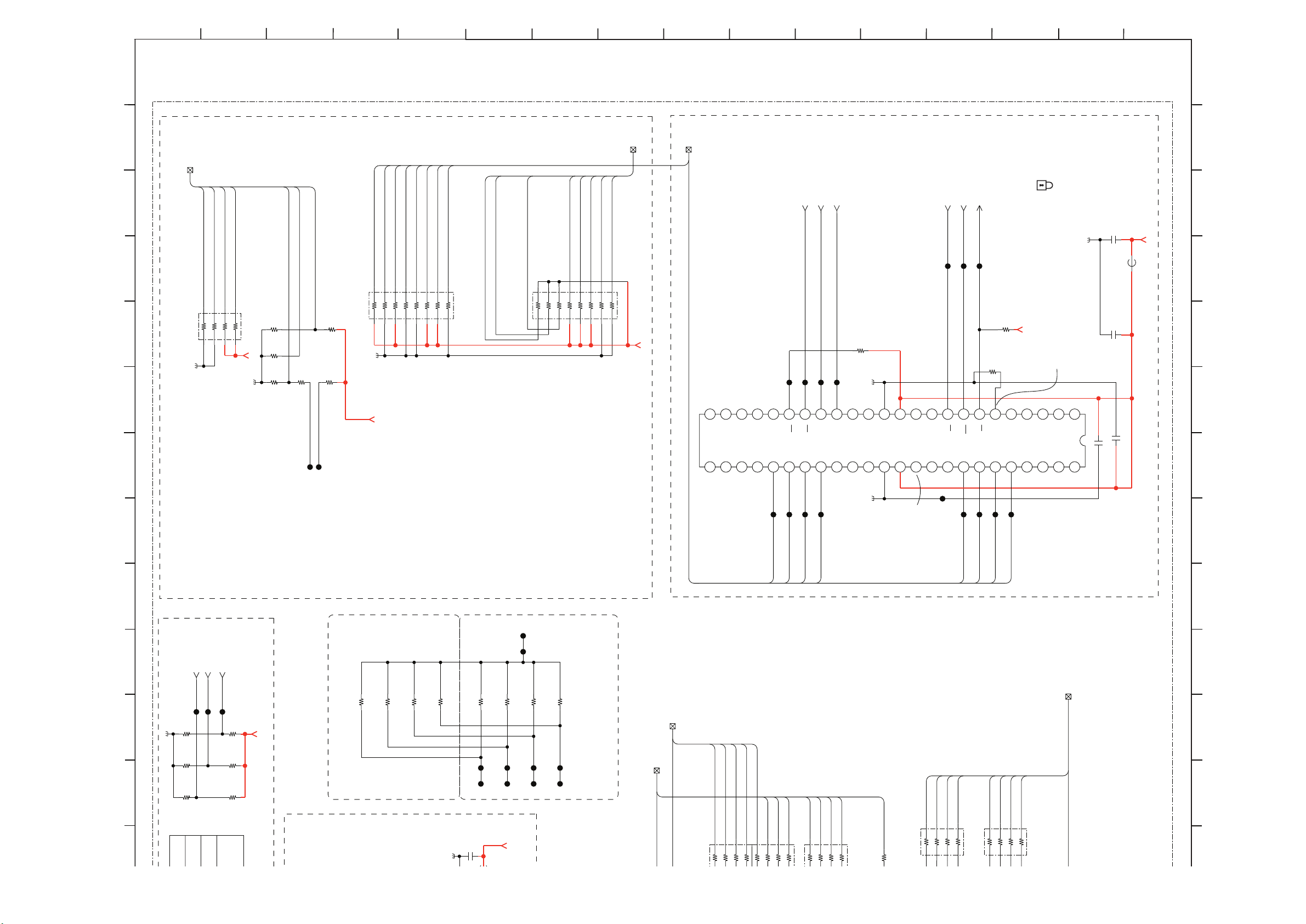

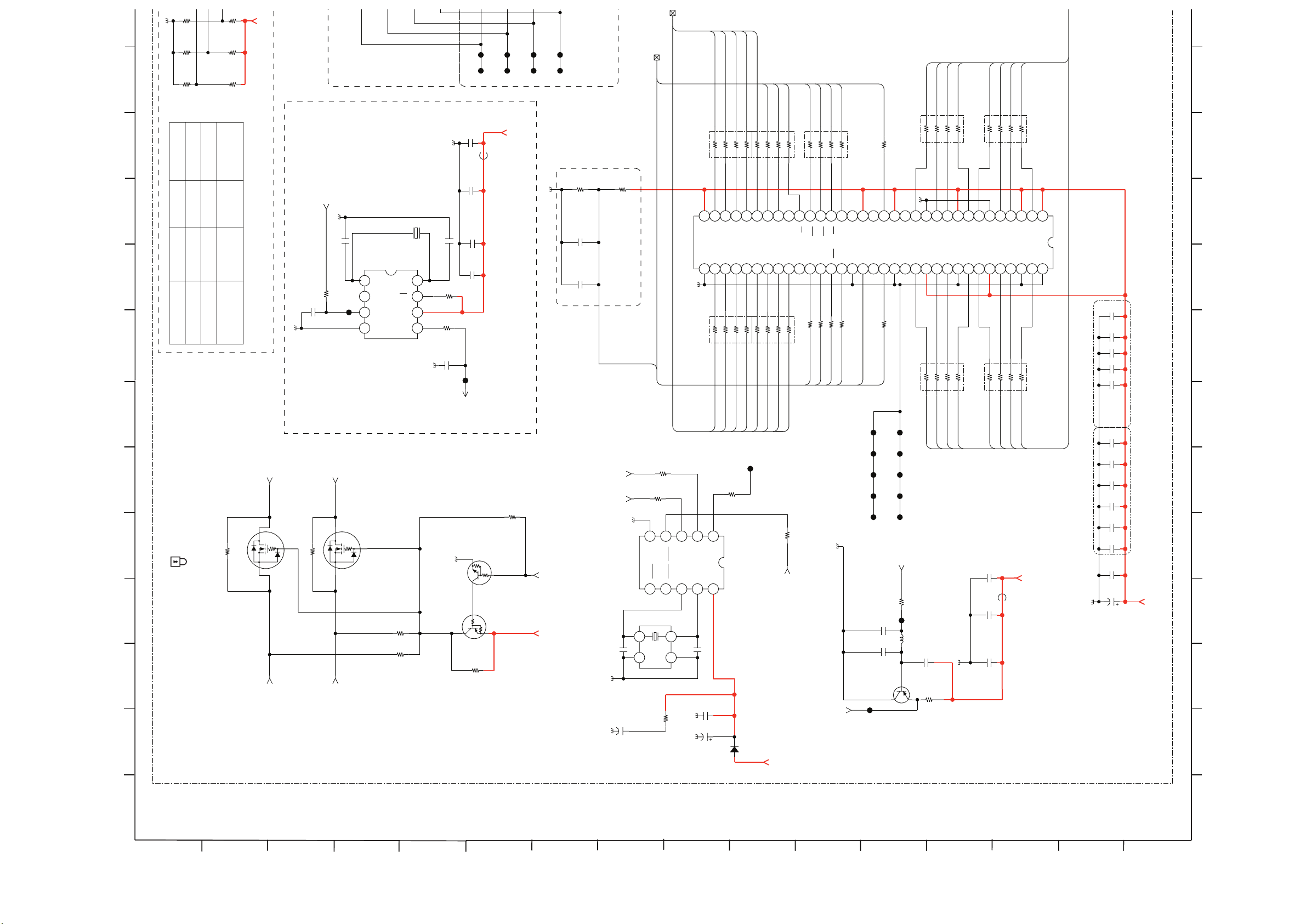

4. DIAGRAMS

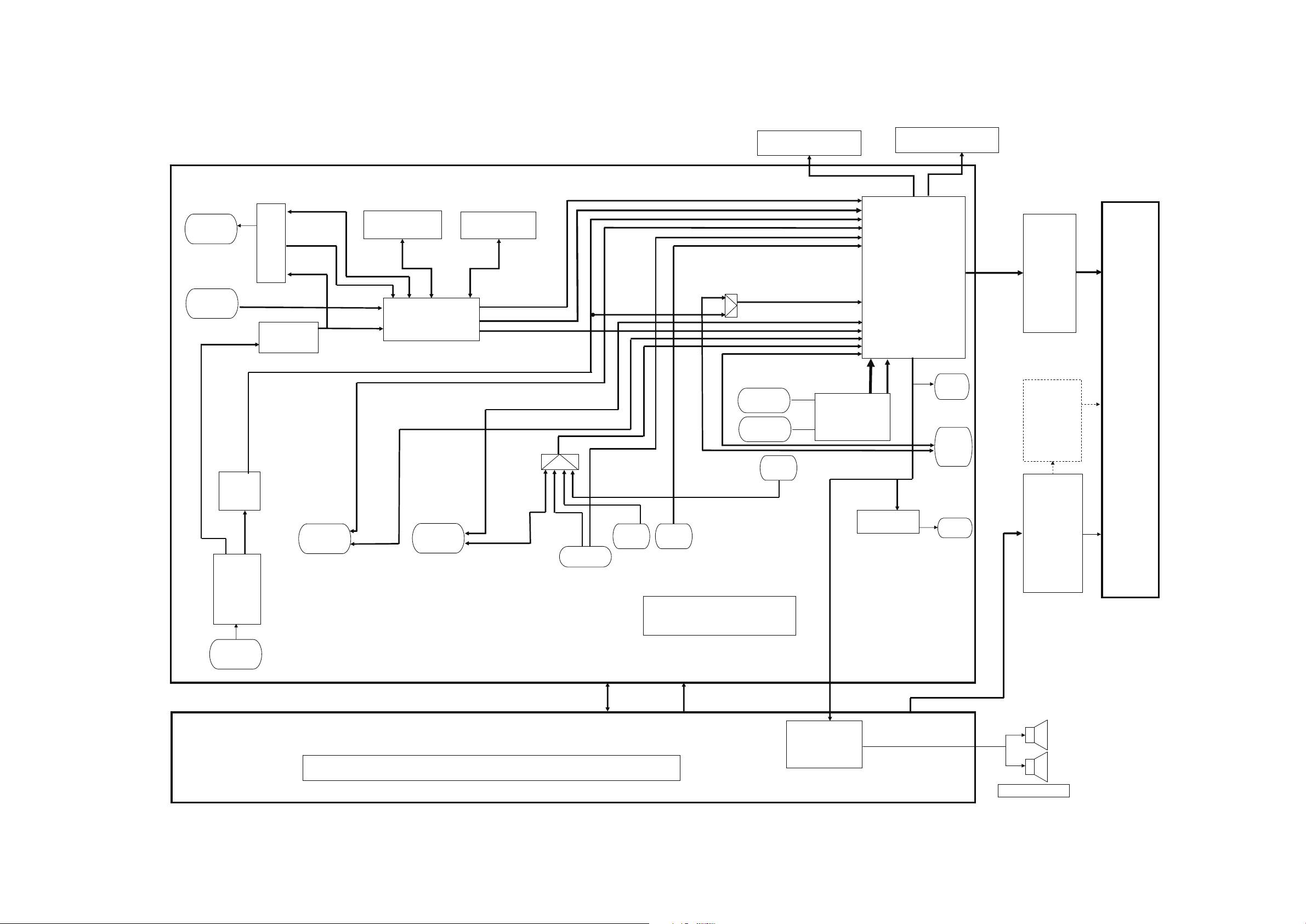

4-1. Block Diagram .................................................... 19

4-2. Circuit Board Location ........................................ 20

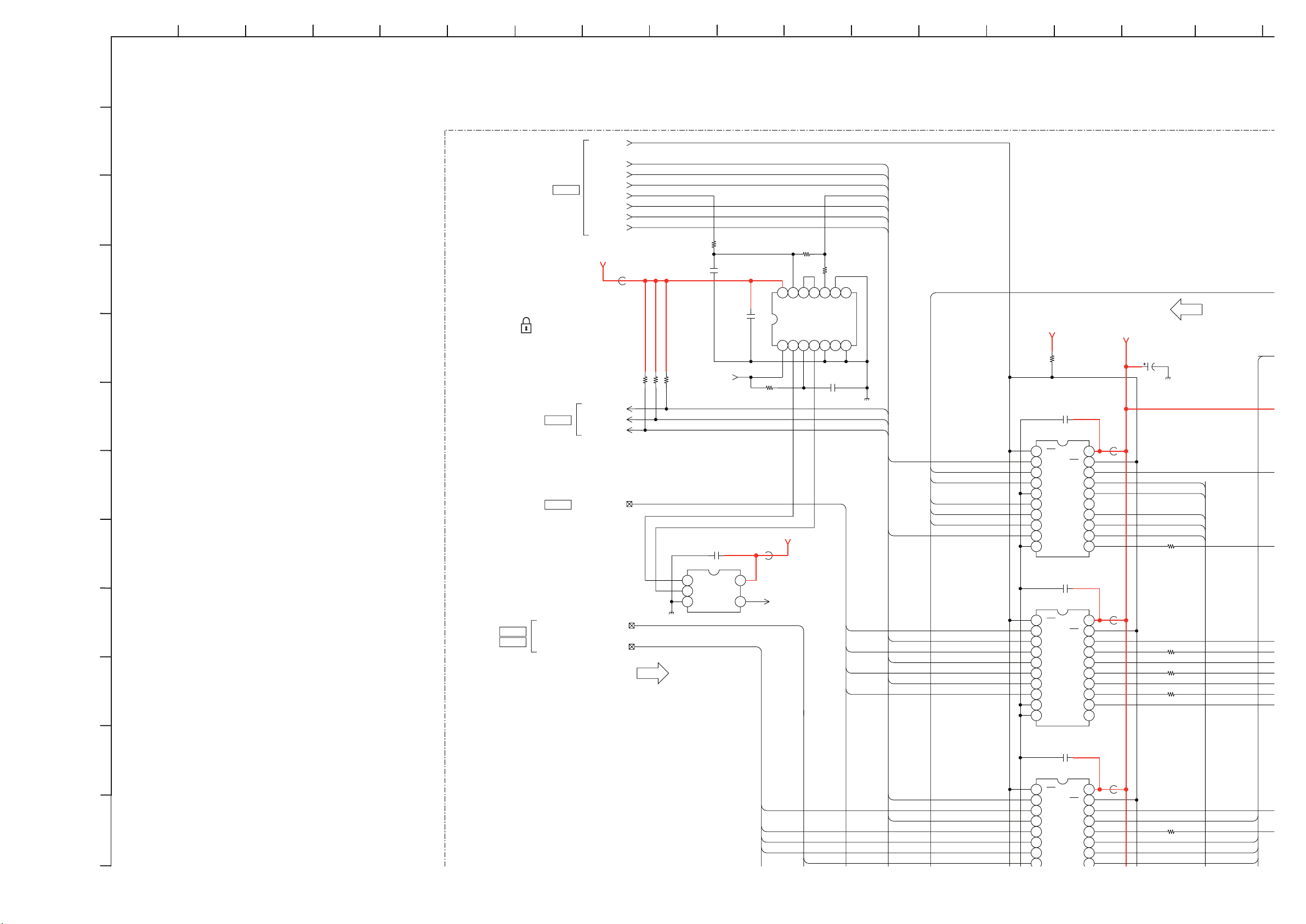

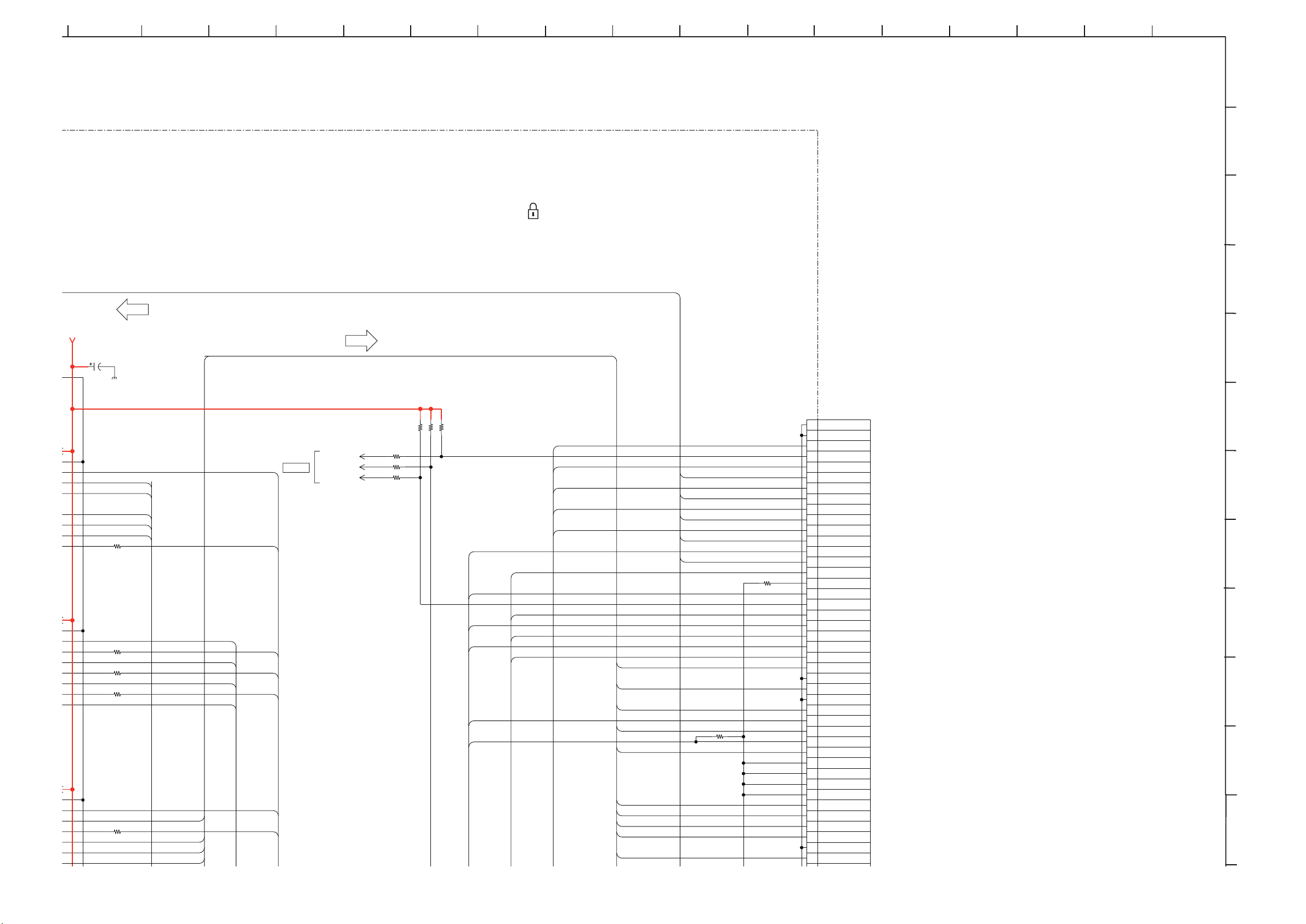

4-3. Schematic Diagrams and Printed Wiring

Boards ................................................................. 20

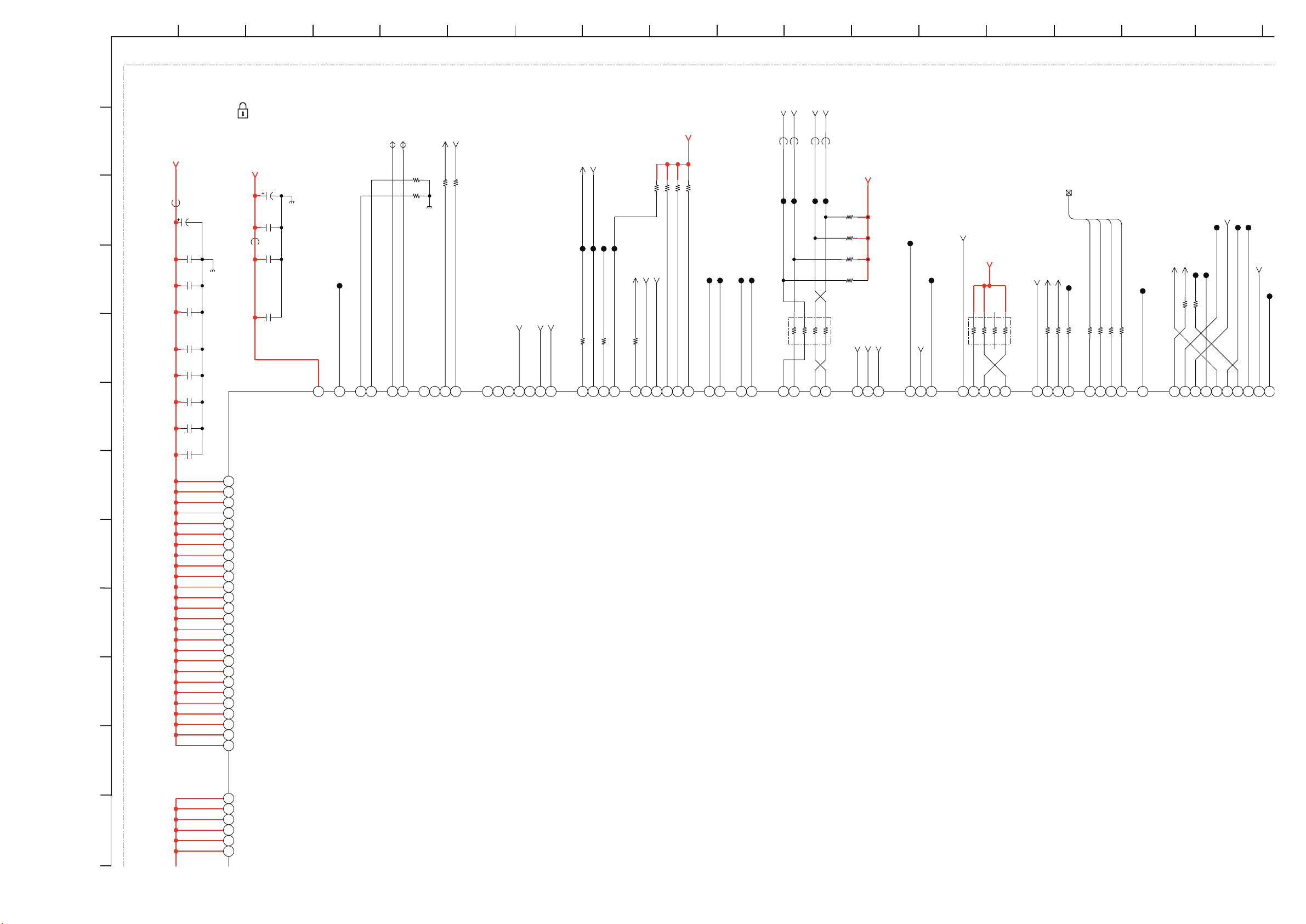

B1 Board Schematic Diagram ............................. 21

DS1 Board Schematic Diagram (40 inches) ....... 46

GS2 Board Schematic Diagram

(26 & 32 inches) ................................................. 50

GS3 Board Schematic Diagram (37 inches) ....... 55

GS4 Board Schematic Diagram (40 inches) ....... 60

H1PS Board Schematic Diagram ....................... 65

H3PS Board Schematic Diagram ....................... 65

B1 Printed Wiring Board .................................... 66

H1PS Printed Wiring Board ............................... 66

H3PS Printed Wiring Board ............................... 67

DS1 Printed Wiring Board ................................. 68

GS2 Printed Wiring Board ................................. 69

GS3 Printed Wiring Board ................................. 70

GS4 Printed Wiring Board ................................. 72

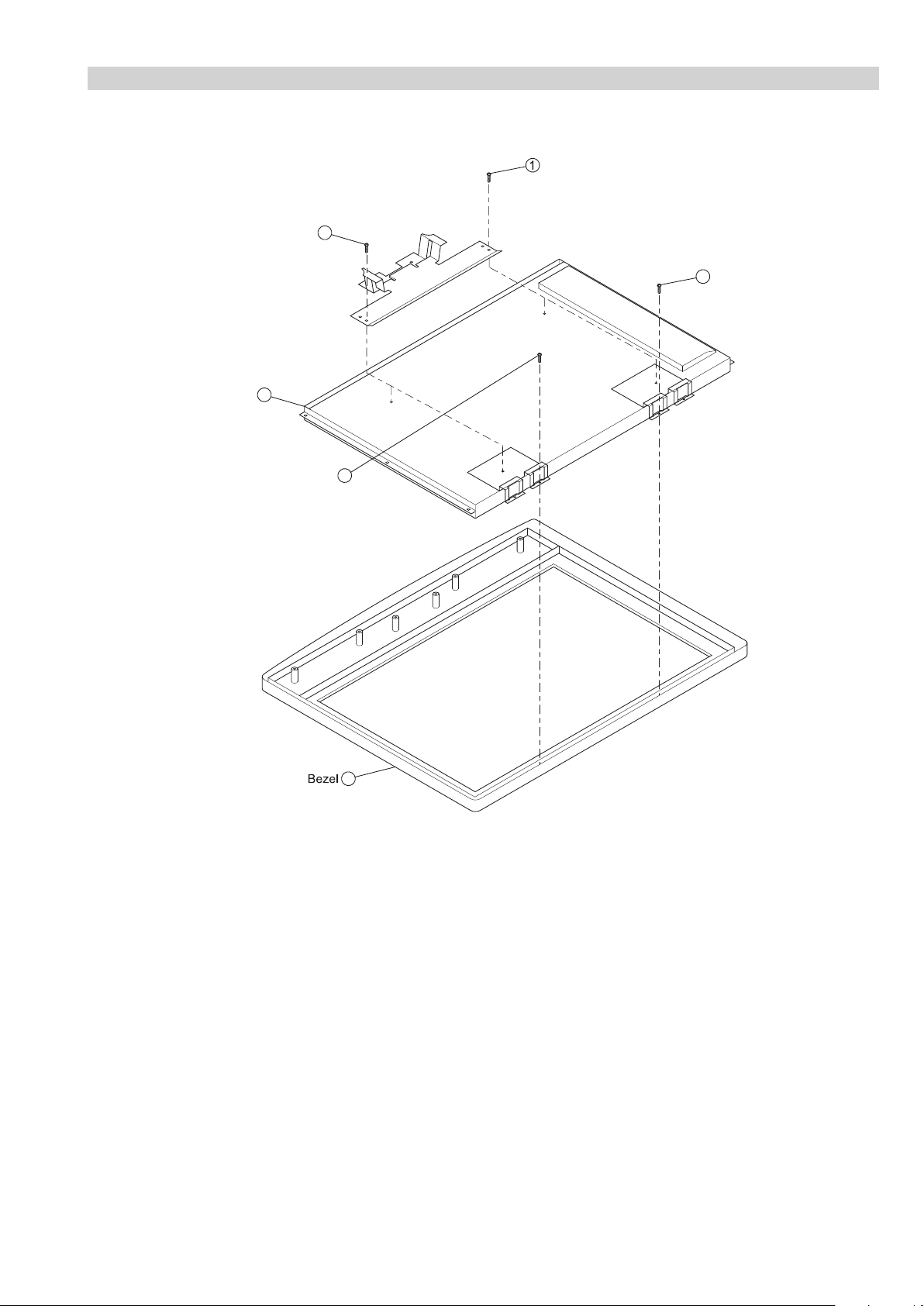

5. EXPLODED VIEWS

5-1. Chassis (26 & 32 inches) .................................... 74

5-2. Chassis (37 & 40 inches) .................................... 75

5-3. Rear Cover, Stand & Bezel (26 & 32 inches) ..... 76

5-4. Rear Cover, Stand & Bezel (37 & 40 inches) ..... 77

6. ELECTRICAL PARTS LIST .................................. 78

SAFETY-RELATED COMPONENT WARNING !!

COMPONENTS IDENTIFIED BY SHADING AND MARKED

ON

THE SCHEMATIC DIAGRAMS, EXPLODED VIEWS AND IN THE

PARTS LIST ARE CRITICAL FOR SAFE OPERATION. REPLACE

THESE COMPONENTS WITH SONY PARTS WHOSE PART

NUMBERS APPEAR AS SHOWN IN THIS MANUAL OR IN

SUPPLEMENTS PUBLISHED BY SONY.

WARNING !!

AN ISOLATION TRANSFORMER SHOULD BE USED DURING

ANY SERVICE WORK TO AVOID POSSIBLE SHOCK HAZARD

DUE TO LIVE CHASSIS, THE CHASSIS OF THIS RECEIVER IS

DIRECTLY CONNECTED TO THE POWER LINE.

- 3 -

SE2

RM-ED009

SECTION 1 GENERAL

The circuit boards used in these models have been processed using

Lead Free Solder. The boards are identified by the LF logo located

close to the board designation e.g. F1, H1 etc [ see examples ]. The

servicing of these boards requires special precautions to be taken as

outlined below.

Lead Free Soldered Boards

example 1

example 2

Lead Free Solder material must be used to comply with environmental requirements of new solder joints. Lead Free Solder is available under

the following part numbers :

Due to the higher melting point of Lead Free Solder the soldering iron tip temperature needs to be set to 370 degrees centigrade. This requires

soldering equipment capable of accurate temperature control coupled with a good heat recovery characteristics.

For more information on the use of Lead Free Solder, please refer to http://www.sony-training.com

rebmuntraP retemaiD skrameR

91-500-046-7 mm3.0 gK52.0

02-500-046-7 mm4.0 gK05.0

12-500-046-7 mm5.0 gK05.0

22-500-046-7 mm6.0 gK52.0

32-500-046-7 mm8.0 gK00.1

42-500-046-7 mm0.1 gK00.1

52-500-046-7 mm2.1 gK00.1

62-500-046-7 mm6.1 gK00.1

CAUTION

SECTION 1 GENERAL

- 4 -

SE2

RM-ED009

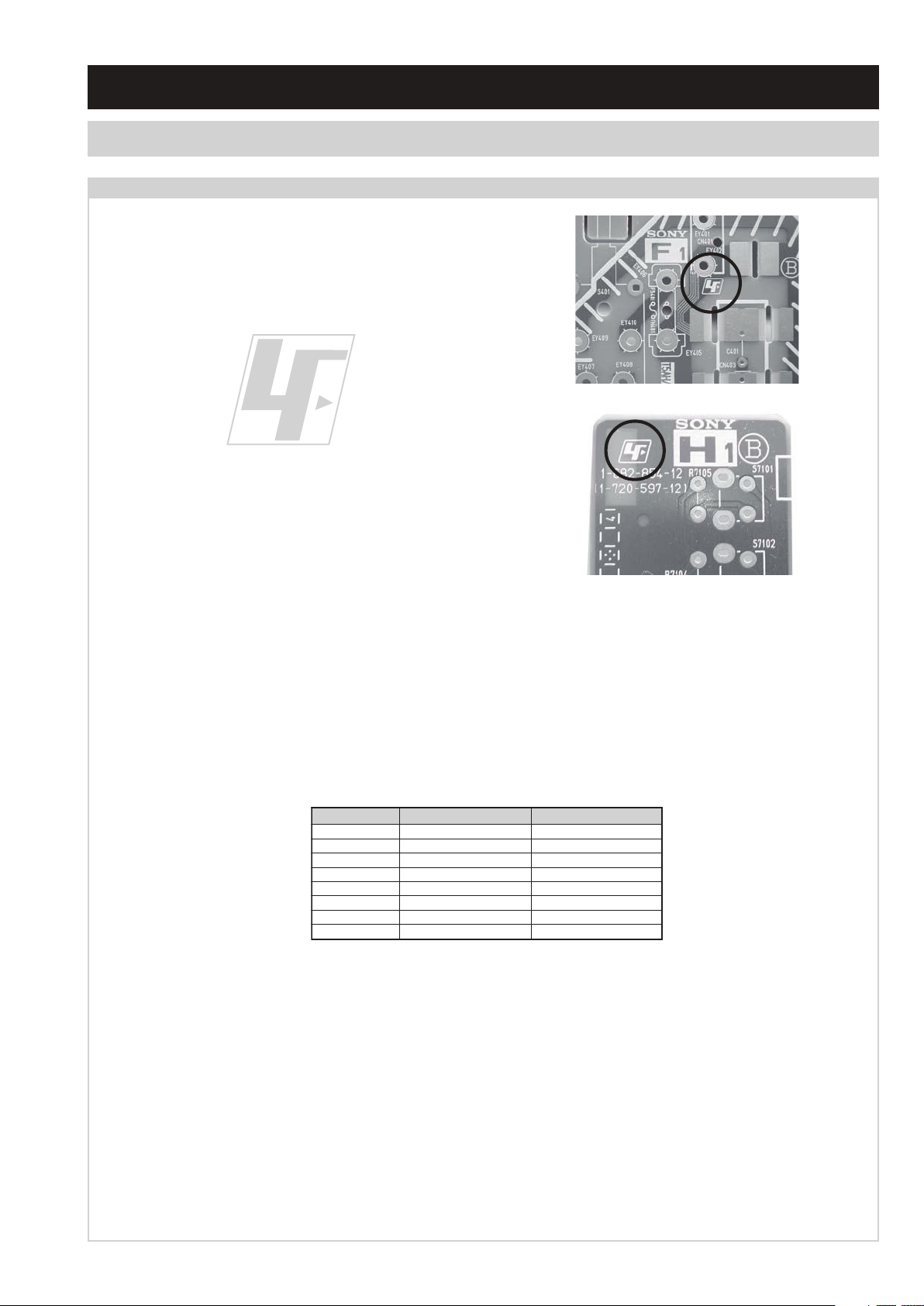

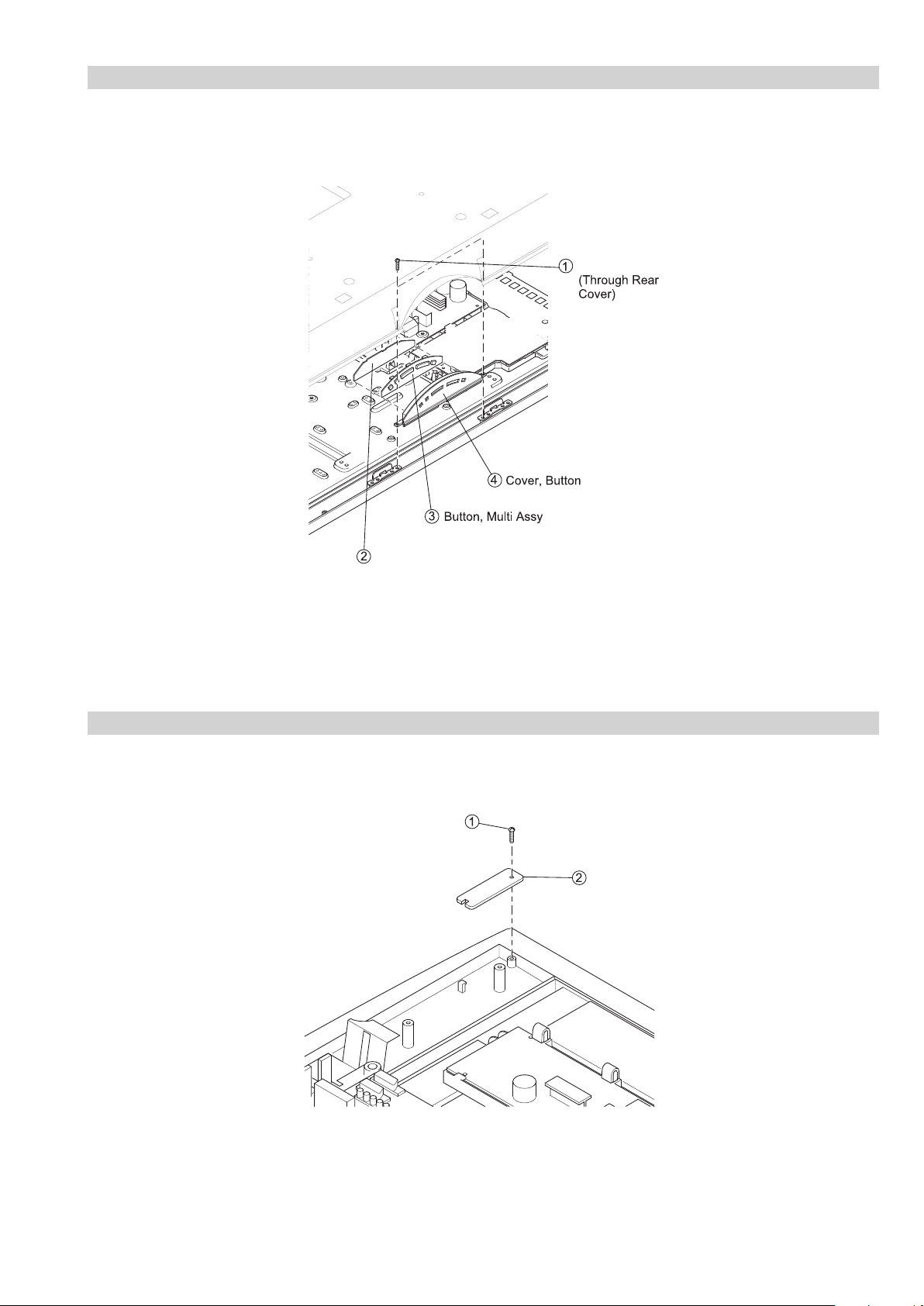

Rear Cover Removal

When removing the rear cover it is important to ensure that the top button plate is fixed to the front cabinet and not removed with the rear cover.

This is to avoid breaking the cable connected to the switch button board. It is also important to remember that whilst removing the rear cover it

is kept parallel to the LCD plane.

CAUTION

- 5 -

SE2

RM-ED009

SPECIFICATIONS

ITEM MODEL Television System Stereo System Channel Coverage Color System

E

Analogue:

B/G/H, D/K, I, L

Digital:

DVB-T

GERMAN/NICAM

Stereo

Analogue: VHF : E2-E12

UHF : E21-E69

CATV : S1-S20

HYPER : S21-S41

D/K: R1-R12, R21-R69

L: F2-F10, B-Q, F21-F69

I: UHF B21-B69

Digital: VHF/UHF

Analogue:

PAL, SECAM

NTSC 3.58/4.43

(VIDEO ONLY)

Digital:

MPEG-2 MP@ML

U

Analogue:

I

Digital:

DVB-T

NICAM Stereo

Analogue: I: UHF B21-B69

Digital: VHF/UHF

Analogue:

PAL, SECAM

NTSC 3.58/4.43

(VIDEO ONLY)

Digital:

MPEG-2 MP@ML

Projected Picture Size

LCD(Liquid Crystal Display) Panel

Approx 26 inches (KDL-26XXXXX)

Approx 32 inches (KDL-32XXXXX)

Approx 37 inches (KDL-37XXXXX)

Approx 40 inches (KDL-40XXXXX)

Sound Output

Right and Left speaker

Sub-woofer

2 x 10W (RMS)

Input/Output Terminals [REAR] General Specifications

1: 21-pin Euro connector

(CENELEC standard)

Inputs for Audio and Video signals.

Inputs for RGB.

Outputs of TV Video and Audio

signals.

Power Requirements 220 - 240V

Power Consumption/

Standby

Approx 90W/0.7W or less (26 inches)

Approx 130W/0.7W or less (32 inches)

Approx 150W/0.6W or less (37 inches)

Approx 165W/0.6W or less (40 inches)

2: 21-pin Euro connector

(CENELEC standard)

Inputs for Audio and Video signals.

Inputs for RGB.

Outputs of Video and Audio signals

(Selectable). SmartLink interface.

Dimensions

Approx 657x500x214mm

(26 inches with stand)

Approx 657x453x121mm

(26 inches without stand)

Approx 790x577x214mm

(32 inches with stand)

Approx 790x530x119mm

(32 inches without stand)

Approx 906x658x265mm

(37 inches with stand)

Approx 906x611x126mm

(37 inches without stand)

Approx 982x690x265mm

(40 inches with stand)

Approx 982x643x124mm

(40 inches without stand)

Weight

Approx 12.0kg (26 inches with stand)

Approx 10.0kg (26 inches without stand)

Approx 15.0kg (32 inches with stand)

Approx 13.0kg (32 inches without stand)

Approx 21.0kg (37 inches with stand)

Approx 18.0kg (37 inches without stand)

Approx 23.5kg (40 inches with stand)

Approx 20.0kg (40 inches without stand)

Phono Jacks

Output Connectors variable for

Audio Signals.

Supplied Accessories

RM-ED009 Remote Commander (1)

IEC designated R06 battery (2)

Support belt (1) and screws (2)

HDMI Inputs HDMI Connectors

Other Features

Intergrated digital Tuner, High Picture Quality,

Bravia Engine, BBE ViVA, 2 HDMI inputs, PC

input.

PC Input 15 Pin D Sub Connector

CAM Slot Conditional Access Module

Input/Output Terminals [SIDE] Remote control system : Infrared control

Headphone jack Stereo mini jack

Power requirements

3V dc

2 batteries IEC designation

R06 (size AA)

Audio input Phono jacks

Video input Phono jack

S Video input 4 pin mini DIN

Design and specifications are subject to change without notice.

- 6 -

SE2

RM-ED009

CONNECTORS

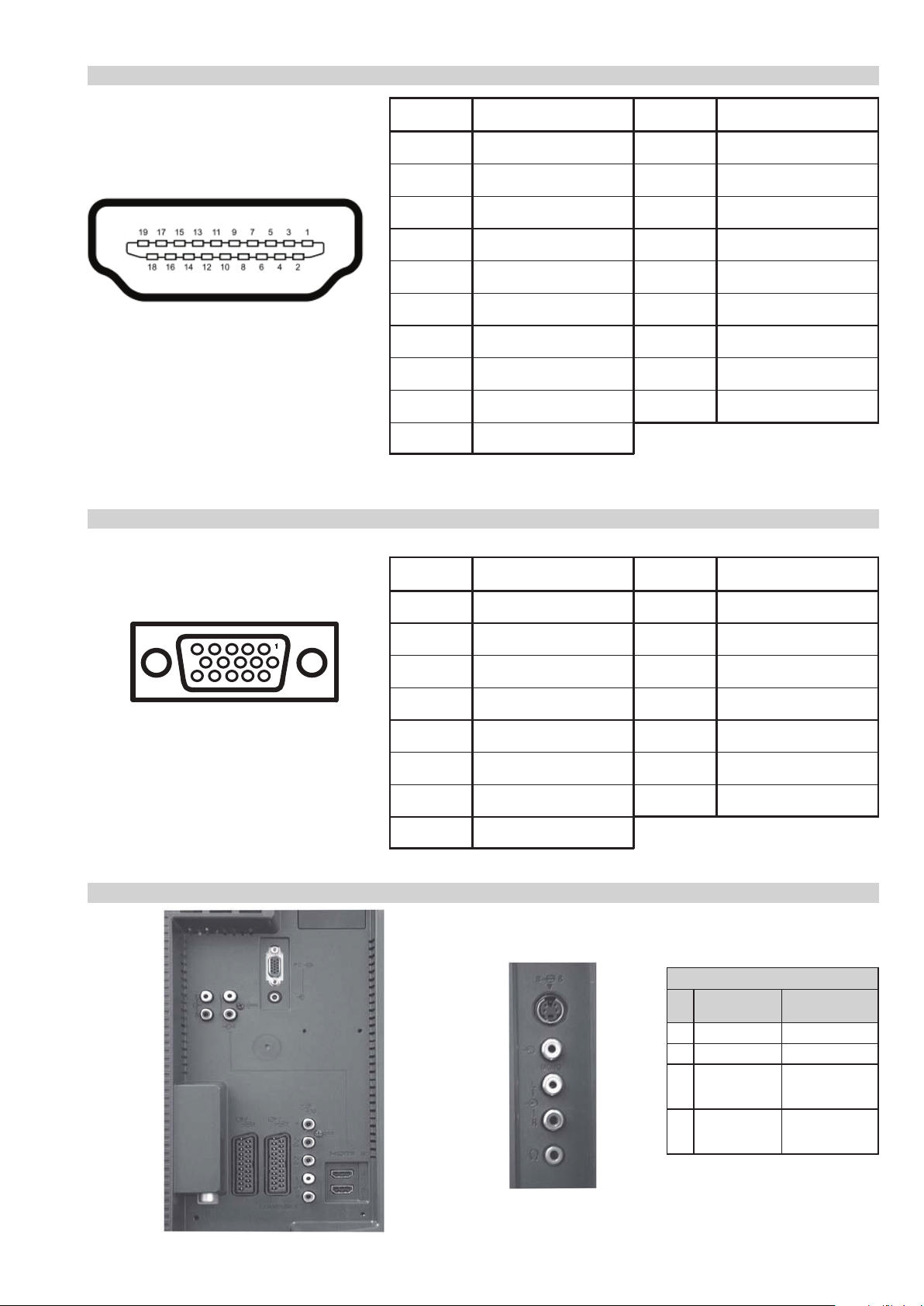

21 Pin Connector (SCART)

_ _ Red input 0.7 +/- 3dB, 75 ohms, positive

_ (S signal Chroma

Connected Not Connected (open) * at 20Hz - 20kHz

Pin No 1 2 Signal Signal level

1 Audio output B

(right)

Standard level : 0.5V rms

Output impedence : Less than 1kohm*

2

Audio input B

(right)

Standard level : 0.5V rms

Output impedence : More than 10kohm*

3

Audio output A

(left)

Standard level : 0.5V rms

Output impedence : Less than 1kohm*

4 Ground (audio)

5 Ground (blue)

6 Audio input A

(left)

Standard level : 0.5V rms

Output impedence : More than 10kohm*

7 Blue input 0.7 +/- 3dB, 75 ohms positive

8 Function select

(AV control)

High state (9.5-12V) : Part mode

Low state (0-2V) : TV mode

Input impedence : More than 10K ohms

Input capacitance : Less than 2nF

9 Ground (green)

10 AVlink

11 Green Green signal : 0.7 +/- 3dB, 75 ohms,

positive

12 Open

13 Ground (red)

14 Ground (blanking)

15

input)

0.3 +/- 3dB, 75 ohms, positive

16 Blanking input

(Ys signal)

High state (1-3V) Low state (0-0.4V)

Input impedence : 75 ohms

17 Ground (video

output)

18 Ground (video

input)

19 Video output 1V +/- 3dB, 75ohms, positive sync 0.3V

(-3+10dB)

20

Video input 1V +/- 3dB, 75ohms, positive sync 0.3V

(-3+10dB)

Video input

Y (S signal)

1V +/- 3dB, 75ohms, positive sync 0.3V

(-3+10dB)

21 Common ground

(plug, shield)

-

-

- -

19

17

15

13

11

9

7

5

3

1

20

18

16

14

12

10

8

6

4

2

21

How to replace the fuse.

Open the fuse compartment with

a screwdriver blade and replace

the fuse.

FUSE

WARNING (UK Models only)

The flexible mains lead is supplied connected to a B.S. 1363 fused

plug having a fuse of the correct rating for the set. Should the fuse

need to be replaced, use a fuse of the same rating approved by ASTA

to BS 1362, ie one that carries the

ASA

T

mark.

IF THE PLUG SUPPLIED WITH THIS APPLIANCE IS NOT SUITABLE FOR THE OUTLET SOCKETS IN YOUR HOME, IT SHOULD

BE CUT OFF AND AN APPROPRIATE PLUG FITTED. THE PLUG

SEVERED FROM THE MAINS LEAD MUST BE DESTROYED AS A

PLUG WITH BARED WIRES IS DANGEROUS IF ENGAGED IN A

LIVE SOCKET.

When an alternative type of plug is used, it should be fitted with the

correct rating fuse, otherwise the circuit should be protected by the

same rating fuse at the distribution board.

UK PLUG WARNING

- 7 -

SE2

RM-ED009

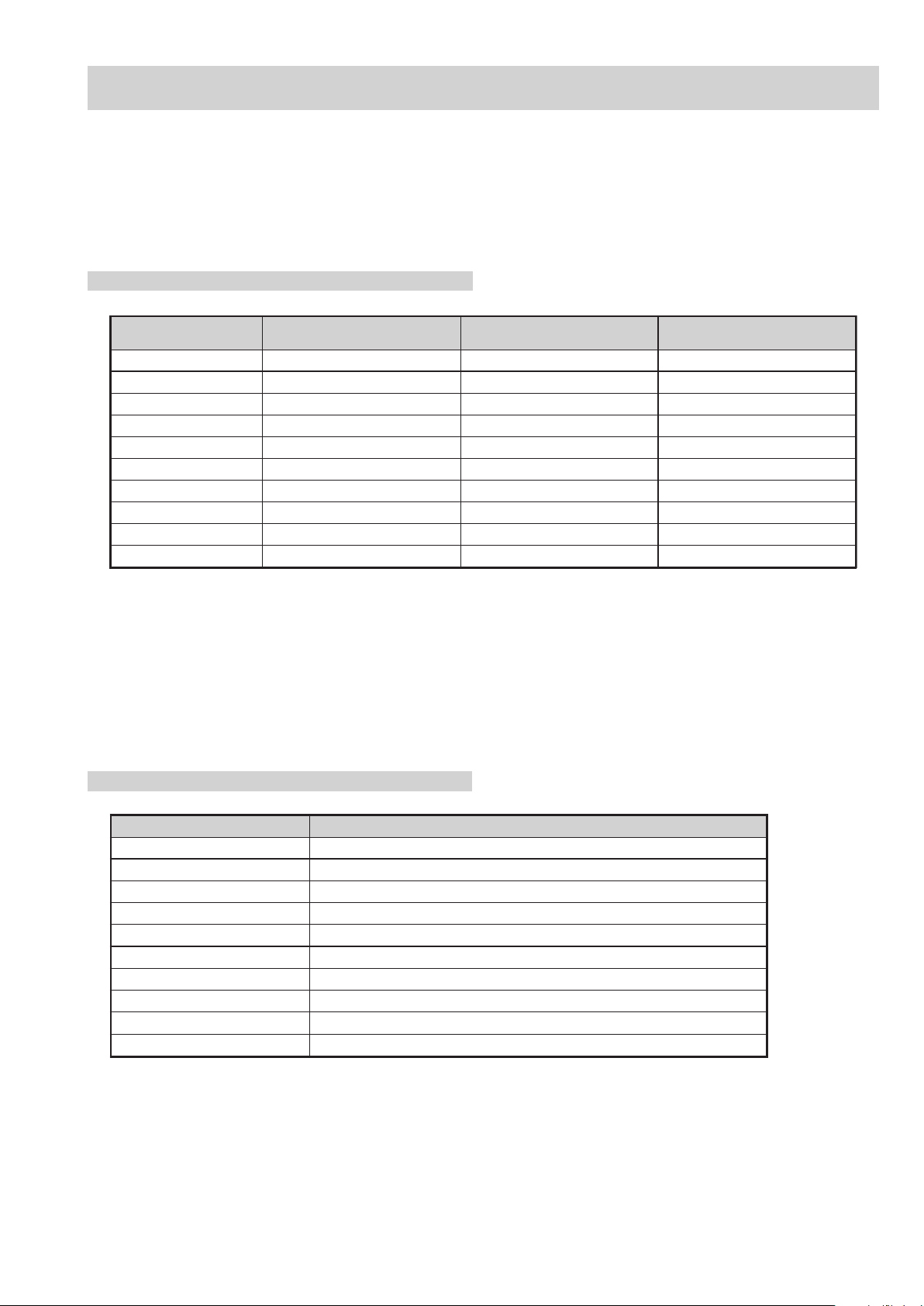

HDMI Connector

Rear Connection Panel Side Connection Panel

noitarugifnocniptekcosoediVS

niP

oN

langiS leveLlangiS

1 dnuorG -

2 dnuorG -

3 tupni)langisS(Y ,mho57Bd3-/+V1

V3.0.cnySevitisop

Bd01+3-

4 tupni)langisS(C Bd3-/+V3.0

evitisop,mho57

.cnyS

S-Video

socket

15 Pin D Sub Connector (PC)

1

Pin No Signal Assignment Pin No Signal Assignment

1 TMDS Data2+ 11 TMDS Clock Shield

2 TMDS Data2 Shield 12 TMDS Clock-

3 TMDS Data2- 13 CEC

4 TMDS Data1+ 14 Reserved (N.C. on device)

5 TMDS Data1 Shield 15 SCL

6 TMDS Data1- 16 SDA

7 TMDS Data0+ 17 DDC/CEC Ground

8 TMDS Data0 Shield 18 +5V Power

9 TMDS Data0- 19 Hot Plug Detect

10 TMDS Clock+

Pin No Signal Assignment Pin No Signal Assignment

1 Red Out 9 +5V DC

2 Green Out 10 Sync Return (Ground)

3 Blue Out 11 Monitor ID0 in Display

4 Unused 12 DCC Serial Data

5 Ground 13 Horizontal Sync

6 Red Return 14 Vertical Sync

7 Green Return (Ground) 15 DCC Serial Clock

8 Blue Return (Ground)

- 8 -

SE2

RM-ED009

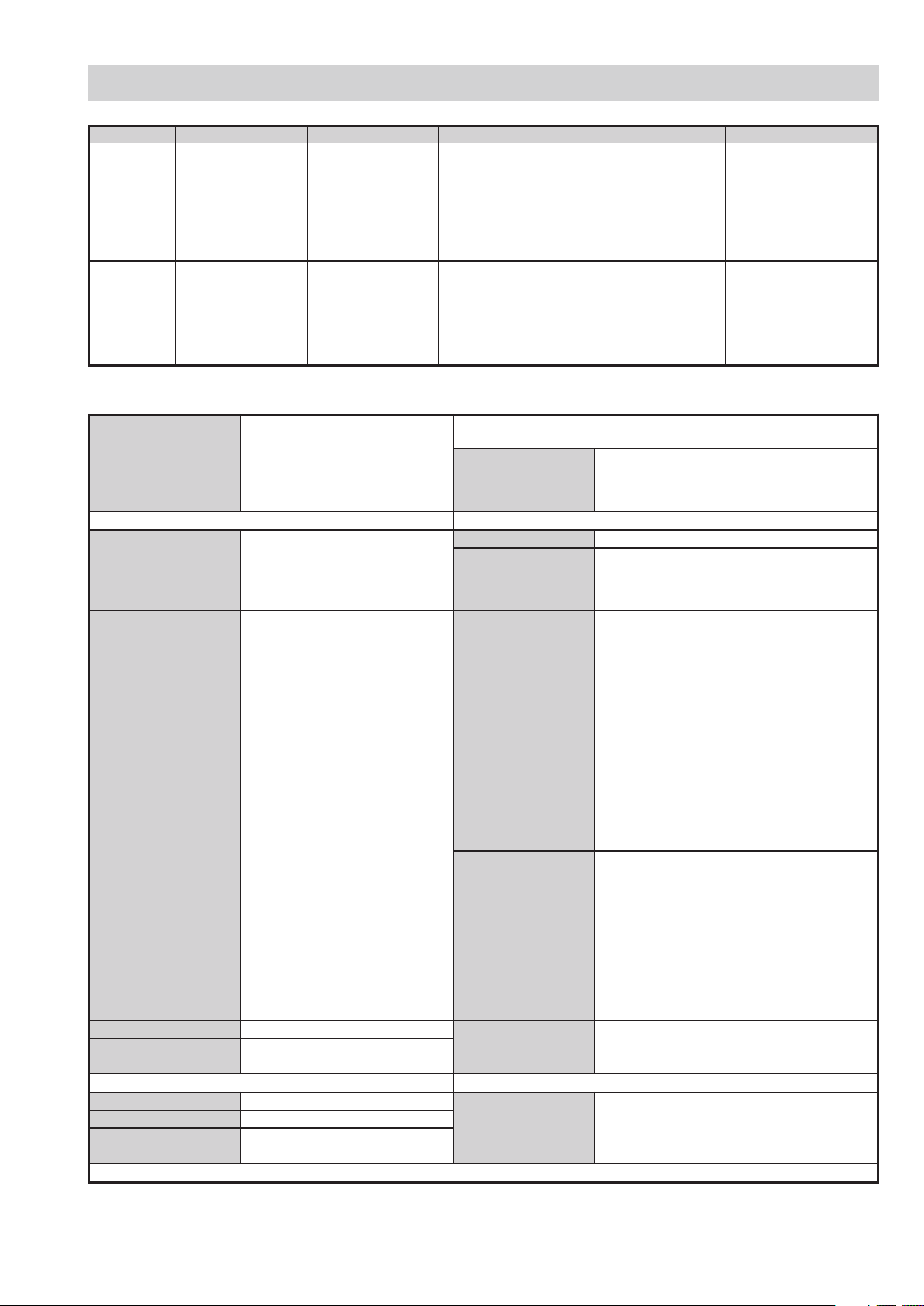

SE2 SELF DIAGNOSTIC SOFTWARE

The identification of errors within the SE2 chassis is triggered in one of two ways :- 1: Busy or 2: Device failure to respond to IIC. In the event

of one of these situations arising the software will first try to release the bus if busy (Failure to do so will report with a continuous flashing

LED) and then communicate with each device in turn to establish if a device is faulty. If a device is found to be faulty the relevant device number

will be displayed through the LED (Series of flashes which must be counted).

LED Error Code

Error Descriptions

Number of LED

Flashes

Error Description Checked Action

02 Balancer error. In normal mode. Goes into standby.

03 Power supply protection error. In normal mode. Goes into standby.

04 Inverter error. In normal mode. Goes into standby.

05 NVM error. In initialisation state. Adds error to error menu.

06 IIC error. In normal mode. Adds error to error menu.

07 HDMI error. In initialisation state. Adds error to error menu.

08 Digital error. In normal mode. Adds error to error menu.

09 Tuner Error In initialisation state. Adds error to error menu.

10 Sound processor In initialisation state. Adds error to error menu.

13 Real time clock error In initialisation state. Adds error to error menu.

Error Description Meaning/Related Fault

Balancer error. Balancer error/PANEL_DET (PMUX2.0) to low level, between 2.48V and 0.83V.

Power supply protection error. 5V, 3.3V or 1.8V failure/POWER_DET (P3_6) to high level.

Panel error. Inverter failure/PANEL_DET (PMUX2.0) to low level, less than 0.83V.

NVM error. EEPROM cannot be read or written.

IIC error. IIC bus cannot be correctly initialised.

HDMI error. HDCP cannot be set-up correctly.

Digital error. Digital CPU does not respond by DPI communication (Only for digital models).

Tuner Error IF circuit or PLL circuit does not respond to IIC commands.

Sound processor MSP3410G IC does not respond to IIC commands.

Real time clock error RTC IC does not respond to IIC commands (Only for digital models).

– 9 –

SE2

RM-ED009

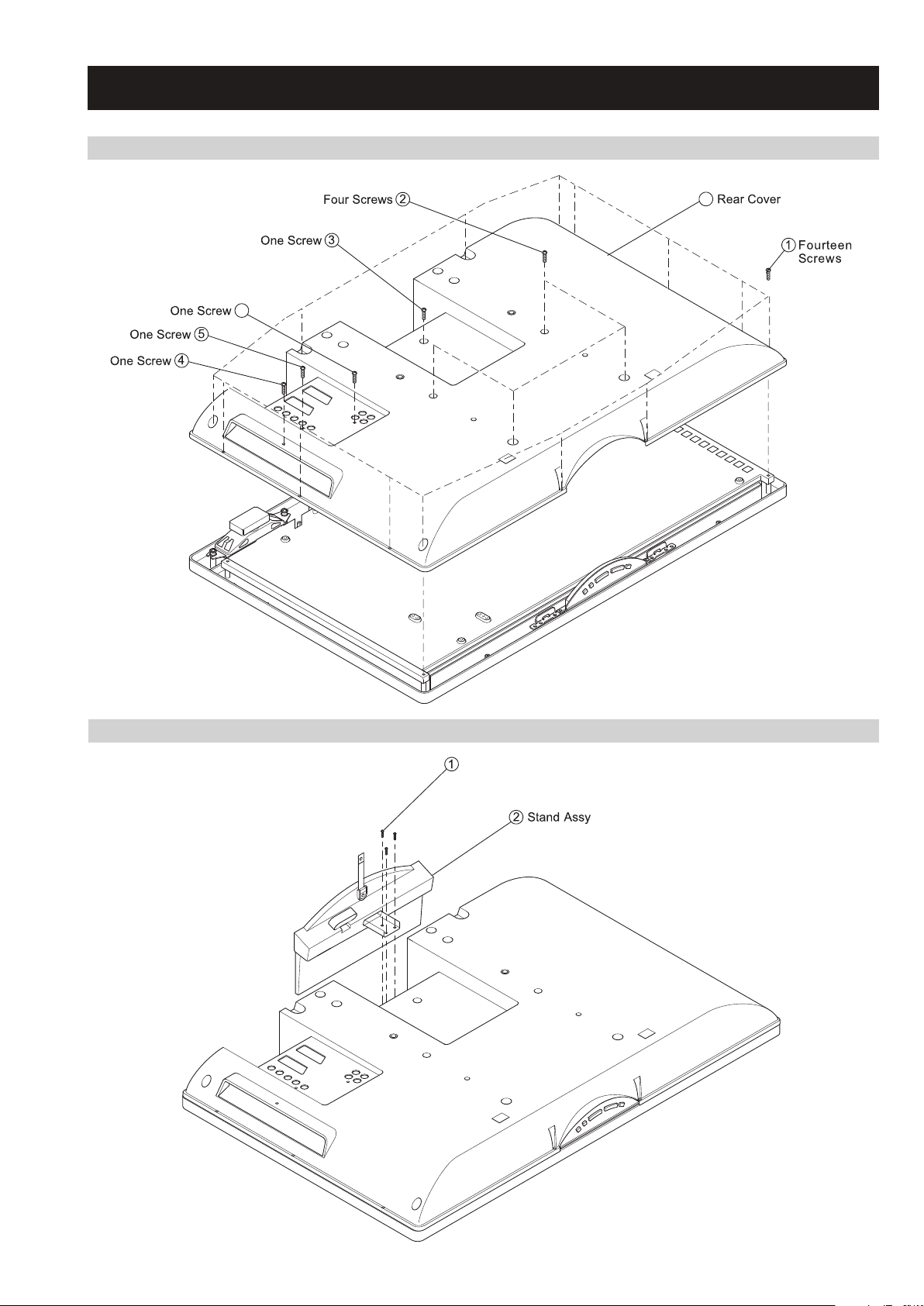

SECTION 2 DISASSEMBLY

2-2. STAND REMOVAL (26 & 32 inches)

2-1. REAR COVER REMOVAL

6

7

Three Screws

– 10 –

SE2

RM-ED009

2-3. STAND REMOVAL (37 & 40 inches)

2-4. LOUDSPEAKER REMOVAL

Loudspeaker

Two Screws

– 11 –

SE2

RM-ED009

2-5. B1 BOARD REMOVAL

2-6. DS1 BOARD REMOVAL (40 inches)

Four Screws

DS1 Board

2

Six Screws

B1 Board

– 12 –

SE2

RM-ED009

2-7. GS2 BOARD REMOVAL (26 & 32 inches)

2-8. GS3/GS4 BOARD REMOVAL (37/40 inches)

Six Screws

GS3/GS4 Board

2

Four Screws

GS2 Board

– 13 –

SE2

RM-ED009

2-9. H1PS BOARD REMOVAL

2-10. H3PS BOARD REMOVAL

H3PS Board

One Screw

H1PS Board

Two Screws

– 14 –

SE2

RM-ED009

2-11. LCD PANEL REMOVAL

Two Screws

LCD Panel

One Screw

2

Two Screws

3

4

5

6

One Screw

- 15 -

SE2

RM-ED009

3-1. Electrical Adjustments

Service adjustments to this model can be performed using the

supplied remote commander RM-ED009.

SECTION 3 CIRCUIT ADJUSTMENTS

‘TT—’ will appear in the upper right corner of the screen.

Other status information will also be displayed (See 3-3 page

18).

3. Press ‘MENU’ on the remote commander to obtain the

following menu on the screen.

4. Move to the corresponding adjustment item using the

up or down arrow buttons on the Remote Commander.

5. Press the right arrow button to enter into the required menu

item.

6. Press the ‘Menu’ button on the Remote Commander to quit

the Service Mode when all adjustments have been completed.

Note :

• After carrying out the service adjustments, to prevent the

customer accessing the ‘Service Menu’ switch the TV set

OFF and then ON again.

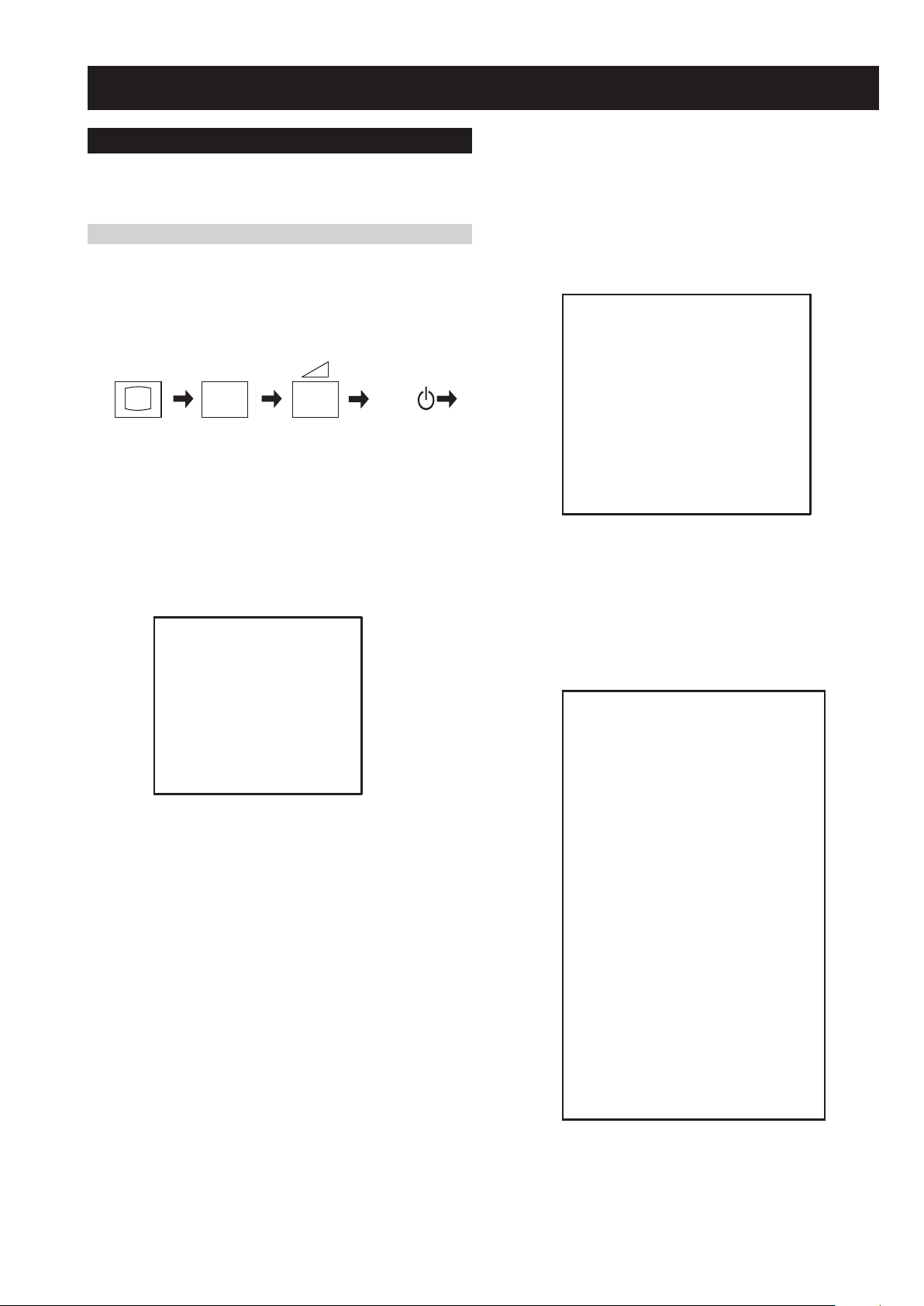

How to enter into the Service Mode

BACKLIGHT

BACKLIGHT

U BACKLIGHT

BL SETUDEN

BL BOTTOM

ECO MODE

APL MAX

DIMMER MIN

APL FACTOR

OSD CONTR MIN

DIMMER

APL MIN

(0, 255)

(0, 10)

(0, 255)

(0, 255)

(0, 1)

(0, 255)

(-128, +127)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

235

10

38

92

1

140

-32

0

40

186

103

HDMI

VAI2

VAI3

Vper MSB

Vper ISB

Hper MSB

HS Width MSB

STM LSB

Ri (MSB)

Ri (LSB)

Aksv_0

Aksv_1

Aksv_2

Aksv_3

Aksv_4

An_0

An_1

An_2

An_3

An_4

An_5

An_6

An_7

Pj

Ainfo

Flags

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

0

0

3

31

0

0

176

218

101

0

0

0

0

0

0

0

0

0

0

0

0

0

202

0

6

+

BACKLIGHT

HDMI

SOUND

IF ADJUST

PANEL TEMP

ERROR MENU

SE2 v0.10

FACTORY DATA: 11111111

SERIAL NUMBER: 4294967295

WORKING TIME: 0:22

1. Turn on the power to the TV set and enter into the stand-by

mode.

2. Press the following sequence of buttons on the remote

commander.

i+

5

+

(ON SCREEN (DIGIT 5) (VOLUME +) (TV)

DISPLAY)

I/

TV

- 16 -

SE2

RM-ED009

IF ADJUST

Automute

Audio Gain

L Gating

Coincidence

AFT window

AFT Status

AGC TOP (-16, +15)

0

0

0

0

1

0111

+0

SOUND

Lineout offset

M-N

M-D

M-S

S-M

D-M

N-M

Effect Mode

BBE Mode

BBE Vol main

BBE Vol res

B1

B2

B3

B4

B5

Loudness

MB_STR

MB_LIM

MB_HMC

MB_LP

MB_HP

SUBW_FREQ

NICAM C AD

NICAM Error

Stereo

(-80, +40)

(0, 511)

(-128, -1)

(+0, +127)

(+0, +127)

(-128, -1)

(0, 1023)

(+0, +2)

(-0, +127)

(+0, +255)

(+0, +7)

(-96, +96)

(-96, +96)

(-96, +96)

(-96, +96)

(-96, +96)

(+0, +68)

(+0, -127)

(-32, +0)

(+0, +127)

(+5, +30)

(+3, +30)

(+5, +40)

(0, 2047)

(-128, +127)

00000

+8

192

-20

+20

+10

-10

496

+1

+0

+3

+0

+8

+2

-12

-12

+6

+23

+0

+0

+0

+5

+3

+5

2047

+0

Status 0000000110

ERROR MENU

E02: BALANCER

E03: DC Fail

E04: INVERTER

E05: NVM

E06: IIC

E07: HDMI

E08: DIGITAL

E09: TUNER

E10: SP

E13: RTC

WORKING TIME

HOURS

MINUTES

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 255)

(0, 65535)

(0, 59)

0

0

0

0

0

0

0

0

0

0

0

0

PANEL TEMP

TEMPERATURE (0, 125) 33

- 17 -

SE2

RM-ED009

TT mode is available by setting the TV for operation in Service Mode [ As shown on Page 15 ] , OSD ‘TT’ appears. The functions described

below are available by selecting the two numbers. To release the ‘Test mode 2’, press 00, 10, 20 ... twice or switch the TV set into Stand-by

mode. In ‘TT Menu’ mode, it is possible to remove the Menu from the screen by pressing the Speaker Off button once. Pressing the Speaker

OFF button a second time will cause the Menu to reappear. The function is kept even when the menu is not displayed on screen !!.

3-2. TT MODE

00

'TT' mode off

03

Set volume to 35%

04

Set volume to 50%

05

Set volume to 65%

06

Set volume to 80%

07

Ageing mode on

08

Shipping Condition

09

WB adj initial conditions

14

Teletext centered

19

Factory toggle mode (on/off)

27

CBA mode toggle (ON/OFF)

31

ECS mode toggle (ON/OFF)

32

Set BCN channels preset

33

Connect/Disconnect EDID write o general I2C bus

34

HDMI log enable/disable

35 Hotel mode toggle

37

PC Monitor mode toggle

38 OTRUM mode

39

Enable Digital Test

41 Re-initialise NVM

43

Select Dual Sound "A"

44

Select Dual Sound "B"

45

Select Dual Sound "Mono"

46

Select Dual Sound "Stereo"

48

Set NVM as non-virgin

49

Set NVM as virgin

51

Hybrid/ALPS tuner selection

52

Temperature sensor enable/disable

53

Digital/Analog model

54

Watchdog toggle

55

Audio delay toggle

56

Set Bravia Model enable/disable

57

MSP Auto Carrier Mute function enable/disable

58

Chip select toggle

59

Visual I2C toggle

61

Set 15" 4:3 XGA settings

62

Set 20" 4:3 VGA settings

63

Set 20" WXGA settings

64

Set 23" WXGA settings

65

Set 26" WXGA settings

66

Set 32" WXGA settings

67

Set 37" WXGA settings

68

Set 40" WXGA settings

71 Auto AGC

72

AM from baseband (AFRIC dem) or fromRF (MSP

dem)

73 HDMI number of inputs (0 to 2)

74

DDC enable

75

Set centred balance

76 Set volume to max

77

Set volume to min

78

Set balance full left

79

Set balance full right

81

Digital BER display

82

Digital Service menu

83

Digital colour bar output from DENC

84

TS CI path through

85

Digital tuner power down (Only 1 power cycle,default

is no power down)

86

Switch between two digital SW banks

87 Local keys test

88

Digital shipping conditions (Clear tune database)

89 LED test

91

OAD enable/disable toggle

92

TS CI path through with Reed Solomon off

94

Spread spectrum toggle

96

Digital debug output enable/disable

97

Digital 656 output enable/disable

98

Digital auto reset function enable/disable

99

Display error and working time menu

- 18 -

SE2

RM-ED009

1. Panel size configuration. Changed by TT61...TT68.

2. D/A: D is shown when Digital mode is enabled; A is shown when Analogue mode is enabled. Changed by TT53.

3. TT-- command prompt.

4. ECS/---: ECS enabled/disabled (TT31).

5. CBA/--: CBA is shown when the TV set is in CBA mode (This mode is available from Factory mode TT19). Changed by TT27.

6. Norm/Fact: Normal or Factory mode. Changed by TT19.

7. DDC/---: DDC enabled/disabled. Changed by TT74.

8. 0/1/2: 0 or 2 HDMI inputs toggle. Changed by TT73.

9. E/-: E is shown when EDID WP is enabled; - is shown otherwise. Changed by TT33.

10. M/HO/-: M is shown when PC monitor mode is enabled changed by TT37; H is shown when Hotel mode is enabled changed by TT35;

O is shown when OTRUM is enabled changed by TT38; - is shown otherwise.

11. C/-: C (Default value) is shown when MSP Auto Carrier Mute function is enabled; - is shown otherwise. Changed by TT57.

12. M/A: M (Default value) is shown when AM sound is demodulated in MSP; A is shown when AFRIC demodulator is used. Changed by

TT72.

13. N/A: Previously used to indicate Clk enabled.

14. T/-: T is shown when digital test is enabled; - is shown otherwise. Changed by TT39.

15. W/-: W is shown when watchdog is enabled; - is shown otherwise. Changed by TT54.

16. C/-: C is shown when chip select is enabled; - is shown instead. This mode is only available in factory mode. Changed by TT58.

17. V/-: V is shown when visual I2C is enabled; - is shown otherwise. Changed by TT59.

18. D/-: D is shown when audio delay is enabled; - is shown otherwise. Changed by TT55.

19. K/-: K is shown when spread spectrum is enabled; - is shown otherwise. Changed by TT94.

20. B/-: B is shown for BRAVIA models; -is shown otherwise. This mode is only available in factory mode. Changed by TT56.

21. S/-: S is shown if temperature sensor is enabled; - is shown otherwise. Changed by TT52.

22. L/-: L is shown when HDMI is enabled; - is shown otherwise. Changed by TT34.

23. X/-: X is shown when teletext is centered (Default value); - is shown otherwise. Changed by TT14.

24. H/A: H is shown when Hybrid tuner is selected; A is shown if ALPS tuner is selected. Changed by TT51.

3-3. TT OSD Labels

Key:

(1)

2 6

"

D

(2)

T T - -

(3)

E C S

(4)

C B A

(5)

B

(20)

N o r m

(6)

D D C

(7)

2

(8)

E

(9)

S

(21)

H

(10)

C

(11)

M

(12)

L

(22)

-

(13)

T

(14)

W

(15)

C

(16)

V

(17)

D

(18)

K

(19)

X

(23)

H

(24)

- 19 -

SE2

RM-ED009

4-1. BLOCK DIAGRAM

COFDM

Decoder

NAND

DDR

VIDEO PROCESSOR

IF IC

TUNER

P

A

N

N

E

L

H1PS

SWITCH-BUTTONS

H3PS

SIRCS, LED

SPEAKERS

AMPLIFIER

GS2, GS3, GS4 POWER SUPPLY BOARD

HP AMPLIFIER

VIDEO PROCESSOR

SPEAKERS

HDMI decoder

B1

SIGNAL BOARD

T-CON

INVERTER

DS1

BALANCER

(only for 40"

panel)

B

U

F

F

E

R

S

PCMCIA

JIG MS

RF

HDMI1

HDMI2

HP

Video

Audio

side in

AUDIO

OUT

SCART1

SCART2

AUDIO

PC

PC

AUDIO

HDMI

COMP

- 20 -

SE2

RM-ED009

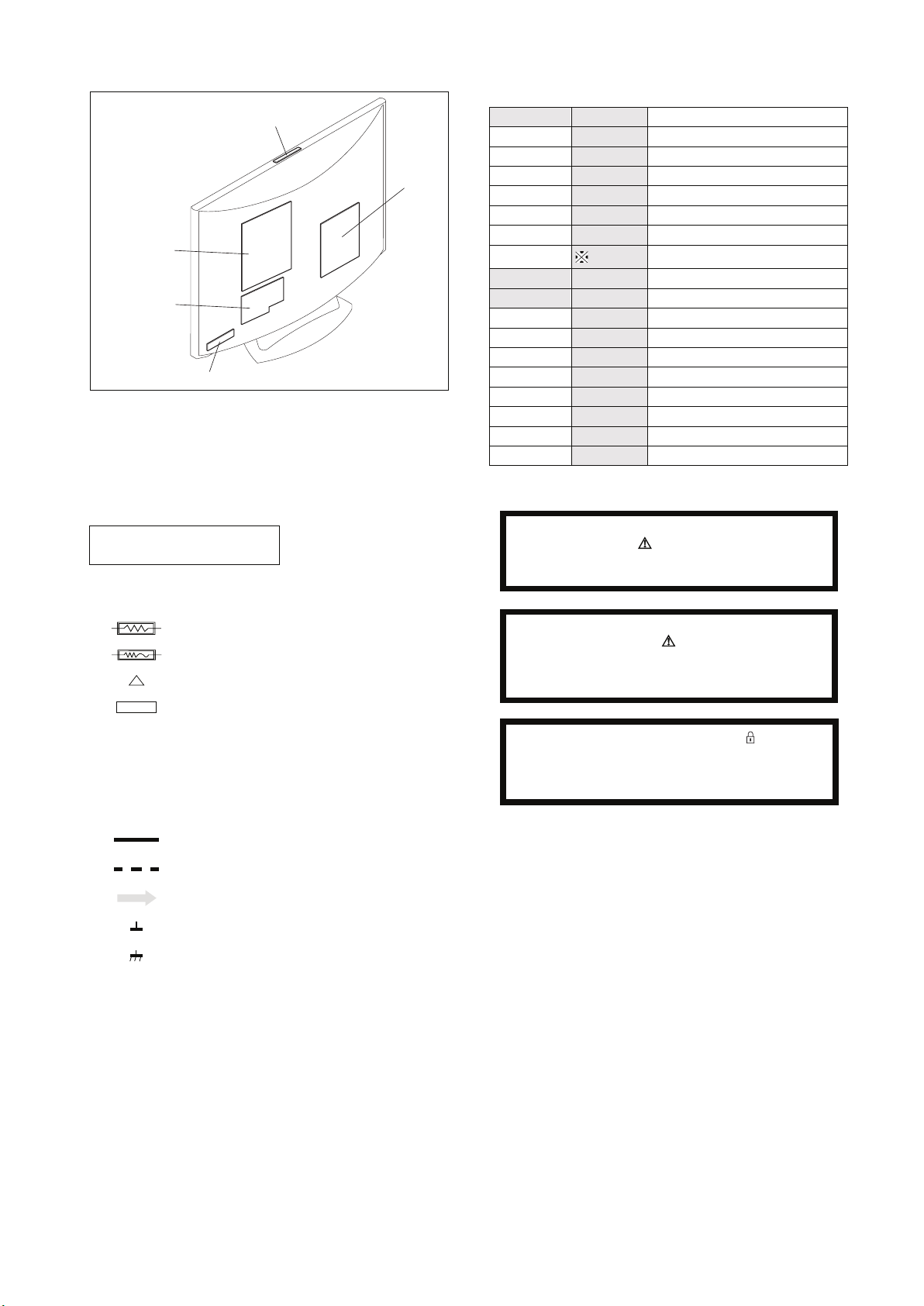

5-2. CIRCUIT BOARD LOCATION

5-3. SCHEMATIC DIAGRAMS AND

PRINTED WIRING BOARDS

Note :

• All capacitors are in µF unless otherwise noted.

• pF : µµF 50WV or less are not indicated except for

electrolytic types.

• Indication of resistance, which does not have one for

rating electrical power, is as follows.

Pitch : 5mm

Electrical power rating : 1/4W

• Chip resistors are 1/10W

• All resistors are in ohms.

k = 1000 ohms, M = 1000,000 ohms

• : nonflammable resistor.

• : fusible resistor.

• : internal component.

• : panel designation or adjustment for repair.

• All variable and adjustable resistors have

characteristic curve B, unless otherwise noted.

• All voltages are in Volts.

• Readings are taken with a 10Mohm digital mutimeter.

• Readings are taken with a color bar input signal.

• Voltage variations may be noted due to normal production

tolerences.

• : B + bus.

• : B - bus.

• : RF signal path.

• : earth - ground.

• : earth - chassis.

Reference Information

RESISTOR RN

: METAL FILM

RC

: SOLID

FPRD

: NON FLAMMABLE CARBON

FUSE

: NON FLAMMABLE FUSIBLE

RS

: NON FLAMMABLE METAL OXIDE

RB

: NON FLAMMABLE CEMENT

RW

: NON FLAMMABLE WIREWOUND

: ADJUSTMENT RESISTOR

COIL LF-8L

: MICRO INDUCTOR

CAPACITOR TA

: TANTALUM

PS

: STYROL

PP

: POLYPROPYLENE

PT

: MYLAR

MPS

: METALIZED POLYESTER

MPP

: METALIZED POLYPROPYLENE

ALB

: BIPOLAR

ALT

: HIGH TEMPERATURE

ALR

: HIGH RIPPLE

Les composants identifiés par une trame et

par une marque sont d'une importance

critique pour la sécurité. Ne les remplacer

que par des pièces de numéro spécifié.

specified.

Note :

The components identified by shading

and marked are critical for safety.

Replace only with the part numbers

specified in the parts list.

Note :

CVM Board

A Board

S1 Board

VM

C

H

D1

A

J

A2

N

D

A1

D2

C

A

4-2. CIRCUIT BOARD LOCATION

4-3. SCHEMATIC DIAGRAMS AND

PRINTED WIRING BOARDS

Note :

The components identified by mark

contain

confidential information.

Strictly follow the instructions whenever the

components are repaired and/or replaced.

Note: Schematic diagrams are for reference only. Please refer to the electrical parts list for

the correct value and part number of components.

H3PS

H1PS

GS2/GS3/GS4

B1

DS1

- 21 -

O

P

10

A B C D E F G H JI K L M N

1

2

3

4

5

6

7

8

9

11

12

Q

JL7 105

C7120

XX

R7111

4. 7k

JL7 102

C7105

0 .1

R7103

XX

C7121

XX

TP7104

C7109

0 .1

FE_MS_BS

FE_RXD1B

TP7107

JL7 1

1

C7108

0 .1

TV_DEM_SEL

TP7119

DIG_OSD_STATUS

JL7 107

3.3V_MAIN

FE_NCI1_OVR

C7110

0 .1

C7117

XX

FE_M_SYNC

FE_FTV_CONFIG2

R7104100

FE_MS_CLK

FE_TXD0B

R7114

XX

R7107 47

FB7100

0uH

GND_1

C7100

XX

JL7 103

R7108 47

JL7 106

R7122 47

C7106

0 .1

TP7103

FE_USB_DN

E8 E9 E10 E11 E 12 E13 E6 E7 E14 E 15 E16 H5 H17 J5 J17 K5 K17 L5 L1 7 M5 N5 P5 P17 R5 T5 U7 U8 U9 U10 U14 U15 U16

R17

P21

R20

R21

T20

T21

U18

U19

U20

U21

AA3

Y4

W4

W3

V5

Y3

AA2

V15

AA1

W15

Y15

AA5

AA6

B5

C5

M19

L20

W19

AA19

N18

L21

Y8

AA8

Y7

AA7

P19

R18

N20

V18

P18

W18

T19

T18

N21

P20

R19

V9W7Y6

V8

W6

Y5

AA4

W5

V6

D20

F19

F18

E21

E19

H21

E20

M18

N19

E18

IC7100

VDD3_USB

R17

USBCLKI / PPORT105

P21

USB_DP1

R20

USB_DN1

R21

USB_DP0

T20

USB_DN0

T21

USB_PPON1 / PPORT109

U18

USB_OCI1 / PPORT108

U19

USB_PPON0 / PPORT107

U20

USB_OCI0 / PPORT106

U21

MSDATA3 / PPORT127

AA3

MSDATA2 / PPORT126Y4MSDATA1 / PPORT132

W4

MSDIO/DATA0 / PPORT131

W3

MSDIR / PPORT128

V5

MSBS / PPORT130

Y3

MSCLK / PPORT129

AA2

TXD0B / CAP/COMP0 / PPORT110

V15

RXD0B / CAP/COMP3 / PPORT137

AA1

CTS0B / CAP/COMP1 / PPORT111

W15

RTS0B / CAP/COMP2 / PPORT112

Y15

TXD1B

AA5

RXD1B

AA6

RTS1B_B / STP0_STRT / PPORT10

B5

CTS1B_B / STP0_ERRB / PPORT11

C5

DCD1B / PPORT55

M19

RI1B / PPORT54

L20

TXD2B / PPORT14

W19

RXD2B / PPORT13

AA19

TXD3B / PPORT53

N18

RXD3B / PPORT52

L21

SDA1

Y8

SCL1

AA8

SDA0

Y7

SCL0

AA7

SCKINOUT / PPORT46

P19

SDIN / PPORT44

R18

SDOUT / PPORT45

N20

IR_IN_1 / PPORT47

V18

IR_IN_0 / PPORT51

P18

IR_OUT / PPORT48

W18

SMRST0 / PPORT39

T19

CMDVCC0 / RI0B / PPORT40

T18

OFF0 / DCD0B / PPORT41

N21

SMCLK0 / DTR0B / PPORT42

P20

SMDAT0 / DSR0B / PPORT43

R19

AO1_DAT / PPORT125

V9

AO1_LRCK / PPORT123

W7

AO1_BCK / PPORT124

Y6

AO1_MCK / PPORT122

V8

AO0_DAT

W6

AO0_LRCK

Y5

AO0_BCK

AA4

AO0_MCK

W5

ATX

V6

PAR / PPORT56

D20

FRAMEB / PPORT57

F19

IRDYB / PPORT58

F18

TRDYB / PPORT59

E21

STOPB / PPORT60

E19

IDSEL / PPORT61

H21

DEVSELB / PPORT62

E20

REQB0 / PPORT63

M18

GNTB0 / PPORT64

N19

PERRB / PPORT65

E18

VDD2

E8

VDD2

E9

VDD2

E10

VDD2

E11

VDD2

E12

VDD2

E13

VDD1

E6

VDD1

E7

VDD1

E14

VDD1

E15

VDD1

E16

VDD1

H5

VDD1

H17

VDD1

J5

VDD1

J17

VDD1

K5

VDD1

K17

VDD1

L5

VDD1

L17

VDD1

M5

VDD1

N5

VDD1

P5

VDD1

P17

VDD1

R5

VDD1

T5

VDD1

U7

VDD1

U8

VDD1

U9

VDD1

U10

VDD1

U14

VDD1

U15

VDD1

U16

R7119 47

GND_1

JL7 110

R7102

XX

TP7105

FE_NCI_EN

FB7105 0uH

GND_1

R7113

XX

R7101

10k

FB7107

0uH

R7112

4. 7k

FB7102

0uH

FE_RXD0B

TP7115

R7118 47

RB7100

100

2143658

7

R7126

47

FE_FTV_CONFIG0

R7117 XX

FE_+1V5

FB7106 0uH

R7100

10k

JL7 100

FE_MS_INS

C7104

0 .1

FE_TXD1B

FB7104 0uH

R7127

47

FE_USB_PON

3.3V_MAIN

R7120 47

TP7102

R7115 47

FE_NDEMOD_RESET

R7105XX

C7119

XX

SDA_DIGITAL

TP7120

FE_CI1_PWR_EN

R7106100

C7101

4 .7

TP7106

SDA_EMMA

R7116 47

TP7112

FE_USB_PON

RB7101 1 0k

FE_NUSB_OVR

R7110 47

3.3V_MAIN

FE_MS_DAT[0]

FE_JIG_MODE

TP7100

JL7 109

FE_ABCK,FE_ADO,FE_ALRCK,FE_AMCK

FE_USB_DP

TP7101

3.3V_MAIN

JL7 104

SCL_DIGITAL

R7109 47

C7107

0 .1

FE_FTV_CONFIG1

SCL_EMMA

JL7 108

FE_ADO

FE_ABCK

FE_ALRCK

FE_NDEMOD_RESET

SIGN14963

SIGN14971

SIGN14979

SIGN14984

FE_AMCK

SIGN14994

SIGN15007

SIGN15015

CI2_VS1B

VDO_VHSB /

CI2_CD1B

CI2_RSTB

nCI2_TSEN

THIS CAPACITOR TO BE

PLACED UNDERNEATH BGA

CI2_IREQB

THESE CAPACITORS TO BE PLACED UNDERNEATH BGA

VDO_VVSB /

B1.SE2

B1

1A/13

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 1A/13 ~

- 22 -

DDCCBBP

EE

FF

Z

1

2

3

4

5

6

7

8

9

10

11

12

Q R S T U V W X Y AA

GND_1

R7142

200

R7143

200

FB7111

0uH

R7149

XX

GND_1

TP7126

C7129

XX

VDCLK,VDO[0-7]

FB7108

0uH

JL7 111

FB7109

0uH

FB7110

0uH

GND_1

TP7119

TP7124

FB7112

0uH

R7144

330

JL7 122

DIG_OSD_STATUS

JL7 107

TP7123

JL7 120

R7145

680

GND_1

R7136

200

TP7121

C7130

XX

JL7 119

FE_CVBS

C7134

XX

R7122 47

C7136

0 .1

W5

V6

D20

F19

F18

E21

E19

H21

E20

M18

N19

E18

B17

C17

D17

D21

M20

K21

A17

C18

B21

A21

B20

A20

A19

B18

A18

G20

G19

G18

F21

D18

C21

C20

C19

K18

J2 1

J2 0

J1 9

H19

H18

G21

J1 8

F20

D19

B19

L19

L18

K20

K19

V21

V20

W21

W20

Y21

Y20

AA21

V19

Y19

V11

V12

W12

AA12

AA13

Y12

W13

Y11

Y13

W11

V14

W14

Y14

AA14

L9 L 10 L 11 L 12 L 13 M9 M10 M11 M12 M13 N9 N10 N11 N12 N13 U11 U12 U13 V13 W10 V10 AA10 Y9 W9 W8 AA9

AA20

H20

IC7100

3

GND

L9

GND

L10

GND

L11

GND

L12

GND

L13

GND

M9

GND

M10

GND

M11

GND

M12

GND

M13

GND

N9

GND

N10

GND

N11

GND

N12

GND

N13

AGNDV

U11

AGNDV

U12

AGNDV

U13

AGNDV

V13

TEST / GND

W10

NMI/EDINT

V10

JTRST

AA10

JTMS

Y9

JTDO

W9

JTDI

W8

JTCK

AA9

AO0_MCK

W5

ATX

V6

PAR / PPORT56

D20

FRAMEB / PPORT57

F19

IRDYB / PPORT58

F18

TRDYB / PPORT59

E21

STOPB / PPORT60

E19

IDSEL / PPORT61

H21

DEVSELB / PPORT62

E20

REQB0 / PPORT63

M18

GNTB0 / PPORT64

N19

PERRB / PPORT65

E18

VDOE_VCK_IN / AD1 / PPORT70

B17

VDOE_VVSB_IN / AD2 / PPORT71

C17

VDOE_VHSB_IN / AD3 / PPORT72

D17

VDOE_VCK / SERRB / PPORT66

D21

VDOE_VVSB_OUT / INTAB / PPORT67

M20

VDOE_VHSB_OUT / PCICLK / PPORT68

K21

VDOE_FLD / AD0 / PPORT69

A17

VDOE_A7 / AD11 / PPORT80

C18

VDOE_A6 / AD10 / PPORT79

B21

VDOE_A5 / AD9 / PPORT78

A21

VDOE_A4 / AD8 / PPORT77

B20

VDOE_A3 / AD7 / PPORT76

A20

VDOE_A2 / AD6 / PPORT75

A19

VDOE_A1 / AD5 / PPORT74

B18

VDOE_A0 / AD4 / PPORT73

A18

VDOE_R7 / AD19 / PPORT88

G20

VDOE_R6 / AD18 / PPORT87

G19

VDOE_R5 / AD17 / PPORT86

G18

VDOE_R4 / AD16 / PPORT85

F21

VDOE_R3 / AD15 / PPORT84

D18

VDOE_R2 / AD14 / PPORT83

C21

VDOE_R1 / AD13 / PPORT82

C20

VDOE_R0 / AD12 / PPORT81

C19

VDOE_G7 / AD27 / PPORT96

K18

VDOE_G6 / AD26 / PPORT95

J21

VDOE_G5 / AD25 / PPORT94

J20

VDOE_G4 / AD24 / PPORT93

J19

VDOE_G3 / AD23 / PPORT92

H20

VDOE_G2 / AD22 / PPORT91

H19

VDOE_G1 / AD21 / PPORT90

H18

VDOE_G0 / AD20 / PPORT89

G21

VDOE_B7 / CBE3 / PPORT104

J18

VDOE_B6 / CBE2 / PPORT103

F20

VDOE_B5 / CBE1 / PPORT102

D19

VDOE_B4 / CBE0 / PPORT101

B19

VDOE_B3 / AD31 / PPORT100

L19

VDOE_B2 / AD30 / PPORT99

L18

VDOE_B1 / AD29 / PPORT98

K20

VDOE_B0 / AD28 / PPORT97

K19

VDO0_D7 / PPORT23

V21

VDO0_D6 / PPORT22

V20

VDO0_D5 / PPORT21

W21

VDO0_D4 / PPORT20

W20

VDO0_D3 / PPORT19

Y21

VDO0_D2 / PPORT18

Y20

VDO0_D1 / PPORT17

AA21

VDO0_D0 / PPORT16

AA20

VDO0_VCK / PPORT15

V19

VDO0_FLD / PPORT12

Y19

VAR

V11

VAG

V12

VAB

W12

VAY

AA12

VAC

AA13

VACVBS

Y12

VREF1

W13

VREF0

Y11

RSET1

Y13

RSET0

W11

AVDDV

V14

AVDDV

W14

AVDDV

Y14

AVDDV

AA14

JL7 110

C7137

0 .1

R7133

0

3.3V_MAIN

C7142

10

TP7125

R7137

200

C7143

0 .1

FE_NUSB_OVR

R7126

47

R7127

47

FE_+1V5

FE_NDEMOD_RESET

FB7117

0uH

TP7120

R7146

XX

C7132

10p

R7138

200

FE_USB_PON

L7100

10uH

TP7127

FE_JIG_MODE

TP7122

C7145

0 .1

TP7128

JL7 121

FB7116

0uH

C7133

XX

FE_JTCK,FE_JTDI,FE_JTDO,FE_JTMS,FE_JTRST,FE_NMI_EDINT

JL7 109

R7147

0

C7144

0 .1

FB7115

0uH

C7131

XX

FB7114

0uH

R7148

470

C7135

4 .7

R7141

200

FB7113

0uH

JL7 108

VDO[7]

FE_NMI_EDINT

VDO[6]

SIGN14954

VDO[5]

VDO[4]

FE_NDEMOD_RESET

VDCLK

VDO[3]

VDO[2]

VDO[1]

VDO[0]

SIGN14984

FE_JTCK

FE

_

AMCK

FE_JTDI

FE_JTDO

FE_JTMS

FE_JTRST

RESERVED FOR HI_RES GRAPHICS

U

NOTE RESISTORS R7153..R7158 ARE 0.5% TOLERANCE

THIS CAPACITOR TO BE

PLACED UNDERNEATH BGA

Y

THESE CAPACITORS

TO BE PLACED

UNDERNEATH BGA

NOTE SYMBOL

IS WRONG

V

CI2_CD2B

B1

1B/13

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 1B/13 ~

- 23 -

11

22

Q

O

P

A B C D E F G H JI K L M N

12

13

14

15

16

17

18

19

20

21

FE_CI1_VS1B

R7128

10k

FE_CI1_INPACKB

R7124 47

FE_CI1_CD1B

TP7109

3.3V_MAIN

C7103

XX

C7127

0 .1

FE_CI1_RSTB

R7125 47

TP7108

C7111

0 .1

C7124

0 .1

TP7116

3.3V_MAIN

FE_CI1_CD2B

GND_1

GND_1

TP7110

R7121 47

TP7113

E5 E17 F5 F 17 G5 G17 T17 U5 U6 U17 E8 E9 E10 E11 E12 E13 E6 E7 E

A16

B16

A15

B15

A14

B14

A13

B13

D13

C13

D14

C14

D15

C15

D16

C16

D12

A9B9D8

A8B8A7B7A6B6D6C6D7

C7

C8

D9

A11

A12

C11

C12

C9

D10

C10

D11

B10

A10

B11

B12

Y17

W17

V17

AA17

AA16

Y16

W16

V16

AA15

A1B2A2B3A3

C4

B4

A4A5D5

F4N4P2

G2R2G1K3V1C1Y1

P3

B1

E4

F2

IC7100

DQ15

A16

DQ14

B16

DQ13

A15

DQ12

B15

DQ11

A14

DQ10

B14

DQ9

A13

DQ8

B13

DQ7

D13

DQ6

C13

DQ5

D14

DQ4

C14

DQ3

D15

DQ2

C15

DQ1

D16

DQ0

C16

DADD13

D12

DADD12A9DADD11B9DADD10D8DADD9A8DADD8B8DADD7A7DADD6B7DADD5A6DADD4B6DADD3D6DADD2C6DADD1D7DADD0C7DBA1C8DBA0D9UDQM

A11

UDQS

A12

LDQM

C11

LDQS

C12

DCSBC9DRASB

D10

DCASB

C10

DWEB

D11

DCKE

B10

DCLK

A10

DCLKB

B11

DVREF

B12

VDI_D7 / PPORT121

Y17

VDI_D6 / PPORT120

W17

VDI_D5 / PPORT119

V17

VDI_D4 / PPORT118

AA17

VDI_D3 / PPORT117

AA16

VDI_D2 / PPORT116

Y16

VDI_D1 / PPORT115

W16

VDI_D0 / PPORT114

V16

VDI_VCK / PPORT113

AA15

STP0_DAT7 / PPORT8A1STP0_DAT6 / PPORT7B2STP0_DAT5 / PPORT6A2STP0_DAT4 / PPORT5B3STP0_DAT3 / PPORT4A3STP0_DAT2 / PPORT3C4STP0_DAT1 / PPORT2B4STP0_DAT0 / PPORT1A4STP0_EN / PPORT9A5STP0_CLK / PPORT0

D5

REGB / PPORT34F4IOWRB / PPORT31N4IORDB / PPORT30

P2

INPACKB / PPORT33G2GPIO_VS1B / PPORT28R2GPIO_RESET / PPORT32G1GPIO_IREQB / PPORT24K3GPIO_CD1B / PPORT26V1GPIO_CD2B / PPORT35C1PCE1B(CE2B_2) / PPORT36Y1PCE0B(CE2B_1) / PPORT27P3IOSI16B / PPORT25

B1

STP1_STRT / PPORT38E4STP1

_

EN / PPORT37

F2

VDD3

E5

VDD3

E17

VDD3

F5

VDD3

F17

VDD3

G5

VDD3

G17

VDD3

T17

VDD3

U5

VDD3

U6

VDD3

U17

VDD2

E8

VDD2

E9

VDD2

E10

VDD2

E11

VDD2

E12

VDD2

E13

VDD1

E6

VDD1

E7

VDD1

E

GND_1

C7125

0 .1

FE_+2V5_DDR

FE_IOWRB

C7118

10

FE_DADD[0-12]

TP7117

FE_D Q[0-15 ]

C7112

0 .1

C7113

0 .1

C7123

0 .1

C7122

0 .1

FE_DBA0,FE_DBA1,FE_DCASB,FE_DCKE,FE_DCLK,FE_DCLKB,FE_DCSB,FE_DQM0,FE_DQM1,FE_DQS0,FE_DQS1,FE_DRASB,FE

_DVREF,FE_DWEB

FE_REGB

C7115

0 .1

R7123 47

FE_CI1_IREQB

C7114

0 .1

TP7111

FB7103

0uH

TP7114

FE_+2V5

FE_IORDB

C7128

0 .1

FB7101

0uH

C7116

0 .1

FE_M_CKOUT,FE_M_DATA[0-7],FE_M_VAL

FE_CI_TSCLK,FE_CI_TSSYNC,FE_CI_TSVAL

C7126

0 .1

TP7118

JL7 101

C7102

4 .7

FE_DQ[8]

FE_CI_TSSYNC

FE_DQS0

FE_DADD[3]

FE_M_DATA[3]

FE_DQ[5]

FE_DQ[7]

FE_DQS1

FE_DQ[4]

FE_DQ[6]

FE_DADD[2]

FE_DQ[3]

FE_DQM0

FE_M_DATA[7]

FE_DQ[2]

FE_M_DATA[6]

FE_DADD[1]

FE CI TSCLK

FE_DCSB

FE_DQ[1]

FE_DVREF

FE_M_DATA[5]

FE_DADD[4]

FE_DQ[0]

FE_DADD[12]

FE_M_DATA[2]

FE_DRASB

FE_DADD[0]

FE_DADD[11]

FE_DCLKB

FE_DADD[9]

FE_DCASB

FE_DCLK

FE_M_DATA[0]

FE_DADD[10]

FE_DWEB

FE_CI_TSVAL

FE_M_DATA[1]

FE_DQ[15 ]

FE_DCKE

FE_DQ[14 ]

FE_DADD[8]

FE_DQ[13 ]

FE_DBA1

FE_M_VAL

FE_DQ[12 ]

FE_DADD[6]

SIGN15011

FE_DQ[11 ]

FE_DADD[7]

FE_DBA0

FE_DQ[10 ]

FE_DQM1

FE_DQ[9]

FE_DADD[5]

FE_M_DATA[4]

FE_M_CKOUT

THESE CAPACITORS TO BE PLACED UNDERNEATH BGA

/ RTS1B

THESE CAPACITORS TO BE PLACED UNDERNEATH BGA

/ CTS1B

THIS CAPACITOR TO BE

PLACED UNDERNEATH BGA

DIFFERENTIAL PAIR

OF CLOCK SIGNALS

COMPONENTS MARKED AS XX REFER TO PARTS LIST, WILL ONLY BE LISTED IF FITTED

B1

1C/13

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 1C/13 ~

- 24 -

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 1D/13 ~

11

21

22

R

Q

P

EE

FF

S

T

U

V

W

X

Y

Z

AA

BB

CC

DD

20

18

19

17

15

16

14

12

13

FE_CI1_VS1B

R7128

10k

FE_CI1_INPACKB

R7124 47

FE_CI1_CD1B

3.3V_MAIN

R7134 47

FE_PWMOUT

FB7118

0uH

FE_NAND_CLE

R7132 47

TP7130

FE_CI1_RSTB

R7129

47

GND_1

R7125 47

FE_CI1_CE1B

GND_1

FE_CI1_CD2B

C7139

0 .1

FE_NAND_ALE

M17 J9 J10 J1 1 J 12 J 13 K9 K10 K11 K12 K13 L9 L10 L11 L12 L 13 M9 M10 M11 M12 M13 N9 N10 N11 N

N4P2G2R2G1K3V1C1Y1

P3

B1

E4

F2

H1

R1

R3

T1

T3

U1D1D2

C3

U2R4V2W2V4C2D4

E2

J1G3J4

K4

L2

M2

N2

L4

M4

J3

H3

M1

N1K1N3

T2

M3

L3

H4

G4J2H2

F1

E3

E1

D3

V3

K2

L1

P1

T4

W1

U3

U4

AA18

Y18

Y2

P4

F3

AA11

Y10

V7

M21

N17

IC7100

IOWRB / PPORT31N4IORDB / PPORT30

P2

INPACKB / PPORT33G2GPIO_VS1B / PPORT28R2GPIO_RESET / PPORT32G1GPIO_IREQB / PPORT24K3GPIO_CD1B / PPORT26V1GPIO_CD2B / PPORT35C1PCE1B(CE2B_2) / PPORT36Y1PCE0B(CE2B_1) / PPORT27P3IOSI16B / PPORT25

B1

STP1_STRT / PPORT38E4STP1_EN / PPORT37F2STP1_CLK / PPORT29

H1

RDATA15 / STP1_DAT7 / BOOT_NAND_SEL1R1RDATA14 / STP1_DAT6 / BOOT_NAND_SEL0R3RDATA13 / STP1_DAT5 / BOOTSEL1T1RDATA12 / STP1_DAT4 / BOOTSEL0T3RDATA11 / STP1_DAT3 / MINIBOOTU1RDATA10 / STP1_DAT2 / BWSELD1RDATA9 / STP1_DAT1 / ROMBENDD2RDATA8 / STP1_DAT0 / MCLKSEL2

C3

RDATA7 / MCLKSEL1U2RDATA6 / MCLKSEL0R4RDATA5 / VRCLKSEL1V2RDATA4 / VRCLKSEL0W2RDATA3V4RDATA2 / MRGMODE1C2RDATA1 / MRGMODE0D4RDATA0 / ENDIAN

E2

RADD25 / HSD7 / EJTAG_MODEJ1RADD24 / HSD6 / DINT_ENG3RADD23 / HSD5 / DSYSELBJ4RADD22 / HSD4 / PCI_MODEK4RADD21 / HSD3 / PCI_SIZE1L2RADD20 / HSD2 / PCI_SIZE0M2RADD19 / HSD1 / NAND_CSN2RADD18 / HSD0L4RADD17 / PKTSTRTM4RADD16 / HSDEJ3RADD15 / HSDCLKH3RADD14M1RADD13N1RADD12K1RADD11N3RADD10T2RADD9M3RADD8L3RADD7H4RADD6G4RADD5J2RADD4H2RADD3F1RADD2E3RADD1E1RADD0

D3

FCSB1V3FCSB0K2FWEBL1FOEBP1NSEBT4NRBBW1NCLEU3NALE

U4

GCSB3 / PPORT50

AA18

GCSB2 / PPORT49

Y18

GCSB1Y2GCSB0P4GRDYB

F3

RSTSWB

AA11

RSTOUT

Y10

PWMOUTV7CLK27IN

M21

AVDDP

N17

AGNDP

M17

GND

J9

GND

J10

GND

J11

GND

J12

GND

J13

GND

K9

GND

K10

GND

K11

GND

K12

GND

K13

GND

L9

GND

L10

GND

L11

GND

L12

GND

L13

GND

M9

GND

M10

GND

M11

GND

M12

GND

M13

GND

N9

GND

N10

GND

N11

GND

N

R7135

XX

C7140

0 .1

FE_FCSB0

FE_NAND_RBB

FE_IOWRB

JL7 117

FE_+1V5

FE_CI1_WAITB

3.3V_MAIN

R7140

47

JL7 114

C7138

4 .7

C7141

0 .1

R7130 47

R7139

XX

FE_FWEB

R7123 47

JL7 115

FE_RADD[0-11]

FE_CI1_IREQB

FE_RADD[19- 25]

JL7 113

FE_ CI_TS D[0-7 ]

FE_IORDB

TP7129

JL7 112

JL7 116

FE_RDATA[0-7]

FE_NMASTER_RESET

JL7 118

R7131 47

FE_CI_TSCLK,FE_CI_TSSYNC,FE_CI_TSVAL

FE_CLK27M

FE_FOEB

FE_RADD[3]

FE_CI_TSSYNC

FE_RDATA[3]

FE_RADD[2]

FE_RDATA[2]

FE_RADD[1]

FE_RDATA[1]

FE_RADD[0]

FE_RDATA[0]

FE_RADD[25]

SIGN14950

FE_RADD[24]

FE_CI_TSCLK

FE_RADD[23]

FE_RADD[22]

FE_RADD[21]

FE_RADD[20]

FE_RADD[19]

SIGN14969

FE_CI _TSD[5]

SIGN14974

SIGN14976

FE_CI _TSD[7]

SIGN14981

SIGN14985

FE_CI _TSD[6]

SIGN14987

FE_CI _TSD[4]

SIGN14989

FE_CI_TSVAL

SIGN14991

FE_CI _TSD[3]

FE_RADD[11]

FE_CI _TSD[2]

FE_RADD[10]

FE_RADD[9]

FE_CI _TSD[1]

FE_RADD[8]

FE_CI _TSD[0]

SIGN15013

FE_RADD[7]

FE_RDATA[7]

SIGN15017

FE_RADD[6]

FE_RDATA[6]

FE_RADD[5]

FE_RDATA[5]

FE_RADD[4]

FE_RDATA[4]

CI2_CE2B

THIS CAPACITOR TO BE

PLACED UNDERNEATH BGA

B1

1D/13 MAIN MICRO CONTROLLER, HDMI/AV SIDE/PC INPUT, AUDIO PROCESSOR, SCARTS

- 25 -

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 2A/13 ~

10

11

12

13

14

15

16

1

5

6

4

2

3

8

9

7

J

I

H

K

L

M

D

C

A

B

E

F

G

J

I

H

K

L

M

D

C

A

B

E

F

G

3.3V_MAIN

TP7215

R7201

XX

FE_NAND_ALE

XX

R7216

10k

R7203

TP7213

FE_NAND_CLE

TP7207

68

RB7205

1

2

345

6

7

8

470

R7206

JL7 207

TP7202

TP7220

JL7 202

JL7 205

0uH

FB7200

100

RB720

7

1

35

7

1kRB7204

2143658

7

470

R7200

3.3V_MAIN

FE_DBA0,FE_DBA1,FE_DCASB,FE_DCKE,FE_DCLK,FE_DCLKB,FE_D

C

_DVREF,FE_DWEB

TP7205

470

R7207

GND_1

FE_RDATA[0-7]

XX

R7210

FE_FOEB

3.3V_MAIN

TP7210

TP7201

FE_NAND_RBB

JL7 209

XX

R7214

1k

R7204

XX

R7225

TP7216

GND_1

TP7209

0 .1

C7203

XX

R7211

4. 7k

R7208

XX

R7215

68

RB7206

1

2

345

6

7

8

0 .1

C7200

XX

R7205

JL7 203

FE_D Q[0-15 ]

TP7200

R7224

10k

10k

R7221

100

RB720

8

1

35

7

TP7218

TP7211

R7202

1k

GND_1

3.3V_MAIN

TP7206

TP7208

FE_FTV_CONFIG0

XX

R7222

JL7 210

1

C7201

GND_1

3.3V_MAIN

TP7219

48 43

65464321

47 45 44

42 41 37383940

1210 11987

36

313233

3435

181716

151413

30 29 28 27 2 6 25

242322212019

IC7 200

NC

NC

NC

NC

NC

NC

RB

FOE

CE

NC

NC

VCC

VSS

NC

NC

CLE

ALE

WE

WP

NC

NC

NC

NC

NC NC

NC

NC

NC

I/O 1

I/O 2

IO/ 3

IO/ 4

NC

NC

NC

VSS

VCC

LOCKPRE

NC

NC

IO/ 5

IO/ 6

IO/ 7

IO/ 8

NC

NC

NC

NC

6

R7217

FE_FTV_CONFIG2

FE_DADD[0-12]

JL7 208

GND_

1

GND_1

TP7204

JL7 204

100

RB720

9

1

35

7

10k

R7209

0 .1C7202

JL7 211

TP7217

JL7 206

XX

R7220

3.3V_MAIN

FE_FTV_CONFIG1

3.3V_MAIN

FE_RADD[19- 25]

TP7203

XX

R7212

FE_FWEB

GND_1

10k

R7223

C

FE_ CI_TS D[0-7 ]

10k

R7213

FE_FCSB0

TP7214

GND_1

TP7212

1k RB7200

214365871091211141316

15

1kRB7202

214365871091211141316

15

FE_DQ[2]

FE_DQ[6]

FE_RDATA[3]

FE_DADD[1]

FE_DQ[4]

FE_DQ[3]

FE_RADD[23]

GND_1

FE_RDATA[4]

FE_RDATA[5]

FE_CI _TSD[3]

FE_DWEB

FE_RDATA[5]

FE_DADD[0]

FE_RDATA[4]

FE_DADD[3]

FE_RDATA[2]

FE_DQ[7]

FE_DBA0

FE_DADD[10]

FE_RADD[21]

FE_RDATA[0]

FE_RDATA[1]

FE_RADD[24]

GND_1

FE_DCSB

FE_DQ[1]

FE_RADD[19]

FE_DQM0

FE_RDATA[2]

FE_RADD[22]

FE_DADD[2]

FE_RDATA[7]

FE_RDATA[6]

FE_RADD[25]

FE_RDATA[0]

FE_DBA1

FE_DCASB

FE_RADD[20]

3.3V_MAIN

GND_1

FE_DRASB

FE_RDATA[7]

FE_RDATA[3]

FE_CI _TSD[6]

FE_DQ[0]

FE_DQ[5]

FE_RDATA[6]

FE_DQS0

FE_RDATA[1]

FE_CI _TSD[5]

FE_CI _TSD[4]

FE_CI _TSD[7]

FE_CI _TSD[1]

FE_CI _TSD[0]

FE_CI _TSD[2]

PLACE R7201 &

R7202 ADJACENT

BOARD VERSION RESISTORS - MOUNT ON

SIDE-A

PLEASE PLACE COMPONENTS IN

FTV_C

O

RESERVED

NAND FLASH

VRCLKSEL1

LEAVE N.C. SO NOT USED

BOOT_NAND_SEL_1

BOOTSEL1

EJTAG_MODE

MCLKSEL1

FTV_C

O

DINT_EN

TO FORCE "BOOT FROM MEMORY STICK",

CONNECT (S HORT) TP7207 TO TP7 208, OR

CONNECT (SHORT) JL7200 T O JL7201

NOTE PIN 6 IS NOT GND ON SAMSUNG

NAND FLASH, ONLY TOSHIBA

FTV_C

O

BOARD VERSION RESISTORS - MOUNT ON

SIDE -B WITH JL’S O N SIDE- B

NANDCS

PCIMODE

27MH

Z

RD ATA [0] = 1 = EN DIA N = Bi g E ndi an

RD ATA [2: 1] = 10 = MR GMOD E1-0 = Ful l m erg e & Al l bytes

RDA TA[3] = -- = R ESER VED

RDAT A[5:4] = 10 = VRCLKSEL1 -0 = 187MHz

RDATA [8:6] = 101 = MCLKSEL2 -0 = 166MHz

RD ATA[ 9] = 1 = ROMB END = B ig E ndi an

RD ATA [10 ] = 1 = BW SEL = 8bi t

RD ATA [11 ] = 1 = MI NIB OOT = use mi nib oot

RDATA[ 13:1 2] = 11 = BOOTS EL1- 0 = Nand, t hen Memo ry S tic k

RDATA[ 15:14] = 0 0 = BOOT_NAND_SEL1-0 = <256mbi t

RADD [25] = 1 = EJTAG_ MODE = EJTAG

RA DD[ 24] = 0 = DI NT_ EN = d is abl e

RA DD[ 23] = 1 = DS YSE LB = m ain on ly

RA DD[ 22] = 1 = PC IMO DE = h ost

RA DD[21:2 0] = 00 = P CI_ SIZ E1-0 = 32M byt e

RA DD[1 9] = 0 = NANDCS = C S0

MCLKSEL2

BWSEL

MINIBOOT

DSYSELB

STRAP PINS

BOOT_NAND_SEL_0

VRCLKSEL0

ENDIAN

MRGMODE0

MRGMODE1

MCLKSEL0

THIS BOX IN SAME AREA ON PWB

S/

W

BOOTSEL0

ROMBEND

PCI_S IZE1

PCI_S IZE0

B1. -SE2

COMPONENTS MARKED AS XX REFER TO PARTS LIST, WILL ONLY BE LISTED IF FITTED

B1

2A /13

- 26 -

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 2B/13 ~

O

P

10

11

R

Q

O

P

S

T

U

V

W

15

16

14

12

13

Q R S T U V W

1

5

6

4

2

3

8

9

7

K

L

M

N

K

L

M

N

10k

R7226

100

R7231

JL7 217

RESET_N

1k

R7235

100 p

C7217

68

RB7205

1

2

345

6

7

8

JL7 207

GND_1

0

100 p

C7215

JL7 205

JL7 220

100

RB7207

1

2

345

6

7

8

TP7221

100

RB7211

1

2

345

6

7

8

RT1N141M-TP-1

Q7203

D

BA1,FE_DCASB,FE_DCKE,FE_DCLK,FE_DCLKB,FE_DCSB,FE_DQM0,FE_DQM1,FE_DQS0,FE_DQS1,FE_DRASB,FE

D

VREF,FE_DWEB

100 5

1/16W

CHIP

5%

R7243

10k

0. 01

C7231

3.3V_MAIN

C7219

0 .1

5V_MAIN

XX

C7230

JL7 209

0 .1

C7212

S

2SK20 36(TE85L)

Q7201

15uH

L7200

XX

R7225

100R7232

0uH

FB7201

100

RB7210

1

2

345

6

7

8

FE_CVBS

GND_1

68

RB7212

1

2

345

6

7

8

C7222

0 .1

JL7 223

X7200

RF_DIGITAL

68

RB7206

1

2

345

6

7

8

100R7229

Q7200

100 p

C7213

0 .1

C7208

R7224

10k

10k

R7221

100

RB7208

1

2

345

6

7

8

8

C7220

0. 1

TP7227

SCL

0 .1

C7210

3.3V_MAIN

GND_1

FE_CLK27M

3.3V_MAIN

100 p

C7216

100 5

1/16W

CHIP

5%

R7242

10k

JL7 216 J L7218

100R7230

SCL_EMMA

0uH

FB7202

68R7228

XX

R7222

JL7 210

0 .1

C7226

GND_1

100 p

C7214

SDA_EMMA

FE_+2V5_DDR

C7218

0 .1

100

R7219

9

27p

C7228

0. 00 1

C7205

68

R7217

JL7 219

68

RB7213

1

2

345

6

7

8

JL7 208

GND_1

TP7224

0 .1

C7227

JL7 204

TP7222

FE_PWMOUT

TP7225

100

RB7209

1

2

345

6

7

8

GND_1

XX

C7207

JL7 211

8 7 6 5

4321

IC7 202

X1

NC

VIN

GND CLK

VDD

PD

X2

0. 1

C7221

JL7 206

XX

R7220

R7234

220

48

9

5356

1

495051

2

55 5 4 52

3 4 5 6 7 8

471046 4 5 44

43 4 2

11 1 2 13 14 15

41 4 0 39 38 37 36 3 5

16 1 7 18 19 20 21 2 2

34

33

23

24 3225 3 1302926 2 7 28

5758

5960616263646566

IC7 201

VDD

DQ0

VDDQ

DQ1

DQ2

VSSQ

DQ3

DQ4

VDDQ

DQ5

DQ6

VSSQ

DQ7

NC

VDDQ

LDQS

NC

VDD

NC

LDM

WE

CAS

RAS

CS

NC

BS0

BS1

A10

A0

A1

A2

A3

DQ15

VSS

A4A5A6A7A8

A9

A11

A12

NC

CKE

CLK

CLK

UDM

VSS

VREF

NC

UDQS

VSSQ

NC

DQ8

VDDQ

DQ9

DQ10

VSSQ

DQ11

DQ12

VDDQ

DQ13

DQ14

VSSQ

VSS

VDD

GND_1

TP7223 TP7226

SDA

RT1P431M-TP-1

Q7204

100

R7218

47

R7233

JL7 221

10k

R7223

68p

C7229

C7223

0 .1

0 .1

C7204

XX

C7206

GND_1

1k

R7227

100

C7225

220

R7246

0. 1

C7234

0. 22F

C7236

SCL

47

C7235

1p

C7233

KEY

JL7 222

D7200

R7244

3. 3k

10 9 8 7 6

54321

IC7 203

32KOUT

SCL

SDA

INTRC

VSS

INTRA

INTRB

OSCOUT

OSCIN

VDD

SDA

1p

C7232

3.3V_STBY

2

3

4

1

X7201

4 .7

C7211

4 .7

C7224

4 .7

C7209

XX

R7236

100

R7237

100

R7238

100

R7241

R7239

XX

R7240

XX

XX

R7245

S

2SK20 36(TE85L)

Q7202

XX

C7237

FE_DADD[7]

FE_DQ[2]

FE_DQ[15 ]

FE_DCLKB

FE_DQ[6]

FE_DADD[1]

FE_DQ[4]

GND_1

FE_DQ[3]

GND_1

FE_DQ[12 ]

FE_DADD[12]

FE_DCKE

FE_DWEB

FE_DADD[6]

FE_DADD[0]

FE_DADD[3]

FE_DQ[7]

FE_DVREF

FE_DBA0

GND_1

FE_DADD[10]

FE_DCLK

FE_DVREF

FE_DQ[10 ]

FE_DQS1

FE_DQ[11 ]

FE_DCSB

FE_DQ[1]

FE_DQM0

FE_DADD[2]

FE_DADD[9]

FE_DADD[5]

FE_DADD[8]

FE_DBA1

FE_DCASB

FE_DQ[13 ]

3.3V_MAIN

FE_DRASB

GND_1

FE_DQM1

FE_DQ[8]

FE_DADD[11]

FE_DADD[0-12 ]

FE_DQ[0]

FE_DQ[5]

FE_DQ[9]

FE_DQS0

FE_DQ[14 ]

FE_DADD[4]

O

RS - MOUNT ON

0

FTV_CONFIG2

DDR SDRAM

LAYOUT NOTE:-

REMOVE GND PLANE AROUND AND UNDERNEATH IC7202

AND X7200 INCLUDING TRACKS FROM XTAL TO IC.

0.5%

FTV_CONFIG0

0 0

OPTION #2

FTV_CONFIG1

O

RS - MOUNT ON

DE-B

VIDEO AMPS/BUFFERS

PLACE T HESE CLOSE T O PIN 49 OF IC

27MHZ CLOCK

0.5%

0

OPTION #3OPTION #1

000

PLACE THESE CAPACITORS CLOSE TO IC PINS.

0

S/W OPTION SELECT RESISTORS

0

B1

2B /13

- 27 -

O

P

10

A B C D E F G H JI K L M N

1

2

3

4

5

6

7

8

9

11

12

Q

3.3V_MAIN

R7304

10k

R7302

10k

XX

R7307

FE_IOWRB

C7303

100 0p

14 1 3 12 11 10 9 8

71 2 3 4 5 6

IC7 303

1A1Y2A2Y3A3YGND 4Y

4A

5Y

5A

6Y

6A

VCC

C7306

0 .1

R7308

100

R7313 47

C7304

0 .1

FE_CI1_INPACKB

C7312

XX

20 1 9 18 17 16 15 1 4 13

12 1 1

1 2 3 4 5 6 7 8

9 10

IC7 305

OE1

A0

A1

A2

A3

A4

A5

A6

A7

GND Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

OE2

VCC

FE_CI1_CE1B

20 1 9 18 17 16 15 1 4 13

1 2 3 4 5 6 7 8

IC7 306

OE1

A0

A1

A2

A3

A4

A5

A6 Y5

Y4

Y3

Y2

Y1

Y0

OE2

VCC

R7312

47

C7307

0 .1

3.3V_MAIN

FE_CI1_WAITB

FE_FWEB

FE_RADD[0-11]

FB7301

0uH

R7303

10k

C7305

100 0p

FE_IOWRB_FWEB

FE_CI1_IREQB

FB7303

0uH

C7302

0 .1

R7315 47

C7308

0 .1

FB7304

0uH

GND_1

FE_CI1_RSTB

FB7305

0uH

FE_NCI_EN

R7306

220

FE_FOEB

FE_M_CKOUT,FE_M_SYNC,FE_M_VAL

R7305

100

FE_BUF_DIR

FE_IORDB

R7309

10k

3.3V_MAIN

R7316 47

20 1 9 18 17 16 15 1 4 13

12 1 1

1 2 3 4 5 6 7 8

9 10

IC7 304

OE1

A0

A1

A2

A3

A4

A5

A6

A7

GND Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

OE2

VCC

FB7302

0uH

FE_REGB

R7314 47

FE_M_DATA[0-7]

3.3V_MAIN

5 4

321

IC7 302

A

B

GND Y

VCC

FE_CI _TSD[7]

FE_FOEB

FE_RADD[8]

FE_CAM_ADD[

FE_CAM_TSOD[5]

FE_D_IOWRB

FE_CI1_WAITB

FE_RADD[9]

FE_IORDB

FE_RADD[11]

FE_IORDB

FE_CAM_TSOD[7]

FE_CI1_RSTB

FE_CI _TSD[5]

FE_CI1_CE1B

FE_CAM_TSOD[3]

FE_CAM_ADD[

FE_CAM_AD

D

FE_CAM_TSID[2]

FE_FWEB

FE_CAM_TSOD[4]

FE_CAM_TSID[3]

FE_CI _TSD[4]

FE_CI1_IREQB

FE_FWEB

FE_CI1_RSTB

FE_CI1_CE1B

FE_D_IOWRB

FE_CI _TSD[6]

FE_CAM_AD

D

FE_CI _TSD[3]

FE_M_DATA[3]

FE_REGB

FE_M_DATA[2]

FE_CAM_TSID[1]

FE_CI1_INPACKB

FE_M_SYNC

FE_M_DATA[1]

FE_CAM1_IREQB

FE_M_DATA[0]

FE_RADD[10]

FE_CAM_TSID[0]

FE_FOEB

FE_CAM_TSOD[6]

EMMA2LR

EMMA2LR

EMMA2LR

EMMA2LR

TS to CAM

TS from

POWER

B1. -SE2

B1

3A /13

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 3A/13 ~

- 28 -

~ B1 Board Schematic Diagram [ Main Microcontroller, HDMI/AV Side/PC Input, Audio Processor, Scarts ] Page 3B/13 ~

DDCCBBP

EE

FF

Z

1

2

3

4

5

6

7

8

9

10

11

12

Q R S T U V W X Y AA

R7322 10 0

R7321 10 0

FE_CI1_CD2B

A1

B1

A2

B2

A3

B3

A4

A5

A6

B4

B5

B6

A7

B7

A8

B8

A9

B9

A10

B10

A11

B11

A12

B12

A13

B13

A14

B14

A15

B15

A16

B16

A17

B17

A18

B18

A19

B19

A20

B20

A21

B21

179 37692 1

GND

D3

D4

D5

D6

D7

CE1#

A10

OE#

A11

A9

A8

A13

A14

WE#

IREQ#

VCC

VPP1

MIVAL

MCLKI

A12

GND

CD1#

MDO3

MDO4

MDO5

MDO6

MDO7

CE2#

VS1#

IORD#

IOWR#

MISTRT

MDI0

MDI1

MDI2

MDI3

VCC

VPP2

MDI4

MDI5

MDI6

FE_CI1_VS1B

R7323

10k

R7313 47

C7312

XX

R7312

47

R7320 10 0

R7328

10k

3.3V_MAIN

R7325

10k

R7324

10k

R7332 1 k

03

R7315 47

04

FE_CI1_CD1B

05

R7316 47

R7314 47

FE_CI _TSD[7]

FE_CAM_TSIVAL

FE_CAM_TSOD[3]

FE_CAM_ADD[10]

FE_CAM_DAT[4]

FE_CAM_OEB

FE_CAM_OEB

FE_CAM_ADD[8]

FE_CAM1_CE1B

FE_CAM_TSID[3]

FE_CAM_ADD[10]

FE_CAM1_RSTB

FE_CAM_TSID[0]

FE_CAM_IORDB

FE_CAM_DAT[7]

FE_CAM_TSID[6]

FE_CI _TSD[5]

FE_CAM1_IREQB

FE_CAM_WEB

FE_CAM_ADD[9]

FE_CAM_TSID[5]

FE_CAM_TSOD[4]

FE_CAM_ADD[11]

FE_CAM_ADD[8]

FE_CAM_TSID[1]

FE_CAM_TSID[2]

FE_CAM_TSID[3]

FE_CI _TSD[4]

FE_CAM_TSOD[5]

FE_CAM_DAT[5]

FE_CAM_DAT[3]

FE_CI _TSD[6]

FE_CAM_TSID[2]

FE_CAM_TSISYNC

FE_CAM_TSID[4]

FE_CAM_DAT[6]

FE_CAM_TSICLK

FE_CAM_ADD[9]

FE_CAM_IOWRB

FE_CI _TSD[3]

FE_CAM_ADD[11]

FE_CAM_IOWRB

FE_CAM_TSID[1]

FE_CAM_TSOD[7]

FE_CAM_TSOD[6]

FE_CAM_TSID[0]

FE_CAM1_CE1B

FE_CAM_WEB

FE_CI1_IREQB

FE_CAM_IORDB

TS to CAM

TS from CAM

PCMCIA DVB-CI CONNECTOR

EMMA2LR

B1

3B /13

- 29 -

11

22

Q

O

P

A B C D E F G H JI K L M N

12

13

14

15

16

17

18

19

20

21

FE_CI_TSCLK,FE_CI_TSSYNC,FE_CI_TSVAL

FE_IOWRB_FWEB

GND_1

C7309

0 .1

FE_CI1_CE1B

FE_BUF_DIR

C7311

0 .1

FB7300

0uH

FB7308

0uH

20 1 9 18 17 16 15 1 4 13

12 1 1

1 2 3 4 5 6 7 8

9 10

IC7 307

OE1

A0

A1

A2

A3

A4

A5

A6

A7

GND Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

OE2

VCC

FB7306

0uH

R7319

47

20 1 9 18 17 16 15 1 4 13

12 1 1

1 2 3 4 5 6 7 8

9 10

IC7 308

OE1

A0

A1

A2

A3

A4

A5

A6

A7

GND Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

OE2

VCC

R7300

10k

20 1 9 18 17 16 15 1 4 13

12 1 1

1 2 3 4 5 6 7 8

9 10

IC7 306

OE1

A0

A1

A2

A3

A4

A5

A6

A7

GND Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

OE2

VCC

20 1 9 18 17 16 15 1 4 13

12 1 1

1 2 3 4 5 6 7 8

9 10

IC7 301

DIR

A0

A1

A2

A3

A4

A5

A6

A7

GND B7

B6

B5

B4

B3

B2

B1

B0

OE

VCC

C7310

0 .1

20 1 9 18 17 16 15 1 4 13

12 1 1

1 2 3 4 5 6 7 8

9 10

IC7 309

OE1

A0

A1

A2

A3

A4

A5

A6

A7

GND Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

OE2

VCC

FE_ CI_TS D[0-7 ]

C7300

0 .1

47

R7310

FB7307

0uH

3.3V_MAIN

FE_IOWRB

GND_1

C7308

0 .1

47

R7311

FB7305

0uH

R7301

XX

FE_RDATA[0-7]

R7317

47

R7318

47

R7316 47

5 4

321

IC7 300

A

B

GND Y

VCC

FE_FWEB

C7301

0 .1

FE_CAM_A

D

FE_CAM_TSISYNC

FE_CI _TSD[1]

FE_CAM_A

D

FE_RADD[1]

FE_CAM1_INPACKB

FE_CAM_TSIVAL

FE_CAM_DAT[0]

FE_RDATA[1] FE_CAM_DAT[2]

FE_CI_TSSYNC

FE_RDATA[6]

FE_REGB

FE_CAM_A

D

FE_CI _TSD[2]

FE_RADD[4]

FE_CAM_TSID[5]

FE_CI _TSD[0]

FE_CAM_TSOSYNC

FE_CAM_TSID[6]

FE_CAM_TSID[2]

FE_FWEB

FE_RDATA[4]

FE_CAM_TSID[3]

FE_RDATA[5]

FE_CAM_TSOD[0]

FE_CAM_TSOVAL

FE_M_DATA[6]

FE_M_VAL

FE_CAM1_WAITB

FE_CI_TSCLK

FE_CAM_TSOCLK

FE_RADD[0]

FE_M_DATA[5]

FE_CAM_A

D

FE_RADD[2]

FE_CAM_A

D

FE_CAM_A

D

FE_RADD[7]

FE_M_DATA[4]

FE_RADD[5]

FE_CAM_TSID[4]

FE_CAM_TSOD[2]

FE_RDATA[3]

FE_CAM_A

D

FE_RADD[3]

FE_CAM_TSID[7]

FE_M_DATA[3]

FE_CAM_TSOD[1]

FE_M_DATA[2]

FE_CAM_DAT[1]

FE_CAM_A

D

FE_CAM_TSID[1]

FE_M_SYNC

FE_M_DATA[1]

FE_CAM1_IREQB

FE_CAM_DAT[3]

FE_M_DATA[0]

FE_CAM_DAT[4]

FE_CAM_TSICLK

FE_RDATA[0]

FE_CAM_DAT[7]

FE_CAM_DAT[5]

FE_M_DATA[7]

FE_CAM_DAT[6]

FE_CAM_TSID[0]

FE_RADD[6]

FE_RDATA[2]

FE_RDATA[7]

FE_CI_TSVAL

FE_M_CKOUT

DATA to/from CAM

EMMA2LR

TS to EMMA

EMMA2LR

EMMA2LR

B1

3C /13