Sony ILX554A Datasheet

ILX554A

2048-pixel CCD Linear Sensor (B/W) for Single 5V Power Supply Bar-code Reader

Description

The ILX554A is a rectangular reduction type CCD

linear image sensor designed for bar code POS

hand scanner and optical measuring equipment use.

A built-in timing generator and clock-drivers ensure

single 5V power supply for easy use.

Features

• Number of effective pixels: 2048 pixels

• Pixel size: 14µm × 56µm

(14µm pitch)

• Single 5V power supply

• Ultra-high sensitivity

• Built-in timing generator and clock-drivers

• Built-in sample-and-hold circuit

• Maximum clock frequency: 2MHz

Block Diagram

22 pin DIP (Cer-DIP)

D40

D39

Readout gate

pulse generator

φROGφCLK

Absolute Maximum Ratings

• Supply voltage VDD 6V

• Operating temperature –10 to +60 °C

• Storage temperature –30 to +80 °C

Pin Configuration (Top Vie w)

V

OUT

NC

NC

SHSW

φCLK

NC

NC

NC

NC

NC

φROG

10

11

1

2

3

4

5

6

7

8

9

1

2048

22

21

20

19

18

17

16

15

14

13

12

NC

NC

V

DD

GND

NC

NC

NC

NC

NC

NC

NC

D33

S2048

S2047

S2046

Readout gate

S3

S2

S1

D32

D2

D1

• Output amplifier

1

OUT

V

CCD analog shift register

• S/H circuit

Clock-drivers

Mode selector

Clock pulse generator/

Sample-and-hold pulse generator

5

19 20 114

SHSW

DD

V

GND

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E00818-PS

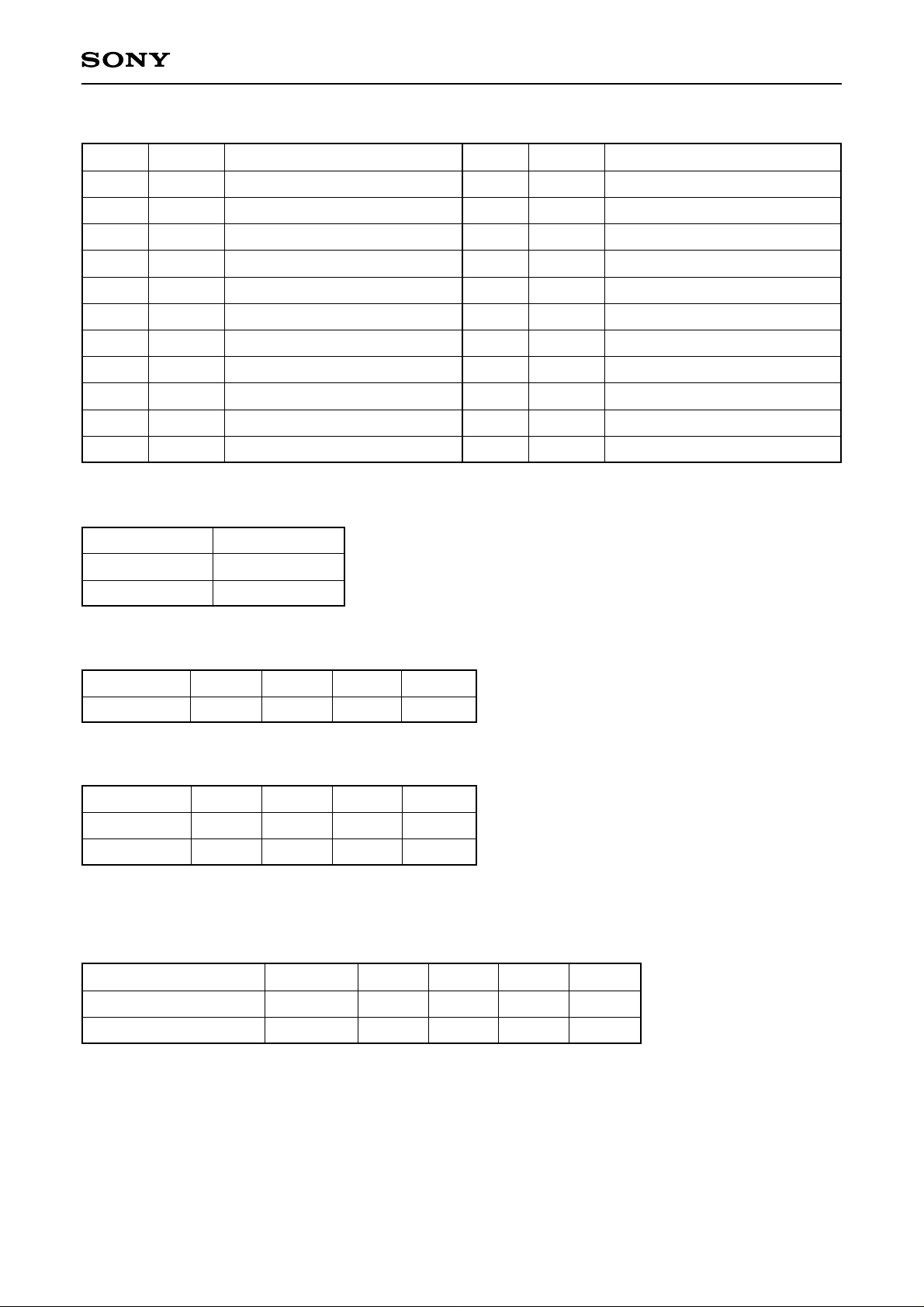

Pin Description

ILX554A

Pin No. Symbol

1

V

OUT

2

NC

3

NC

4

SHSW

5

φCLK

6

NC

7

NC

8

NC

9

NC

10

11

NC

φROG

Mode Description

Mode in use

With S/H

Without S/H

Description

Signal output

NC

NC

Switch (with S/H or without S/H)

Clock pulse input

NC

NC

NC

NC

NC

Readout gate pulse input

Pin 4 (SHSW)

GND

VDD

Pin No.

12

13

14

15

16

17

18

19

20

21

22

Symbol Description

NC

NC

NC

NC

NC

NC

NC

GND

VDD

NC

NC

NC

NC

NC

NC

NC

NC

NC

GND

5V power supply

NC

NC

Recommended Supply voltage

Item Min.

VDD 4.5

Input Clock voltage Condition

Item Min.

VIH

VIL

∗1

This is applied to the all pulses applied externally. (φCLK, φROG)

4.5

0

Typ.

5.0

Typ.

5.0

—

∗∗

∗1

∗∗

Max.

5.5

Max.

VDD

0.5

Unit

V

Unit

V

V

Clock Characteristics

Item Min.

Input capacity of φCLK

Input capacity of φROG

Symbol

CφCLK

CφROG

—

—

Typ.

10

10

Max.

—

—

Unit

pF

pF

– 2 –

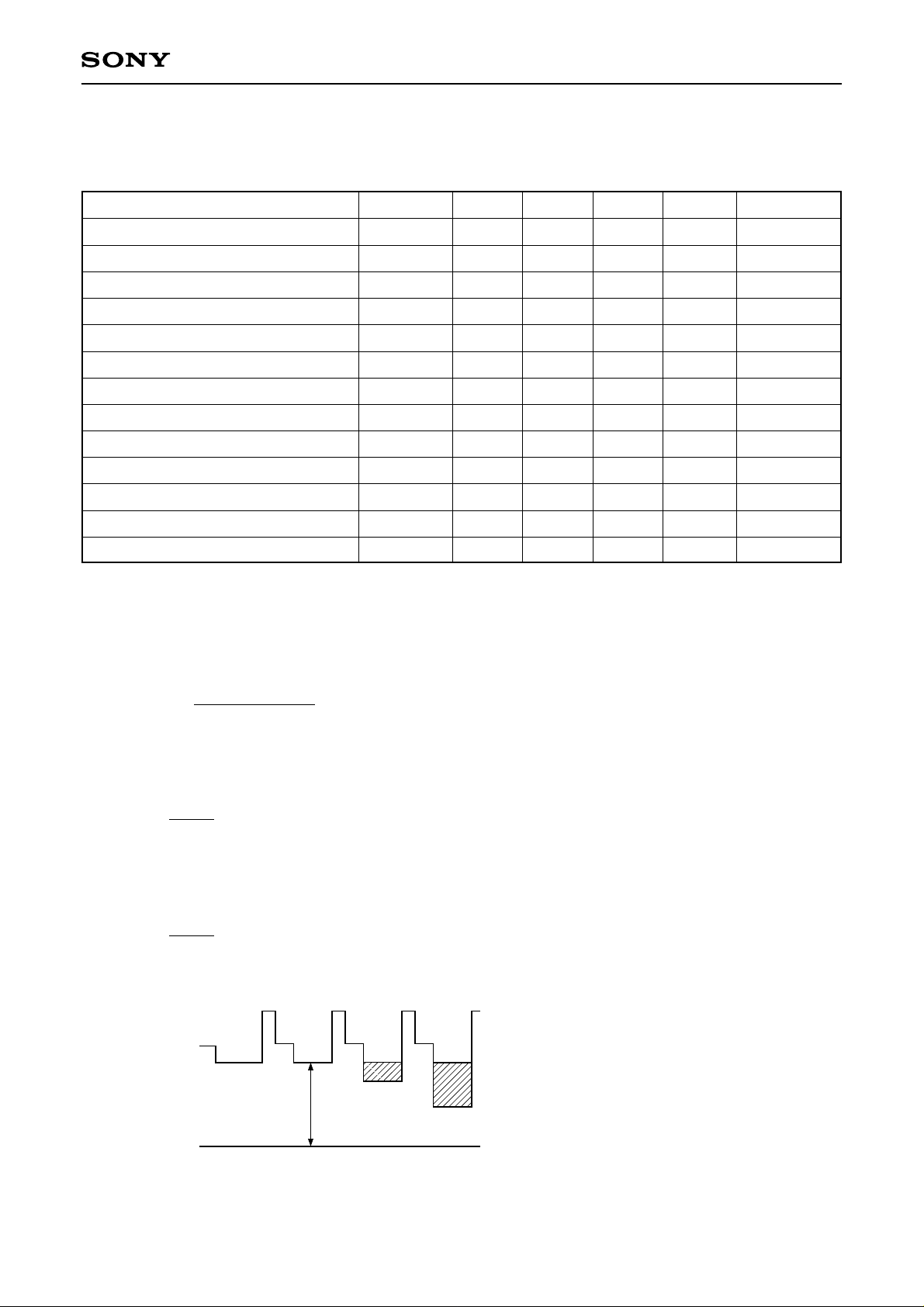

Electro-optical Characteristics

(Ta = 25°C, VDD = 5V, Clock frequency: 1MHz, Light source = 3200K,

IR cut filter: CM-500S (t = 1.0mm), Without S/H mode)

ILX554A

Item Min.

Sensitivity 1

Sensitivity 2

Sensitivity nonuniformity

Saturation output voltage

Dark voltage average

Dark signal nonuniformity

Image lag

Dynamic range

Saturation exposure

5V current consumption

Total transfer efficiency

Output impedance

Offset level

Symbol

R1

R2

PRNU

VSAT

VDRK

DSNU

IL

DR

SE

IVDD

TTE

ZO

VOS

180

—

—

0.8

—

—

—

—

—

—

92

—

—

Typ.

240

3500

5.0

1.0

3.0

6.0

1

333

0.004

5.0

98.0

250

2.85

Max.

300

—

10.0

—

6.0

12.0

—

—

—

10

—

—

—

Unit

V/(lx · s)

V/(lx · s)

%

V

mV

mV

%

—

lx · s

mA

%

Ω

V

Note)

1. For the sensitivity test light is applied with a uniform intensity of illumination.

2. Light sourse: LED λ = 660nm

3. PRNU is defined as indicated below. Ray incidence conditions are the same as for Note 1.

Remarks

Note 1

Note 2

Note 3

—

Note 4

Note 4

Note 5

Note 6

Note 7

—

—

—

Note 8

PRNU = × 100 [%]

(VMAX – VMIN)/2

VAVE

The maximum output of all the valid pixels is set to VMAX,

the minimum output to VMIN and the average output to VAVE.

4. Integration time is 10ms.

5. Typical value is used for clock pulse and readout pulse. VOUT = 500mV.

6. DR =

VSAT

VDRK

When optical integration time is shorter, the dynamic range sets wider because dark voltage is in

proportion to optical integration time.

7. SE =

VSAT

R1

8. VOS is defined as indicated below.

Vout

DD D SI

V

OS

GND

– 3 –

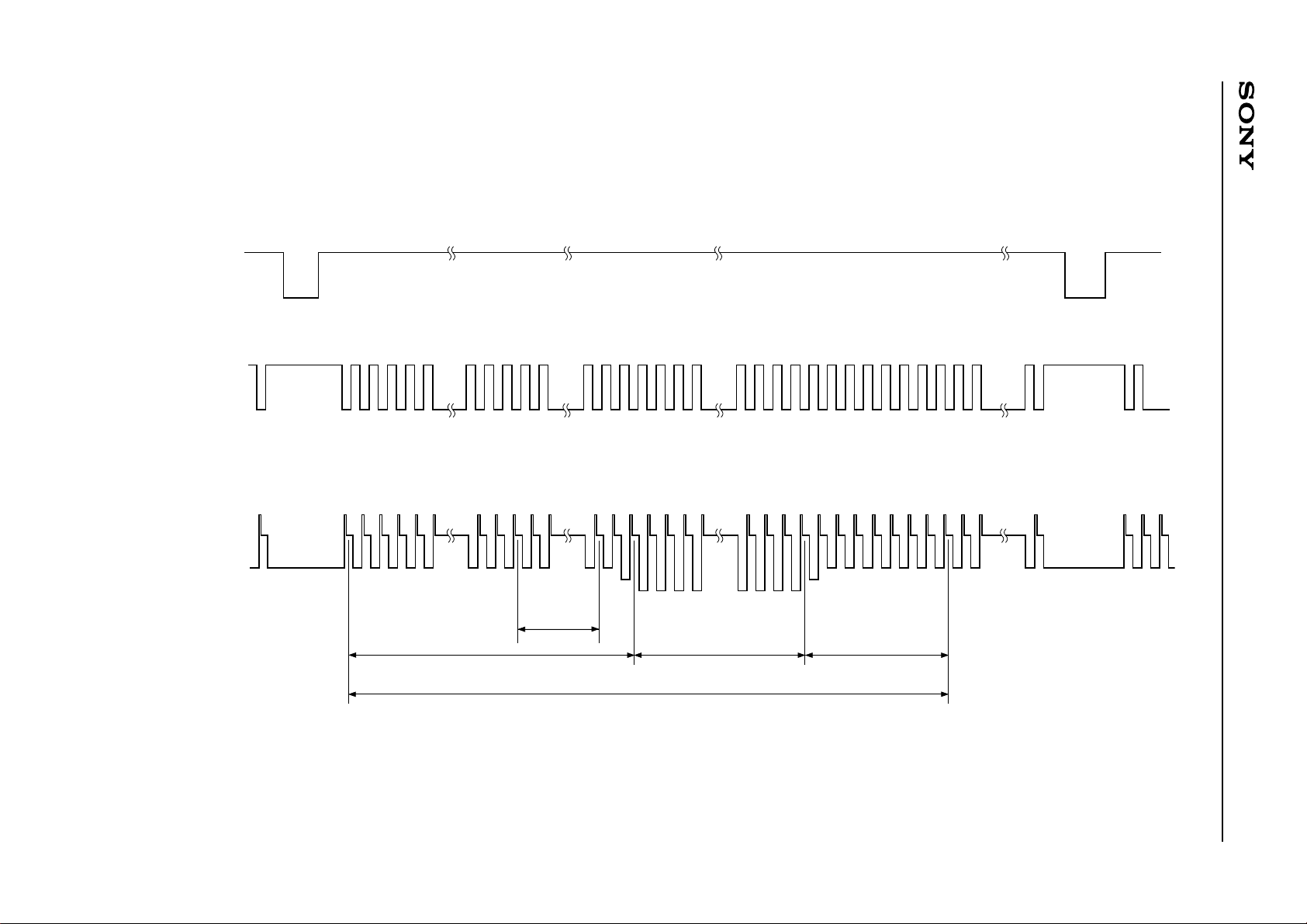

Clock Timing Diagram (without S/H mode)

5

φROG

0

1

φCLK

5

0

0

123

2088

– 4 –

D1D2D3D4D5

∗

V

OUT

∗

Without S/H mode (4 pin → V

D10

D11

D12

D13

D14

D30

D31

D32S1S2S3S4

Optical black

(18 pixels)

1-line output period (2088 pixels)

DD)

Effective picture elements signal

(2048 pixels)

S2045

S2046

S2047

S2048

D33

D34

D35

Dummy signal

(8 pixels)Dummy signal (32 pixels)

D36

D37

D38

D39

D40

Note) 2090 or more clock pulse are required.

ILX554A

Loading...

Loading...