Page 1

S®

Digital Video

Player

Training Manual

Circuit Description and Troubleshooting

Course: D VD-02

Page 2

Course Description

and Troubleshooting:

Model: DVP-S530D

Prepared by: National Training Department

Sony Service Company

A Division of Sony Electronics Inc.

Course presented by______________________________________

Date___________________________________________________

Student Name ___________________________________________

Page 3

Sony Service Company

A Division of Sony Electronics Inc ©1999

All Rights Reserved

Printed in U.S.A.

“DTS” is a trademark of Digital Theater Systems, Inc.

“AC-3” is a trademark of Dolby Laboratories Licensing Corporation.

“Dolby” and “Dolby Surround” are trademarks of Dolby Laboratories

Licensing Corporation.

“Sony” and “Digital Cinema Sound” are trademarks of Sony .

“THX” is a trademark of Lucasfilm, Ltd.

Page 4

Table of Contents

Introduction to the DTS Audio Format 1

What is DTS? 2

What do I need to play the DTS surround format? 2

What do I need to play both the AC-3 and

DTS surround formats? 2

Will a 5.1 channel DTS CD play in my CD player? 2

Why won’t my older DVD player play DTS DVDs? 3

Can DVD movies contain both DTS and AC-3

audio tracks? 3

How does DTS work? 3

Board Layout 5

DVD Features 6

Block Diagram 7

Power Supply 7

Communications 7

Servo Control 7

Video and Audio Processing 9

Power Supply Block 11

Standby Power Supply 11

Main Power Supply 11

Power Consumption 11

Oscillator Frequencies 11

Standby Oscillator 13

Start 13

Run 13

Regulation Concept 13

Regulation Circuitry 13

Main Oscillator 15

Enable 15

Start 15

Run 15

Regulation 15

Power Control 17

Plug In 17

Communications Block 21

Serial Data 21

Parallel Data 21

Serial Data Communications 23

Serial Bus 0 23

Serial Bus 1 25

Parallel Data Communications 27

Communications from IC202 to Other ICs 29

Communications from a Destination IC to IC202 29

Mechanism 31

Disc Tray and Laser Platform Position 31

Tilt Motor 32

Power ON Mechanical Sequence - No Disc 34

Power ON Mechanical Sequence - DVD Disc 35

Tray Motor Drive 37

Page 5

Initial Sled Motor Drive 41

Manually Driving the Tilt Motor 71

Initial Sled Movement 41

Home Position Detection 45

Laser Servo 47

KHM-220A DVD Optical Block 49

DVD Focus 49

CD Focus 49

Three Laser Beams from One Laser 50

Photo Detectors 51

Disc Identification 53

Operation 5 3

SACD Disc Type 53

Focus 55

Search 55

Servo 55

Focus Drive 57

Focus Search Communications 57

A/V Processing Block 73

A/V Processing 75

Test Mode 81

Test Mode Access 81

Tests 81

Additional Test Mode 83

Self-Diagnostic Function (Customer Error Codes) 83

Troubleshooting 85

General Problems and Troubleshooting Guide 85

Spindle Motor 61

Kick Mode 61

CLV PB Mode 63

Tracking Servo 65

Tracking Counting in Pause or Picture Jump 65

Sled Motor Drive - PB 67

Following the Track 59

Tilt Servo 69

Operation 6 9

Page 6

1

Introduction to the DTS Audio Format

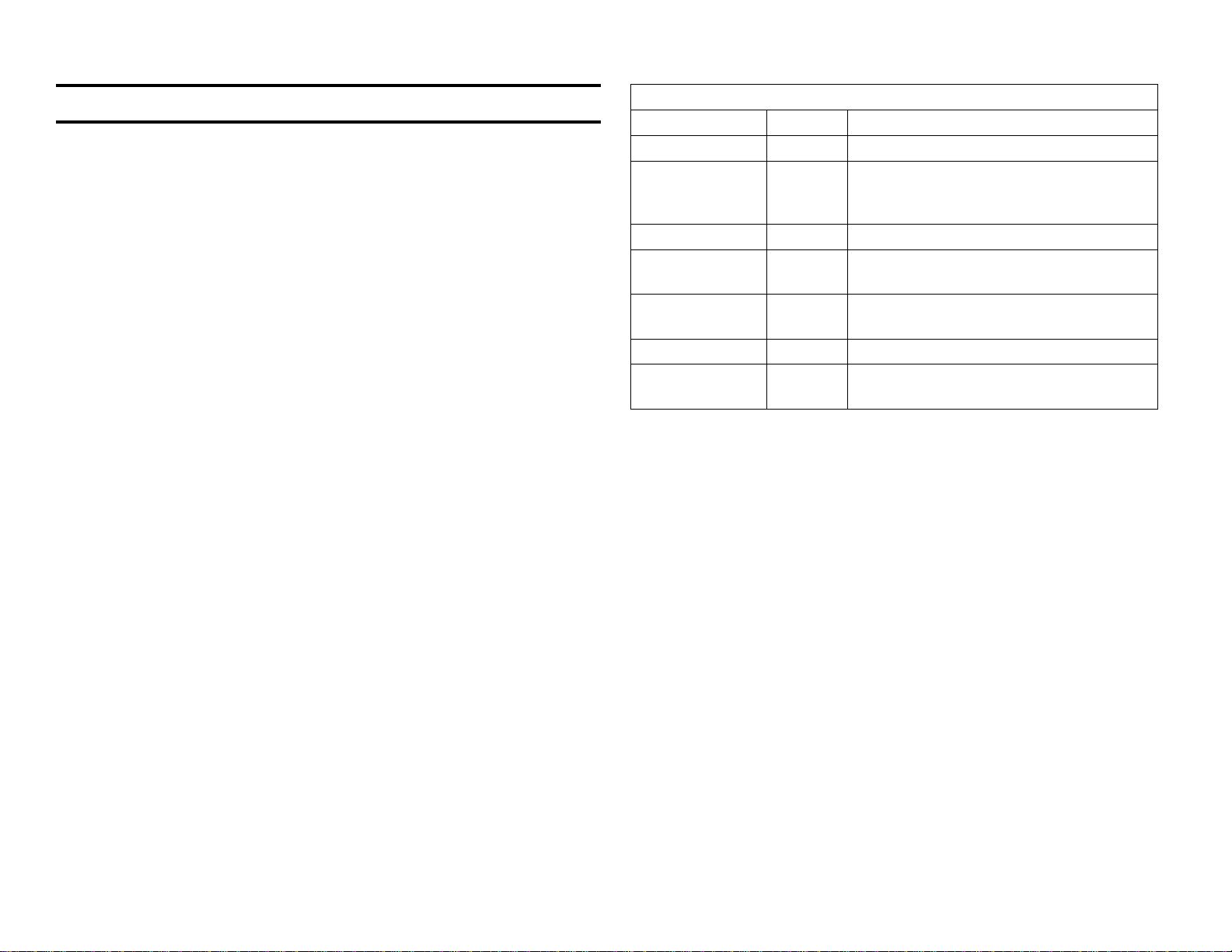

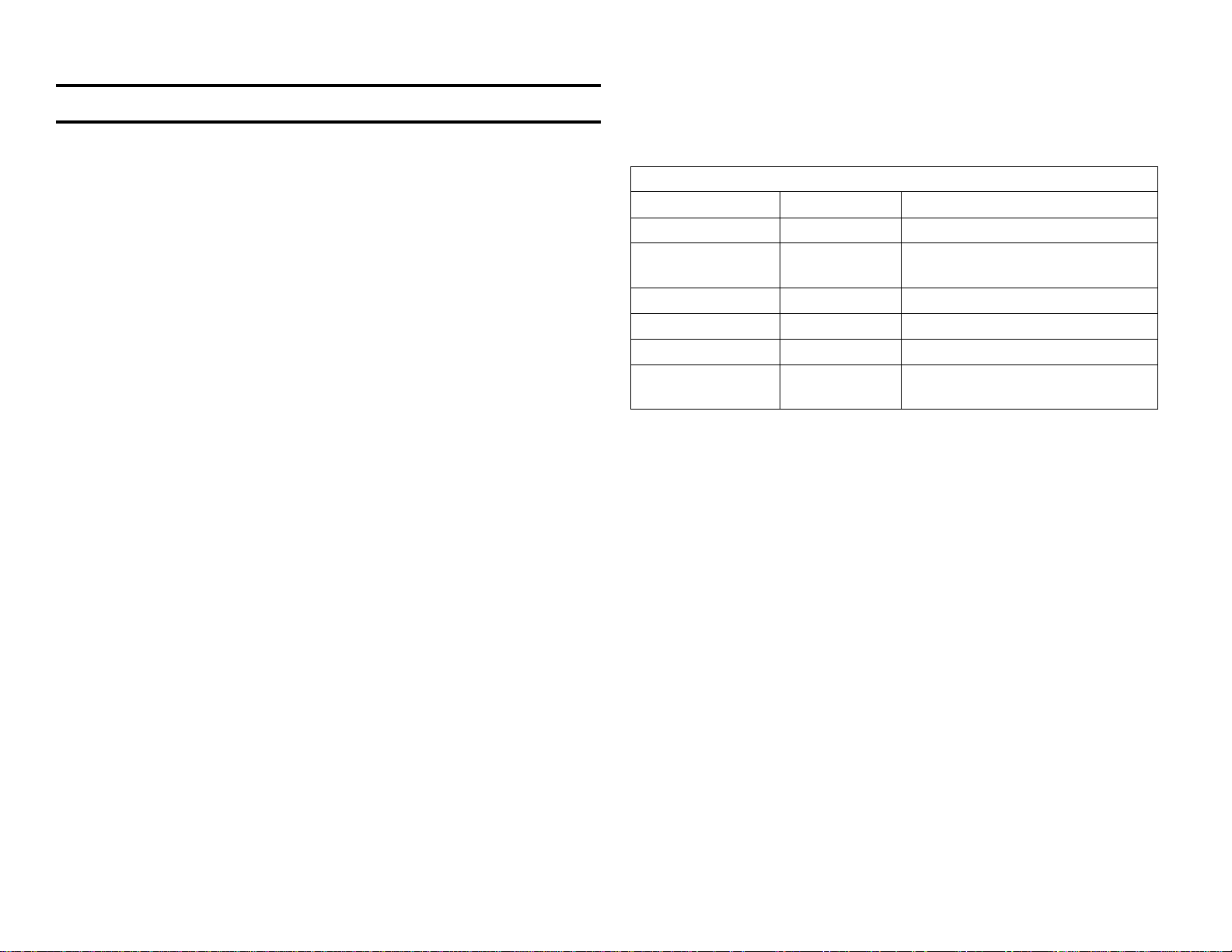

Several major consumer audio formats that exist today are listed in this table:

Audio Formats

Format (note 1)

1. Stereo 1933 2 Analog linear FM, VHS, CD, LD, etc.

2. PCM (digital

version of stereo)

3. Dolby Surround

4. Dolby Prologic

5. Dolby Digital

6. DTS

7. THX

Year

Used

1982 3 Analog None VHS

1987 4 Analog None

1991 6 Digital 20 bits /

1993 6 Digital

1982 2-6 Either Theaters, DVD, LD, VHS

Chan

-nels

2 Digital 16 bits /

Class

Typical

sample

sample.

sample

20 bits /

sample

Typical Data Rate

(note 2)

705kbit/sec

(44.1kHz sample)

384 Kbytes/sec

(44.1kHz sample)

1,411kbits/sec

(44.1kHz sample)

Compression

(Approx.)

None DVD, LD

90%

75%

Test Disc Signal Source (note 3)

Prologic test CD

Dolby DVD-TEST1

Dolby DVD-TEST1

DTS Test CD

DTS Test DVD

VHS, theaters

DVD, LD, DTV

DVD, LD, CD

Note 1 - All formats require decoders, except Stereo and THX. THX is not a processing system but an audio/video quality control approval system.

Its certification stamp means that the video and audio quality at theaters and CD/DVD discs meet uniform standards. This means the same

movie viewed at one theater will not be different when viewing it at another theater.

Note 2 - Data rate = bits sampled X sample rate. A CD player (44.1kHz) rate was chosen for comparison. The DVD sample rate of 48kHz would

make its data rate higher than shown.

Note 3 - LD = Laser Discs; DVD = Digital videodiscs; DTV = Digital TV; theaters = Movie theaters; VHS = Videotape format.

Test discs can be purchased from different distributors:

Prologic test CD #SSTCD

· Sony parts distributors. Call 1-800-222-Sony for a distributor

Dolby DVD – TEST 1 # 22707 $45.

· USC Products Marketing Co.; 1 800 983 6529

DTS Test CD (digital output only)

· Digital Sound Systems Entertainment

DTS Test DVD #DTS-DVD 98061

5171 Clareton Drive, Agoura Hills, Calif. 91301

1-818-706-3525 part #DTS-CD 96091

· Sony parts distributors. Call 1-800-222-Sony for a distributor

CD part # J2501-154-A $7.76 list price

· Digital Sound Systems Entertainment

Agoura Hills, Calif. 91301

1-818-706-3525 part #DTS- DVD 98061

Page 7

What is DTS?

Digital Theater Systems has developed a digital audio compression method

similar to Dolby Digital AC-3. DTS processed audio is not as compressed

as Dolby AC-3. Therefore it is said to have more surround detail (separation), envelopment and better bass because of less compression (losses).

What do I need to play the DTS surround format?

The DTS source can be a DVD movie or CD. The DTS decoder is commonly found in the receiver.

5 Speakers

CD/DVD Player 6 Channel Receiver

With DTS Decoder

Digital output preamp out to

Sub Woofer

AC-3 decoder in the Receiver:

5 Speakers

CD/DVD Player 6 Channel Receiver

With DTS Decoder

And AC-3 Decoder

Digital output preamp out to

Sub Woofer

Will a 5.1 channel DTS CD play in my CD player?

Only digital noise will appear from the L/R analog outputs if not automatically muted. There will be digital output from the coaxial and optical ports.

Either digital output can be fed to a DTS stand-alone decoder or a receiver with a DTS internal decoder. The DTS receiver will produce the six

channels (“5.1”) or be downmixed into two (front L/R) channels depending upon the user menu.

What do I need to play both the AC-3 and DTS surround formats?

The AC-3 source can be DVD or HDTV (future). The decoder can be

found in the player or receiver.

AC-3 decoder in the Player:

5 Speakers

CD/DVD Player 6 Channel Receiver

With AC-3 decoder With DTS Decoder

preamp out to

Digital Output Sub Woofer

A DTS CD compresses the six channels of audio into the space originally

occupied by the two-channel uncompressed CD audio. In order for six

compressed channels to fit on a CD, the data rate must be equal to or

less than the rate of a normal uncompressed CD.

Data rate of an uncompressed CD per channel =

16 bits/sample x 44, 100 samples/second = 706 Kbytes/sec.

There are two channels so the rate is doubled. Therefore the data rate of

a normal stereo CD = 1,412kbit/sec.

This is just about the same data rate as a DTS compressed CD. The DTS

data rate is 1,411kbits, so no analog sound will be output from a DTS CD.

For comparison, CD, DTS, and AC-3 data rates are shown:

Data Rate Comparison (44.1 kHz sample rate)

Format Output Data Rate

CD Not compressed 1,412 Kbytes/sec.

DTS Compressed 1,411 Kbytes/sec.

Dolby Digital AC-3 Compressed 384 Kbytes/sec.

2

Page 8

3

Why won’t my older DVD player play DTS DVDs?

The DVD DTS flag was not established until Nov 1998. This flag must be

inserted into the DVD’s digital coax or optical output for the receiver to

recognize and decode DTS. Therefore DVD units that are not marked

“DTS ready” will not play DTS even though they have digital outputs.

Can DVD movies contain both DTS and AC-3 audio tracks?

Yes they can. Currently the DVD audio choices are:

· PCM – Producing the conventional analog L/R sound

· Dolby Digital or AC-3 – Compressed 5.1 channel surround sound

· DTS – Compressed 5.1 channel surround sound

How does DTS work?

The DTS and AC-3 encoding formats are generally similar. DTS and AC3 can accept digital (PCM) audio with word lengths from 16 to 24 bits.

Both encoders can accept the common 32, 44.1 and 48kHz PCM sampling frequencies, but DTS has 12 more optional frequencies.

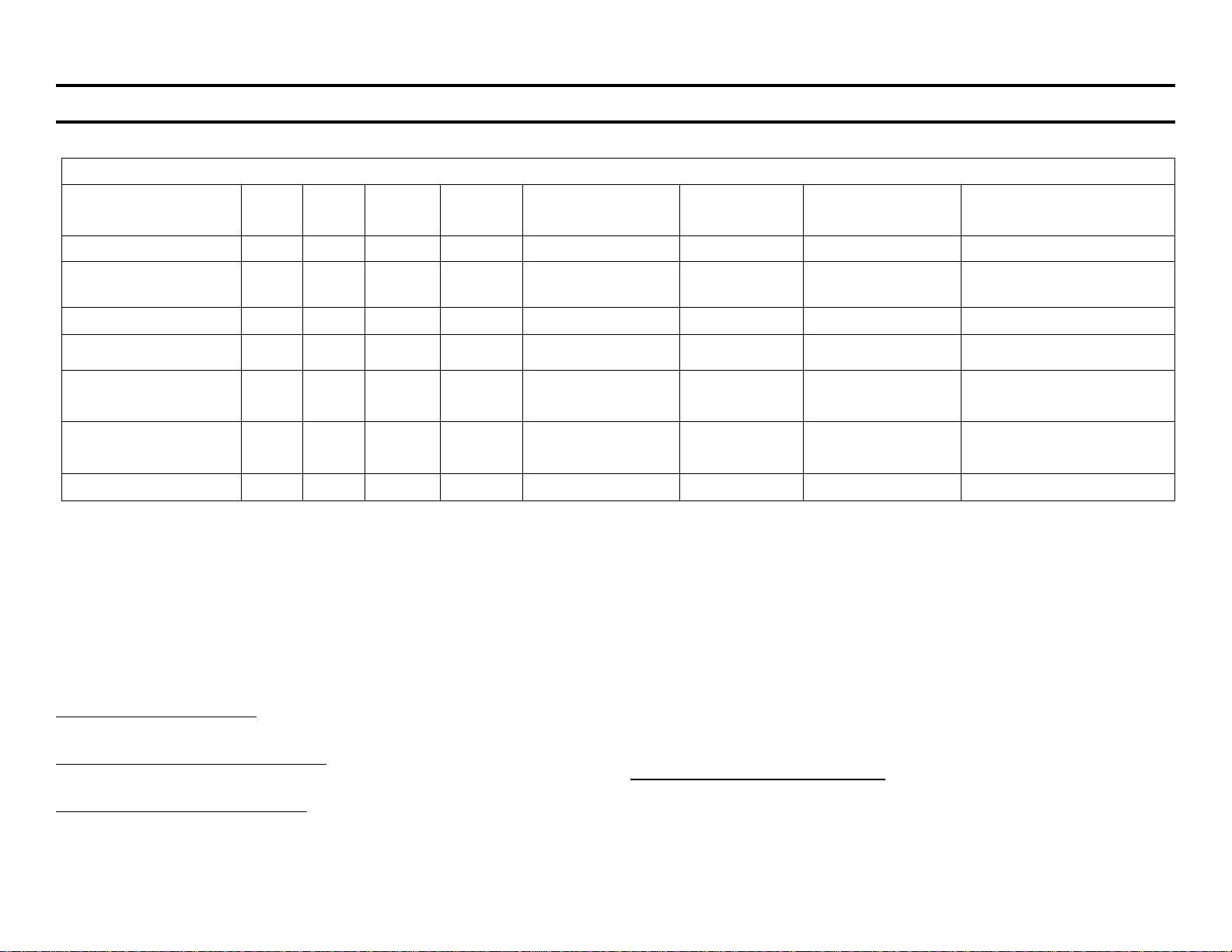

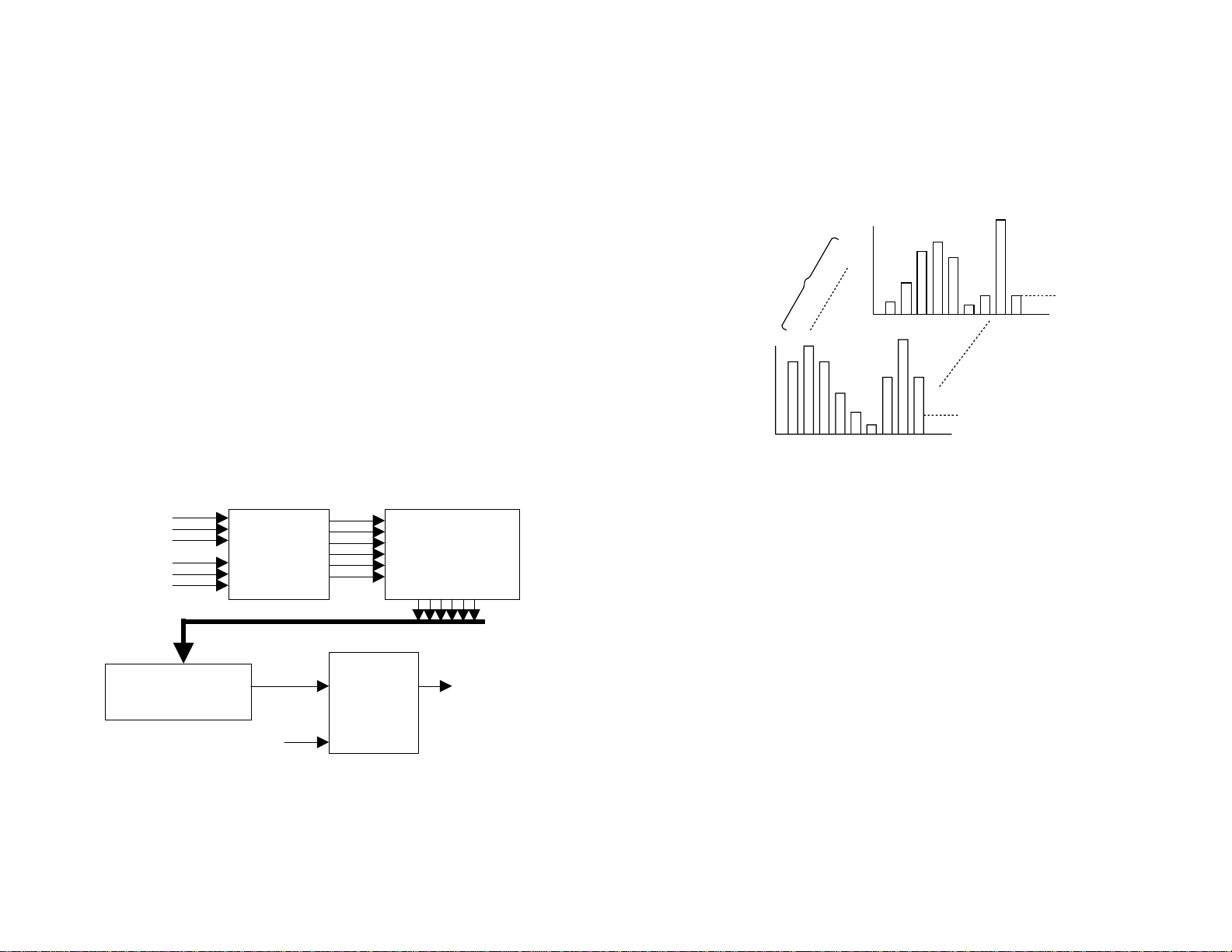

The general encoding of the DTS compression system will be explained.

DTS has four blocks used to compress the PCM input audio into a single

bit stream:

PCM audio Time to

6 Channels Frequency Compression

Conversion

6 lines

DTS

Multiplexer Packer Compressed

Bit Stream

Sync

MDCT Time to Frequency Conversion

Each single channel PCM source signal is grouped and allocated to one

of 32 frequency bands for analysis. The process is commonly known as

Modified Discrete Cosine Transformation (MDTC). This frequency band

allocation allows for identification and removal of redundancy among the

channels in the next compression stage.

Coefficients

6

CHANNELS

Frequency

Coefficients

Frequency

Compression

Adaptive Predictive Coding (ADPCM)

ADPCM involves smaller support stages to:

· Combine the same sounds found in other channels,

· Remove undetectable audio levels (below human hearing thresholds),

· Remove short interval noises that are swamped by louder sounds

(psycho acoustic masking); and

· Remove transient noises that do not repeat on the same or other

channels.

The support stages include transient, vector and prediction analysis stages

to determine if the sound is short term, increasing or decreasing, and if

the sound will repeat. Removal or the combination of sounds (compression) is determined by the analysis.

Page 9

From

time to

freq

Converter

Compression Block:

ADPCM:

• Transient analysis

• Vector analysis

• Prediction analysis

Global Bit Management

Variable Length Coding

Multiplexer

Multiplexer

The six compressed channels are combined into a single line for ease of

delivery. To do this each channel is stored into a register made up of flipflops. A high speed Multiplexer removes the information at six times the

storage (sample) speed. Multiplexer

Six Channels

N sample

frequency

F/F type

Registers

6 lines

Packer

Global Bit Management

Once compression has taken place, an examination of the six data streams

for density is made. Bit groups are tagged and moved from a high-density channel to a low-density channel equalizing the amount of data.

0011100011000011111001010101 channel 1

0000001011000000000000000000 channel 3

Variable Length Coding

Common fixed length codes and no data (00000000) codes are removed

and replaced with shorter codes using a look up table. These shorter

length code replacements are flagged for decoding.

0100011111 ROM Table 011 + flag

The packer organizes the information into blocks and adds:

· Error correction

· Synchronization information to each block and groups of blocks

4

Page 10

5

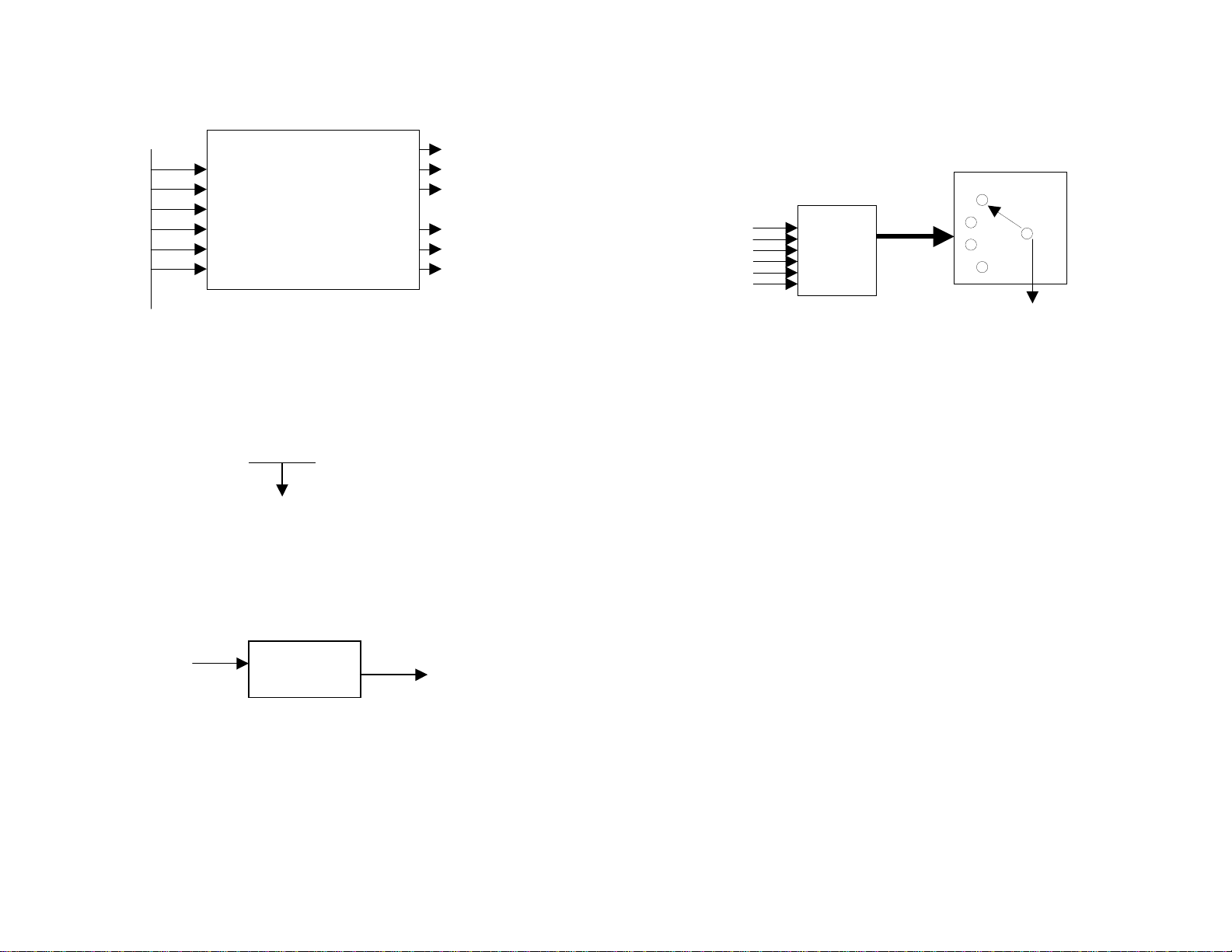

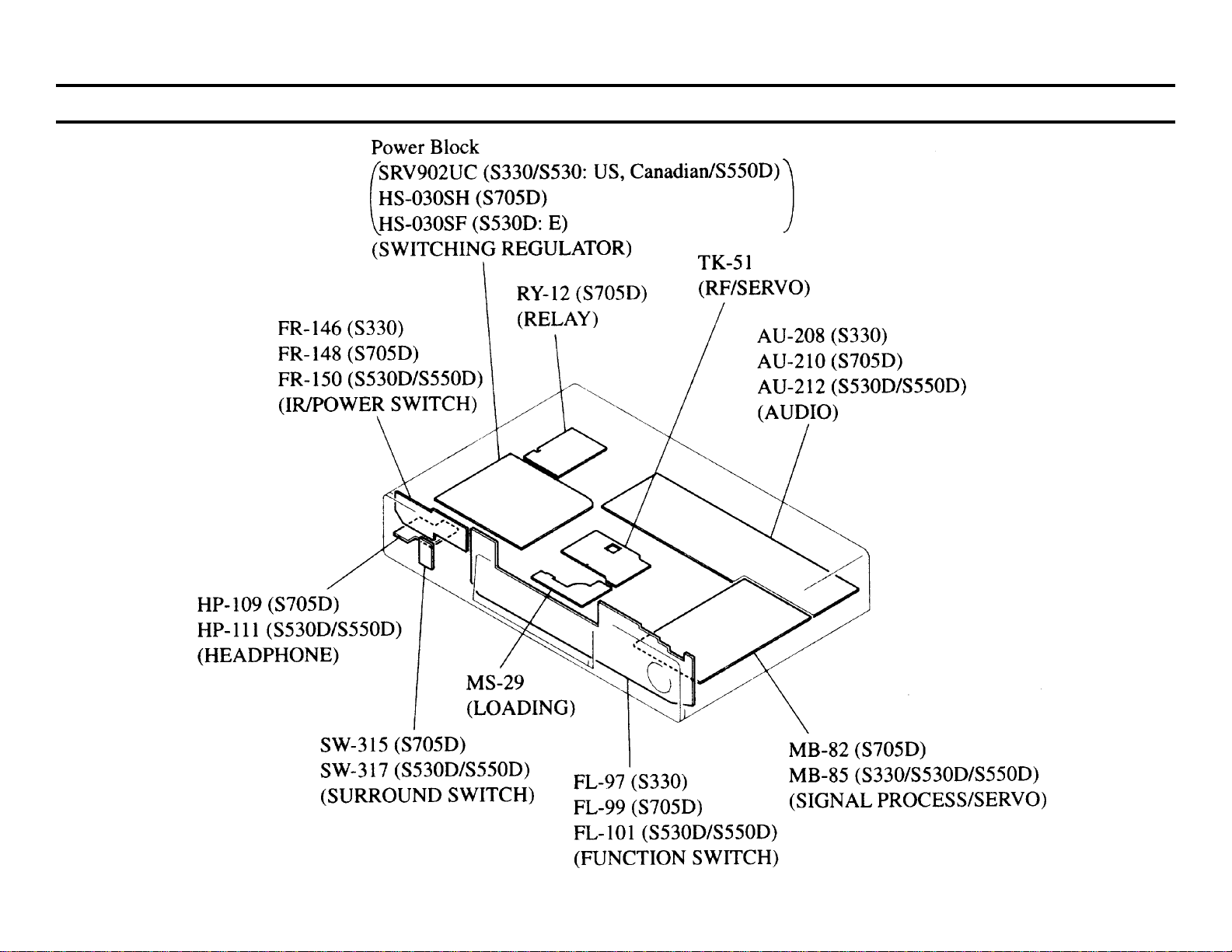

BOARD LAYOUT

Page 11

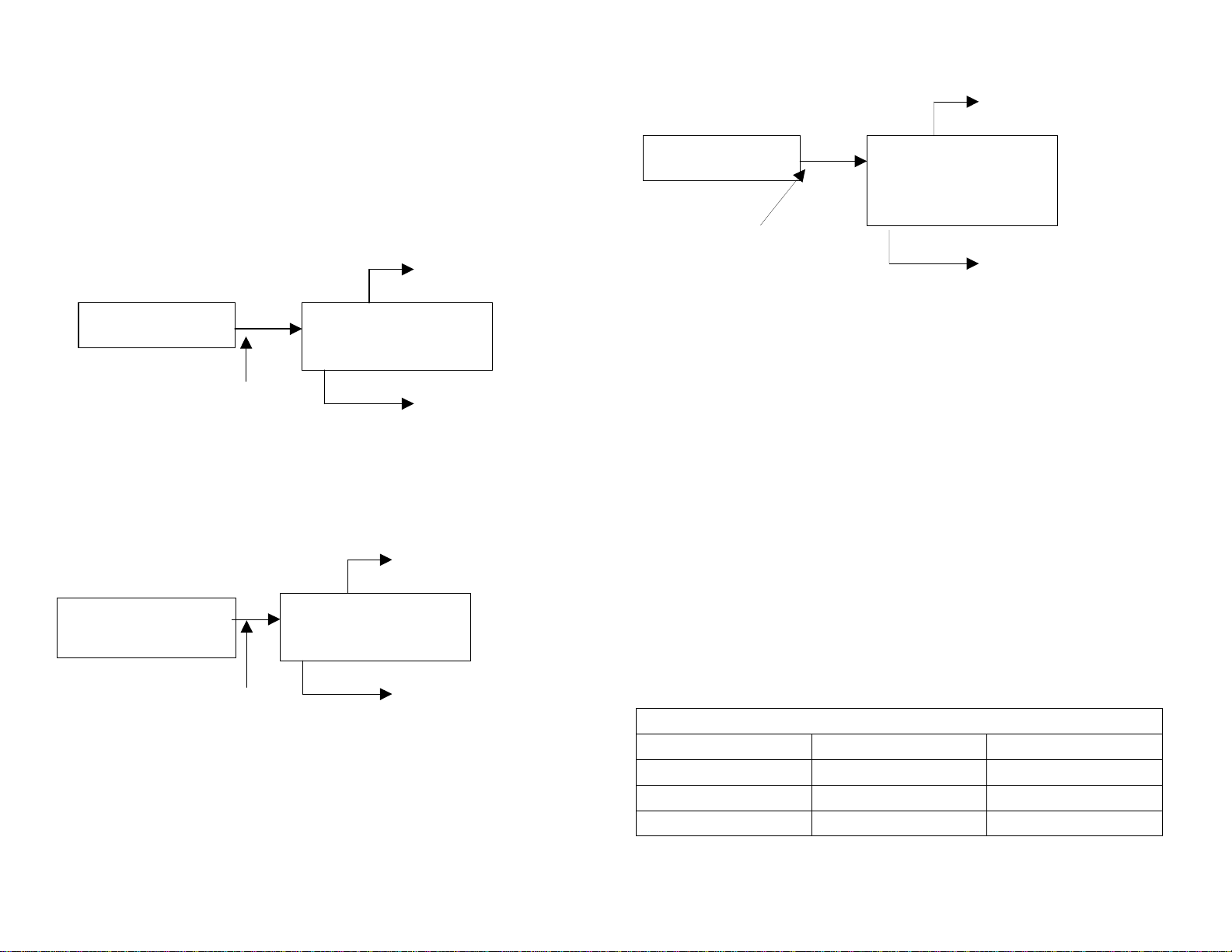

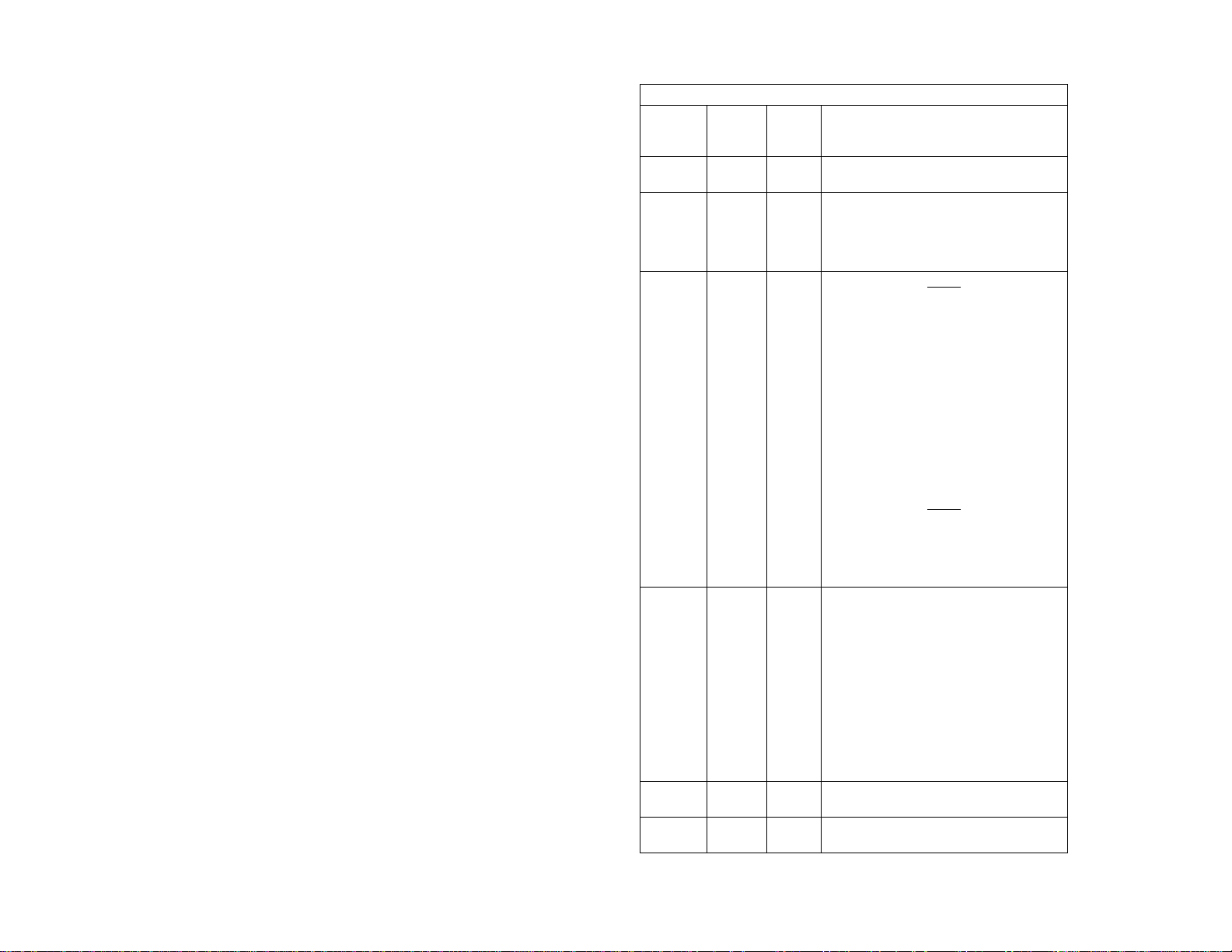

DVD Features

gg

DVP-S330

DVD Models

DVD Models

MSRP * 449.00$ 499.00$ 599.00$ 899.00$ 1,399.00$

General

Single Optical Assembly x x x

Dual Optical Assembly x x

Active laser platform tilt servo x x x x

TV / receiver / DVD Remote x x x x

Advanced Test Mode x x x x

Glow in the dark Remote keys x x

Glass Epoxy Circuit Boards x

Anti-Resonate Chassis & tray x

Copper Plated Shielded Chassis x

Video

10 bit Video D/A Converter x x x x

Digital RF Processor x x x x

Digital Noise Reduction x x

Video Page Bookmark x x x

2 Composite Video Outputs xxxx x

2 S-Video Outputs xxxx x

Component Video (Y, U, V) Outputs x x x x

DVP-S530D

DVP-S550D

DVP-C600

DVP-S7700

Audio

96kHz / 24 bit audio D/A Converter xxxx x

Sony Digital Cinema Sound x x

Virtual Surround Sound x

Dolby AC-3 Surround Decoder x x

DTS Decoder

2 Analog Outputs xxxx x

Coax & Optical Digital Outputs xxxx x

1/4" Headphone Output x x x x

* MSRP = Manufacturer's Su

ested List Price

6

Page 12

7

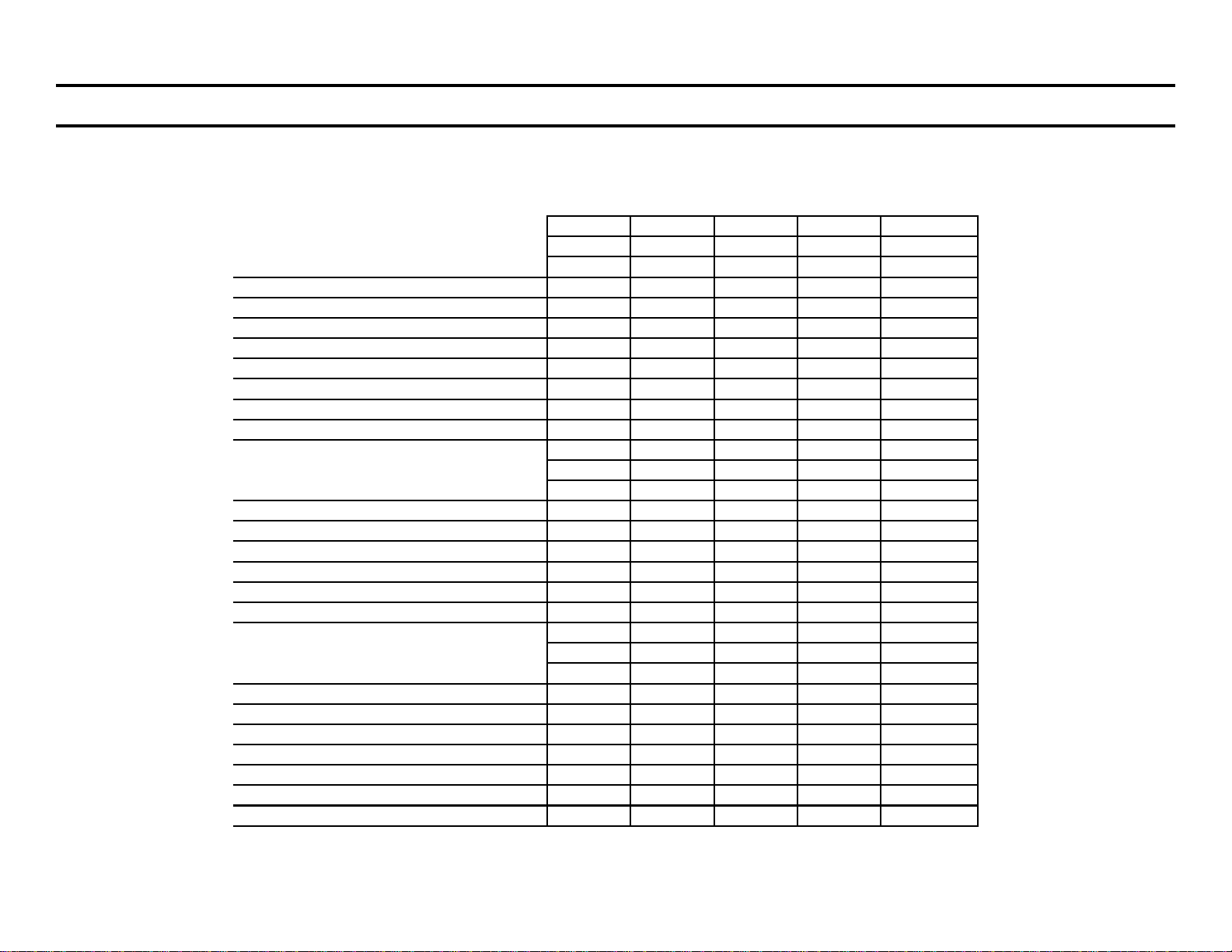

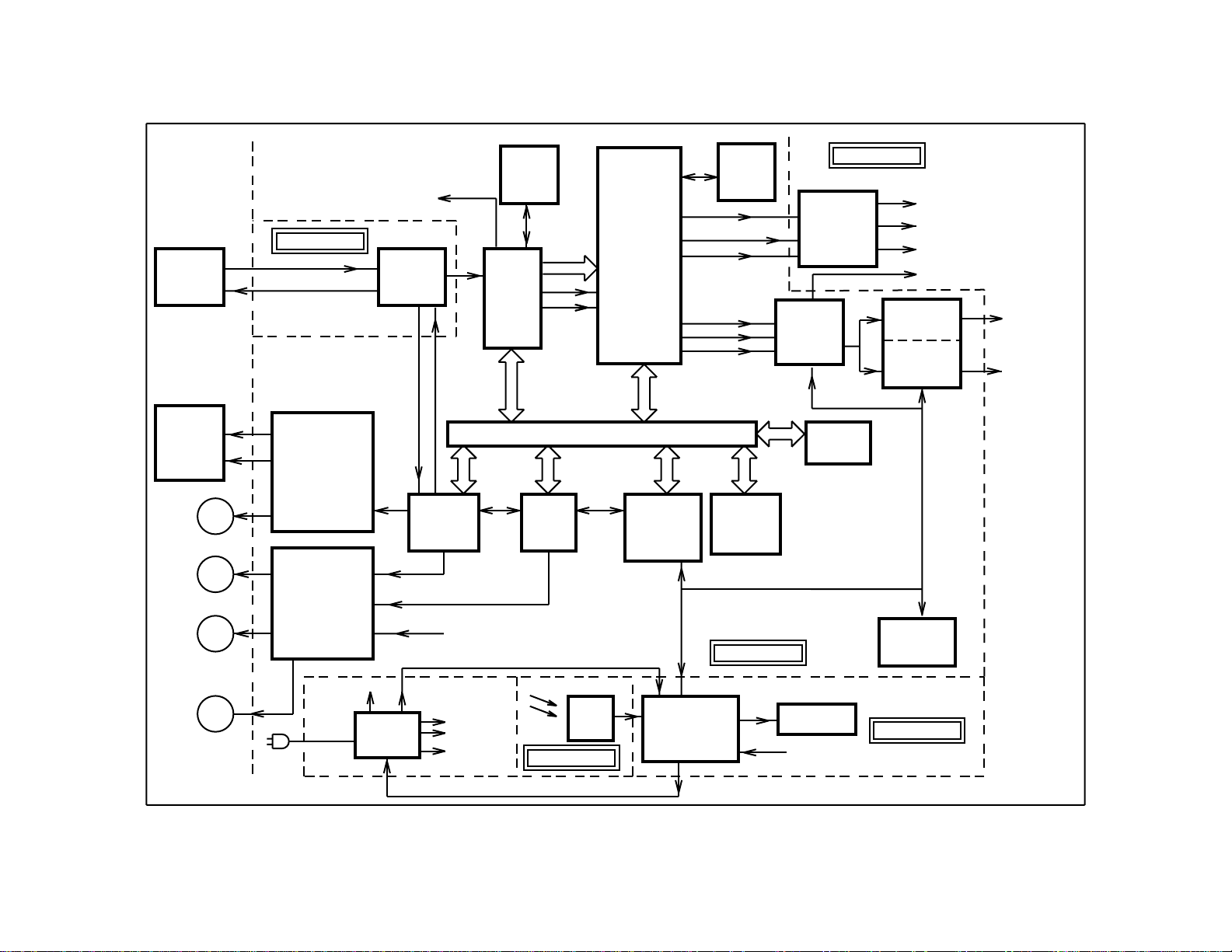

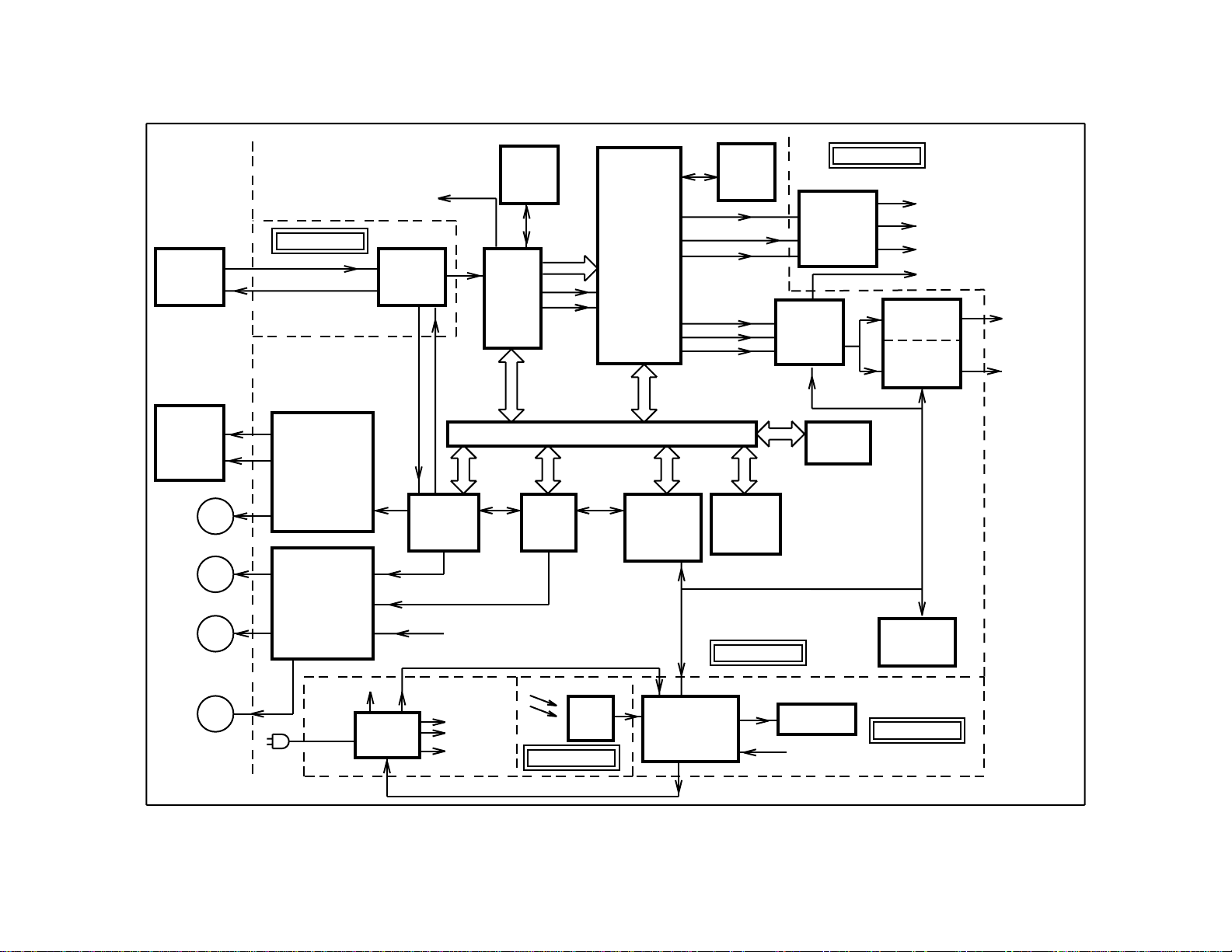

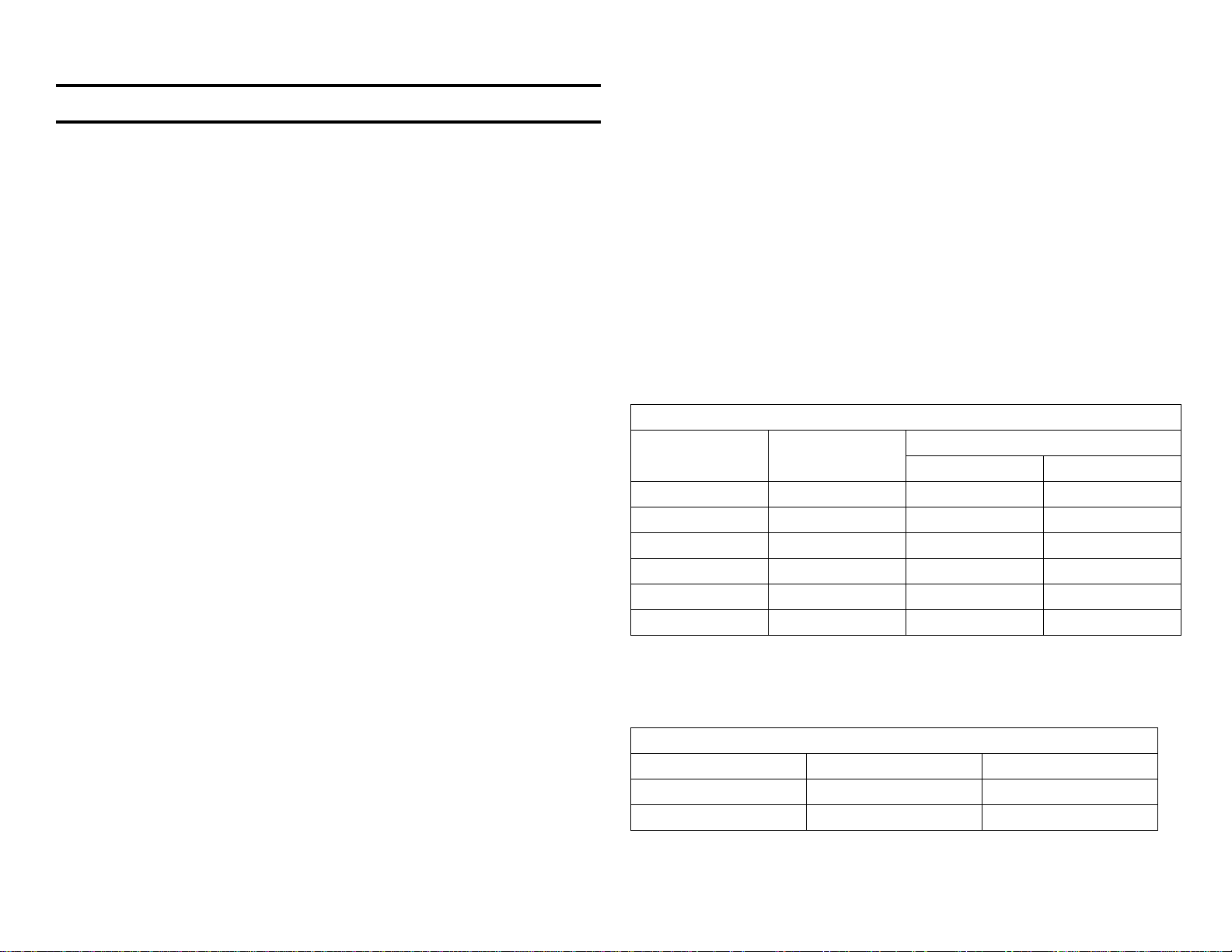

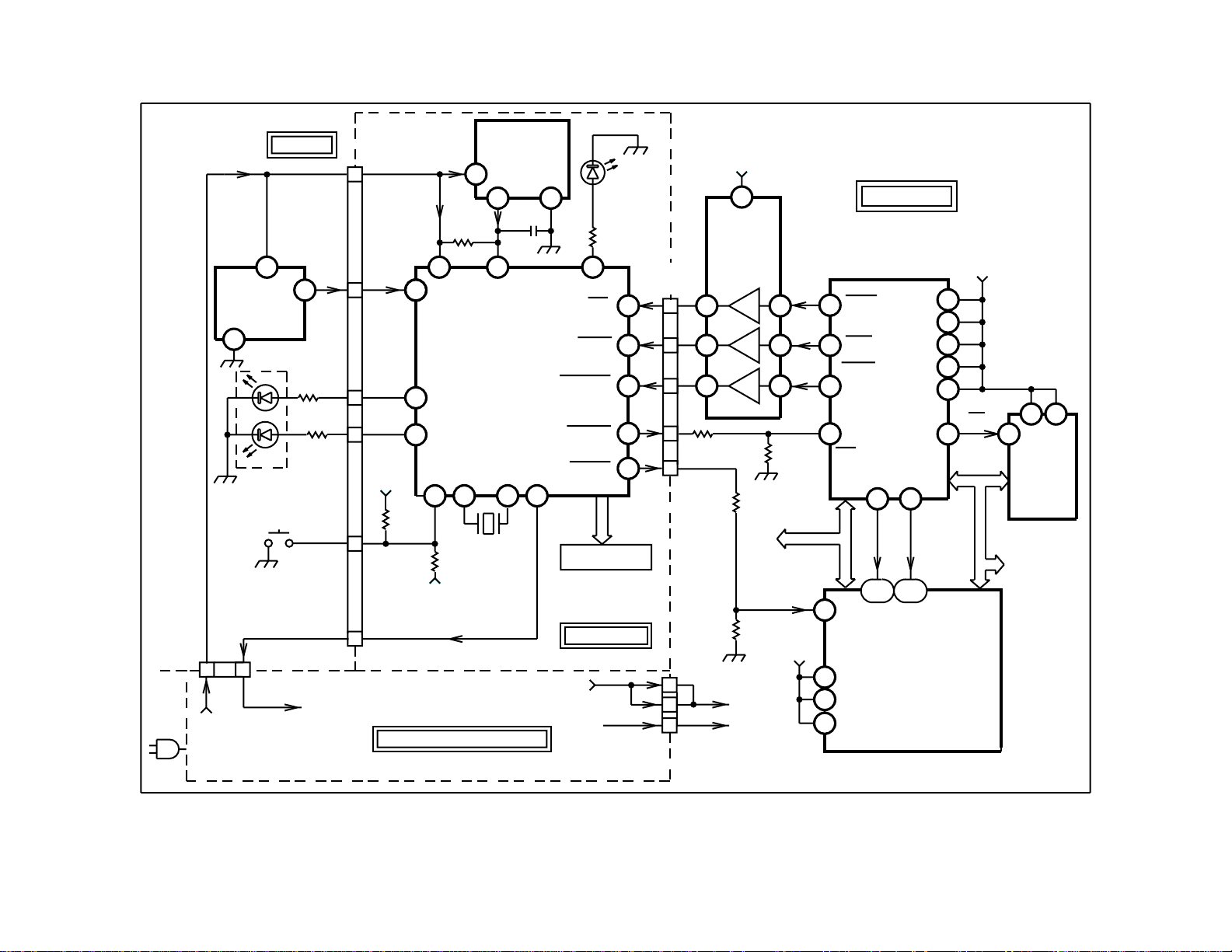

Block Diagram

There are four major stages within this DVD player. They operate in this

sequence to produce the discs’ video and audio:

· Power Supply

· Communications

· Servo Control

· Video and Audio Processing

Power Supply

The power supply block delivers five different voltages. Ever 5V is the

only voltage present when the unit is plugged into AC. Ever 5V powers

Interface IC201 to switch on the remainder of the voltages when it receives the power ON (P Cont) command.

Communications

Plug In

At plug in, Interface IC201 powers on the unit for 1.3 seconds, keeping

the display dark. During this time there is a brief communication between

Interface IC201 and System Control IC202 on the serial bus. At the conclusion of this communication “handshaking”, the front panel Dolby Digital

indicator lights and quickly extinguishes as the unit powers off. The front

panel red standby light is on during the entire initial communication, never

turning green when momentarily powering up at plug in.

Power ON

At power ON, the red standby light turns to green and the power supply is

turned on. After another brief communication between IC201 and IC202,

IC202 retrieves and implements the start up program stored in Flash

Memory IC205.

The start up program requires IC202 to check for the presence of these

six ICs on the parallel bus and IC501 on the serial bus:

ICs Checked During Start Up

Name Number Purpose

1. Flash ROM IC205 Start up program instructions

2. Hybrid Gate

Array

3. SRAM IC204 IC202’s local memory

4. AV Decoder IC401 Audio (AC-3) and Video (MPEG 2)

5. ARP2 IC303 CD/DVD data processing and

6. Servo IC701 Analog servo control

7. Audio DSP IC501

If an IC does not reply, IC202 instructs IC201 to power off the set.

IC601 Expansion port for System Control

IC202 to indirectly communicate with

others on the parallel bus.

decoder

separation

Dolby Prologic, Rear channel delays,

5.1 channel downmixing to 2 channels

Servo Control

At the successful conclusion of the start up program, IC202 retrieves servo

parameter data from EEProm IC201 using the serial bus. Then IC202

communicates with expansion port HGA IC601. IC601 relays the information to other ICs connected to it. One of those ICs is IC701. Servo

IC701 is instructed to reset the base unit mechanism to the initial position

and confirm it:

· Tray closed

· Tilt servo at mid position

· Sled returned to home position

If the initial position is not confirmed before a time limit (“time out”), IC201

will power off the set. Confirmation comes from IC701 through IC601 to

IC202.

IC202 then sends commands back to servo IC701 for disc detection.

Page 13

MECHANISM

OPTICAL

DEVICE

RF

TK-51 BD.

LD

SPINDLE

CONTROL

IC802

IC001

RF

AMP

FE

TE

PI

RF

S.

DATA

CLK

IC304

DRAM

IC303

ARP2

DVD

DATA

CD

DATA,

CLK

IC401

AV

DECODER

Y,C

Y,P , P

Y

SPDIF,

ACHI-6,

CLK

IC402

IC403

SDRAM

rb

VIDEO

BUFFERS

IC501

AUDIO

DSP

AU212 BD.

S VIDEO OUT

COMPONENT V OUT

COMPOSITE V OUT

DIGITAL AUDIO OUT

IC902

DAC

IC905-7

DAC

ANALOG

AUDIO

OUT

5.1 CH

AC-3

OUT

FOCUS

COIL

TRACK

COIL

TILT

SPINDLE

SLED

LOADING

IC801

FOCUS

&

TRACKING

COIL

M

M

M

M

TILT MOTOR

DRIVER

IC802

SPINDLE,

SLED, &

LOADING

MOTOR

DRIVER

3.3V EVER 5V

POWER

BLOCK

IC701

SERVO

SPINDLE

CONTROL

IC303

5V

12V

-12V

P CONT.

PARALLEL BUS

IC601

HGA

IR

REC

FR150 BD.

IC202

SYSTEM

CONTROL

BLOCK DIAGRAM

IC201

INTERFACE

MICRO

IC205

FLASH

MEM

SERIAL BUS

MB-85 BD.

IC204

SRAM

DISPLAY

PANEL

SWITCHES

IC201

EEPROM

FL101 BD.

6 22 991DVD02 1146

8

Page 14

9

Video and Audio Processing

After the servos have begun, RF data will come from the optical assembly

within the base unit. The “eye pattern” RF data is split into two paths to

provide:

1. Feedback signal to lock the servos; and

2. Video and audio information.

In the A/V processing chain, the RF data is processed by the following

ICs:

Audio / Video Processing ICs

Name IC

RF Amp IC001 A/V

ARP2 IC303 A/V

Decoder IC401 A/V

DSP IC501 A

DAC IC902 A

DACs IC905-

IC907

Audio

Video

(both)

(both)

(both)

A 3 Digital to analog converters for the

or

Matrix the optical outputs to produce

signals for servo and A/V circuits

16 to 8 bit Demodulation

•

Descrambles the main data using

•

external memory IC304

Generates bit clock

•

MPEG decompression using the

•

external IC402 and IC403

memories

Crops the 16x9 image for a 4x3 TV

•

picture

Controls spindle motor speed

•

Sends disc’s control and menu

•

data to IC202

On screen display graphics

•

D/A Converter (analog video

•

output)

MPEG audio decompression

•

Dolby Digital AC-3 decompression

•

using external SRAM IC402 /

IC403

Sound enhancements when there

•

is no AC-3 received (Rear channel

delay)

Downmixing of 6 channel AC-3

•

into 2 (L/R) channels

Dolby Prologic decoding

•

Digital coax and optical output

•

Rear channel delay

•

Front/rear level balancing

•

Test tone generation

•

Digital to analog converter for the front

left and right channels

six AC-3 channels

Purpose

Video

Audio

Page 15

MECHANISM

OPTICAL

DEVICE

RF

TK-51 BD.

LD

SPINDLE

CONTROL

IC802

IC001

RF

AMP

FE

TE

PI

RF

S.

DATA

CLK

IC304

DRAM

IC303

ARP2

DVD

DATA

CD

DATA,

CLK

IC401

AV

DECODER

Y,C

Y,P , P

Y

SPDIF,

ACHI-6,

CLK

IC402

IC403

SDRAM

rb

VIDEO

BUFFERS

IC501

AUDIO

DSP

AU212 BD.

S VIDEO OUT

COMPONENT V OUT

COMPOSITE V OUT

DIGITAL AUDIO OUT

IC902

DAC

IC905-7

DAC

ANALOG

AUDIO

OUT

5.1 CH

AC-3

OUT

FOCUS

COIL

TRACK

COIL

TILT

SPINDLE

SLED

LOADING

IC801

FOCUS

&

TRACKING

COIL

M

M

M

M

TILT MOTOR

DRIVER

IC802

SPINDLE,

SLED, &

LOADING

MOTOR

DRIVER

3.3V EVER 5V

POWER

BLOCK

IC701

SERVO

SPINDLE

CONTROL

IC303

5V

12V

-12V

P CONT.

PARALLEL BUS

IC601

HGA

IR

REC

FR150 BD.

IC202

SYSTEM

CONTROL

BLOCK DIAGRAM

IC201

INTERFACE

MICRO

IC205

FLASH

MEM

SERIAL BUS

MB-85 BD.

IC204

SRAM

DISPLAY

PANEL

SWITCHES

IC201

EEPROM

FL101 BD.

6 22 991DVD02 1146

10

Page 16

11

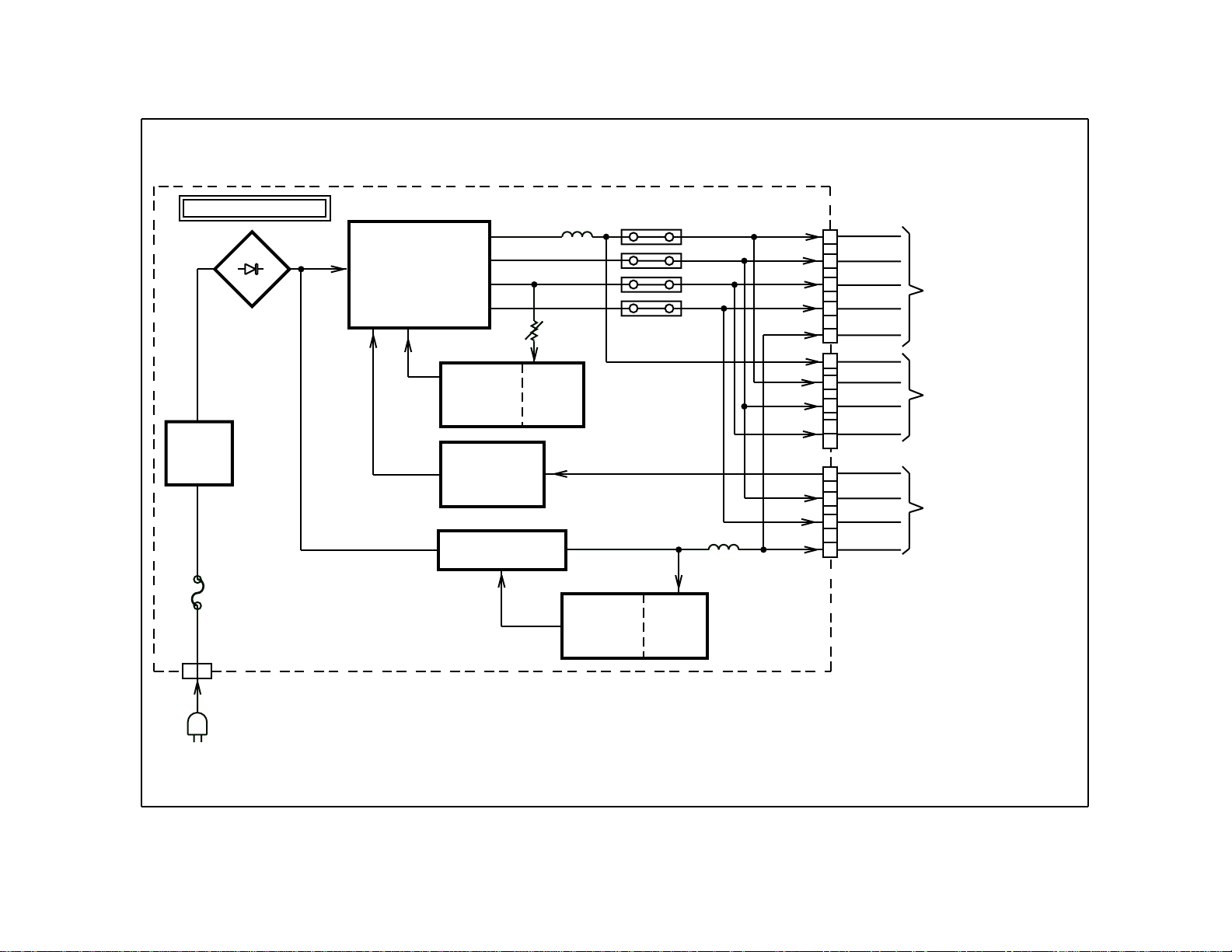

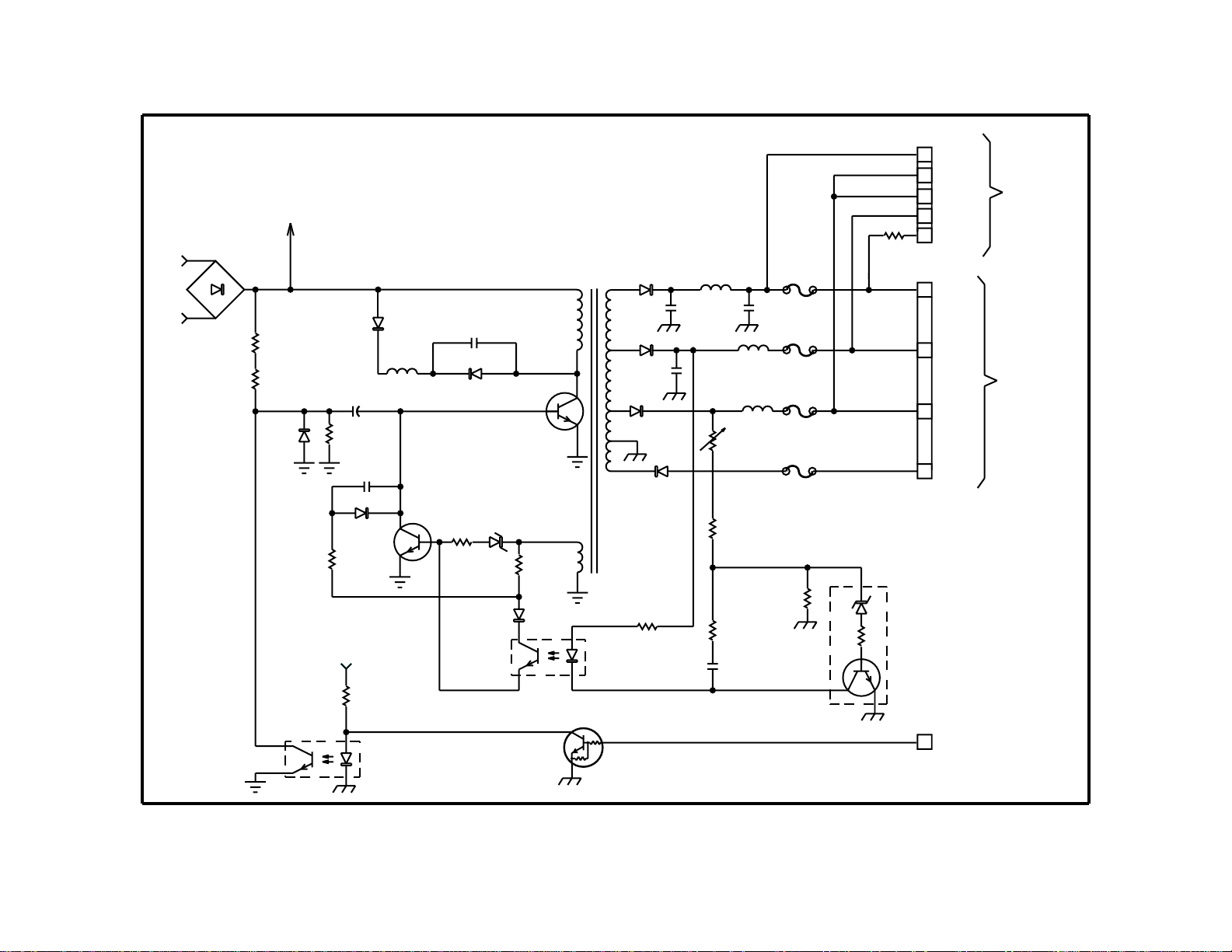

Power Supply Block

The power supply is on a single board located to the left of the DVD

mechanism. This board contains both the standby and the main power

supply. The input line filter L101 and the board connectors are the only

parts that are not available.

Standby Power Supply

This power supply produces Ever 5V as long as AC is present. Ever 5V is

supplied to interface IC201 (MB85 board) and the mute transistors (AU212

board). The standby power supply consists of an oscillator and an error

regulator. The oscillator consists of switch Q121 and a control transistor

Q122. The oscillator output is applied to T102. T102’s secondary is

rectified to output Ever 5V.

Regulation

The Ever 5V voltage regulation circuit uses:

· IC202 – error detector

· PC121 – photocoupler

· Q122 – control transistor.

IC202 samples the Ever 5V output and produces a correction voltage.

Photocoupler PC121 passes the error voltage from the cold ground circuit to the hot ground side circuit. The control transistor Q122 receives

the error voltage and uses it to alter the base bias of switch Q121. The

change in bias alters the off time of the oscillator signal. This changes the

oscillator frequency. The changes in frequency affect the efficiency of the

transformer, which regulates the Ever 5V.

Main Power Supply

The main power supply works similarly to the standby supply except the

main supply is switched, handles more power and has multiple secondaries.

The main power supply is switched ON by PCONT from the Interface IC

on the FR148 board. A high at PCONT enables switch Q101 to begin

oscillating. Transformer T101 produces several output voltages that are

rectified into DC for the remainder of the DVD unit.

When a shorted spindle motor driver IC802 loaded the unfused +12V

supply line, the main oscillator quit. The oscillator worked again when the

short was removed.

Regulation

The 3.3Vdc output is used to regulate the main power supply. Error

detector IC201 receives the 3.3Vdc and produces a correction voltage. If

the input voltage increases, the error detector output decreases. The

PC101 photocoupler passes the correction signal to the control transistor

Q102. Q102 adjusts the off time of the oscillator signal to correct the

3.3Vdc output the secondary. If the DVD power consumption is normal,

the remainder of the T101 outputs will be correct.

Power Consumption

The current along each supply line was measured in both the idle and the

DVD disc playback mode.

Model DVP-S530D Current Consumption

Part replaced

by Ammeter

Ever 5V L205 30ma (set off) 77mA (set on )

+12V partial PS201 196mA 198mA

+12V total L201 236mA 350-700m A

+5V PS202 281mA 305m A

+3.3V PS20 3 * 894mA 950mA

-12V PS204 129mA 130m A

* Use short ammeter leads or the unit will not PB the disc and the display

will not come on. The PS203 current without the display will only be

580mA.

Idle Disc PB

CurrentSupply line

Oscillator Frequencies

Power Supply Oscillator Frequencies

Power Supply Set Off Set On (stop mode)

Standby (Q121/D) 57.45kHz 49.65kHz

Main (Q101/C) 0 101.2kHz

Page 17

SRV902UC BOARD

D101-104

L101

LINE

FILTER

F101

CN101

1

2

Q101,102,T101

MAIN OSC.

+12V

+5V

RV201

PC101

PHOTO

COUPLER

PC102,Q201

POWER

CONTROL

Q121,122,T102

STBY OSC.

L201

+3.3V

-12V

IC201

ERROR

DET.

EVER 5V

PC121

PHOTO

COUPLER

PS201

PS202

PS203

PS204

IC202

ERROR

DET.

L205

CN201

CN202

CN203

+12V

4

+5V

2

+3.3V

1

-12V

6

EVER 5V

7

M+12V

2

A+12V

1

+5V

5

+3.3V

6

7

PCONT

1

+5V

3

-12V

5

EVER 5V

2

TO

AU212 BD.

ANALOG AUDIO/

VIDEO

TO

MB 85 BD.

SERVO CONTROL

TO

FR148,FL101 BDS.

INTERFACE/

DISPLAY

POWER SUPPLY BLOCK

12

4 27 992DVD02 1137

Page 18

13

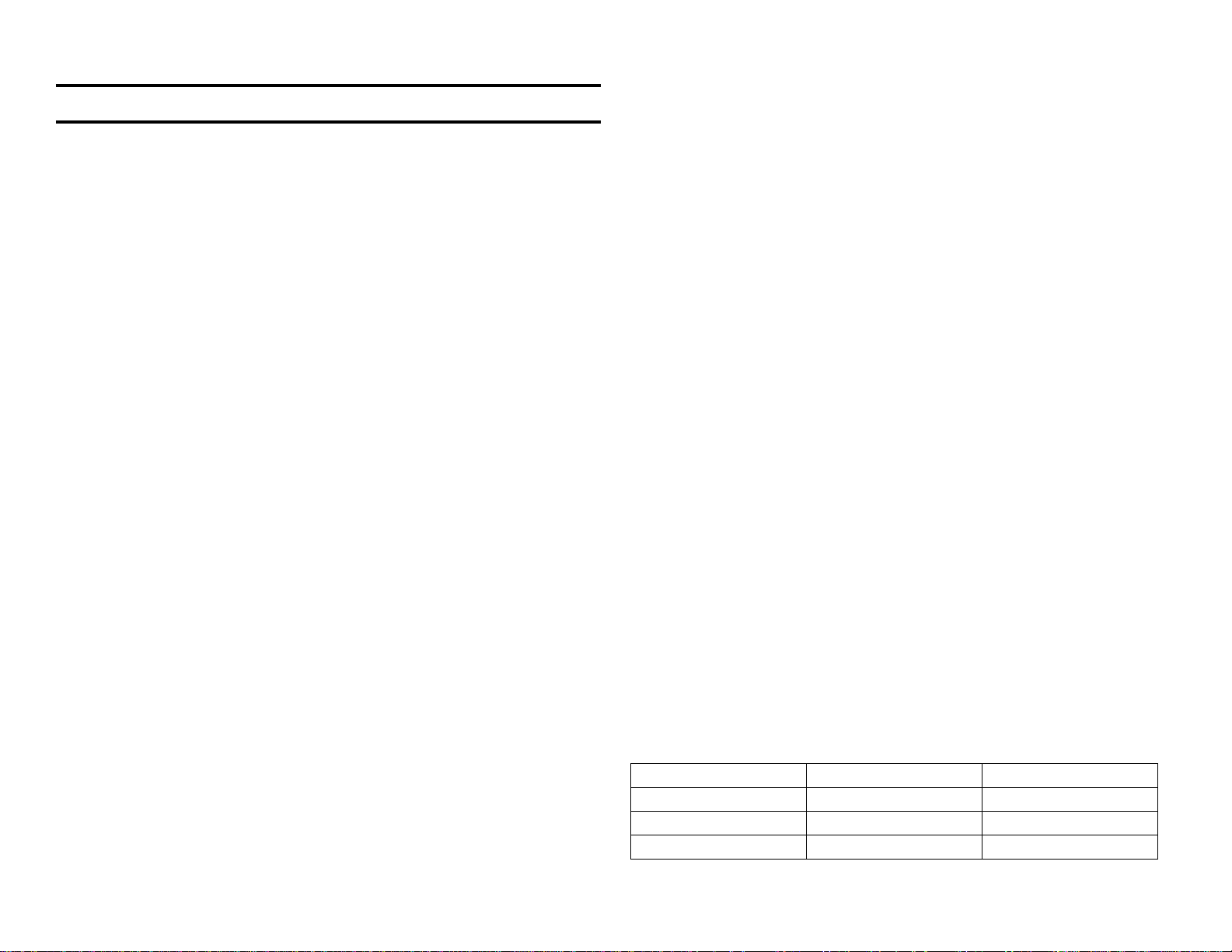

Standby Oscillator

The standby oscillator produces Ever +5 volts when the DVD player is

plugged into 120VAC. This Ever 5V is applied to the Interface IC201 (on

the circuit board behind the front panel) and the audio and video mute

transistors (on the rear board). The standby oscillator stage consists of

two transistors and a transformer. Regulation is performed using the Ever

5V output to control the off time of the oscillator cycle.

The standby oscillator has three operational parts:

· Start

· Run

· Regulation

Start

At AC plug in, the standby oscillator stage begins when R122 and R123

bring the FET Q121 gate voltage from 0 to about 1volt. This turns on the

low power FET, allowing it to pass Drain to Source current and complete

T102’s primary circuit path to hot ground.

Run

Oscillator transistor Q121 turns ON

As current flows in T102’s upper left primary winding, a voltage is induced

in the lower secondary winding that will keep FET oscillator Q121 turned

ON. A positive voltage from the lower secondary winding takes two paths.

The first path is through R126, R125 and C121 to Q121’s gate. This

keeps Q121 conducting. The second path is through R127 and R128 to

Q122’s base. Q122’s collector is connected to the oscillator’s gate. As a

result, Q122 becomes an active resistor. Q122’s conduction prevents the

gate voltage from rising too high (protection) and later we will see that it is

used for regulation.

Oscillator transistor Q101 turns OFF

When Q101 is saturated, there is no longer a change in T102’s primary

current. The voltage induced into the lower secondary winding decays.

This reduction in bias voltage permits Q121 to turn OFF. With Q121 OFF,

the magnetic field in T102’s primary winding collapses, causing current

flow thorough C123 and limiter R130.

The collapsing magnetic field induces a negative voltage into the lower

secondary winding. The negative voltage takes two paths to reset the

oscillator. The first path is through R126, R125 and C121 to keep oscillator transistor Q121 OFF. The second path is through D121 and R128 into

the base of Q122. This turns off transistor Q122 in preparation for the

next oscillator cycle.

Regulation Concept

Regulation of the Ever 5V line is accomplished by sampling the output

voltage and using it to reduce the off time of the oscillator. By reducing

the off time, the total oscillator cycle is reduced. Shortening the time it

takes to complete a cycle means its frequency is increased.

This oscillator signal is applied to transformer T102. A transformer has

an optimum frequency that will allow maximum power transfer (at resonance). When the applied oscillator frequency is above resonance, the

efficiency drops and its secondary voltage is reduced. By varying the

applied frequency, the output voltage can be regulated.

Regulation Circuitry

IC202 is the error regulator for this stage. Voltage divider R212, R209

and R210 reduce the Ever 5V so there is 2.5V at IC202’s input. This

allows its operation in the linear region. IC202’s output (collector) is inversely proportional to its input. The collector output is connected to the

opto-isolator diode that passes the error signal to the hot ground oscillator

circuit.

If the Ever 5V increased, the opto-isolator transistor would conduct more,

reducing the resistance between the lower secondary winding and Q122’s

base. The reduced resistance allows more current to flow, permitting

Q122 to turn on sooner. The sooner it turns on, the sooner the FET turns

off, increasing its frequency of operation that results in a reduced output

voltage for regulation.

IMPORTANT VOLTAGES MEASURED WITH THE SET OFF:

Voltage DC Voltage

Q101/Drain 300Vp-p 166V

Q101/Gate 13.8Vp-p 2V

D121/Anode 16Vp-p 0V

Page 19

D101-D104

MAIN OSC

R121

T102

C102

L101

LINE

FILTER

C108

220

Q122

R122

R123

R128

22k

C121

R125

R127

D122

PC121

ON3131

R126

R129D121

100 OHM

IC202

AN1431

Q121

R124

C123

R130

D

S

R206 470 OHMS

4.1V

R207

1k

R208

D206

D208

C212

5V

++

C210

100

R212

R209

2.5V

R210

CN203L205

CN201

+

C211

100

2

7

EVER 5V

TO FR150 BD.

(DISPLAY)

EVER 5V

TO AV212 BD.

(MUTE)

STANDBY OSCILLATOR

14

6 28 9929DVD02 1175

Page 20

15

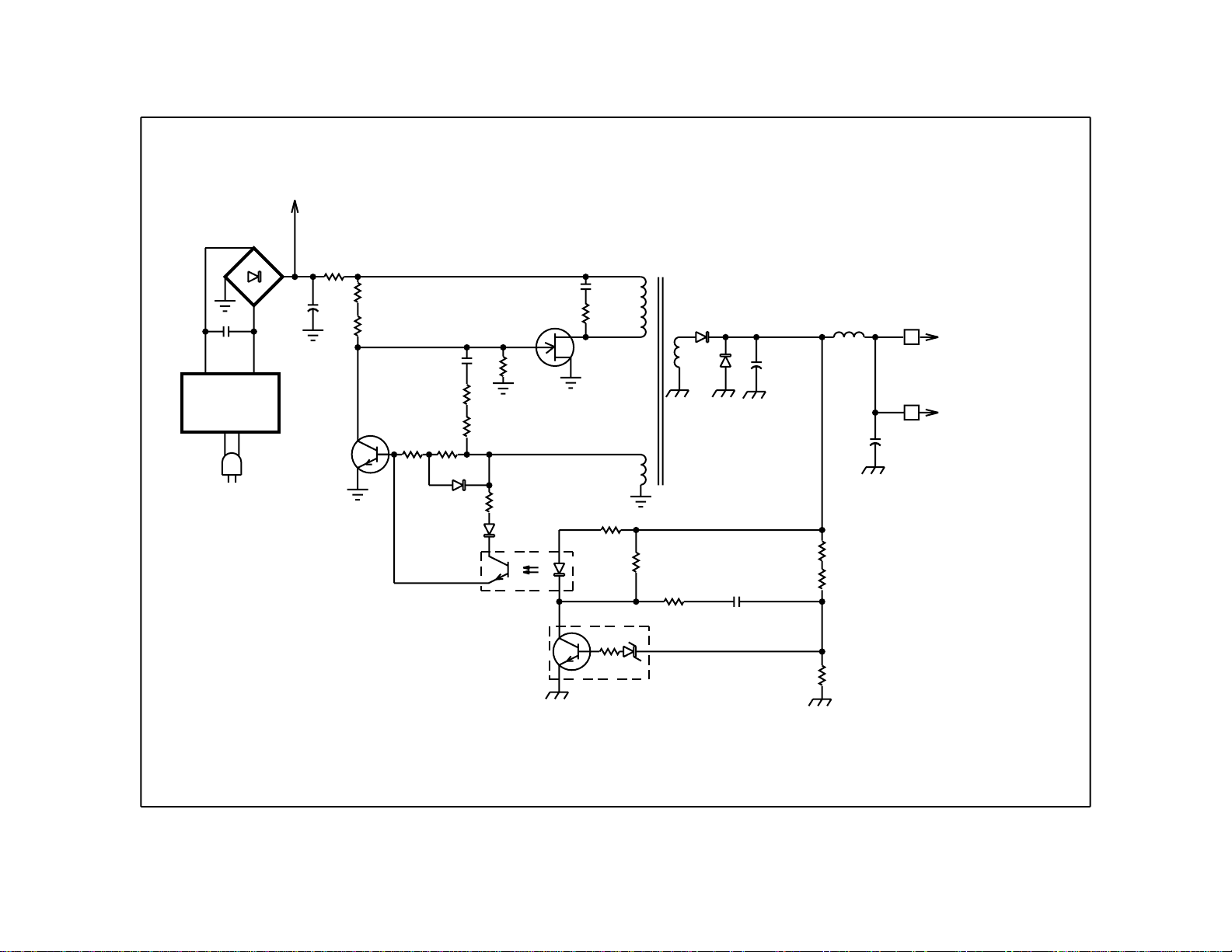

Main Oscillator

The main oscillator stage operates like the standby oscillator stage except that the main oscillator is switched ON/OFF and there are multiple

secondaries to supply the needs of the DVD player.

The main oscillator has four parts:

· Enable

· Start

· Run

· Regulation

Enable

Oscillator OFF

The operation of the main oscillator is inhibited by PC102. When the unit

is plugged into AC, Ever 5V is made by the standby oscillator stage and is

used to turn on the opto-isolator LED in PC102. The LED’s infrared light

turns on the phototransistor and it conducts.

PC102’s phototransistor is connected to oscillator transistor Q101’s start

voltage applied to the base. When PC201 conducts, the start voltage

from R102/R103 is grounded, stopping the oscillator.

Oscillator ON

Q201 removes the voltage to the opto-isolator diode in PC102, permitting

the main oscillator stage to run. When PCONT from Interface IC201 goes

high at CN203/pin 1, Q201 turns ON. Its conduction grounds the voltage

from R211, removing voltage from the LED. PC102 transistor turns off,

removing the ground from R103 so the main oscillator transistor Q101

can start.

Start

Once the PCONT control line at CN203/pin 1 goes high, PC102’s transistor no longer conducts. The ground is removed from the start voltage at

the junction of C111 and R104 so it rises. It will reach 6.6V, limited by the

voltage divider formed by R102, R103 and R104.

Sufficient current passes through C111 during this voltage increase to

turn ON main oscillator Q101. This is how oscillator transistor Q101 starts

conducting (turns ON) and the main oscillator starts.

Run

Q101 Turns ON

When Q101 turns ON, current flows through the main transformer’s pri-

mary winding at the upper left of T101. This induces a positive voltage to

the lower T101 winding that follows two paths. The first path is through

R106, R107, D109 and C113 to Q101’s base to keep it conducting. The

second path is through D108 and R109 to bias Q102. Q102 acts like an

active resistor at Q101’s base to keep the voltage from becoming excessive (protection) and is used later for regulation. Consequently the correct value components and transistors are critical.

When Q101 reaches saturation, there is no longer a change in T101’s

primary current. The steady current flow no longer induces a voltage into

the lower secondary winding and the secondary voltage decays.

Q101 Turns OFF

The reduction in secondary voltage turns Q101’s OFF. The magnetic

field in T101’s primary collapses. D105, limiter, L102 and C110 short its

energy. D106 is used to discharge C110 (when Q101 is ON).

The collapsing (changing) magnetic field induces a negative voltage at

the lower secondary winding. This negative voltage from T101 passes

through R106, R107 and C113 to the base of oscillator transistor Q101. It

is used to cut off Q101 to conclude this oscillator cycle.

Regulation

The 3.3-volt output is monitored by error regulator IC201 and used to

control the conduction of phototransistor PC101. If the 3.3-volt line rises,

the phototransistor conducts harder. This reduces the resistance between

the lower secondary winding and Q102’s base, increasing Q102 base

current.

The increased base current drives Q102 harder, lowering the oscillator’s

base bias voltage and causing the oscillator to be turned OFF sooner.

When part of the oscillator waveform is shortened, its frequency increases.

This reduces T101 efficiency and the 3.3V output voltage is returned to

normal.

IMPORTANT VOLTAGES:

Q101/Collector = 336Vp-p; 150Vdc.

PC101/collector = 2.6Vdc. PC101/emitter = 0.21Vdc

Feedback secondary voltage at D108/cathode = 20Vp-p; 0.21Vdc.

Page 21

AC

R102

R103

STBY

OSC

L105

D110

R107

C111

4.7mF

R104

C113

D109

EVER 5V

R211

D105

L102

Q102

C110

D106

R109

D107

PC101

ON3131

Q101

D108

MTZJ3.0

R106

47

1W

T101

4V

D201

D202

C203

D203

R201

D204

L201

C201

C202

L202

L203

RV201

3.3V ADJ.

R204

R205

R203

C205

PS201

0.5A

PS202

1A

PS203

PS204

0.75A

2.5V

CN202

R213

IC201

AN1431

2

6

7

5

1

CN201

4

2

1

6

M+12V

+3.3V

+5V

A+12V

+12V

+5V

+3.3V

-12V

TO

MB85 BD.

TO

AV212 BD.

PC102

ON3131

Q201

MAIN OSCILLATOR

16

P CONT

CN203

FROM

1

FR150 BD.

7 12 9930DVD02 1174

Page 22

17

Power Control

Plug In

When the DVD player is plugged into AC, the power supply only outputs

Ever 5V to:

· Analog audio mute transistors – AU-212 board

· Interface IC201/pin 16 – FL101 board

· Reset IC202/pin 5 - FL101 board

The mute transistors are biased ON to keep the 5.1, headphones and L/

R channel audio outputs grounded.

Ever 5V applied to Interface IC201 starts the 4MHz X201 crystal connected to pins 14 and 15.

Reset IC202 on the FL101 board uses C211 to hold its pin 4 momentarily

low when Ever 5V is first applied. This resets Interface IC201/pin 18.

After reset, a brief communication occurs between IC201 and IC202. A

momentary light of the front panel blue Dolby Digital LED (D203) marks

the end of the plug in communications and the unit shuts down.

The plug in sequence is listed below:

1. AC plug in

2. Ever 5V is applied to Interface IC201/pin 16

3. X201 becomes active and stays active

4. Red power off/standby LED comes ON.

5. PCONT from Interface IC201/pin 24 goes high to power the set

6. Ready pulse is output IC201/pin 78 as an interrupt line to IC202 to

begin communications. It is difficult to see this low going interrupt

pulse on a a scope, but it will light a scope’s “triggered” LED.

7. IC601 transfers this “ready” (interrupt) information to System Control

IC202 by using another interrupt signal from IC601/pin 155 (low going). The low forces IC202 to generate a chip select (CS1 or CS4) so

the data can be transferred to IC202 on the parallel bus.

8. System Control IC202 sends chip select (difficult to see the low going

pulse from pin 97), bit clock (low pulses from pin 78) and serial data

(high pulses from pin 77) to Interface IC201.

9. IC201 acknowledges by lighting the Digital Dolby LED D203

10. Interface IC201 brings PCONT low, removing power to the set.

Unit is now in standby and ready to be powered ON.

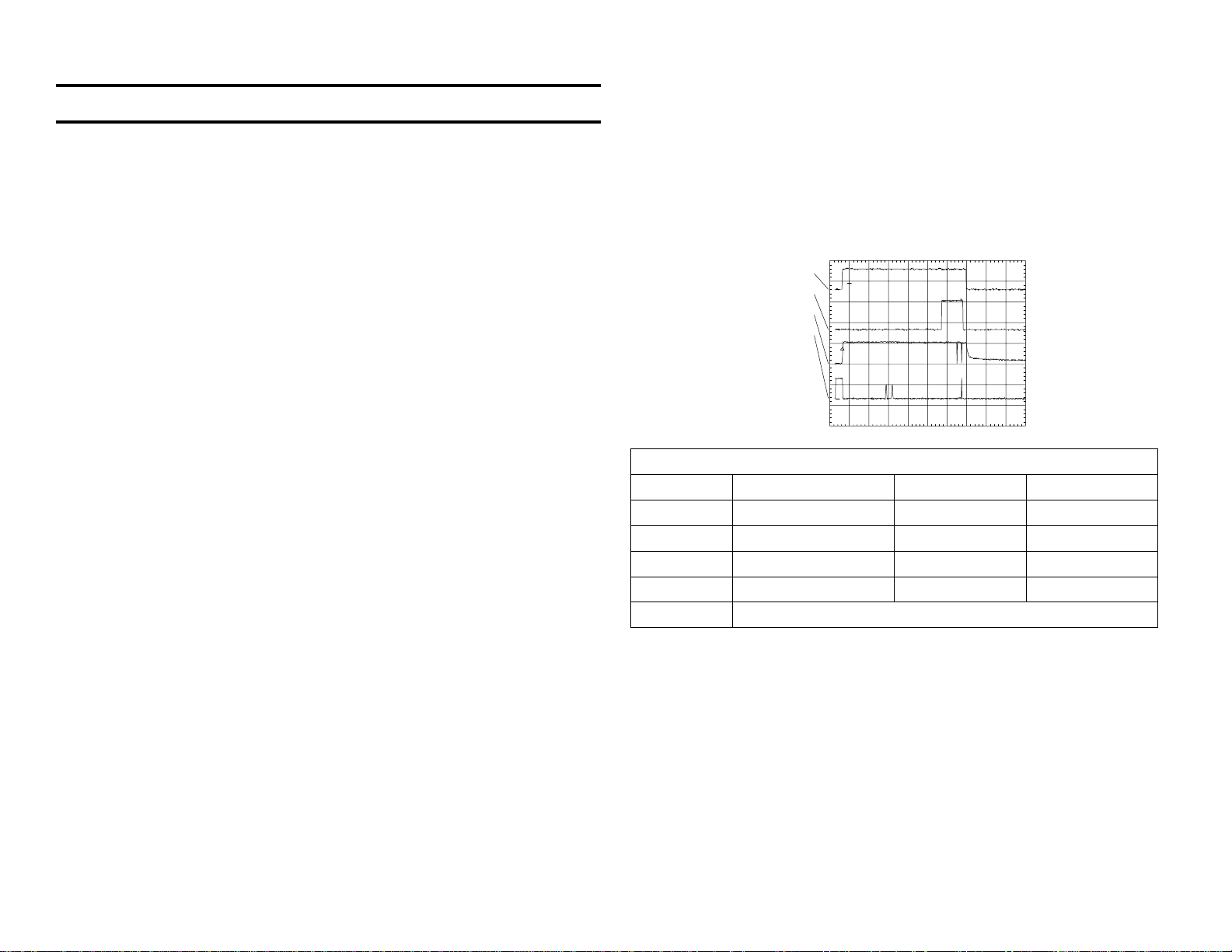

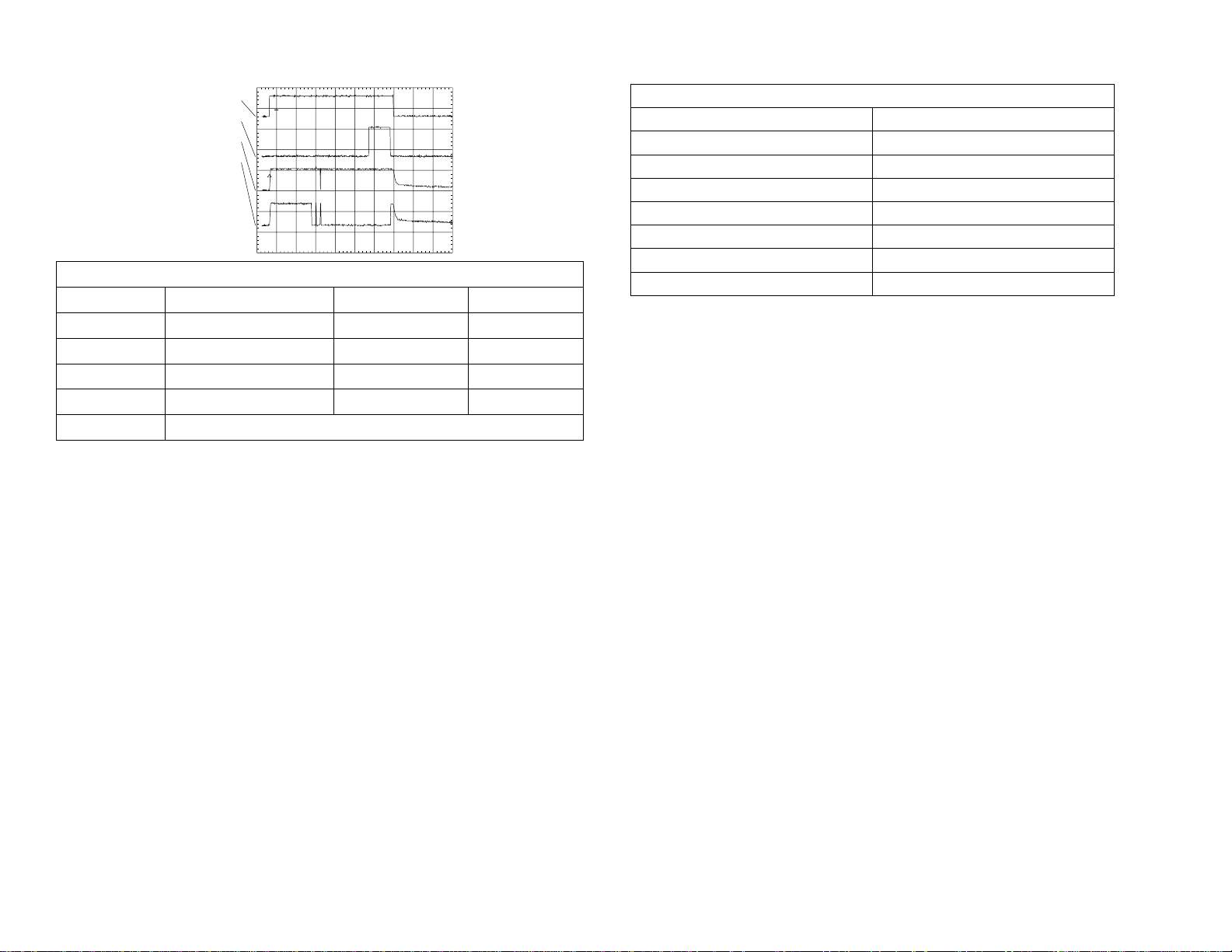

IC201 – IC202 Communications Waveforms

The following sets of waveforms show this communication between IC201

and IC202. Notice that the Dolby Digital LED is turned ON only at the

conclusion of the plug in communications. The LED does not light when

there are incomplete communications.

PM3394, FLUKE & PHILIPS

ch1

ch2

ch3

ch4

Plug in Communications – between IC201 / IC202

Channel 1 PCONT CN203/pin 1 5Vp-p

Channel 2 Dolby Digital LED D203/anode 2Vp-p

Channel 3 CS from IC202 CN006/pin 3 5Vp-p

Channel 4 Data from IC201 CN006/pin 4 5Vp-p

Time base 200msec/div.

The following second set of waveforms is taken of IC202 CS signal (ch 3)

that is replying to IC201. Notice that the return clock (ch 3) and data (ch

4) from IC202 occur before IC201 turns the LED (ch 2) ON.

T

1

2

3

CH1!5.00 V=

4

CH2!2.00 V=

CH3!5.00 V=

CH4!5.00 V= CHP MTB 200ms- 0.40dv ch1+

Name Location Voltage/div

Page 23

EVER 5V

IC051

IR

RECEIVER

3

EVER 5V

FR150

5

CN201/

CN002

R274

2

1

GRN

R072

R071

RED

S071

POWER

12

4

6

7

EVER

5V

3

12

P CONT.

16

9

31

32

R221

R222

FRONT PANEL

BUTTONS

S212-S218

SRV902UC PWR BLK

IC202

RESET

PST9140

5

4

C211

18

IC201

INTERFACE

CONTROL

M38857

MCHE206FP

2415145

X201

4MHz

3

SBUSY1

3.3V

D203

DOLBY

DIGITAL

R285

30

SIN

SCLK

S OUT

SRDY1

DISPLAY

FL101 BD.

5V

CN202

CN001/

72

70

76

71

78

CN202/

CN006

5

6

3

4

2

6

2

5

3

6

11

R044

R036

5V

14

IC203

BUFFER

SN74

HCT08

R037

3.3V

5V

1

4

12

R045

PARALLEL

BUS

22

3.3V

40

20

77

78

97

76

1

SO01

SC0

CSOL

SI0

XIF

INT

MB85 BD.

IC202

SYSTEM

CONTROL

MB91101

PFV

CS4

CS4

4

43

69

70

93

11

CS1

107

141142

CS1

IC601

HGA

CXD8788Q

3.3V

CE

26

IC205

FLASH

ROM

MBM29

LV160

PARALLEL

BUS

4737

POWER CONTROL

18

6 22 9913DVD02 1154

Page 24

PM3394, FLUKE & PHILIPS

ch1

ch2

ch3

ch4

T

1

2

3

CH1!5.00 V=

4

CH2!2.00 V=

CH3!5.00 V=

CH4!5.00 V= CHP MTB 200ms- 0.40dv ch1+

Plug in Communications – between IC201 / IC202

Name Location Voltage/div

Channel 1 PCONT CN203/pin 1 5Vp-p

Channel 2 Dolby Digital LED D203/anode 2Vp-p

Channel 3 Bit clock from IC202 CN006/pin 6 5Vp-p

Channel 4 Data from IC202 CN006/pin 5 5Vp-p

Time base 200msec/div.

Power ON

IC201

The power ON operation works much like a modern day computer. When

the power ON command is received, Interface IC201 begins a boot up

sequence using IC202 and IC205 to finish it. IC201 causes:

· The red standby light to turn to green;

· PCONT (at IC201/pin 24) to go high, powering the set; and

· Communications with System Control IC202, continuing the power

ON operation

IC202

IC202 continues the power ON operation, retrieving start up information

from the Flash ROM IC205. This start up information instructs IC202 to

check each IC on the parallel bus and wait for an acknowledgement signal. At power ON, these ICs are polled in the order shown in the table:

19

Power ON IC check sequence (not shown in the diagram)

Chip Select Source Destination IC

1. CS 1 - IC202/pin 10 SRAM IC204 / HGA IC601

2. CE – IC202/pin 11 Flash ROM IC205

3. CS 3 – IC202/pin 8 AV Decoder IC401

4. CS 4 – IC202/pin 7 HGA IC601

5. CS 2 – IC202/pin 9 AV Decoder IC401

6. XCS – IC601/pin 111 ARP2 IC303

7. HCS - IC601/pin 118 Servo IC701

When all the replies have been received, Interface IC201 is informed and

IC201 keeps the unit powered ON (PCONT remains high). At the same

time, IC201 turns on the front panel blue Dolby Digital LED.

If a communications failure occurs and there is no acknowledgement signal to IC202 within three seconds of power ON, the unit will turn off. The

PCONT signal (from IC201/pin 24) will go low and the player power is

removed. The green power ON light changes back to red (standby mode).

Post Power ON Check

Therefore, if the blue Dolby Digital LED lights, communications have taken

place and the unit remains ON. The next step is to determine if there is a

disc present. The disc check sequence is:

1. Tray up and chucked – chuck switch feedback

2. Sled moves to home position – photosensor feedback

3. Sled moves outward – no feedback (stepping motor)

4. Laser is turned ON momentarily while focus searching

5. Focus Search is performed – FE and PI feedback signal

6. Sled moves outward further – no feedback

7. Laser is turned ON and Search is performed again

8. Sled moves outward further – no feedback

9. Laser is turned ON and Search is performed a third time

10. Sled moves inward to home – photosensor feedback

11. Laser is turned ON and Search is performed a fourth time

12. Spindle motor rotates – FG amp kick drive feedback

13. Display reads NO DISC.

If an IC fails to receive the correct feedback from its sensors, System

Control will instruct IC201 to enter standby (red front panel light).

Page 25

EVER 5V

IC051

IR

RECEIVER

3

EVER 5V

FR150

5

CN201/

CN002

R274

2

1

GRN

R072

R071

RED

S071

POWER

12

4

6

7

EVER

5V

3

12

P CONT.

16

9

31

32

R221

R222

FRONT PANEL

BUTTONS

S212-S218

SRV902UC PWR BLK

IC202

RESET

PST9140

5

4

C211

18

IC201

INTERFACE

CONTROL

M38857

MCHE206FP

2415145

X201

4MHz

3

SBUSY1

3.3V

D203

DOLBY

DIGITAL

R285

30

SIN

SCLK

S OUT

SRDY1

DISPLAY

FL101 BD.

5V

CN202

CN001/

72

70

76

71

78

CN202/

CN006

5

6

3

4

2

6

2

5

3

6

11

R044

R036

5V

14

IC203

BUFFER

SN74

HCT08

R037

3.3V

5V

1

4

12

R045

PARALLEL

BUS

22

3.3V

40

20

77

78

97

76

1

SO01

SC0

CSOL

SI0

XIF

INT

MB85 BD.

IC202

SYSTEM

CONTROL

MB91101

PFV

CS4

CS4

4

43

69

70

93

11

CS1

107

141142

CS1

IC601

HGA

CXD8788Q

3.3V

CE

26

IC205

FLASH

ROM

MBM29

LV160

PARALLEL

BUS

4737

POWER CONTROL

20

6 22 9913DVD02 1154

Page 26

21

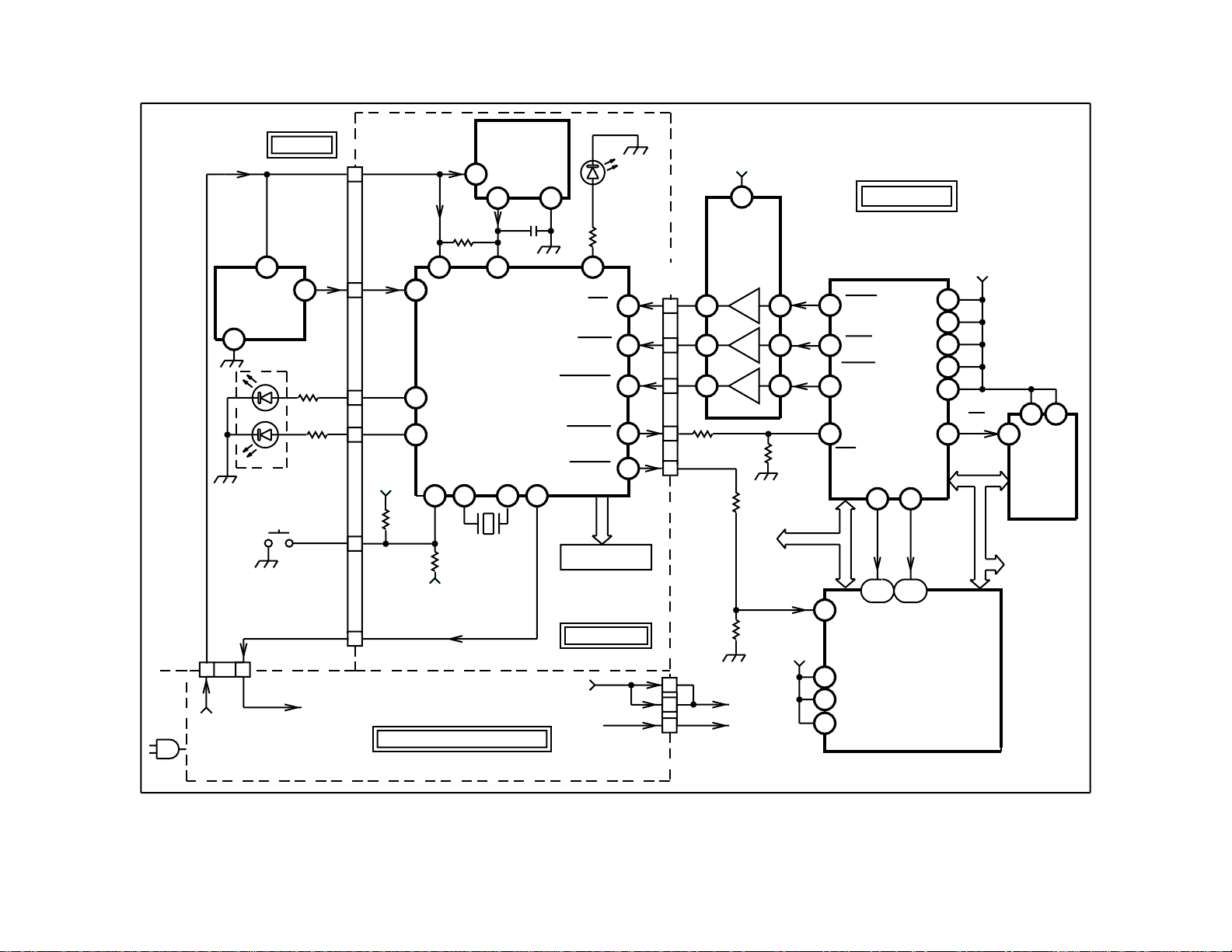

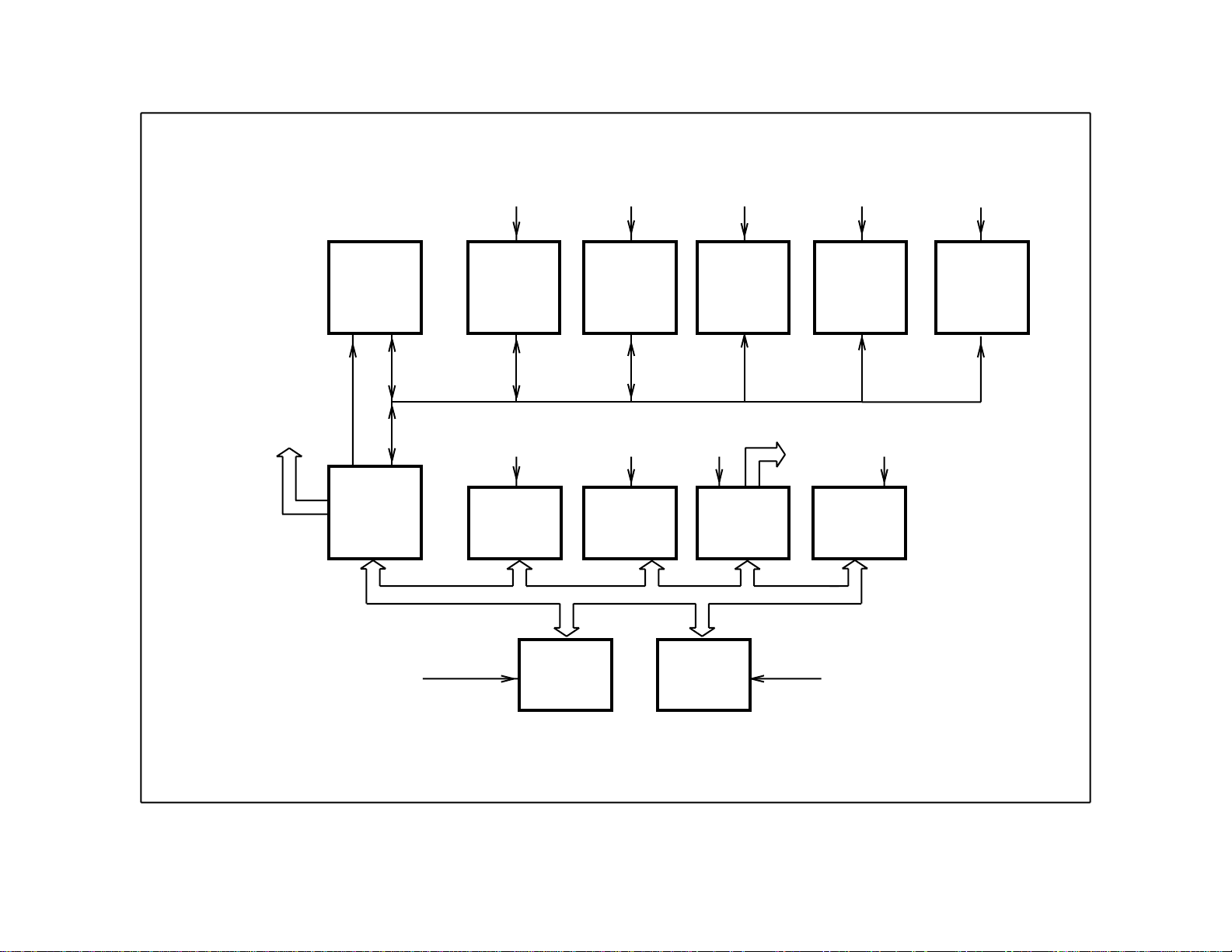

Communications Block

Both serial and parallel bus structures are used in the same unit of today’s

DVD players. The serial data bus is a simple way to provide communications between ICs. On one line, data is transmitted one bit after another

to the next IC in 8, 16, 20, 24 or 32 bit groups. On another line, corresponding clock pulses accompany the bits of data. One clock pulse identifies each bit of data - this is why this line is also called a bit clock. Therefore, it takes 8, 16, 20, 24 or 32 clock pulses to receive a group of data in

a serial bus.

A parallel data bus is used when large amounts of data need to be transmitted in a shorter time frame. In the parallel bus, multiple data lines are

used along with a clock line. When a single clock pulse is sent, the 8, 16,

20, 24 or 32 lines each simultaneously transmit a bit of data to the receiving IC. (Only 16 data lines are used here.) Therefore, it takes only one

clock pulse to receive a group of data in a parallel bus.

The parallel bus is used in processing video information (IC401) and in

the disc playback servo (IC701) where large amounts of data must be

handled quickly.

Serial Data

Parallel Data

The parallel data bus is much more complicated than the serial bus. It

consists of address lines, data lines and a clock line. Just before data is

transmitted from one IC to another, a location is designated using address lines. Then clock pulses are sent from the master IC202 to transfer

the data into the receiving IC.

When communications are bi-directional on the parallel bus, an additional

line identified as write enable (WE) and/or read enable (RE) is used. These

lines determine the direction of the data to or from the master IC. When

there is no WE or RE line, the bi-directional data communication is preestablished first as read-data from the master micro. Write-data occurs

afterwards.

The serial data bus connects several ICs and consists of two or three

lines. Serial data is transmitted from one IC to another on a unidirectional

line (arrows shown in one direction). This data is accompanied by a clock

signal for a total of two lines in a unidirectional serial communication.

The interface control IC201 and System Control IC202 communicate

bidirectionally (arrows shown in two directions). Three lines are necessary when bi-directional transmissions are called. There is a data line for

each direction. The additional clock signal makes a total of three lines for

a bi-directional serial bus. The clock signal usually comes from the controlling micro, which in this case is System Control IC202.

System Control IC202 communications with Interface IC201, EEProm

IC201 and DSP IC501 are bi-directional. System Control communications to the Digital to Analog Converters (DAC) IC902, IC905-7 are unidirectional.

Page 27

CS FROM

IC601

CS FROM

IC202 IC202

CS FROM

IC202

CS FROM

CS FROM

IC601

CHIP

SELECTS

IC201

INTERFACE

CONTROL

CS

IC202

SYSTEM

CONTROL

CS FROM

IC202

SERIAL BUS

IC201

4k

EEPROM

CS FROM

IC202

IC205

FLASH

IC501

AUDIO

DSP

CS FROM

IC202

PARALLEL BUS

IC401

AV

DECODE

IC204

SRAM

CS FROM

IC202

IC303

ARP2

IC902

AUDIO

2 CH

DAC

IC601

HGA

CHIP

SELECTS

CS FROM

IC601

IC905

DAC

FRONT

CS FROM

IC601

IC701

SERVO

IC906-7

DAC

REAR,

CENTER

COMMUNICATIONS BLOCK

22

6 23 996DVD02 1149

Page 28

23

Serial Data Communications

A close examination of the serial bus structure shows there are two serial

buses. Both are active as long as the set is ON.

Serial Bus 0

Serial Bus 1

Serial Bus 0

Bus 0 is used for bi-directional communications between:

· System Control IC202

· Interface IC201

· EEProm IC201

System Control IC202 is the master IC. It sends and receives data on the

serial data in (SI0, at IC202/pin 76) and out (SO0, at IC202/pin 77) lines.

The data is always accompanied by serial clock (SC0, at IC202/pin 78)

from IC202. There are always communications between these two ICs

as long as there is power applied.

Interface IC201

System Control IC202 has the continuous task of transferring display information to the Interface IC201. The Interface IC201 must inform System Control IC202 that there is a new command such as play or stop.

Communications begin when Interface IC201/pin 78 outputs a low going

“ready” pulse. In this IC the ready command is more like an interrupt

command. This low going pulse is received by IC601/pin 22, which is

used as an expansion port to access System Control IC201 via the parallel bus. The interrupt input is periodically checked within IC202’s program.

When found, IC202 will enter a subroutine and acknowledge IC201’s request to send data for processing.

IC202/pins 76 and 77 to occur. The entire operation is similar to someone working when interrupted by a doorbell. When he is ready, he will

answer the door. Afterwards he returns to his work in the house or elsewhere. The IC201 to IC202 communications sequence is:

System Control IC202 and Interface IC201 Data Transfer Sequence

Name of Signal Signal Source Signal purpose

1. SRDY (ready) IC201pin 78 Request communications

2. CSOL (chip

select)

3. SC0 (clock) IC202/pin 78 Serial clock for data

4. SI0 (data) IC201/pin 71 User commands

5. SO0 (data) IC202/pin 77 Display update

6. CSOL (chip

select)

IC202/pin 97 Communications window (active

low)

IC202/pin 97

Communications ends (returns

high)

EEProm IC201

During playback or when playback is started, System Control IC202 retrieves information held in EEProm IC201. IC201 holds servo data and

stores some disc parameters, such as how many information layers are on

the disc. Some of this data is visible in the test mode.

Bi-directional communications between System Control IC202 and EEProm

IC201 is accomplished using:

· Two single direction serial data lines (SO0 and SI0)

· Clock pulses from IC202/pin 78

· Chip Select signal from IC601/pin 23

Periodically in IC202’s routine, EEProm IC201is chip selected (when pin 3

is brought low). When this occurs, data is transferred between the ICs on

the data lines (SO0 and SI0).

System Control IC202 acknowledges the interrupt signal by outputting

two signals: a low chip select signal from pin 97 and a clock signal from

pin 78. This allows for data communications on the SI0 and SO0 lines at

Page 29

FL101 BD. MB85 BD.

DISPLAY

CN202/

CN006

SC1

7678

72

71

70

5

4

6

3

2

SIN 1

S OUT 1

IC201

INTERFACE

CONTROL

M38857MCH

S BUSY

SRDY

SO0

SI0

SC0

XFMCS

XIF BUSY

IC201

4k

EEPROM

AK6440AF

SO0SI0

IC202

SYSTEM CONTROL

MB91101PFV

CSOL

97

3

CS

SI0SO0SC0

SC0

CSO

262761

141

142

XIFINT

28

IC905

FRONT

L/R DAC

CXD8799N

SC1

IC601

HGA

CXD8788Q

XDACS3

XDACS2

OICS

XECS

22

97

96

28

23

CS2

SO1

28

2627

IC906

SC1

27

26

27

26

REAR

L/R DAC

CXD8799N

SO1

IC907

SC1

CENTER

WOOFER DAC

CXD8799N

SO1

CS2

CS3

28

28

62

IC501

AUDIO

DSP

CDX1901R

SC1

654

66

79

SI1

CS

SI1

63

SERIAL BUS 1

89

80787776

SC1

SO1

PB3

PB2

10

7

99

98

IC902

AUDIO

2 CH DAC

CXD8799N

SC1 SO1SO1

CS1

CS4

PARALLEL

BUS

SERIAL DATA COMMUNICATIONS

24

6 23 994DVD02.DWG 1144

Page 30

25

Serial Bus 1

Bus 1 is used for communications between:

· System Control IC202

· Audio DSP IC501

· Audio 2 channel IC902

· Front, Rear, and Center D/A converters IC905 to IC907

System Control IC202 is the master IC. It sends and receives data on the

serial data in (SI1, at IC202/pin 79) and out (SO1, at IC202/pin 80) lines.

The data is always accompanied by serial clock (SC1, at IC202/pin 89)

from IC202. There are always communications present at IC202/pins

79,80 and 89 as long as there is power applied just like in serial bus 0.

Audio DSP IC501

Bi-directional communications between System Control IC202 and IC501

is similar to that with EEProm IC201. Communications between System

Control IC202 and Audio DSP IC501 are accomplished using:

· Two serial data lines (SO1 and SI1)

· Clock from IC202/pin 89

· Chip Select from IC601/pin 28

Periodically in IC202’s routine, Audio DSP IC501 is chip selected. When

the chip select pin 62 line is brought low, data is transferred between the

ICs on the data lines (SO1 and SI1).

IC Function

IC Name Number Function

System Control IC202 Main Micro

Interface IC201-FL101

Bd

EEProm IC201-MB85 Bd Stores serv o info

Audio DSP IC501

Audio 2 channel D/A

Converter

Front, Rear, Center,

D/A Converter

IC902 D/A Converter for analog

IC905 - IC907 D/A Converter for 5.1 AC-3

Accepts user commands

(play, open tray, next, etc)

Delays (echoes) for speaker

effects

audio

signal.

Audio 2 Channel D/A Converter IC902

Audio Front, Rear, and Center D/A Converters IC905 - IC907

System Control IC202 communicates with the remainder of the ICs on

the serial bus 1 lines in a unidirectional manner. Each one of these D/A

Converters has an individual chip select line from IC601. The SO1 data

line from IC202/pin 80 is common to the D/A Converters. Data applies

only to the D/A Converter when its chip line is low. The data as always is

accompanied by bit clock from IC202/pin 89.

Page 31

FL101 BD. MB85 BD.

DISPLAY

CN202/

CN006

SC1

7678

72

71

70

5

4

6

3

2

SIN 1

S OUT 1

IC201

INTERFACE

CONTROL

M38857MCH

S BUSY

SRDY

SO0

SI0

SC0

XFMCS

XIF BUSY

IC201

4k

EEPROM

AK6440AF

SO0SI0

IC202

SYSTEM CONTROL

MB91101PFV

CSOL

97

3

CS

SI0SO0SC0

SC0

CSO

262761

141

142

XIFINT

28

IC905

FRONT

L/R DAC

CXD8799N

SC1

IC601

HGA

CXD8788Q

XDACS3

XDACS2

OICS

XECS

22

97

96

28

23

CS2

SO1

28

2627

IC906

SC1

27

26

27

26

REAR

L/R DAC

CXD8799N

SO1

IC907

SC1

CENTER

WOOFER DAC

CXD8799N

SO1

CS2

CS3

28

28

62

IC501

AUDIO

DSP

CDX1901R

SC1

654

66

79

SI1

CS

SI1

63

SERIAL BUS 1

89

80787776

SC1

SO1

PB3

PB2

10

7

99

98

IC902

AUDIO

2 CH DAC

CXD8799N

SC1 SO1SO1

CS1

CS4

PARALLEL

BUS

SERIAL DATA COMMUNICATIONS

26

6 23 994DVD02.DWG 1144

Page 32

27

Parallel Data Communications

There are six ICs that communicate with System Control IC202 on the

parallel bus:

ICs on the Parallel Bus

Name Number Purpose

1. Flash ROM IC205 Start up program instructions

2. Hybrid Gate

Array

3. SRAM IC204 IC202’s local memory

4. AV Decoder IC401

5. ARP2 IC303 CD/DVD data processing & separation

6. Servo DSP IC701 Analog servo control

Bi-directional communications between these ICs are accomplished using the following lines; however, not all ICs use the last three lines:

· Chip Select from IC202

· Address from IC202

· Data (bi-directional)

· Clock from IC202

· Interrupt from destination IC

· Read/Write from IC202

Chip Select Line

System Control IC202 systematically polls each IC on the communications bus with a chip select signal. This low or high going pulse identifies

the individual destination IC that System Control wants to communicate

with. The chip select output sequence is listed below:

IC601 Expansion port for System Control

IC202

Audio (AC-3) and Video (MPEG 2)

decoder

Chip Select Signals from IC202 (active low)

CS Source Destinatio n

Pulse

Width/Polarity

1. CS 1 - IC202/pin 10 SRAM IC204 /

HGA IC601

0.56us /–

0.9usec/-

2. CE – IC202/pin 11 Flash ROM IC205 0.56us /–

3. CS 2 – IC202/pin 9 AV Decoder IC401

0.7 & .26

usec/-

4. CS 4 – IC202/pin 7 HGA IC601 0.3usec/-

5. CS 3 – IC202/pin 8 AV Decoder IC401 1.2usec/-

6. XCS – IC601/pin 111 ARP2 IC303 0.3usec/-

7. HCS - IC601/pin 118 Servo IC701 0.3usec/-

Chip Select Waveforms

The following waveforms show the chip select signals going to the S RAM

IC204 (ch 1) and AV Decoder IC401 (ch 2 and 3). They can be compared

to the D1 data (ch 4) to show that the chip select (ch 1-3) signals occupy

more than one bit clock interval. Note that on each of the CS 1 (ch 1) and

CS 2 (ch 2) lines, two different pulse widths are used. These waveforms

were taken with the unit on without a disc being played.

ch1

ch2

ch3

ch4

Chip Select signals from IC202 (active low)

Channel 1 CS = CS1 IC202/pin 10 5Vp-p

Channel 2 CS = CS2 IC202/pin 9 5Vp-p

Channel 3 CS = CS3 IC202/pin 8 5Vp-p

Channel 4 Data = D1 IC202/pin 26 2Vp-p

Time base 5usec/div.

PM3394, FLUKE & PHILIPS

1

T

2

3

CH1!5.00 V=

CH2!5.00 V=

CH3!5.00 V=

4

CH4!2.00 V= ALT MTB5.00us- 1.34dv ch2-

Name Location Voltage/div

Page 33

INTERRUPT

196

198

WAIT/INTERRUPT

IC601/72

95

IC202

SYSTEM

CONTROL

MB91101PFV

SI

SO

SC

SERIAL BUS

TO IC201

IC501

IC902

IC905-7

107

26

1198

CECS2CS3

CS1CS4

6

XCS1

IC202

IC205

16M FLASH

MBM29LV160B

CE

AO-21

DO-15

IC204

1M SRAM

IDT71VD16S20

CS

INTERRUPTS

INTERRUPTS

IC601/PIN

PIN 157PIN 19

PIN 155PIN 88

PIN 156PIN 97

XCS3

99

SDCS

XCS2

98

A1-20

DO-15

ADDRESS & DATA PARALLEL BUS

A1-16

DO-15

IC601

HGA

CXD8788Q

CS1

141

142

CS4

OON

IC401

AV DECODER

CXD1930Q

SDCS1ON

120

AO-21

DO-15

AO-5

A17-19

D8-15

118

115

107

111

IC402

16M SRAM

KM416S1020

121

3

ARP INTERRUPT

18

CS

18

IC403

16M SRAM

KM416S1020

A0-1

DO-7

HCS

IC701

SERVO DSP

CXDP791Q

128

INTERRUPT

CS

ADDRESS, WE, CAS,

RAS, DATA

AO-7

D8-15

83

84

XCS

OE

XOE

IC304 16M DRAM

KM416V1200

WE

17

DATA

148

XMWR

MB85 BD.

ADDRESS

IC303

ARP2

CXD8784R

RAS

35341833

150151152

CAS

PARALLEL DATA COMMUNICATION

28

6 29 995DVD02 1146

Page 34

29

Address Lines

Direct Addressing

The parallel bus in this unit contains multiple address lines to designate

the destination of the data within the IC that is chip selected. These address lines are labeled A0-21 from master IC202. Address lines are shared

by some destination ICs and none use all 22 address lines.

Column and Row Addressing

IC401 and IC303 control three memory ICs. A memory IC has more data

locations than can be accessed by one set of address lines directly. CAS

and RAS lines are used to expand that number. Memory locations can be

addressed like cells in a multiplication table. For example, when CAS is

active, the address lines identify a column of memory locations. Then

when RAS is active, the address lines now pin point the memory cell by

identifying the row it is in.

Data and Clock Lines

Serial data communications involve the fewest number of connections

between ICs. When speed is important, the parallel data structure is

used. Instead of having a single data line between the communicating

ICs, there are 8 or 16 lines that carry data. As in the serial bus structure,

on a separate line the parallel bus uses a bit clock signal. When a single

bit clock pulse occurs, the entire group of 8 or 16 bits of data is transferred

at once. Therefore, the data transfer rate of the parallel bus system is

much faster than the serial bus.

Interrupt Lines

Interrupt signals are used when the destination IC has carried out the

instruction given to it and wants to reply with resultant data (such as task

completed or information such as AC-3 detected). A destination IC can

not generate a clock or chip select lines to send data to the master IC202.

The destination IC must send an interrupt signal to the master IC202

requesting attention. When the master IC202 is ready, it will send chip

select and clock signals, allowing the destination IC to send data.

Read / Write Lines

Bi-directional communications on the parallel bus may use a single write

enable (WE) / read enable (RE) line from the master IC202. During the

chip select interval, this line determines the direction of the data to or from

the master IC202. A high is one data direction while a low is the other. In

some systems, two individual read and write lines are used.

When there are no interrupt, WE or RE lines, communications are preestablished to share the time to read and write during the chip select

interval.

Communications from IC202 to Other ICs

IC202 can only send data to another IC after it chip selects the IC and

supplies internal address and bit clock to carry the data. Consequently, a

list of communications from IC202 would consist of the following:

· Chip Select (usually active low)

· Write control line (usually active low)

· Address data (Identifies the registers/memory location in the destina-

tion IC to put the data)

· Bit clock

· Data

Communications from Another IC to IC202

If another IC has finished a task and wants to reply with sensor information, it must request the service (signals) above to return data. Once the

destination IC sends an interrupt pulse, IC202 will reply with all the signals listed above so the other IC can send data to IC202.

The Read control line (from IC202) is active instead of the write line in the

date reply to IC202. All or some of the address locations are checked by

IC202. The number is dependent upon the firmware built into Syscon

IC202. For example, IC202 may request the Servo IC701 perform a sled

movement to home task. Later IC202 receives an interrupt from IC701.

Instead of checking all of IC701’s address locations, it will just access the

one that contains the sled at home data.

Page 35

INTERRUPT

196

198

WAIT/INTERRUPT

IC601/72

95

IC202

SYSTEM

CONTROL

MB91101PFV

SI

SO

SC

SERIAL BUS

TO IC201

IC501

IC902

IC905-7

107

26

1198

CECS2CS3

CS1CS4

6

XCS1

IC202

IC205

16M FLASH

MBM29LV160B

CE

AO-21

DO-15

IC204

1M SRAM

IDT71VD16S20

CS

INTERRUPTS

INTERRUPTS

IC601/PIN

PIN 157PIN 19

PIN 155PIN 88

PIN 156PIN 97

XCS3

99

SDCS

XCS2

98

A1-20

DO-15

ADDRESS & DATA PARALLEL BUS

A1-16

DO-15

IC601

HGA

CXD8788Q

CS1

141

142

CS4

OON

IC401

AV DECODER

CXD1930Q

SDCS1ON

120

AO-21

DO-15

AO-5

A17-19

D8-15

118

115

107

111

IC402

16M SRAM

KM416S1020

121

3

ARP INTERRUPT

18

CS

18

IC403

16M SRAM

KM416S1020

A0-1

DO-7

HCS

IC701

SERVO DSP

CXDP791Q

128

INTERRUPT

CS

ADDRESS, WE, CAS,

RAS, DATA

AO-7

D8-15

83

84

XCS

OE

XOE

IC304 16M DRAM

KM416V1200

WE

17

DATA

148

XMWR

MB85 BD.

ADDRESS

IC303

ARP2

CXD8784R

RAS

35341833

150151152

CAS

PARALLEL DATA COMMUNICATION

30

6 29 995DVD02 1146

Page 36

Mechanism

Disc Tray and Laser Platform Position

Tray Movement

The loading motor moves the disc tray in or out. Without the tray, the

loading motor’s shaft is seen on the right side.

31

Pawl

Channel

Teeth

Tray

Bottom

Loading Motor

Top View

The rotation of the motor turns the three gears to its left. The final gear at

the far-left mates with the teeth on the tray. Motor direction determines

tray movement. Electrical feedback to stop the motor is an opened/closed

electrical switch under the white activator arm. The tray at the end position pushes the arm.

Platform Position

When the loading motor drives the tray inward, a channel in the tray moves

a spring-loaded pawl into the middle rotating gear. The gear’s rotation

continues to slide this pawl to the left. The front part of this pawl that

faces the laser assembly platform lifts a pin connected to the platform. As

the pawl slides left, the platform is lifted up. The pawl in the tray’s channel

prevents the tray from sliding out.

No Power Tray Removal – From the Bottom

A spring-loaded pawl under the tray locks the tray closed. The bottom

part of this pawl can be accessed from under the mechanism assembly.

Tab underneath

Mechanism

Bottom T ab

1. Unplug AC power and press the power button to discharge the power

supply capacitors.

2. At the mechanism top, remove the two screws and the mechanism’s

top cover. The cover acts as a tray stop. Cover removal allows the

tray to be pulled out later.

3. At the rear of the mechanism remove the rear black screw for finger

clearance.

4. Place your finger under the mechanism. Push the slider’s bottom tab.

5. At the bottom of the assembly, slide the tab toward the center of the

mechanism. This lowers the laser (unchucks), freeing the tray.

6. From the top of the mechanism, slide the tray out

Page 37

No Power Tray Removal – From the Top

1. Remove the two screws and the mechanism’s top cover to expose

the tray and laser platform.

2. Locate the top pawl under the tray by inserting a small screwdriver

between the platform and tray. The pawl is just in front of the spindle

motor.

3. Slide the pawl to the right to lower the platform and free the tray.

4. Remove the tray.

Tilt Motor

Purpose

Incline Gear

The stepping motor then increments the incline gear to the middle position. This position is stored in EEProm IC201 and updated during the test

mode automatic adjustments. During DVD playback, if the RF level fluctuates, the tilt motor rotates until the RF level stabilizes. The incline gear

remains at the middle position during CD playback.

Sled Position

The sled motor moves the laser assembly away from home position at

the spindle motor. The laser assembly‘s home position is marked as it

blocks the light to a photo detector sensor. This picture shows the photosensor location under the sled motor shaft.

Maximum RF output level occurs when the laser beam is perpendicular to

the disc’s information layer. The tilt motor raises one end of the laser

platform so its beam is perpendicular to the disc.

Access and Operation

The tilt motor is a stepping motor located next to the incline gear. At

power OFF, the incline gear lowers one end of the laser platform. At

power ON, the incline gear raises the platform to full height.

Sled Sensor

32

Page 38

33

Focus Coil

Voltage applied to the focus coil that is connected to the lens opposes a

stationary vertical magnet. The force generated moves the objective lens

up or down to focus the laser spot on the information layer of the disc.

F Coil

LensMagnet

Protection Spot

Laser

A ribbon cable connects the laser assembly to its circuit board. A circuit

board connector clamps the assembly’s ribbon cable. Free the cable

from the connector by pulling the connector tabs on both sides 1mm toward the cable. The connector will slide out..

In this picture the left side of the cable is free from the connector.

Left connector

unlocked

In a replacement laser assembly, a spot of solder is placed on the foils of

the ribbon cable (see the focus coil picture) to protect the laser diode from

static damage that will shorten its life. Remove the solder spot AFTER

connecting the laser assembly cable to the circuit board.

Ribbon Cable

Page 39

Power ON Mechanical Sequence – No Disc

,

q

y

,

Operation Purpose

1. Power On button is pressed. IC202 retrieves start up program from Flash ROM IC205. After the

ICs are checked for basic communications

IC701 to start the mechanical se

stored in EEProm IC201.

uence. The servo parameters are

IC202 instructs Servo

2. Disc tray is closed (if open) and placed into a

chucked position.

3. Sled moves the optical assembly to home position. Sled starting point.

4. Tilt Motor resets laser platform to mid position. Presets the laser beam perpendicular to the disc for max RF.

5. Sled moves outward quickly, then slows down. Optical assembly is moving under the disc’s information area.

6. Laser is turned ON momentarily during focus

search.

7. Focus search one time.

8. Sled increases speed moving further outward. Sled slows down in a second attempt to locate a disc.

9. Sled slows down

10. Laser is turned ON momentarily during focus

search.

11. Focus search. Looks for the disc’s information laye.

12. Sled again moves quickly outward then slows

followed by laser and focus search.

13. Sled moves inward to home and stops. Disc check at home position.

14. Laser is turned ON momentarily. Final attempt to identify a disc.

15. Focus search.

Clamps a disc on the spindle motor platform.

Looks for a disc. Reflected light identifies a disc.

Optical assembl

information layer.

Looks for a disc using reflected light.

Third attempt to locate a disc.

lens moves up then down, looking for the disc’s

16. Spindle motor rotates. (laser is off)

17. Display reads NO DISC User feedback

34

Page 40

35

,

q

Power ON Mechanical Sequence – DVD Disc

Operation Purpose

1. Power On button is pressed. IC202 r etr ieves start up program from Flash ROM IC205. After t he

ICs are checked for basic communications

IC701 to start the mechanical se

stored in EEProm IC201.

uence. The servo parameters are

IC202 instructs Servo

2. Disc tray is closed (if open) and placed into a

chucked position.

3. Sled moves the optical assembly to home position. Sled starting point.

4. Tilt Motor resets laser platform to mid position. Presets the laser beam perpendicular to the disc for max RF.

5. Sled moves outward quickly then slows down. Optical assembly is moving under the disc’s information area.

6. Laser is turned ON momentarily during focus search. Looks for a disc. Reflected light identifies a disc.

7. Focus search one time. Optical assembly lens moves up then down, counting the number of

8. Sled stops moving when a disc Is identified.

9. Spindle motor rotates. Rotates the disc.

10. Laser is turned ON a second time. To begin playback.

11. Focus search. Focuses on the first information layer on the disc.

12. Focus servo is turned ON. Maintains focus on the layer.

13. Tracking begins. Keeps the laser beam at the information track’s center.

14. Tilt motor servo starts. Maintains high RF level.

15. Disc PB begins. Display shows elapsed time. Playback verification.

Clamps a disc on the spindle motor platform.

disc layers.

Page 41

NOTES

36

Page 42

37

Tray Motor Drive

The opening and closing of the disc tray involves two micro controllers,

one gate array IC and a driver IC that powers the loading motor. The

loading motor is powered by pressing the front panel open/close tray button S212. The following occurs when the tray button is pressed:

1. Interface Controller IC201 recognizes the tray button

2. IC201 turns on the display to show the command entered

3. IC201 communicates with System Control IC202

4. IC202 instructs Hybrid gate array IC601 to issue a drive command

5. Driver IC802 translates the command into loading motor current

6. The tray position switch returns information to IC201 (via IC601)

The tray position switch information is sent to Interface IC201 via IC202 to

complete the tray open cycle. The “OPEN” display disappears when the

cycle is complete. This also sets the latch, permitting the tray to be closed

the next time the tray button is pressed.

Interface Controller IC201 Recognizes the Tray Button

Pressing the tray button S212 reduces the voltage at IC201/pin 5 from

+5V to +0.65V.

IC201 Turns On the Display

Once the command is recognized by Interface Control IC201, the ND201

fluorescent display digits and segments lines are multiplexed with a LOW

to illuminate the word OPEN.

IC201 Communicates with System Control IC202

2. IC601 sends this information along the parallel bus to IC202. This

occurs when IC601/pin 142 is periodically (chip) selected using CS1