Page 1

FEATURES

• SMBus, version 1.0, compliant

• Intel PAS Protected Storage support

• Support Pentium and x86-based designs

• Support SMBus Q-Buffering via PWRGD

• Support SMBus selector for dual/triple DIMMs

• 32KHZ input clock or Crystal input

• Support 2 different power planes

• 10 bytes scratch pad registers

• 20 possible edge-sensitive programmable GPIOs

per device

• 8 possible Open Drain, Open Collector outputs

• Programmable addresses for cascaded OZ998s

• Supports 3.3V or 5V operation

• Supports 5V tolerant LVTTL inputs (OZ998B)

• LOW power hardware-driven speaker alarm

outputs

• SMBALERT# and SMI event outputs

• 8 programmable interrupt inputs for SMI event or

SMBALERT#

• 8 Auto LED Flash (ALF) programmable outputs

with 10% or 50% duty cycles

ORDERING INFORMATION

OZ998S - 28 pin SSOP

OZ998

Intelligent Manager

Smart Multi-DIMM Selector

GENERAL DESCRIPTION

Micro’s OZ998 Multi-DIMM Selector supports the

O

2

switching between a primary SMBus and 3 other

secondary SMBus. This function is particularly useful

for DIMM devices and the support of Intel’s PAS

(Preboot Authentication Service).

In addition, the OZ998 can be configured to support

two different power planes with different sets of

General Purpose Input/Output (GPIO) signals, which

supplements and enhances the power management

capability of the chipsets, commonly found in an ACPI

(Advanced Configuration of Power Interface)

subsystem.

Up to 20 possible GPIOs are available per device,

and among those, GPIO[15:8] are programmable to

be either positive or negative-edged triggers to

generate an SMIEVENT/SMBALERT# to the system.

GPIO[7:0] are programmable to be either a regular

TTL level output, open drain or open collector output.

To support over 20 GPIOs through cascading multiple

OZ998 devices, configure each individual OZ998

device ID. Up to 8 Auto LED Flash (ALF) are available

to drive an LED or speaker at a programmable

frequency.

The OZ998 is packaged in a low profile, small 28 pin

SSOP.

07/13/00 OZ998-SF-2.2 Page 1

©Copyright 2000 by O2Micro All Rights Reserved

Page 2

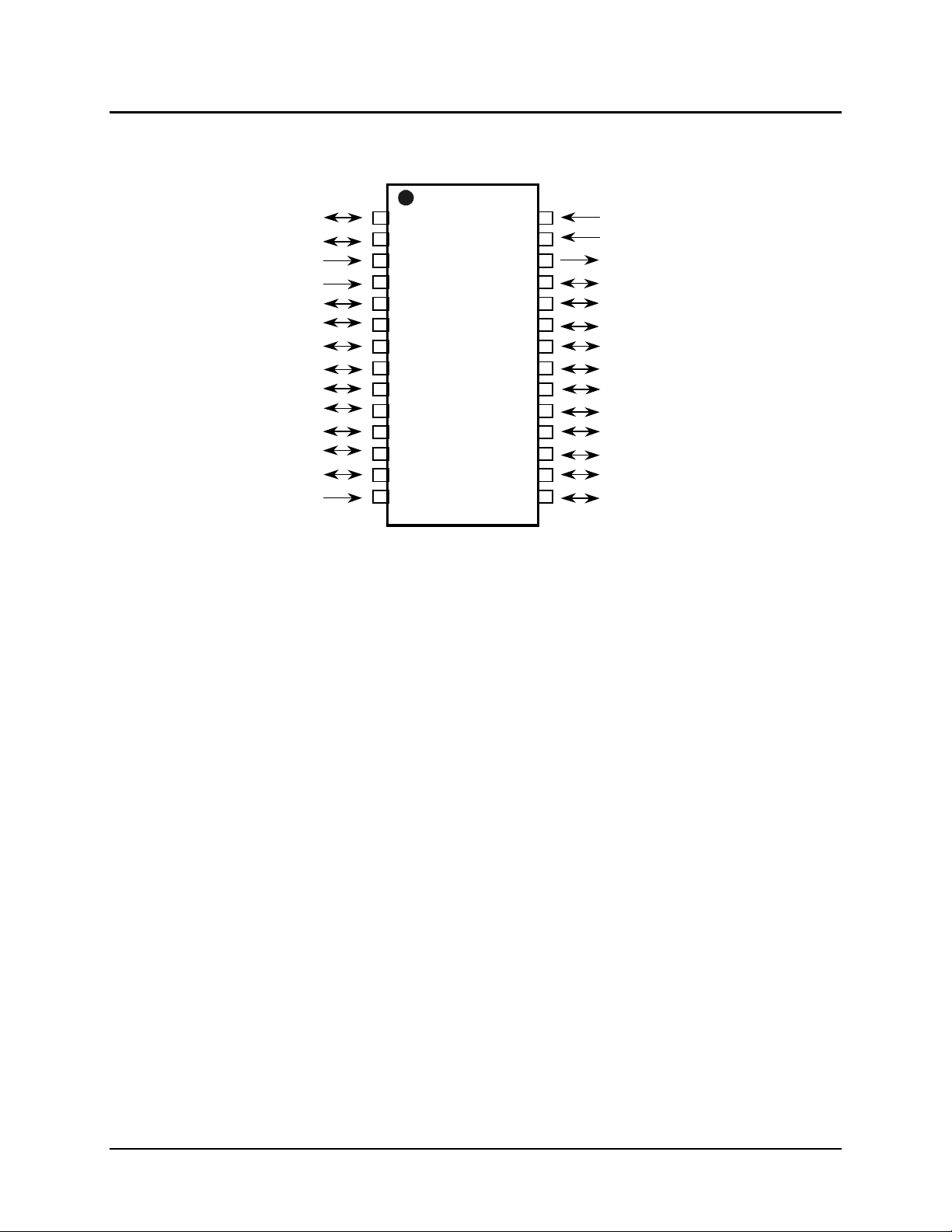

PIN DIAGRAM

OZ998

OZ998

P_SMBCLK

P_SMBDATA

PWRGD

RESET#

GPIO[16]/S_SMBCLK1

GPIO[17]/S_SMBDATA1

GPIO[18]/S_SMBCLK2

GPIO[19]/S_SMBDATA2

GPIO[0]/SMIEVENT/ID[0]

GPIO[1]/ID[1]

GPIO[2]/SMBALERT#/ID[2]

GPIO[3]/ID[3]

GPIO[4]/ID[4]

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VCC

XIN/32KHZ

XOUT

GPIO[15]/S_SMBCLK3

GPIO[14]/S_SMBDATA3

GPIO[13]/SMB_SEL[1]

GPIO[12]/SMB_SEL[0]

GPIO[11]

GPIO[10]

GPIO[9]

GPIO[8]

GPIO[7]/ID[7]

GPIO[6]/ID[6]

GPIO[5]/ID[5]

OZ998-SF-2.2 Page 2

Page 3

PIN DESCRIPTION

Name Pin

P_SMBCLK

Primary SMBus Clock Input for SMBus protocol communicati on.

P_SMBDATA

Primary SMBus Data Input /Output for SMBus protocol communicati on.

PWRGD

RESET#

GPIO[16]/

S_SMBCLK1

GPIO[17]/

S_SMBDATA1

GPIO[18]/

S_SMBCLK2

GPIO[19]/

S_SMBDATA2

GPIO[0]/

SMIEVENT/ID[0]

GPIO[1]/ID[1]

GPIO[2]/

SMBALERT#/ID[2]

No.

1 I 3.3V/5V Ext-PU 2 I/O 3.3V/5V Ext-PU 12mA

3 I TTL -

This pin indicates that the host system’s power, including the Core Logic chipsets, is stable. Before the

host system’s power is stable, this input pin will tri-state the output pins, GPO[19:8], from OZ998 while

GPO[7:0] will maintain its original value. Upon PWRGD going Low, the Secondary SMBus will be

disconnected from the Primary SMBus.

4 I TTL -

This active low pin will reset the OZ998.

5 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[16] is

defaulted as an input. It is programmable to function as GPI[16] input, GPO[16] output or secondary

SMBus-1 Clock Input/Output. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO

Config. Tables (section 8) for input/output selections.

6 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[17] is

defaulted as an input. It is programmable to function as GPI[17] input, GPO[17] output or secondary

SMBus-1 Data Input/Output. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO Config.

Tables (section 8) for input/output selections.

7 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[18] is

defaulted as an input. It is programmable to function as GPI[18] input, GPO[18] output or secondary

SMBus-2 Clock Input/Output. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO

Config. Tables (section 8) for input/output selecti ons. Note: OZ998A GPIO [19:18] need 47k

normal operation, OZ998B doesn’t.

8 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[19] is

defaulted as an input. It is programmable to function as GPI[19] input, GPO[19] output or secondary

SMBus-2 Data Input/Output. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO Config.

Tables (section 8) for input/output selections. Note: OZ998A GPIO [19:18] need 47k

operation, OZ998B doesn’t.

9 I/O TTL 12mA

Fully programmable GPIO that can be used for a variety of dedicated or specif ic funct i ons. Pin GPIO[0] has

an SMIEVENT output as an alternate function. GPIO[0] is set as default. It is also programmable to

function as GPI[0] input, GPO[0] output, ALF[0] output, or ID[0] input. In addition, if this pin is configured as

output, TTL output, Open Drain or Open collector output can be selected. Refer to GPIO Config.1&2

Registers for more detai l s and GPIO Config. Tables (sec tion 8) for input/output selections.

10 I/O TTL 12mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. GPIO[1] pin

defaults as input. It is also programmable to function as GPI[1] input, GPO[1] output, ALF[1] output, or ID[1]

input. In addition, if this pin is configured as output, TTL output, Open Drain or Open collector output can

be selected. Refer to GPIO Config.1&2 Registers for more details and GPIO Config. Tables (section 8) for

input/output selecti ons.

11 I/O TTL 12mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[2]

defaults as input. This pin, when programmed as an alternate function, can generate the SMBALERT#

interrupt. SMBALERT# is an interrupt servi ce request signal to the SMBus Host which can be generated by

all devices connected to the OZ998. Pin GPIO[2]/SMBALERT# is also programmable to function as GPI[2]

input, GPO[2] output, ALF[2] output, or ID[2] input. In addition, if this pin is configured as output, TTL

output, Open Drain or Open collector can be selected. Refer to GPIO Config.1&2 Registers for more

details and GPIO Config. Tables (section 8) for I/O s el ections.

OZ998

Type Input Drive Definition

Primary SMBus Clock Input

Primary SMBus Data I/O

Host System Power Good

Reset

General Purpose I/O/

Secondary SMBus-1 Clock I/O

General Purpose I/O/

Secondary SMBus-1 Data I/O

General Purpose I/O/

Secondary SMBus-2 Clock I/O

General Purpose I/O /

Secondary SMBus-2 Data I/O

:

pull-up for normal

General Purpose I/O /

SMIEVENT

General Purpose I/O

General Purpose I/O/

SMBALERT#

:

pull-up for

OZ998-SF-2.2 Page 3

Page 4

Name Pin No. Type Input Drive

GPIO[7:3]/ID[7:3]

GPIO[10:8]

GPIO[11]

GPIO[12]/

SMB_SEL[0]

GPIO[13]/

SMB_SEL[1]

GPIO[14]/

S_SMBDATA3

GPIO[15]/

S_SMBCLK3

XOUT

XIN/32KHZ

GND

VCC

[17:15],

[13:12]

Fully programmable GPIOs that can be used for a variety of dedicated or specific functions. GPIO[7:3] pins

default as inputs. They are programmable to function as GPI[7:3] inputs, GPO[7:3] outputs, ALF[7:3]

outputs, or ID[7:3] inputs. In addition, if this pin is configured as output, TTL output, Open Drain or Open

collector can be selected. Refer to GPIO Config.1&2 Registers f or more details and GPIO Config. Tables

(section 8) for input/out put selections.

[20:18] I/O TTL 4mA

Fully programmable GPIOs that can be used for a variety of dedicated or specific functions. Pins

GPIO[10:8] default as inputs. Pins GPIO[10:8] as inputs are programmable to generate SMI/SMB

interrupts. They are also programmable to function as GPI[10:8] inputs, GPO[10:8] out puts. Refer to GPIO

Config.1&2 Registers for more details and GPIO Confi g. Tabl es (section 8) for input/output selections.

21 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[11] is

default as input. Pin GPIO[11] as input is programmable to generate SMI/SMB interrupts. They are also

programmable to function as GPI[11] input, GPO[11] output. Refer to GPIO Config.1&2 Registers for more

details and GPIO Config. Tables (section 8) for input/out put selections.

22 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. By default,

GPIO[12] becomes SMB_SEL[0] input to be used to select Secondary SMBus. Pin GPIO[12] default as

input. Pin GPIO[12] as input is programmable to generate SMI/SMB interrupts. It is also programm able to

function as GPI[12] input, GPO[12] output. Refer to GPIO Config.1&2 Registers for more details and GPIO

Config. Tables (section 8) for input/output selections.

SMB_SEL[1:0] Selected Secondary SMBus

00 None

01 Secondary SMBus-1

10 Secondary SMBus-2

11 Secondary SMBus-3

23 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. On default,

GPIO[13] becomes SMB_SEL[1] input to be used to select Secondary SMBus. Pin GPIO[13] default as

input. Pin GPIO[13], as input is programmable to generate SMI/SMB interrupts. It is also programmable to

function as GPI[13] input, GPO[13] output. Refer to GPIO Config.1&2 Registers for more details and GPIO

Config. Tables (section 8) for input/output selections.

24 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[14]

default as input. Pin GPIO[14], as input is programmable to generate SMI/SMB interrupts. It is also

programmable to function as GPI[14] input, GPO[14] outputs or secondary SMBus-3 Data Input/Output.

Refer to GPIO Config.1&2 Registers for more details and GPIO Config. Tables (section 8) for input/output

selections.

25 I/O TTL 4mA

Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[15]

default as input. Pin GPIO[15], as input is programmable to generate SMI/SMB interrupts. It is also

programmable to function as GPI[15] input, GPO[15] output or secondary SMBus -3 Clock Input/Output.

Refer to GPIO Config.1&2 Registers for more details and GPIO Config. Tables (section 8) for input/output

selections.

26 O - Crystal output pin. See appli cation diagram on p.18.

27 I TTL 32KHZ input clock sourc e. Crystal input pin as alternate. See application diagram on p.18.

14 GND - Ground.

28 PWR - -

3.3V or 5V Power Supply.

I/O TTL 12mA

Definition

General Purpose I/Os

General Purpose I/Os

General Purpose I/O

General Purpose I/O /

Secondary SMBus Select 0

General Purpose I/O /

Secondary SMBus Select 1

General Purpose I/O /

Secondary SMBus-3 Data I/O

General Purpose I/O /

Secondary SMBus-3 Clock I/O

3.3V/5V Power Supply

OZ998

XOUT Output

XIN Input/32KHZ

Ground

OZ998-SF-2.2 Page 4

Page 5

DC CHARACTERISTICS

DC TABLE FOR VCC = 5.0V r 10%

Symbol Parameter Min Max Units

VCC

VIH

VIl

VOH

VOL

IIL

IOL

DC TABLE FOR VCC = 3.3V r 10%

Symbol Parameter Min Max Units

VCC

VIH

VIl

VOH

VOL

IIL

IOL

CAPACITANCE

Symbol Parameter

CIN

C

OUT

CIO

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Units

VCC

V

IN, VOUT

I

IN

T

STG

T

OPER|

Power Supply Voltage 4.5 5.5 V

Input HIGH Voltage 2.0 - V

Input LOW Voltage - 0.8 V

Output HIGH Voltage 2.4 - V

Output LOW Voltage - 0.4 V

Maximum Input Leakage Current -10 10

Maximum Output Leakage -10 10

Power Supply Voltage 3.0 3.6 V

Input HIGH Voltage 2.0 - V

Input LOW Voltage - 0.8 V

Output HIGH Voltage 2.4 - V

Output LOW Voltage - 0.4 V

Maximum Input Leakage Current -10 10

Maximum Output Leakage -10 10

0 qC to 70qC

Maximum Input Capacitance 10 pF

Maximum Output Capacitance 10 pF

Maximum I/O Capacitance 10 pF

DC Power Supply Voltage -0.3 to 5.5 V

DC Input, Output Voltage -0.3 to V

DC Current Drain V

Pins

Storage Temperature -40 to +125

Operation Temperature 0 to 70

and VCC

CC

+ 0.3 V

CC

±25

µA

µA

µA

µA

Units

mA

°C

°C

OZ998

OZ998-SF-2.2 Page 5

Page 6

ICC SPECIFICATIONS

Symbol Parameter Typ Max Units

I

Supply Current, V

CC5V

32KHZ input clock source is

used)

I

Supply Current, V

CC3V

(when 32KHZ input clock source

is used)

I

Supply Current, V

CC5V

external OSC is used based on

configuration on p.18)

I

Supply Current, V

CC3V

(when external OSC is used

based on configuration on p.18)

= 5V (when

CC

= 3.3V

CC

= 5V (when

CC

= 3.3V

CC

8 15

5 10

150 200

50 80

µA

µA

µA

µA

OZ998

OZ998-SF-2.2 Page 6

Page 7

13. OZ998 PACKAGE INFORMATION

e

B

D

E H

A

A1

SSOP

PACKAGE

(209 mil)

D

L

OZ998

DIM

A 0.084 2.13

A1 0.002 0.010 0.05 0.25

B 0.009 0.015 0.22 0.38

C 0.004 0.008 0.09 0.20

D 0.390 0.413 9.90 10.50

E 0.197 0.220 5.00 5.60

e 0.0256 0.65

H 0.291 0.323 7.40 8.20

L 0.025 0.041 0.63 1.03

α 0° 8° 0° 8°

C

INCHES MILLIMETERS

MIN MAX MIN MAX

OZ998-SF-2.2 Page 7

Loading...

Loading...