Sony CXK5B18120TM-12 Datasheet

CXK5B18120TM

For the availability of this product, please contact the sales office.

65536-word × 18-bit High Speed Bi-CMOS Static RAM

Description

CXK5B18120TM is a high speed 1M bit BiCMOS static RAM organized as 65536 words by

18 bits. Operating on a single 3.3V supply this

asynchronous IC is suitable for use in high speed

and low power applications.

Features

• Single 3.3V Supply 3.3V±0.3V

• Fast access time 12ns (Max.)

• Low stand-by current: 10mA (Max.)

• Low power operation 1116mW (Max.)

• Package line-up

Dual Vcc/Vss

CXK5B18120TM 400mil 44pin TSOP Package

Function

65536-word × 18-bit static RAM

Structure

Silicon gate Bi-CMOS IC

44 pin TSOP (Plastic)

-12

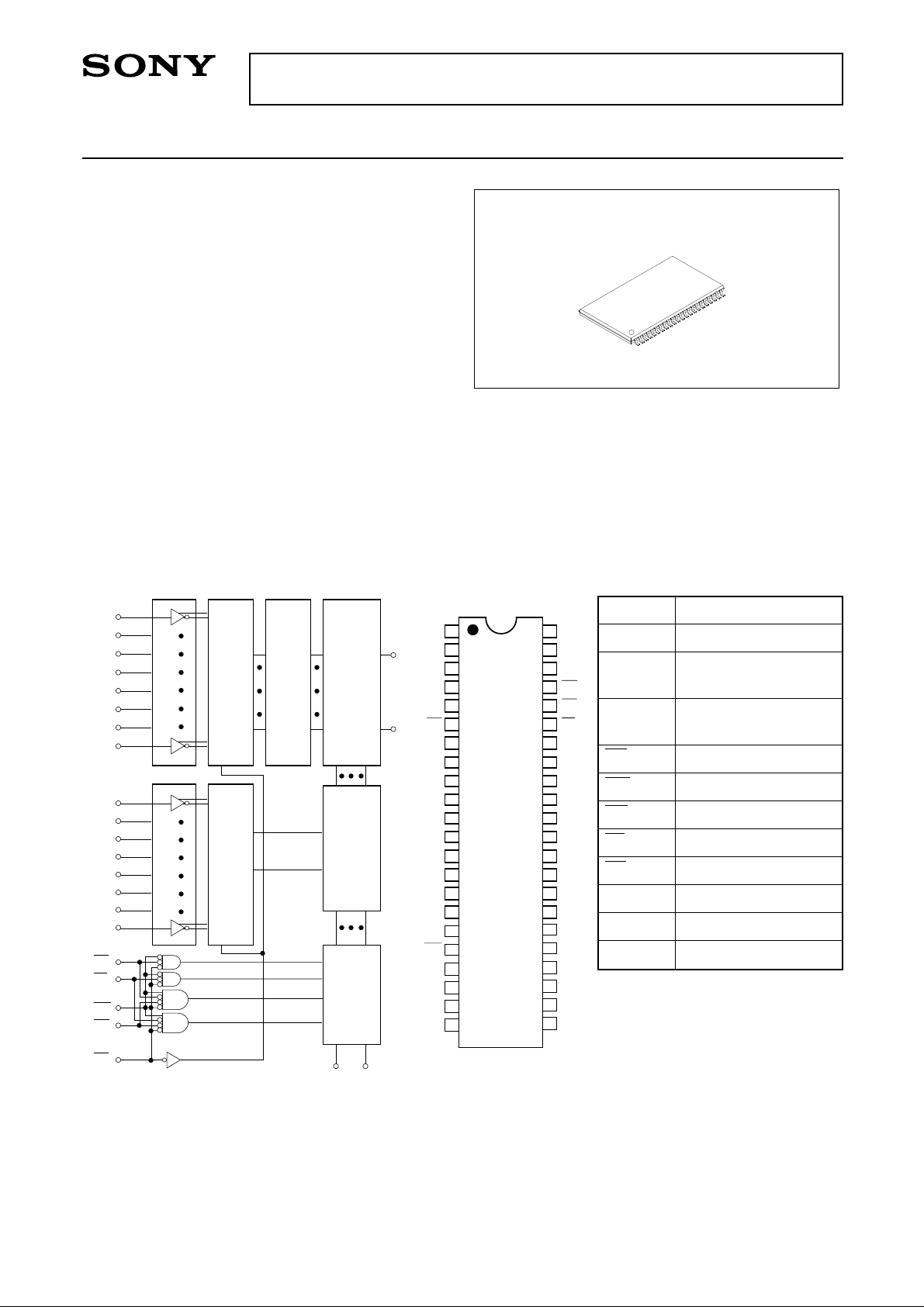

Block Diagram Pin Description

A14

A15

A9

A8

A12

A13

A11

A10

A5

A4

A3

A0

A2

A1

A6

A7

UB

LB

WE

OE

Buffer

Buffer

Row

Decoder

Memory

Matrix

256 × 4608

GND

I/O Gate

Column

Decoder

I/O

Buffer

Pin configuration

A4

1

A3

2

Vcc

A2

3

A1

4

5

A0

6

CE

I/O1

7

I/O2

8

I/O3

9

I/O4

1

0

Vcc

11

GND

12

I/O5

13

I/O6

14

I/O7

15

I/O8

16

I/O9

17

18

WE

A15

19

A14

20

A13

21

A12

22

(Top View)

Symbol

A5

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

A6

A7

OE

UB

LB

I/O18

I/O17

I/O16

I/O15

GND

Vcc

I/O14

I/O13

I/O12

I/O11

I/O10

NC

A8

A9

A10

A11

A0 to A15

I/O1

to I/O9

I/O10

to I/O18

CE

WE

OE

LB

UB

Vcc

GND

NC

Address input

Data input output

(lower byte I/O)

Data input output

(upper byte I/O)

Chip enable input

Write enable input

Output enable input

Lower byte select input

Upper byte select input

+3.3V Power supply

Ground

No connection

Description

CE

I/O1 I/O18

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 1 –

E93585A57-PK

Absolute Maximum Ratings (Ta = 25°C, GND = 0V)

Item Symbol Rating Unit

∗

Supply voltage

Input voltage

Input and output voltage

Allowable power dissipation

VCC

VIN

VI/O

PD

–0.5

–0.5

1

–0.5

∗

1

to VCC + 0.5

∗

1

to VCC + 0.5

1.5

to +4.6

∗

2

V

V

V

W

CXK5B18120TM

Operating temperature

Storage temperature

Soldering temperature • time

∗

1 Vcc, VIN, VI/O = –2.0V Min. for pulse width less than 5ns

∗

2 Air Flow ≥ 1m/s

Topr

Tstg

Tsolder

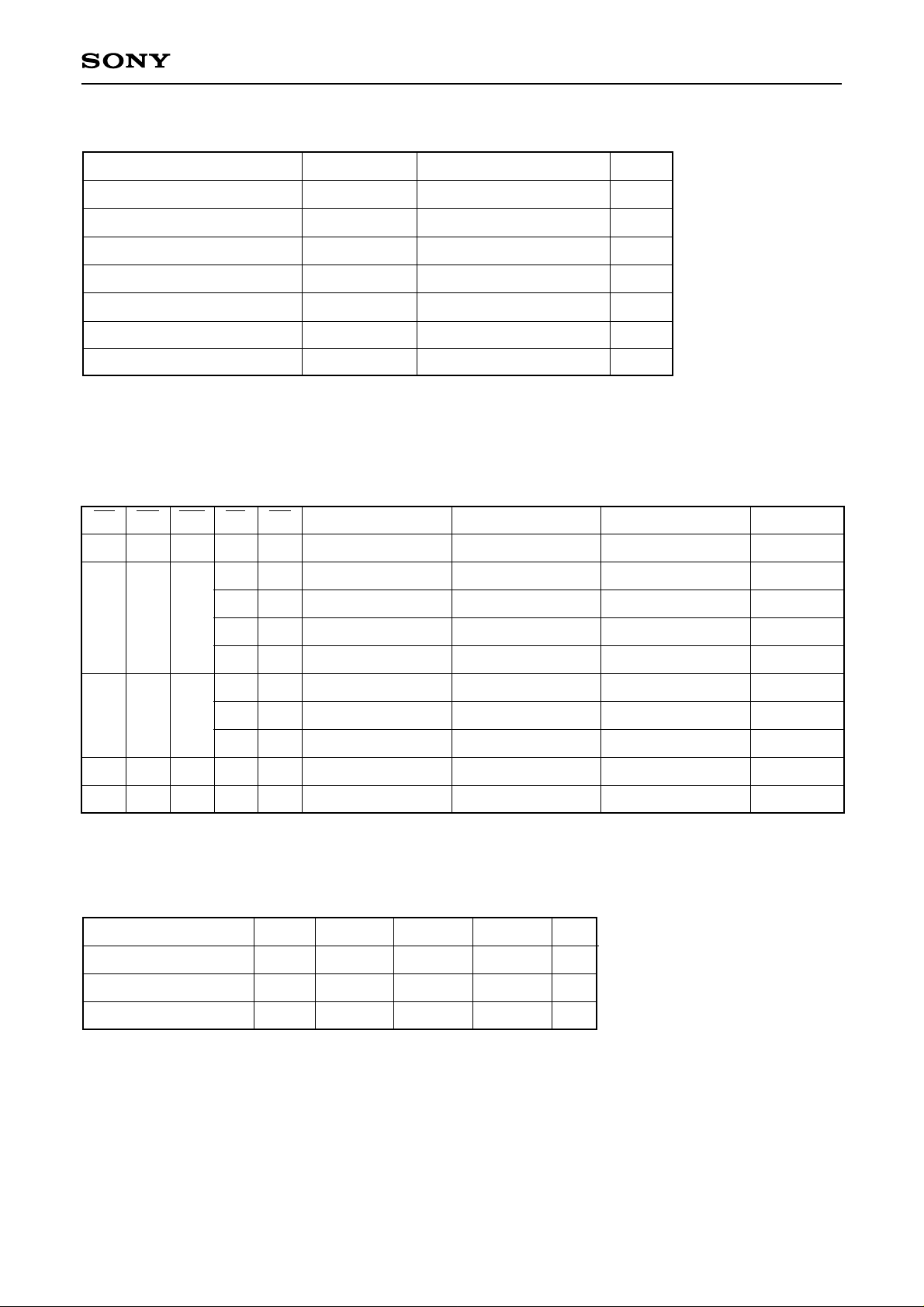

Truth Table

CE

OE WE LB UB Mode I/O1 to I/O9 I/O10 to I/O18 Current

H

×

×

×

×

Not selected

L

L

Read

L

H

L

L

H

H

H

L

L

×

L

L

H

Read

L

Read

H

Not selected

L

Write

H

Write

L

Write

0 to +70

–55 to +150

235 • 10

High Z

Data Out

Data Out

High Z

High Z

Data in

Data in

High Z

°C

°C

°C • sec

High Z

Data out

High Z

Data out

High Z

Data in

High Z

Data in

ISB1, ISB2

ICC

ICC

ICC

ICC

ICC

ICC

ICC

L

H

H

×

×

Output disable

L

×

×

H

H

Not selected

High Z

High Z

×: “H” or “L”

Recommended Operating Conditions (Ta = 0 to +70°C, GND = 0V)

Item Symbol Min. Typ. Max. Unit

Supply voltage

Input high voltage

Input low voltage

∗

VIL = –2.0V Min. for pulse width less than 5ns

VCC

VIH

VIL

3.0

2.0

–0.3

3.3

—

∗

—

3.6

VCC + 0.3

0.8

V

V

V

High Z

High Z

ICC

ICC

– 2 –

CXK5B18120TM

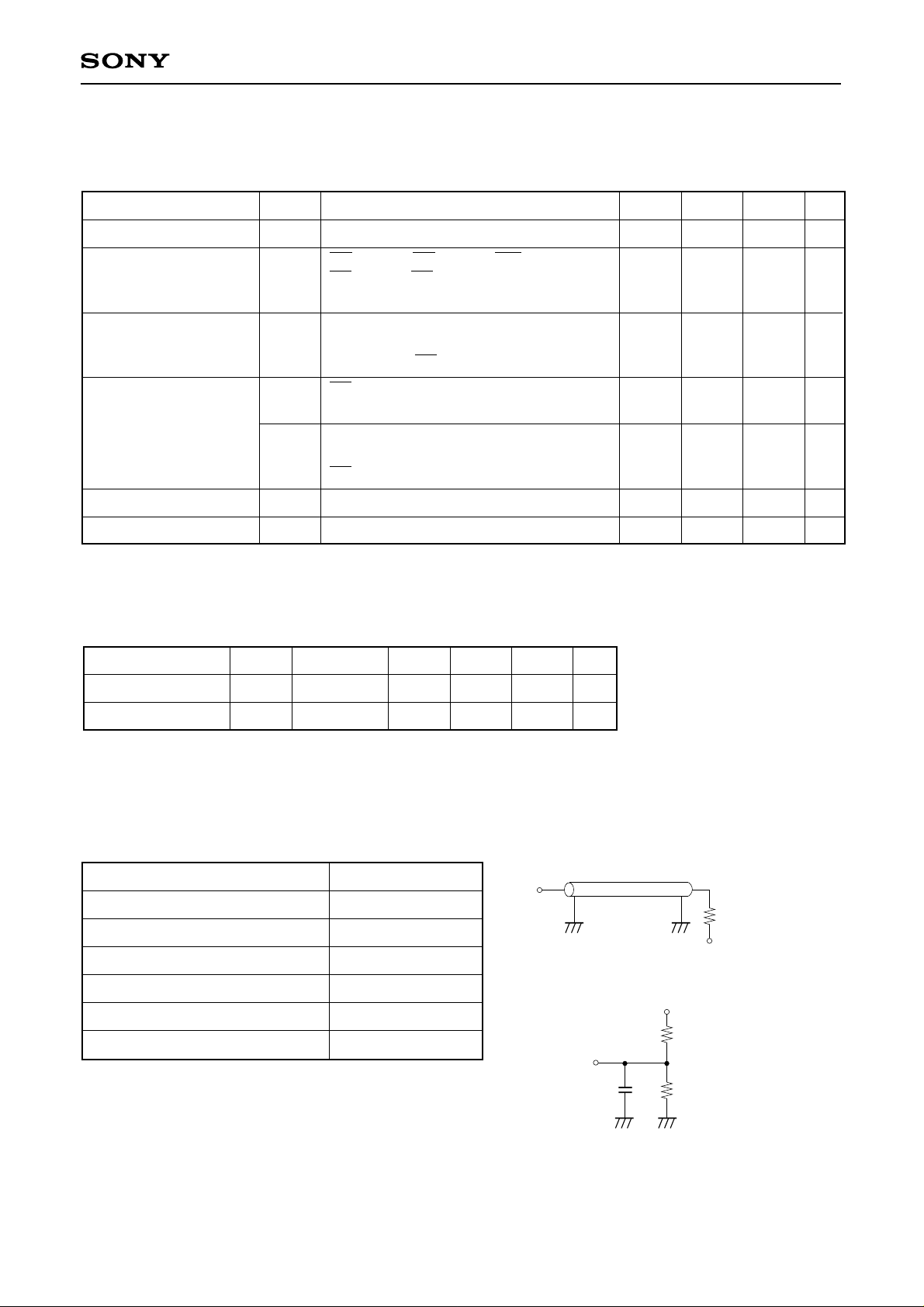

Electrical Characteristics

DC Characteristics (Vcc = 3.3V±0.3V, GND = 0V, Ta = 0 to +70°C)

∗

Item Symbol Conditions

Min.

Typ.

Max. Unit

Input leakage current

ILI

VIN = GND to Vcc

CE = VIH or OE = VIH or WE = VIL or

Output leakage current

ILO

UB = VIH or LB = VIH

VI/O = GND to Vcc

Average operating

current

Standby current

ICC

ISB1

ISB2

Min. Cycle

Duty =100%

IOUT = 0mA, CE = VIL, VIN = VIH or VIL

CE ≥ Vcc – 0.2V

VIN ≥ Vcc – 0.2V or VIN ≤ 0.2V

Min. Cycle

Duty =100%

CE = VIH, VIN = VIH or VIL

Output high voltage

Output low voltage

VOH

VOL

IOH = –2.0mA

IOL = 2.0mA

* Vcc = 3.3V, Ta = 25°C

I/O Capacitance (Ta = 25°C, f = 1MHz)

Item

Input capacitance

Symbol Conditions Min. Typ. Max. Unit

CIN

VIN = 0V

—

—

5

pF

–10

–10

—

—

—

2.4

—

—

—

—

—

—

—

—

+10

+10

310

10

100

—

0.4

µA

µA

mA

mA

mA

V

V

I/O capacitance

CI/O

VI/O = 0V

—

Note) This parameter is sampled and is not 100% tested.

AC Characteristics

• AC test condition (Vcc = 3.3V±0.3V, Ta = 0 to +70°C)

Item

Input pulse high level

Input pulse low level

Input rise time

Input fall time

Input and output reference level

Output load conditions

Condition

VIH = 3.0V

VIL = 0.0V

tr = 2ns

tf = 2ns

1.4V

Fig. 1

—

*1. For tLZ, tOLZ, tLBLZ, tUBLZ, tHZ, tOHZ, tLBHZ, tUBHZ, tOW, tWHZ

*2. Including scope and jig capacitances.

7

I/O

pF

Output load (1)

Zo=50Ω

Output load (2)*

I/O

2

5pF*

3.3V

V

L=1.4V

1

1179Ω

868Ω

L=50Ω

R

– 3 –

Fig. 1

Loading...

Loading...