Distribution

Restraint

Internal Outside

Prohibited Prohibited

7.96cm 320 480 16,777,216 colors HVGA Transflective color LCD Module

ACX567AKM-7

Description

This display is a 7.96cm diagonal active matrix transflective color LCD module based on Low temperature

polycrystalline silicon TFT technology. This LCD has 320 480 pixels and integrated driver which provides a

symmetric module with narrow edge frame. This module includes a LED backlight and a memory integrated

one chip driver IC with Low power consumption. The driver IC contains FL3G/SPI and RGB interface circuit,

partial memory, CABC function and DC-DC converter.

(Application: Smartphone)

Features

LCD type : Transflective

Symmetric and narrow frame edge module

Dot layout : RGB stripe

Number of dots : 320 RGB 480 / Portrait type

Dot size : 0.046mm 0.138mm (184ppi)

Number of colors : 16,777,216 (R,G, B each 8bit)

Interface : 8bit FL3G/SPI or RGB

Partial RAM size : 320 120 3bit

Supply voltage : VDD_18 1.8V 5%

DD (VBATT) 3.0V 3%

V

Low power consumption : 32mW (max.) (Vertical B/W worst image @VBATT = 3.7V)

100W (max.) (Standby mode)

High reflectivity : 1.7% (@Diffusion)

High contrast ratio : 700:1 (typ.) (LED backlight on)

Luminance (LED backlight on) : 400cd/m

Built-in DC-DC converter

Weight : 15g

2

(typ.)

Prohibited Prohibited

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license

by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating

the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

- 1 -

E08Z19-SP

ACX567AKM-7

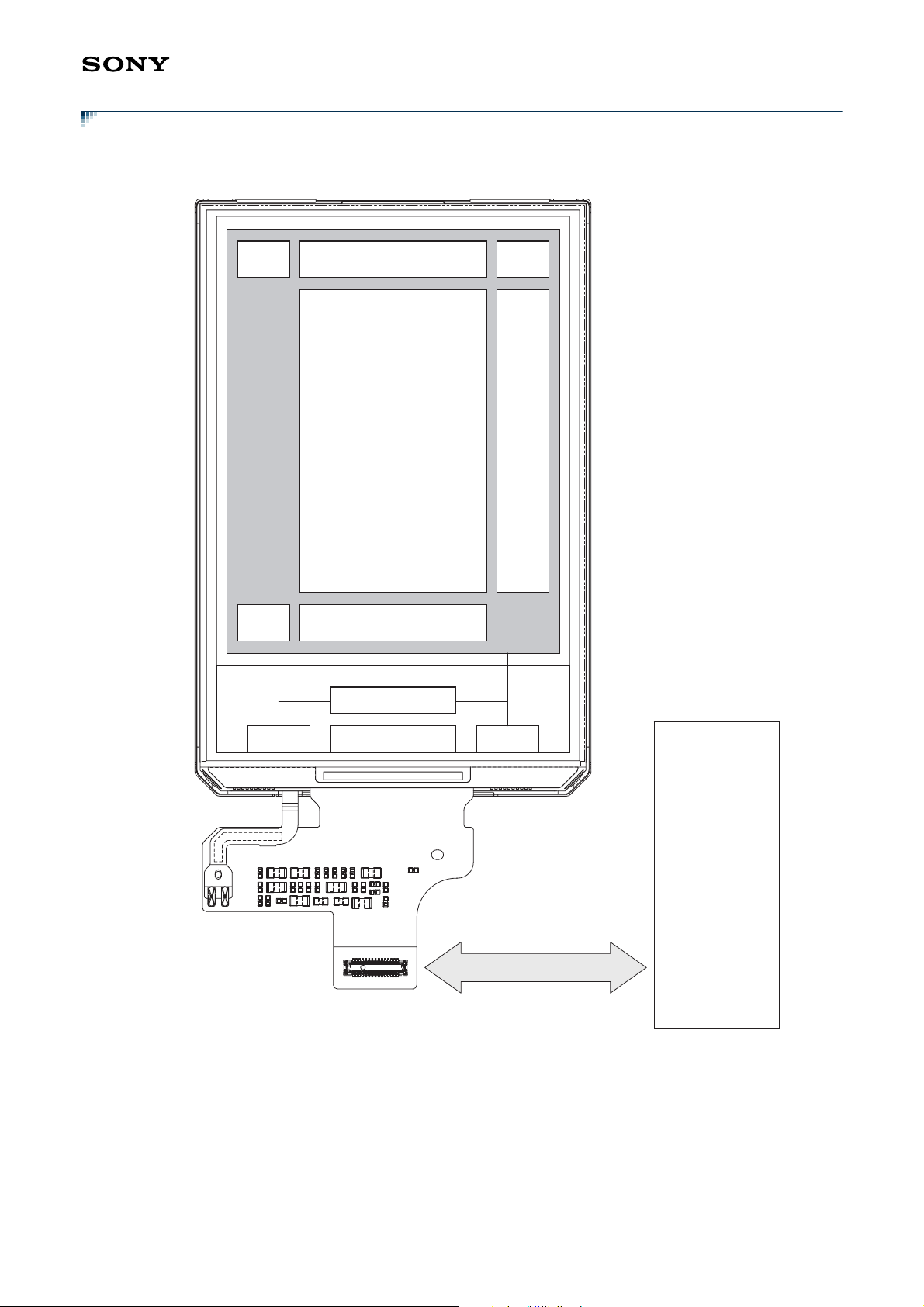

Element Structure

Active matrix TFT-LCD panel with built-in peripheral driving circuitry using Low temperature polycrystalline

silicon transistors.

Driver IC mounted on TFT glass as COG

5 LEDs backlight

Hardcoated surface polarizer

Number of active dots: 320 (H) 3 480 (V) = 460,800

Dimensions

Module dimensions: 49.86mm (W) 75.19mm (H) 1.64mm (t)

Thickness: from top polarizer to FPC surface

Effective display dimensions (Active area): 44.16mm (H) 66.24mm (V)

- 2 -

ACX567AKM-7

Block Diagram

The panel block diagram is shown below.

TSW-

control

Precharge/TEST circuit

Active Area

320 × RGB × 480

TSIG-

control

VCS-

Driver

Selector

Control

Selector SW

COG

TEST PAD1 TEST PAD2

I/F PAD

V

DD

VDDIO

RESETX

SPI

CSX

WRX

RDX

SDX

Sub_LVDS

CLK+, CLK–

D0+, D0–

D1+, D1–

B/L

LED_Anode

LED_Cathode

Matching connector:

501591-3010 (Molex)

- 3 -

ACX567AKM-7

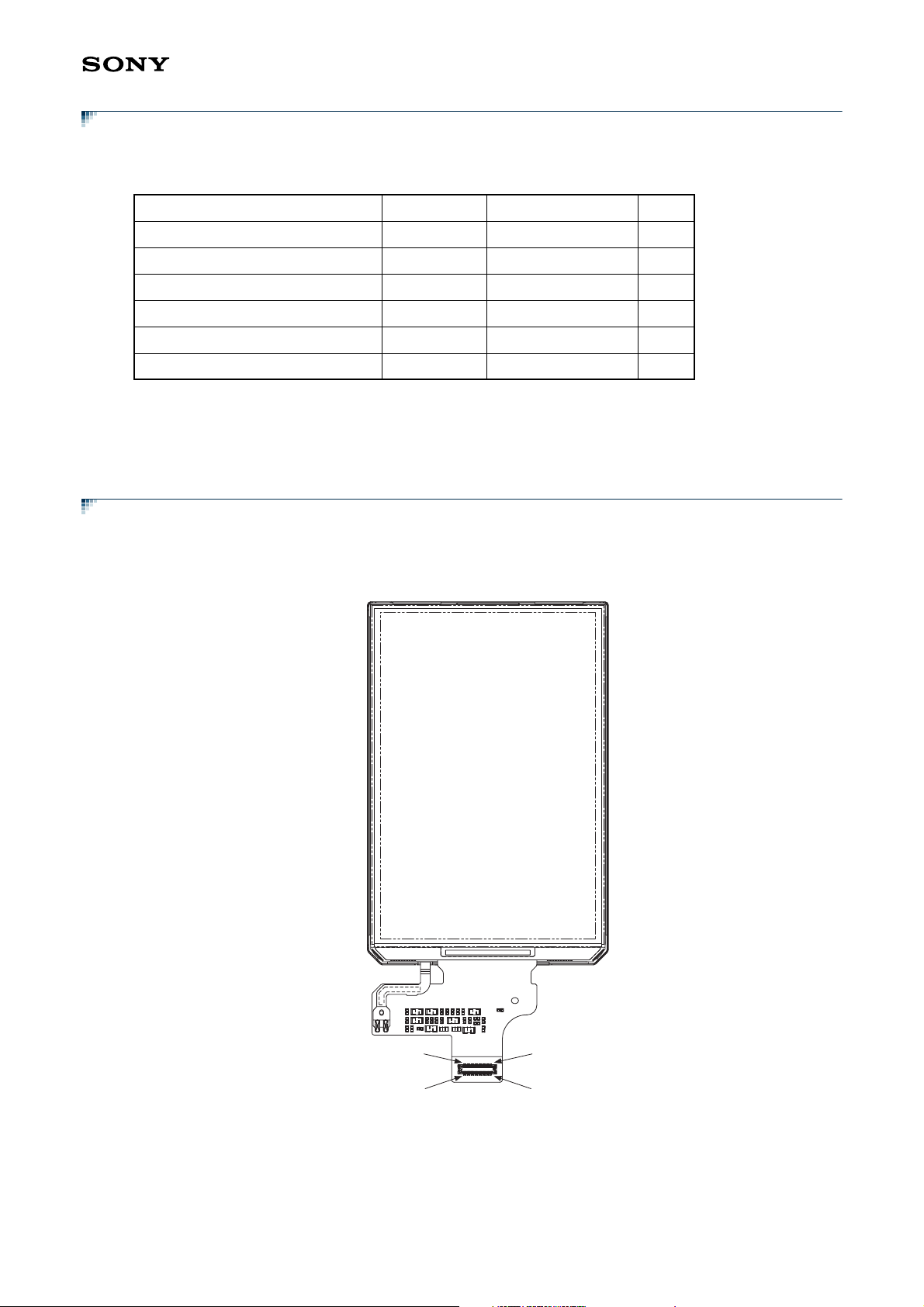

Absolute Maximum Ratings

(VSS = 0V)

Parameter Symbol Rating Unit

Power supply voltage 1 V

Power supply voltage 2 V

Logic signal input voltage 1 (

Logic signal output voltage (

Operation temperature Topr –10 to +60

Storage temperature Tstr –30 to +70

Note)

Ta = –30 to +70C (no damage at –40 to +85C)

*1

SPI_CS, SPI_DI, SPI_CLK, RESETX

*2

SPI_DO, PWM_LCD

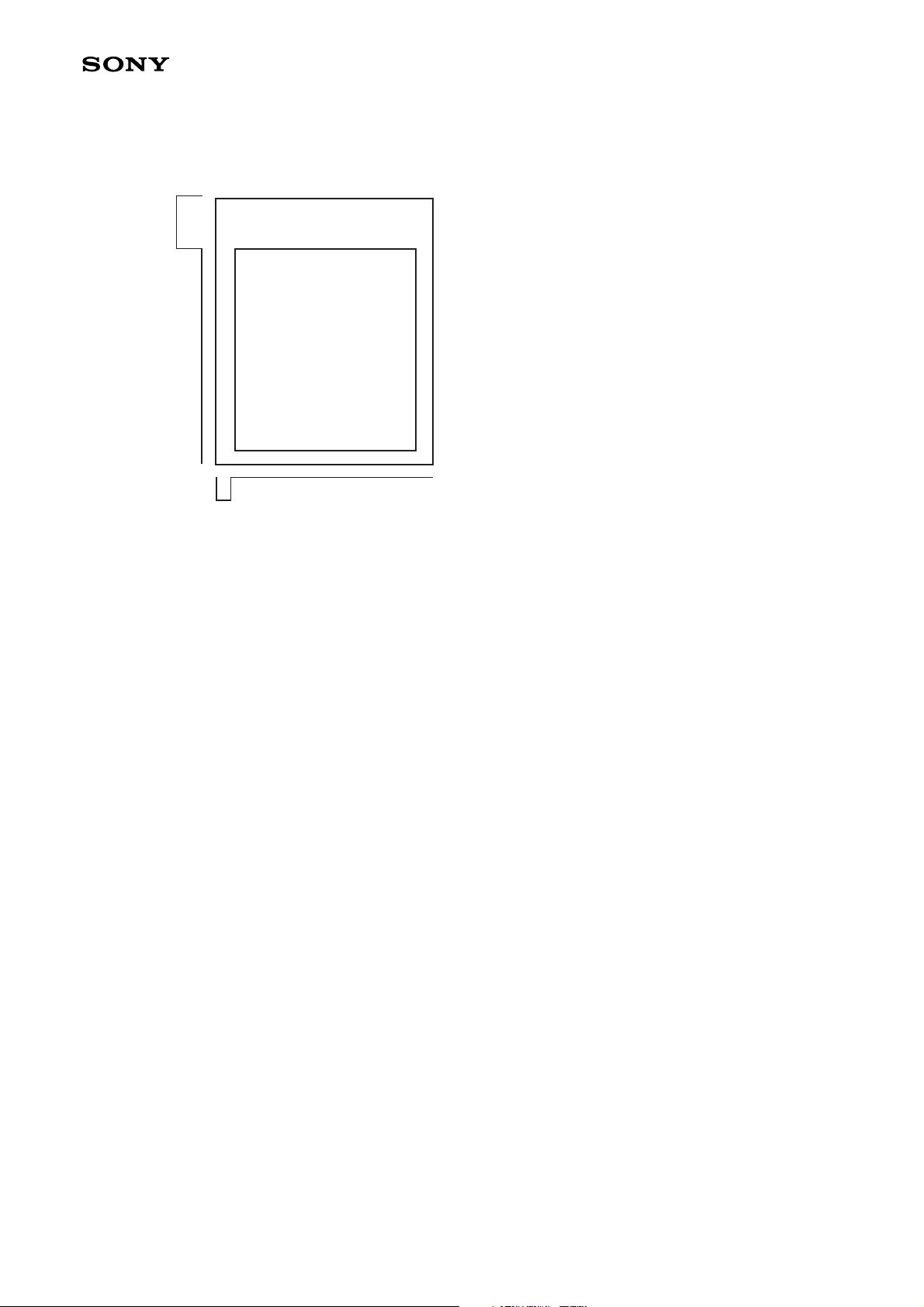

Pin Location

The pin assignment is described in the next page. The location of Pad is shown below.

BATT –0.3 to +5.5 V

DD_18 –0.3 to +3.0 V

*1

)VI1 –0.5 to VDD_18 + 0.5 V

*2

)VO –0.5 to VDD_18 + 0.5 V

C

C

Pin 2

Pin 1

Pin 30

Pin 29

- 4 -

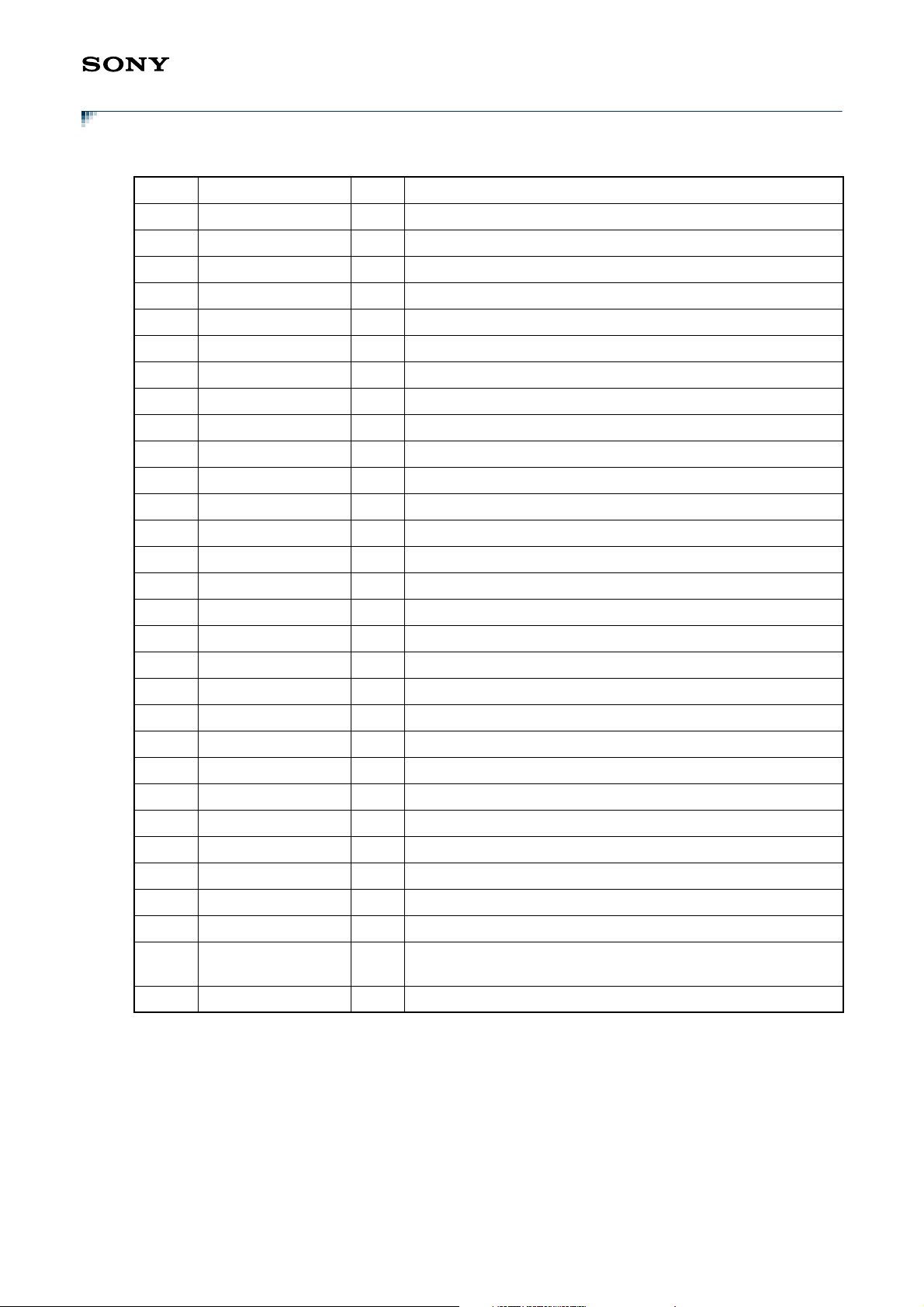

ACX567AKM-7

Pin Description

Pin No. Symbol I/O Description

1N.C. Non connect. For customer, this pin should be open.

2BL LED ANODE Common anode for LED's

3BL LED CATHODE Common cathode for LED's

4SPI_CS ISerial interface CHIP SET input

5PWM_LCD OPWM signal output for LCD

6SPI_DI/DO I/OSerial interface DATA input/output

7N.C. Non connect. For customer, this pin should be open.

8GND Ground

9N.C. Non connect. For customer, this pin should be open.

10 GND Ground

11 GND Ground

12 FL3G D0– I Negative polarity signal of High-speed data channel 0

13 SPI_CLK I Serial interface clock input

14 FL3G D0+ I Positive polarity signal of High-speed data channel 0

15 GND Ground

16 GND Ground

17 RESETX I Hard reset input. (Active-Low)

18 FL3G CK– I Negative polarity signal of High-speed clock channel

19 GND Ground

20 FL3G CK+ I Positive polarity signal of High-speed clock channel

21 V

BATT PPositive power supply 3.0V

22 GND Ground

23 VBATT PPositive power supply 3.0V

24 FL3G D1– I Negative polarity signal of High-speed data channel 1

25 V

DD_18 P Positive power supply 1.8V

26 FL3G D1+ I Positive polarity signal of High-speed data channel 1

27 V

DD_18 P Positive power supply 1.8V

28 GND Ground

29 NVM

Non connect. For customer, this pin should be open.

Using SONY's manufactory only.

30 N.C. Non connect. For customer, this pin should be open.

- 5 -

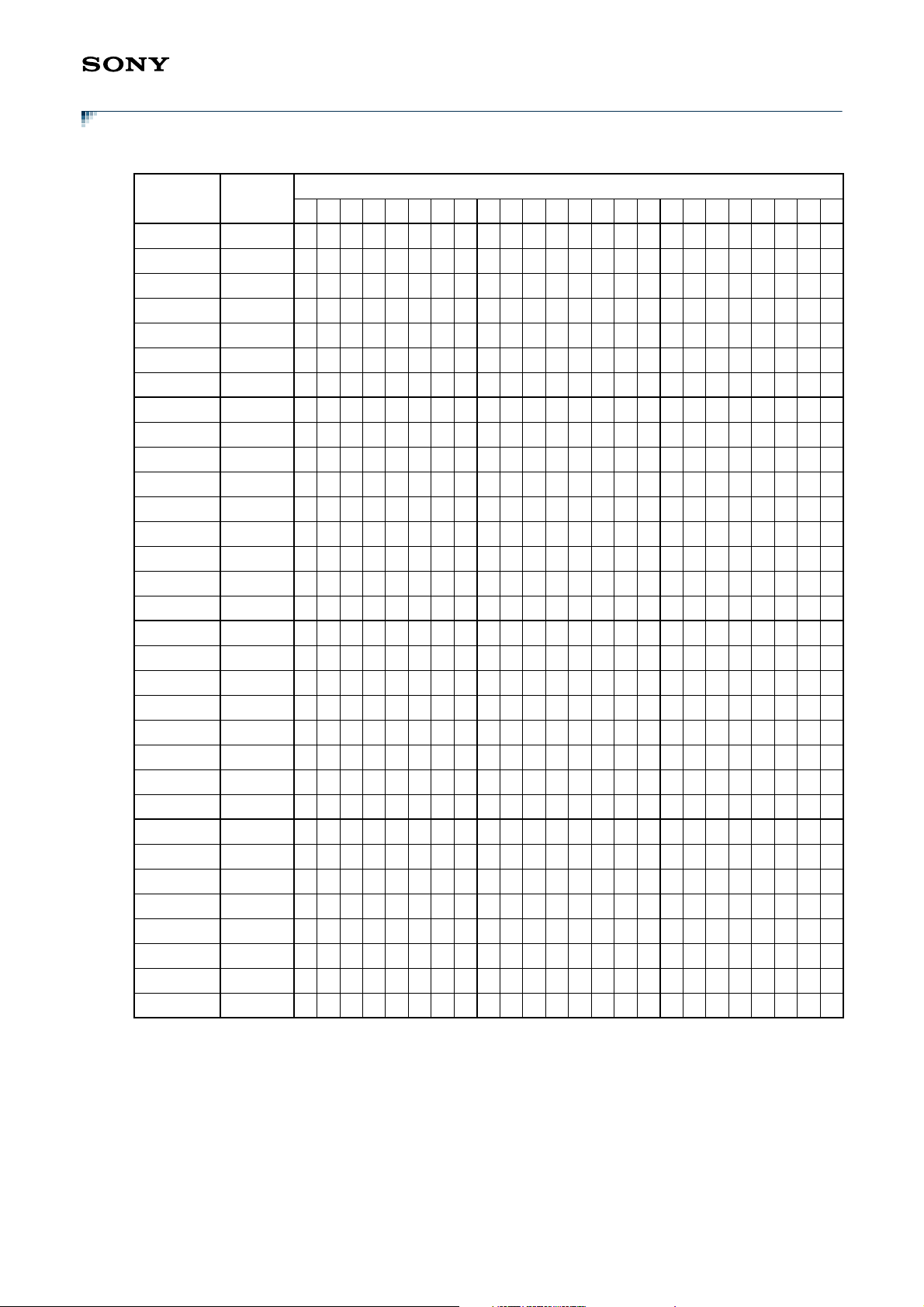

Color Table

ACX567AKM-7

Color & gray

scale

Gray scale

level

R0 R1 R2 R3 R4 R5 R6 R7 G0 G1 G2 G3 G4 G5 G6 G7 B0 B1 B2 B3 B4 B5 B6 B7

Data signal

Black — L L L L L L L L L L L L L L L L L L L L L L L L

Blue — L L L L L L L L L L L L L L L L H H H H H H H H

Green — L L L L L L L L H H H H H H H H L L L L L L L L

Cyan — L L L L L L L L H H H H H H H H H H H H H H H H

Red — H H H H H H H H L L L L L L L L L L L L L L L L

Magenta — H H H H H H H H L L L L L L L L H H H H H H H H

Yellow — H H H H H H H H H H H H H H H H L L LLLLLL

White — H H H H H H H H H H H H H H H H H H H H H H H H

Black GS0 L L L L L L L L L L L L L L L L L L L L L L L L

GS1 H L L L L L L L L L L L L L L L L L L L L L L L

Darker GS2 L H L L L L L L L L L L L L L L L L L L L L L L

—

—

Brighter GS253 H L H H H H H H L L L L L L L L L L L L L L L L

GS254 L H H H H H H H L L L L L L L L L L L L L L L L

Red GS255 H H H H H H H H L L L L L L L L L L L L L L L L

Black GS0 L L L L L L L L L L L L L L L L L L L L L L L L

GS1 L L L L L L L L H L L L L L L L L L L L L L L L

Darker GS2 L L L L L L L L L H L L L L L L L L L L L L L L

—

—

Brighter GS253 L L L L L L L L H L H H H H H H L L L L L L L L

GS254 L L L L L L L L L H H H H H H H L L L L L L L L

Green GS255 L L L L L L L L H H H H H H H H L L L L L L L L

Black GS0 L L L L L L L L L L L L L L L L L L L L L L L L

GS1 L L L L L L L L L L L L L L L L H L L L L L L L

Darker GS2 L L L L L L L L L L L L L L L L L H L L L L L L

—

—

Brighter GS253 L L L L L L L L L L L L L L L L H L H H H H H H

GS254 L L L L L L L L L L L L L L L L L H H H H H H H

Blue GS255 L L L L L L L L L L L L L L L L H H H H H H H H

- 6 -

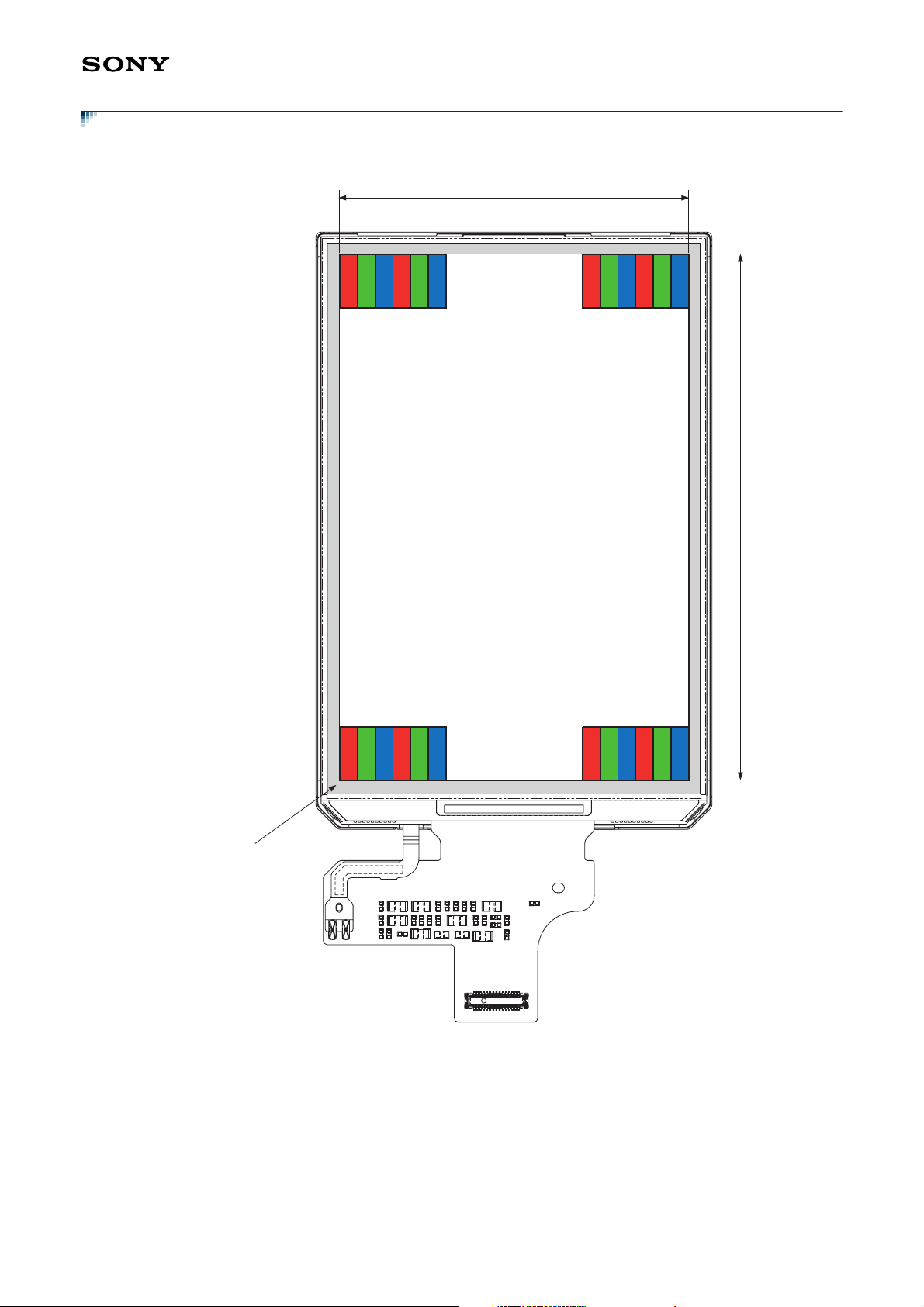

Color Coding

ACX567AKM-7

Active Area: 320 pixels

RGBRGB RGBRGB

Black Mask

Active Area: 480 pixels

RGBRGB RGBRGB

- 7 -

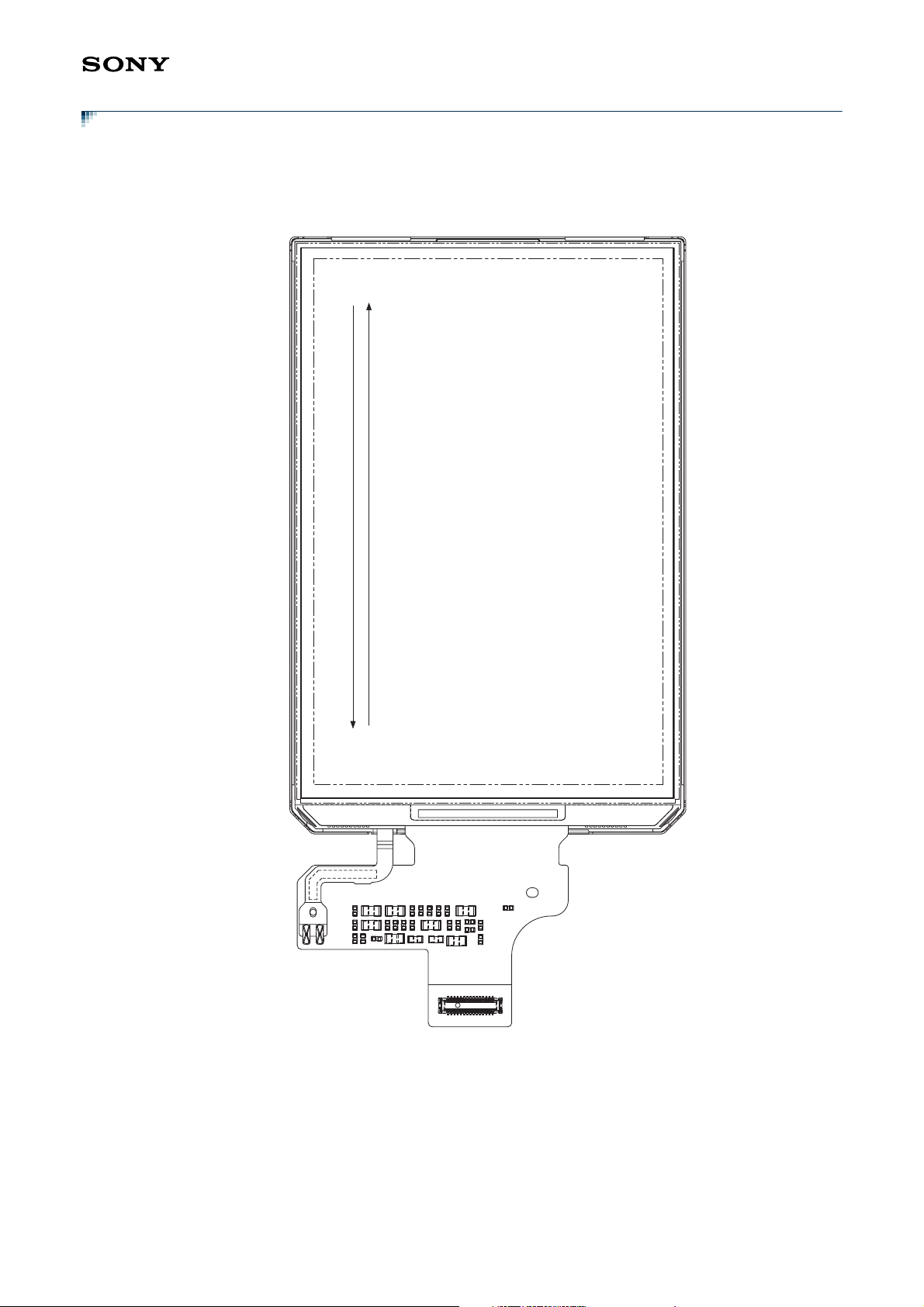

Scanning Direction

The scanning direction for the vertical period are A as shown below.

This scanning directions is from a front view.

ACX567AKM-7

Active Area

320 × RGB × 480

Vertical Direction (DWN = L)

Vertical Direction (DWN = H)

- 8 -

ACX567AKM-7

Electrical Characteristics

DC Characteristics

(VBATT = 3.0V 3%, VDD_18 = 1.8V 5%, Ta = –30 to +70C (no damage at –40 to +85C))

Item Symbol

Application

pins

Condition Min. Typ. Max. Unit

Power supply voltage 1 VBATT VBATT –3% 3.0 3% V

Power supply voltage 2 V

Power supply voltage

noise

*1

This value is not symmetric amplitude which center point is VDD_18. The value of VDD_18 is an average

DD_18 VDD_18 –5% 1.80 5% V

DD_NOISE VDD_18

V

V

BATT_NOISE VBATT ——300mVp-p

*1

——100mVp-p

value. See example below. These values are valid up to 100MHz.

DD_18 (average)

V

BATT = 3.0V 3%, VDD_18 = 1.8V 5%, Ta = –30 to +70

(V

Item Symbol

Logic High level

input voltage 1

Logic Low level

input voltage 1

Logic OUT High

level output voltage

V

IH1

V

IL1 VSS —

V

DOH

Application

pins

SPI_CS,

SPI_DI,

SPI_CLK,

RESETX,

Condition Min. Typ. Max. Unit

OUT = –1mA

I

C (no damage at –40 to +85C))

0.7

DD_18

V

0.8

VDD_18

100mVp-p

—VDD_18 V

—VDD_18 V

PWM_LCD

Logic OUT Low

level output voltage

V

DOL IOUT = +1mA VSS —

0.3

VDD_18

0.2

DD_18

V

V

V

- 9 -

ACX567AKM-7

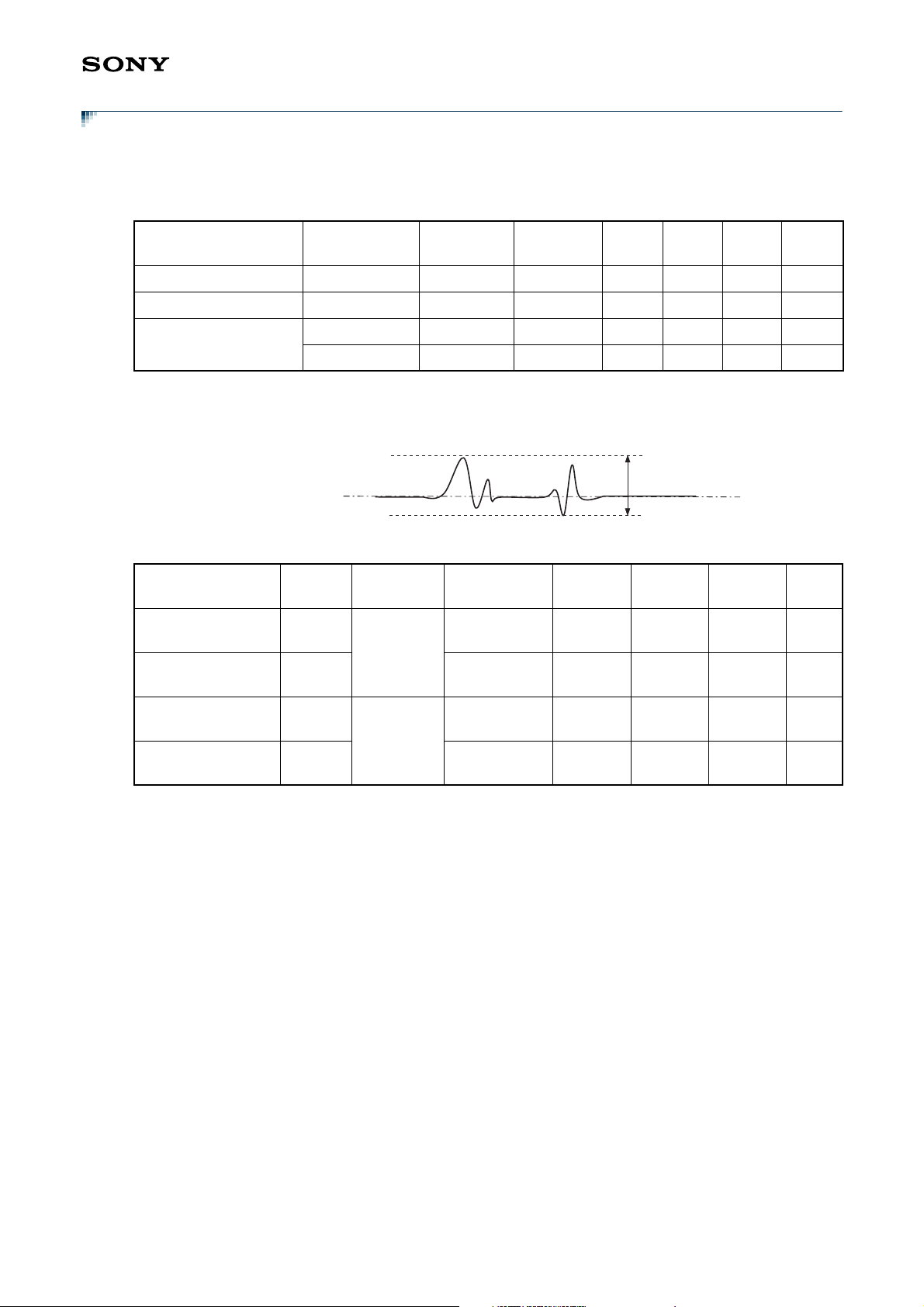

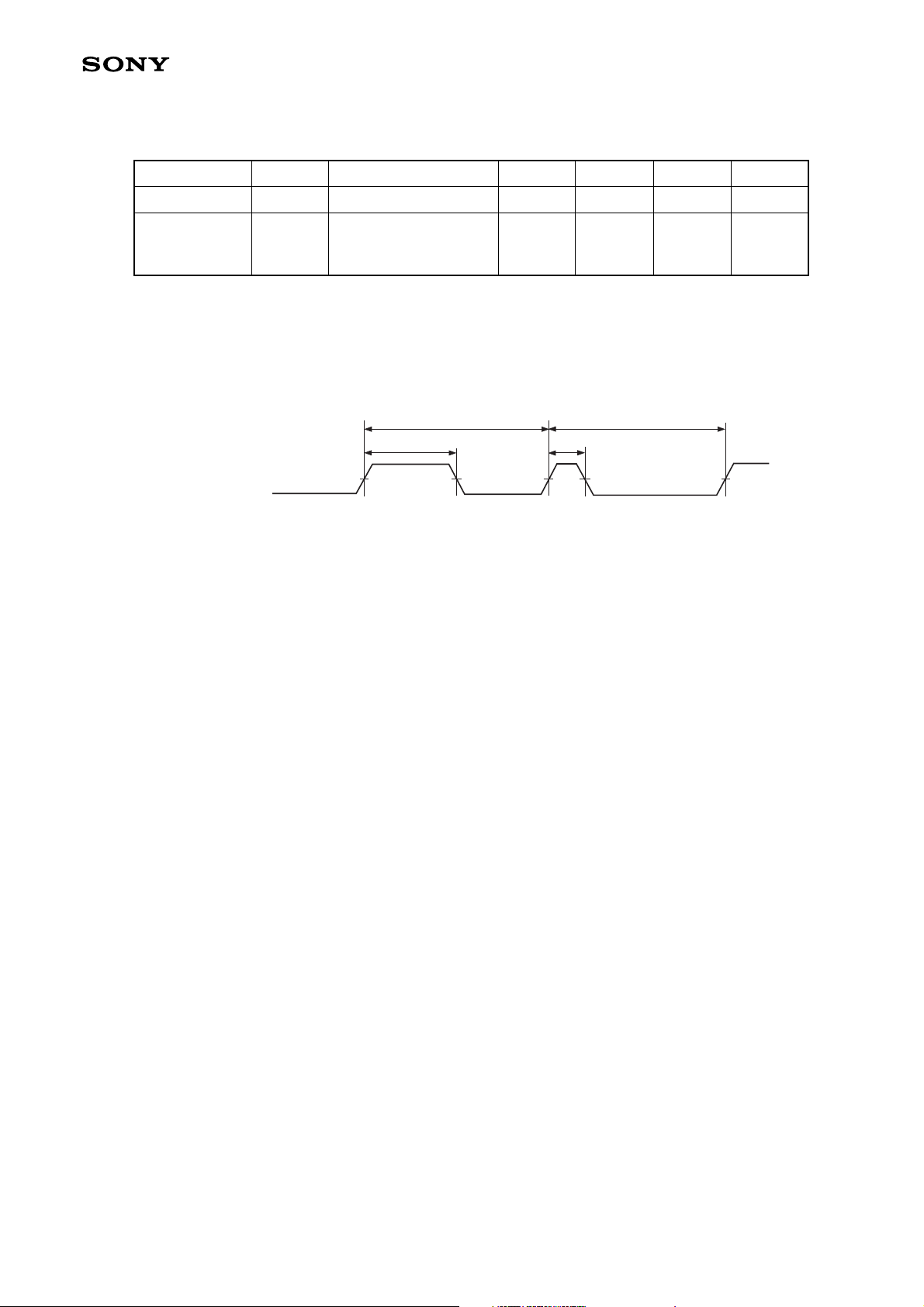

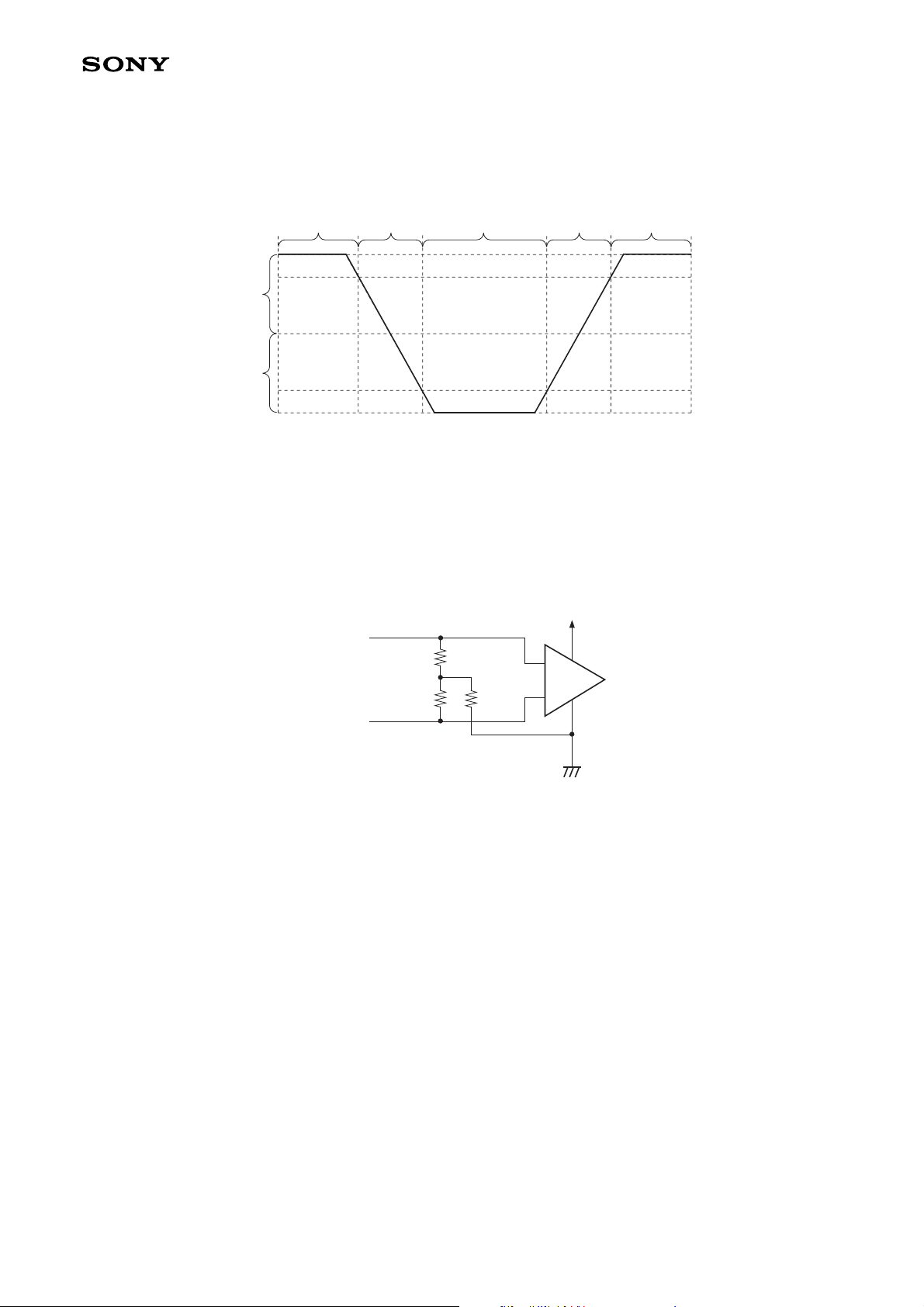

PWM Outputs

(VBATT = 3.0V 3%, VDD_18 = 1.8V 5%, Ta = –30 to +70C (no damage at –40 to +85C))

Item Symbol Condition Min. Typ. Max. Unit

500 Hz

LBV[7:0] = 00h to FFh

PWM_LBL duty d

lpwm

No Load

0—100%

Note2

Note 1: The PWM frequency for LCD B/L is adjustable by internal 8bits register that is programmed to NVM in

Sony’s factory.

Note 2: User can adjust PWM Duty for LCD B/L by register (WRLBV / 51h).

PWM Output for LCD

PWM_LBL

50%

tlcyc

A

50%

dlpwm = A/tlcyc

A'

50%

tlcyc

- 10 -

Input Timing

FlatLink3G Interface

ACX567AKM-7

Introduction

The number of data channels between TX and RX is programmable from 1 to 2 depending on bandwidth

needed. The data link speed is defined according to pixel clock (PCLK) of RGB I/F and the number of data

channels. FlatLink3G has 2 different power modes; shutdown and active. In shutdown mode, FlatLink3G

is totally inactive and assumed to consume least power (order of A). In active mode, FlatLink3G works as

a High-speed data link as defined.

TX adds odd parity bit in every data frame and RX checks the pixel data according to the sent parity.

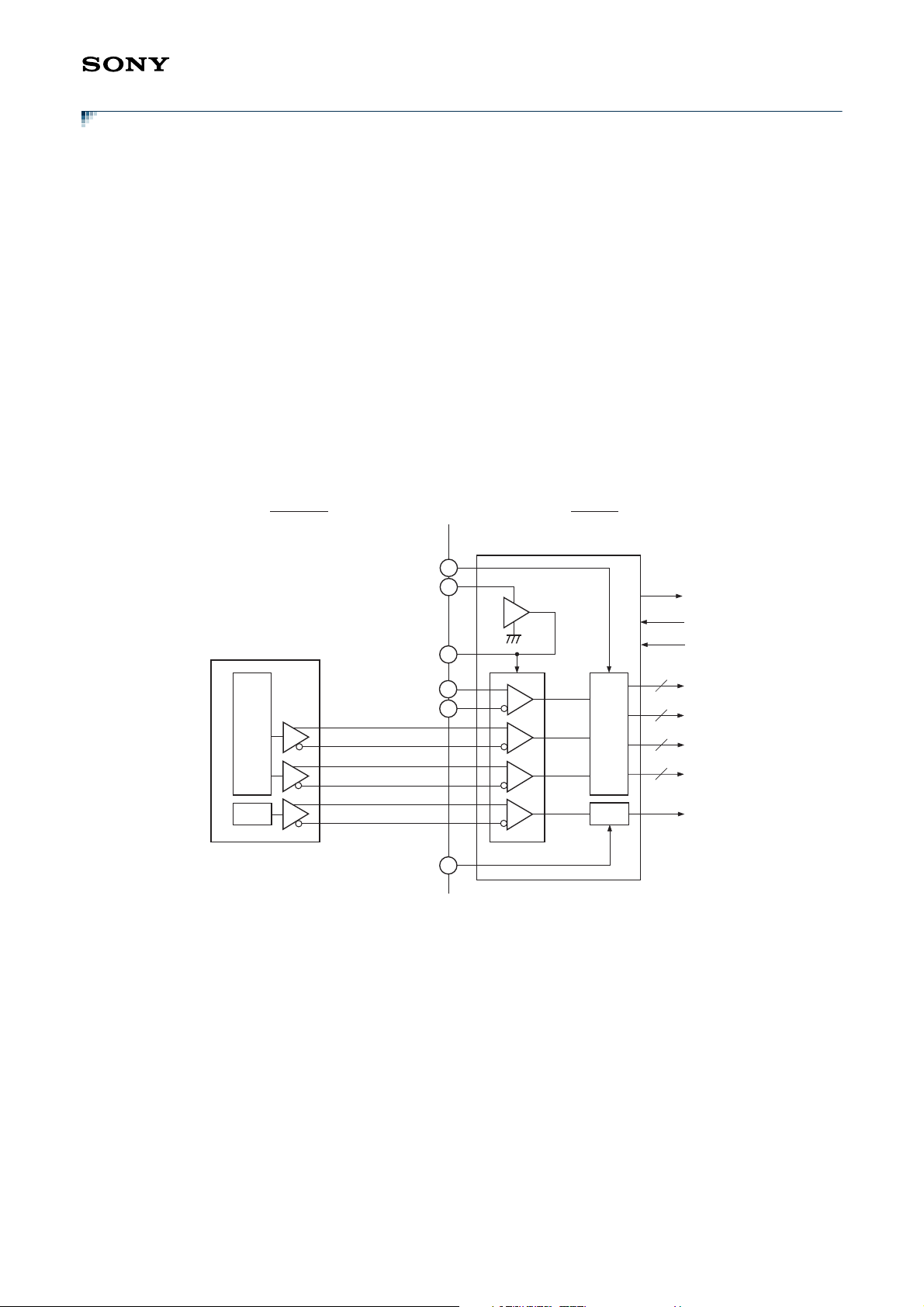

System Block Diagram and Link Protocol

System Block Diagram of FlatLink3G

FlatLink3G consists of three parts; TX, RX and High-speed signaling channels, as shown below.

SET Side

Receiver Block (RX)

VDDI

V

DD

V3G_LDO

D1+/D1–

converter

Parallel to serial

PLL

DDI is a link power and logic level supply and GND is a ground level of all circuits from a system power

V

D0+/D0–

CLK+/CLK1–

V

DD

_PLL

IC Side

PLL

To Internal Circuit

8

8

8

converter

Serial to parallel

3

RX_CPO

RX_LS

RX_SD

RX_R[7:0]

RX_G[7:0]

RX_B[7:0]

RX_HS, VS, DE

RX_PCLK

supply.

TX_R[7:0], TX_G[7:0], TX_B[7:0], TX_VS, TX_HS, TX_DE and TX_PCLK are RGB I/F parallel CMOS

signals provided for TX. PLL of TX provides necessary multiplied clock internally based on TX_PCLK.

TX serializes TX_R[7:0], TX_G[7:0], TX_B[7:0], TX_VS, TX_HS and TX_DE into High-speed data

channels, D0+/D0–, D1+/D1–, D2+/D2–, based on the multiplied clock. TX transfers TX_PLCK into a

High-speed clock channel, CLK+/CLK–, with its original rate. The number of data channels is

programmed by TX_LS and RX_LS.

PLL of RX provides necessary multiplied clock internally based on the High-speed clock channel

inputs. RX desterilizes the High-speed data channel inputs into RX_R[7:0], RX_G[7:0], RX_B[7:0],

RX_VS, RX_HS and RX_DE based on the multiplied clock. TX transfers the High-speed clock channel

into RX_PCLK. RX_R[7:0], RX_G[7:0], RX_B[7:0], RX_VS, RX_HS, RX_DE and RX_PCLK construct

RGB I/F parallel CMOS signals as output.

RX_XSD are CMOS signals for shutdown of TX and RX.

- 11 -

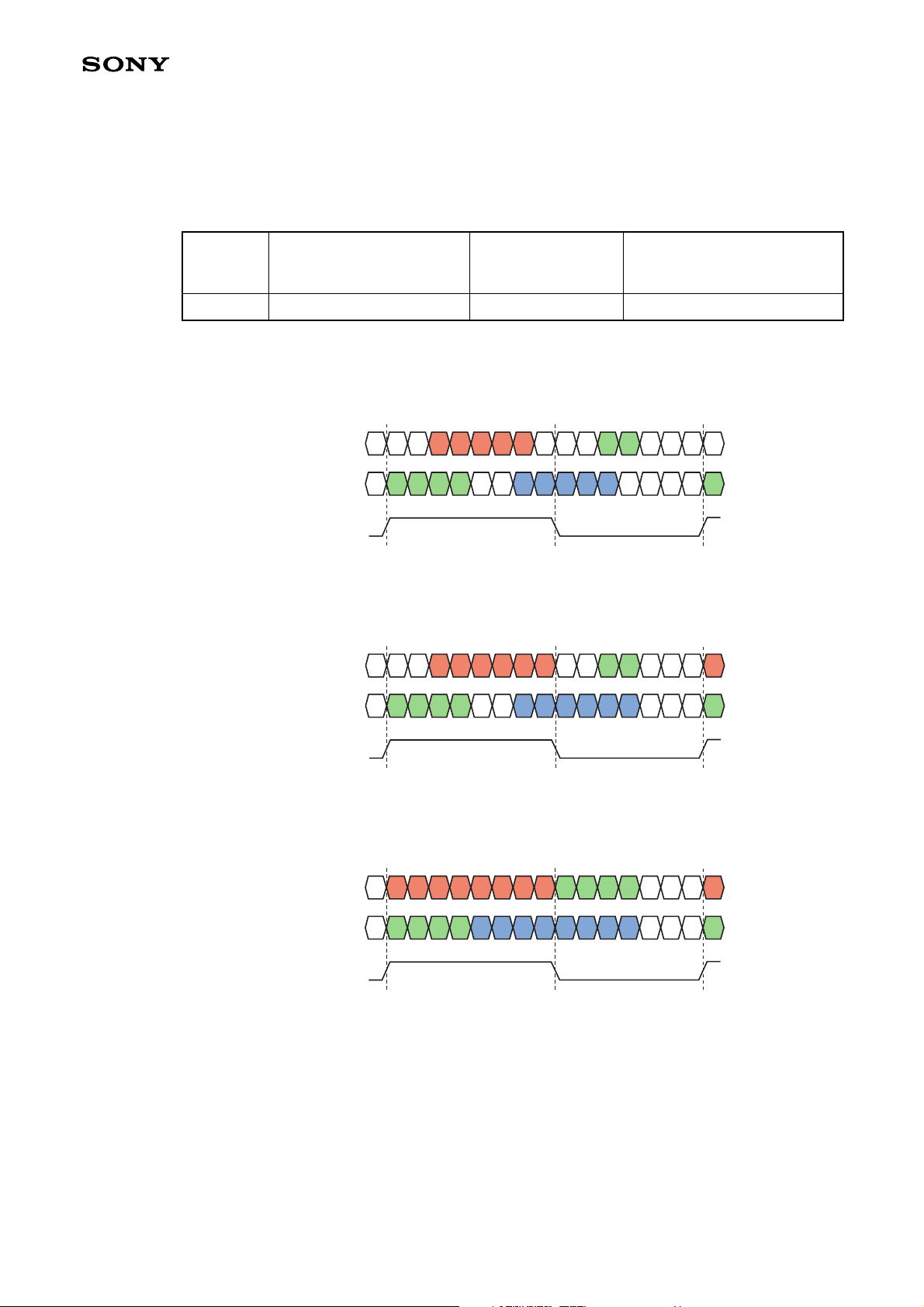

ACX567AKM-7

Link Programmability

The number of High-speed data channels is programmed in NVM by CM[2:0].

Table 1 shows the relation among CM, the number of High-speed data channels, the supported

RX_PCLK range and the guaranteed data bandwidth per channel.

Table 1. Link programmability

CM[2:0]

The number of High-speed

data channels

Supported

RX_PCLK range

[MHz]

Supported guaranteed data

bandwidth per channel

[Mbits/sec]

(0, 0, 1) 2 8.0 - 30.0 120 - 450

Option 1: The number of High-speed data channels is 2;

D0 Channel

D1 Channel

CLK Channel (∗)

D0 Channel

CP

res

CP

R4 R3

G0

G2 G1

G3

Protocol for 2-channel deta (16-bit Mode)

R5

R4 R3

R2

B4 B3

R0

R1

R0

R2 R1

B2 B1

G5

B0

G5

G4

G4

VS

HS

VS

res

DE

res

CP

res

CP

G3

R7

D1 Channel

CLK Channel (∗)

D0 Channel

D1 Channel

CLK Channel (∗)

res

CP

res

G3

R7 R6

G3

G0

G0

G2 G1

Protocol for 2-channel deta (18-bit Mode)

R5

R4 R3

G0

G2

G1

Protocol for 2-channel deta (24-bit Mode)

R2

B7 B6

B5

R1

B5

B4 B3

R0

B4 B3

G7

B2

G6

B2

B1

G5

B1

B0

G4

B0

HS

VS

HS

DE

res

DE

res

CP

res

G3

R7

G3

- 12 -

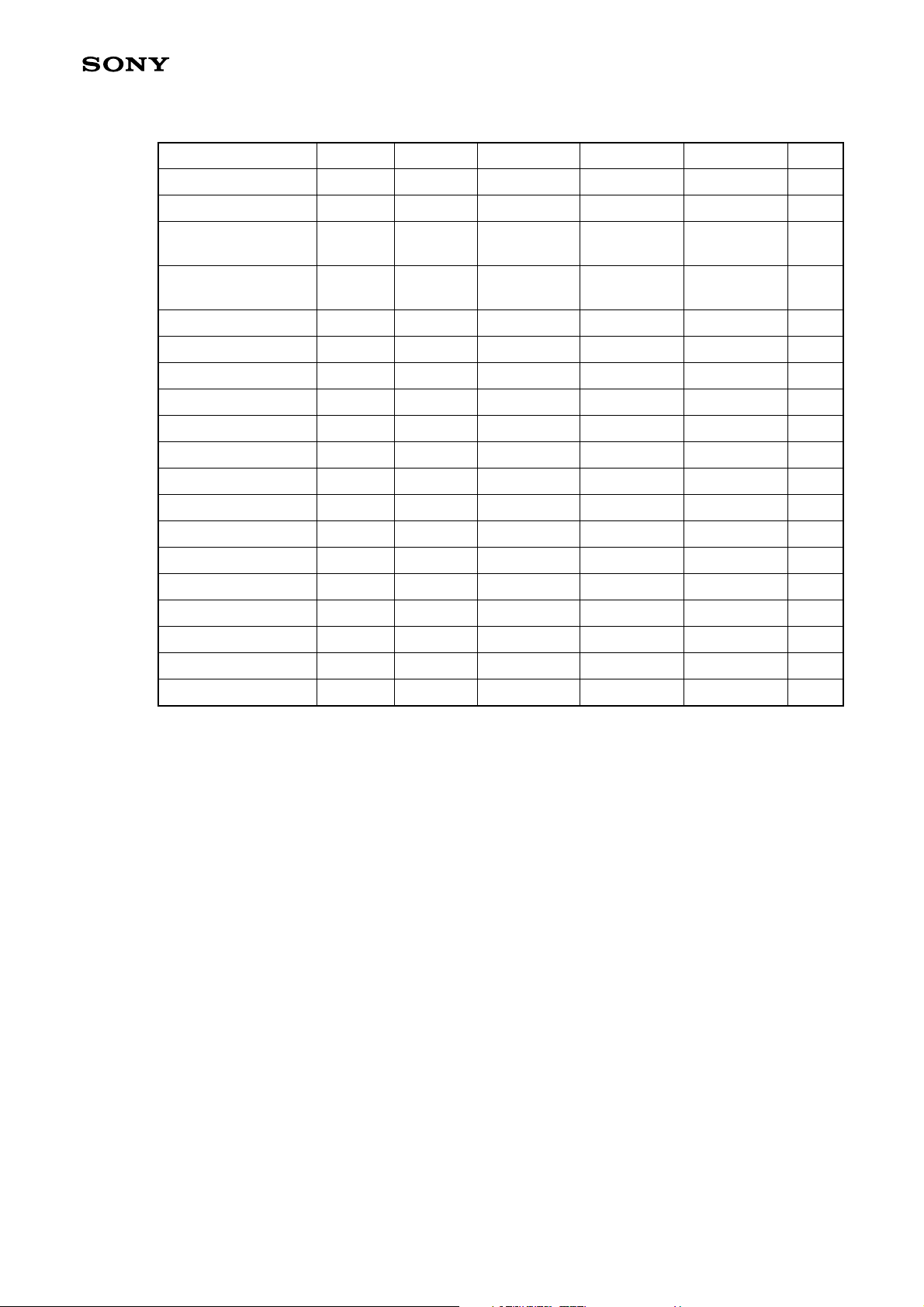

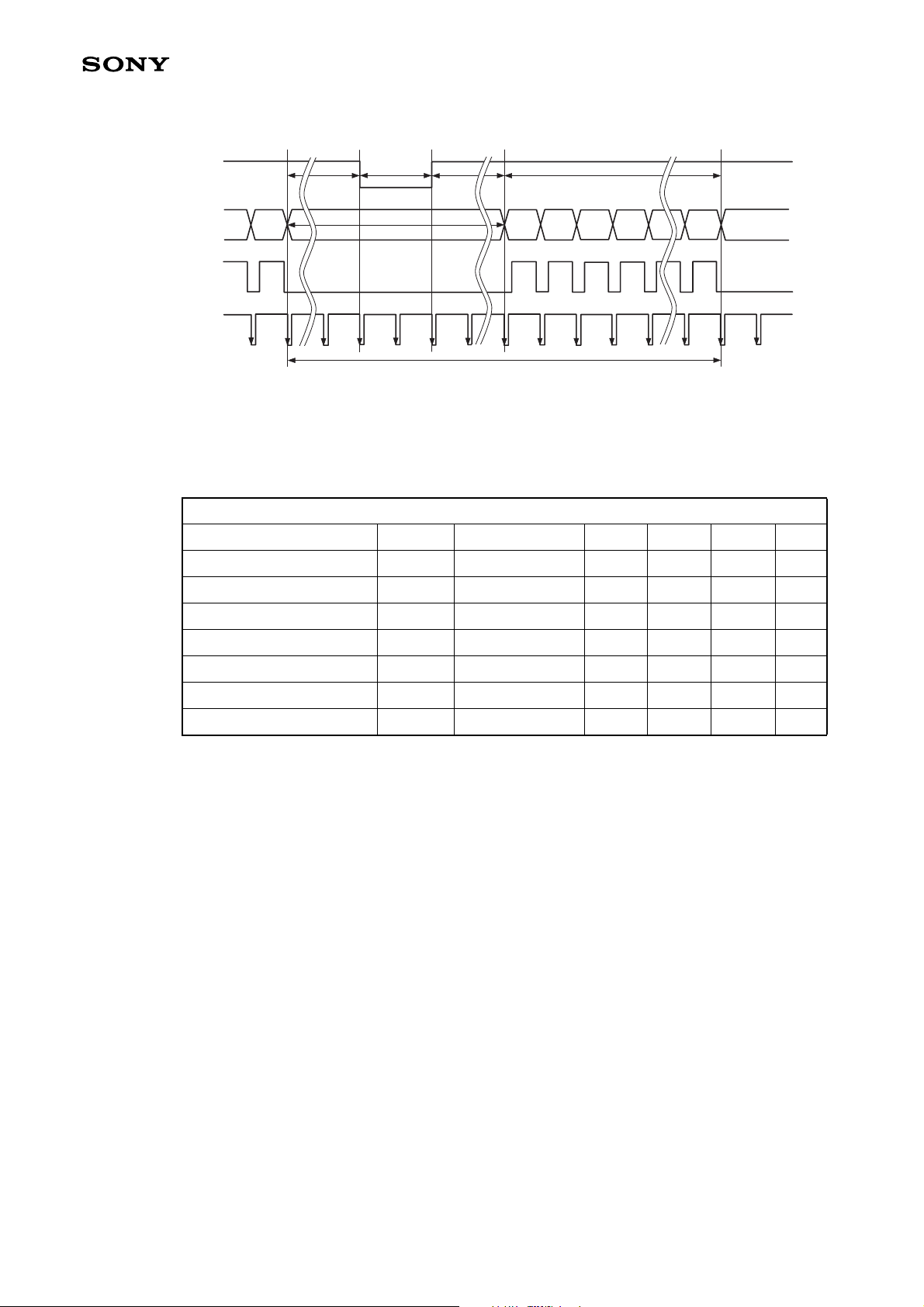

ACX567AKM-7

Two Data Channel Case

Item Symbol Condition Min. Typ. Max. Unit

Pixel clock frequency PCLK 8.0 — 30.0 MHz

Pixel clock cycle t

Clock-to-clock

position jitter

Clock-to-data

posittion jitter

CLK Ideal tCLK 60 — 125 ns

t

CLKjitter 0—300ps

t

DATAjitter 0—330ps

Ideal tpos0 position tpos0 Note 2 0 0 0 ns

Ideal tpos1 position tpos1 Note 2 (1/15) tCLK (1/15) tCLK (1/15) tCLK ns

Ideal tpos2 position tpos2 Note 2 (2/15) t

Ideal tpos3 position tpos3 Note 2 (3/15) t

CLK (2/15) tCLK (2/15) tCLK ns

CLK (3/15) tCLK (3/15) tCLK ns

Ideal tpos4 position tpos4 Note 2 (4/15) t

Ideal tpos5 position tpos5 Note 2 (5/15) t

Ideal tpos6 position tpos6 Note 2 (6/15) t

Ideal tpos7 position tpos7 Note 2 (7/15) t

Ideal tpos8 position tpos8 Note 2 (8/15) t

Ideal tpos9 position tpos9 Note 2 (9/15) t

Ideal tpos10 position tpos10 Note 2 (10/15) t

Ideal tpos11 position tpos11 Note 2 (11/15) t

Ideal tpos12 position tpos12 Note 2 (12/15) t

Ideal tpos13 position tpos13 Note 2 (13/15) t

Ideal tpos14 position tpos14 Note 2 (14/15) t

CLK (4/15) tCLK (4/15) tCLK ns

CLK (5/15) tCLK (5/15) tCLK ns

CLK (6/15) tCLK (6/15) tCLK ns

CLK (7/15) tCLK (7/15) tCLK ns

CLK (8/15) tCLK (8/15) tCLK ns

CLK (9/15) tCLK (9/15) tCLK ns

CLK (10/15) tCLK (10/15) tCLK ns

CLK (11/15) tCLK (11/15) tCLK ns

CLK (12/15) tCLK (12/15) tCLK ns

CLK (13/15) tCLK (13/15) tCLK ns

CLK (14/15) tCLK (14/15) tCLK ns

Note 1: Ta = –30 to +70C (to +85C no damage), VDDI = 1.65 to 1.95V, VSS (DGND) = 0V

Note 2: The reference point is when the CLK channel is changing from logical “0” to logical “1” at the 50%

level. This reference point is used to defined ideal t

POSn (n = 0, 1, 2, 3, ... ,14) positions.

- 13 -

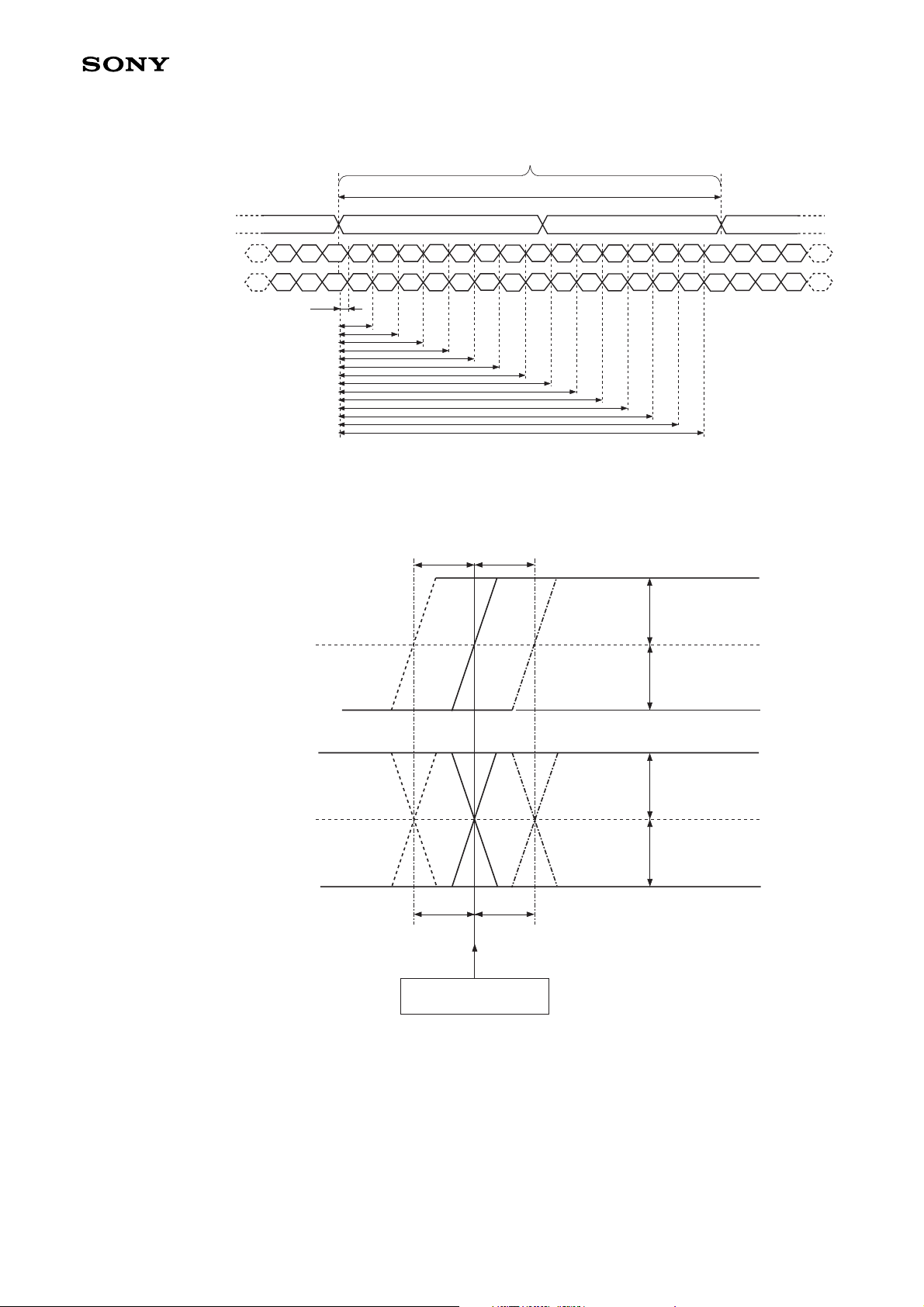

One Pixel

t

CLK

ACX567AKM-7

CLK Channel

D0 Channel

D1 Channel

Differential CLK

VS

HS

Res

DE

CLK+

D18

5

D17 D16 D15

D6

D5 D4

t

POS

tPOS

6

tPOS

7

8

D19

D7

4

t

POS

tPOS

D23

CP

Res

D11

0

t

POS

D21

D22

D10

POS

t

1

D20

D9

D8

POS

t

2

3

tPOS

Data Position - Two Data Channel Case

CLK_jitter

t

tCLK_jitter

CLK–

D13

D1

POS

t

11

D12

D0

POS

t

12

D14

D3

D2

POS

t

9

tPOS

10

HS

tPOS

13

Res

DE

t

POS

14

CP

Res

D23

D11

VS

D22

D10

D21

D9

50%

0

Differential Data

50%

50%

50%

tDATA_jitter

tDATA_jitter

Ideal Data Position

(tPOSn) n = 0, 1, 2..., 14

Clock and Data Jitters - Two Data Channel Case

0

- 14 -

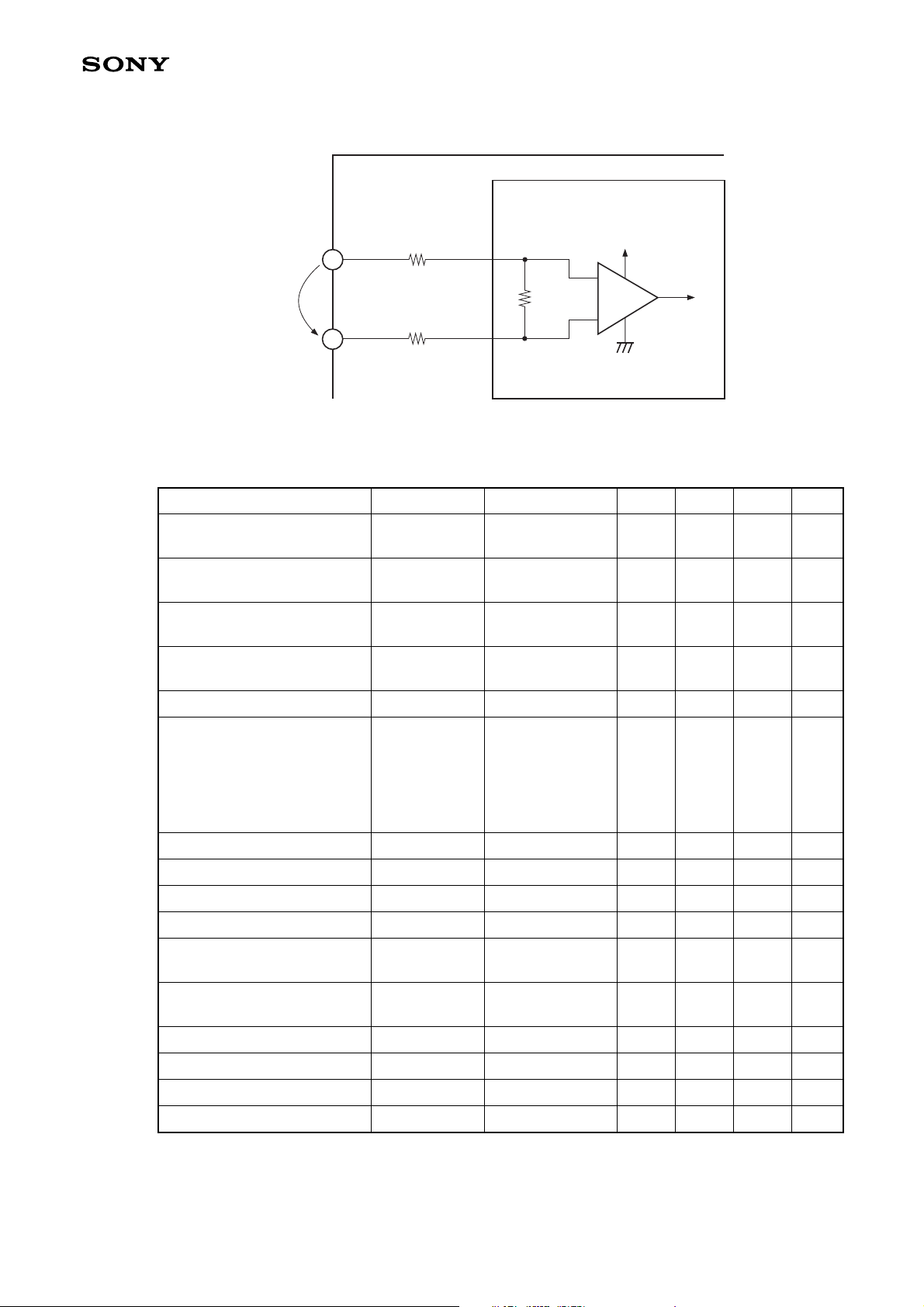

DC Characteristics for FlatLink3G

Module

ACX567AKM-7

IC

V3G_LDO

SS_LVS

V

Vdiff_rx

InP

Rinp

R_rx

InN

Rinn

SubLVDS Receiver

SubLVDS Receiver Electrical Characteristics

Item Symbol Condition Min. Typ. Max. Unit

Input differential voltage range

*1

Input Low level threshold

voltage

*1

Input High level threshold

voltage

*1

Input common mode voltage

*1

range

Common mode ripple

*1

Vdiff_rx 70 — 200

mVp-p

VTHL –40 — — mV

VTHH — — 40 mV

Vcm_rx 0.6 0.9 1.2 V

Vcm_rx_ripple –75 — 75 mV

Rinp: 2 (min),

3 (typ),

Differential termination

resistor

R_rx

7.5 (max)

Rinn: 2 (min),

80 100 120

3 (typ),

7.5 (max)

Self bias resistor R_self — — 500 k

*1

Vdiff_rx rise time (20-80%)

Vdiff_rx fall time (20-80%)

tr — — 800 ps

*1

tf — — 800 ps

Operating frequency — — 225 MHz

Amplitude mismatch

(Vdiff _tx/Vdiff_tx)

*2

Common mode mismatch

(Vcm _tx)

Rise time difference

Fall time difference

*3

*4

*4

–10 — 10 %

–0.1 — 0.1 V

–100 — 100 ps

–100 — 100 ps

Input leakage current +/– IIN+/– — — 90 A

Output leakage current +/– IOUT+/– Note — — 3.0 A

Note)

This current is what the host can supply when its differential outputs are in Hi-Z state.

- 15 -

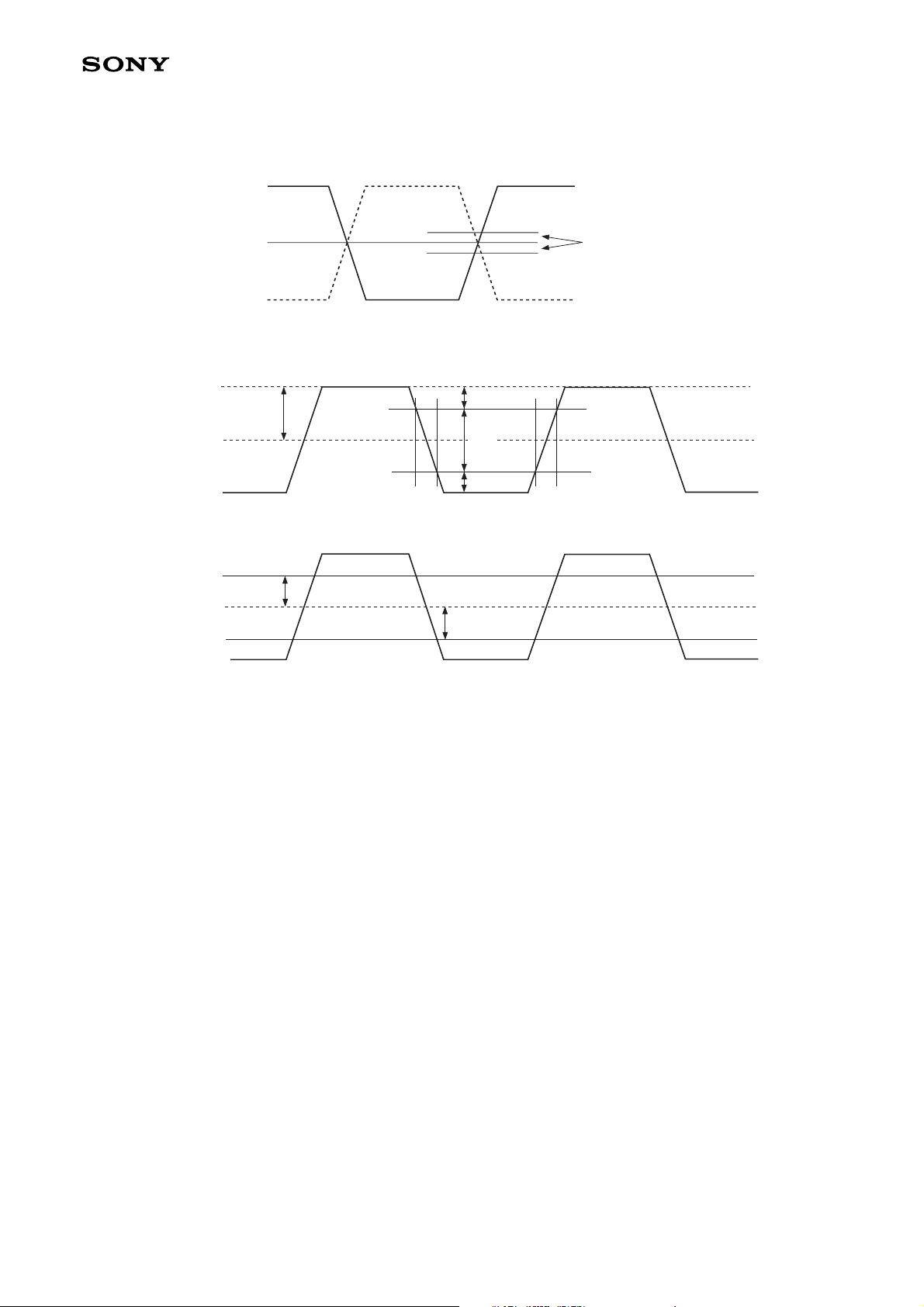

ACX567AKM-7

*1

Single-ended

InP

Vcm_rx

Vdiff_rx

0

0

InN

VTHH

Differential (Inp – InN)

tf

20%

60%

20%

Differential (Inp – InN)

VTHL

Vcm_rx_ripple

tr

Mismatch is Signal Properties at TX Output Causes Same Mismatches to RX Input

- 16 -

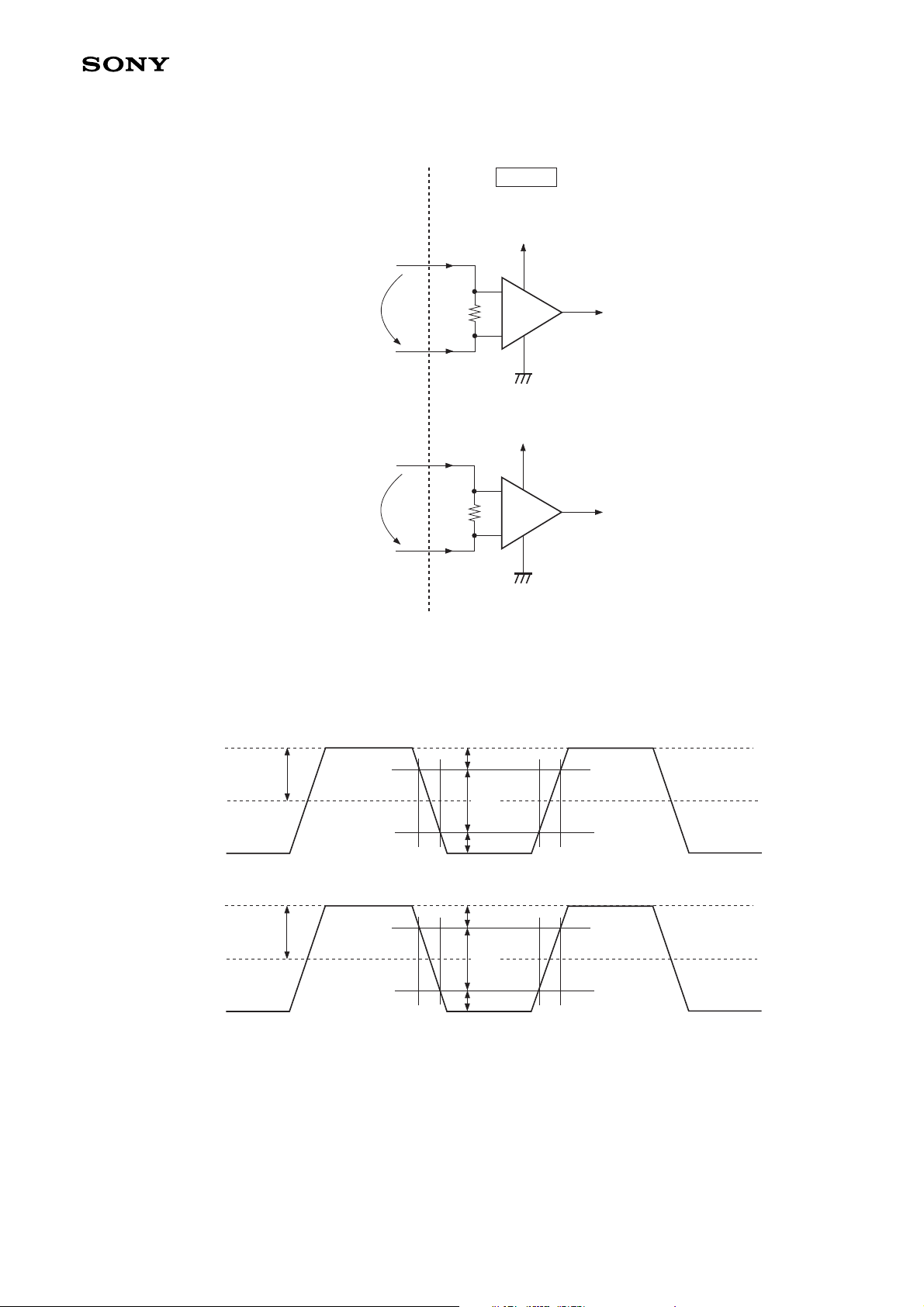

*2

Vdiff_tx = Vdiff_CLK – Vdiff_DATA

*3

Vcm_tx = Vcm_CLK – Vcm_DATA

CLKP

ACX567AKM-7

Receiver

CLK:

VDD

Vdiff_CLK

R_rx

CLKN

DATA:

D0/D1/D2

DATAP

Vdiff_DATA

*4

Rise time difference = tr1 – tr2, Fall time difference = tf1 – tf2

R_rx

DATAN

CLK

Vdiff_CLK

tf1

20%

Out_CLK

GND

VDD

Out_DATA

GND

tr1

0

Vdiff_DATA

0

60%

20%

DATA (D0/D1/D2)

tf2

20%

60%

20%

- 17 -

tr2

ACX567AKM-7

The FlatLink3G receiver is understanding that there is logical “1” when a differential voltage is more than

VTHH and the FlatLink3G receiver is understanding that there is logical “0” when a differential voltage is

more than VTHH. There is undefined state if the differential voltage is less than VTHH and less than VTHH.

A reference figure is below.

Vdiff_rx

0V Reference

for

Differential Inputs

Vdiff_rx

"1"

"0"

"Undefined"

"1""Undefined"

VTHH

CLK+/–, D1+/–, D0+/–

VTHL

Differential Inputs Logical “0”s and “1”s, Threshold High/Low, Differential Voltage Range

The FlatLink3G transmitter can be driven to Hi-Z on the host side, when the FlatLink3G interface is not used.

Therefore, there is implemented pull-down or pull-up resistor(s) (RSELFBIAS) to avoid e.g. unstable

situations for differential inputs of the FlatLink3G receiver.

Therefore, those two examples, which are shown below, are only for reference purposes, when there is

defined an implementation of the pull-up or pull-down resistor(s) (RSELFBIAS).

V3G_LDO

(R_rx)/2

+

(R_rx)/2

Note)

1. R_self is used if a transmitter is not driven Clock (CLK+/–) or Data (D1+/–, D0+/–) channels.

R_self

–

V

SS_LVS

2. R_self can be implemented as pull-up or pull-down.

- 18 -

RGB Interface

General Timing Diagram

ACX567AKM-7

VS

Blanking area (Timing information

that is not possible to see on display)

DE = 0 (Low)

Active area (Image which can

be seen on display)

DE = 1 (High)

HS

Note)

The horizontal and vertical blanking number (also sync widths,

front and back poach number) are unsettled value in this system,

therefore internal synchronization is operated by only DE pulse,

HS and VS are only used reset for H system and V system.

General Timing Diagram

The image information must be correct on the display, when the timings are in range on the interface.

However, the image information can be incorrect on the display, when timings are out of the range on the

interface (Out of the range timings cannot cause any damage on the display module or it cannot cause any

damage on the host side). The correct image information must be displayed automatically (by the display

module) on the next frame (vertical sync.), when there is returned from out of the range to in range interface

timings.

- 19 -

ACX567AKM-7

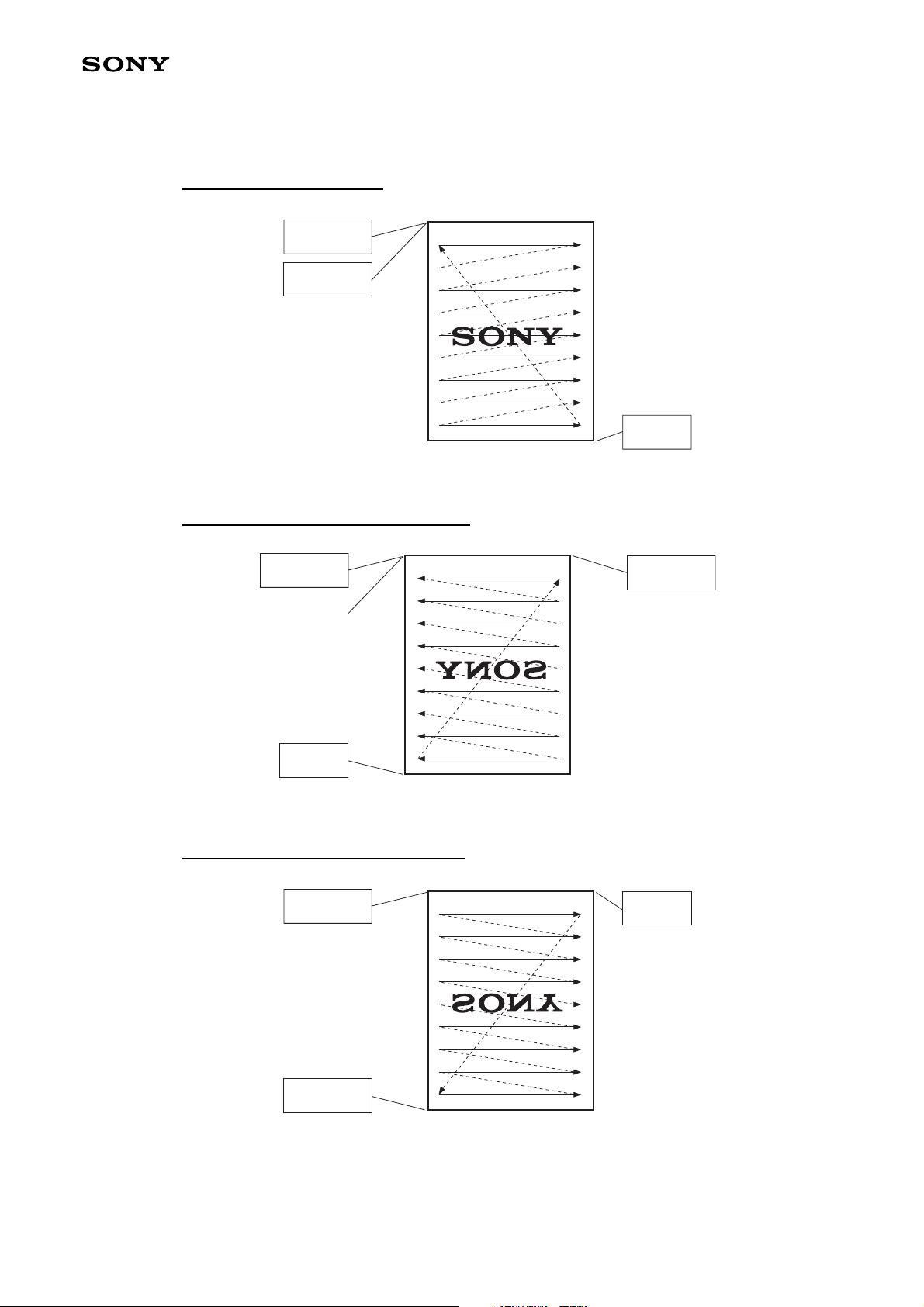

Updating Order on Display Active Area (Normal Display Mode On + Sleep Out)

There is defined different kind of updating orders for Display. These updating orders are controlled by bits.

Normal Scan Direction Mode

Physical point

(0, 0)

Start point

(0, 0)

Updating order when MADCTL's B7 = 0 and B6 = 0

Active area of LCD

Vertical counter (0 - 479)

Horizontal counter (0 - 319)

Left/Right Inversion Scan Direction Mode

Physical point

(0, 0)

Active area of LCD

End point

(319, 479)

Start point

(0, 0)

Vertical counter (0 - 479)

End point

(319, 479)

Horizontal counter (0 - 319)

Updating order when MADCTL's B7 = 0 and B6 = 1

Up/Down Inversion Scan Direction Mode

Physical point

(0, 0)

Vertical counter (0 - 479)

Start point

(0, 0)

Horizontal counter (0 - 319)

Updating order when MADCTL's B7 = 1 and B6 = 0

Active area of LCD

End point

(319, 479)

- 20 -

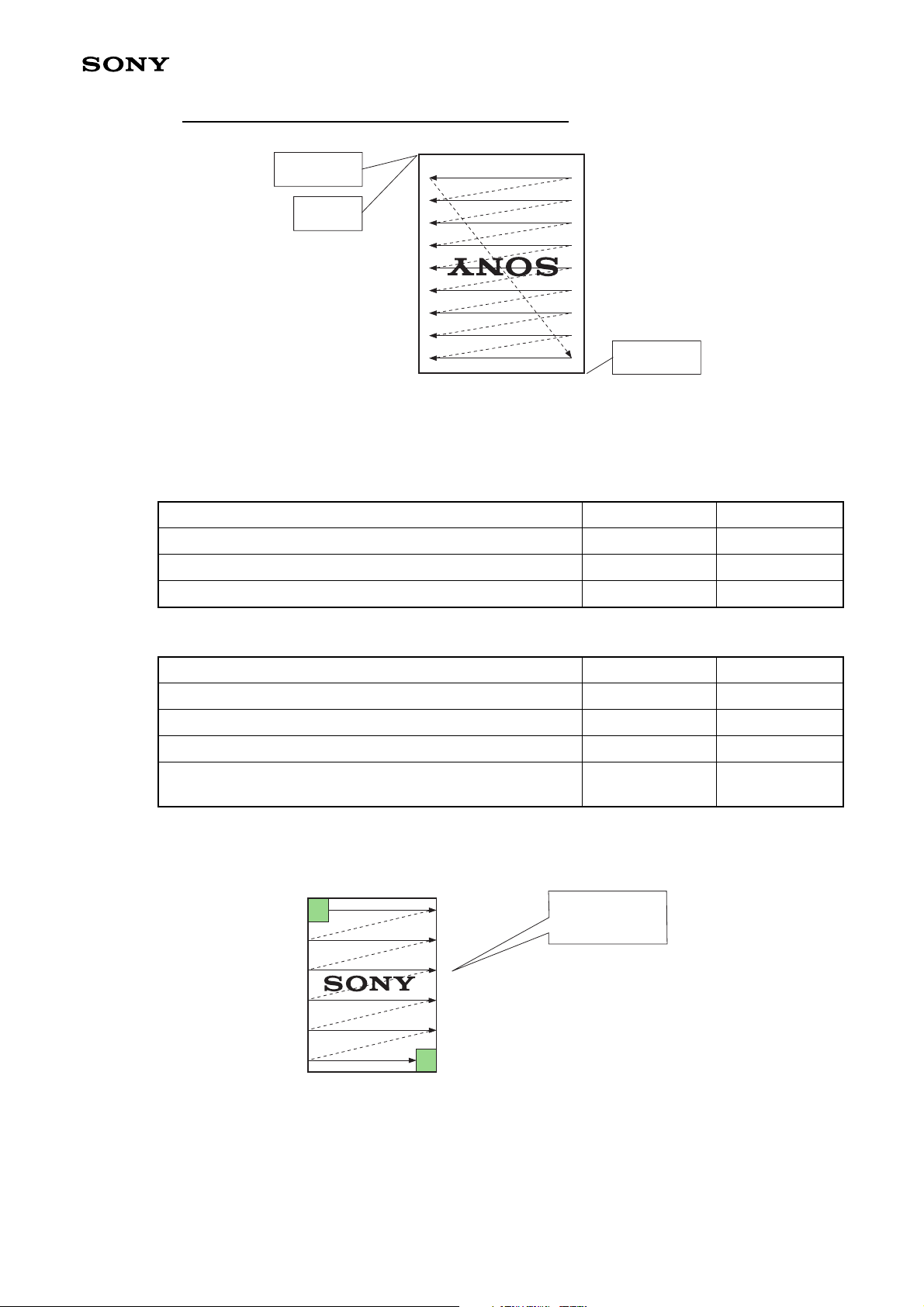

Up/Down and Left/Right Inversion Scan Direction Mode

ACX567AKM-7

Physical point

(0, 0)

End point

(319, 479)

Updating order when MADCTL's B7 = 1 and B6 = 1

Active area of LCD

Vertical counter (0 - 479)

Start point

(0, 0)

Horizontal counter (0 - 319)

Rules for Updating the Display

Condition Horizontal counter Vertical counter

An active VS signal is received Return to 0 Return to 0

Single pixel information of active area is received Increment by 1 No change

An active HS signal is received after a falling edge of DE signal Return to 0 Increment by 1

Rules for Updating Order

Condition Horizontal counter Vertical counter

An active VS signal is received Return to 0 Return to 0

Single pixel information of the active area is received Increment by 1 No change

An active HS signal between two active area lines Return to 0 Increment by 1

The Horizontal counter value is larger than 319 and the vertical

counter value is larger than 479 (In case of 320 480 mode)

Note)

1. Pixel order is RGB on the display.

Return to 0 Return to 0

2. Data streaming direction from the host to the display is described in the following figure.

B

E

Data stream from

Video I/F is

like in this figure.

Data streaming order from RGB I/F

- 21 -

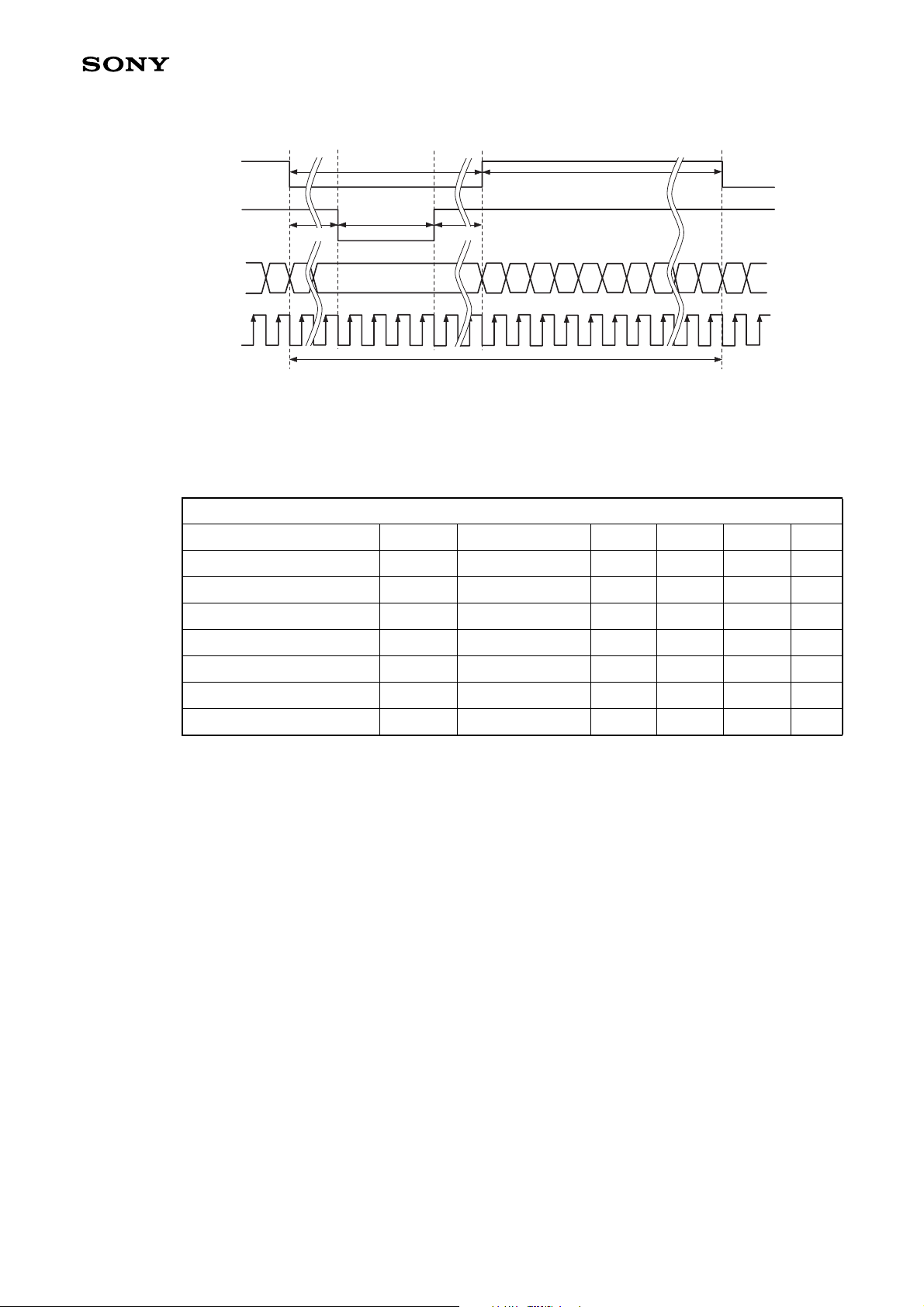

Vertical Timing of RGB Interface (RGB I/F / FlatLink3G)

ACX567AKM-7

VS

Data

DE

HS

VFP

VSW

VBL

VBP

VDISP

VP

Vertical Timing Diagram of RGB Interface (RGB I/F)

Vertical Timing of RGB Interface (320 480 Mode)

(Ta = –30 to +70C, VDDI = 1.65 to 1.95V, VDD = 2.3 to 4.3V, VSS = 0V)

480 Mode

320

Item Symbol Condition Min. Typ. Max. Unit

Vertical cycle VP Normal Mode 486 488 490 lines

Vertical Low pulse width VSW Normal Mode 2 2 4 lines

Vertical front porch VFP Normal Mode 2 3 4 lines

Vertical back porch VBP Normal Mode 2 3 4 lines

Vertical blanking period VBL Normal Mode 6 8 10 lines

Vertical active area VDSIP Normal Mode — 480 — lines

Vertical frequency Normal Mode 50 60 65 Hz

Note)

1. Signal rise and fall times are equal or less than 20ns.

2. Measuring of input signals are using 0.30 V

DDI for Low state and 0.70 VDDI for High state.

3. Data lines can be set to “High” or “Low” during blanking time — Don’t care.

- 22 -

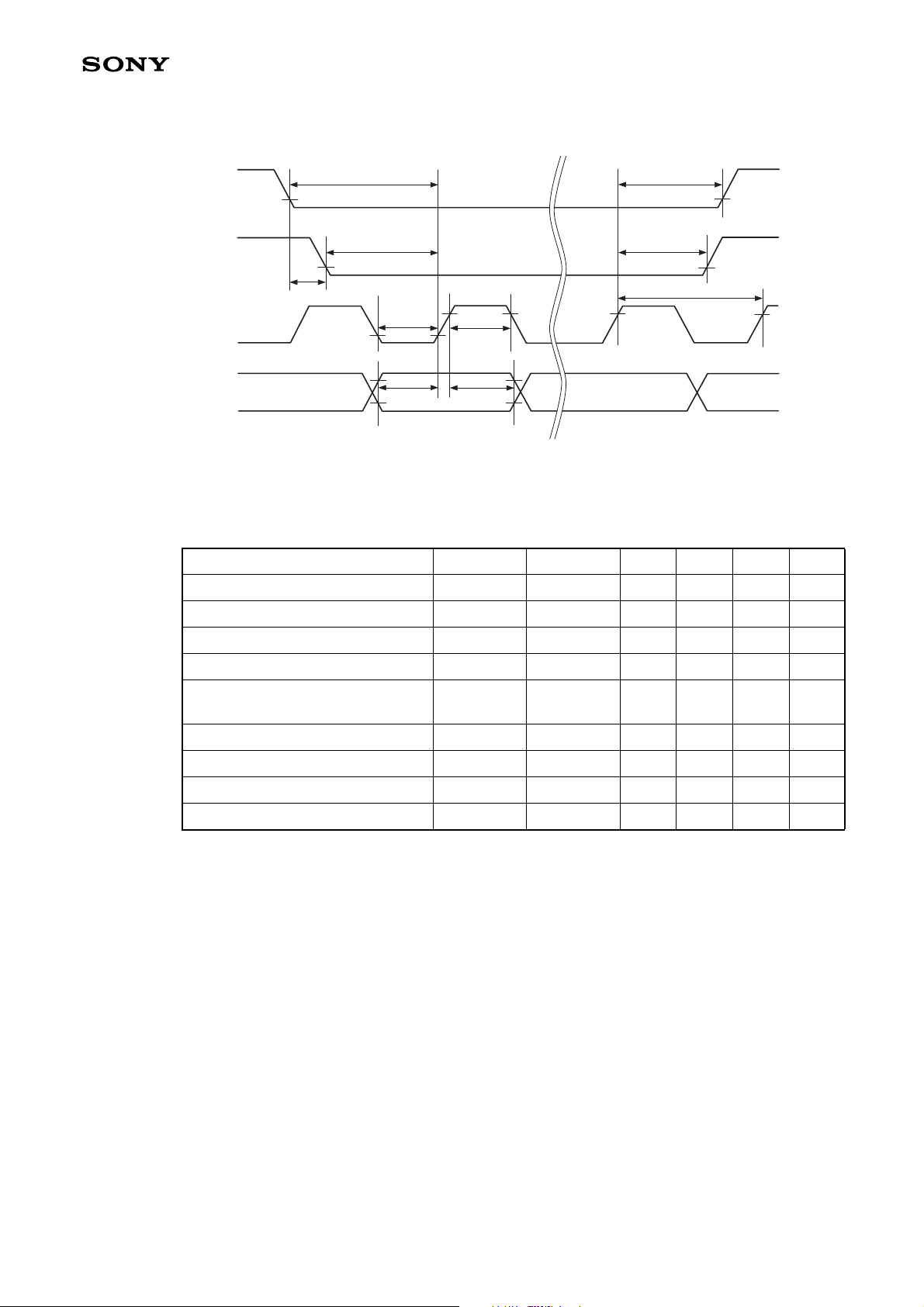

Horizontal Timing of RGB Interface (RGB I/F / FlatLink3G)

ACX567AKM-7

DE

HS

Data

PCLK

HFP

HBL

HDISP

HSW

HBP

HP

Horizontal Timing Diagram of RGB Interface

Horizontal Timing of RGB Interface (320 480 Mode)

(Ta = –30 to +70C, VDDI = 1.65 to 1.95V, VDD = 2.3 to 2.9V, VSS = 0V)

320 480 Mode

Item Symbol Condition Min. Typ. Max. Unit

Horizontal cycle HP Normal Mode 344 352 376 dots

Horizontal Low pulse width HSW Normal Mode 2 4 52 dots

Horizontal front porch HFP Normal Mode 2 16 52 dots

Horizontal back porch HBP Normal Mode 2 12 52 dots

Horizontal blanking period HBL Normal Mode 24 32 56 dots

Horizontal active area HDISP Normal Mode — 320 — dots

Pixel clock frequency PCLK Normal Mode 8.36 10.31 11.98 MHz

Note)

1. Signal rise and fall times are equal or less than 20ns.

2. Measuring of input signals are using 0.30 V

DDI for Low state and 0.70 VDDI for High state.

3. HP is multiples of eight PCLK.

4. Data lines can be set to “High” or “Low” during blanking time — Don’t care.

- 23 -

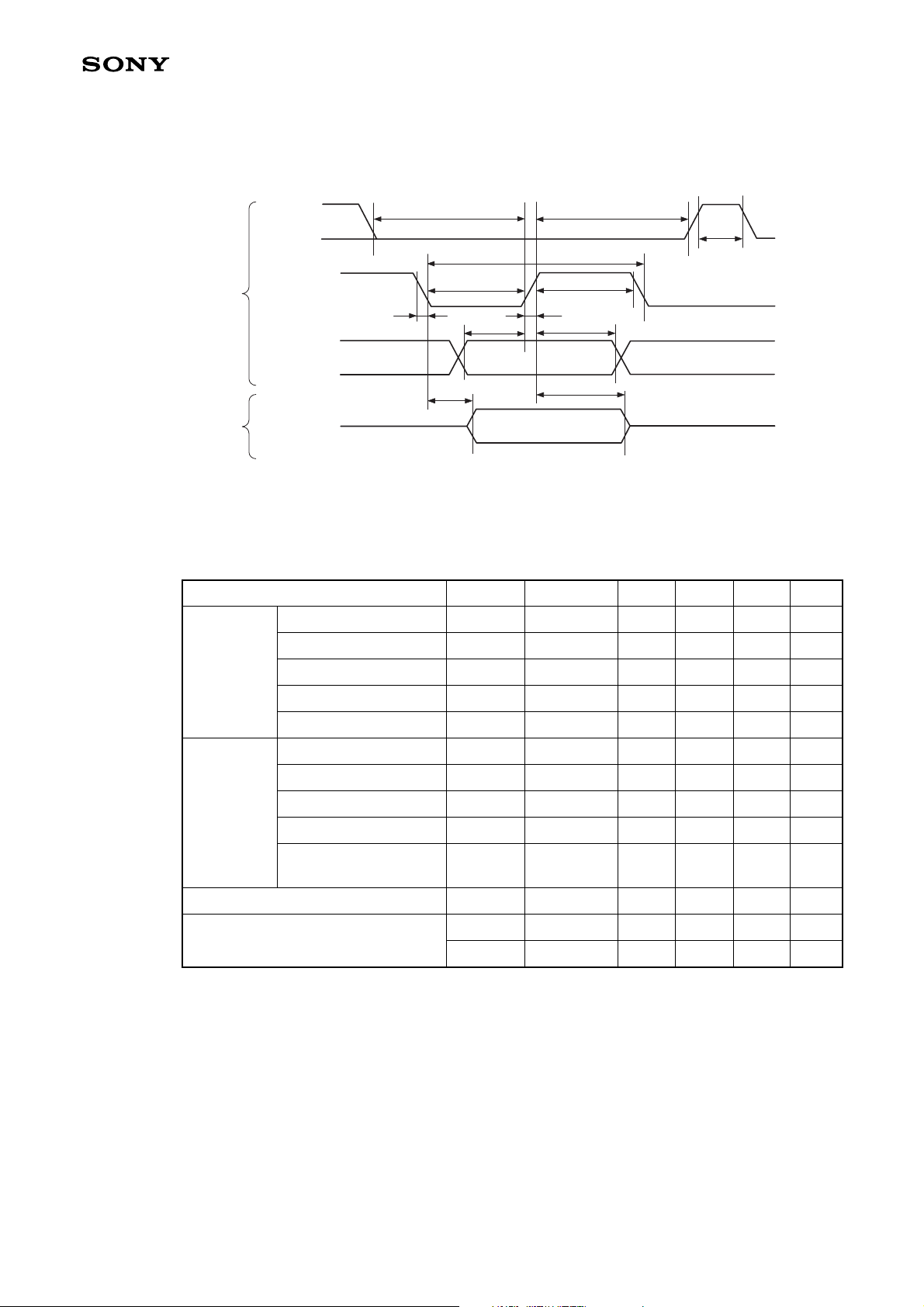

General Timing Diagram of RGB Interface

ACX567AKM-7

VS

HS

PCLK

Data, DE

30%

HVPD

VSSU

30%

30%

70%

30%

HSSU

PCLKL

30%

DSU

70%

PCLKH

DHO

70%

70%

30%

70%

VSHO

30%

HSHO

30%

PCLKCYC

70%

General Timing Diagram of RGB Interface

General Timing of RGB Interface

Item Symbol Condition Min. Typ. Max. Unit

VS setup time VSSU 5 — — ns

VS hold time VSHO 5 — — ns

HS setup time HSSU 5 — — ns

HS hold time HSHO 5 — — ns

Phase difference of sync. signal

falling edge

HVPD — 0 — ns

Pixel clock Low time PCLKL 15 — — ns

Pixel clock High time PCLKH 15 — — ns

Data setup time DSU 5 — — ns

Data hold time DHO 5 — — ns

Note)

1. Signal rise and fall times are equal or less than 20ns.

2. Measuring of input signals are using 0.30 V

DDI for low state and 0.70 VDDI for High state.

- 24 -

Serial Interface

Timing of Serial Interface

ACX567AKM-7

tcsh

tshw

tsdh

toh

Host

Driver

SPI_CS

SPI_CLK

SPI_DI

(Host)

SPI_DO

(Driver)

Hi-Z

tcss

tscyc

tslw

tf

tsds

tacc

tr

Timing Diagram of Serial Interface

Timing of Serial Interface

(Ta = –30 to +70C, VDDI = 1.65 to 1.95V, VDD = 2.3 to 2.9V, VSS = 0V)

Item Symbol Condition Min. Typ. Max. Unit

Serial clock cycle tscyc SPI_CLK 100 — — ns

SCL High pulse width tshw SPI_CLK 35 — — ns

Write mode

SCL Low pulse width tslw SPI_CLK 30 — — ns

tchw

Data setup time (write) tsds SPI_DI 20 — — ns

Data hold time tsdh SPI_DI 20 — — ns

Serial clock cycle tscyc SPI_CLK 150 — — ns

SCL High pulse width tshw SPI_CLK 60 — — ns

Read mode

SCL Low pulse width tslw SPI_CLK 60 — — ns

Access time (Note 1) tacc SPI_DO 10 — 50 ns

Output disable time

(Note 1)

toh SPI_DO 15 — 50 ns

XSC High pulse width tchw SPI_CS 40 — — ns

tcss SPI_CS 30 — — ns

XSC - SCL time

tcsh SPI_CS 35 — — ns

Note)

1. The output signal’s rise and fall times are to be stipulated maximum 15ns.

2. The input signal’s rise and fall times are equal or less than 15ns.

3. Logic High and Low levels of input signals are specified as 0.3 V

DDI for High state.

V

DDI for Low state and 0.7

4. SPI_CLK can be High or Low during off state.

- 25 -

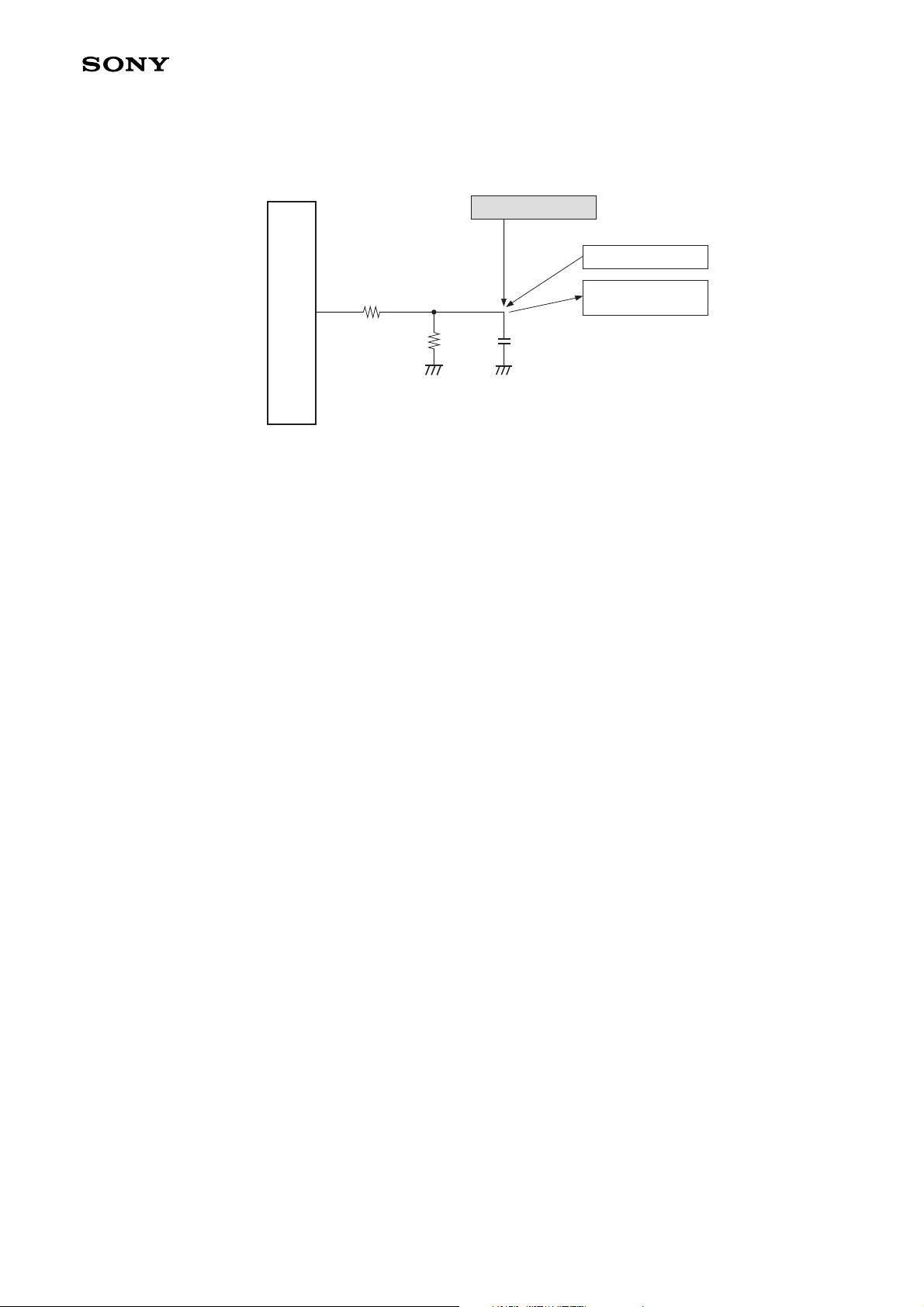

tACC and tOH Measurement Condition for Serial Interface

Measurement Condition and Setup

Measurement point

IC

Measurement Condition and Setup

Note)

Capacitances and resistances of the oscilloscope’s probe must be included in external

components in these measurements.

ACX567AKM-7

Data generator

Oscilloscope

(Note)

- 26 -

Loading...

Loading...