Sony ACX301AKM Datasheet

ACX301AKM

5.1cm (2.0 Type) NTSC/PAL Color LCD Panel (Module with Backlight)

Description

The ACX301AKM is an LCD panel module with

back light developed exclusively for the ACX301AK

5.1cm diagonal active matrix TFT-LCD panel

addressed by low temperature polycrystalline silicon

transistors with built-in peripheral driving circuitry.

This module provides full-color representation for

NTSC and PAL systems. In addition, RGB dots are

arranged in a delta pattern that provides smooth

picture quality without fixed color patterns compared

to vertical stripe and mosaic patterns.

Features

• Number of active dots: 200,000, 5.1cm (2.0 Type) in diagonal

• Horizontal resolution: 440 TV lines

• Center luminance: 250cd/m2(typ.)

• High contrast ratio with normally white mode: 200 (typ.)

• Built-in H and V driving circuitry (built-in input level conversion circuit, 3V drive possible)

• Low voltage, low power consumption: 12V drive: 50mW (panel block, typ.)

0.48W (CCFL∗power consumption, typ.)

∗

Cold cathode fluorecene lamp

• Smooth pictures with a RGB delta arrangement

• Supports NTSC/PAL

• Built-in picture quality improvement circuit

• Up/down and/or right/left inverse display function

• 16:9 screen display function

• LR (low reflectance) surface treatment provides an easy-to-see display even outdoors

• Dirt-resistant surface treatment

• Thin package using a dedicated backlight (5.8mm thick)

• High color reproductivity using a backlight optimum for LCD panels

Element Structure

• Active matrix TFT-LCD panel with built-in peripheral driving circuitry using low temperature polycrystalline

silicon transistors

• Edge-light type backlight using cold cathode tubes

• Number of pixels

Total number of dots: 896 (H) × 230 (V) = 206,080

Number of active dots: 880 (H) × 228 (V) = 200,640

• Module dimensions

Package dimensions: 50.5 (W) × 45.6 (D) × 5.8 (H) (mm)

Effective display dimensions: 40.5 (H) × 30.6 (V) (mm)

Applications

LCD monitors, etc.

– 1 –

E99633A01-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

– 2 –

ACX301AKM

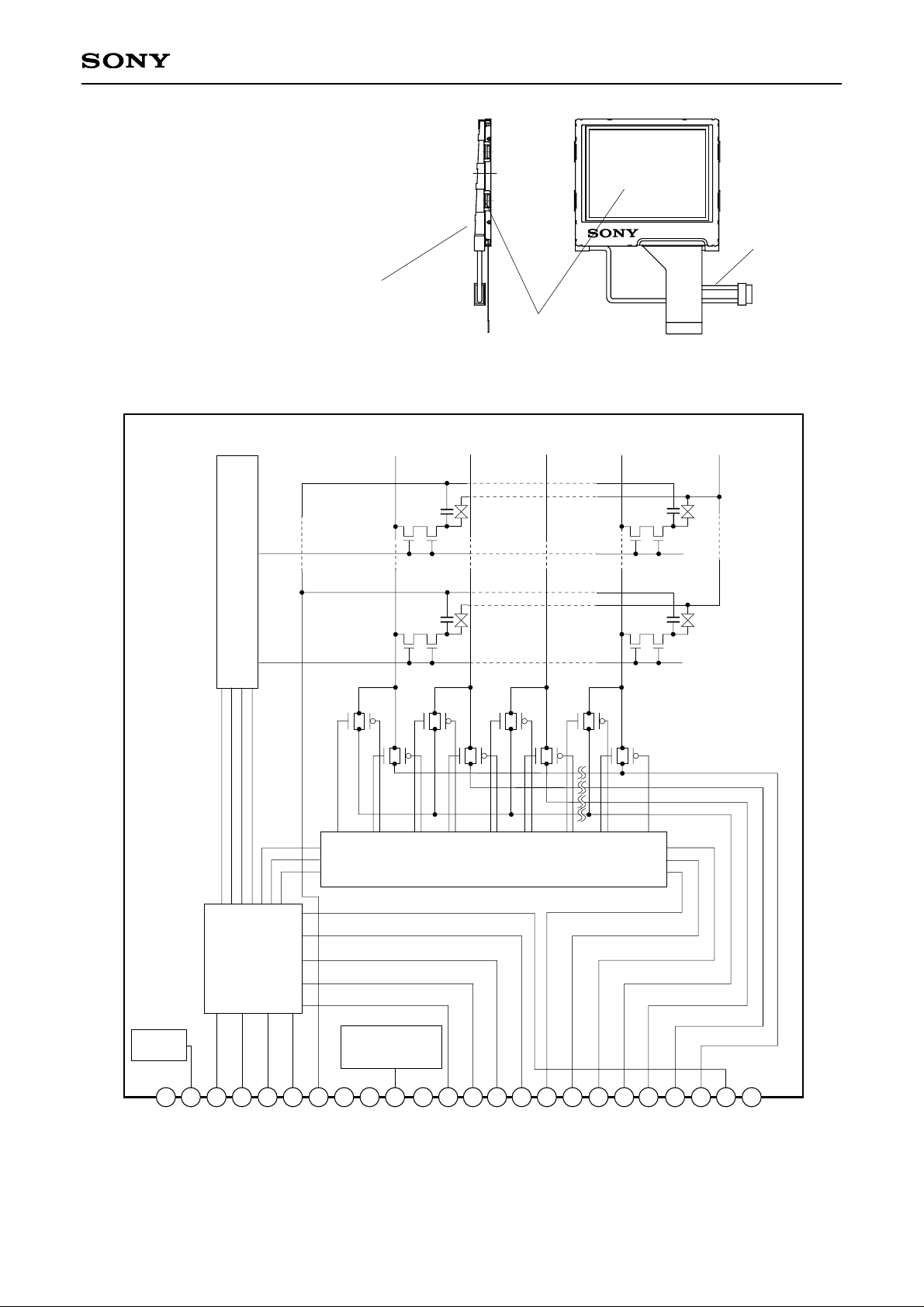

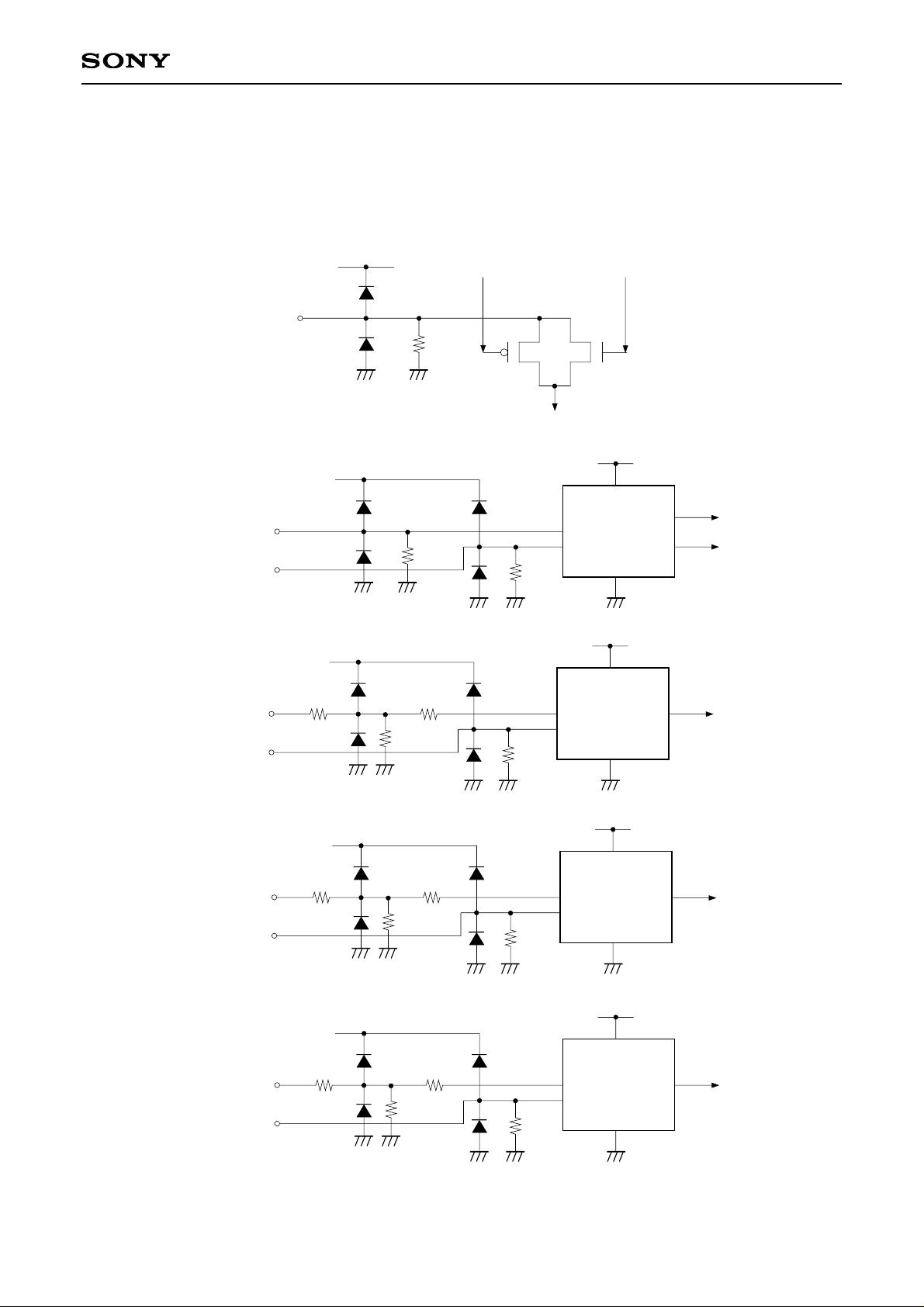

Block Diagram

The panel block diagram is shown below.

LCCS

TESTL

TESTR

COM

VST

VCK

EN

DWN

VV

DD

V

SS

HV

DD

VSSG

TEST2

WIDE

HST

REF

TEST

Cext/Rext

HCK2

HCK1

PSIG

GREEN

RED

BLUE

RGT

COM

2

3

4

5

6

7

8

9

10

11

12

13

14 15

16

18

19

20

21

22

23

1

24

17

V Shift Register

H, V Level

Shifter

Negative Voltage

Generation Circuit

Common

Voltage

H Shift Register

LCD panel

ACX301AK

Backlight block

harness

Integrated type

dedicated backlight

Module Configuration

This module is comprised of a 2.0 Type 200,000dot color TFT-LCD panel (ACX301AK) combined

with an integrated type dedicated backlight as

shown in the figure on the right.

– 3 –

ACX301AKM

Absolute Maximum Ratings (Vss = 0V)

• H driver supply voltage HVDD, Cext/Rext –1.0 to +17 V

• V driver supply voltage VVDD –1.0 to +15 V

• V driver negative supply voltage VSSG –3.0 to +1.0 V

• Common voltage of panel COM –1.0 to +17 V

• H driver input pin voltage HST, HCK1, HCK2, RGT, WIDE –1.0 to +17 V

• V driver input pin voltage VST, VCK, EN, DWN, REF –1.0 to +15 V

• Video signal, uniformity improvement signal input pin voltage

GREEN, RED, BLUE, PSIG –1.0 to +13 V

• Operating temperature Topr –10 to +60 °C

• Storage temperature Tstg –30 to +85 °C

• Storage humidity Hstg 40°C 95% RH

• CCFL voltage Vcfl 2.0 kVp-p

• CCFL current Icfl 4 mArms

Operating Conditions of Panel Block

1. Input/output supply voltage conditions

∗1

(VSS = 0V)

Item

Supply voltage

HVDD

VVDD

Cext/Rext

∗2

VSSG

Rext

11.4

11.4

HVDD – 3.4

–2.3

—

12.0

12.0

12.0

–1.8

10

14.0

14.0

—

–1.5

160

V

V

V

V

kΩ

VSSG output voltage setting

∗3

Resistor connected to Cext/Rext pin

∗2

Symbol

Min. Typ.

Max.

Unit

∗1

The HVDD/VVDD typical voltage setting is noted as 12.0V in these specifications.

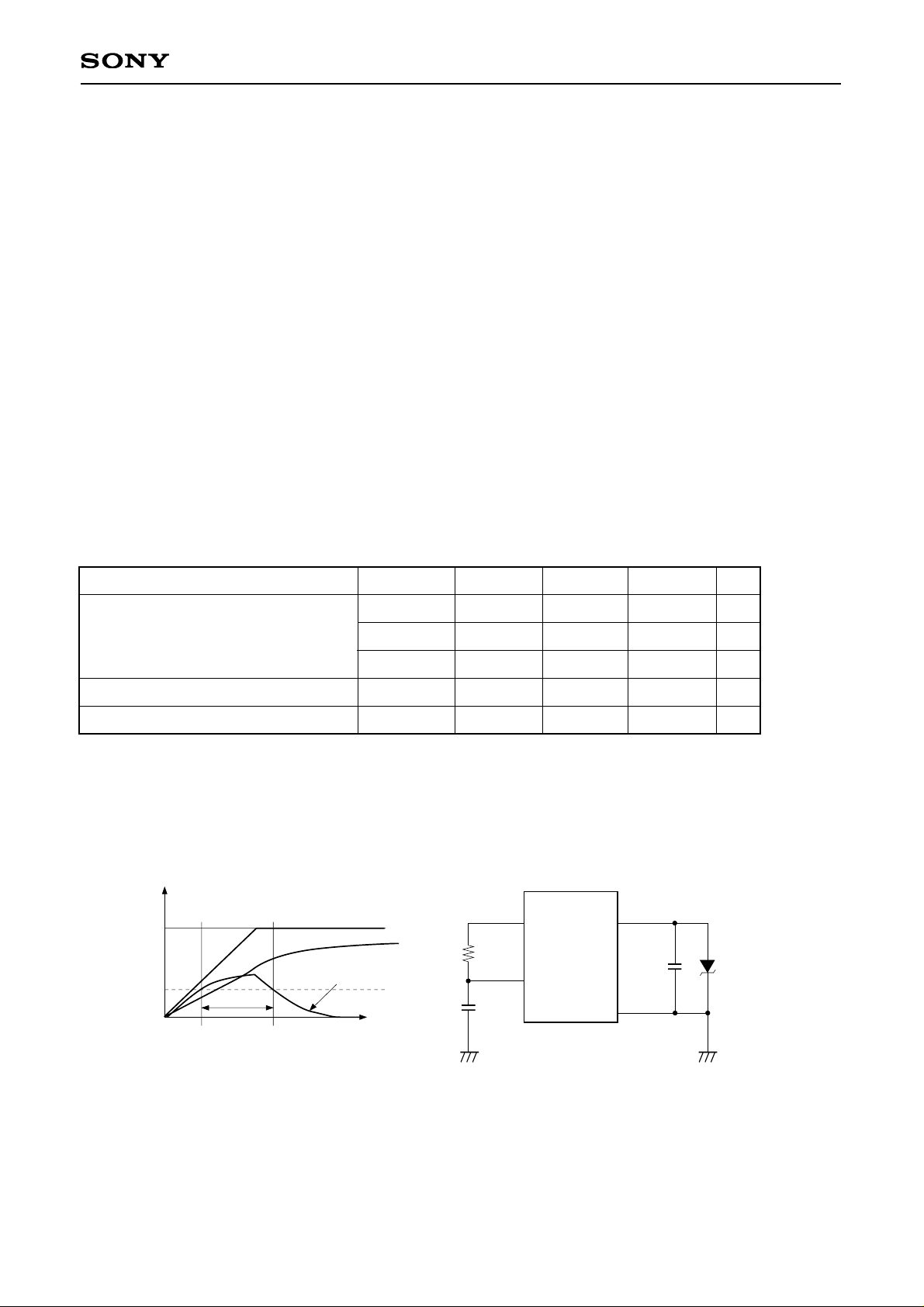

∗2

Connect the resistor and capacitor to the Cext/Rext pin as shown in the figure below.

∗3

For the VSSG output setting, connect an external smoothing capacitor and a voltage stabilizing Zener diode

as shown in the figure below.

HVDD – Cext/Rext

Cext/Rext

HVDD

HVDD

7

Voltage

Time

text

Set a Cext and a Rext value that

satisfies

text > 1ms for the period

HVDD – Cext/Rext > 7V.

Cext/Rext constant setting condition

Rext

ACX301AKM

HV

DD

VSSG

V

SS

Cext/Rext

1µF

Use a Zener

voltage of 2.7V.

(RD2.7UM is

recommended)

Cext

– 4 –

ACX301AKM

∗4

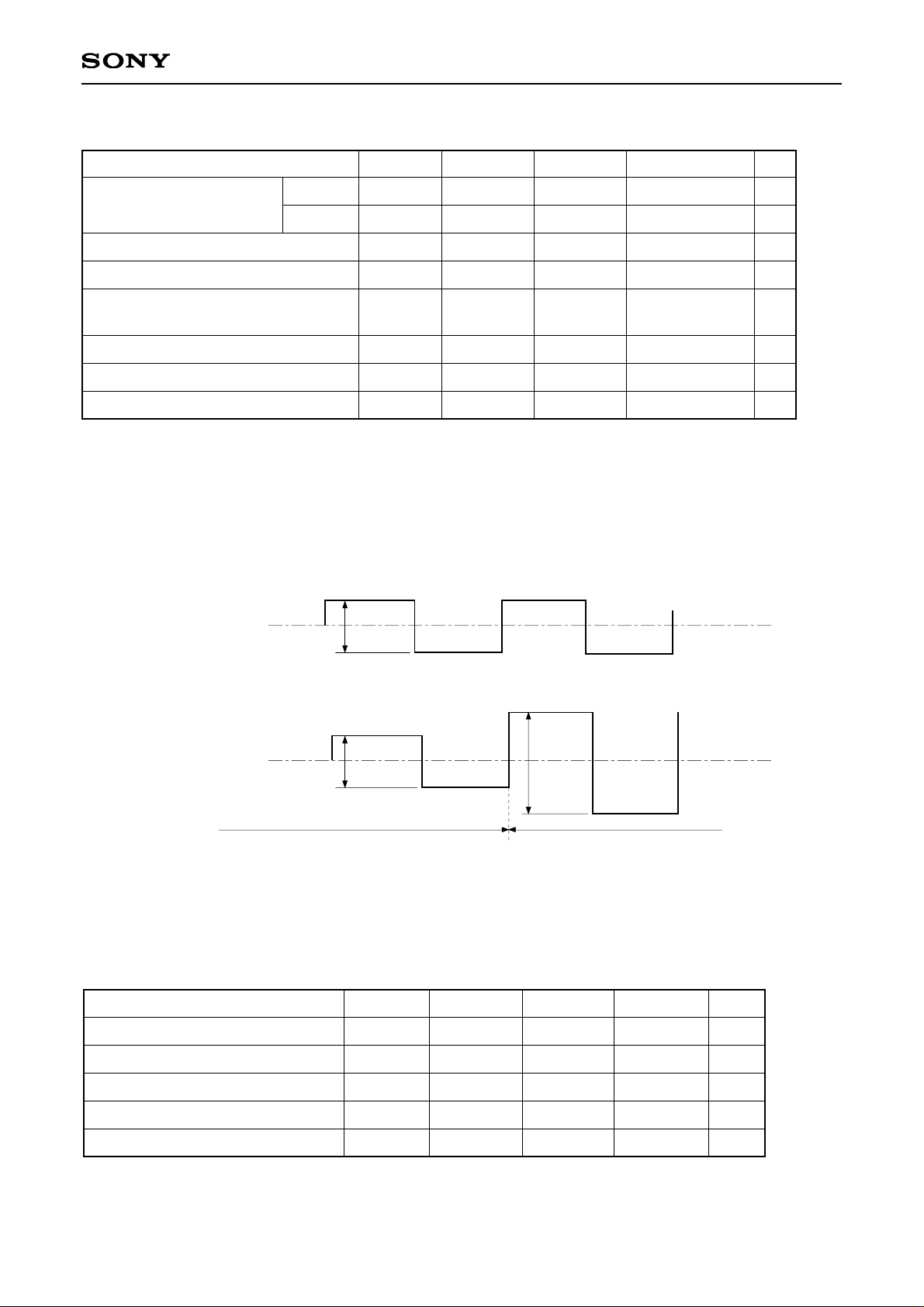

Input video and uniformity improvement signals should be symmetrical to VVC.

The input conditions for the uniformity improvement signal Vpsig differ for 4:3 display and 16:9 display.

1) During 4:3 display, input the voltage amplitude symmetrical to VVC as shown in Fig. 1.

2) During 16:9 display, input the same signal amplitude as in 1) above during the effective display portion,

and input the black signal level VpsigBK during the top/bottom black input portion as shown in Fig. 2.

During 4:3 display

PSIG waveform

VVC

Vpsig

During 16:9 display

PSIG waveform

VVC

Vpsig VpsigBK

VVC ± 4.0V

VVC ± 2.5V

Top/bottom black display portion

(letterbox portion)

Effective display portion

Fig. 1

Fig. 2

Item

Lighting start voltage (Ta = –10°C)

Driving frequency

CCFL voltage (Ta = 25°C)

CCFL current (Ta = 25°C)

Wire harness applied voltage

Vstart

Fcfl

VLcfl

ILcfl

Vlmax

—

50

180

1.0

—

—

—

200

2.4

—

640

100

220

4.0

2.0

Vrms

kHz

Vrms

mArms

kVp-p

Symbol

Min.

Typ.

Max.

Unit

Operating Conditions of Backlight Block

Input supply voltage conditions

Item

H/V driver input voltage

(Low)

(High)

VIL

VIH

VREF

VVC

Vsig

Vpsig

VpsigBK

Vcom

–0.3

2.6

VIH/2 – 0.3

5.3

1.0

VVC ± 2.3

VVC – 0.55

0.0

3.0

VIH/2

5.5

VVC ± 4.0

VVC ± 2.5

VVC ± 4.0

VVC – 0.4

0.3

5.5

VIH/2 + 0.3

5.7

VV

DD – 2.0

(however, 10V or less)

VVC ± 2.7

VVC ± 4.5

VVC – 0.25

V

V

V

V

V

V

V

V

REF input voltage

Video signal center voltage

Video signal input range

Uniformity improvement signal

16:9 display top/bottom black signal

∗4

Common voltage of panel (Ta = 25°C)

Symbol Min. Typ. Max. Unit

2. Panel input signal voltage conditions (VSS = 0V)

– 5 –

ACX301AKM

Pin

No.

1

2

3

4

5

6

7

8

9

10

11

12

TESTL

COM

VST

VCK

EN

DWN

VV

DD

VSS

HVDD

VSSG

TEST2

WIDE

13

14

15

16

17

18

19

20

21

22

23

24

HST

REF

TEST

Cext/

Rext

HCK2

HCK1

PSIG

GREEN

RED

BLUE

RGT

TESTR

Start pulse input for H shift register

drive

Level shifter circuit REF voltage

input

Panel test output; no connection

Time constant power supply input

for H shift register drive

Clock input for H shift register drive

Clock input for H shift register drive

Uniformity improvement signal input

Video signal (G) input to panel

Video signal (R) input to panel

Video signal (B) input to panel

H shift register drive direction signal

input

Panel test output; no connection

Symbol Description

Pin

No.

Symbol Description

Panel test output; no connection

Common voltage input of panel

Start pulse input for V shift register

drive

Clock input for V shift register drive

Gate selection pulse enable input

V shift register drive direction signal

input

Power supply input for V driver

H and V driver GND

Power supply input for H driver

Negative power supply setting for

V driver

No connection inside the panel.

(with 1MΩ terminating resistor)

Pulse input for 16:9 mode

Pin Description of Panel Block

Pin

No.

1 CH 4 CL CCFL low voltage side connection

Symbol Description

Pin

No.

Symbol Description

CCFL high voltage side connection

Pin Description of Backlight Block

– 6 –

ACX301AKM

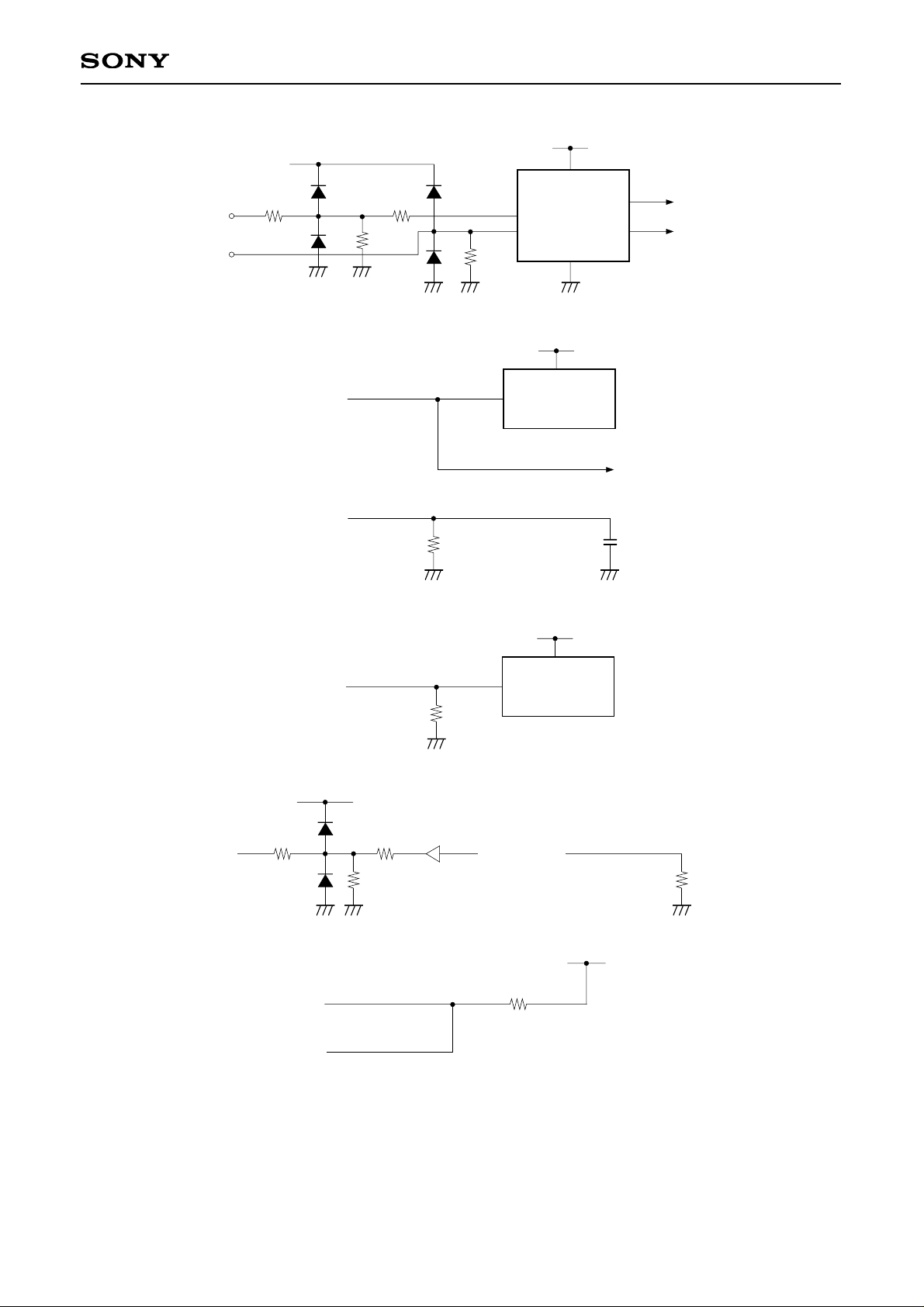

Input Equivalent Circuits of Panel Block

To prevent static charges, protective diodes are provided for each pin except the power supplies. In addition,

protective resistors are added to all pins except the video signal input pins. All pins are connected to VSS with a

high resistance of 1MΩ (typ.). The equivalent circuit of each input pin is shown below: (Resistor value: typ.)

(1) RED, GREEN, BLUE, PSIG

HVDD

1MΩ

Input

Signal line

(2) HCK1, HCK2

1MΩ

1MΩ

HV

DD

HVDD

HCK1

HCK2

H level shifter and

shift register circuit

(3) HST, WIDE, REF

1MΩ

350Ω

1MΩ

350Ω

HV

DD

HVDD

Input

REF

Level conversion

circuit

(4) RGT, REF

1MΩ

2kΩ

1MΩ

2kΩ

HV

DD

HVDD

Input

REF

Level conversion

circuit

(5) VST, VCK, EN, REF

1MΩ

800Ω

1MΩ

800Ω

VV

DD

VVDD

Input

REF

Level conversion

circuit

– 7 –

ACX301AKM

(10) TEST/TEST2

HVDD

TEST

350Ω

1MΩ

350Ω

TEST2

1MΩ

(11) TESTL, TESTR

TESTL

TESTR

VVDD

1.5MΩ

(6) DWN, REF

1MΩ

1MΩ

VV

DD

VVDD

Input

REF

2kΩ2kΩ

Level conversion

circuit

(7) VSSG

HVDD

VSSG

Negative voltage

generation circuit

(8) COM

1MΩ

Input

LC

(9) Cext/Rext

HVDD

Cext/Rext

H driver

1MΩ

– 8 –

ACX301AKM

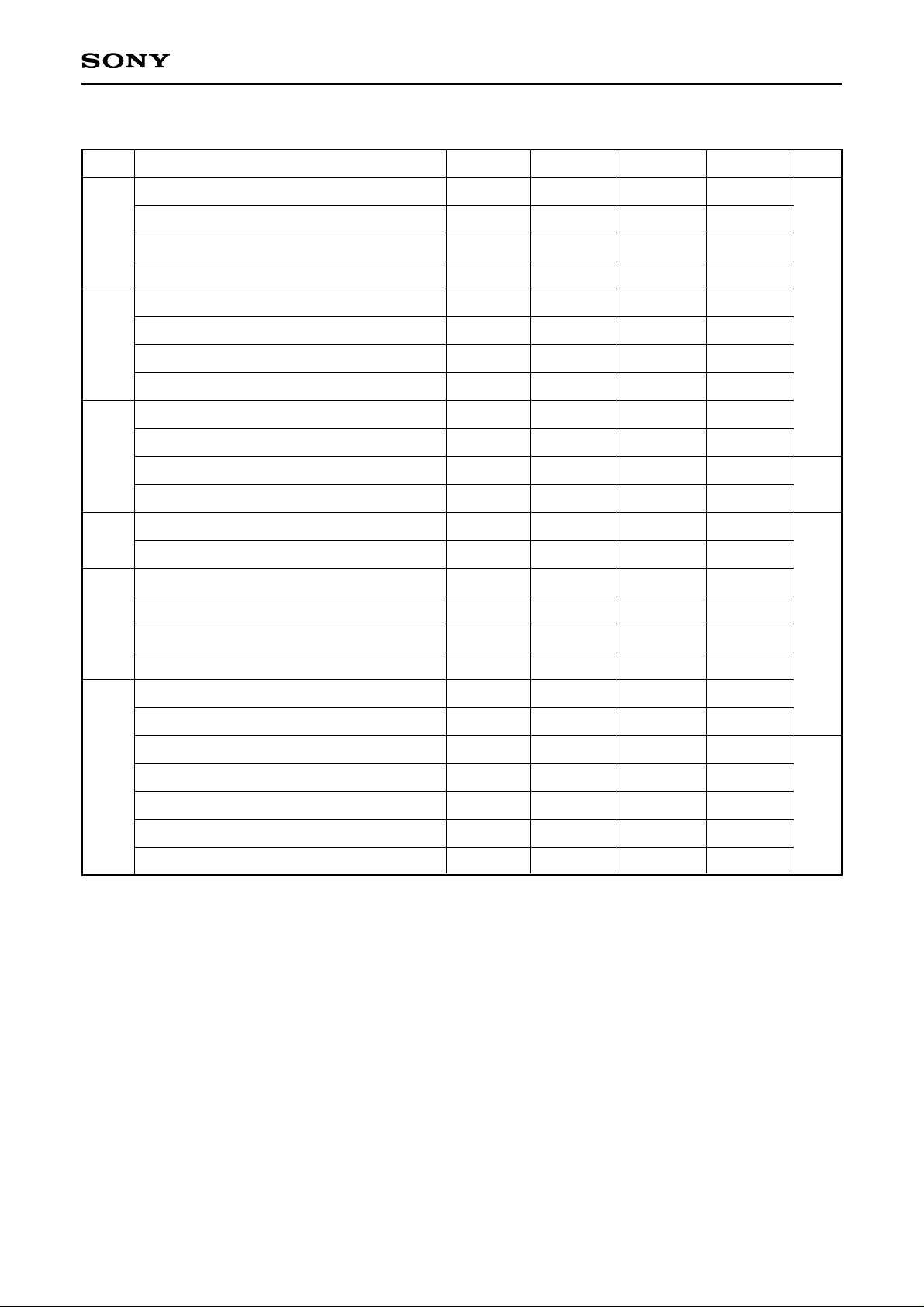

Clock Timing Conditions of Panel Block (VIH = 3.0V, HVDD = VVDD = 12V, Ta = 25°C)

HST rise time

HST fall time

HST data setup time

HST data hold time

HCKn∗5rise time

HCKn∗5fall time

HCK1 fall to HCK2 rise time

HCK1 rise to HCK2 fall time

VST rise time

VST fall time

VST data setup time

VST data hold time

VCK rise time

VCK fall time

EN rise time

EN fall time

EN fall to VCK rise/fall time

EN pulse width

WIDE rise time

WIDE fall time

WIDE (H) rise to VCK rise/fall time

WIDE (H) pulse width

WIDE (V) pulse width

WIDE (V) fall to EN rise time

EN rise to WIDE (V) fall time

trHst

tfHst

tdHst

thHst

trHckn

tfHckn

to1Hck

to2Hck

trVst

tfVst

tdVst

thVst

trVckn

tfVckn

trEn

tfEn

tdEn

twEn

trWide

tfWide

tdhWide

twhWide

twvWide

tov1Wide

tov2Wide

—

—

137

–30

—

—

–15

–15

—

—

30

–30

—

—

—

—

2400

5400

—

—

0.9

2.8

1928

25

25

—

—

167

0

—

—

0

0

—

—

32

–32

—

—

—

—

2500

5500

—

—

1.1

3.0

1933

32

32

30

30

197

30

30

30

15

15

100

100

34

–34

100

100

100

100

2600

5600

100

100

1.3

3.3

1938

—

—

ns

µs

µs

ns

Item

Symbol

Min. Typ. Max. Unit

HST

HCK

VST

VCK

EN

WIDE

∗5

HCKn means HCK1 and HCK2. (fHCKn = 3.0MHz)

Loading...

Loading...