SONY 249A Service Manual

24C02/24C04

Two-Wire Serial EEPROM

Preliminary datasheet 2K (256 X 8)/4K (512 X 8)

Features

Low-voltage and Standard-voltage Operation

– 1.8 (VCC = 1.8V to 5.5V)

Operating Ambient Temperature: -40°C to

+85°C

Internally Organized 256 X 8 (2K), 512 X 8

(4K)

Two-wire Serial Interface

Schmitt Trigger, Filtered Inputs for Noise

Suppression

Bidirectional Data Transfer Protocol

1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V)

General Description

The 24C02 / 24C04 provides 2048/4096 bits of

serial electrically erasable and programmable

read-only memory (EEPROM) organized as

256/512 words of 8 bits each The device is

optimized for use in many industrial and

commercial applications where low-power and

low-voltage operation are essential. The 24C02 /

Compatibility

Write Protect Pin for Hardware Data Protection

8-byte Page (2K), 16-byte Page (4K) Write

Modes

Partial Page Writes Allowed

Self-timed Write Cycle (5 ms max)

High-reliability

– Endurance: 1 Million Write Cycles

– Data Retention: 100 Years

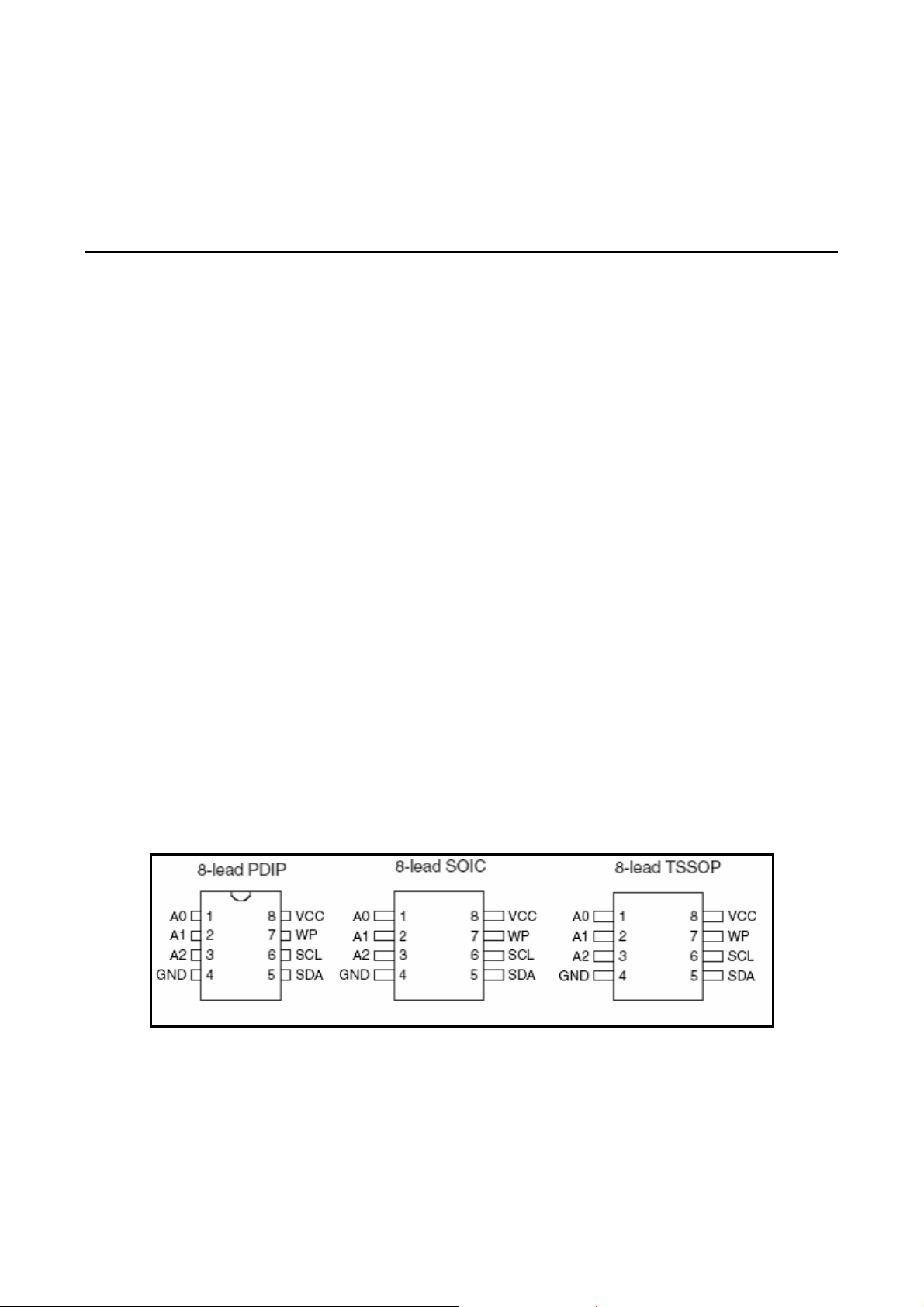

8-lead PDIP, 8-lead JEDEC SOIC and 8-lead

TSSOP Packages

24C04 is available in space-saving 8-lead PDIP,

8-lead JEDEC SOIC, and 8-lead TSSOP packages

and is accessed via a Two-wire serial interface. In

addition, the 24C02 / 24C04 is available in 1.8V

(1.8V to 5.5V) version.

Pin Configuration

1/15 MRD

24C02/24C04

Pin Descriptions

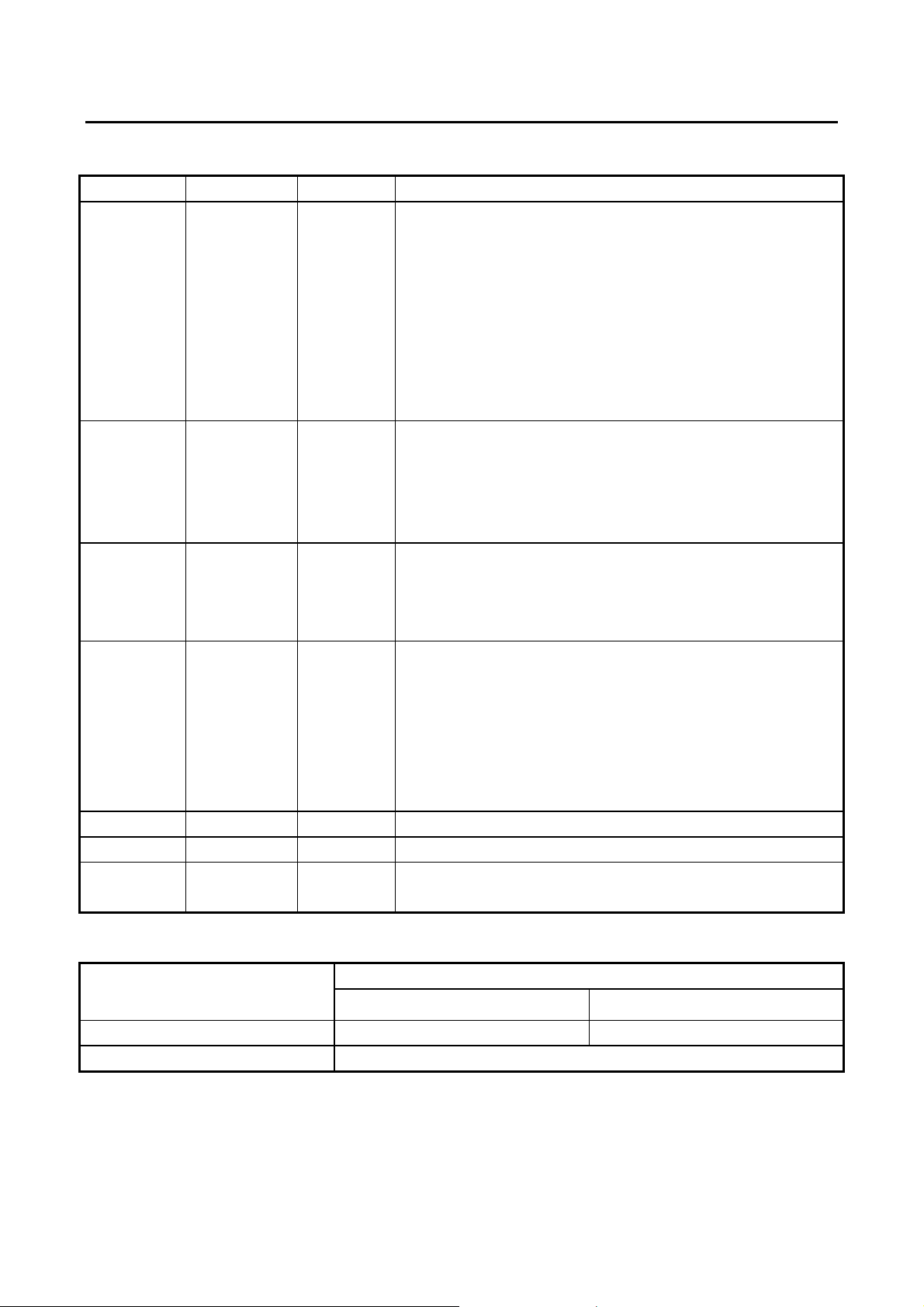

Pin number Designation Type Name and Functions

Address Inputs

DEVICE/PAGE ADDRESSES (A2, A1, A0) : The A2, A1 and

A0 pins are device address inputs that are hard wired for the

24C02. eight 2K devices may be addressed on a single bus

1 – 3

5

6

7

4

8

1

Table 1: Write Protect

A0 - A2

SDA

SCL I

WP I

GND P Ground

VCC P Power Supply

NC NC

I

I/O

&

Open-drain

system (device addressing is discussed in detail under the

Device Addressing section).

The 24C04 uses the A2 and A1 inputs for hard wire addressing

and a total of four 4K devices may be addressed on a single

bus system. The A0 pin is a no connect.

Serial Data

SERIAL DATA (SDA): The SDA pin is bi-directional for serial

data transfer. This pin is open-drain driven and may be

wire-ORed with any number of other open-drain or opencollector devices.

Serial Clock Input

SERIAL CLOCK (SCL): The SCL input is used to positive edge

clock data into each EEPROM device and negative edge clock

data out of each device.

Write Protect

WRITE PROTECT (WP): The 24C02/24C04 has a Write

Protect pin that provides hardware data protection. The Write

Protect pin allows normal read/write operations when

connected to ground (GND). When the Write Protect pin is

connected to VCC, the write protection feature is enabled and

operates as shown in the following Table 1.

No Connect

For 24C04.

WP Pin Status:

24C02 24C04

At VCC Full (2K) Array Full (4K) Array

At GND Normal Read/Write Operations

2/15 MRD

Part of the Array Protected

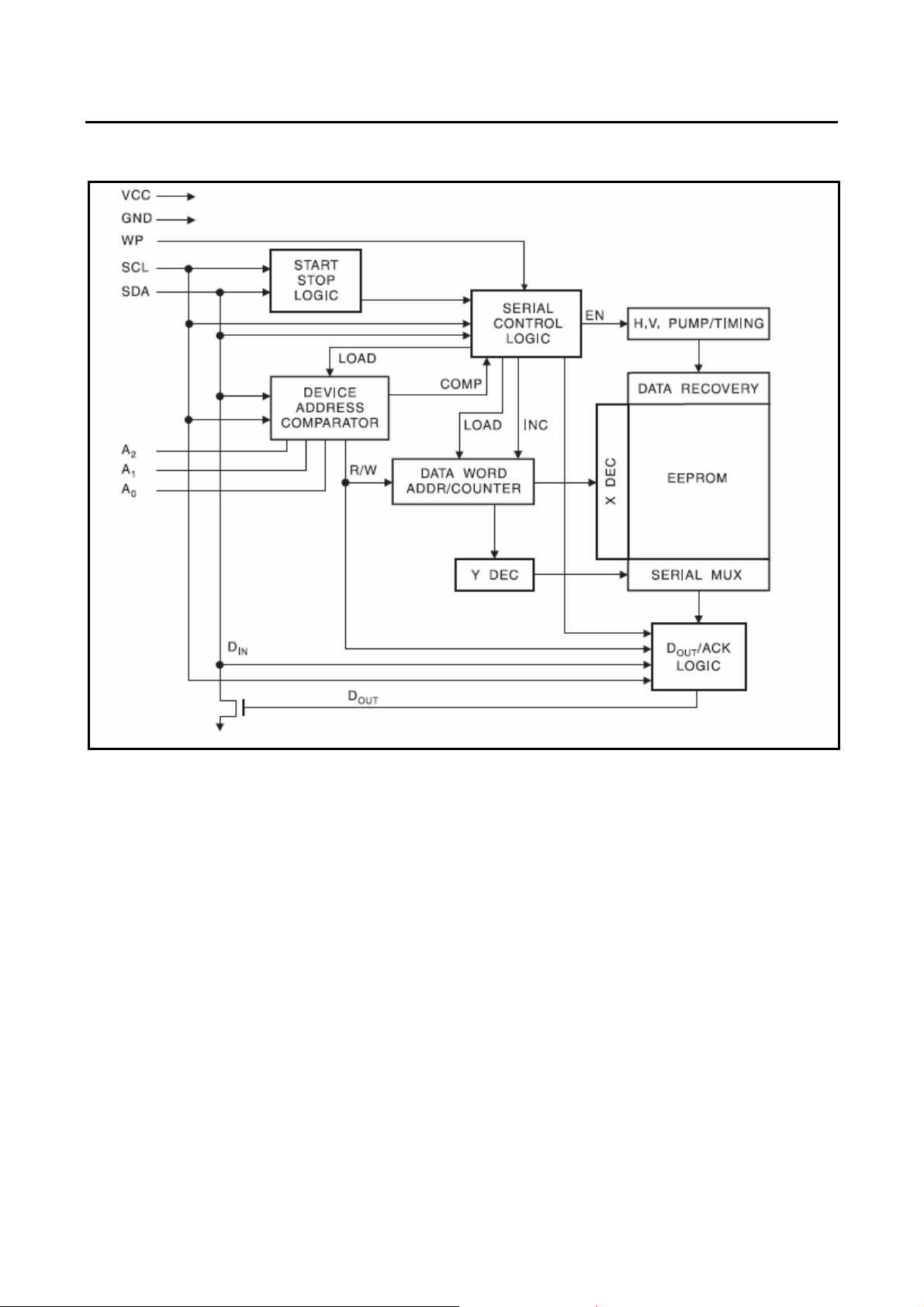

Block Diagram

24C02/24C04

3/15 MRD

24C02/24C04

Functional Description

1. Memory Organization

24C02, 2K SERIAL EEPROM: Internally organized with 32 pages of 8 bytes each, the 2K requires an 8-bit

data word address for random word addressing.

24C04, 4K SERIAL EEPROM: Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit

data word address for random word addressing.

2. Device Operation

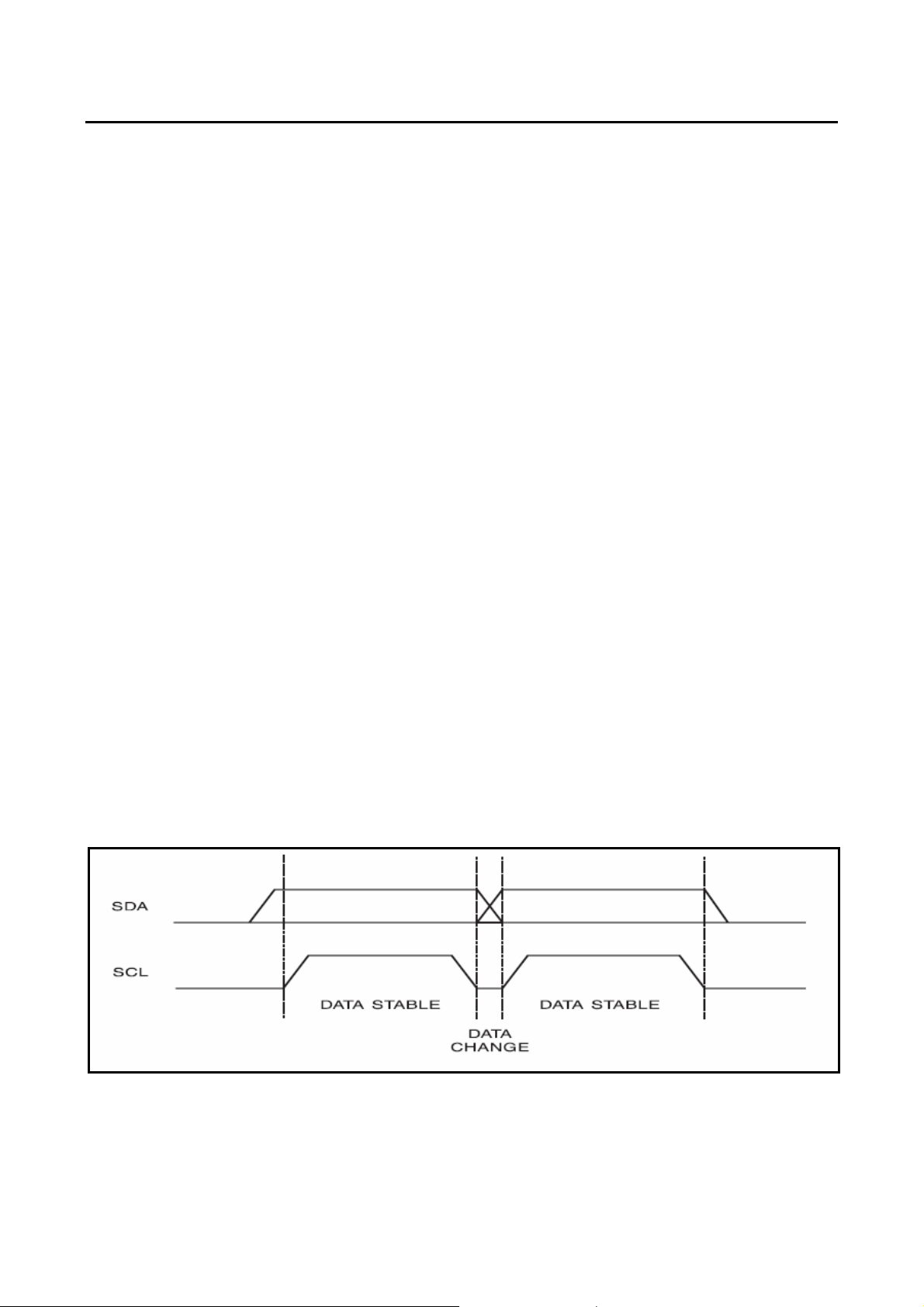

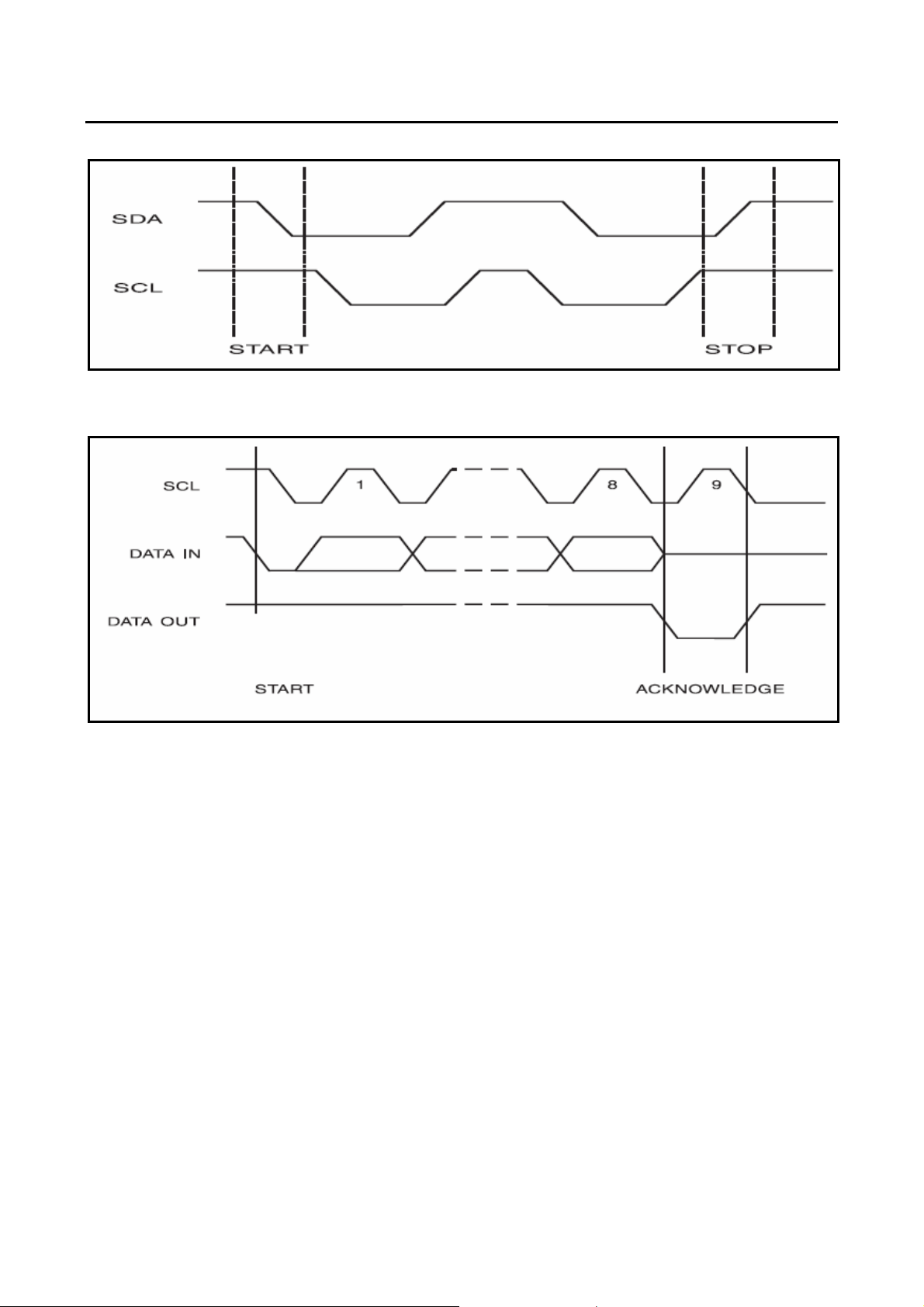

CLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device. Data on

the SDA pin may change only during SCL low time periods (see to Figure 1 on page 4). Data changes during

SCL high periods will indicate a start or stop condition as defined below.

START CONDITION: A high-to-low transit ion of SDA with SCL hig h is a start condit ion which must pre cede

any other command (see to Figure 2 on page 5).

STOP CONDITION: A low-to-high transition of SDA with SC L high is a stop cond ition. After a read seq uence,

the stop command will place the EEPROM in a standby power mode (see Figure 2 on page 5).

ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the EEPROM in 8-bit

words. The EEPROM sends a “0” to acknowledge that it has received each word. This happens during the

ninth clock cycle.

STANDBY MODE: The 24C02/ 24C04 features a low-power standby mode which is enabled: (a) upon

power-up and (b) after the receipt of the STOP bit and the completion of any internal operations

MEMORY RESET: After an interruption in protocol, power loss or system reset, any two-wire part can be

reset by following these steps:

1. Clock up to 9 cycles.

2. Look for SDA high in each cycle while SCL is high.

3. Create a start condition.

Figure 1.

Data Validity

4/15 MRD

Figure 2. Start and Stop Definition

Figure 3. Output Acknowledge

24C02/24C04

3. Device Addressing

The 2K and 4K EEPROM devices all require an 8-bit device address word following a start condition to enable

the chip for a read or write operation (see to Figure 4 on page 4).

The device address word consists of a mandatory “1”, “0” sequence for the first four most significant bits as

shown. This is common to all the Serial EEPROM devices.

The next 3 bits are the A2, A1 and A0 device address bits for the 2K EEPROM. These 3 bits must compare to

their corresponding hardwired input pins.

The 4K EEPROM only uses the A2 and A1 device address bits with the third bit being a memory page address

bit. The two device address bits must compare to their corresponding hardwired input pins. The A0 pin is no

connect.

The eighth bit o f the devic e addre ss is the r ead/write operation select bit . A read o peration is initiate d if this

bit is high and a write operation is initiated if this bit is low.

Upon a compare of the device address, the EEPROM will output a “0”. If a compare is not made, the chip will

return to a standby state.

5/15 MRD