查询USB2005供应商

USB2005

USB2.0 ATA/ATAPI

Controller with PD-DRM

PRODUCT FEATURES

■ Provides support for digital rights management for

portable devices (PD-DRM) via Mass Storage Class

SCSI Inquiry command as specified by Microsoft for

Windows Media Systems (WM-DRM). Reports all

media as Removable (HDDs only).

■ 2.5 Volt, Low Power Core Operation

■ 3.3 Volt I/O with 5V input tolerance

■ Supports a low-cost single 3.3V regulator design, by

using a 1N4001 diode to provide the 2.5V core

voltage (from the 3.3V supply)

■ Complete USB Specification 2.0 Compatibility

— Includes USB2.0 Transceiver

— A Bi-directional Control and a Bi-directional Bulk

Endpoint are provided.

■ Complete System Solution for interfacing ATA or

ATAPI devices to USB2.0 bus

— Supports USB Mass Storage Compliant Bootable BIOS

— Supports ATA6 Drive capacities up to 2048GB

— True UDMA Mode 4 transfer rates

— Support for ATAPI Devices:

– CD-ROM

– CD-R

– CD-RW

–DVD

–DVD/R/W

■ Support for sharing ATA/ATAPI drive with external

microprocessor for file playback in portable media

player applications

— Pin indication of USB bus SUSPEND state

— Control pin to force drive interface high impedance

state for drive sharing

Datasheet

■ 8051 8 bit microprocessor

— Provides low speed control functions

— 30 Mhz execution speed at 4 cycles per instruction

average

— 768 Bytes of internal SRAM for general purpose

scratchpad or program execution while re-flashing

external ROM

■ Double Buffered Bulk Endpoint

— Bi-directional 512 Byte Buffer for Bulk Endpoint

— 64 Byte RX Control Endpoint Buffer

— 64 Byte TX Control Endpoint Buffer

■ Internal or External Program Memory Interface

— 48K Byte Internal ROM or optional 64K Byte External

Code Space using Flash, SRAM, or EPROM Memory

■ On Board 12Mhz Crystal Driver Circuit

■ Internal PLL for 480Mhz USB2.0 Sampling, 30Mhz

MCU clock, and 60Mhz ATA clock

■ Supports firmware upgrade via USB bus if "boot

block" Flash program memory is used for optional

external program memory

■ Optional Serial EEPROM interface for VID/PID/Serial

Number Customization

■ 100STQFP Package (12x12x1.4mm body, 14x14mm

footprint); green, lead-free package also available

SMSC USB2005 DATASHEET Revision 0.2 (06-07-05)

USB2.0 ATA/ATAPI Controller with PD-DRM

ORDER NUMBER(S):

USB2005-MN FOR 100 PIN, STQFP PACKAGE

USB2005-MV-01 FOR 100 PIN, STQFP PACKAGE (GREEN, LEAD-FREE)

Datasheet

Hauppauge, NY 11788

(631) 435-6000

FAX (631) 273-3123

80 Arkay Drive

Copyright © 2005 S MSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently,

complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be

accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any

time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this

information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual

property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated

version of SMSC's standard Terms of Sale Agreem ent dated before the date of your order (the "Terms of Sale Agreement"). The product may

contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifica tions. Anomaly

sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other

application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written

approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. C opies of this document or other

SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC’s website at http://www.smsc.com. SMSC is a

registered trademark of Standard Microsystems Corporation (“SMSC”). Product names and company names are the trademarks of their respective

holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE,

AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL

DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION,

WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR

OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER

OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Revision 0.2 (06-07-05) 2 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Table of Contents

Chapter 1 General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Chapter 2 Pin Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 3 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Chapter 4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 5 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5.1 Buffer Type Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Chapter 6 Typical Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Chapter 7 PD-DRM Usage & Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7.1 SCSI Inquiry Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7.2 SCSI Inquiry Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7.2.1 Device Serial Number & Page Length (Bytes 3 & 4...n) . . . . . . . . . . . . . . . . . . . . . . . . . 16

Chapter 8 DC Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

8.1 Maximum Guaranteed Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

8.2 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Chapter 9 AC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

9.1 ATA/ATAPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

9.2 USB2.0 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Chapter 10 Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

SMSC USB2005 3 Revision 0.2 (06-07-05)

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

List of Figures

Figure 3.1 USB2005 STQFP 100 Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 4.1 USB2005 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 6.1 USB2005 Typical Application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 10.1 USB2005 100 Pin STQFP Package (12x12x1.4 mm body, 14x14 mm footprint) . . . . . . . . . 21

Revision 0.2 (06-07-05) 4 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

List of Tables

Table 1.1 Operational Conditions to Electrically Detach USB2005 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 2.1 USB2005 Pin Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 5.1 USB2005 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 5.2 USB2005 Buffer Type Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 7.1 SCSI INQUIRY Command Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 7.2 Data Buffer Returned for Device Serial Number Query. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

SMSC USB2005 5 Revision 0.2 (06-07-05)

DATASHEET

Chapter 1 General Description

The USB2005 is a USB2.0 Mass Storage Class Peripheral Controller intended for use with standard

ATA-5 and -6 hard in media player applications requiring Portable Device – Digital Rights Management

(PD-DRM) as specified by Microsoft for Windows Media systems. This includes reporting all media as

removable drives and providing the drive serial number to the PC host via a SCSI Inquiry command.

The device consists of a USB2.0 PHY and SIE, buffers, Fast 8051 microprocessor with expanded

scratchpad and 768 of program SRAM, internal 48 KB program ROM, and an ATA-66 compatible

interface.

Provisions for optional external Flash Memory up to 64K bytes for program storage is provided. An

optional serial EEPROM which can be modified via USB from the host provides unique VID/PID/Serial

numbers, as well as optional configuration information.

Internal 768 Bytes of scratchpad SRAM are also provided. This internal SRAM can also be used for

program storage to implement program upgrade via USB download to external “boot block” Flash

program memory, if desired.

To facilitate portable media player designs, the ability to electrically detach the USB2005 from the drive

under external microprocessor control is provided, as well as an indication to that processor if the USB

bus is SUSPENDed when the USB2005 is attached to a USB host. See table below:

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Table 1.1 Operational Conditions to Electrically Detach USB2005

USB BUS

OPERATIONAL CONDITION

Attached to USB but USB host powered down. ie no

VBUS from host PC (IDE interface high impedance)

Media player uP forcing USB detach and high

impedance of USB2005 IDE interface

External uP in media player allows USB connection of

USB2005 while attached to USB bus

Normal USB operation/access to IDE Normal

USB2005 attached to USB bus; USB Host in SUSPEND

or Safe Removal has occurred via toolbar applet

(USB2005 IDE interface high impedance)

Media Player detached from USB bus (USB2005 IDE

interface high impedance)

STATUS GPIO3 INPUT

Unpowered 0 0

X00

Enumerating 1 Toggle due to

Operation

SUSPEND X 0

Unconnected X 0

GPIO1

OUTPUT

optional

external

SEEPROM

data reads

11

Revision 0.2 (06-07-05) 6 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Chapter 2 Pin Table

DISK DRIVE INTERFACE (27 PINS)

IDE_D0 IDE_D1 IDE_D2 IDE_D3

IDE_D4 IDE_D5 IDE_D6 IDE_D7

IDE_D8 IDE_D9 IDE_D10 IDE_D11

IDE_D12 IDE_D13 IDE_D14 IDE_D15

IDE_nIOR IDE_nIOW IDE_IRQ IDE_DACK

IDE_DRQ IDE_nCS0 IDE_nCS1 IDE_SA0

IDE_SA1 IDE_SA2 IORDY

USBD+ USBD- LOOPFLTR RBIAS

Table 2.1 USB2005 Pin Table

USB INTERFACE (7 PINS)

RTERM FS+ FS-

MEMORY/IO INTERFACE (28 PINS)

MD0 MD1 MD2 MD3

MD4 MD5 MD6 MD7

MA0 MA1 MA2 MA3

MA4 MA5 MA6 MA7

MA8 MA9 MA10 MA11

MA12 MA13 MA14 MA15

nMRD nIOR nMWR nIOW

MISC (15 PINS)

ROMEN GPIO1/SUSPEND GPIO2/EE_CS GPIO3/VBUS

GPIO4/EE_DIO GPIO5/ATA RESET GPIO6/A16 GPIO7/EE_CLK

XTAL1/CLKIN XTAL2 nRESET nTEST/nDBGSTR

TST_OUT/DBGOUT nTESTEN CLKOUT

POWER, GROUNDS, AND NO CONNECTS (23 PINS)

SMSC USB2005 7 Revision 0.2 (06-07-05)

DATASHEET

Chapter 3 Pin Configuration

ROMEN

GPIO1

GPIO2

GPIO3

GND

GPIO4

GPIO5

GPIO6

GPIO7

nTEST0

nTEST1

nTEST2

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

VDDIO

IDE_D8

IDE_D7

IDE_D9

VDD

IDE_D6

IDE_D10

GND

IDE_D5

IDE_D11

IDE_D4

VDDIO

IDE_D12

RBIAS

VDDA

FS+

USB+

USB-

FS-

RTERM

VSSA

XTAL1/CLKIN

XTAL2

VSSP

LOOPFLTR

VDDP

N.C.

N.C.

MD7

MD6

MD5

MD4

GND

MD3

MD2

MD1

MD0

nRESET

75

51

IDE_D3

IDE_D13

IDE_D2

GND

IDE_D14

IDE_D1

IDE_D15

IDE_D0

VDDIO

IDE_DRQ

IDE_nIOW

IDE_nIOR

USB2005

1

MA9

MA8

VDD

nIOR

nIOW

VDDIO

GND

MA15

MA14

MA13

MA12

MA11

MA10

CLKOUT

MA7

VDDIO

MA6

MA5

MA4

N.C.

MA3

MA2

MA1

25

MA0

GND

IORDY

GND

IDE_DACK

IDE_IRQ

IDE_SA1

IDE_SA0

VDD

IDE_SA2

IDE_nCS0

IDE_nCS1

VDDIO

nMWR

nMRD

Figure 3.1 USB2005 STQFP 100 Pin

Revision 0.2 (06-07-05) 8 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

ROMEN

Drive

ATA/ATAPI

48KB ROM

Clocked byPhase 2 Clock

ATA-66

Interface

Future phase 3

SRAM

1.25KB

60MHz32 Bit

s

s

u

B

a

t

a

D

64 Bytes EP0TX

64 Bytes EP1TX

64 Bytes EP0RX

64 Bytes EP1RX

512 Bytes EP2 TX/RX Buffer A

512 Bytes EP2 TX/RX Buffer B

Latch phase 1 Latch phase 2

15MHz

Data @ 32 bit

8 bits ( Address and Data busses )

XDATA

Address Register

GPIO 7 pins

SRAM

768 Byte

Program/Scratchpad

Interrupt Controller

Bus

Program Memory/ IO

2 pins

MEM/IO Bus 29pins

CPU CORE

FAST 8051

Debug

Serial 2 wire ( Data/Strobe)

Clocked byPhase 1 Clock

Latch phase 0

Address

Osc

Address MUX

s

s

s

s

e

e

r

r

d

d

d

d

A

A

Address

Address

EP1TX_BC

EP0TX_BC

EP0RX_BC

Auto address generators

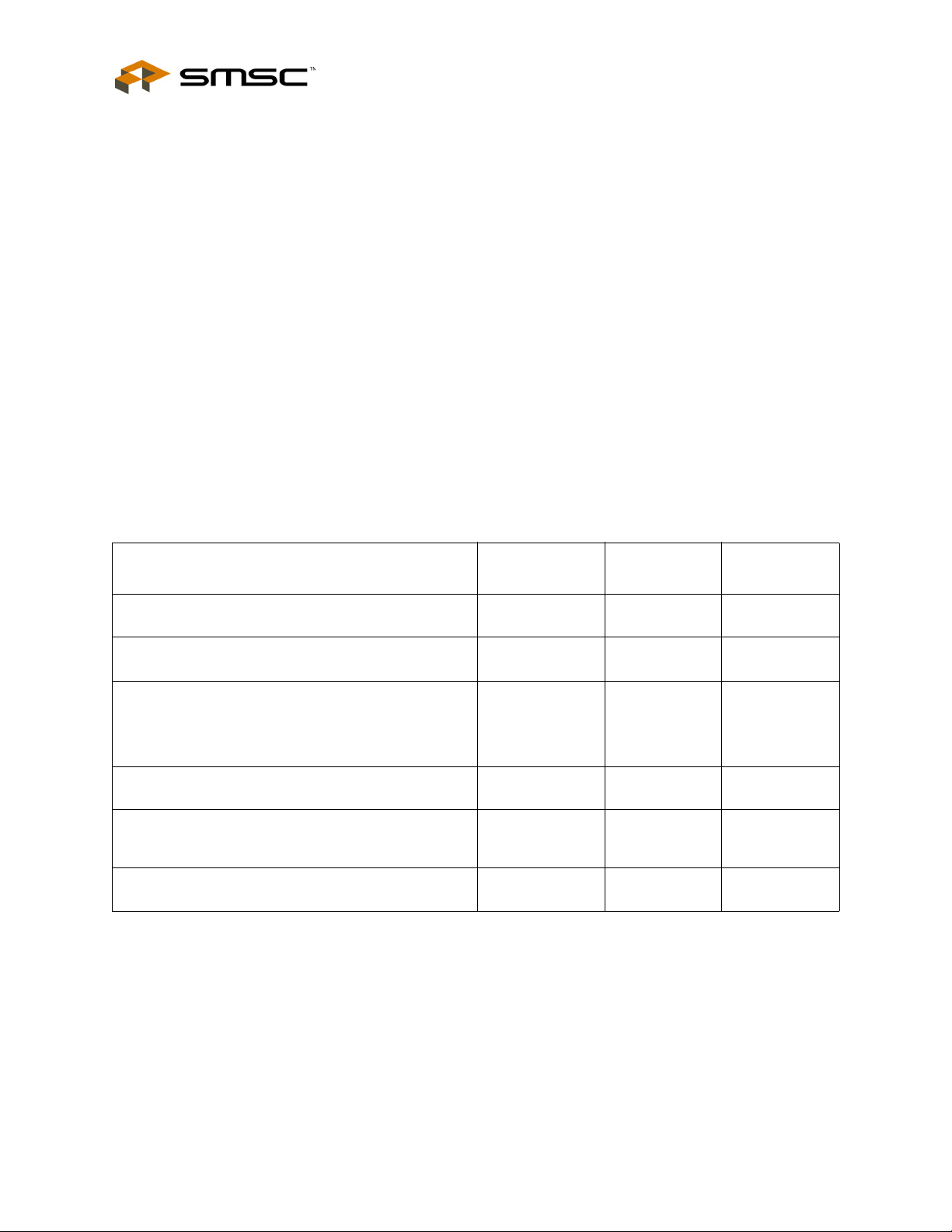

Chapter 4 Block Diagram

Revision 0.2 (06-07-05) 9 SMSC USB2005

EP1RX_BC

Address

RAMWR_A/B

Address

Clocked byPhase 0 Clock

RAMRD_A/B

DATASHEET

SIE Control Regs

32 bit 15MHz Data Buss

SIE

( Serial Interface Engine )

Clock Generation

Configuration and Control

USB2.0 PHY

( Transciever )

XTAL

12 MHz

CLOCKOUT

7 pins

OPTIONAL

External PHY

Figure 4.1 USB2005 Block Diagram

Chapter 5 Pin Description

Table 5.1 USB2005 Pin Descriptions

DISK DRIVE INTERFACE

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

IDE DMA Request IDE_DRQ IS This pin is the active high DMA request from

IDE IO Read Strobe IDE_nIOR O20 This pin is the active low read signal for the

IDE Register

Address 1

IDE Register

Address 0

IDE Register

Address 2

IDE Data IDE_D15 IO20 This pin is the bi-directional data bus bit 15

IDE IO Write Strobe IDE_nIOW O20 This pin is active low write signal for the

IDE DMA

Acknowledge

IDE Interrupt

Request

IDE Data IDE_D13 IO20 This pin is the bi-directional data bus bit 13

IDE Data IDE_D14 IO20 This pin is the bi-directional data bus bit 14

IDE_SA1 O20 This pin is the register select address bit 1

IDE_SA0 O20 This pin is the register select address bit 0

IDE_SA2 O20 This pin is the register select address bit 2

IDE_nDACK O20 This pin is the active low DMA acknowledge

IDE_IRQ IS This pin is the active high interrupt request

the ATA/ATAPI interface.

interface.

signal for the ATA/ATAPI interface.

signal for the ATA/ATAPI interface.

signal for the ATA/ATAPI interface.

signal for the ATA/ATAPI interface.

ATA/ ATA PI int e rfac e .

signal for the ATA/ATAPI interface.

signal for the ATA/ATAPI interface.

signal for the ATA/ATAPI interface.

signal for the ATA/ATAPI interface.

IDE Chip Select 0 IDE_nCS0 O20 This pin is the active low chip select 0 signal for

IDE Chip Select 1 0 IDE_nCS1 O20 This pin is the active low select 1 signal for the

IDE Data IDE_D[0:12] IO20 These pins are bits 0-12 of the ATA/ATAPI bi-

IO Ready IORDY I This pin is the active high IORDY signal from

USB INTERFACE

USB Bus Data USB-

USB Transceiver

Filter

USB Transceiver

Bias

Termination Resistor RTERM A precision 1.5Kohm precision resistor is

Revision 0.2 (06-07-05) 10 SMSC USB2005

USB+

LOOPFLTR This pin provides the ability to supplement the

RBIAS A 9.09 Kohm precision resistor is attached from

IO-U These pins connect to the USB bus data

the ATA/ATAPI interface.

ATA/ ATA PI int e rfac e .

directional data bus.

the IDE drive.

signals.

internal filtering of the transceiver with an

external network, if required.

ground to this pin to set the transceiver’s

internal bias currents.

attached to this pin from a 3.3V supply.

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Table 5.1 USB2005 Pin Descriptions (continued)

Full Speed USB

Data

Memory Data Bus MD[7:0] IO12PU When ROMEN=0, these signals are used to

Memory Address

Bus

Memory Write Strobe nMWR O12 Program Memory Write; active low

Memory Read

Strobe

IO Read Strobe nIOR O12 XDATA space Read; active low

IO Write Strobe nIOW O12 XDATA space Write; active low

Crystal

Input/External Clock

Input

Crystal Output XTAL2 OCLKx 12Mhz Crystal

FSFS+

MA[15:0] O12 These signals address memory locations within

nMRD O12 Program Memory Read; active low

XTAL1/

CLKIN

IO-U These pins connect to the USB- and USB+

pins through 31.6 ohm series resistors.

MEMORY/IO INTERFACE

transfer data between the internal CPU and the

external program memory. When ROMEN=1, a

weak internal pull up is activated to prevent

these pins from floating.

the external memory.

MISC

ICLKx 12Mhz Crystal or external clock input.

This pin can be connected to one terminal of

the crystal or can be connected to an external

12Mhz clock when a crystal is not used.

This is the other terminal of the crystal, or left

open when an external clock source is used to

drive XTAL1/CLKIN. It may not be used to

drive any external circuitry other than the

crystal circuit.

Clock Output CLKOUT O8 This pin produces a 30Mhz clock signal

Internal ROM Enable ROMEN IP When left unconnected or tied high, the

General Purpose I/O GPIO[1:7] IO20 These general purpose pins may be used

independent of the processor clock divider. It is

held inactive and low whenever the internal

processor clock is stopped or is being obtained

from the ring oscillator.

USB97C202 uses the internal ROM for

program execution. When tied low, an external

program memory should be connected to the

memory/data bus. The state of this pin latched

internally on the rising edge of nRESET.

either as inputs, edge sensitive interrupt inputs,

or outputs. When using internal ROM mode,

these pins have the following assignments:

GPIO1: USB SUSPEND Indicator; active high

GPIO2: Optional Serial EEPROM (93LC56

type) Chip Select

GPIO3: USB VBUS Detect Input (can be used

to force the IDE interface to high impedance

state)

GPIO4: Optional Serial EEPROM Data In/Out

GPIO5: ATA Drive Reset

GPIO6: A16 control line for external program

Flash memory when using firmware upgrade

capability (external ROM operation only)

GPIO7: Optional Serial EEPROM Clock output

SMSC USB2005 11 Revision 0.2 (06-07-05)

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Table 5.1 USB2005 Pin Descriptions (continued)

Datasheet

RESET input nRESET IS This active low signal is used by the system to

Test input nTest[0:2] IP These signals are used for testing the chip.

POWER, GROUNDS, AND NO CONNECTS

VDD +2.5V Core power

VDDIO +3.3V I/O power

VDDP +2.5 Analog power

VSSP Analog Ground Reference

VDDA +3.3V Analog power

VSSA Analog Ground Reference

reset the chip. The active low pulse should be

at least 100ns wide.

User should normally leave them unconnected.

For board continuity testing, all pads (except

RBIAS, FSDP, USBDP, USBDM, FSDM,

RTERM, XTAL1, XTAL2, LOOPFLTR and

nTEST[0:2]) are included in an XNOR chain

which is enabled by pulling nTEST2 low. nIOR

is the output of the chain (the chain begins at

pin 2) and will reflect the toggling of a signal

on each pin. Circuit board continuity of the pin

solder connections after assembly can be

checked in this manner

GND Ground Reference

NC No Connect. These pins should not be

5.1 Buffer Type Descriptions

Table 5.2 USB2005 Buffer Type Descriptions

BUFFER DESCRIPTION

I Input

IS Input with Schmitt trigger

IP Input with weak pull-up

IO8 Input/Output with 8 mA drive

O8 Output with 8mA drive

O12 Output with 12mA drive

IO12PU Input/Output with 12 ma drive and controlled weak pull up

IO12 Input/Output with 12 ma drive

connected externally.

IO20 Input/output with 20mA drive

O20 Output with 20mA drive

O20PU Output with 20mA drive and weak pullup

Revision 0.2 (06-07-05) 12 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Table 5.2 USB2005 Buffer Type Descriptions (continued)

BUFFER DESCRIPTION

ICLKx XTAL clock input

OCLKx XTAL clock output

I/O-U Defined in USB specification

SMSC USB2005 13 Revision 0.2 (06-07-05)

DATASHEET

Chapter 6 Typical Application

USB power input

3.3V Battery supply to USB2005

USB

Bus

Status

3.3V

Regulator

1N4001

3.3V 2. 5V

HDD Interface

Control

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Media

Player

USB

USB2005

Optional

Configuration

SEEPROM

Figure 6.1 USB2005 Typical Application

Optional

External

Program

Memory

Micro HDD

Revision 0.2 (06-07-05) 14 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Chapter 7 PD-DRM Usage & Description

The USB2005 is a USB2.0 Mass Storage Class Peripheral Controller intended for use with standard

ATA-5 and -6 hard disk drives in media player applications requiring Portable Device – Digital Rights

Management (PD-DRM) as specified by Microsoft for Windows Media systems. This includes reporting

all media as removable drives and providing the drive serial number to the PC host via the SCSI

Inquiry command.

7.1 SCSI Inquiry Command

In accordance with the SCSI-2 specification the INQUIRY command has the format shown in Ta b le 7 .1 ,

"SCSI INQUIRY Command Block"

Table 7.1 SCSI INQUIRY Command Block

BIT 7BIT 6BIT 5BIT 4BIT 3BIT 2BIT 1BIT 0

Byte 0: Operation Code 12h

Byte 1: Logical Unit Number LUN Reserved EVPD

Byte 2: Parameters 1 Page Code

Byte 3: Parameters 2 Reserved

Byte 4: Parameters 3 Allocation Length

Byte 5: Control Field Vendor Specific Reserved Flag Link

When performing a device serial number query, the following fields must be programmed as follows:

EVPD = 1, and Page Code = 80h

7.2 SCSI Inquiry Response

In accordance with the SCSI-2 specification the response to INQUIRY command has the format shown

in Table 7.2, "Data Buffer Returned for Device Serial Number Query".

Table 7.2 Data Buffer Returned for Device Serial Number Query

BYTE # BIT 7BIT 6BIT 5BIT 4BIT 3BIT 2BIT 1BIT 0

0 Peripheral Qualifier Device Type Code

1 Page Code (80h)

2 Reserved

3 Page Length (n-3)

4 Device serial number

n

SMSC USB2005 15 Revision 0.2 (06-07-05)

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

7.2.1 Device Serial Number & Page Length (Bytes 3 & 4...n)

In response to a SCSI INQUIRY Command, the USB2005 firmware will read the “Device Identify

Information” of an IDE drive. The Device Serial Number is created by removing all NULL code (00h)

and BLANK code (20h) characters from the “Device Identify Information” response. The Device Serial

Number is reported in Byte 4...n (see Table 7.2). The number of characters of the Device Serial

Number will be reported as the Page Length (Byte 3) see Table 7.2.

As a simple example, If the Device Identify Information of an IDE drive is 713 740, then the USB2005

will return 713740 as the Device Serial Number with a Page Length of 6.

Datasheet

Revision 0.2 (06-07-05) 16 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Chapter 8 DC Parameters

8.1 Maximum Guaranteed Ratings

Operating Temperature Range ............................................................................................0oC to +70oC

Storage Temperature Range .............................................................................................-55

Lead Temperature Range (soldering, 10 seconds) ...................................................................... +325

Positive Voltage on any pin, with respect to Ground........................................................................ 5.5V

Negative Voltage on any pin, with respect to Ground .....................................................................-0.3V

o

to +150oC

o

C

Maximum V

Maximum V

DDA, VDDIO

DD, VDDP

..................................................................................................................... +4.0V

........................................................................................................................ +3.0V

*Stresses above the specified parameters could cause permanent damage to the device. This is a

stress rating only and functional operation of the device at any other condition above those indicated

in the operation sections of this specification is not implied.

Note: When powering this device from laboratory or system power supplies, it is important that the

Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies

exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition,

voltage transients on the AC power line may appear on the DC output. When this possibility

exists, it is suggested that a clamp circuit be used.

8.2 DC Electrical Characteristics

(TA = 0°C - 70°C, V

PARAMETER SYMBOL MIN TYP MAX UNITS COMMENTS

I Type Input Buffer

Low Input Level

High Input Level

ICLK Input Buffer

DDIO, VDDA

= +3.3 V ± 10%, V

V

ILI

V

IHI

2.0

DD, VDDP

= +2.5 V ± 10%,)

0.8 V

V

TTL Levels

Low Input Level

High Input Level

V

V

ILCK

IHCK

2.2

0.4 V

V

Input Leakage

(All I and IS buffers)

Low Input Leakage

High Input Leakage

SMSC USB2005 17 Revision 0.2 (06-07-05)

I

IL

I

IH

-10

-10

+10

+10

µA

µA

VIN = 0

VIN = V

DDIO

DATASHEET

PARAMETER SYMBOL MIN TYP MAX UNITS COMMENTS

O8 Type Buffer

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Low Output Level

High Output Level

Output Leakage

I/O8 Type Buffer

Low Output Level

High Output Level

Output Leakage

I/O12 Type Buffer

Low Output Level

High Output Level

V

OL

V

OH

I

OL

V

OL

V

OH

I

OL

V

OL

V

OH

2.4

-10

2.4

-10

2.4

0.4

+10

0.4

+10

0.4

V

V

µA

V

V

µA

V

V

IOL = 8 mA @

V

= 3.3V

DDIO

IOH = -4mA @

V

= 3.3V

DDIO

VIN = 0 to V

(Note 8.1)

DDIO

IOL = 8 mA @

V

= 3.3V

DDIO

IOH = -4 mA @

V

= 3.3V

DDIO

VIN = 0 to V

(Note 8.1, 8.2)

DDIO

IOL = 12 mA @

V

= 3.3V

DDIO

IOH = -6mA @

V

= 3.3V

DDIO

Output Leakage

I/O20 Type Buffer

Low Output Level

High Output Level

Output Leakage

IO-U

Supply Current Unconfigured I

Supply Current Active I

Note 8.1 Output leakage is measured with the current pins in high impedance.

Note 8.2 Output leakage is valid only on pins without internal weak pull ups or pull downs.

I

OL

V

OL

V

OH

I

OL

CCINIT

CC

-10

2.4

-10

65

85

+10

0.4

+10

85

120

µA

V

V

µA

mA

mA

mA

mA

VIN = 0 to V

(Note 8.1, 8.2)

I

= 20 mA @

OL

V

DDIO

= -5 mA @

I

OH

V

DDIO

VIN = 0 to V

(Note 8.1, 8.2)

V

DDIO, VDDA

V

DD, VDDP

V

DDIO, VDDA

V

DD, VDDP

DDIO

= 3.3V

= 3.3V

DDIO

Revision 0.2 (06-07-05) 18 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

CAPACITANCE TA = 25°C; fc = 1MHz; VDD = 2.5V

PARAMETER SYMBOL MIN TYP MAX UNIT TEST CONDITION

LIMITS

Clock Input Capacitance C

Input Capacitance C

Output Capacitance C

IN

IN

OUT

20 pF All pins except USB pins

(and pins under test tied to

AC ground)

10 pF

20 pF

SMSC USB2005 19 Revision 0.2 (06-07-05)

DATASHEET

Chapter 9 AC Specifications

9.1 ATA/ATAPI

The USB2005 conforms to all timing diagrams and specifications for ATAPI-5 as set forth in the

T13/1321D Revision 3 NCITS specification. Please refer to this specification for more information.

9.2 USB2.0 Timing

The USB2005 conforms to all timing diagrams and specifications for USB peripheral silicon building

blocks as set forth in the USB-IF USB2.0 specification. Please refer to this specification for more

information.

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

Revision 0.2 (06-07-05) 20 SMSC USB2005

DATASHEET

USB2.0 ATA/ATAPI Controller with PD-DRM

Datasheet

RELEASED BY

--

DATEDESCRIPTION

C

REV

1 OF 1

REVISION HISTORY

SEE SPE C FRONT PAGE FOR REVI SION HISTORY

-

REVISION

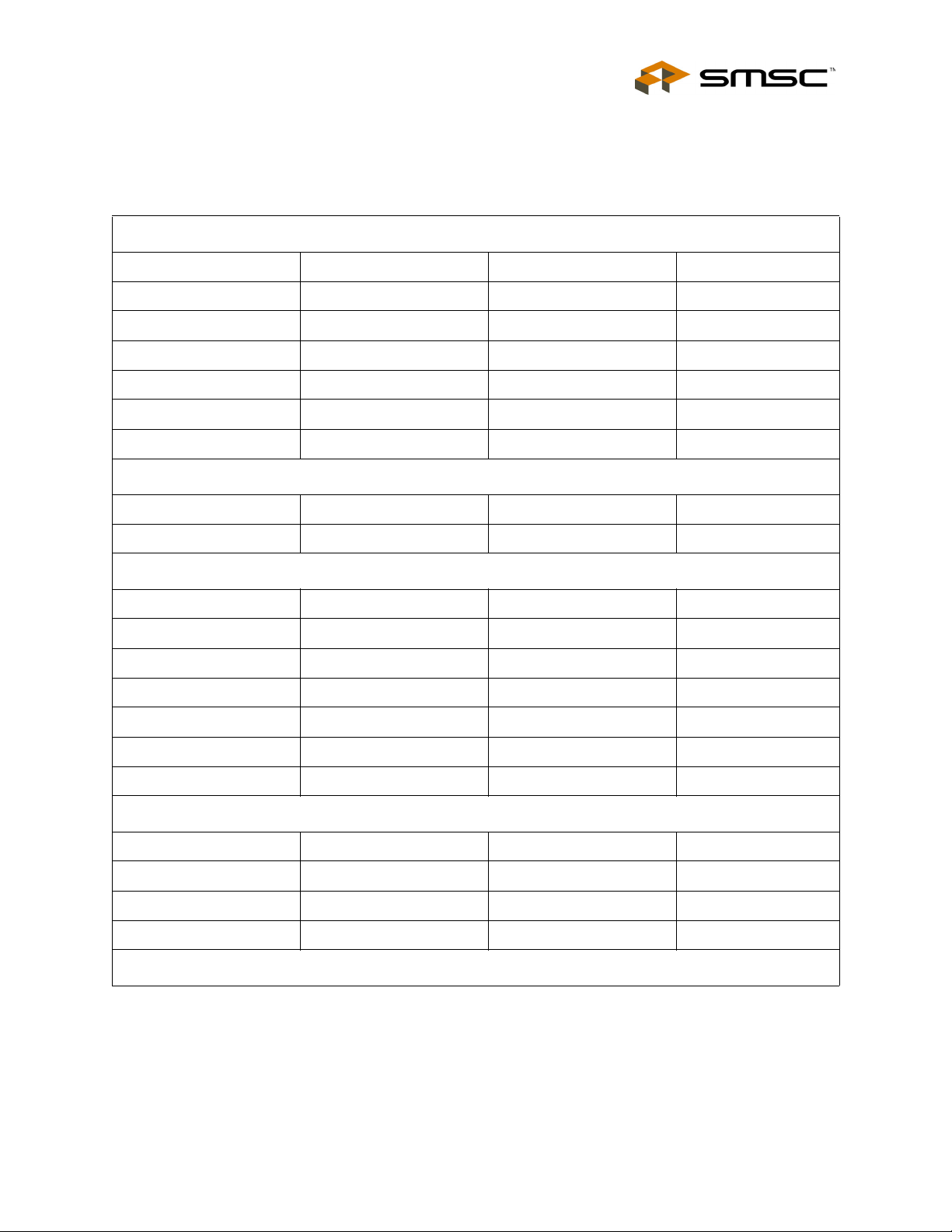

THIRD ANGLE PROJECTION

2. TRUE POSI TION SPREAD TOLERAN CE OF EACH LEAD IS ± 0.0 35mm MAXIMUM.

3. DIMENSI ONS "D1" AND "E1" DO NOT INCLUDE MOL D PROTRUSIONS. MAX IMUM ALLOWED

NOTES:

1. ALL DIMENSIONS ARE IN MILLIMETER.

0°-7°

0.25

R2

R1

GAUGE PLANE

L1

L

UNLESS OTHERWISE SPECIFIED

PROTRU SION IS 0.25 mm PER SIDE.

4. DIMENSION "L" IS MEASURED AT THE GAUGE PLANE, 0.25mm ABOVE THE SEATING PLANE.

INDICATED.

5. DETAILS ON PIN 1 IDENTIFI ER ARE OPTIONAL BUT MUST BE LOCAT ED WITHIN THE ZONE

PACKAGE OUTLINE

80 ARKAY DRIVE

HAUP PAUG E, NY 11788

USA

TITLE

NAME DATE

±1°±0.1

ANGULAR

±0.05

±0.025

ASME Y14.5 M - 1994

INTE RPRE T DIM A ND TOL PER

AND TOLERANCES ARE:

DIMENSIONS ARE IN MILL IMETERS

X.X

X.XX

X.XXX

DECIMAL

JEDEC: MS-026 (D)

STD C OMPL IANCE

MO-100-STQFP-12x12x1.4

1:1

100 STQFP-12x12x1.4mm BODY-0.4mm PITCH

SCALE SHEET

DWG NUMBER

12/17/04

12/17/04

12/17/04

S.K.ILIEV

S.K.ILIEV

S.K.ILIEV

APPROVED

CHECKED

DRAWN

-

-

DO NOT S CALE DRAWING

PRINT WITH "SCALE TO FIT"

MATERIAL

FINISH

DETAIL "A"

4

C

SEATIN G PLANE

E

2

b

A

A1

ccc C

3

D

D1

E1/4

D1/4

e

TOP VIEW

SEE DETAIL "A"

SIDE VIEW

c

3-D VIEW

Figure 10.1 USB2005 100 Pin STQFP Package (12x12x1.4 mm body, 14x14 mm footprint)

5

E1

3

Chapter 10 Package Outline

Revision 0.2 (06-07-05) 21 SMSC USB2005

DATASHEET

A2

Loading...

Loading...