LPC47N217

64-Pin Super I/O with LPC

Interface

Datasheet

Product Features

3.3 Volt Operation (5V tolerant)

Programmable Wakeup Event Interface

(IO_PME# Pin)

SMI Support (IO_SMI# Pin)

GPIOs (14)

Two IRQ Input Pins

XNOR Chain

PC99a, PC2001

ACPI 2.0 Compliant

64-pin STQFP Packages (2mm footprint)

Intelligent Auto Power Management

Serial Ports

− One Full Function Serial Port

− High Speed 16C550A Compatible UART with

Send/Receive 16-Byte FIFO

− Supports 230k and 460k Baud

− Programmable Baud Rate Generator

− Modem Control Circuitry

Infrared Communications Controller

− IrDA v1.2 (4Mbps), HPSIR, ASKIR, Consumer IR

Support

− 1 IR Port

− 96 Base I/O Address, 15 IRQ Options and 3 DMA

Options

Multi-Mode Parallel Port with ChiProtect™

− Standard Mode IBM PC/XT®, PC/AT®, and PS/2™

Compatible Bidirectional Parallel Port

− Enhanced Parallel Port (EPP) Compatible - EPP 1.7

and EPP 1.9 (IEEE 1284 Compliant)

− IEEE 1284 Compliant Enhanced Capabilities Port

(ECP)

− ChiProtect Circuitry for Protection Against Damage

Due to Printer Power-On

− 192 Base I/O Address, 15 IRQ and 3 DMA Options

LPC Bus Host Interface

− Multiplexed Command, Address and Data Bus

− 8-Bit I/O Transfers

− 8-Bit DMA Transfers

− 16-Bit Address Qualification

− Serial IRQ Interface Compatible with Serialized IRQ

Support for PCI Systems

− PCI CLKRUN# Support

− Power Management Event (IO_PME#) Interface Pin

SMSC LPC47N217 Page 1 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

ORDERING INFORMATION

Order Number(s):

LPC47N217-JN for 64 pin STQFP package

LPC47N217-JV for 64 pin lead-free STQFP package

Hauppauge, NY 11788

(631) 435-6000

FAX (631) 273-3123

80 Arkay Drive

Copyright © SMSC 2004. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete

information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no

responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without

notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information

does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of

SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's

standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or

errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon

request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure

could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC

and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms

of Sale Agreement, may be obtained by visiting SMSC’s website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems

Corporation (“SMSC”). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES

OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND

ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES;

OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON

CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR

NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN

ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Revision 0.2 (06-10-03) Page 2 SMSC LPC47N217

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

Table of Contents

Chapter 1 General Description ...............................................................................................................9

Chapter 2 Pinout ................................................................................................................................... 10

Chapter 3 Pin Configuration..................................................................................................................11

Chapter 4 Pin Description .....................................................................................................................12

4.1 Buffer Type Description..............................................................................................................................16

Chapter 5 Block Diagram ...................................................................................................................... 17

Chapter 6 3.3 Volt Operation / 5 Volt Tolerance ................................................................................... 18

Chapter 7 Power Functionality.............................................................................................................. 19

7.1 VCC Power.................................................................................................................................................19

7.2 VTR Support ..............................................................................................................................................19

7.3 Internal PWRGOOD ...................................................................................................................................19

7.4 Trickle Power Functionality.........................................................................................................................19

7.5 Maximum Current Values...........................................................................................................................20

7.6 Power Management Events (PME/SCI) .....................................................................................................20

Chapter 8 Functional Description..........................................................................................................21

8.1 Super I/O Registers....................................................................................................................................21

8.2 Host Processor Interface (LPC)..................................................................................................................21

8.3 LPC Interface .............................................................................................................................................21

8.3.1 LPC Interface Signal Definition ...........................................................................................................21

8.3.2 Power Management ............................................................................................................................23

8.3.3 LPC Transfers .....................................................................................................................................25

Chapter 9 Serial Port (UART) ...............................................................................................................26

9.1 Register Description ...................................................................................................................................26

9.1.1 Receive Buffer Register (RB) ..............................................................................................................27

9.1.2 Transmit Buffer Register (TB) .............................................................................................................27

9.1.3 Interrupt Enable Register (IER) ...........................................................................................................27

9.1.4 FIFO Control Register (FCR) ..............................................................................................................28

9.1.5 Interrupt Identification Register (IIR) ...................................................................................................28

9.1.6 Line Control Register (LCR) ................................................................................................................30

9.1.7 Modem Control Register (MCR)..........................................................................................................32

9.1.8 Line Status Register (LSR)..................................................................................................................33

9.1.9 Modem Status Register (MSR) ...........................................................................................................34

9.1.10 Scratchpad Register (SCR) .............................................................................................................35

9.2 Programmable Baud Rate Generator (AND Divisor Latches DLH, DLL) ....................................................35

9.3 Effect Of The Reset on Register File..........................................................................................................35

9.4 FIFO Interrupt Mode Operation ..................................................................................................................36

9.5 FIFO Polled Mode Opertion .......................................................................................................................37

9.6 Notes On Serial Port Operation..................................................................................................................41

9.6.1 FIFO Mode Operation .........................................................................................................................41

9.6.2 TX AND RX FIFO Operation ...............................................................................................................41

Chapter 10 Infrared Interface .................................................................................................................. 42

10.1 IrDA SIR/FIR and ASKIR........................................................................................................................42

10.2 Consumer IR...........................................................................................................................................42

10.3 Hardware Interface .................................................................................................................................42

10.4 IR Half Duplex Turnaround Delay Time..................................................................................................44

10.5 IR Transmit Pins.....................................................................................................................................44

Chapter 11 Parallel Port..........................................................................................................................46

11.1 IBM XT/AT Compatible, Bi-Directional And EPP Modes.........................................................................47

11.1.1 Data Port .........................................................................................................................................47

11.1.2 Status Port.......................................................................................................................................47

11.1.3 Control Port .....................................................................................................................................48

11.1.4 EPP Address Port............................................................................................................................49

11.1.5 EPP Data Port 0 ..............................................................................................................................49

11.1.6 EPP Data Port 1 ..............................................................................................................................49

11.1.7 EPP Data Port 2 ..............................................................................................................................50

11.1.8 EPP Data Port 3 ..............................................................................................................................50

11.2 EPP 1.9 Operation..................................................................................................................................50

SMSC LPC47N217 Page 3 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

11.2.1 Software Constraints .......................................................................................................................50

11.2.2 EPP 1.9 Write ..................................................................................................................................50

11.2.3 EPP 1.9 Read..................................................................................................................................51

11.3 EPP 1.7 Operation..................................................................................................................................51

11.3.1 Software Constraints .......................................................................................................................52

11.3.2 EPP 1.7 Write ..................................................................................................................................52

11.3.3 EPP 1.7 Read..................................................................................................................................52

11.4 Extended Capabilities Parallel Port.........................................................................................................53

11.5 Vocabulary..............................................................................................................................................53

11.6 ECP Implementation Standard ...............................................................................................................54

11.6.1 Description.......................................................................................................................................54

11.6.2 Register Definitions .........................................................................................................................56

11.6.3 Operation.........................................................................................................................................62

Chapter 12 Power Management .............................................................................................................67

12.1 UART Power Management.....................................................................................................................67

12.1.1 Exit Auto Powerdown ......................................................................................................................67

12.2 Parallel Port ............................................................................................................................................67

12.2.1 Exit Auto Powerdown ......................................................................................................................67

Chapter 13 Serial IRQ............................................................................................................................. 68

13.1 Timing Diagrams For SER_IRQ Cycle....................................................................................................68

13.1.1 SER_IRQ Cycle Control ..................................................................................................................69

13.1.2 SER_IRQ Data Frame.....................................................................................................................69

13.1.3 Stop Cycle Control...........................................................................................................................70

13.1.4 Latency ............................................................................................................................................70

13.1.5 EOI/ISR Read Latency ....................................................................................................................71

13.1.6 AC/DC Specification Issue...............................................................................................................71

13.1.7 Reset and Initialization.....................................................................................................................71

13.2 Routable IRQ Inputs ...............................................................................................................................71

Chapter 14 PCI CLKRUN Support.......................................................................................................... 72

14.1 Overview.................................................................................................................................................72

14.2 CLKRUN# for Serial IRQ ........................................................................................................................72

14.3 CLKRUN# for LDRQ#.............................................................................................................................72

14.4 Using CLKRUN#.....................................................................................................................................72

Chapter 15 General Purpose I/O ............................................................................................................74

15.1 GPIO Pins...............................................................................................................................................74

15.2 Description..............................................................................................................................................74

15.3 GPIO Control..........................................................................................................................................75

15.4 GPIO Operation......................................................................................................................................76

15.5 GPIO PME and SMI Functionality...........................................................................................................77

Chapter 16 System Management Interrupt (SMI) ................................................................................... 78

16.1 SMI Registers.........................................................................................................................................78

Chapter 17 PME Support ........................................................................................................................79

17.1 PME Registers........................................................................................................................................79

Chapter 18 Runtime Registers................................................................................................................ 80

18.1 Runtime Registers Block Summary ........................................................................................................80

18.2 Runtime Registers Block Description......................................................................................................81

Chapter 19 Configuration ........................................................................................................................ 86

19.1 Configuration Access Ports.....................................................................................................................86

19.2 Configuration State.................................................................................................................................86

19.2.1 Entering the Configuration State......................................................................................................86

19.2.2 Configuration Register Programming...............................................................................................87

19.2.3 Exiting the Configuration State ........................................................................................................87

19.2.4 Programming Example ....................................................................................................................87

19.2.5 Configuration Select Register (CSR) ...............................................................................................87

19.3 Configuration Registers Summary..........................................................................................................88

19.4 Configuration Registers Description .......................................................................................................89

19.4.1 CR00 ...............................................................................................................................................89

19.4.2 CR01 ...............................................................................................................................................90

19.4.3 CR02 ...............................................................................................................................................90

Revision 0.2 (06-10-03) Page 4 SMSC LPC47N217

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

19.4.4 CR03 ...............................................................................................................................................91

19.4.5 CR04 ...............................................................................................................................................91

19.4.6 CR05 ...............................................................................................................................................92

19.4.7 CR06 ...............................................................................................................................................92

19.4.8 CR07 ...............................................................................................................................................92

19.4.9 CR08 ...............................................................................................................................................93

19.4.10 CR09 ...............................................................................................................................................93

19.4.11 CR0A...............................................................................................................................................94

19.4.12 CR0B...............................................................................................................................................94

19.4.13 CR0C...............................................................................................................................................95

19.4.14 CR0D...............................................................................................................................................95

19.4.15 CR0E...............................................................................................................................................95

19.4.16 CR0F ...............................................................................................................................................96

19.4.17 CR10 ...............................................................................................................................................96

19.4.18 CR11 ...............................................................................................................................................97

19.4.19 CR12 - CR13 ...................................................................................................................................97

19.4.20 CR14 ...............................................................................................................................................98

19.4.21 CR15 ...............................................................................................................................................99

19.4.22 CR16 ...............................................................................................................................................99

19.4.23 CR17 ...............................................................................................................................................99

19.4.24 CR18 - CR1E.................................................................................................................................100

19.4.25 CR1F .............................................................................................................................................100

19.4.26 CR20 .............................................................................................................................................100

19.4.27 CR21 .............................................................................................................................................101

19.4.28 CR22 .............................................................................................................................................101

19.4.29 CR23 .............................................................................................................................................102

19.4.30 CR24 .............................................................................................................................................102

19.4.31 CR25 .............................................................................................................................................103

19.4.32 CR26 .............................................................................................................................................103

19.4.33 CR27 .............................................................................................................................................104

19.4.34 CR28 .............................................................................................................................................105

19.4.35 CR29 .............................................................................................................................................106

19.4.36 CR2A.............................................................................................................................................106

19.4.37 CR2B.............................................................................................................................................107

19.4.38 CR2C.............................................................................................................................................107

19.4.39 CR2D.............................................................................................................................................108

19.4.40 CR2E.............................................................................................................................................108

19.4.41 CR2F .............................................................................................................................................108

19.4.42 CR30 .............................................................................................................................................109

19.4.43 CR31 .............................................................................................................................................109

19.4.44 CR32 .............................................................................................................................................110

19.4.45 CR33 .............................................................................................................................................110

19.4.46 CR34 .............................................................................................................................................111

19.4.47 CR35 .............................................................................................................................................111

19.4.48 CR36 .............................................................................................................................................112

19.4.49 CR37 .............................................................................................................................................112

19.4.50 CR38 .............................................................................................................................................113

19.4.51 CR39 .............................................................................................................................................113

19.5 Logical Device Base I/O Address and Range.......................................................................................114

19.6 Note A. Logical Device IRQ and DMA Operation..................................................................................115

Chapter 20 Operational Description...................................................................................................... 116

20.1 Maximum Guaranteed Ratings .............................................................................................................116

20.2 DC Electrical Characteristics ................................................................................................................116

20.3 Valid Power States ...............................................................................................................................119

Chapter 21 Timing Diagrams ................................................................................................................120

21.1 Power-Up Timing ..................................................................................................................................120

21.2 Input Clock Timing................................................................................................................................121

21.3 LPC Interface Timing............................................................................................................................121

21.4 Parallel Port Timing ..............................................................................................................................124

21.5 ECP Parallel Port Timing......................................................................................................................127

SMSC LPC47N217 Page 5 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

21.6 IR Timing ..............................................................................................................................................131

21.7 Setup and Hold Timing for Serial IRQ’s................................................................................................135

21.8 UART Timing........................................................................................................................................135

Chapter 22 XNOR-Chain Test Mode .................................................................................................... 136

22.1 Entering and Exiting Test Mode............................................................................................................136

22.1.1 XNOR-Chain test mode can be entered as follows:.......................................................................136

22.1.2 Exit XNOR-Chain test mode as follows: ........................................................................................136

22.2 Pin List of XNOR Chain ........................................................................................................................137

22.3 Setup of XNOR Chain...........................................................................................................................137

22.4 Testing Procedure ................................................................................................................................137

Chapter 23 Package Outline ................................................................................................................. 139

List of Figures

Figure 3.1 - LPC47N217 Pin Configuration ..................................................................................................................11

Figure 5.1 - LPC47N217 Block Diagram ......................................................................................................................17

Figure 9.1 - Serial Data ................................................................................................................................................30

Figure 10.1 - Infrared Interface Block Diagram ............................................................................................................44

Figure 14.1 - CLKRUN# System Implementation Example ..........................................................................................73

Figure 14.2 - Clock Start Illustration .............................................................................................................................73

Figure 15.1 - GPIO Function Illustration.......................................................................................................................76

Figure 21.1 - Power-Up Timing ..................................................................................................................................120

Figure 21.2 - Input Clock Timing ................................................................................................................................121

Figure 21.3 - PCI Clock Timing ..................................................................................................................................121

Figure 21.4 - Reset Timing.........................................................................................................................................121

Figure 21.5 - Output Timing Measurement Conditions, LPC Signals .........................................................................122

Figure 21.6 - Input Timing Measurement Conditions, LPC Signals............................................................................122

Figure 21.7 - I/O Write................................................................................................................................................122

Figure 21.8 - I/O Read ...............................................................................................................................................123

Figure 21.9 - DMA Request Assertion Through LDRQ#.............................................................................................123

Figure 21.10 - DMA Write (First Byte) ........................................................................................................................123

Figure 21.11 - DMA Read (First Byte)........................................................................................................................123

Figure 21.12 - EPP 1.9 Data or Address Write Cycle.................................................................................................124

Figure 21.13 - EPP 1.9 Data or Address Read Cycle.................................................................................................125

Figure 21.14 - EPP 1.7 Data or Address Write Cycle.................................................................................................126

Figure 21.15 - EPP 1.7 Data or Address Read Cycle.................................................................................................126

Figure 21.16 - Parallel Port FIFO Timing ...................................................................................................................128

Figure 21.17 - ECP Parallel Port Forward Timing ......................................................................................................129

Figure 21.18 - ECP Parallel Port Reverse Timing ......................................................................................................130

Figure 21.19 - IrDA Receive Timing ...........................................................................................................................131

Figure 21.20 - IrDA Transmit Timing ..........................................................................................................................132

Figure 21.21 - Amplitude Shift Keyed IR Receive Timing...........................................................................................133

Figure 21.22 - Amplitude Shift Keyed IR Transmit Timing..........................................................................................134

Figure 21.23 - Setup and Hold Time ..........................................................................................................................135

Figure 21.24 - Serial Port Data...................................................................................................................................135

Figure 22.1 - XNOR-Chain Test Structure..................................................................................................................136

Figure 23.1 - 64 Pin STQFP Package Outline, 7X7X1.4 Body, 2 MM Footprint ................................................139

List of Tables

Table 8.1 - Super I/O Block Addresses ........................................................................................................................21

Table 9.1 - Addressing the Serial Port .........................................................................................................................26

Table 9.2 - Interrupt Control Table ................................................................................................................................29

Table 9.3 - Baud Rates ................................................................................................................................................37

Table 9.4 - Reset Function Table..................................................................................................................................38

Table 9.5 - Register Summary for an Individual UART Channel ..................................................................................39

Table 10.1 - FIR Transceiver Module-Type Select.......................................................................................................43

Revision 0.2 (06-10-03) Page 6 SMSC LPC47N217

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

Table 10.2 - IR Rx Data Pin Selection..........................................................................................................................43

Table 11.1 - Parallel Port Connector .............................................................................................................................46

Table 11.2 - EPP Pin Descriptions ................................................................................................................................53

Table 11.3 - Bit map of the Extended Parallel Port Registers ......................................................................................54

Table 11.4 - ECP Pin Descriptions................................................................................................................................55

Table 11.5 - ECP Register Definitions...........................................................................................................................56

Table 11.6 - Mode Descriptions ....................................................................................................................................56

Table 11.7A - Extended Control Register ......................................................................................................................62

Table 11.8 - Forward and Reverse Channel Commands ...............................................................................................64

Table 13.1 - SER_IRQ Sampling Periods ....................................................................................................................70

Table 14.1 - LPC47N217 CLKRUN# Function .............................................................................................................73

Table 15.1 - GPIO Pin Functionality.............................................................................................................................74

Table 15.2 - General Purpose I/O Port Assignments ...................................................................................................75

Table 15.3 - GPIO Configuration Summary..................................................................................................................76

Table 15.4 - GPIO Read/Write Behavior ......................................................................................................................77

Table 15.5 - PME and SMI Functionality......................................................................................................................77

Table 18.1 - Runtime Register Block Summary ...........................................................................................................80

Table 18.2 - Runtime Registers Block Description .......................................................................................................81

Table 19.1 - Configuration Access Ports ......................................................................................................................86

Table 19.2 - Configuration Registers Summary ...........................................................................................................88

Table 19.3 - CR00........................................................................................................................................................89

Table 19.4 - CR01........................................................................................................................................................90

Table 19.5 - CR02........................................................................................................................................................90

Table 19.6 - CR03........................................................................................................................................................91

Table 19.7 - CR04........................................................................................................................................................91

Table 19.8 - CR05........................................................................................................................................................92

Table 19.9 - CR06........................................................................................................................................................92

Table 10 – CR07 ..........................................................................................................................................................92

Table 19.11 - CR09......................................................................................................................................................93

Table 19.12 - CR0A .....................................................................................................................................................94

Table 19.13 - CR0B .....................................................................................................................................................94

Table 19.14 - CR0C .....................................................................................................................................................95

Table 19.15 - CR0F......................................................................................................................................................96

Table 19.16 - CR10......................................................................................................................................................96

Table 19.17 - CR11......................................................................................................................................................97

Table 19.18 - CR12......................................................................................................................................................98

Table 19.19 - CR13......................................................................................................................................................98

Table 19.20 - CR14......................................................................................................................................................98

Table 19.21 - CR15......................................................................................................................................................99

Table 19.22 - CR17......................................................................................................................................................99

Table 19.23 - CR1F....................................................................................................................................................100

Table 19.24 - CR20....................................................................................................................................................100

Table 19.25 - CR21....................................................................................................................................................101

Table 19.26 - CR22....................................................................................................................................................101

Table 19.27 - CR23....................................................................................................................................................102

Table 19.28 - Parallel Port Addressing Options .........................................................................................................102

Table 19.29 - CR24....................................................................................................................................................102

Table 19.30 - CR25....................................................................................................................................................103

Table 19.31 - CR26....................................................................................................................................................103

Table 19.32 - DMA Selection .....................................................................................................................................104

Table 19.33 - CR27....................................................................................................................................................104

Table 19.34 - IRQ Encoding.......................................................................................................................................105

Table 19.35 - CR28....................................................................................................................................................105

Table 19.36 - UART Interrupt Operation ....................................................................................................................105

Table 19.37 - CR29....................................................................................................................................................106

Table 19.38 - CR2A ...................................................................................................................................................106

Table 19.39 - CR2B ...................................................................................................................................................107

Table 19.40 - CR2C ...................................................................................................................................................107

Table 19.41 - CR2D ...................................................................................................................................................108

Table 19.42 - CR2E ...................................................................................................................................................108

SMSC LPC47N217 Page 7 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

Table 19.43 - CR2F....................................................................................................................................................108

Table 19.44 - CR30....................................................................................................................................................109

Table 19.45 - CR31....................................................................................................................................................109

Table 19.46 - CR32....................................................................................................................................................110

Table 19.47 - CR33....................................................................................................................................................110

Table 19.48 - CR34....................................................................................................................................................111

Table 19.49 - CR35....................................................................................................................................................111

Table 19.50 - CR36....................................................................................................................................................112

Table 19.51 - CR37....................................................................................................................................................112

Table 19.52 - CR38....................................................................................................................................................113

Table 19.53 - CR39....................................................................................................................................................113

Table 19.54 - I/O Base Address Configuration Register Description..........................................................................114

Table 23.1 - 64 Pin STQFP Package Parameters.................................................................................................139

Revision 0.2 (06-10-03) Page 8 SMSC LPC47N217

DATASHEET

Chapter 1 General Description

The SMSC LPC47N217 is a 3.3V PC 99, PC2001, and ACPI 2.0 compliant Super I/O Controller. The

LPC47N217 implements the LPC interface, a pin reduced ISA interface which provides the same or better

performance as the ISA/X-bus with a substantial savings in pins used. The part also includes 14 GPIO

pins.

The LPC47N217 incorporates a 16C550A compatible UART and one Multi-Mode parallel port with

ChiProtect circuitry plus EPP and ECP support. This device also offers a full 16-bit internally decoded

address bus, a Serial IRQ interface with PCI CLKRUN# support, relocatable configuration ports, and three

DMA channel options.

The on-chip UART is compatible with the 16C550A. There is a dedicated Serial Infrared interface UART,

which complies with IrDA v1.2 (Fast IR), HPSIR, and ASKIR formats (used by Sharp and other PDAs), as

well as Consumer IR.

The parallel port is compatible with IBM PC/AT architectures, as well as IEEE 1284 EPP and ECP. The

parallel port ChiProtect circuitry prevents damage caused by an attached powered printer when the

LPC47N217 is not powered.

The LPC47N217 features Software Configurable Logic (SCL) for ease of use. SCL allows programmable

system configuration of key functions such as the parallel port and UART.

64-Pin Super I/O with LPC Interface

Datasheet

The LPC47N217 supports the ISA Plug-and-Play Standard register set (Version 1.0a) and provides the

recommended functionality to support Windows operating systems, PC99, and PC2001. The I/O Address,

DMA Channel, and Hardware IRQ of each device in the LPC47N217 may be reprogrammed through the

internal configuration registers. There are multiple I/O address location options, a Serialized IRQ interface,

and three DMA channels.

IBM, PC/XT and PC/AT are registered trademarks and PS/2 is a trademark of International Business Machines Corporation. SMSC is a

registered trademark and ChiProtect, SuperCell, and Multi-Mode are trademarks of Standard Microsystems Corporation.

SMSC LPC47N217 Page 9 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

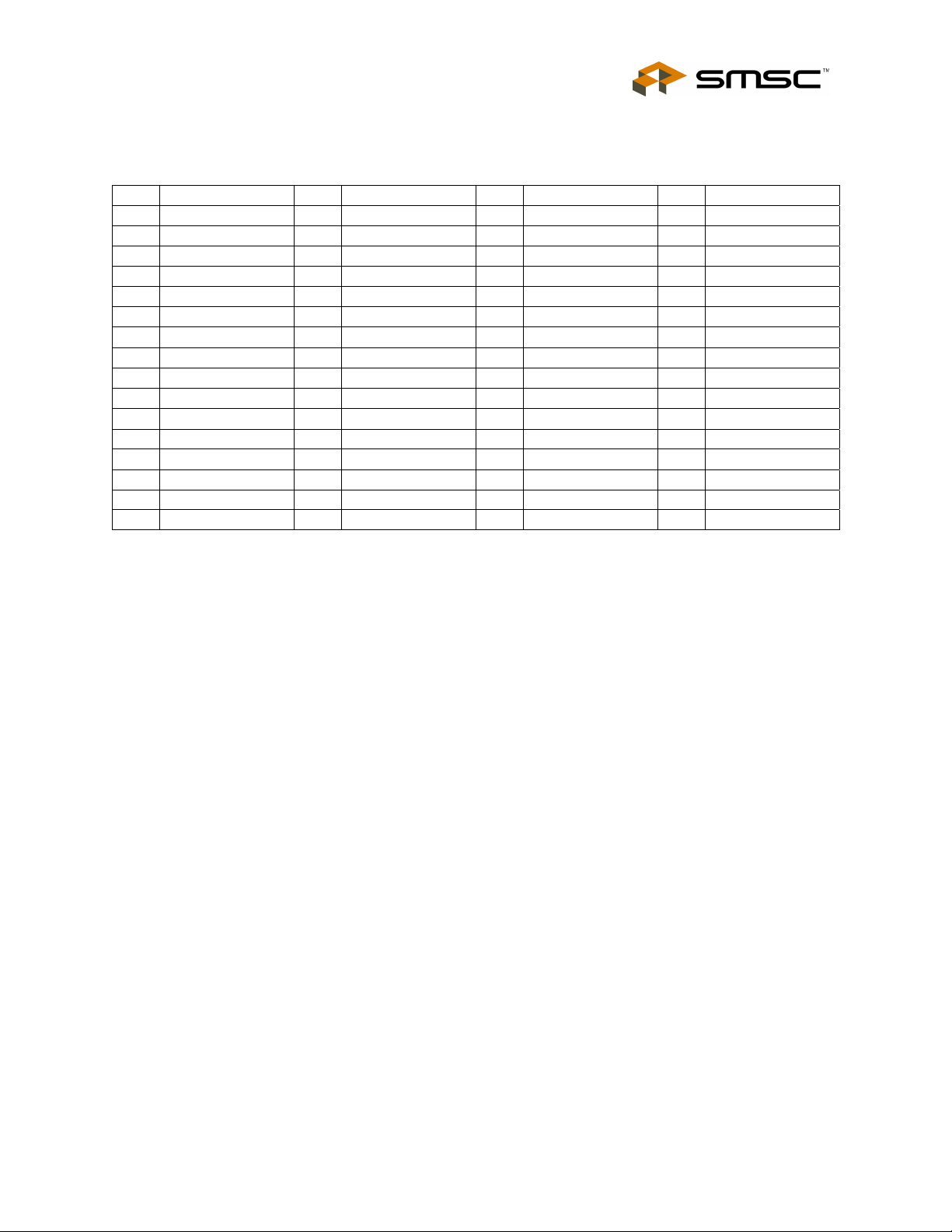

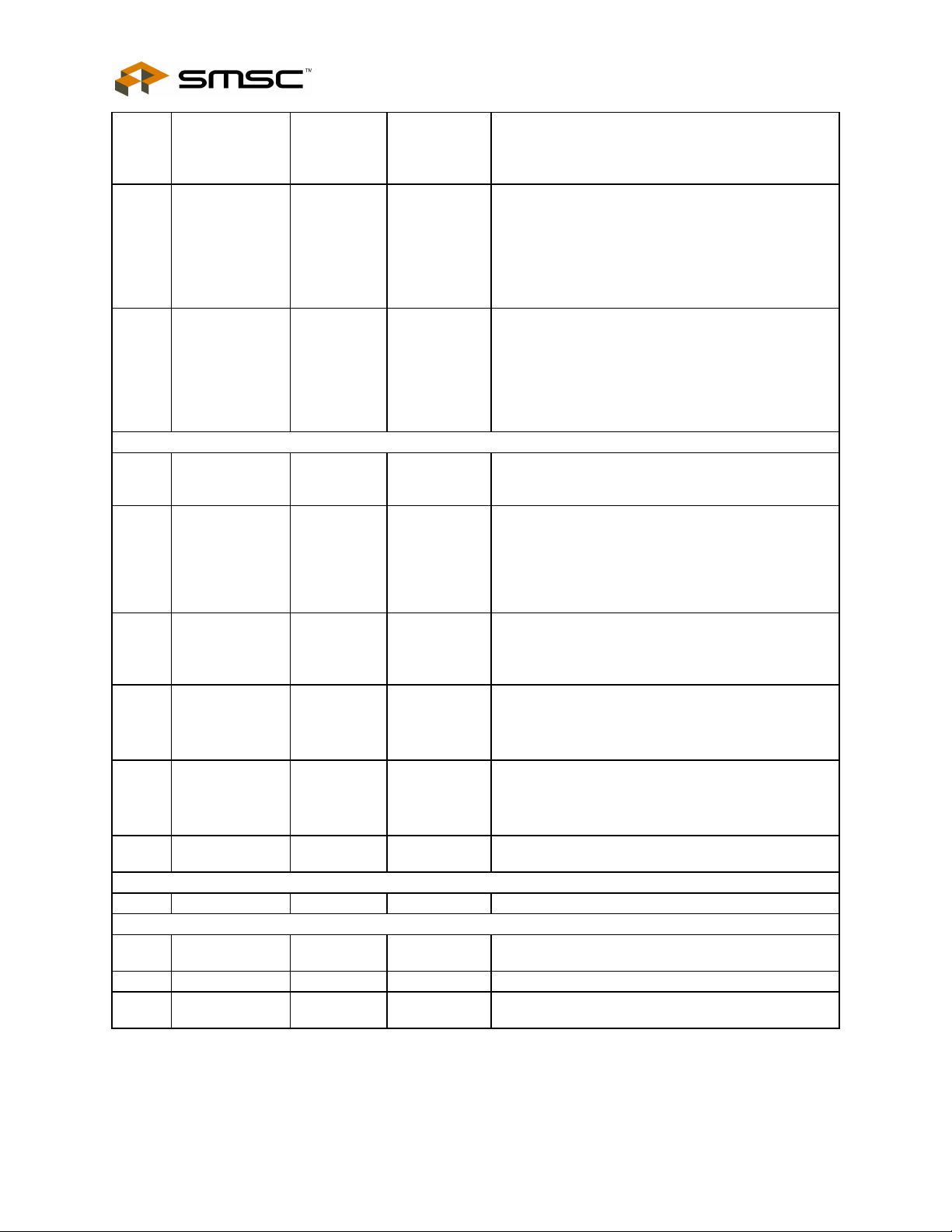

Chapter 2 Pinout

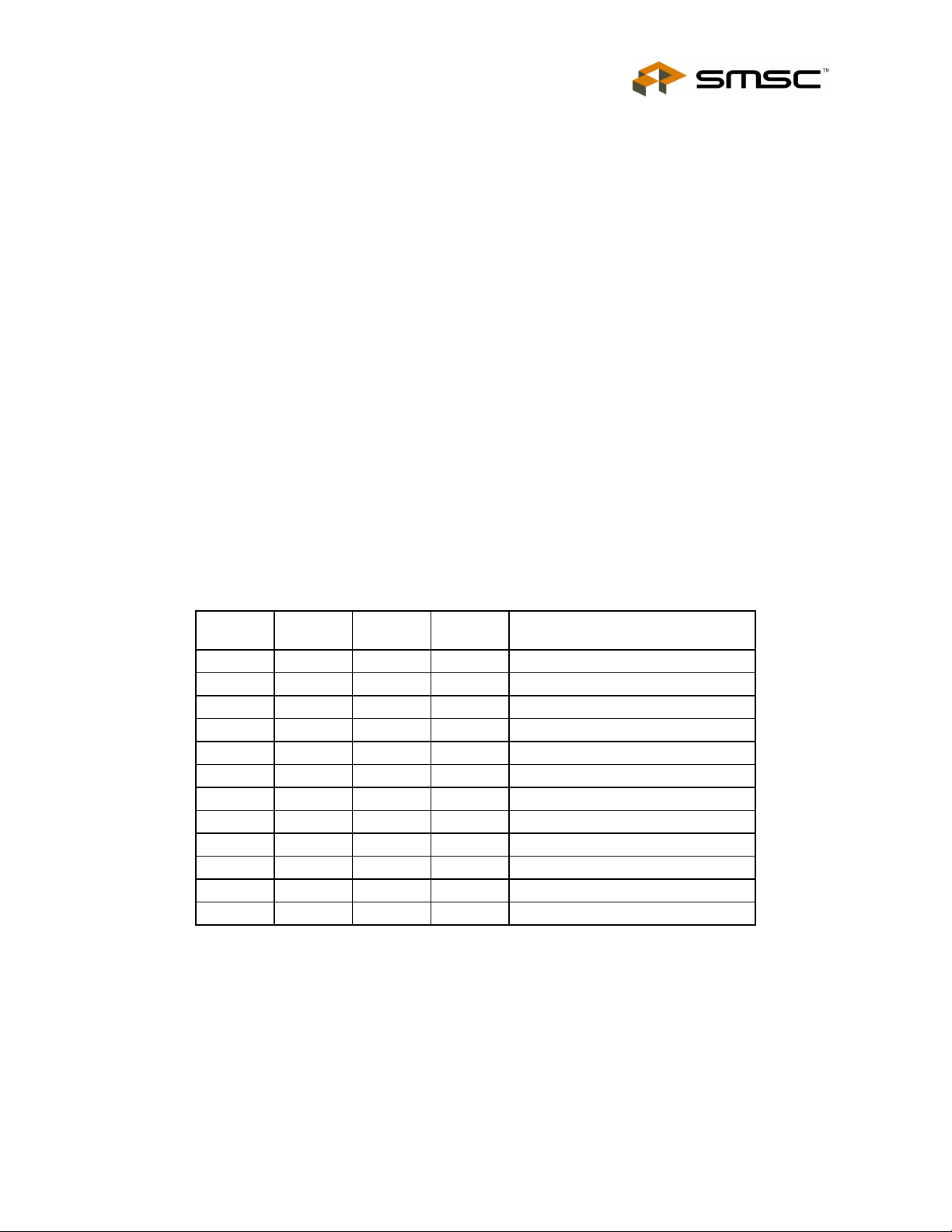

PIN # NAME PIN # NAME PIN # NAME PIN # NAME

1 nRTS1 17 PCI_RESET# 33 GP11/SYSOPT 49 PD4

2 nCTS1 18 LPCPD# 34 GP12/IO_SMI# 50 PD5

3 nDTR1 19 CLKRUN# 35 GP13/IRQIN1 51 PD6

4 nRI1 20 PCI_CLK 36 GP14/IRQIN2 52

5 nDCD1 21 SER_IRQ 37 IRRX2 53 PD7

6 IO_PME# 22

7

8

9 CLOCKI 25 GP42 41 nINIT 57 BUSY

10 LAD0 26

11

12 LAD1 28 GP44 44 PD0 60 nALF

13 LAD2 29 GP45 45

14 LAD3 30 GP46 46 PD1 62 RXD1

15 LFRAME# 31 GP47 47 PD2 63 TXD1

16 LDRQ# 32 GP10 48 PD3 64 nDSR1

VTR

VSS

VCC

23 GP40 39 IRMODE/IRRX3 55 SLCT

24 GP41 40 GP23 56 PE

27 GP43 43

VSS

VCC

38 IRTX2 54

42 nSLCTIN 58 nACK

VSS

VCC

59 nERROR

61 nSTROBE

VSS

VCC

Revision 0.2 (06-10-03) Page 10 SMSC LPC47N217

DATASHEET

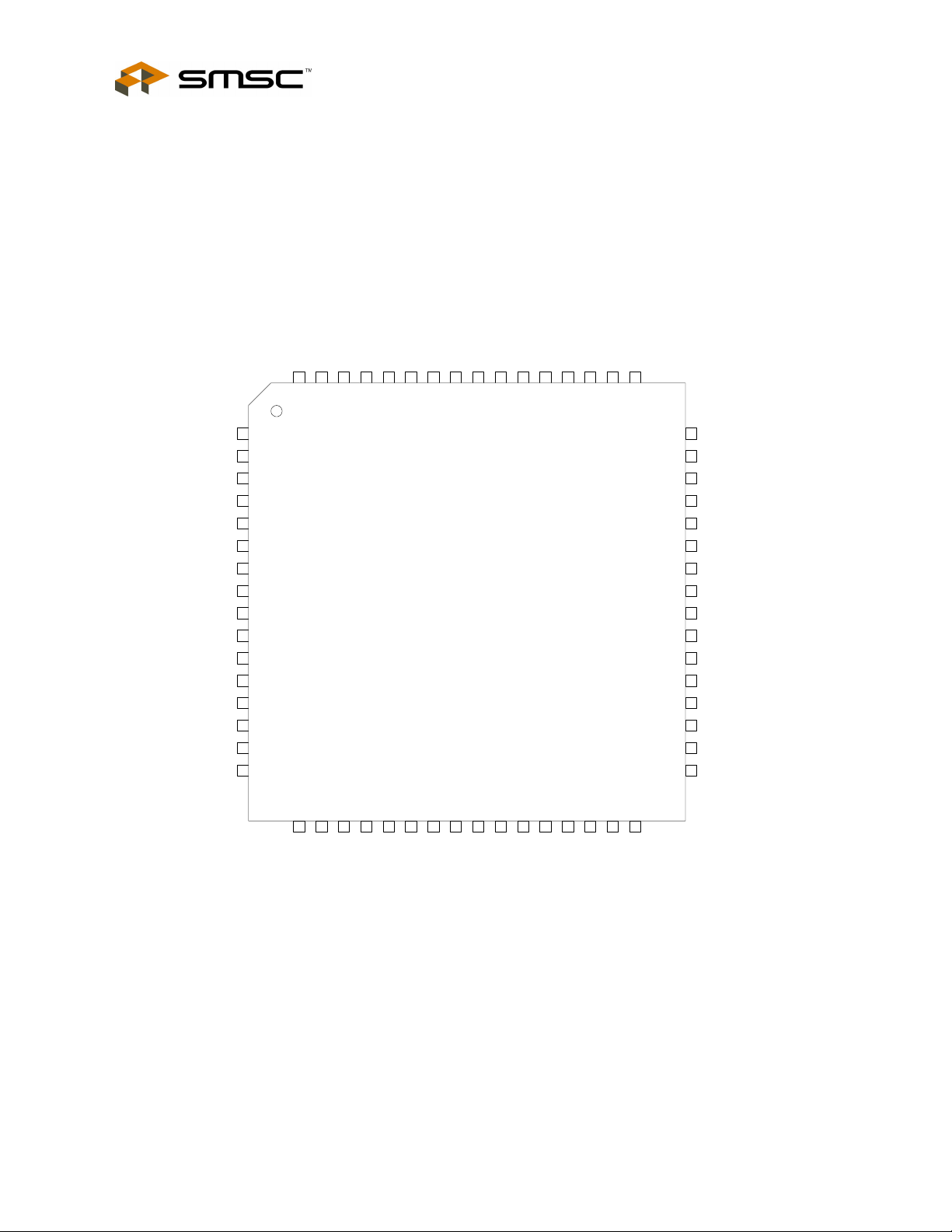

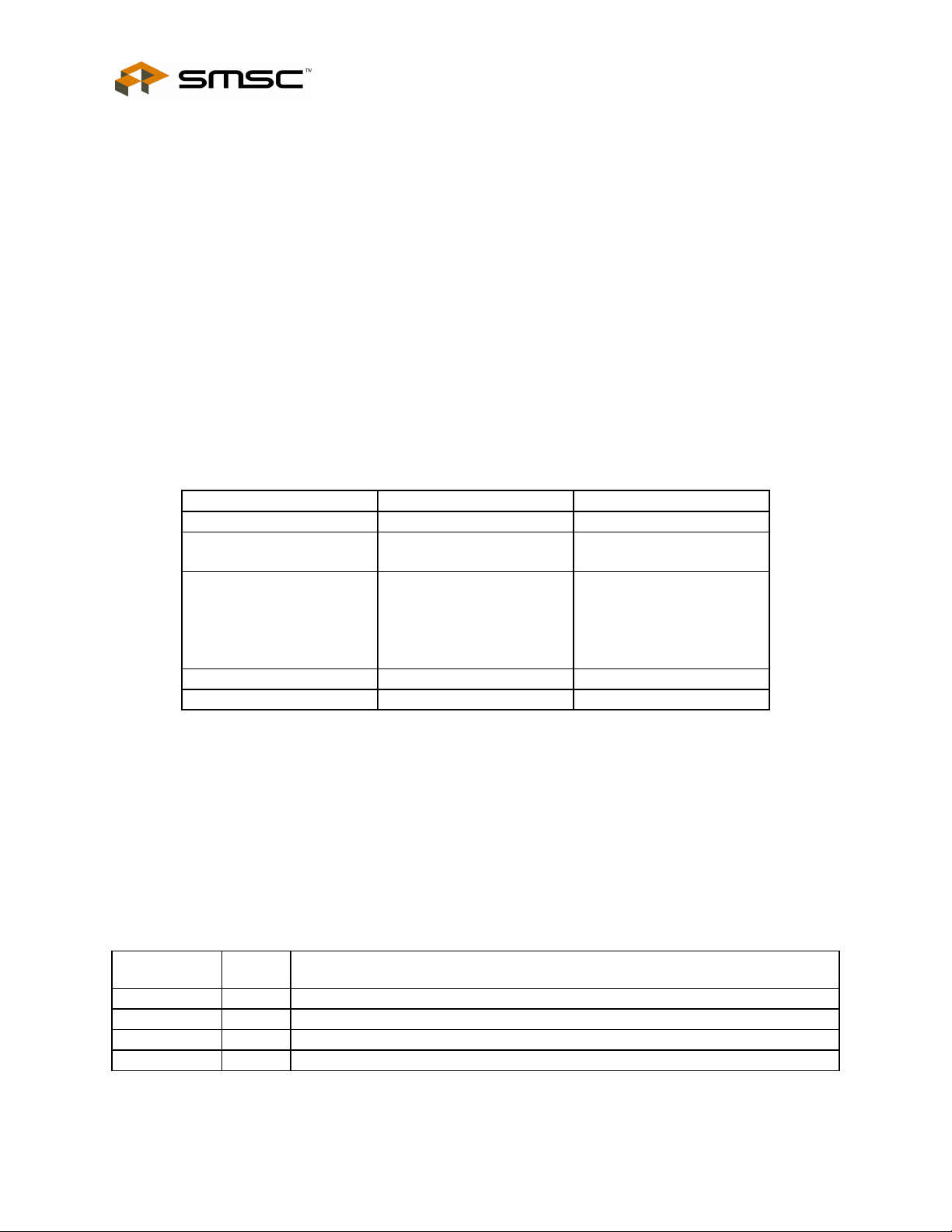

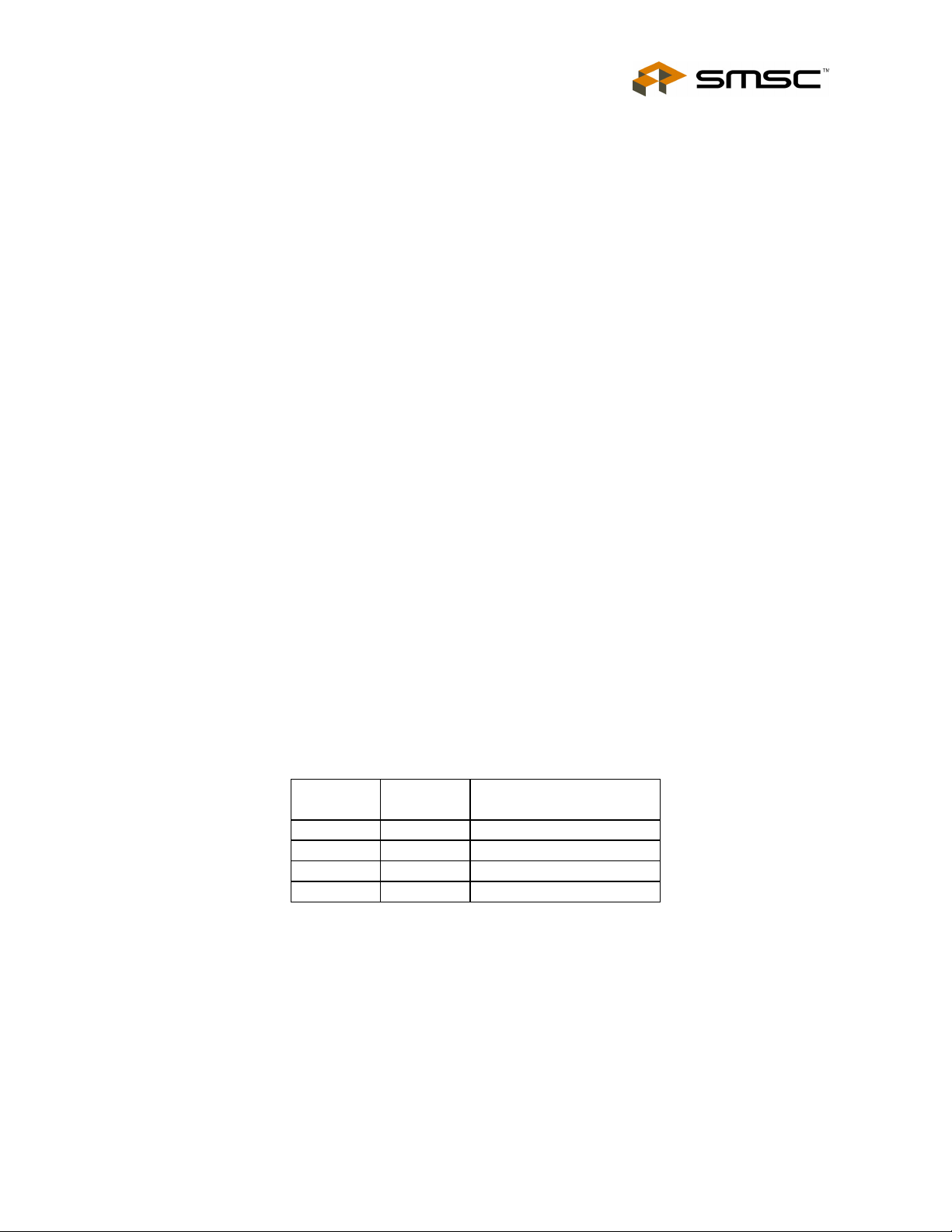

Chapter 3 Pin Configuration

nDSR1

TXD1

RXD1

nSTROBE

nALF

nERROR

nACK

BUSY

PE

SLCT

64-Pin Super I/O with LPC Interface

Datasheet

VCC

PD7

VSS

PD6

PD5

PD4

nRTS1

nCTS1

nDTR1

nRI1

nDCD1

IO_PME#

VTR

VSS

CLOCKI

LAD0

VCC

LAD1

LAD2

LAD3

LFRAME#

LDRQ#

646362616059585756555453525150

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

171819202122232425262728293031

LPC47N217

64 PIN STQFP

49

32

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

PD3

PD2

PD1

VCC

PD0

VSS

nSLCTIN

nINIT

GP23

IRMODE/IRRX3

IRTX2

IRRX2

GP14/IRQIN2

GP13/IRQIN1

GP12/IO_SMI#

GP11/SYSOPT

VSS

GP40

LPCPD#

PCI_CLK

SER_IRQ

CLKRUN#

PCI_RESET#

Figure 3.1 - LPC47N217 Pin Configuration

SMSC LPC47N217 Page 11 Revision 0.2 (06-10-03)

GP41

VCC

GP42

GP43

GP44

GP45

GP46

GP47

GP10

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

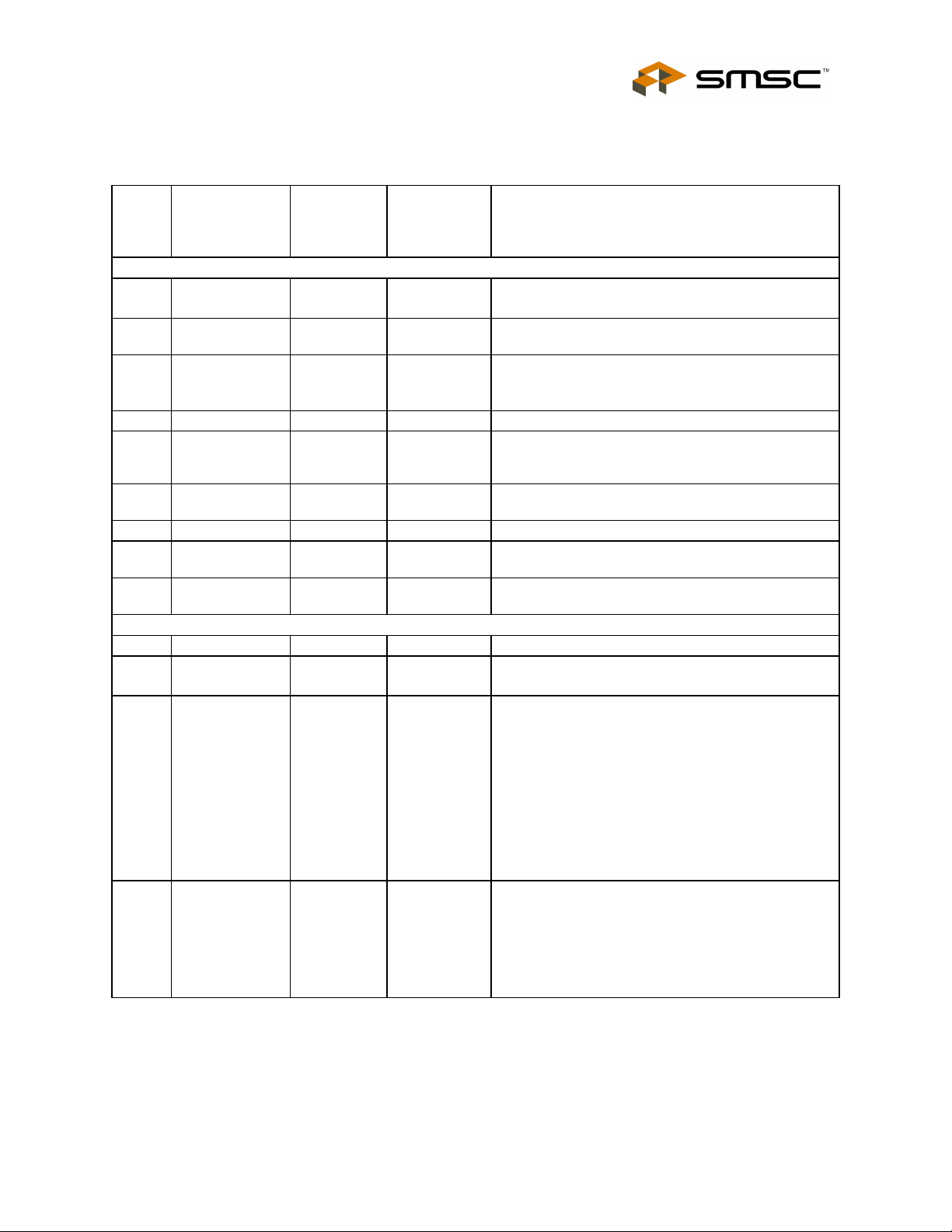

Chapter 4 Pin Description

BUFFER

PIN # NAME SYMBOL

14:12,

LPC Address/

10

Data bus 3-0

15 LPC Frame LFRAME# PCI_I Active low signal indicates start of new cycle and

16 LPC

DMA/Bus Master

Request

17 PCI RESET PCI_RESET# PCI_I Active low signal used as LPC Interface Reset.

18 LPC Power

Down

(Note 4.3)

19 PCI Clock

Controller

20 PCI Clock PCI_CLK PCI_CLK PCI clock input.

21 Serial IRQ SER_IRQ PCI_IO Serial IRQ pin used with the PCI_CLK pin to transfer

6 Power Mgt.

Event

62 Receive Data 1 RXD1 IS Receiver serial data input for port 1.

63 Transmit

Data 1

64 Data Set

Ready 1

LAD[3:0] PCI_IO Active high LPC signals used for multiplexed

LDRQ# PCI_O Active low signal used for encoded DMA/Bus Master

LPCPD# PCI_I Active low Power Down signal indicates that the

CLKRUN# PCI_OD This signal is used to indicate the PCI clock status

IO_PME# (O12/OD12) This active low Power Management Event signal

TXD1 O12 Transmit serial data output for port 1.

nDSR1 I Active low Data Set Ready inputs for the serial port.

TYPE PER

FUNCTION

(NOTE 4.1)

LPC INTERFACE (12)

command, address and data bus.

termination of broken cycle.

request for the LPC interface.

LPC47N217 should prepare for power to be shut on

the LPC interface.

and to request that a stopped clock be started.

LPC47N217 interrupts to the host.

allows the LPC47N217 to request wakeup.

SERIAL PORTS INTERFACE (8)

Handshake signal which notifies the UART that the

modem is ready to establish the communication link.

The CPU can monitor the status of nDSR signal by

reading bit 5 of Modem Status Register (MSR). A

nDSR signal state change from low to high after the

last MSR read will set MSR bit 1 to a 1. If bit 3 of

Interrupt Enable Register is set, the interrupt is

generated when nDSR changes state.

DESCRIPTION

Note: Bit 5 of MSR is the complement of nDSR.

1 Request to Send 1 nRTS1 O6 Active low Request to Send outputs for the Serial Port.

Handshake output signal notifies modem that the

UART is ready to transmit data. This signal can be

programmed by writing to bit 1 of the Modem Control

Register (MCR). The hardware reset will reset the

nRTS signal to inactive mode (high). nRTS is forced

inactive during loop mode operation.

Revision 0.2 (06-10-03) Page 12 SMSC LPC47N217

DATASHEET

PIN # NAME SYMBOL

2 Clear to

nCTS1 I Active low Clear to Send inputs for the serial port.

Send 1

BUFFER

TYPE PER

FUNCTION

(NOTE 4.1)

64-Pin Super I/O with LPC Interface

Datasheet

DESCRIPTION

Handshake signal which notifies the UART that the

modem is ready to receive data. The CPU can

monitor the status of nCTS signal by reading bit 4 of

Modem Status Register (MSR). A nCTS signal state

change from low to high after the last MSR read will

set MSR bit 0 to a 1. If bit 3 of the Interrupt Enable

Register is set, the interrupt is generated when nCTS

changes state. The nCTS signal has no effect on the

transmitter.

Note: Bit 4 of MSR is the complement of nCTS.

3 Data Terminal

Ready 1

4 Ring

Indicator 1

5 Data Carrier

Detect 1

nDTR1 O6 Active low Data Terminal Ready outputs for the serial

port. Handshake output signal notifies modem that

the UART is ready to establish data communication

link. This signal can be programmed by writing to bit 0

of Modem Control Register (MCR). The hardware

reset will reset the nDTR signal to inactive mode

(high). nDTR is forced inactive during loop mode

operation.

nRI1 I

Active low Ring Indicator inputs for the serial port.

Handshake signal which notifies the UART that the

telephone ring signal is detected by the modem. The

CPU can monitor the status of nRI signal by reading

bit 6 of Modem Status Register (MSR). A nRI signal

state change from low to high after the last MSR read

will set MSR bit 2 to a 1. If bit 3 of Interrupt Enable

Register is set, the interrupt is generated when nRI

changes state.

Note: Bit 6 of MSR is the complement of nRI.

nDCD1 I Active low Data Carrier Detect inputs for the serial

port. Handshake signal which notifies the UART that

carrier signal is detected by the modem. The CPU

can monitor the status of nDCD signal by reading bit 7

of Modem Status Register (MSR). A nDCD signal

state change from low to high after the last MSR read

will set MSR bit 3 to a 1. If bit 3 of Interrupt Enable

Register is set, the interrupt is generated when nDCD

changes state.

Note: Bit 7 of MSR is the complement of nDCD.

INFRARED INTERFACE (3)

37 IR Receive IRRX2

(Note 4.6)

38 IR Transmit IRTX2

(Note 4.6)

39 IR Mode/

IR Receive 3

SMSC LPC47N217 Page 13 Revision 0.2 (06-10-03)

IRMODE/

IRRX3

IS IR Receive.

O12 IR Transmit.

O6/

IS

IR mode.

IR Receive 3.

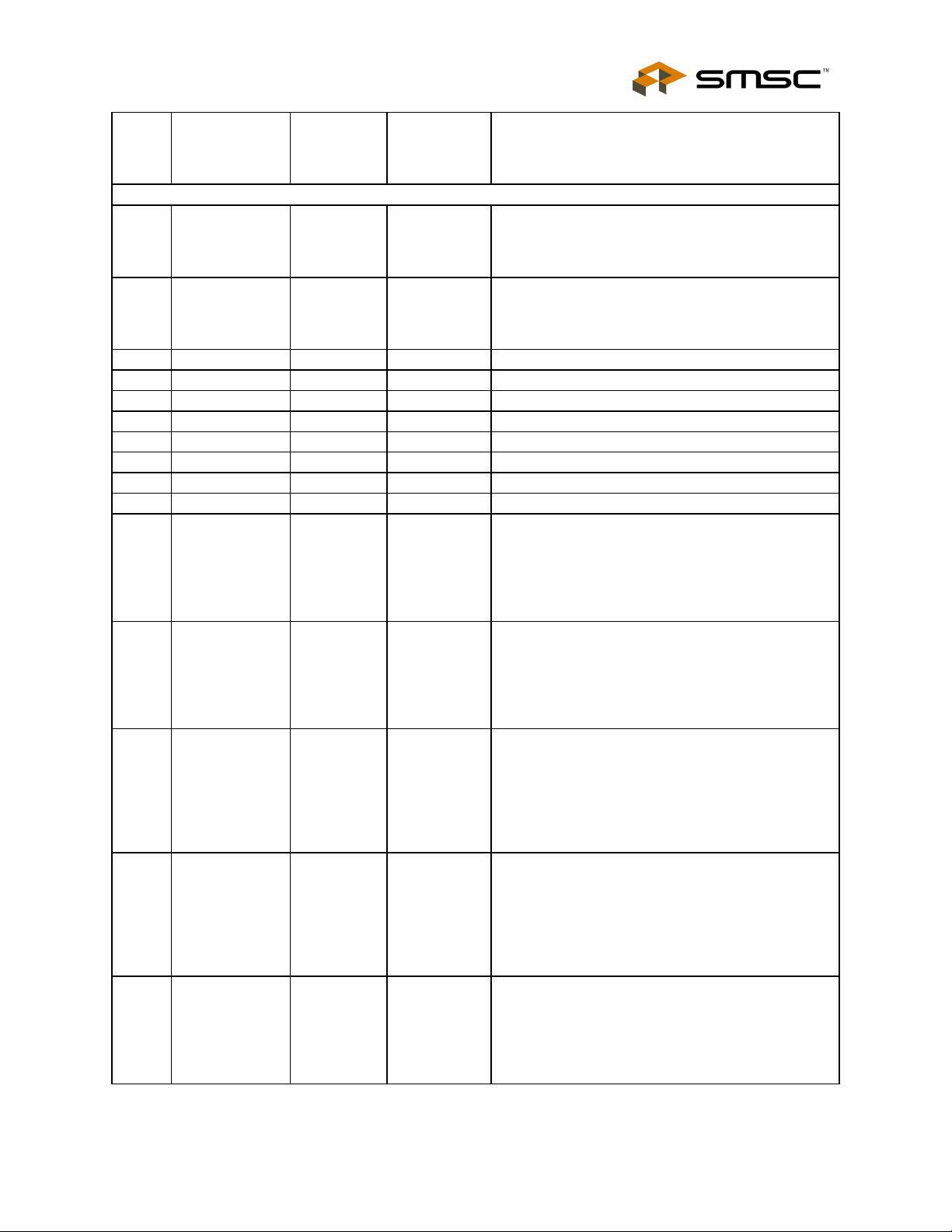

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

BUFFER

PIN # NAME SYMBOL

TYPE PER

FUNCTION

(NOTE 4.1)

DESCRIPTION

PARALLEL PORT INTERFACE (17)

41 Initiate Output

(Note 4.4)

nINIT (OD14/OP14)

This output is bit 2 of the printer control register. This

is used to initiate the printer when low.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

42 Printer Select

Input

(Note 4.4)

nSLCTIN (OD14/OP14) This active low output selects the printer. This is the

complement of bit 3 of the Printer Control Register.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

44 Port Data 0 PD0 IOP14 Port Data 0

46 Port Data 1 PD1 IOP14 Port Data 1

47 Port Data 2 PD2 IOP14 Port Data 2

48 Port Data 3 PD3 IOP14 Port Data 3

49 Port Data 4 PD4 IOP14 Port Data 4

50 Port Data 5 PD5 IOP14 Port Data 5

51 Port Data 6 PD6 IOP14 Port Data 6

53 Port Data 7 PD7 IOP14 Port Data 7

55 Printer Selected

Status

SLCT I This high active output from the printer indicates that it

has power on. Bit 4 of the Printer Status Register

reads the SLCT input.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

56 Paper End PE I Another status output from the printer, a high

indicating that the printer is out of paper. Bit 5 of the

Printer Status Register reads the PE input.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

57 Busy BUSY I This is a status output from the printer, a high

indicating that the printer is not ready to receive new

data. Bit 7 of the Printer Status Register is the

complement of the BUSY input.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

58 Acknowledge nACK I A low active output from the printer indicating that it

has received the data and is ready to accept new

data. Bit 6 of the Printer Status Register reads the

nACK input.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

59 Error nERROR I A low on this input from the printer indicates that there

is a error condition at the printer. Bit 3 of the Printer

Status register reads the nERR input.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

Revision 0.2 (06-10-03) Page 14 SMSC LPC47N217

DATASHEET

BUFFER

PIN # NAME SYMBOL

60 Autofeed Output

(Note 4.4)

nALF (OD14/OP14) This output goes low to cause the printer to

TYPE PER

FUNCTION

(NOTE 4.1)

automatically feed one line after each line is printed.

DESCRIPTION

The nALF output is the complement of bit 1 of the

Printer Control Register.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

61 Strobe Output

(Note 4.4)

nSTROBE (OD14/OP14) An active low pulse on this output is used to strobe the

printer data into the printer. The nSTROBE output is

the complement of bit 0 of the Printer Control

Register.

Refer to Parallel Port description for use of this pin in

ECP and EPP mode.

GENERAL PURPOSE I/O (14)

23-25,

27-31,

General Purpose

I/O

GP40-GP47

GP10

(I/O8/OD8) Dedicated General Purpose Input/Output.

32

33 General Purpose

I/O

(System Option)

(Note 4.5)

GP11/

(SYSOPT)

(I/O8/OD8) General Purpose Input/Output.

At the trailing edge of hardware reset the GP11 pin is

latched to determine the configuration base address: 0

= Index Base I/O Address 02E Hex; 1 = Index Base

I/O Address 04E Hex.

34 General Purpose

I/O/

System Mgt.

GP12/

IO_SMI#

(I/O12/OD12)/

(O12/OD12)

General Purpose Input/Output.

Active low System Management Interrupt Output.

Interrupt

35 General Purpose

I/O/ IRQ Input 1

GP13/

IRQIN1

(I/O8/OD8)/

I

General Purpose Input/Output.

External Interrupt Input. Steerable onto one of the 15

Serial IRQs.

36 General Purpose

I/O/ IRQ Input 2

GP14/

IRQIN2

(I/O8/OD8)/

I

General Purpose Input/Output.

External Interrupt Input. Steerable onto one of the 15

Serial IRQs.

40 General Purpose

GP23 (I/O8/OD8) General Purpose Input/Output.

I/O

CLOCK PINS (1)

9 14MHz Clock CLOCKI IS 14.318MHz Clock Input.

POWER PINS (9)

11, 26,

VCC VCC +3.3 Volt Supply Voltage.

45, 54

7 VTR VTR +3.3 Volt Standby Voltage.

8, 22,

VSS VSS Ground.

43, 52

64-Pin Super I/O with LPC Interface

Datasheet

Note 4.1 The "n" as the first letter of a signal name or the “#” as the suffix of a signal name indicates an “Active Low”

signal.

SMSC LPC47N217 Page 15 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

Note 4.2 Buffer types per function on multiplexed pins are separated by a slash “/”. Buffer types in parenthesis

represent multiple buffer types for a single pin function.

Note 4.3 The LPCPD# pin may be tied high.

Note 4.4 Active (push-pull) output drivers are required on these pins in the enhanced parallel port modes.

Note 4.5 The GP11/SYSOPT pin requires an external pulldown resistor to put the base IO address for configuration

at 0x02E. An external pullup resistor is required to move the base IO address for configuration to 0x04E.

Note 4.6 To activate the IRTX2 and IRRX2 pins set bits[7:6] IR Output Mux located in CR0A to ‘01’.

4.1 Buffer Type Description

I Input TTL Compatible.

IS Input with Schmitt Trigger.

O6 Output, 6mA sink, 3mA source.

O8 Output, 8mA sink, 4mA source.

OD8 Open Drain Output, 8mA sink.

IO8 Input/Output, 8mA sink, 4mA source.

O12 Output, 12mA sink, 6mA source.

OD12 Open Drain Output, 12mA sink.

IO12 Input/Output, 12mA sink, 6mA source.

OD14 Open Drain Output, 14mA sink.

OP14 Output, 14mA sink, 14mA source.

IOP14 Input/Output, 14mA sink, 14mA source. Backdrive protected.

PCI_I Input. These pins meet the PCI 3.3V AC and DC Characteristics.

PCI_O Output. These pins meet the PCI 3.3V AC and DC Characteristics. (Note 4.7)

PCI_OD Open Drain Output. These pins meet the PCI 3.3V AC and DC Characteristics.

PCI_IO Input/Output. These pins meet the PCI 3.3V AC and DC Characteristics.

PCI_ICLK Clock Input. These pins meet the PCI 3.3V AC and DC Characteristics and timing.

Note 4.7 See the PCI Local Bus Specification, Revision 2.1, Section 4.2.2.

(Note 4.7)

(Note 4.7)

(Note 4.7)

(Note 4.8)

Note 4.8 See the PCI Local Bus Specification, Revision 2.1, Section 4.2.2. and 4.2.3.

Revision 0.2 (06-10-03) Page 16 SMSC LPC47N217

DATASHEET

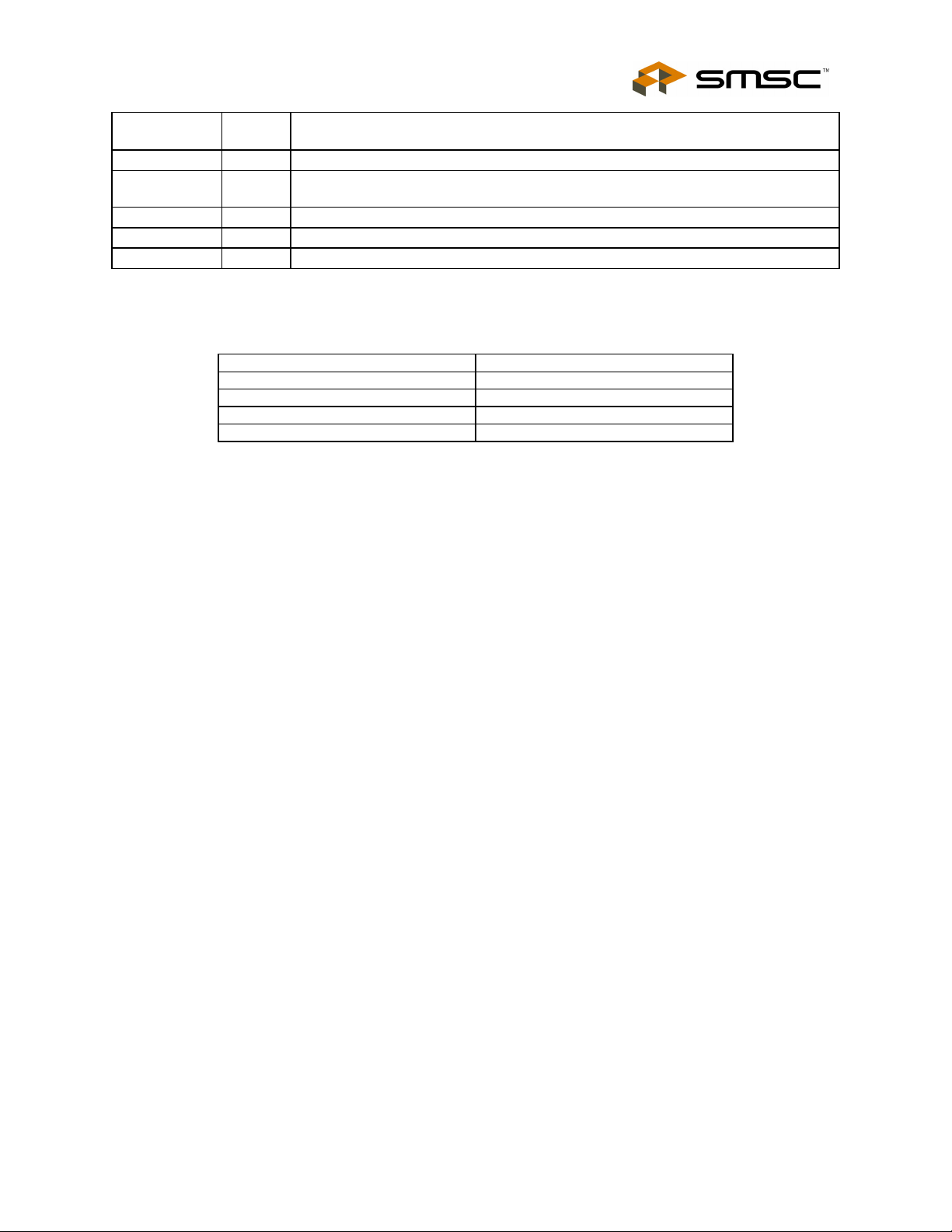

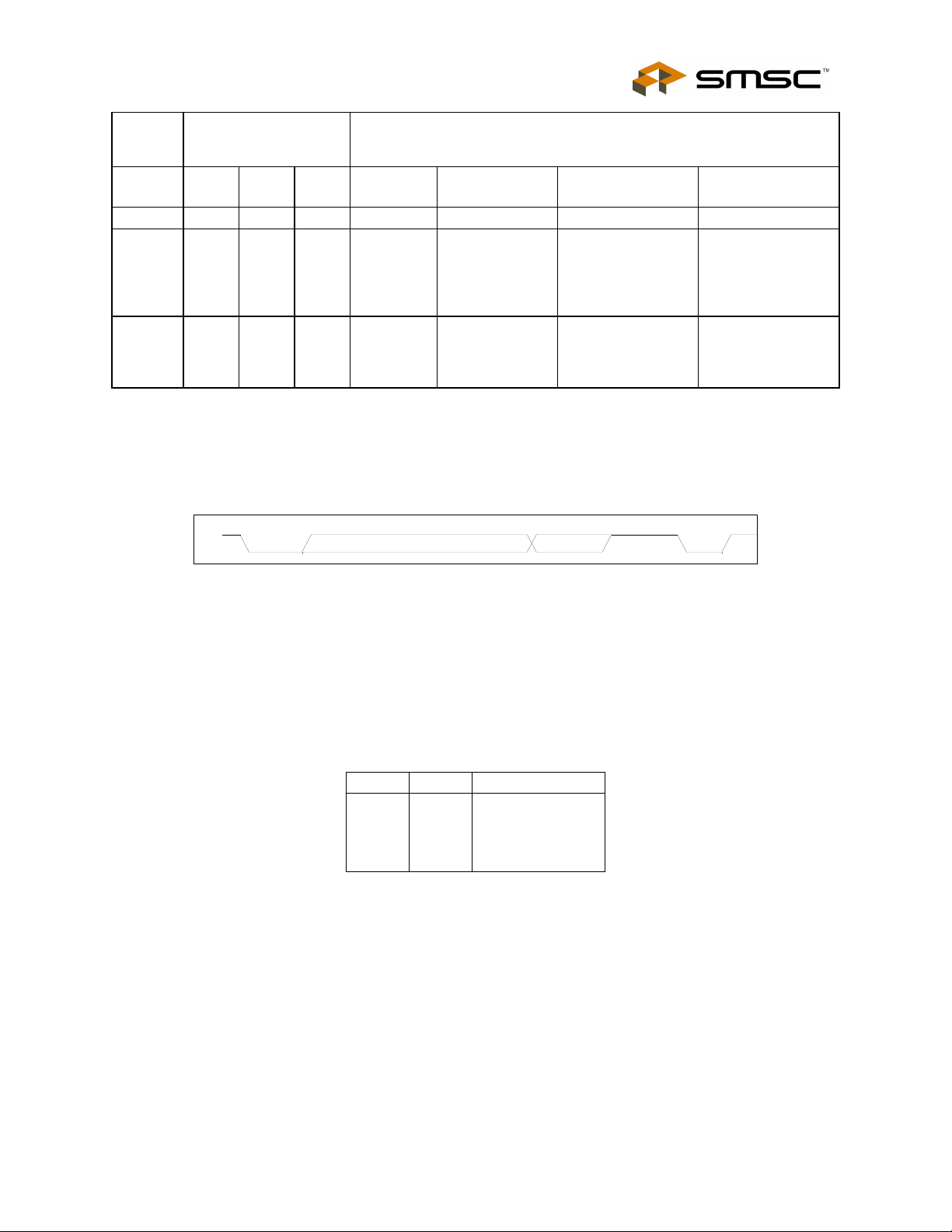

Chapter 5 Block Diagram

64-Pin Super I/O with LPC Interface

Datasheet

SER_IRQ

PCI_CLK

LAD0

LAD1

LAD2

LAD3

LFRAME#

LDRQ#

PCI_RESET#

LPCPD#

CLKRUN#

V

TR

Vcc

INTERFACE

Vss

SERIAL

IRQ

LPC BUS

IO_SMI#*

CLOCK

GEN

CLOCKI

IO_PME#

SMI PME WDT

CONTROL, ADDRESS, DATA

CONFIGURATION

REGISTERS

BLOCK

Figure 5.1 - LPC47N217 Block Diagram

ACPI

MULTI-MODE

PARALLEL

PORT

GENERAL

PURPOSE

I/O

16C550

COMPATIBLE

SERIAL

PORT 1

INFRARED

INTERFACE

PD[0:7],

BUSY, SLCT,

PE, nERROR, nACK

nSLCTIN, nALF

nINIT, nSTROBE

GP10, GP11,

GP12*, GP13*,

GP14*,

GP23*,

GP4[0:7]

IRQIN1*, IRQIN2*

TXD1, nRTS1, nDTR1

nCTS1, RXD1,

nDSR1, nDCD1, nRI1

IRTX2, IRMODE*

IRRX2, IRRX3*

*

Denotes Multifunction Pins

SMSC LPC47N217 Page 17 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

Chapter 6 3.3 Volt Operation / 5 Volt Tolerance

The LPC47N217 is a 3.3 Volt part. It is intended solely for 3.3V applications. Non-LPC bus pins are 5V

tolerant; that is, the input voltage is 5.5V max, and the I/O buffer output pads are backdrive protected.

The LPC interface pins are 3.3 V only. These signals meet PCI DC specifications for 3.3V signaling.

These pins are:

LAD[3:0]

LFRAME#

LDRQ#

LPCPD#

The input voltage for all other pins is 5.5V max. These pins include all non-LPC Bus pins and the following

pins:

PCI_RESET#

PCI_CLK

SER_IRQ

CLKRUN#

IO_PME#

Revision 0.2 (06-10-03) Page 18 SMSC LPC47N217

DATASHEET

Chapter 7 Power Functionality

The LPC47N217 has two power planes: VCC and VTR.

7.1 VCC Power

The LPC47N217 is a 3.3 Volt part. The VCC supply is 3.3 Volts (nominal). See Chapter 20 - Operational

Description and the Maximum Current Values subsection.

7.2 VTR Support

The LPC47N217 requires a trickle supply (VTR) to provide sleep current for the programmable wake-up

events in the PME interface when VCC is removed. The VTR supply is 3.3 Volts (nominal). See the

Operational Description section. The maximum VTR current that is required depends on the functions that

are used in the part. See Trickle Power Functionality subsection and the Maximum Current Values

subsection. If the LPC47N217 is not intended to provide wake-up capabilities on standby current, VTR can

be connected to VCC. The VTR pin generates a VTR Power-on-Reset signal to initialize these

components.

64-Pin Super I/O with LPC Interface

Datasheet

Note: If VTR is to be used for programmable wake-up events when VCC is removed, VTR must be at its full

minimum potential at least 10 µs before VCC begins a power-on cycle.

7.3 Internal PWRGOOD

An internal PWRGOOD logical control is included to minimize the effects of pin-state uncertainty in the

host interface as VCC cycles on and off. When the internal PWRGOOD signal is “1” (active), VCC > 2.3V

(nominal), and the LPC47N217 host interface is active. When the internal PWRGOOD signal is “0”

(inactive), VCC ≤ 2.3V (nominal), and the LPC47N217 host interface is inactive; that is, LPC bus reads and

writes will not be decoded.

The LPC47N217 device pins IO_PME#, nRI1, and most GPIOs (as input) are part of the PME interface

and remain active when the internal PWRGOOD signal has gone inactive, provided VTR is powered. See

Section 7.4 - Trickle Power Functionality.

7.4 Trickle Power Functionality

When the LPC47N217 is running under VTR only, the PME wakeup events are active and (if enabled) able

to assert the IO_PME# pin active low. The following lists the wakeup events:

UART 1 Ring Indicator

GPIOs for wakeup. See below.

The following requirements apply to all I/O pins that are specified to be 5 volt tolerant.

I/O buffers that are wake-up event compatible are powered by VCC. Under VTR power (VCC=0),

these pins may only be configured as inputs. These pins have input buffers into the wakeup logic that

are powered by VTR.

I/O buffers that may be configured as either push-pull or open drain under VTR power (VCC=0), are

powered by VTR. This means they will, at a minimum, source their specified current from VTR even

when VCC is present.

SMSC LPC47N217 Page 19 Revision 0.2 (06-10-03)

DATASHEET

64-Pin Super I/O with LPC Interface

Datasheet

The GPIOs that are used for PME wakeup inputs are GP10-GP14, GP23. These GPIOs function as

follows:

Buffers are powered by VCC, but in the absence of VCC they are backdrive protected (they do not

impose a load on any external VTR powered circuitry). They are wakeup compatible as inputs under

VTR power. These pins have input buffers into the wakeup logic that are powered by VTR.

All GPIOs listed above are for PME wakeup as a GPIO function (or alternate function).

See the Table in the GPIO section for more information.

The following list summarizes the blocks, registers and pins that are powered by VTR.

PME interface block

Runtime register block (includes all PME, SMI, GP data registers)

Pins for PME Wakeup:

− GPIOs (GP10-GP14, GP23)

− IO_PME#

− nRI1

7.5 Maximum Current Values

See Chapter 20 - Operational Description for the maximum current values.

The maximum VTR current, I

(i.e., 0V or 3.3V). The total maximum current for the part is the unloaded value PLUS the maximum

current sourced by the pin that is driven by VTR. The pin that is powered by VTR (as output) is IO_PME#.

This pin, if configured as a push-pull output, will source a minimum of 6mA at 2.4V when driving.

The maximum VCC current, I

(i.e., 0V or 3.3V).

, is given with all outputs open (not loaded), and all inputs in a fixed state

TR

, is given with all outputs open (not loaded), and all inputs in a fixed state

CC

7.6 Power Management Events (PME/SCI)

The LPC47N217 offers support for Power Management Events (PMEs), also referred to as System Control

Interrupt (SCI) events. The terms PME and SCI are used synonymously throughout this document to refer

to the indication of an event to the chipset via the assertion of the IO_PME# pin. See PME Support Chapter 17.

Revision 0.2 (06-10-03) Page 20 SMSC LPC47N217

DATASHEET

Chapter 8 Functional Description

8.1 Super I/O Registers

The address map, shown below in Table 8.1, shows the addresses of the different blocks of the Super I/O

immediately after power up. The base addresses of the serial and parallel ports, runtime register block,

and configuration register block can be moved via the configuration registers. Some addresses are used to

access more than one register.

8.2 Host Processor Interface (LPC)

The host processor communicates with the LPC47N217 through a series of read/write registers via the

LPC interface. The port addresses for these registers are shown in Table 8.1. Register access is

accomplished through I/O cycles or DMA transfers. All registers are 8 bits wide.

Table 8.1 - Super I/O Block Addresses

ADDRESS BLOCK NAME NOTES

Base+(0-7) Serial Port Com 1

Base1+(0-7)

Base2+(0-7)

Base+(0-3)

Base+(0-7)

Base+(0-3), +(400-402)

Base+(0-7), +(400-402)

Base + (0-F) Runtime Registers

Base + (0-1) Configuration

Serial Port Com 2

Parallel Port

SPP

EPP

ECP

ECP+EPP+SPP

IR Support

FIR and CIR

64-Pin Super I/O with LPC Interface

Datasheet

Note 1: Refer to the configuration register descriptions for setting the base address.

8.3 LPC Interface

The following sub-sections specify the implementation of the LPC bus.

8.3.1 LPC Interface Signal Definition

The signals required for the LPC bus interface are described in the table below. LPC bus signals use PCI