Page 1

LAN9420/LAN9420i

Single-Chip Ethernet Controller

with HP Auto-MDIX Support

and PCI Interface

PRODUCT FEATURES

Highlights

Optimized fo r embedded applications with 32-bit

RISC CPUs

Integra ted descriptor based scatter-gather DMA and

IRQ deassertion timer effectively increase network

throughput and reduce CPU loading

Integra ted Ethernet MAC with full-duplex support

Integra ted 10/100 Ethernet PHY with HP Auto-MDIX

support

3 2-bit, 33MHz, PCI 3.0 compliant interface

Re duced power operating modes with PCI Power

Management Specification 1.1 compliance

Sup ports multiple audio & video streams over

Ethernet

Target Applications

Ca ble, satellite, and IP set-top boxes

Digital televisions

Di gital video recorders

Ho me gateways

Di gital media clients/servers

Industrial au tomation systems

Indu strial/single board PC

Kio sk/POS enterprise equipment

Key Benefits

Integra ted High-Performance 10/100 Ethernet

Controller

— Fully compliant with IEEE802.3/802.3u

— Integrated Ethernet MAC and PHY

— 10BASE-T and 100BASE-TX support

— Full- and half-duplex support

— Full-duplex flow control

— Preamble generation and removal

— Automatic 32-bit CRC generation and checking

— Automatic payload padding and pad removal

— Loop-back modes

— Flexible address filtering modes

– One 48-bit perfect address

– 64 hash-filtered multicast addresses

– Pass all multicast

Datasheet

– Promiscuous mode

– Inverse filtering

– Pass all incoming with status report

— Wakeup packet support

— Integrated 10/100 Ethernet PHY

– Auto-negotiation

– Automatic polarity detection and correction

– Supports HP Auto-MDIX

– Supports energy-detect power down

— Support for 3 status LEDs

— Receive and transmit TCP checksum offload

PCI Interface

— PCI Local Bus Specification Revision 3.0 compliant

— 32-bit/33-MHz PCI bus

— Descriptor based scatter-gather DMA enables zero-

copy drivers

C omprehensive Power Management Features

— Supports PCI Bus Power Management Interface

Specification, Revision 1.1

— Supports optional wake from D3cold

(via configuration strap option when Vaux is available)

— Wake on LAN

— Wake on link status change (energy detect)

— Magic packet wakeup

Gene ral Purpose I/O

— 3 programmable GPIO pins

— 2 GPO pins

Su pport for Optional EEPROM

— Serial interface provided for EEPROM

— Used to store PCI and MAC address configuration

values

Misce llaneous Features

— Big/Little/Mixed endian support for registers,

descriptors, and buffers

— IRQ deassertion timer

— General purpose timer

Si ngle 3.3V Power Supply

— Integrated 1.8V regulator

Packaging

— Available in 128-pin VTQFP Lead-free RoHS Compliant

package

Environmental

— Available in commercial & industrial temperature ranges

SMSC LAN9420/LAN9420i DATASHEET Revision 1.22 (09-25-08)

Page 2

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

ORDER NUMBERS:

LAN9420-NU FOR 128-PIN VTQFP, LEAD-FREE ROHS COMPLIANT PACKAGE (0 TO 70oC)

LAN9420i-NU FOR 128-PIN VTQFP, LEAD-FREE ROHS COMPLIANT PACKAGE (-40o TO 85oC)

Datasheet

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2008 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a mean s of illustrating typical applications. Conse quently, complete information sufficient for

construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC

reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications

before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent

rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently da ted

version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors

known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not

designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property

damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of

this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC’s website at http://www.smsc.com. SMSC is a registered

trademark of Standard Microsystems Corporation (“SMSC”). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY,

FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE

OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL

DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT;

TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD

TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Revision 1.22 (09-25-08) 2 SMSC LAN9420/LAN9420i

DATASHEET

Page 3

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Table of Contents

Chapter 1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.1 Block Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.2 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

1.3 PCI Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.4 DMA Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.5 Ethernet MAC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.6 Ethernet PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.7 System Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.7.1 Interrupt Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1.7.2 PLL and Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.7.3 EEPROM Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.7.4 GPIO/LED Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.7.5 General Purpose Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.7.6 Free Run Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1.8 Control and Status Registers (CSR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Chapter 2 Pin Description and Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.1 Pin List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.2 Buffer Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Chapter 3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.1 Functional Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2 PCI Bridge (PCIB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.2.1 PCI Bridge (PCIB) Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.2.2 PCI Interface Environments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2.3 PCI Master Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.2.3.1 PCI Master Transaction Errors.......................................................................................25

3.2.4 PCI Target Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.2.4.1 PCI Configuration Space Registers ...............................................................................26

3.2.4.2 Control and Status Registers (CSR)..............................................................................26

3.2.4.2.1 CSR Endianness.......................................................................................................26

3.2.4.2.2 I/O Mapping of CSR..................... ... ... ... .... ... ....................................... ... ... ... ... .... ......27

3.2.4.3 PCI Target Interface Transaction Errors........................................................................27

3.2.4.4 PCI Discard Timer..........................................................................................................27

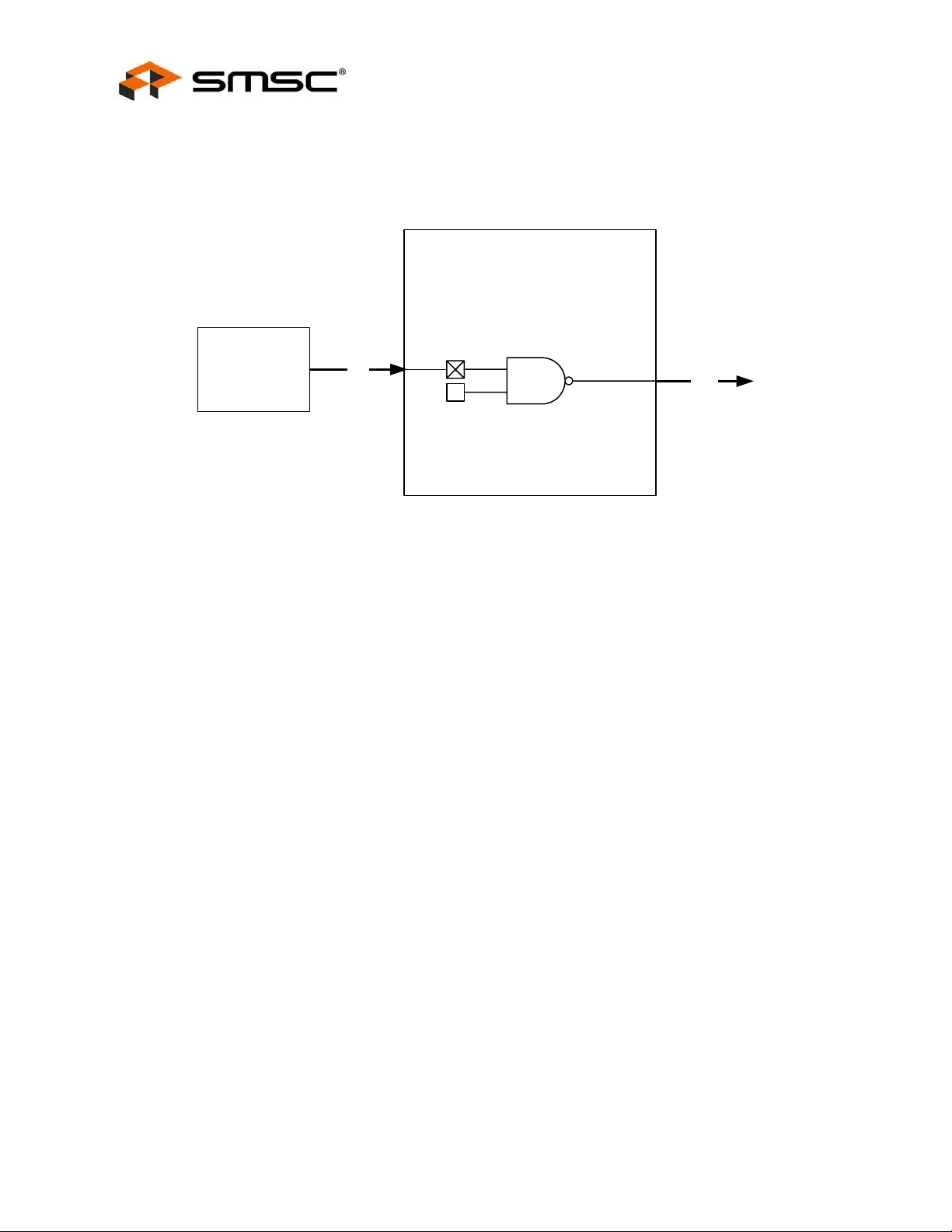

3.2.5 Interrupt Gating Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.3 System Control Block (SCB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

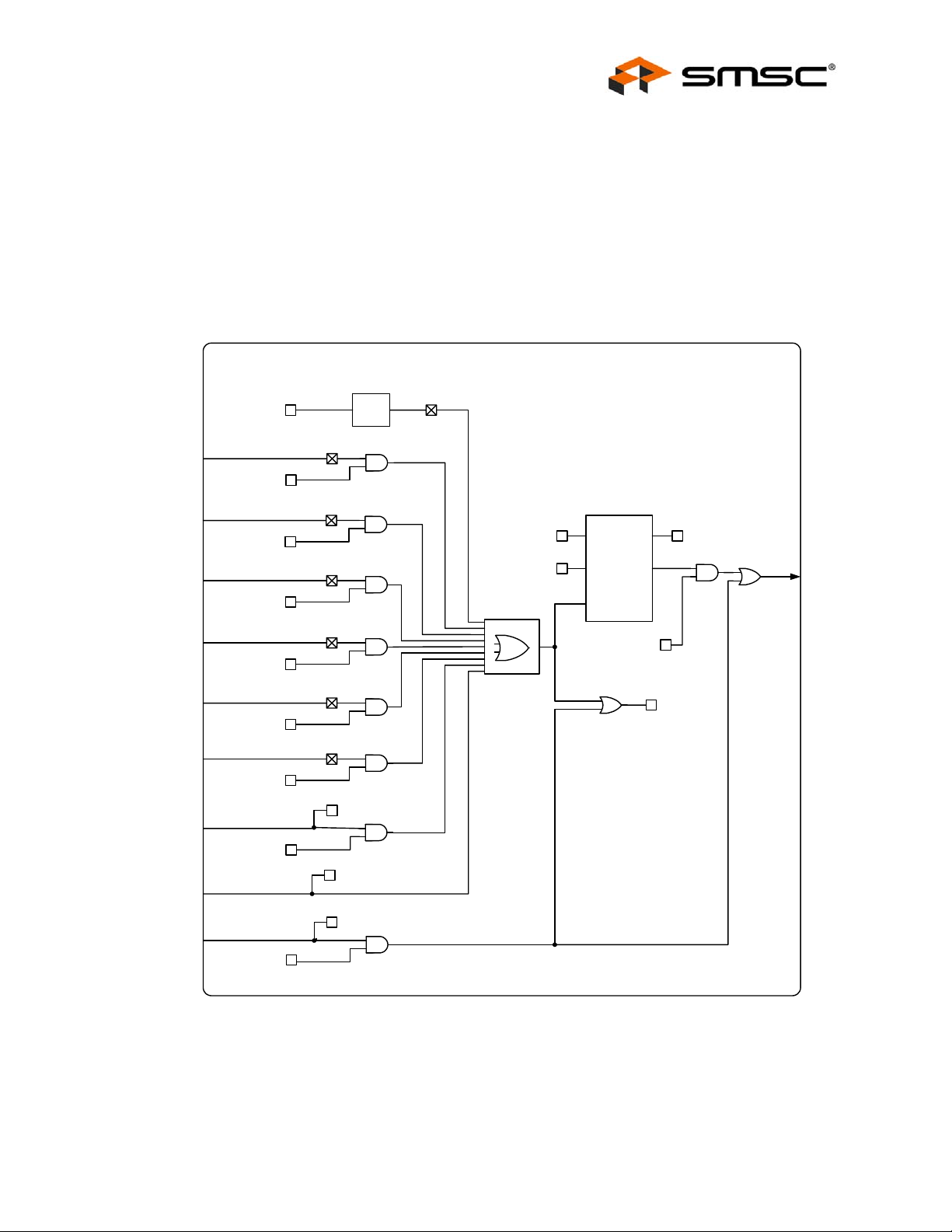

3.3.1 Interrupt Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.3.2 Wake Event Detection Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.3.3 General Purpose Timer (GPT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.3.4 Free-Run Counter (FRC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.3.5 EEPROM Controller (EPC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.3.5.1 EEPROM Format...........................................................................................................31

3.3.5.2 MAC Address, Subsystem ID, and Subsystem Vendor ID Auto-Load...........................32

3.3.5.3 EEPROM Host Operations.............................................................................................32

3.3.5.3.1 Supported EEPROM Operations..............................................................................33

3.3.5.3.2 Host Initiated MAC Address, SSID, SSVID Reload..................................................37

3.3.5.3.3 EEPROM Command and Data Registers.................................................................37

3.3.5.3.4 EEPROM Timing.......................................................................................................37

3.3.6 System Control and Status Registers (SCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.4 DMA Controller (DMAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.4.1 DMA Controller Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

SMSC LAN9420/LAN9420i 3 Revision 1.22 (09-25-08)

DATASHEET

Page 4

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

3.4.2 Data Descriptors and Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.4.2.1 Receive Descriptors.......................................................................................................41

3.4.2.2 Transmit descriptors.......................................................................................................45

3.4.3 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.4.4 Transmit Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.4.5 Receive Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.4.6 Receive Descriptor Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.4.7 Suspend State Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.4.7.1 Transmit Engine.............................................................................................................51

3.4.7.2 Receive Engine..............................................................................................................51

3.4.8 Stopping Transmission and Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.4.9 TX Buffer Fragmentation Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.4.9.1 Calculating Worst-Case TX FIFO (MIL) Usage................. ... ... .... ... ... ... .... ... ... ................52

3.4.10 DMAC Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.4.11 DMAC Control and Status Registers (DCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.5 10/100 Ethernet MAC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.5.1 Flow Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.5.1.1 Full-Duplex Flow Control................................................................................................54

3.5.2 Virtual Local Area Network (VLAN) Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.5.3 Address Filtering Functional Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.5.3.1 Perfect Filtering..............................................................................................................56

3.5.3.2 Hash Only Filtering Mode...............................................................................................56

3.5.3.3 Hash Perfect Filtering ....................................................................................................56

3.5.3.4 Inverse Filtering .............................................................................................................56

3.5.4 Wakeup Frame Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.5.4.1 Magic Packet Detection .................................................................................................59

3.5.5 Receive Checksum Offload Engine (RXCOE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

3.5.5.1 RX Checksum Calculation ......................... .... ... ... ... .... ...................................... ... .... ... ...63

3.5.6 Transmit Checksum Offload Engine (TXCOE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.5.6.1 TX Checksum Calculation..............................................................................................64

3.5.7 MAC Control and Status Registers (MCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

3.6 10/100 Ethernet PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

3.6.1 100BASE-TX Transmit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.6.1.1 4B/5B Encoding .............................................................................................................65

3.6.1.2 Scrambling.....................................................................................................................66

3.6.1.3 NRZI and MLT3 Encoding .............................................................................................67

3.6.1.4 100M Transmit Driver................................. .... ... ... ... .... ... ... ... ....................................... ...67

3.6.1.5 100M Phase Lock Loop (PLL) .......................................................................................67

3.6.2 100BASE-TX Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.6.2.1 100M Receive Input.................................................................... ... ... ... .... ... ... ... ... ..........67

3.6.2.2 Equalizer, Baseline Wander Correction and Clock and Data Recovery ........................67

3.6.2.3 NRZI and MLT-3 Decoding............................... ... ... .... ... ... ....................................... ... ...68

3.6.2.4 Descrambling.................................................................................................................68

3.6.2.5 Alignment.......................................................................................................................68

3.6.2.6 5B/4B Decoding.............................................................................................................68

3.6.2.7 Receiver Errors..............................................................................................................68

3.6.3 10BASE-T Transmit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.6.3.1 10M Transmit Data Across the Internal MII Bus ............................................................69

3.6.3.2 Manchester Encoding ....................................................................................................69

3.6.3.3 10M Transmit Drivers.....................................................................................................69

3.6.4 10BASE-T Receive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.6.4.1 10M Receive Input and Squelch....................................................................................69

3.6.4.2 Manchester Decoding....................................................................................................69

3.6.4.3 Jabber Detection............................................................................................................70

3.6.5 Auto-negotiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Revision 1.22 (09-25-08) 4 SMSC LAN9420/LAN9420i

DATASHEET

Page 5

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

3.6.6 Parallel Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

3.6.6.1 Re-starting Auto-negotiation ................... ... .... ... ... ... .... ... ... ....................................... ... ...71

3.6.6.2 Disabling Auto-negotiation.............................................................................................71

3.6.6.3 Half vs. Full-Duplex........................................................................................................72

3.6.7 HP Auto-MDIX. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

3.6.8 PHY Power-Down Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

3.6.8.1 General Power-Down . ....................................... ... ... .... ... ...................................... .... ... ...72

3.6.8.2 Energy Detect Power-Down...........................................................................................73

3.6.9 PHY Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.6.9.1 PHY Soft Reset via PMT_CTRL bit 10 (PHY_RST).......................................................73

3.6.9.2 PHY Soft Reset via PHY Basic Control Register bit 15 (PHY Reg. 0.15)......................73

3.6.10 Required Ethernet Magnetics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.6.11 PHY Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.7 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.7.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.7.2 Related External Signals and Power Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.7.3 Device Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.7.4 Power States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3.7.4.1 G3 State (Mechanical Off) .............................................................................................75

3.7.4.1.1 Power Management Events in

G3................................................................................................. 75

3.7.4.1.2 Exiting the G3 State..................................................................................................76

3.7.4.2 D0UNINTIALIZED State (D0U)......................................................................................76

3.7.4.2.1 Exiting the D0U State................................................................................................76

3.7.4.3 D0ACTIVE State (D0A). .... ... ... ... ....................................... ... ... .... ... ... ... .... ... ...................76

3.7.4.3.1 Power Management Events in

D0A............................................................................................... 76

3.7.4.3.2 Exiting the D0A State................................................................................................77

3.7.4.4 The D3HOT State ..........................................................................................................77

3.7.4.4.1 Power Management Events in

D3HOT.......................................................................................... 77

3.7.4.4.2 Exiting the D3HOT State...........................................................................................77

3.7.4.5 The D3COLD State........................................................................................................78

3.7.4.5.1 Power Management Events in

D3COLD....................................................................................... 78

3.7.4.5.2 Exiting the D3COLD State ........................................................................................78

3.7.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

3.7.5.1 PHY Resets .. ... ....................................... ... .... ...................................... .... ... ...................80

3.7.6 Detecting Power Management Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

3.7.6.1 Enabling Wakeup Frame Wake Events .........................................................................81

3.7.7 Enabling Link Status Change (Energy Detect) Wake Events . . . . . . . . . . . . . . . . . . . . . 81

Chapter 4 Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.1 Register Nomenclature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

4.2 System Control and Status Registers (SCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

4.2.1 ID and Revision (ID_REV). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4.2.2 Interrupt Control Register (INT_CTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.2.3 Interrupt Status Register (INT_STS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

4.2.4 Interrupt Configuration Register (INT_CFG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4.2.5 General Purpose Input/Output Configuration Register (GPIO_CFG) . . . . . . . . . . . . . . . 92

4.2.6 General Purpose Timer Configuration Register (GPT_CFG) . . . . . . . . . . . . . . . . . . . . . 94

4.2.7 General Purpose Timer Current Count Register (GPT_CNT). . . . . . . . . . . . . . . . . . . . . 95

4.2.8 Bus Master Bridge Configuration Register (BUS_CFG) . . . . . . . . . . . . . . . . . . . . . . . . . 96

4.2.9 Power Management Control Register (PMT_CTRL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

4.2.10 Free Run Counter (FREE_RUN). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

4.2.11 EEPROM Command Register (E2P_CMD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

4.2.12 EEPROM Data Register (E2P_DATA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

4.3 DMAC Control and Status Registers (DCSR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

4.3.1 Bus Mode Register (BUS_MODE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

SMSC LAN9420/LAN9420i 5 Revision 1.22 (09-25-08)

DATASHEET

Page 6

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

4.3.2 Transmit Poll Demand Register (TX_POLL_DEMAND) . . . . . . . . . . . . . . . . . . . . . . . . 105

4.3.3 Receive Poll Demand Register (RX_POLL_DEMAND). . . . . . . . . . . . . . . . . . . . . . . . . 106

4.3.4 Receive List Base Address Register (RX_BASE_ADDR). . . . . . . . . . . . . . . . . . . . . . . 107

4.3.5 Transmit List Base Address Register (TX_BASE_ADDR). . . . . . . . . . . . . . . . . . . . . . . 108

4.3.6 DMA Controller Status Register (DMAC_STATUS) . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

4.3.7 DMA Controller Control (Operation Mode) Register (DMAC_CONTROL) . . . . . . . . . . 111

4.3.8 DMA Controller Interrupt Enable Register (DMAC_INTR_ENA) . . . . . . . . . . . . . . . . . . 113

4.3.9 Missed Frame and Buffer Overflow Counter Reg (MISS_FRAME_CNTR). . . . . . . . . . 115

4.3.10 Current Transmit Buffer Address Register (TX_BUFF_ADDR). . . . . . . . . . . . . . . . . . . 116

4.3.11 Current Receive Buffer Address Register (RX_BUFF_ADDR) . . . . . . . . . . . . . . . . . . . 117

4.4 MAC Control and Status Registers (MCSR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

4.4.1 MAC Control Register (MAC_CR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

4.4.2 MAC Address High Register (ADDRH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

4.4.3 MAC Address Low Register (ADDRL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

4.4.4 Multicast Hash Table High Register (HASHH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

4.4.5 Multicast Hash Table Low Register (HASHL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

4.4.6 MII Access Register (MII_ACCESS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

4.4.7 MII Data Register (MII_DATA). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

4.4.8 Flow Control Register (FLOW) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

4.4.9 VLAN1 Tag Register (VLAN1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

4.4.10 VLAN2 Tag Register (VLAN2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

4.4.11 Wakeup Frame Filter (WUFF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

4.4.12 Wakeup Control and Status Register (WUCSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

4.4.13 Checksum Offload Engine Control Register (COE_CR) . . . . . . . . . . . . . . . . . . . . . . . . 134

4.5 PHY Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

4.5.1 Basic Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

4.5.2 Basic Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

4.5.3 PHY Identifier 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

4.5.4 PHY Identifier 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

4.5.5 Auto Negotiation Advertisement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

4.5.6 Auto Negotiation Link Partner Ability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

4.5.7 Auto Negotiation Expansion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

4.5.8 Mode Control/Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

4.5.9 Special Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

4.5.10 Special Control/Status Indications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

4.5.11 Interrupt Source Flag. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

4.5.12 Interrupt Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

4.5.13 PHY Special Control/Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

4.6 PCI Configuration Space CSR (CONFIG CSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

4.6.1 PCI Power Management Capabilities Register (PCI_PMC) . . . . . . . . . . . . . . . . . . . . . 151

4.6.2 PCI Power Management Control and Status Register (PCI_PMCSR) . . . . . . . . . . . . . 153

Chapter 5 Operational Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

5.1 Absolute Maximum Ratings*. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

5.2 Operating Conditions**. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

5.3 Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

5.3.1 D0 - Normal Operation with Ethernet Traffic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

5.3.2 D3 - Enabled for Wake Up Packet Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

5.3.3 D3 - Enabled for Link Status Change Detection (Energy Detect) . . . . . . . . . . . . . . . . . 157

5.3.4 D3 - PHY in General Power Down Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

5.3.5 Maximum Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

5.4 DC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

5.5 AC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

5.5.1 Equivalent Test Load (Non-PCI Signals). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

5.6 PCI Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Revision 1.22 (09-25-08) 6 SMSC LAN9420/LAN9420i

DATASHEET

Page 7

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

5.7 PCI I/O Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

5.8 EEPROM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

5.9 Clock Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Chapter 6 Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

6.1 128-VTQFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Chapter 7 Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

SMSC LAN9420/LAN9420i 7 Revision 1.22 (09-25-08)

DATASHEET

Page 8

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

List of Figures

Figure 1.1 System Level Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 1.2 LAN9420/LAN9420i Internal Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

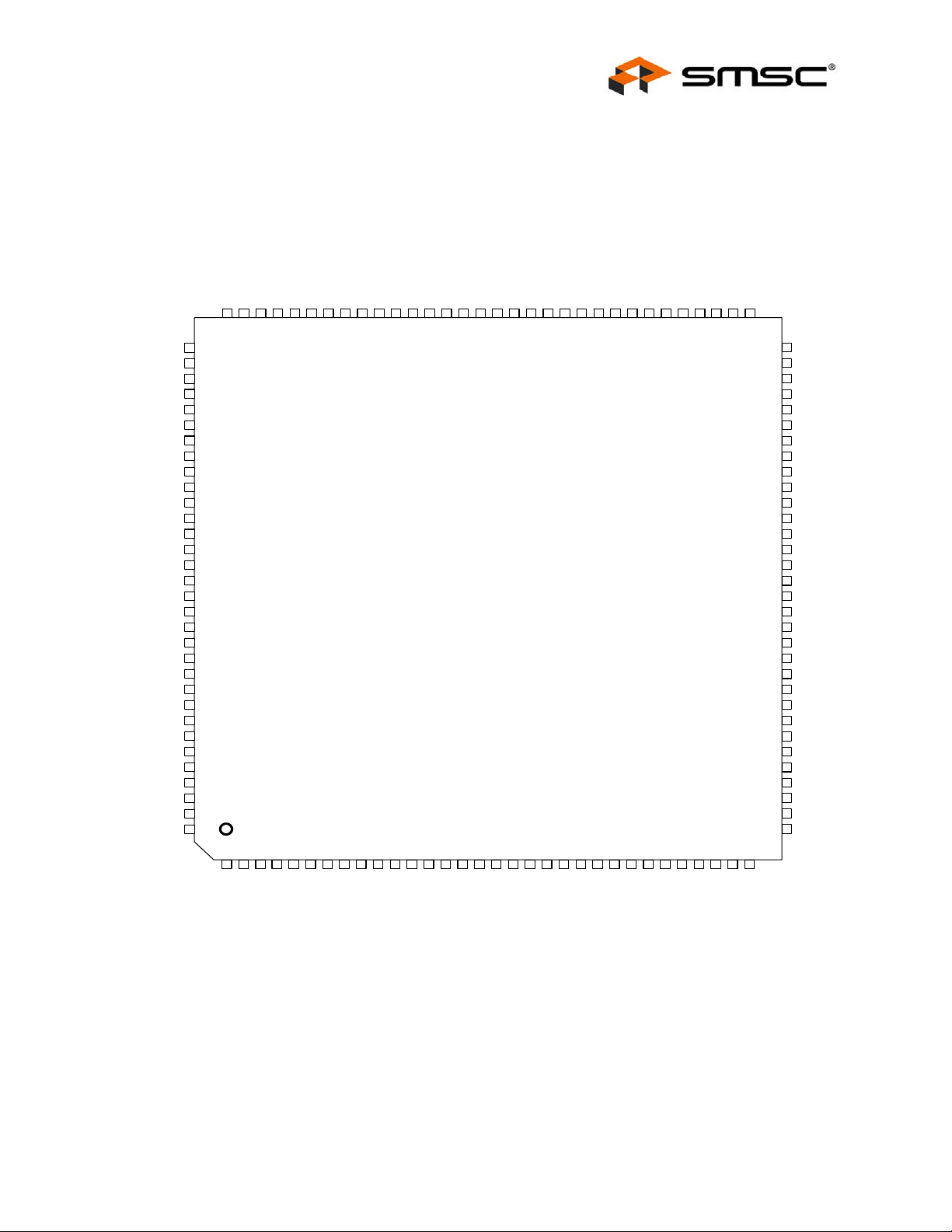

Figure 2.1 LAN9420/LAN9420i 128-VTQFP (Top View). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 3.1 PCI Bridge Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 3.2 Device Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 3.3 CSR Double Endian Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 3.4 I/O Bar Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 3.5 Interrupt Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 3.6 Interrupt Controller Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 3.7 EEPROM Access Flow Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 3.8 EEPROM ERASE Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 3.9 EEPROM ERAL Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 3.10 EEPROM EWDS Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 3.11 EEPROM EWEN Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 3.12 EEPROM READ Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 3.13 EEPROM WRITE Cycle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 3.14 EEPROM WRAL Cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 3.15 Ring and Chain Descriptor Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 3.16 Receive Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 3.17 Transmit Descriptor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Figure 3.18 VLAN Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 3.19 RXCOE Checksum Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 3.20 Type II Ethernet Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 3.21 Ethernet Frame with VLAN Tag. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 3.22 Ethernet Frame with Length Field and SNAP Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 3.23 Ethernet Frame with VLAN Tag and SNAP Header. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 3.24 Ethernet Frame with multiple VLAN Tags and SNAP Header . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 3.25 100BASE-TX Data Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 3.26 Receive Data Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 3.27 Direct Cable Connection vs. Cross-Over Cable Connection . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 3.28 LAN9420/LAN9420i Device Power States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 3.29 Wake Event Detection Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 4.1 LAN9420/LAN9420i CSR Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Figure 4.2 Example ADDRL, ADDRH Address Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 5.1 Output Equivalent Test Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Figure 5.2 PCI Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Figure 5.3 PCI I/O Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 5.4 EEPROM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Figure 6.1 LAN9420/LAN9420i 128-VTQFP Package Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Figure 6.2 LAN9420/LAN9420i 128-VTQFP Recommended PCB Land Pattern . . . . . . . . . . . . . . . . . 168

Revision 1.22 (09-25-08) 8 SMSC LAN9420/LAN9420i

DATASHEET

Page 9

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

List of Tables

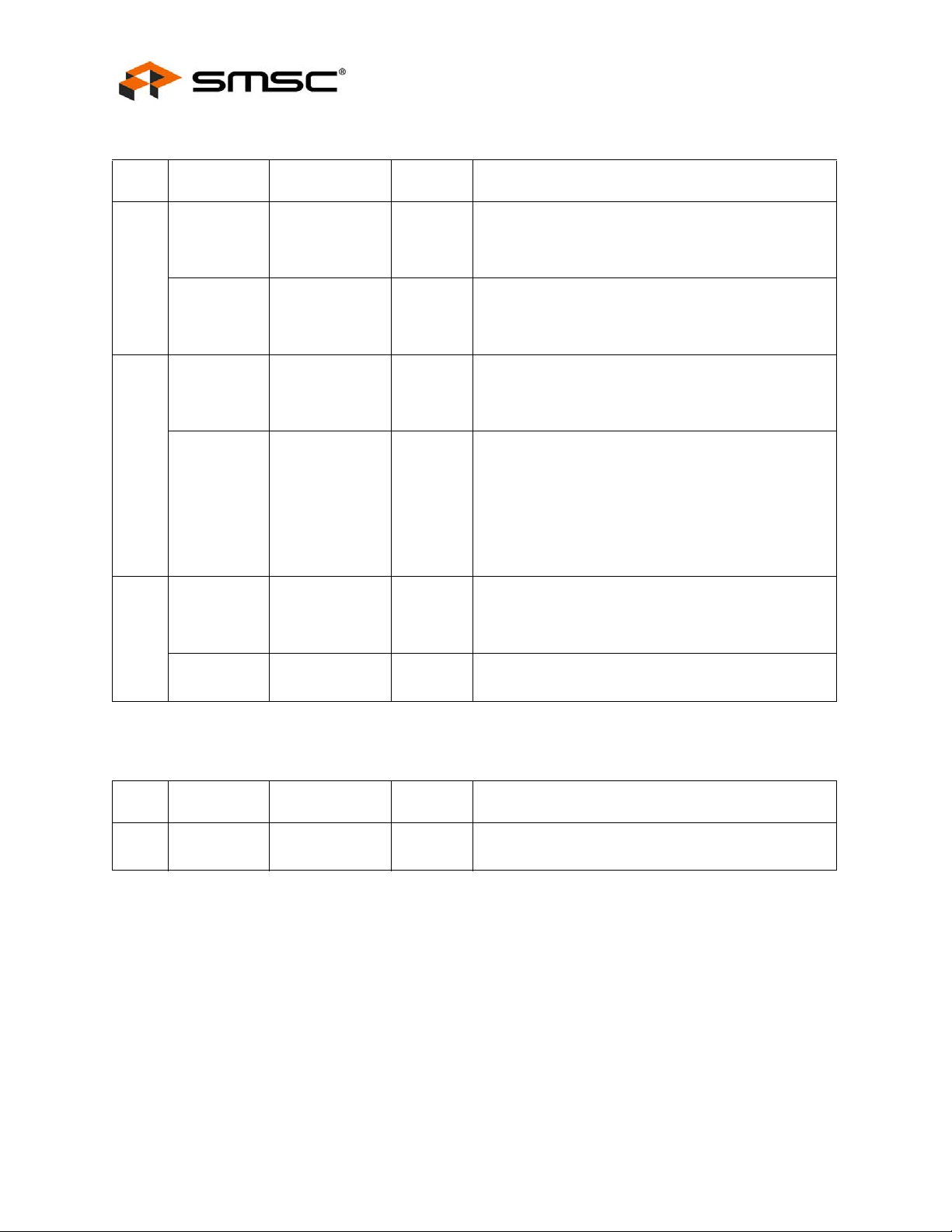

Table 2.1 PCI Bus Interface Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2.2 EEPROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 2.3 GPIO and LED Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 2.4 Configuration Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 2.5 PLL and Ethernet PHY Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 2.6 Power and Ground Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 2.7 No-Connect Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 2.8 128-VTQFP Package Pin Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 3.1 PCI Address Spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 3.2 EEPROM Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 3.3 EEPROM Variable Defaults. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 3.4 Required EECLK Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 3.5 RDES0 Bit Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 3.6 RDES1 Bit Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 3.7 RDES2 Bit Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 3.8 RDES3 Bit Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 3.9 TDES0 Bit Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 3.10 TDES1 Bit Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 3.11 TDES2 Bit Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 3.12 TDES3 Bit Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 3.13 Address Filtering Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 3.14 Wakeup Frame Filter Register Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 3.15 Filter i Byte Mask Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 3.16 Filter i Command Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 3.17 Filter i Offset Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 3.18 Filter i CRC-16 Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 3.19 Wakeup Generation Cases . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 3.20 TX Checksum Preamble . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 3.21 4B/5B Code Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 3.22 Reset Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 3.23 PHY Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 4.1 Register Bit Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 4.2 System Control and Status Register Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 4.3 EEPROM Enable Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 4.4 DMAC Control and Status Register (DCSR) Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 4.5 MAC Control and Status Register (MCSR) Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 4.6 ADDRL, ADDRH Byte Ordering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 4.7 PHY Control and Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 4.8 MODE Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 4.9 PCI Configuration Space CSR (CONFIG CSR) Address Map . . . . . . . . . . . . . . . . . . . . . . . 149

Table 4.10 Standard PCI Header Registers Supported. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table 5.1 D0 - Normal Operation - Supply and Current (Typical) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Table 5.2 D3 - Enabled for Wake Up Packet Detection - Supply and Current (Typical) . . . . . . . . . . . . 157

Table 5.3 D3 - Enabled for Link Status Change Detection - Supply and Current (Typical). . . . . . . . . . 157

Table 5.4 D3 - PHY in General Power Down Mode - Supply and Current (Typical) . . . . . . . . . . . . . . . 158

Table 5.5 Maximum Power Consumption - Supply and Current (Maximum). . . . . . . . . . . . . . . . . . . . . 158

Table 5.6 I/O Buffer Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Table 5.7 100BASE-TX Transceiver Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 5.8 10BASE-T Transceiver Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 5.9 PCI Clock Timing Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 5.10 PCI I/O Timing Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Table 5.11 PCI I/O Timing Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 5.12 EEPROM Timing Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

SMSC LAN9420/LAN9420i 9 Revision 1.22 (09-25-08)

DATASHEET

Page 10

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Table 5.13 LAN9420/LAN9420i Crystal Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Table 6.1 LAN9420/LAN9420i 128-VTQFP Dimensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Table 7.1 Customer Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Revision 1.22 (09-25-08) 10 SMSC LAN9420/LAN9420i

DATASHEET

Page 11

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Chapter 1 Introduction

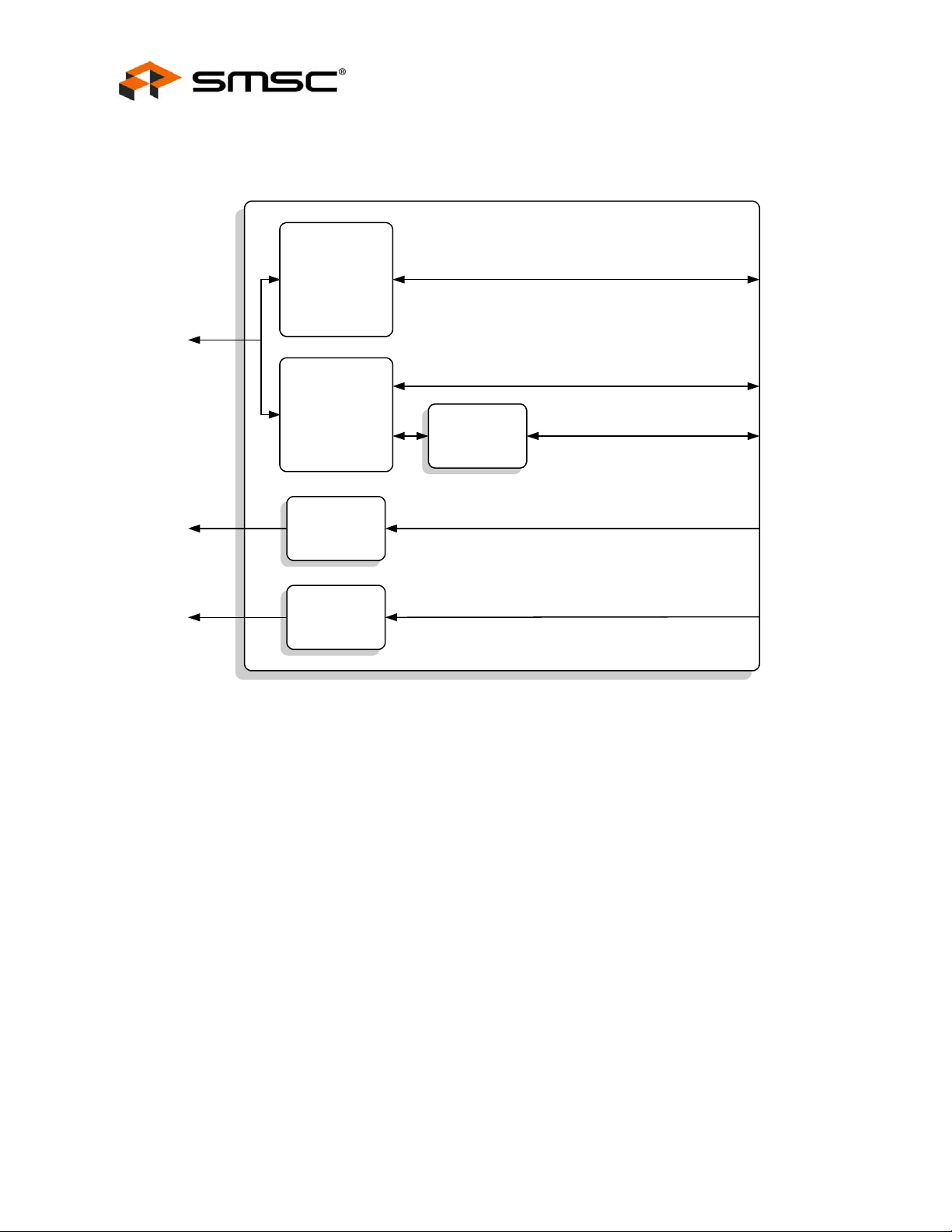

1.1 Block Diagrams

PCI Host

EEPROM

(optional)

PCI

PCI Brid ge (P CIB )

PCI Master

PCI Target

PCI Bus

LAN9420/LAN9420i

PCI Device

PCI Device

External

25MHz Crystal

Figure 1.1 System Level Block Diagram

DMA Controller

Arbiter

TX DMA Engine

RX DMA Engine

DMA Control &

Status Registers

(DCSR)

TX FIFO (2KB)

RX FIFO (2KB)

MAC Interface Layer

(MIL)

Ethernet MAC

TX COE

RX COE

MAC Control & S tatus

Registers (MCSR)

Magnetics

GPIOs/LEDs

(optional)

MAC

To Ethernet

10/100

Ethernet

PHY

Ethernet

System Con trol Block (SC B )

Interrup t

Controller

(INT)

Power

Management

(PM)

System Control &

Status Registers

(SCSR)

EEPROM

Controller

(EPC)

GPIO/LED

Controller

(GPIO)

GP Timer

Free-Run

Counter

3.3V to 1.8V

Regulator

PLL

LAN9420/LAN9420i

EEPROM

(optional)

GPIOs/LEDs

(optional)

+3.3V

25MHz

Figure 1.2 LAN9420/LAN9 420i Internal Block Diagram

SMSC LAN9420/LAN9420i 11 Revision 1.22 (09-25-08)

DATASHEET

Page 12

1.2 General Description

LAN9420/LAN9420i is a full-featured, Fast Ethernet controller which allows for the easy and costeffective integration of Fast Ethernet into a PCI-based system. A system configuration diagram of

LAN9420/LAN9420i in a typical embedded environment can be seen in Figure 1.1, followed by an

internal block diagram of LAN9420/LAN9420i in Figure 1.2. LAN9420/LAN9420i consists of a PCI

Local Bus Specification Revision 3.0 compliant interface

Ethernet PHY.

LAN9420/LAN9420i provides full IEEE 802.3 compliance and all internal compo nents support full/halfduplex 10BASE-T, 100BASE-TX, and manual full-duplex flow control. The descriptor based scattergather DMA supports usage of zero-copy drivers, effectively increasing throughput while decreasing

Host load. The integrated IRQ deassertion timer allows a minimum IRQ deassertion time to be set,

providing reduced Host load and greater control over service routines. Automatic 32-bit CRC

generation/checking, automatic payload padding, and 2K jumbo packets (2048 byte) are supported.

Big, little, and mixed endian support provides independent control over regi ster, descriptor, and buffer

endianess. This feature enables easy integration into various ARM/MIPS/PowerPC designs.

LAN9420/LAN9420i supports the PCI Bus Power Management Interface Specification Revision 1.1 and

provides the optional ability to generate wake events in the D3cold state when Vaux is available. Wake

on LAN, wake on link status change (energy detect), and magic packet wakeup detection are also

supported, allowing for a range of power management options.

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

, DMA Controller, Ethernet MAC, and 10/100

LAN9420/LAN9420i contains an EEPROM controller for connection to an optional EEPROM. This

allows for the automatic loading of static configuration data upon power-up or reset. When connected,

the EEPROM can be configured to load a predetermined MAC address, the PCI SSID, and the PCI

SSVID of LAN9420/LAN9420i.

In addition to the primary functionality described above, LAN9420/LAN9420i provides additional

features designed for extended functionality. These include a multipurpose 16-bit configurable General

Purpose Timer (GPT), a Free-Run Counter, a 3-pin configurable GPIO/LED interface, and 2 GPO pins.

All aspects of LAN9420/LAN9420i are managed via a set of memory mapped control and status

registers.

LAN9420/LAN9420i’s performance and features make it an ideal solution for many applications in the

consumer electronics, enterprise, and industrial automation markets. Targeted applications include: set

top boxes (cable, satellite and IP), digital televisions, digital video recorders, home gateways, digital

media clients/servers, industrial automation systems, industrial single board PCs, and kiosk/POS

enterprise equipment.

Revision 1.22 (09-25-08) 12 SMSC LAN9420/LAN9420i

DATASHEET

Page 13

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

1.3 PCI Bridge

LAN9420/LAN9420i implements a PCI Local Bus Specification Revision 3.0 compliant interface,

supporting the PCI Bus Power Management Interface Specification Revision 1.1. It provides the PCI

Configuration Space Control and Status registers used to configure LAN9420/LAN9420i for PCI de vice

operation. Please refer to Section 3.2, "PCI Bridge (PCIB)," on page 23 for more information.

1.4 DMA Controller

The DMA controller consists of independent Transmit and Receive engines and a control and status

register (CSR) space. The Transmit Engine transfers data from Host memory to the MAC Interface

Layer (MIL) while the Receive Engine transfers data from the MIL to Host memory. The controller

utilizes descriptors to efficiently move data from source to destination with minimal processor

intervention. Descriptors are DWORD aligned data structures in system memory that inform the DMA

controller of the location of data buffers in Host memory and also provide a mechanism for

communicating the status to the Host CPU. The DMA controller has been desig ned for packet-oriented

data transfer, such as frames in Ethernet. Zero copy DMA transfer is supported. Copy operations for

the purpose of data re-alignment are not required in the case where buffers are fragmented or not

aligned to a DWORD boundary. The controller can be programmed to interrupt the Host on the

occurrence of particular events, such as frame transmit or receive transfer completed, and other

normal, as well as error, conditions. Please refer to Section 3.4, "DMA Controller (DMAC)," on page 38

for more information.

1.5 Ethernet MAC

The transmit and receive data paths are separate within the 10/100 Ethernet MAC, allowi ng the hi ghest

performance, especially in full duplex mode. The data paths connect to the PCI Bridge via a DMA

engine. The MAC also implements a CSR space used by the Host to obtain status and control its

operation. The MAC Interface Layer (MIL), within the MAC, contains a 2K Byte transmit and receive

FIFO. The MIL supports store and forward and operate on second frame mode for minimum interpacket gap. Please refer to Section 3.5, "10/100 Ethernet MAC," on page 53 for more information.

1.6 Ethernet PHY

The PHY implements an IEEE 802.3 physical layer for twisted pair Ethernet applications. It can be

configured for either 100 Mbps (100BASE-TX) or 10 Mbps (10BASE-T) Ethernet operation in either full

or half duplex configurations. The PHY block includes support for auto-negotiation, auto-polarity

correction and Auto-MDIX. Minimal external components are required for the utilization of the

integrated PHY. Please refer to Section 3.6, "10/100 Ethernet PHY," on page 64 for more information.

1.7 System Control Block

The System Control Block provides the following additional elements for system operation. These

elements are controlled via its System Control and Status Registers (SCSR). Please refer to Section

3.3, "System Control Block (SCB)," on page 28 for more information.

1.7.1 Interrupt Controller

The Interrupt Controller (INT) can be programmed to issue a PCI interrupt to the Host on the

occurrence of various events. Please refer to Section 3.3.1, "Inte rrupt Controller," on page 28 for more

information.

SMSC LAN9420/LAN9420i 13 Revision 1.22 (09-25-08)

DATASHEET

Page 14

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

1.7.2 PLL and Power Management

LAN9420/LAN9420i interfaces with a 25MHz crystal oscillator from which all internal clocks, with the

exception of PCI clock, are generated. The internal clocks are all genera ted by the PLL and Power

Management blocks. Various power savings modes exists that allow for the clocks to be shut down.

These modes are defined by the power state of the PCI function. Please refer to Section 3.7 , "Power

Management," on page 73 for more information.

1.7.3 EEPROM Controller

LAN9420/LAN9420i provides support for an optional EEPROM via the EEPROM Controller. Please

refer to Section 3.3.5, "EEPROM Controller (EPC)," on page 31 for more information.

1.7.4 GPIO/LED Controller

The 3-bit GPIO and 2-bit GPO (Multiplexed on the LED and EEPROM Pins) interface is managed by

the GPIO/LED Controller. It is accessible via the System Control and Status Registers (SCSR). The

GPIO signals can function as inputs, push-pull outputs and open drain outputs. The GPIOs can also

be configured to trigger interrupts with programmable polarity. The GPOs are outputs only and have

no means of generating interrupts.

Please refer to Section 4.2.5, "General Purpose Input/Output Config uration Register (GPIO_CFG)," on

page 92 for more information.

Datasheet

1.7.5 General Purpose Timer

The General Purpose Timer has no dedicated function within LAN9420/LAN9420i and may be

programmed to issue a timed interrupt. Please refer to Section 3.3.3, "General Purpose Timer (GPT),"

on page 30 for more information.

1.7.6 Free Run Counter

The Free Run Counter has no dedicated function w ithin LAN9420/LAN9420i and may be used by the

software drivers as a timebase. Please refer to Section 3.3.4, "Free-Run Counter (FRC)," on page 31

for more information.

1.8 Control and Status Registers (CSR)

LAN9420/LAN9420i’s functions are controlled and monitored by the Host via the Con trol and Status

Registers (CSR). This register space includes registers that control and monitor the DMA controller

(DMA Control and Status Registers - DCSR), the MAC (MAC Control and Status Registers - MCSR),

the PHY (accessed indirectly through the MAC via the MII_ACCESS and MII_DATA registers), and the

elements of the System Control Block via the System Control and Status Registers (SCSR). The CSR

may be accessed be via I/O or memory operations. Big or Little Endian access is also configu rable.

Revision 1.22 (09-25-08) 14 SMSC LAN9420/LAN9420i

DATASHEET

Page 15

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Chapter 2 Pin Description and Configuration

NC

EECS

EECLK/GPO4

EEDIO/GPO3NCVDD33IONCAD0

VSS

AD2

AD1

AD4

AD3

VDD18CORE

VSS

VDD33IO

VSS

AD6

AD5

nCBE0

AD7

VDD33IO

AD8

AD9

VSS

AD11

AD10

AD12

AD13

VSS

VDD33IO

AD14

NC

NC

VSS

TPO-

TPO+

VSS

VDD33A

TPI-

NC

TPI+

VDD33A

VSS

EXRES

VSS

VDD33BIAS

NC

NC

NC

AUTOMDIX_EN

VDD18TX

VDD18PLL

VSS

XO

PWRGOOD

VAUXDET

GPIO0/nLED1

NC

NC

NC

NC

NC

96959493929190898887868584838281807978777675747372717069686766

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

XI

121

122

123

124

125

126

127

128

12345678910111213141516171819202122232425262728293031

VSS

VDD33IO

VDD33IO

VDD33IO

GPIO1/nLED2

GPIO2/nLED3

LAN9420/LAN9420i

VSS

VSS

VDD33IO

VDD18CORE

VDD18CORE

SMSC

128-VTQFP

TOP VIEW

VSS

nINT

VDD33IO

nGNT

nPME

nREQ

PCICLK

PCInRST

VSS

VDD33IO

AD30

AD31

AD29

VSS

AD28

AD27

AD26

VDD33IO

65

64

NC

63

NC

62

AD15

61

nCBE1

60

PAR

59

nSERR

58

VDD33IO

57

VSS

56

nPERR

55

nSTOP

54

nDEVSEL

53

nTRDY

52

nIRDY

51

VDD33IO

50

VSS

49

VSS

48

nFRAME

47

nCBE2

46

AD16

45

AD17

44

AD18

43

VDD33IO

42

VSS

41

AD19

40

AD20

39

AD21

38

AD22

37

AD23

36

VDD33IO

35

VSS

IDSEL

34

nCBE3

33

32

NC

AD24

AD25

NOTE: When H P A uto-MDIX is activated, the TPO+/- pins function as TPI+/- and vice-versa.

Figure 2.1 LAN9420/LAN9420i 128 -VTQFP (Top View)

SMSC LAN9420/LAN9420i 15 Revision 1.22 (09-25-08)

DATASHEET

Page 16

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

2.1 Pin List

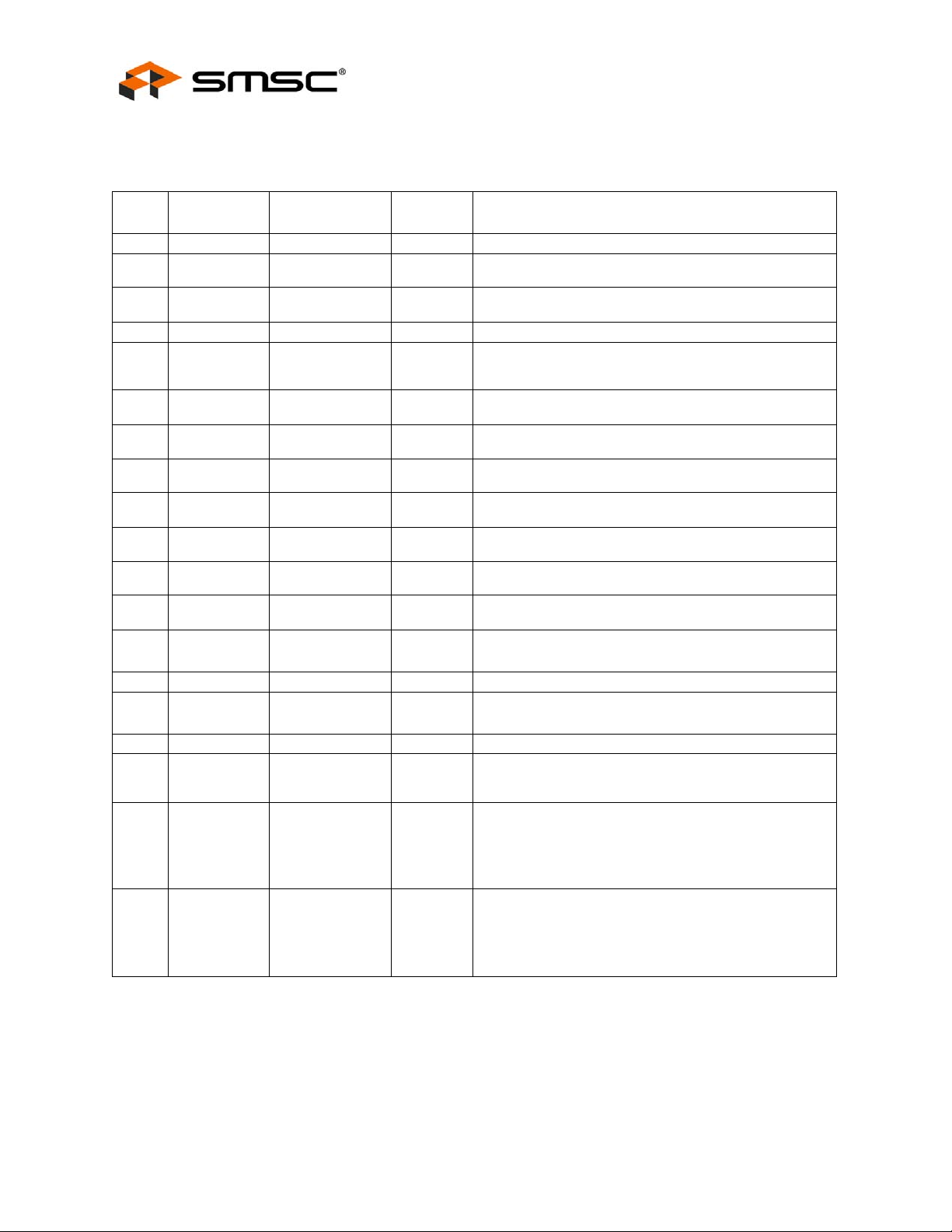

Table 2.1 PCI Bus Interface Pins

NUM

PINS NAME SYMBOL

1 PCI Clock In PCICLK IS PCI Clock In: 0 to 33MHz PCI Clock Input.

1 PCI Frame nFRAME IPCI/

32 PCI Address

and Data Bus

1 PCI Reset PCInRST IS PCI Reset

4PCI Bus

Command and

Byte Enables

1 PCI Initiator

1PCI Target

1 PCI Stop nSTOP IPCI/

1 PCI Device

1 PCI Parity PAR IPCI/

1PCI Parity

1 PCI System

1 PCI Interrupt nINT OPCI PCI Interrupt

1 PCI IDSEL IDSEL IPCI PCI IDSEL

1 PCI Request nREQ OPCI PCI Re quest

1PCI Grant nGNT IPCIPCI Grant

1 PCI Power

1 Power Good PWRGOOD IS

1V

Ready

Ready

Select

Error

Error

Management

Event

Detection VAUXDET IS

AUX

AD[31:0] IPCI/

nCBE[3:0] IPCI/

nIRDY IPCI/

nTRDY IPCI/

nDEVSEL IPCI/

nPERR IPCI/

nSERR IPCI/

nPME OPCI PCI Power Management Event

BUFFER

TYPE DESCRIPTION

OPCI

OPCI

OPCI

OPCI

OPCI

OPCI

OPCI

OPCI

OPCI

OPCI

(PD)

(PD)

PCI Cycle Frame

PCI Address and Data Bus

PCI Bus Command and Byte Enables

PCI Initiator Ready

PCI Target Ready

PCI Stop

PCI Device Select

PCI Parity

PCI Parity Error

PCI System Error

Note: This pin is an open drain output.

Note: This pin is a tri-state output.

Note: This pin is an open drain output.

PCI Bus Power Good: This pin is used to sense the

presence of PCI bus power during the D3 power

management state.

Note: This pin is pulled low through an internal pull-

down resistor

PCI Auxiliary Voltage Sense: This pin is used to sense

the presence of a 3.3V auxiliary supply in order to define

the PME support available.

Note: This pin is pulled low through an internal pull-

down resistor

Datasheet

Revision 1.22 (09-25-08) 16 SMSC LAN9420/LAN9420i

DATASHEET

Page 17

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

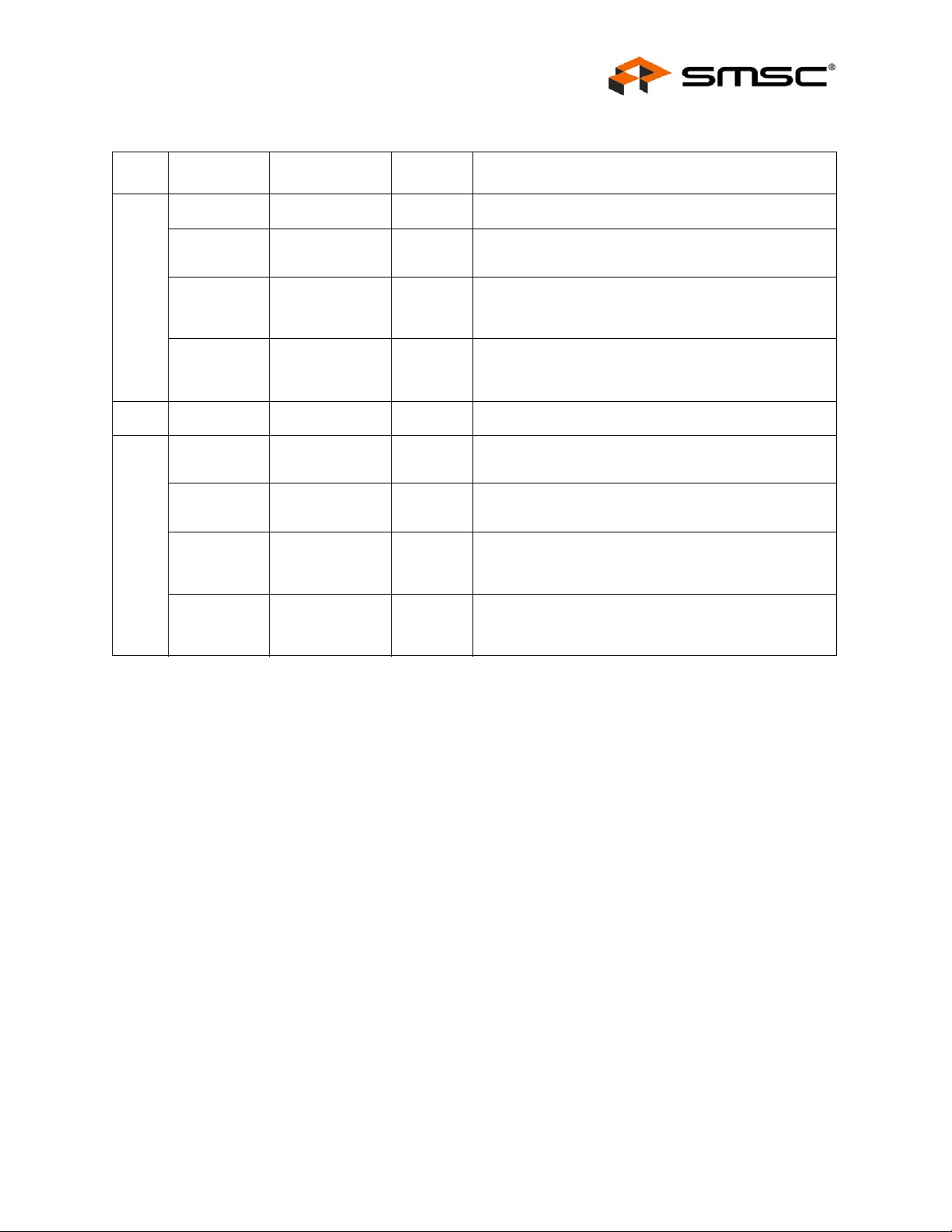

T able 2.2 EEPROM

NUM

PINS NAME SYMBOL

EEPROM Data EEDIO IS/O8 EEPROM Data: This bi-directional pin can be connected

GPO3 GPO3 O8 General Purpose Output 3: This pin can also function

1

TX_EN TX_EN O8 TX_EN Signal Monitor: This pin can also be configured

TX_CLK TX_CLK O8 TX_CLK Signal Monitor: This pin can also be configured

EEPROM Chip

1

Select

EEPROM

EECS O8 Serial EEPROM Chip Select.

EECLK IS/O8

Clock

GPO4 GPO4 O8 General Purpose Output 4: This pin can also function

1

RX_DV RX_DV O8 RX_DV Signal Monitor: This pin can also be configured

RX_CLK RX_CLK O8 RX_CLK Signal Monitor: This pin can also be

BUFFER

TYPE DESCRIPTION

to an optional serial EEPROM DIO.

as a general purpose output. The EECS pin is deasserted

so as to never unintentionally access the serial EEPROM.

to monitor the TX_EN signal on the internal MII port. The

EECS pin is deasserted so as to never unintentionally

access the serial EEPROM.

to monitor the TX_CLK signal on the internal MII port.

The EECS pin is deasserted so as to never

unintentionally access the serial EEPROM.

EEPROM Clock: Serial EEPROM Clock pin

(PU)

Note 2.1

as a general purpose output. The EECS pin is deasserted

so as to never unintentionally access the serial EEPROM.

to monitor the RX_DV signal on the internal MII port. The

EECS pin is deasserted so as to never unintentionally

access the serial EEPROM.

configured to monitor the RX_CLK signal on the internal

MII port. The EECS pin is deasserted so as to never

unintentionally access the serial EEPROM.

Note 2.1 This pin is used for factory testing and is latched on power up. This pin is pulled high

through an internal resistor and must not be pulled low externally. This pin must be

augmented with an external resistor when connected to a load. The value of the resistor

must be such that the pin reaches its valid level before de-assertion of PCInRST following

power up. The “IS” input buffer type is enabled only during power up. The “IS” input buffer

type is disabled at all other times.

SMSC LAN9420/LAN9420i 17 Revision 1.22 (09-25-08)

DATASHEET

Page 18

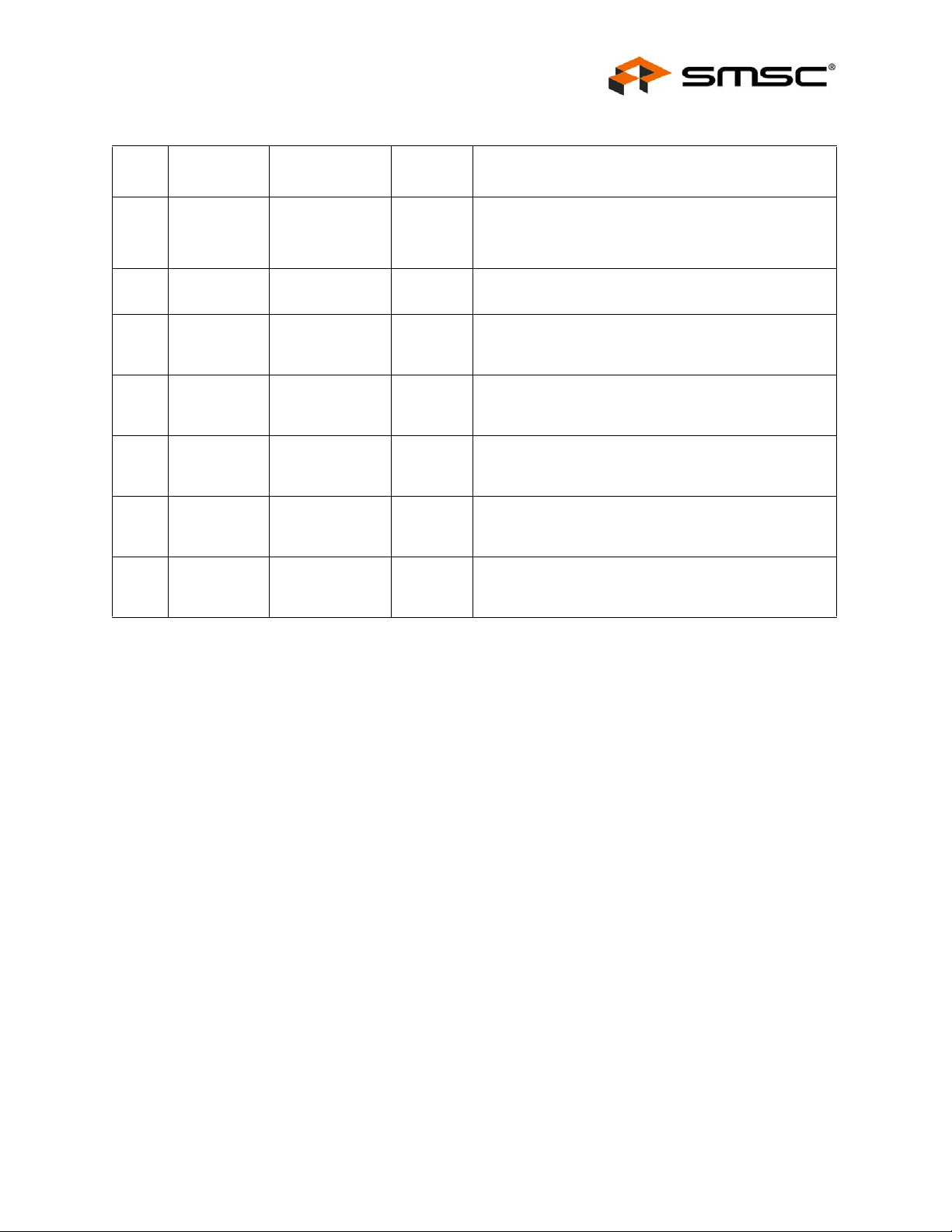

NUM

PINS NAME SYMBOL

General

GPIO0 IS/O12/

Purpose I/O

data 0

1

nLED1 (Speed

nLED1 OD12 nLED1 (Speed Indicator): This pin can also function as

Indicator)

General

GPIO1 IS/O12/

Purpose I/O

data 1

nLED2 (Link &

1

Activity

Indicator)

General

nLED2 OD12 nLED2 (Link & Activity Indicator): This pin can also

GPIO2 IS/O12/

Purpose I/O

data 2

1

nLED3 (Full-

nLED3 OD12 nLED3 (Full-Duplex Indicator): This pin can also

Duplex

Indicator)

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Ta bl e 2.3 GPIO and LED Pins

BUFFER

TYPE DESCRIPTION

General Purpose I/O data 0: This general-purpose pin is

OD12

fully programmable as either push-pull output, open-drain

output or input by writing the GPIO_CFG configuration

register in the SCSR. GPIO pins are Schmitt-triggered

inputs.

the Ethernet speed indicator LED and is driven low when

the operating speed is 100Mbs, during auto-negotiatio n,

and when the cable is disconnected. This pin is drive n

high only during 10Mbs operation.

General Purpose I/O data 1: This general-purpose pin is

OD12

fully programmable as either push-pull output, open-drain

output or input by writing the GPIO_CFG configuration

register in the SCSR. GPIO pins are Schmitt-triggered

inputs.

function as the Ethernet Link and Activity Indicator LED

and is driven low (LED on) when LAN9420/LAN9420i

detects a valid link. This pin is pulsed high (LED off) for

80mS whenever transmit or receive activity is detected.

This pin is then driven low again for a minimum of 80mS,

after which time it will repeat the process if TX or RX

activity is detected. Effectively, LED2 is activated solid for

a link. When transmit or receive activity is sensed, LED2

will flash as an activity indicator.

General Purpose I/O data 2: This general-purpose pin is

OD12

fully programmable as either push-pull output, open-drain

output or input by writing the GPIO_CFG configuration

register in the SCSR. GPIO pins are Schmitt-triggered

inputs.

function as the Ethernet Full-Duplex Indicator LED and is

driven low when the link is operating in full-duple x mode.

Datasheet

Table 2.4 Configuration Pins

NUM

PINS NAME SYMBOL

1

Enable

AutoMDIX

AUTOMDIX_EN IS

BUFFER

TYPE DESCRIPTION

AutoMDIX Enable: Enables Auto-MDIX. Pull high or

(PU)

leave unconnected to enable Auto-MDIX, pull low to

disable Auto-MDIX.

Revision 1.22 (09-25-08) 18 SMSC LAN9420/LAN9420i

DATASHEET

Page 19

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

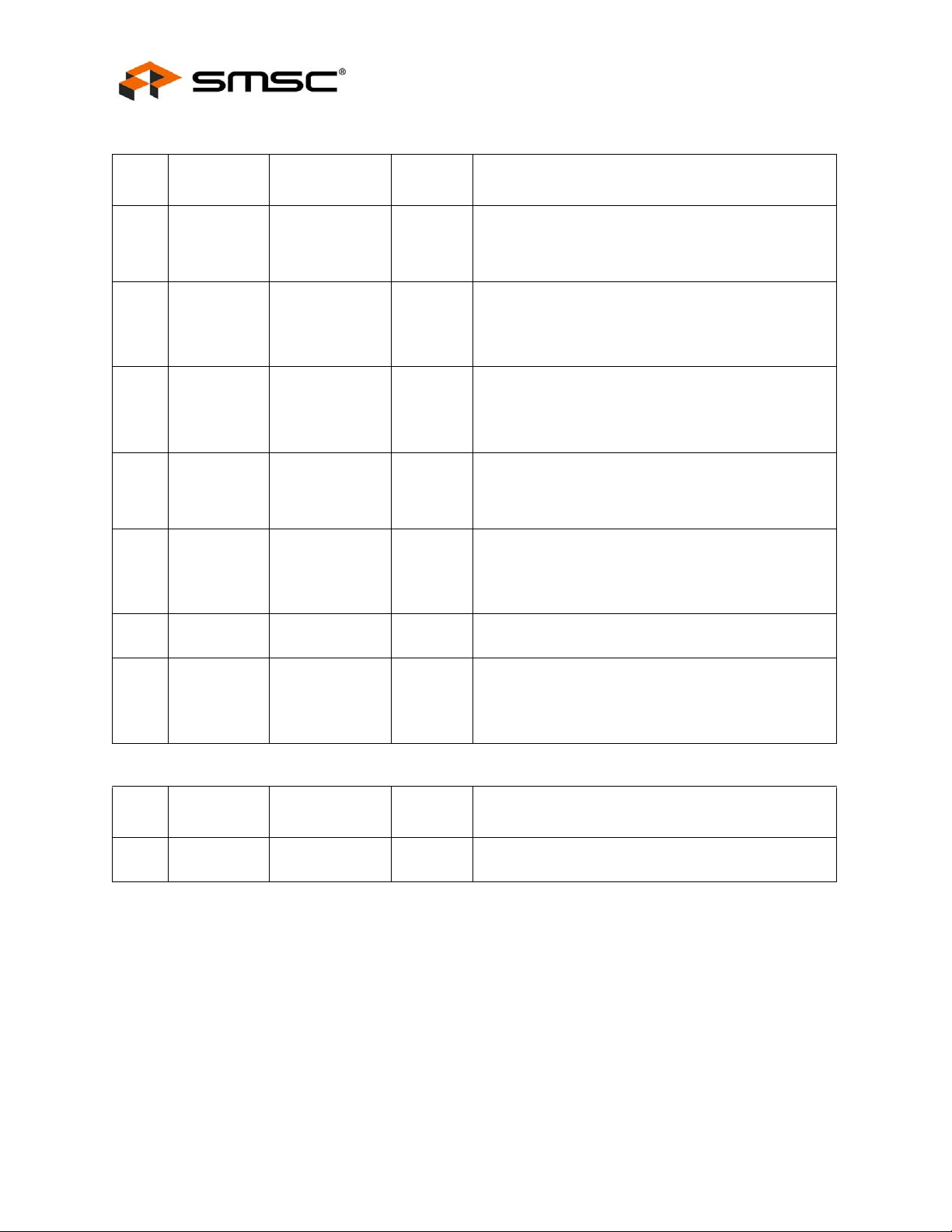

Table 2.5 PLL and Ethernet PHY Pins

NUM

PINS NAME SYMBOL

Crystal Input XI ICLK Crystal Input: External 25MHz crystal input. This pin

1

1

1

Crystal

Output

Ethernet TX

Data Out

XO OCLK Cry stal Output: External 25MHz crystal output.

TPO- AIO Ethernet Transmit Data Out Negative: The transmit

Negative

1

Ethernet TX

Data Out

TPO+ AIO Ethernet Transmit Data Out Positive: The transmit

Positive

1

Ethernet RX

Data In

TPI- AIO Etherne t Receive Data In Negative: The receive data

Negative

1

Ethernet RX

Data In

TPI+ AIO Ethernet Receive Data In Positive: The receive data

Positive

1

PHY Bias

External

EXRES AI External PHY Bias Resistor: Used for the internal

Resistor

BUFFER

TYPE DESCRIPTION

can also be driven by a single-ended clock oscillator.

When this method is used, XO should be left

unconnected.

data outputs may be swapped internally with receive

data inputs when Auto-MDIX is enabled.

data outputs may be swapped internally with receive

data inputs when Auto-MDIX is enabled.

inputs may be swapped internally with transmit data

outputs when Auto-MDIX is enabled.

inputs may be swapped internally with transmit data

outputs when Auto-MDIX is enabled.

PHY bias circuits. Connect to an external 12.4K 1.0%

resistor to ground.

SMSC LAN9420/LAN9420i 19 Revision 1.22 (09-25-08)

DATASHEET

Page 20

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Ta ble 2.6 Power and Ground Pins

Datasheet

NUM

PINS NAME SYMBOL

+3.3V

2

Analog

Power

VDD33A P +3.3V Analog Power Supply

Supply

+1.8V PLL

VDD18PLL P +1.8V PLL Power Supply: This pin must be connected

Power

1

1

1

Supply

+1.8V TX

Power

Supply

+3.3V

Master Bias

Power

VDD18TX P +1.8V Transmitter Power Supply: This pin must be

VDD33BIAS P +3.3V Master Bias Power Supply

Supply

15

+3.3V I/O

Power

VDD33IO P +3.3V Power Supply for I/O Pins and Internal

BUFFER

TYPE DESCRIPTION

Refer to the LAN9420/LAN9420i application note for

connection information.

to VDD18CORE for proper operation.

Refer to the LAN9420/LAN9420i application note for

additional connection information.

connected to VDD18CORE for proper operation.

Refer to the LAN9420/LAN9420i application note for

additional connection information.

Refer to the LAN9420/LAN9420i application note for

additional connection information.

Regulator

Refer to the LAN9420/LAN9420i application note for

additional connection information.

21 Ground VSS P Common Ground for I/O Pins, Core, and Analog

Circuitry

3

+1.8V Core

Power

VDD18CORE P Digital Core +1.8V Power Supply Output from

Internal Regulator

Refer to the LAN9420/LAN9420i application note for

additional connection information.

Table 2.7 No-Connect Pins

NUM

PINS NAME SYMBOL

BUFFER

TYPE DESCRIPTION

17 No Connect NC - No Connect: These pins must be left floating for

normal device operation.

Revision 1.22 (09-25-08) 20 SMSC LAN9420/LAN9420i

DATASHEET

Page 21

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

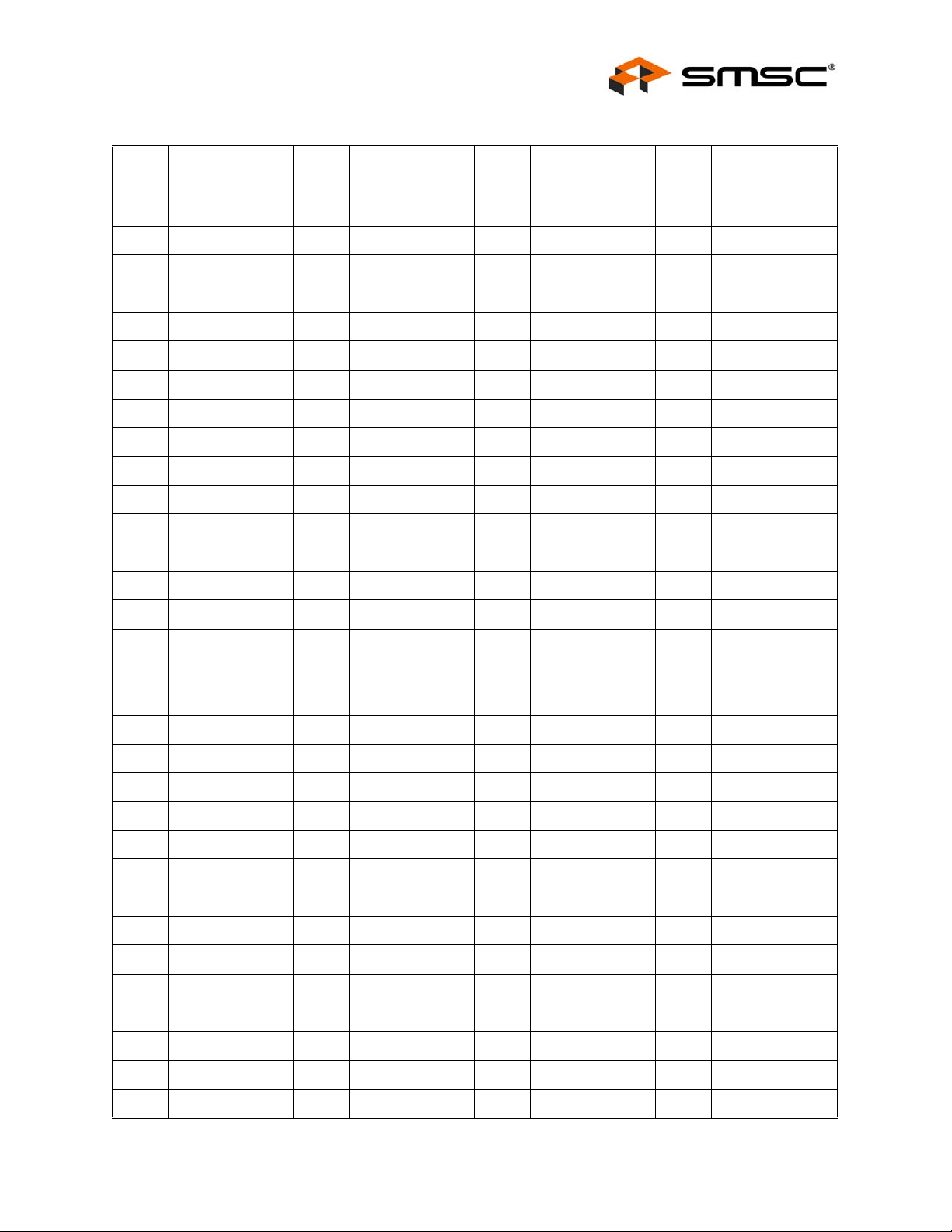

Table 2.8 128-VTQFP Package Pin Assignments

PIN

NUM PIN NAME

1 GPIO1/nLED2 33 nCBE3 65 AD14 97 NC

2 GPIO2/nLED3 34 IDSEL 66 VSS 98 NC

3 VDD33IO 35 VSS 67 VDD33IO 99 VSS

4 VSS 36 VDD33IO 68 AD13 100 TPO5 VDD33IO 37 AD23 69 AD12 101 TPO+

6 VDD33IO 38 AD22 70 AD11 102 VSS

7 VDD33IO 39 AD21 71 AD10 103 VDD33A

8 VDD18CORE 40 AD20 72 AD9 104 TPI9 VDD18CORE 41 AD19 73 VSS 105 NC

10 VSS 42 VSS 74 VDD33IO 106 TPI+

11 VSS 43 VDD33IO 75 AD8 107 VDD33A

12 VSS 44AD1876nCBE0108VSS

13VDD33IO45AD1777 AD7109EXRES

14 nINT 46 AD16 78 AD6 110 VSS

15 PCInRST 47 nCBE2 79 AD5 111 VDD33BIAS

PIN

NUM PIN NA ME

PIN

NUM PIN NAME

PIN

NUM PIN NAME

16 PCICLK 48 nFRAME 80 VSS 112 NC

17 nGNT 49 VSS 81 VDD33IO 113 NC

18 nREQ 50 VSS 82 VDD18CORE 114 NC

19 nPME 51 VDD33IO 83 VSS 115 AUTOMDIX_EN

20 VSS 52 nIRDY 84 AD4 116 VDD18TX

21 VDD33IO 53 nTRDY 85 AD3 117 VDD18PLL

22 AD31 54 nDEVSEL 86 AD2 118 VSS

23 AD30 55 nSTOP 87 AD1 119 XO

24 AD29 56 nPERR 88 AD0 120 XI

25 AD28 57 VSS 89 VSS 121 PWRGOOD

26 AD27 58 VDD33IO 90 VDD33IO 122 VAUXDET

27 VSS 59 nSERR 91 NC 123 GPIO0/nLED1

28 VDD33IO 60 PAR 92 EEDIO/GPO3 124 NC

29 AD26 61 nCBE1 93 NC 125 NC

30 AD25 62 AD15 94 EECS 126 NC

31 AD24 63 NC 95 EECLK/GPO4 127 NC

32 NC 64 NC 96 NC 128 NC

SMSC LAN9420/LAN9420i 21 Revision 1.22 (09-25-08)

DATASHEET

Page 22

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

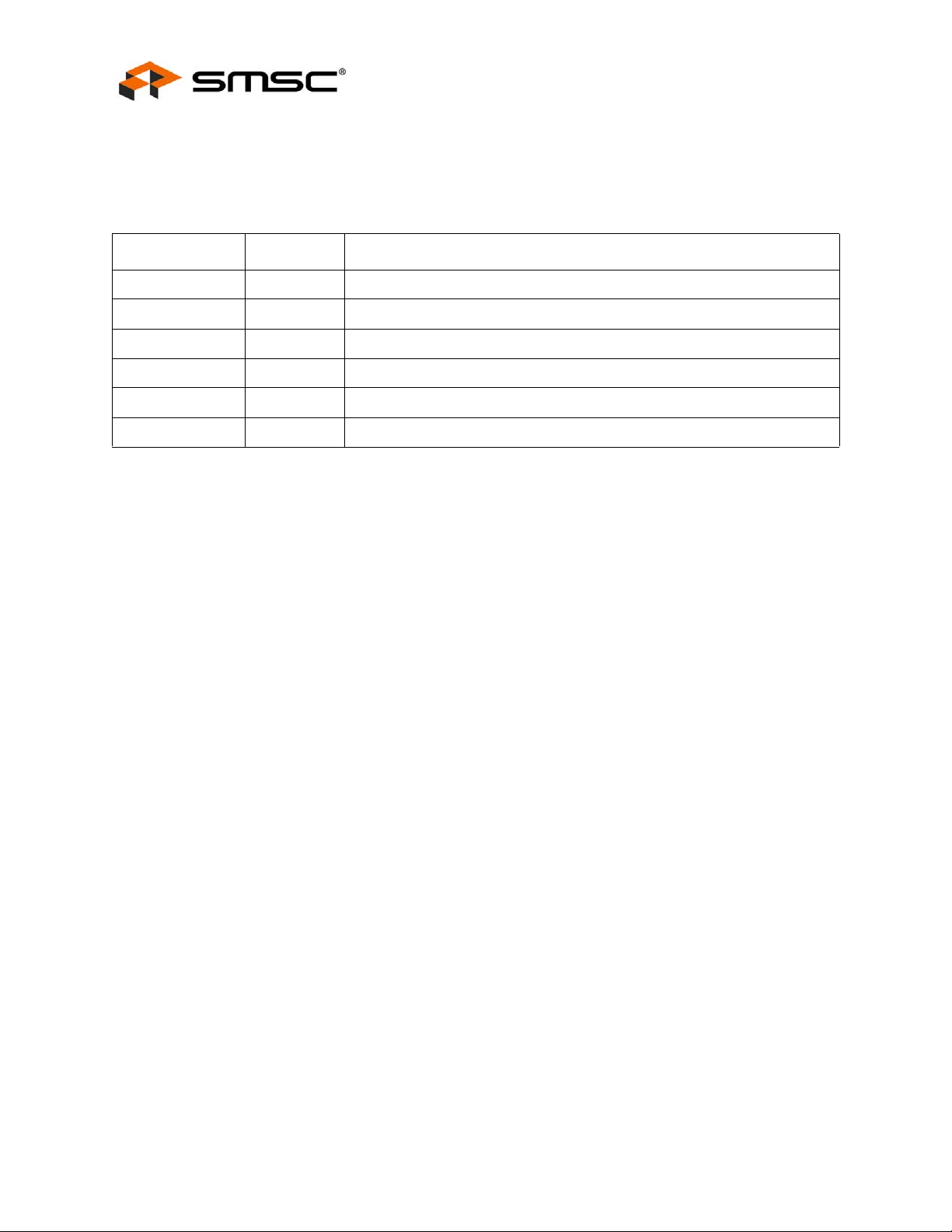

2.2 Buffer Types

BUFFER TYPE DESCRIPTION

IS Schmitt-triggered Input

O8 Output with 8mA sink and 8mA source curre nt

O12 Output with 12mA sink and 12mA source current

OD12 Open-drain output with 12mA sink current

IPCI PCI compliant Input

OPCI PCI compliant Output

Datasheet

PU 50uA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups

PD 50uA (typical) internal pull-down. Unless otherwise note d in the pin description, internal pull-

AI Analog Input

AIO Analo g bi-directional

ICLK Crystal oscillator input

OCLK Crystal oscillator output

P Power and Ground pin

are always enabled.

Note: Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on

internal resistors to drive signals external to LAN9420/LAN9420i. W hen connected

to a load that must be pulled high, an external resistor must be added.

downs are always enabled.

Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely

on internal resistors to drive signals external to LAN9420/LAN9420i. When

connected to a load that must be pulled low, an external resistor must be added.

Revision 1.22 (09-25-08) 22 SMSC LAN9420/LAN9420i

DATASHEET

Page 23

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Chapter 3 Functional Description

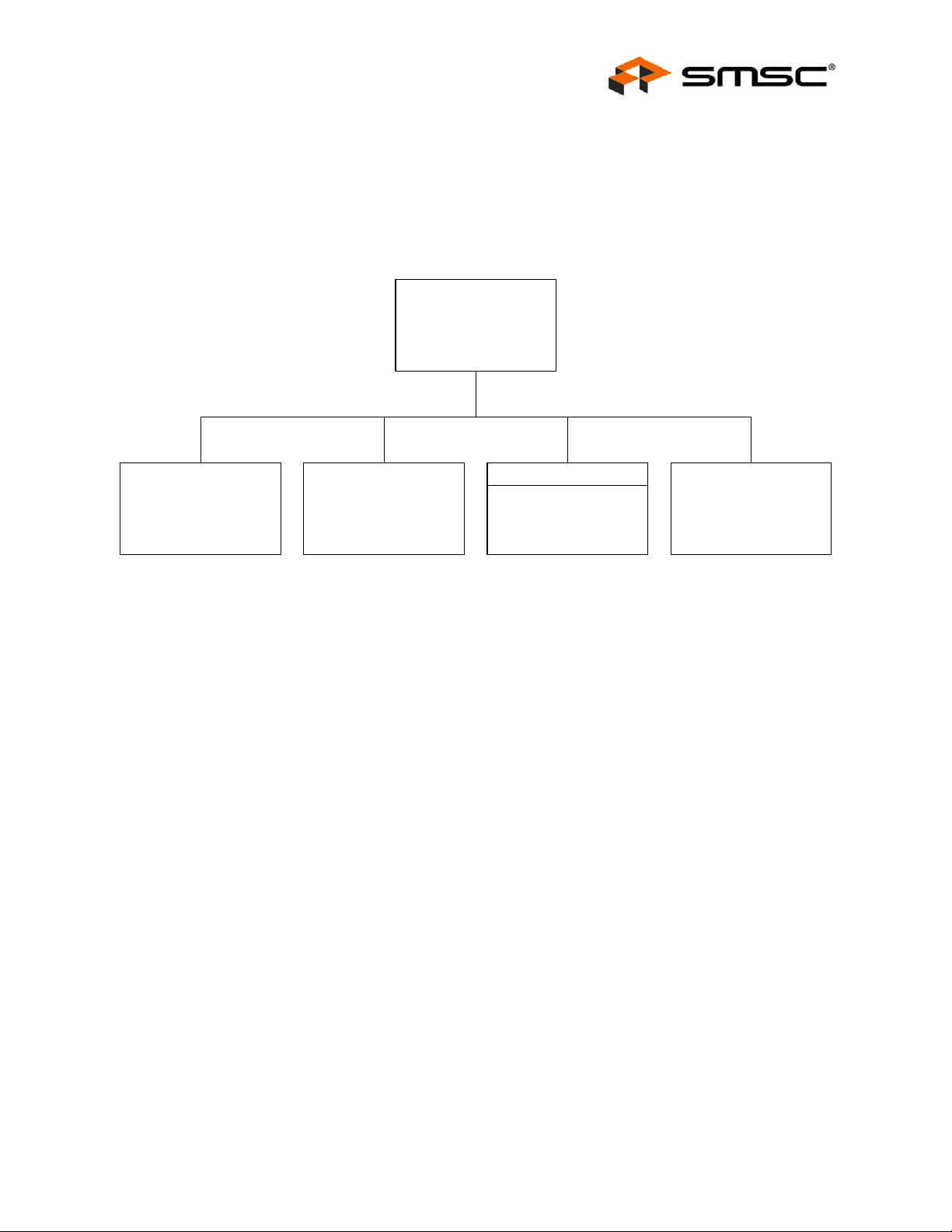

3.1 Functional Overview

The LAN9420/LAN9420i Ethernet Controller consists of five major fun ctional blocks. These blocks are:

PCI Bridge (PCIB)

System Control Block (SCB)

DMA Controller (DMAC)

10/100 Ethernet MAC

10/100 Ethernet PHY

The following sections discuss the features of each block. A block diagram of LAN9420/LAN 9420i is

shown in Figure 1.2 LAN9420/LAN 9420i Internal Block Diagram on page 11.

3.2 PCI Bridge (PCIB)

The PCI Bridge (PCIB) facilitates LAN9420/LAN9420i’s operation on a PCI bus as a device. It has the